# Reconfigurable Impedance Matching Networks Based on RF-MEMS and CMOS-MEMS Technologies

by

Siamak Fouladi Azarnaminy

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2010

© Siamak Fouladi Azarnaminy 2010

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Siamak Fouladi Azarnaminy

#### Abstract

Reconfigurable impedance matching networks are an integral part of multiband radiofrequency (RF) transceivers. They are used to compensate for the input/output impedance variations between the different blocks caused by switching the frequency band of operation or by adjusting the output power level. Various tuning techniques have been developed to construct tunable impedance matching networks employing solid-state p-i-n diodes and varactors. At millimeter-wave frequencies, the increased loss due to the low quality factor of the solid-state devices becomes an important issue. Another drawback of the solid-state tuning elements is the increased nonlinearity and noise at higher RF power levels.

The objective of the research described in this thesis is to investigate the feasibility of using RF microelectromechanical systems (RF-MEMS) technology to develop reconfigurable impedance matching networks. Different types of tunable impedance matching networks with improved impedance tuning range, power handling capability, and lower insertion loss have been developed. Another objective is to investigate the realization of a fully integrated one-chip solution by integrating MEMS devices in standard processes used for RF integrated circuits (RFICs).

A new CMOS-MEMS post-processing technique has been developed that allows the integration of tunable RF MEMS devices with vertical actuation within a CMOS chip. Various types of CMOS-MEMS components used as tuning elements in reconfigurable RF transceivers have been developed. These include tunable parallel-plate capacitors that outperform the available CMOS solid-state varactors in terms of quality factor and linearity. A tunable microwave band-pass filter has been demonstrated by employing the proposed RF MEMS tunable capacitors. For the first time, CMOS-MEMS capacitive type switches for microwave and millimeter-wave applications have been developed using TSMC 0.35-µm CMOS process employing the proposed CMOS-MEMS integration technique. The switch demonstrates an excellent RF performance from 10-20 GHz.

Novel MEMS-based reconfigurable impedance matching networks integrated in standard CMOS technologies are also presented. An 8-bit reconfigurable impedance matching network based on the distributed MEMS transmission line (DMTL) concept operating at 13-24 GHz is presented. The network is implemented using standard 0.35-µm CMOS technology and employs a novel suspended slow-wave structure on a silicon substrate. To our knowledge, this is the first implementation of a DMTL tunable MEMS impedance matching network using a standard CMOS technology. A reconfigurable amplifier chip for WLAN applications operating at 5.2 GHz is also designed and implemented. The amplifier achieves maximum power gain under variable load and source impedance conditions by using the integrated RF-MEMS impedance matching networks. This is the first single-chip implementation of a reconfigurable amplifier using high-Q MEMS impedance matching networks. The monolithic CMOS implementation of the proposed RF MEMS impedance matching networks enables the development of future low-cost single-chip RF multiband transceivers with improved performance and functionality.

#### Acknowledgements

I would like to sincerely thank my advisor Professor Raafat Mansour, for all his support throughout my cherished years at the University of Waterloo. His guidance and advice have had a major impact on the final outcome of this thesis. He will be a life-long role model for me and I will try to follow in his footsteps. I am also grateful to the members of my committee, Professor Safavi-Naeini, Professor Siva Sivoththaman, and Professor Patricia Nieva for the knowledge they provided during my research and Professor John Papapolymerou from the School of Electrical and Computer Engineering at Georgia Institute of Technology for taking the time to serve as my external examiner.

It was such a great opportunity for me to be a member of the Centre for Integrated RF Engineering (CIRFE), a research group which has attracted many talents. I would like to recognize my colleague Dr. Frédéric Domingue for his help especially during the last year of my study, Arash Akhavan Fomani for his valuable discussions. Many thanks go to Dr. Maher Bakri-Kassem, Dr. Winter Yan and Nino Zahirovic for all their support when I needed them, Dr. Reena Al-Dahleh and Dr. Mojgan Daneshmand for their guidance during the beginning stages of my research. I am also indebted to Bill Jolley, the CIRFE lab manager, for his support and friendship. I also want to deeply acknowledge the special people who have become my friends during these years and their kindness and support have contributed a great part to my life.

I would like to acknowledge the financial support from Natural Sciences and Engineering Research Council of Canada (NSERC), COM DEV International Ltd., and Canadian Microelectronics Corporation (CMC). Their contribution is greatly appreciated.

Last but not least I would like to thank my parents as well my brothers and my uncle for their support and encouragement that allowed me to meet this important goal in my life.

# Contents

| Li | ist of Tables                |                                                    |    |  |

|----|------------------------------|----------------------------------------------------|----|--|

| Li | st of                        | Figures                                            | xx |  |

| 1  | Intr                         | roduction                                          | 1  |  |

|    | 1.1                          | Motivation                                         | 1  |  |

|    | 1.2                          | Objectives                                         | 2  |  |

|    | 1.3                          | Thesis Outline                                     | 5  |  |

| 2  | $\operatorname{Lit}\epsilon$ | erature Survey                                     | 6  |  |

|    | 2.1                          | Reconfigurable Impedance Matching Networks         | 6  |  |

|    |                              | 2.1.1 MEMS Tuning Method                           | 7  |  |

|    |                              | 2.1.2 Electronic Tuning Method                     | 14 |  |

|    |                              | 2.1.3 Tuning Using Ferroelectric Varactors         | 16 |  |

|    | 2.2                          | Adaptive Amplifiers and Automatic Matching Systems | 18 |  |

|    | 2.3                          | Integrated CMOS-MEMS Devices                       | 21 |  |

| 3 | $\mathbf{RF}$          | MEMS                                                           | S Tunable Impedance Matching Networks                            | 28 |  |  |

|---|------------------------|----------------------------------------------------------------|------------------------------------------------------------------|----|--|--|

|   | 3.1                    | Introd                                                         | uction                                                           | 28 |  |  |

|   | 3.2                    | Imped                                                          | ance Matching Network Using Dual-Beam MEMS Switches              | 30 |  |  |

|   |                        | 3.2.1                                                          | Design and Analysis                                              | 30 |  |  |

|   |                        | 3.2.2                                                          | Fabrication Process                                              | 35 |  |  |

|   |                        | 3.2.3                                                          | Experimental Results                                             | 37 |  |  |

|   | 3.3                    | Match                                                          | ing Network Using DGS structure                                  | 43 |  |  |

|   |                        | 3.3.1                                                          | Design and Analysis                                              | 44 |  |  |

|   |                        | 3.3.2                                                          | Fabrication Process                                              | 51 |  |  |

|   |                        | 3.3.3                                                          | Experimental Results                                             | 54 |  |  |

|   | 3.4                    | Summ                                                           | ary                                                              | 62 |  |  |

| 4 | $\mathbf{C}\mathbf{M}$ | IOS-MEMS Integration and RF-MEMS Devices Fabricated using This |                                                                  |    |  |  |

|   |                        | cess                                                           |                                                                  | 63 |  |  |

|   | 4.1                    | Introd                                                         | uction                                                           | 63 |  |  |

|   | 4.2                    | CMOS                                                           | S-MEMS Integration                                               | 65 |  |  |

|   | 4.3                    | CMOS                                                           | S-MEMS Tunable Capacitors                                        | 73 |  |  |

|   | 4.4                    | Microv                                                         | wave Tunable Bandpass Filter Integrated in CMOS Technology       | 81 |  |  |

|   | 4.5                    | Capac                                                          | itive RF MEMS Switches Fabricated using Standard CMOS Technology | 86 |  |  |

|   |                        | 4.5.1                                                          | Introduction                                                     | 86 |  |  |

|   |                        | 4.5.2                                                          | Switch Design                                                    | 87 |  |  |

|   |                        | 453                                                            | Fabrication                                                      | 91 |  |  |

|   |      | 4.5.4   | Mechanical Simulation Results                                      | 91      |

|---|------|---------|--------------------------------------------------------------------|---------|

|   |      | 4.5.5   | EM Simulation Results                                              | 96      |

|   |      | 4.5.6   | Measurement Results                                                | 98      |

|   |      | 4.5.7   | Cascaded Switch                                                    | 100     |

|   | 4.6  | Summ    | ary                                                                | 104     |

| 5 | Rec  | onfigu  | rable MEMS Impedance Matching Networks Fabricated b                | ${f y}$ |

|   | Star | ndard   | CMOS Technologies                                                  | 107     |

|   | 5.1  | Introd  | uction                                                             | 107     |

|   | 5.2  | Distrib | buted MEMS Tunable Impedance Matching Network Based on Sus-        |         |

|   |      | pende   | d Slow-Wave Structure Fabricated in 0.35-µm CMOS Technology $$     | 109     |

|   |      | 5.2.1   | Design and Optimization                                            | 109     |

|   |      | 5.2.2   | CMOS Implementation                                                | 111     |

|   |      | 5.2.3   | Suspended Slow-Wave Transmission Line                              | 115     |

|   |      | 5.2.4   | DMTL Unit Cell                                                     | 120     |

|   |      | 5.2.5   | Impedance Coverage                                                 | 121     |

|   |      | 5.2.6   | Experimental Results                                               | 124     |

|   |      | 5.2.7   | Loss Analysis                                                      | 126     |

|   |      | 5.2.8   | Impedance Coverage and Power Transfer                              | 126     |

|   |      | 5.2.9   | Intermodulation Distortion                                         | 130     |

|   | 5.3  | Recon   | figurable Amplifier with Tunable Matching Networks in 0.18-μm CMOS | }       |

|   |      | Techn   | ology                                                              | 133     |

|   |      | 5.3.1   | CMOS-MEMS Process for the 0.18-um CMOS Technology                  | 133     |

|                |       | 5.3.2  | Reconfigurable Amplifier Design | 134 |

|----------------|-------|--------|---------------------------------|-----|

|                |       | 5.3.3  | Experimental Results            | 137 |

|                | 5.4   | Summ   | ary                             | 140 |

| _              | ~     |        |                                 |     |

| 6              | Con   | clusio | ns                              | 142 |

|                | 6.1   | Contri | butions                         | 142 |

|                | 6.2   | Future | e Work                          | 145 |

|                |       |        |                                 |     |

| $\mathbf{A}$ ] | PPE]  | NDICI  | ${f ES}$                        | 148 |

| $\mathbf{A}$   | List  | of Ac  | ronyms                          | 149 |

| Bi             | bliog | graphy |                                 | 149 |

# List of Tables

| 3.1 | tri-state MEMS switch and DMTL line parameters                            | 35  |

|-----|---------------------------------------------------------------------------|-----|

| 3.2 | Equivalent circuit model parameters of the DMTL unit-cell extracted from  |     |

|     | the measured S-parameters                                                 | 39  |

| 3.3 | Geometrical parameters and the equivalent circuit model parameters        | 49  |

| 4.1 | RIE etch parameters for the first CMOS-MEMS processing step               | 69  |

| 4.2 | RIE etch parameters for the isotropic silicon etching                     | 71  |

| 4.3 | Comparison between the developed CMOS-MEMS tunable capacitors and         |     |

|     | MOS varactors in CMOS technology                                          | 80  |

| 5.1 | Design parameters for the DMTL matching network operating from 13-24      |     |

|     | GHz                                                                       | 110 |

| 5.2 | Geometrical parameters of the CPW, S-CPW, and SSW-CPW lines $\ . \ . \ .$ | 117 |

| 5.3 | The equivalent circuit model parameters of the DMTL unit-cell extracted   |     |

|     | from EM simulation results                                                | 121 |

| 5.4 | The equivalent circuit model parameters of the DMTL unit-cell extracted   |     |

|     | from the measured S-parameters                                            | 124 |

| 5.5 | Optimum Source and Load Impedances                                        | 135 |

| 6.1 | Comparison   | between    | the   | developed      | MEMS  | tunable | impedance | matching |     |

|-----|--------------|------------|-------|----------------|-------|---------|-----------|----------|-----|

|     | networks and | d other re | eport | ed technologie | ogies |         |           |          | 146 |

# List of Figures

| 2.1 | (a) Block diagram of an adaptive LC matching network and (b) die photograph of the MEMS capacitor bank [1]                                                          | 7  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | (a) Schematic circuit diagram and (b) measured impedance coverage of the analog impedance tuner in [2]                                                              | 8  |

| 2.3 | (a) Schematic circuit diagram and (b) measured impedance coverage of the digital impedance tuner in [2]                                                             | ć  |

| 2.4 | Photograph of (a) single-stub impedance tuner and (b) switched MEMS capacitor (c) circuit diagram and (d) impedance coverage at 40 GHz [4].                         | 10 |

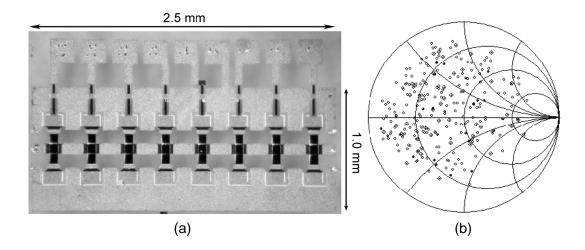

| 2.5 | (a) Photograph and (b) impedance coverage of the reconfigurable impedance matching network based on DMTL structure with 8 switched MEMS capacitors at 40 GHz [9]    | 11 |

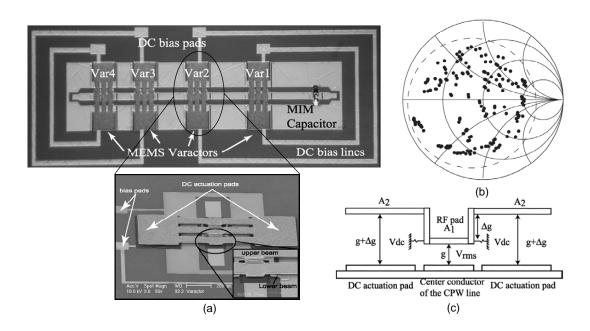

| 2.6 | (a) SEM of the impedance tuner with high-power MEMS varactors, (b) the measured impedance coverage at 30 GHz, and (c) a cross section of the MEMS varactor [11, 12] | 12 |

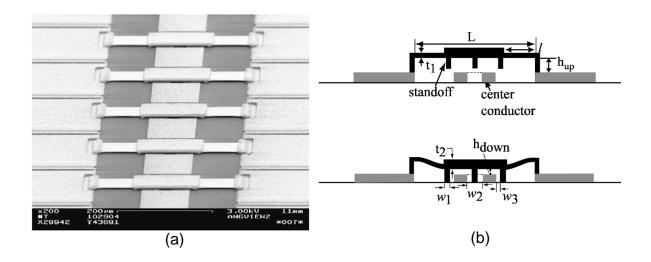

| 2.7 | (a) SEM and (b) cross-section view of the minimal-contact varactor [13]                                                                                             | 13 |

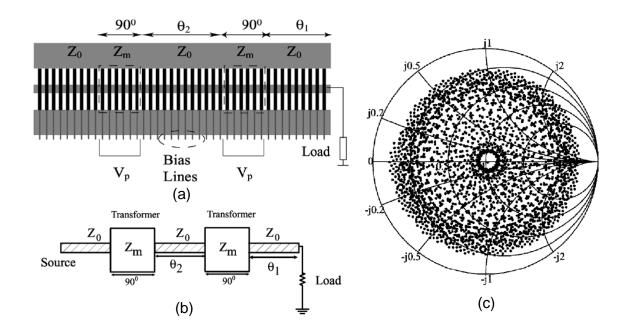

| 2.8 | <ul><li>(a) Topology and (b) schematic diagram of the double-slug impedance tuner,</li><li>(c) measured impedance coverage at 27.8 GHz [13]</li></ul>               | 14 |

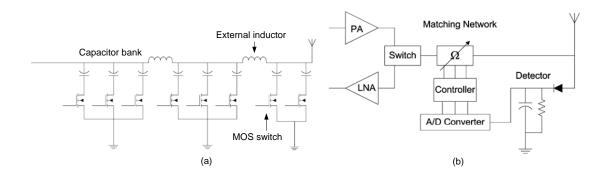

| 2.9  | (a) Circuit diagram of the impedance tuner for ISM 2.4 GHz band and (b)            |    |

|------|------------------------------------------------------------------------------------|----|

|      | system block diagram of the antenna tuning unit (ATU) [22]                         | 15 |

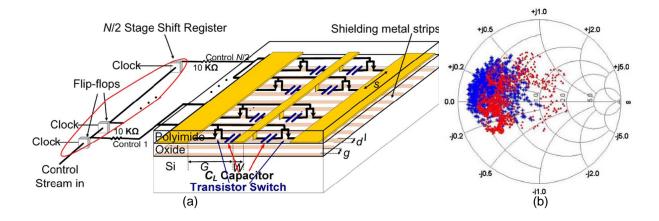

| 2.10 | (a) Structure of the CMOS tuner based on switched capacitors and (b)               |    |

|      | measured impedance coverage at 10 GHz for tuners with a transmission line          |    |

|      | length of 1.6 mm (blue asterisks) and 3.6 mm (red triangles) [23]                  | 16 |

| 2.11 | (a) A typical interdigitated BST varactor, (b) the measured C-V character-         |    |

|      | istic and $Q$ -factor at 2 GHz [24]                                                | 17 |

| 2.12 | (a) Circuit diagram of the double stub matching networks and the photo-            |    |

|      | graph of the adaptive amplifier [29]                                               | 18 |

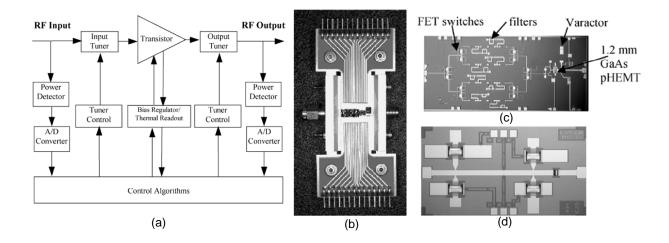

| 2.13 | (a) Block diagram of the intelligent power amplifier, (b) picture of the over-     |    |

|      | all system, (c) transistors and active circuitry (d) output MEMS matching          |    |

|      | network [30]                                                                       | 19 |

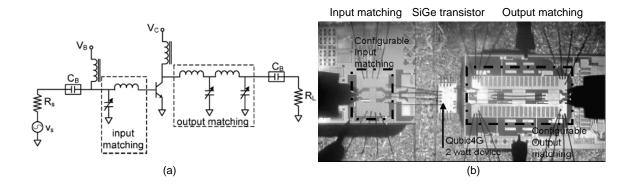

| 2.14 | (a) Block diagram and (b) microphotograph of the multiband power ampli-            |    |

|      | fier in [16]                                                                       | 20 |

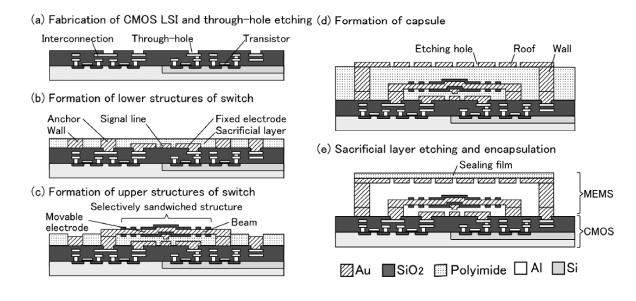

| 2.15 | Process flow for the CMOS-compatible MEMS process in [31]                          | 21 |

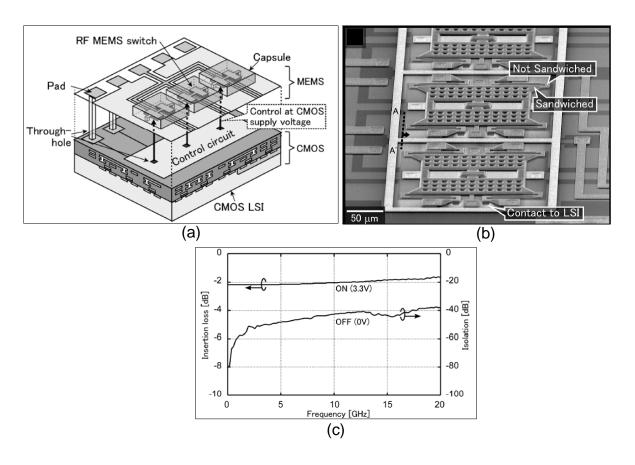

| 2.16 | (a) Schematic view, (b) SEM image and (c) measured S-parameters of the             |    |

|      | CMOS-MEMS switth [31]                                                              | 22 |

| 2.17 | Process flow for CMOS-MEMS processing at CMU (a) before applying the               |    |

|      | processing (b) after anisotropic oxide etching (c) after anisotropic silicon       |    |

|      | etching and (d) after isotropic etching of the silicon substrate and release [32]. | 23 |

| 2.18 | SEM image of the CMOS-MEMS tunable capacitor [35]                                  | 24 |

| 2.19 | (a) SEM image and circuit diagram of the tunable bandpass filter (b) S-            |    |

|      | parameters [38]                                                                    | 25 |

| 2.20 | (a) Cantilever micromechanical resonator and (b) square frame resonators           |    |

|      | fabricated by CMOS-MEMS technology [37, 39]                                        | 26 |

| 2.21 | (a) 3-D view, (b) SEM image and (c) S-parameters of the CMOS RF MEMS switch [41]                                                                                                          | 27       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

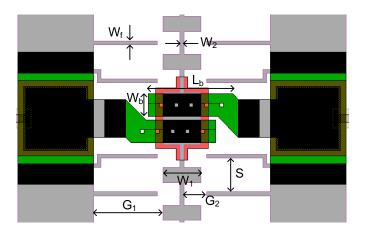

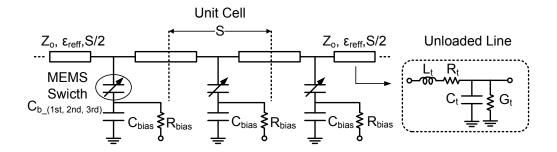

| 3.1  | (a) Schematic view of the conventional DMTL structure with MEMS switches and (b) equivalent circuit diagram                                                                               | 31       |

| 3.2  | Pie shaped sub-sections used to estimate the uniformity factor                                                                                                                            | 32       |

| 3.3  | Layout of the proposed unit cell, $G_1$ =185 $\mu$ m, $G_2$ =60 $\mu$ m, $W_1$ =100 $\mu$ m, $W_2$ =10 $\mu$ m, $W_f$ =10 $\mu$ m, $S$ =90 $\mu$ m, $W_b$ =60 $\mu$ m, $U_b$ =240 $\mu$ m | n,<br>34 |

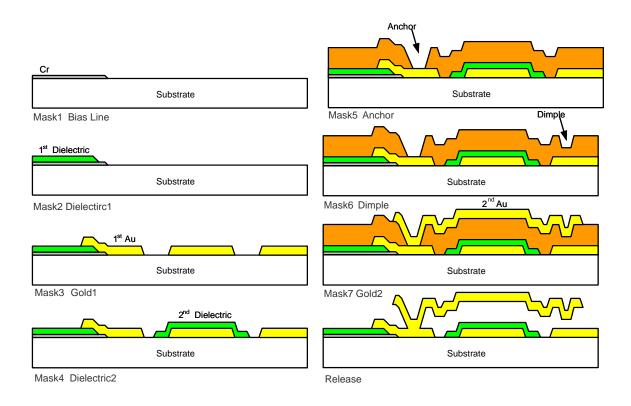

| 3.4  | UW-MEMS fabrication process steps                                                                                                                                                         | 36       |

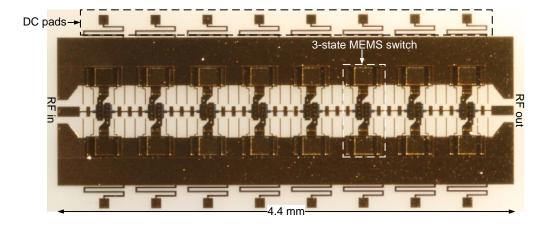

| 3.5  | Photograph of the fabricated impedance matching network                                                                                                                                   | 36       |

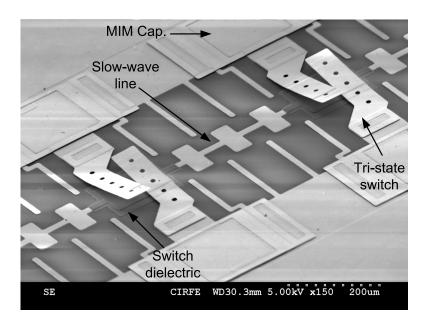

| 3.6  | SEM image of the tri-state MEMS switch                                                                                                                                                    | 37       |

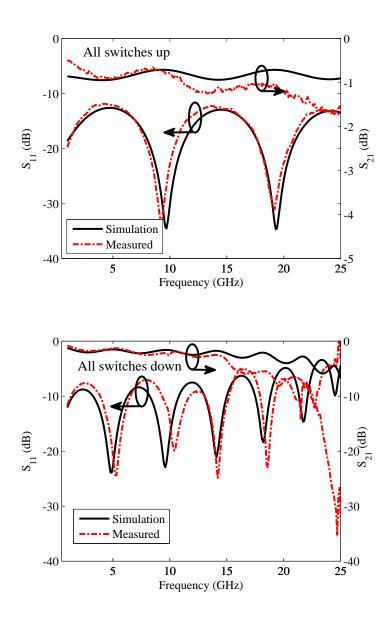

| 3.7  | Measured v.s. simulated S-parameters of the fabricated impedance matching network for two different states of the MEMS switches                                                           | 38       |

| 3.8  | Equivalent circuit model of the matching network with 3-state MEMS switches.                                                                                                              | 39       |

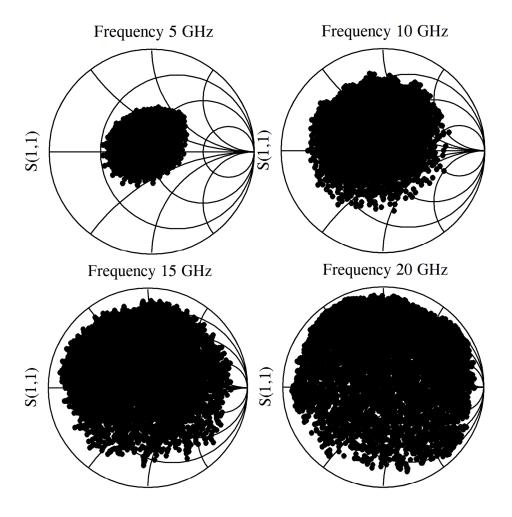

| 3.9  | Measured impedance coverage of the matching network                                                                                                                                       | 40       |

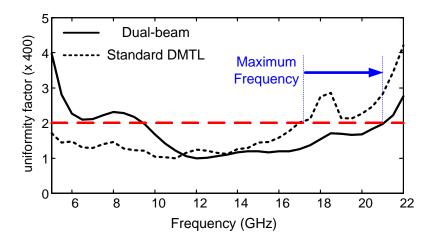

| 3.10 | Measured uniformity factor of the matching network with tri-state MEMS switches compared to a standard DMTL network                                                                       | 41       |

| 3.11 | Measured return loss performance of the network at (a) 5 GHz, (b) 10 GHz, (c) 15 GHz and (d) 20 GHz                                                                                       | 42       |

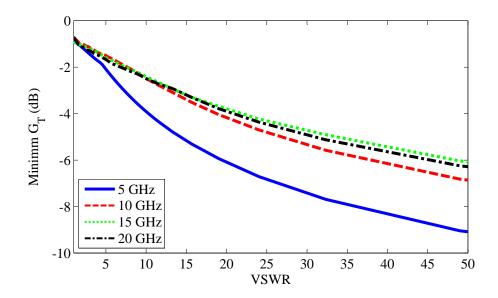

| 3.12 | Measured minimum power transfer ratio of the fabricated network versus VSWR at different frequencies                                                                                      | 43       |

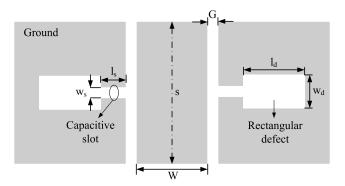

| 3.13 | Layout of the DGS unit cell, $l_s$ and $w_s$ are the slot dimensions, $l_d$ and $w_d$ are the rectangular defect dimensions and $W$ and $G$ are the CPW transmission                      | , ,      |

|      | line dimensions                                                                                                                                                                           | 44       |

| 3.14 | Equivalent circuit model of the DGS structure                                                                                                                                                          | 45 |

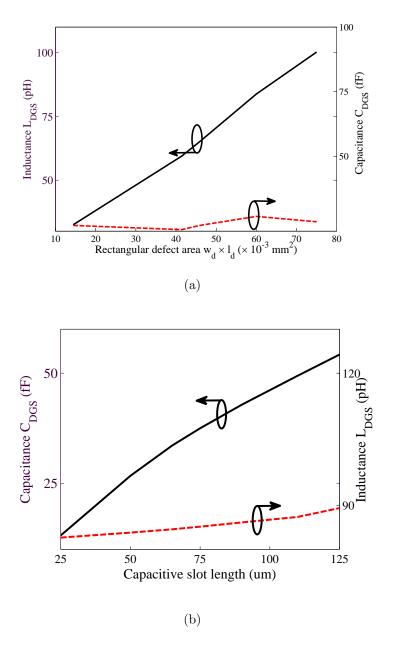

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.15 | $L_{DGS}$ and $C_{DGS}$ as a function of the (a) rectangular defect area $w_d \times l_d$ , $l_s$ = 50 $\mu$ m and (b) the capacitive slot length $l_s$ , $w_d$ = 200 $\mu$ m and $l_d$ = 300 $\mu$ m. | 46 |

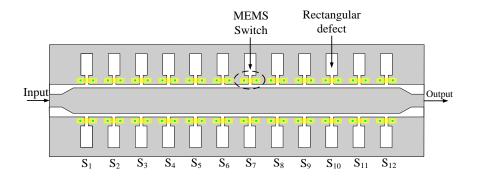

| 3.16 | Schematic of the reconfigurable impedance matching network with DGS and                                                                                                                                | 47 |

| 9 17 | MEMS contact switches                                                                                                                                                                                  | 47 |

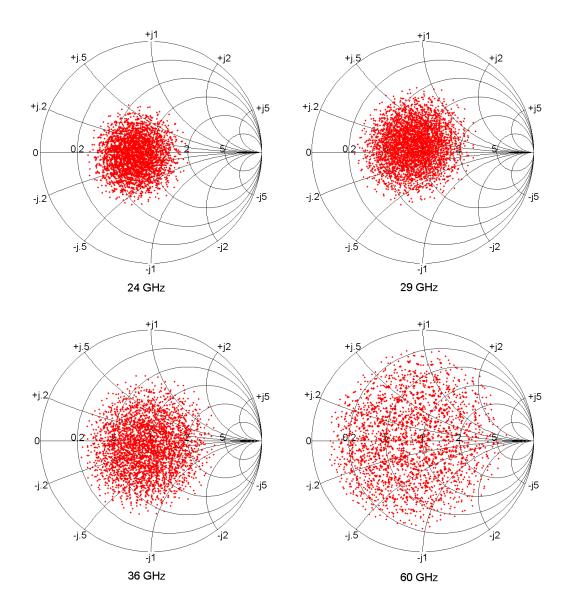

| 3.17 | Calculated impedance coverage of the DGS impedance matching network at different frequencies from 24 to 60 GHz.                                                                                        | 50 |

| 3.18 |                                                                                                                                                                                                        |    |

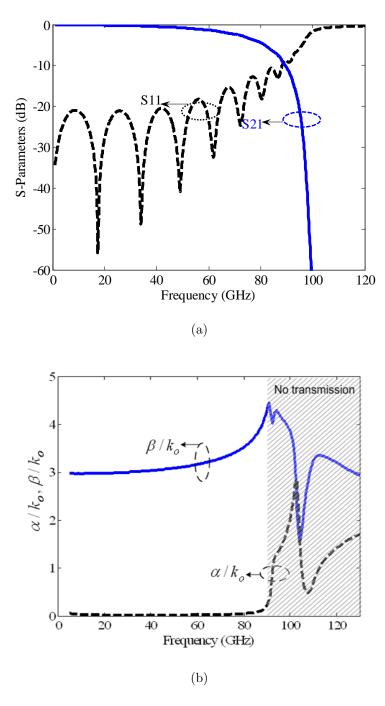

|      | riodic DGS structure                                                                                                                                                                                   | 52 |

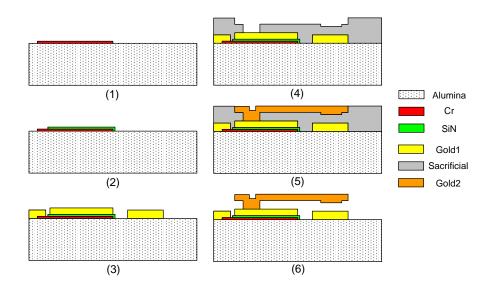

| 3.19 | The fabrication process for the DGS impedance matching network                                                                                                                                         | 53 |

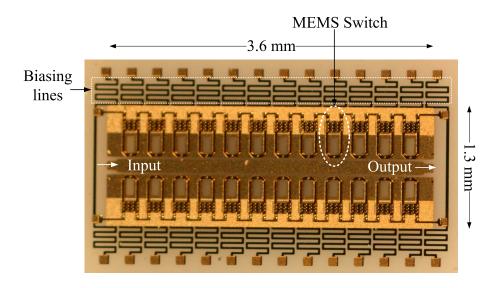

| 3.20 | Picture of the fabricated reconfigurable impedance matching network using                                                                                                                              |    |

|      | DGS structure                                                                                                                                                                                          | 53 |

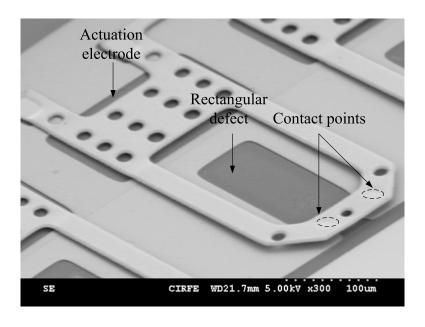

| 3.21 | SEM image of the fabricated MEMS series-contact switch                                                                                                                                                 | 54 |

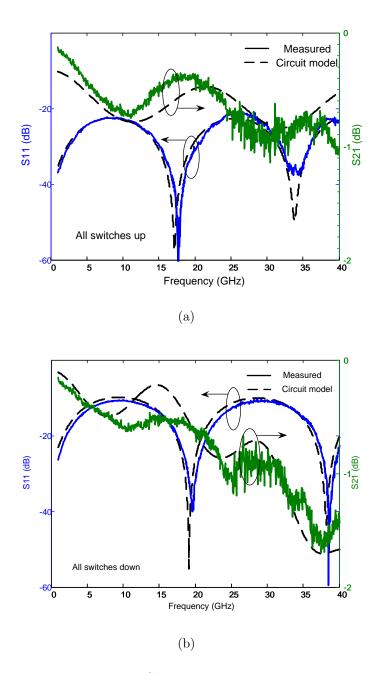

| 3.22 | Simulated v.s. measured S-parameters when all the switches are in their (a)                                                                                                                            |    |

|      | up-state position 'off' and (b) down state position 'on'                                                                                                                                               | 55 |

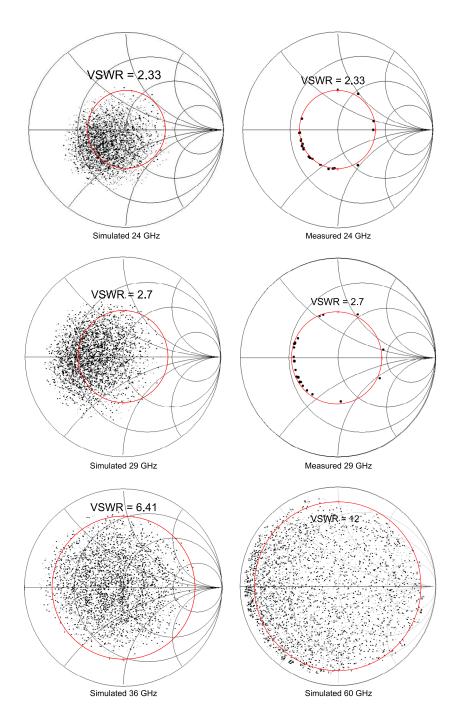

| 3.23 | Simulated (4096) and measured (20) impedance points of the fabricated                                                                                                                                  |    |

|      | reconfigurable impedance matching network at different frequencies                                                                                                                                     | 56 |

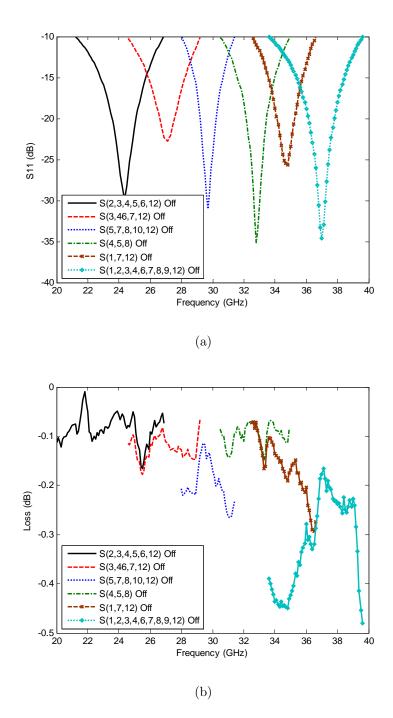

| 3.24 | Measured $S_{11}$ and loss of the matching network when used to match a 10 $\Omega$                                                                                                                    |    |

|      | load to 50 $\Omega$                                                                                                                                                                                    | 57 |

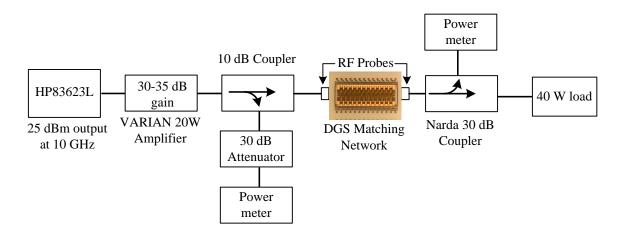

| 3.25 | High power measurement setup                                                                                                                                                                           | 59 |

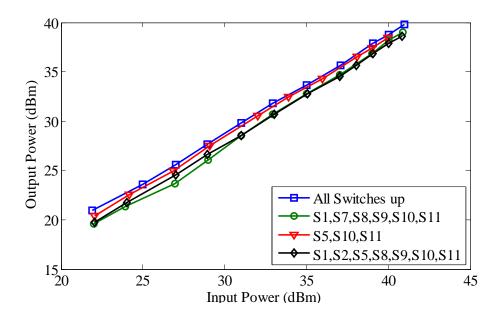

| 3.26 | Measured power handling of the matching network                                                                                                                                                        | 59 |

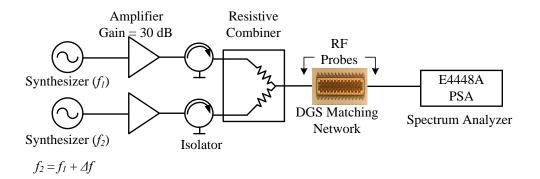

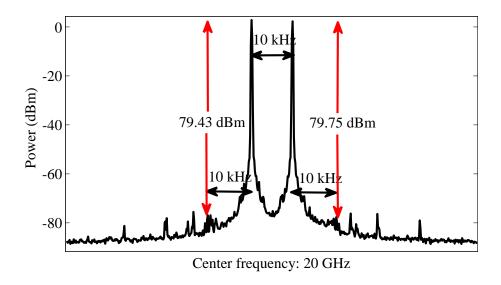

| 3.27 | Intermodulation test setup.                                                                                                                                                                            | 60 |

| 3 28 | Measured output spectrum for $f = 20$ GHz and $\Delta f = 10$ kHz                                                                                                                                      | 61 |

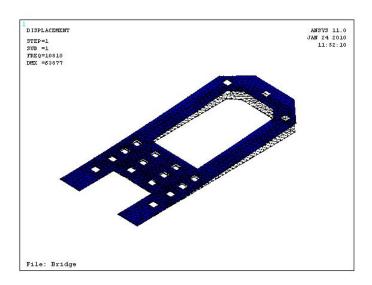

| 3.29 | Simulated mechanical self-resonance frequency of the cantilever MEMS switch.                               | 61 |

|------|------------------------------------------------------------------------------------------------------------|----|

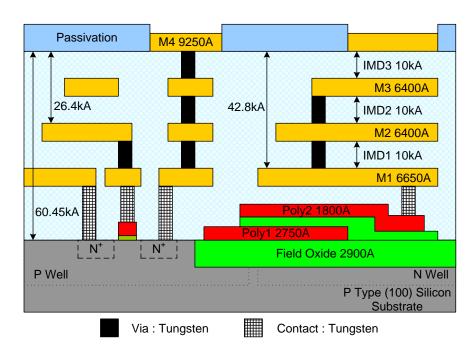

| 4.1  | 2P4M 0.35-μm CMOS process from TSMC                                                                        | 66 |

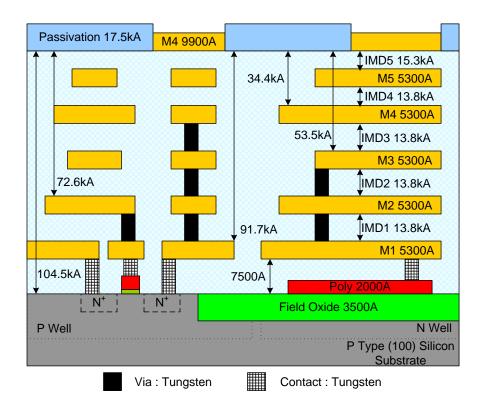

| 4.2  | 1P6M 0.18-μm CMOS process from TSMC                                                                        | 67 |

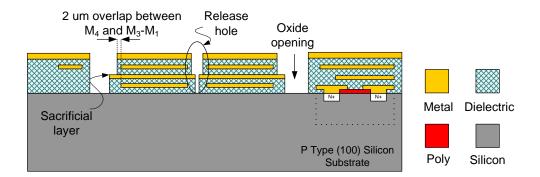

| 4.3  | CMOS chip after standard processing. $\mathrm{M}_4$ is used as RIE mask, $\mathrm{M}_3$ and $\mathrm{M}_1$ |    |

|      | are the MEMS structural layers, and $M_2$ is the sacrificial layer                                         | 68 |

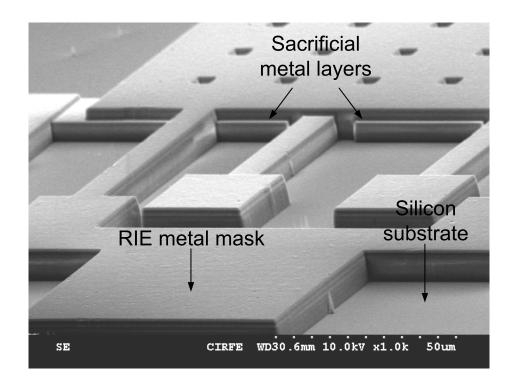

| 4.4  | First RIE removal of CMOS dielectric layer                                                                 | 69 |

| 4.5  | First RIE removal of CMOS dielectric layer                                                                 | 70 |

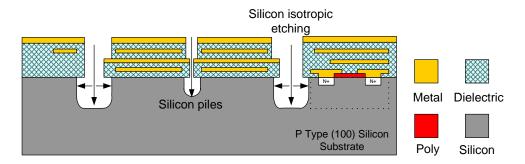

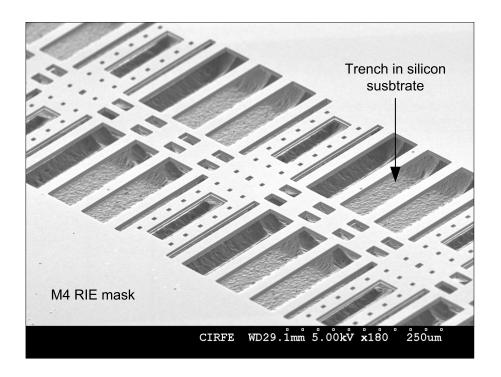

| 4.6  | Isotropic RIE of silicon substrate under the MEMS structures                                               | 70 |

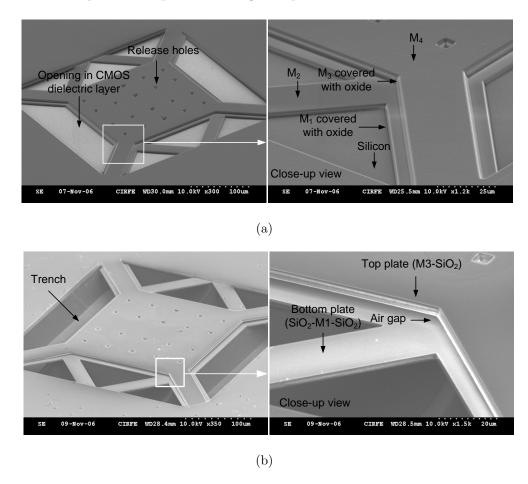

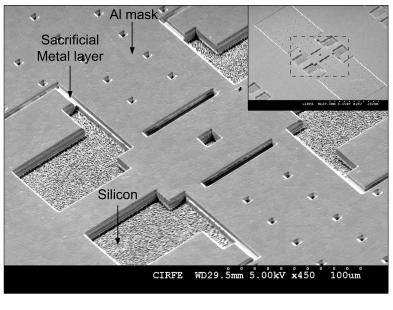

| 4.7  | SEM image of the CMOS chip after the isotropic RIE of silicon substrate                                    | 71 |

| 4.8  | Wet etching of the sacrificial layer and the silicon substrate                                             | 72 |

| 4.9  | CMOS chip after the second RIE of the CMOS dielectric layer                                                | 73 |

| 4.10 | SEM image of a MEMS tunable capacitor with parallel-plate structure fab-                                   |    |

|      | ricated using the CMOS-MEMS processing                                                                     | 73 |

| 4.11 | Layout and cross-section view of the parallel-plate MEMS capacitor fabri-                                  |    |

|      | cated using the 2P4M 0.35- $\mu$ m CMOS process                                                            | 74 |

| 4.12 | SEM image of the MEMS capacitor (a) after removing the CMOS dielectric                                     |    |

|      | layer and (b) after all the CMOS-MEMS processing steps                                                     | 75 |

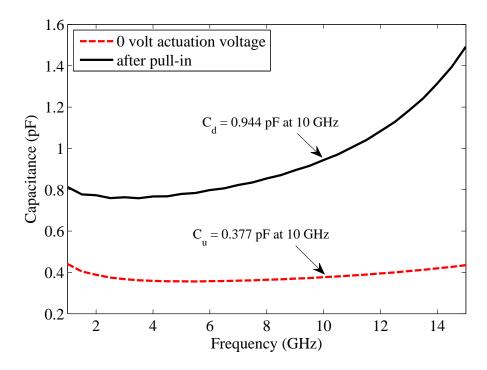

| 4.13 | Simulated capacitance value of the CMOS-MEMS capacitor                                                     | 76 |

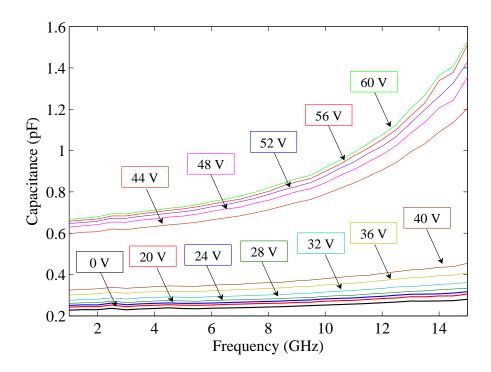

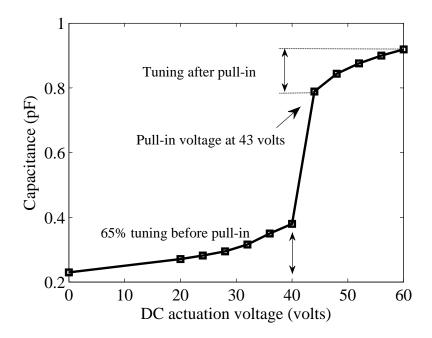

| 4.14 | Measured capacitance value of the CMOS-MEMS capacitor for different DC                                     |    |

|      | actuation voltages                                                                                         | 77 |

| 4.15 | Simulated deflection profile of the top plate of the CMOS-MEMS capacitor                                   |    |

|      | due to the residual stress gradient in the $Al/SiO_2$ layer                                                | 78 |

| 4.16 | Extracted capacitance versus DC actuation voltage at 10 GHz                                                | 78 |

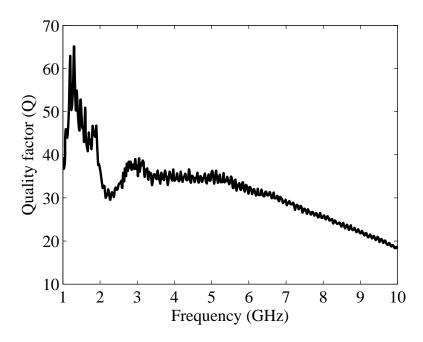

| 4.17 | Measured quality factor of the CMOS-MEMS tunable capacitor                                                 | 79 |

|------|------------------------------------------------------------------------------------------------------------|----|

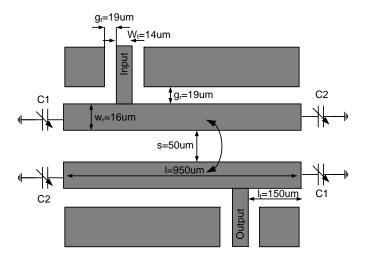

| 4.18 | Layout of the 2-pole interdigital bandpass filter with CMOS-MEMS tunable                                   |    |

|      | capacitors                                                                                                 | 81 |

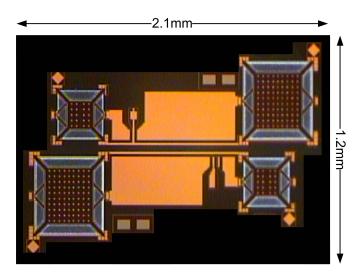

| 4.19 | Optical photograph of the integrated tunable bandpass filter                                               | 82 |

| 4.20 | Simulated and measured insertion and return loss at 0 volt                                                 | 83 |

| 4.21 | Simulation results for tuning the filter center frequency which illustrates the                            |    |

|      | need to use both sets of capacitors to maintain a constant bandwidth                                       | 84 |

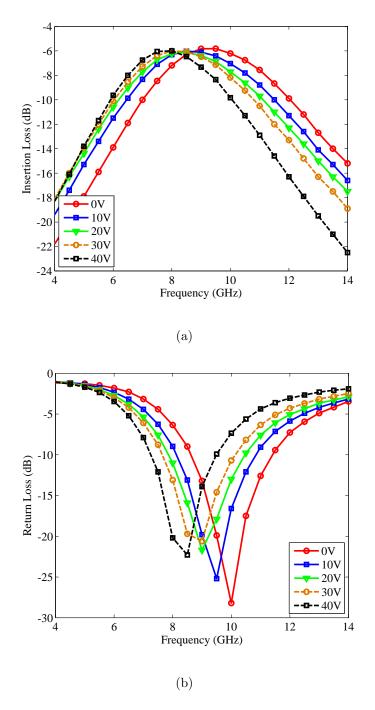

| 4.22 | Measured (a) insertion loss and (b) return loss of the tunable filter for different DC actuation voltages. | 85 |

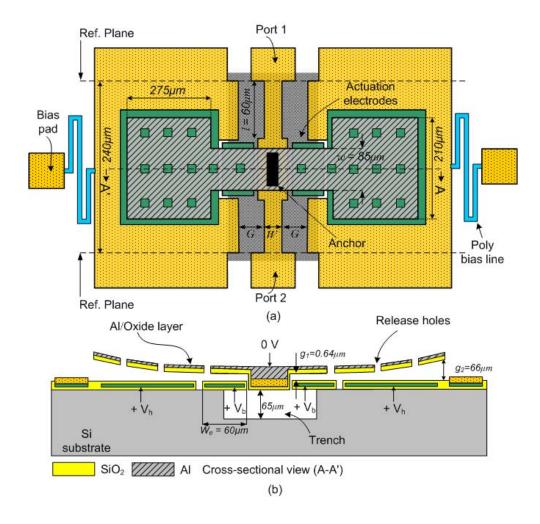

| 4.23 | (a) Top view and (b) cross-sectional view of the shunt capacitive CMOS RF                                  |    |

|      | MEMS switch                                                                                                | 88 |

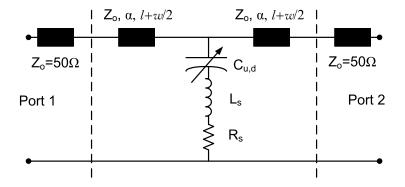

| 4.24 | Equivalent circuit diagram of the shunt capacitive CMOS RF MEMS switch.                                    | 89 |

| 4.25 | SEM image of the switch after (a) removing the CMOS dielectric layer using                                 |    |

|      | RIE and (b) the isotropic RIE of the Si substrate                                                          | 90 |

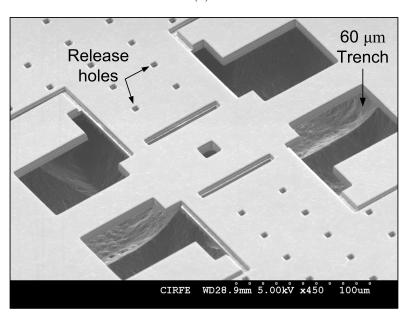

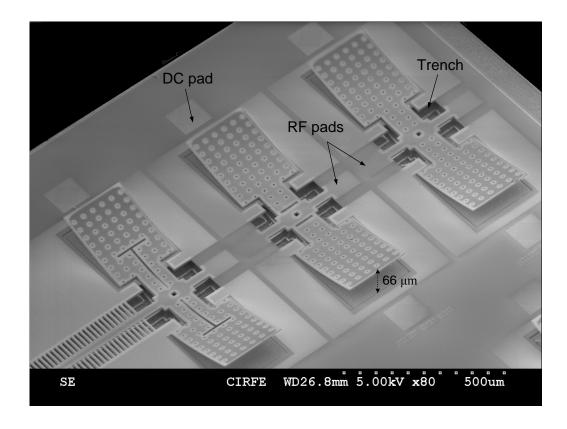

| 4.26 | SEM image of the fabricated CMOS RF MEMS switches                                                          | 92 |

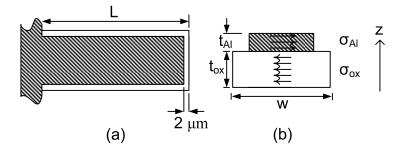

| 4.27 | (a) Top view and (b) cross-section of the composite $\mathrm{Al/SiO_2}$ cantilever beams                   |    |

|      | used to extract residual stress components of each layer                                                   | 92 |

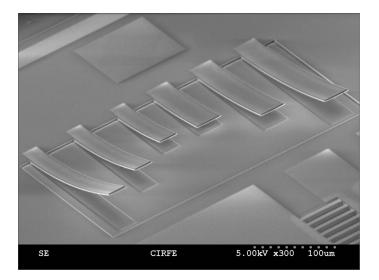

| 4.28 | SEM image of the cantilever beams used as test structures for stress analysis.                             | 93 |

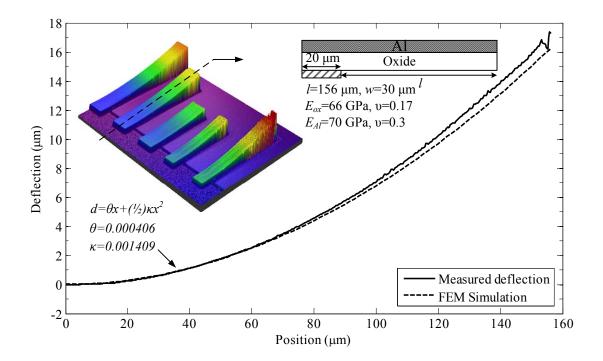

| 4.29 | Measured deflection profile of the bilayer cantilever beam and FEM simula-                                 |    |

|      | tion result for $\sigma_{mis}$ =144.74 MPa                                                                 | 94 |

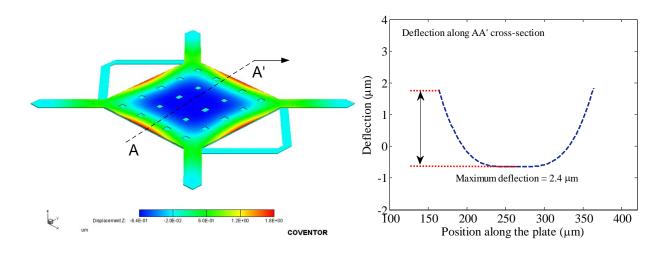

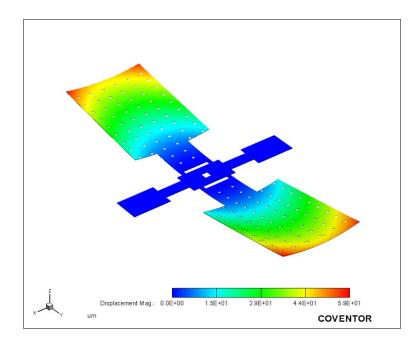

| 4.30 | FEM simulation result for the fabricated CMOS-MEMS switch with warped                                      |    |

|      | plates using the determined residual stress values, the maximum deflection                                 |    |

|      | of the top plate is simulated to be 59 µm                                                                  | 95 |

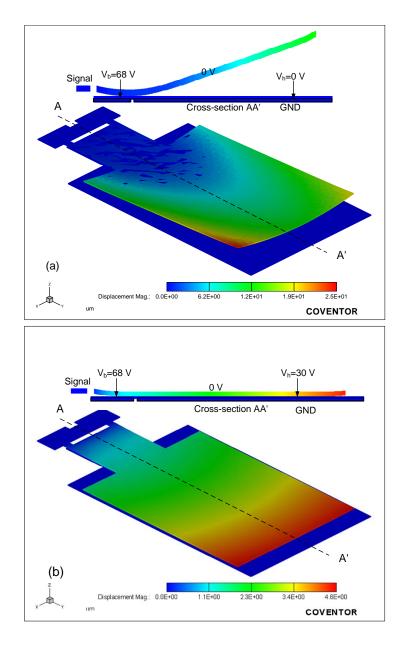

| 4.31 | FEM simulation results for the actuation voltage of the switch (a) when the        |      |

|------|------------------------------------------------------------------------------------|------|

|      | first bias voltage $V_b$ is applied between the signal and the actuation electrode |      |

|      | and (b) when the warped plates are pulled down by applying the second bias         |      |

|      | voltage $V_h$ between signal and ground conductors                                 | 97   |

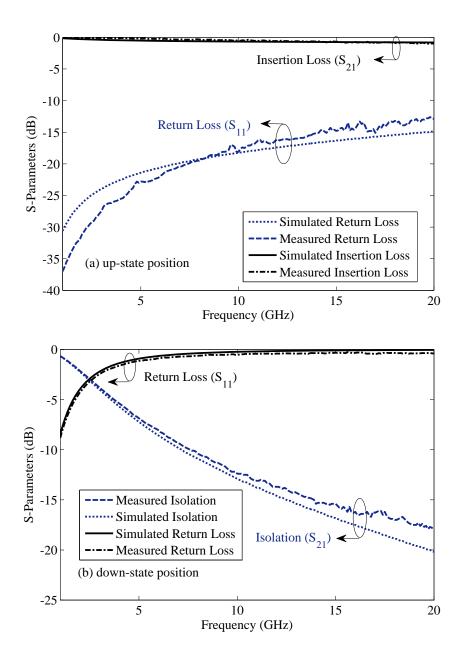

| 4.32 | Simulated and measured S-parameters of the fabricated capacitive switch            |      |

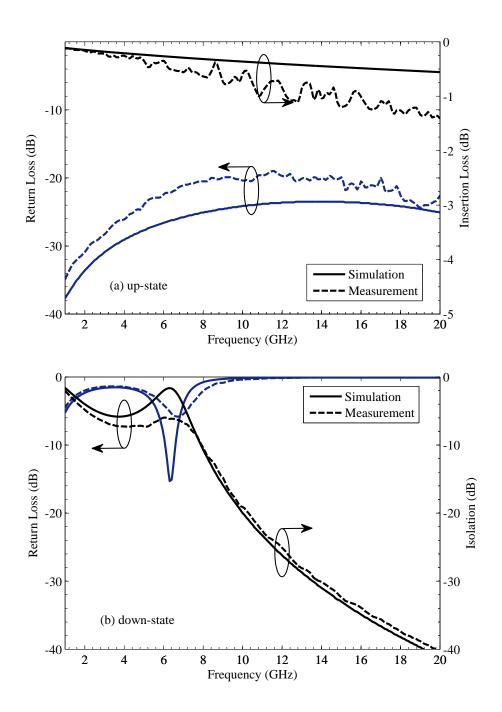

|      | for (a) up-state and (b) down-state positions                                      | 99   |

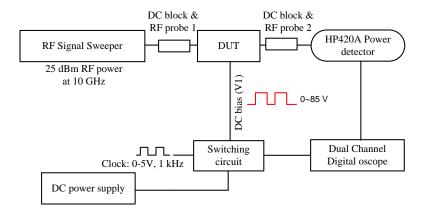

| 4.33 | Switching time measurement setup                                                   | 100  |

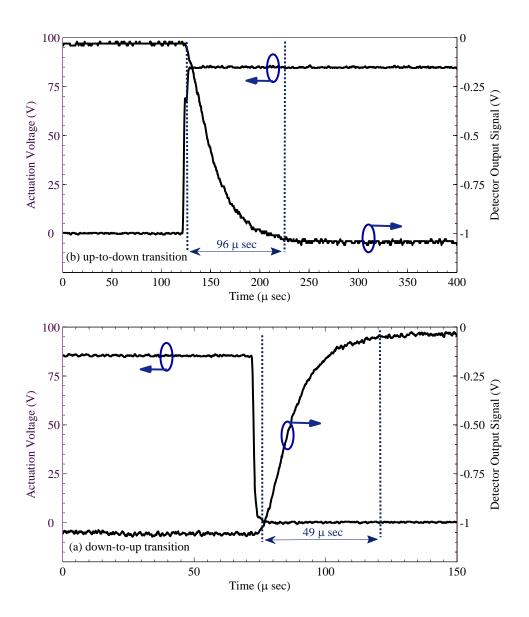

| 4.34 | Switching time measurement results of the fabricated switch for (a) up-to-         |      |

|      | down state and (b) down-to-up state transitions                                    | 101  |

| 4.35 | Equivalent circuit diagram of the cascaded switch with $\pi\text{-match}$ circuit  | 102  |

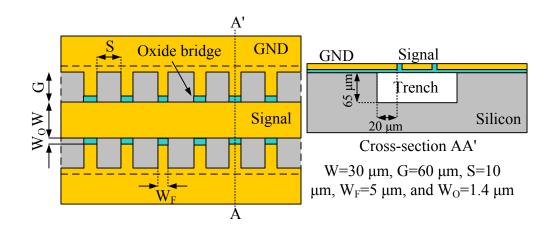

| 4.36 | Top view and the cross-sectional view of the CPW slow-wave structure               | 103  |

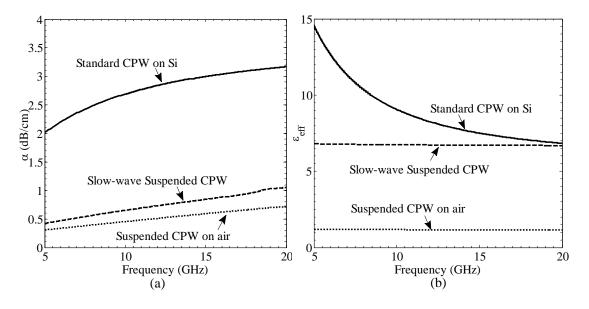

| 4.37 | (a) Attenuation constant and (b) effective dielectric constant of three differ-    |      |

|      | ent CPW transmission lines on CMOS silicon substrate                               | 103  |

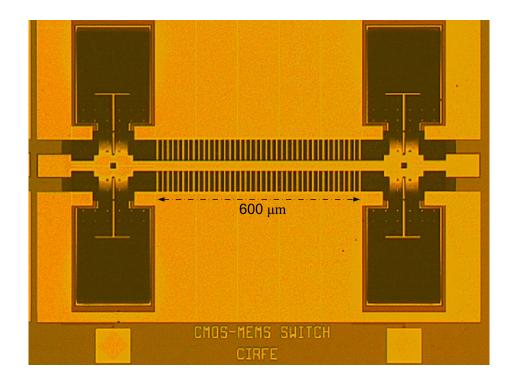

| 4.38 | Optical micrograph of the cascaded switch with improved isolation and re-          |      |

|      | turn loss                                                                          | 104  |

| 4.39 | Measured S-parameters of the fabricated cascaded switch with $\pi$ -match cir-     |      |

|      | cuit integrated in CMOS technology for (a) up-state and (b) down-state             | 105  |

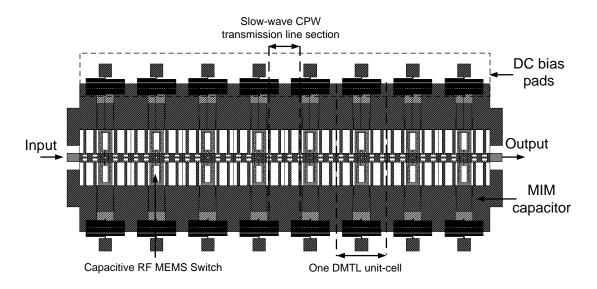

| 5.1  | Layout of the MEMS DMTL impedance matching network in 0.35- $\mu$ m CMOS           | .109 |

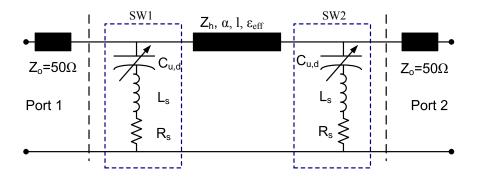

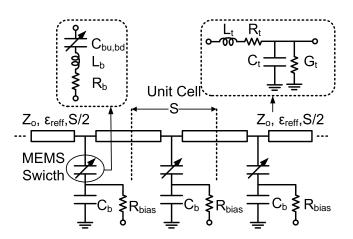

| 5.2  | Equivalent circuit diagram of a DMTL structure                                     | 110  |

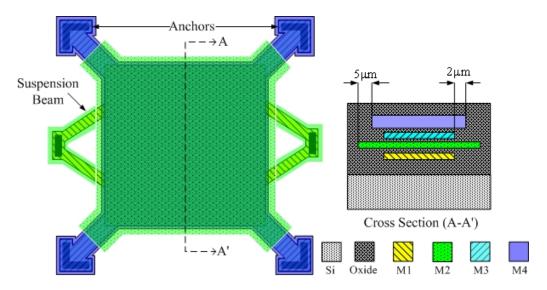

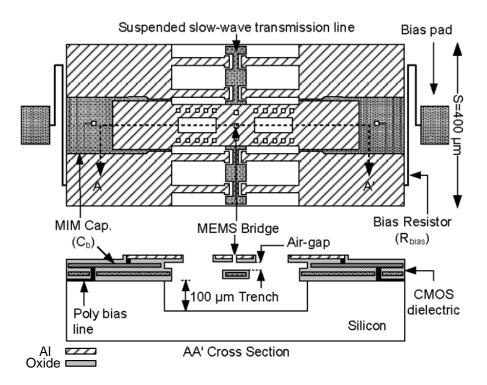

| 5.3  | Top view and the cross sectional view of the DMTL unit cell                        | 111  |

| 5.4  | CMOS-MEMS processing steps required to integrate the MEMS capacitive               |      |

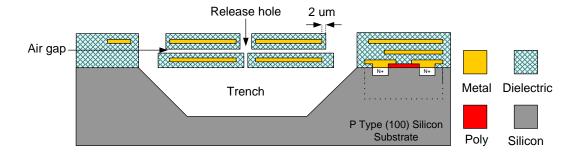

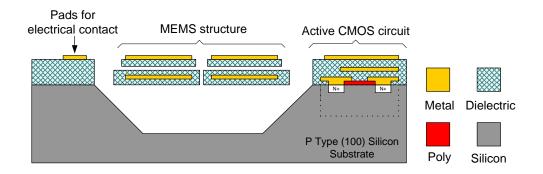

|      | switches in the 0.35- $\mu$ m CMOS technology                                      | 112  |

| 5.5  | RIE of the CMOS dielectric layer to expose the silicon substrate and M2            |      |

|      | sacrificial layer                                                                  | 113  |

| 5.6  | RIE of the silicon substrate to create a trench under the signal line                                                                          | 113          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

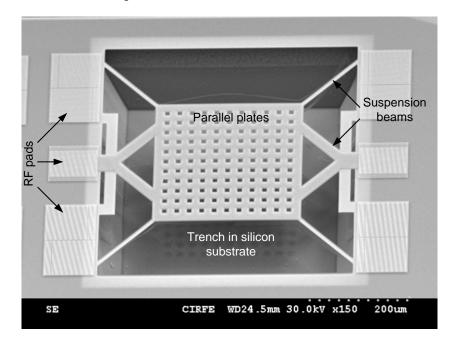

| 5.7  | SEM image of the CMOS-MEMS capacitive switch                                                                                                   | 114          |

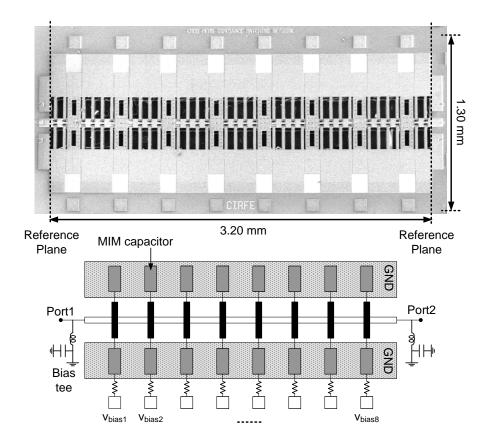

| 5.8  | (a) Photograph and (b) diagram of the DMTL impedance matching network with 8 MEMS switches built in 0.35- $\mu$ m CMOS technology              | 115          |

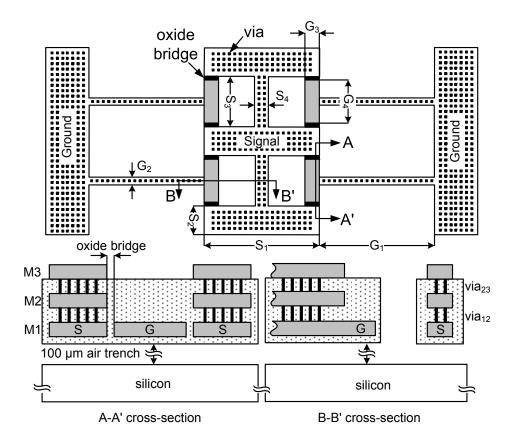

| 5.9  | Top view and the cross-sectional view of the suspended slow-wave CPW transmission line, $S$ and $G$ parameters mark the signal line and ground | <del>.</del> |

|      | plane dimensions, respectively                                                                                                                 | 117          |

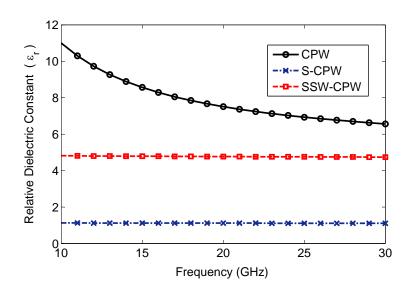

| 5.10 | Simulated relative dielectric constant $(\varepsilon_r)$ of the CPW, S-CPW, and SSW-CPW transmission lines                                     | 118          |

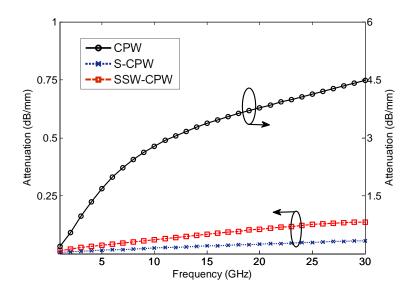

| 5.11 | Simulated attenuation ( $\alpha$ ) per millimeter length of the CPW on silicon substrate, S-CPW, and SSW-CPW transmission lines                | 119          |

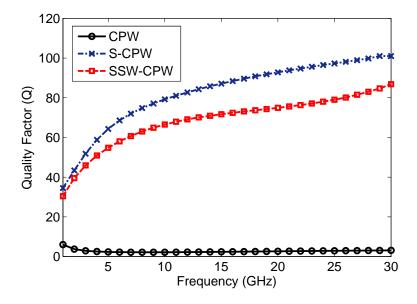

| 5.12 | Simulated quality factor $(Q)$ of the CPW on silicon substrate, S-CPW, and SSW-CPW transmission lines                                          | 119          |

| 5.13 | Simulated impedance coverage of the designed DMTL impedance matching network at different frequencies                                          | 122          |

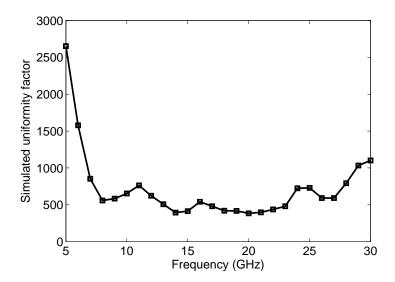

| 5.14 | Estimated uniformity factor of the designed DMTL impedance matching network                                                                    | 123          |

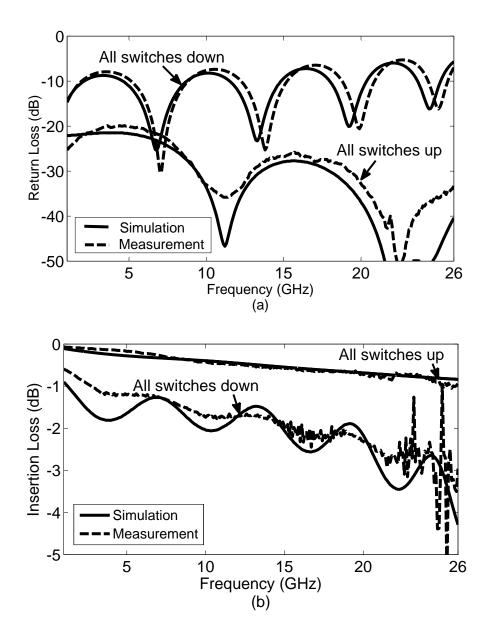

| 5.15 | Measurement and simulation results of the CMOS DMTL impedance matching network (a) return loss for two different combinations of MEMS switches |              |

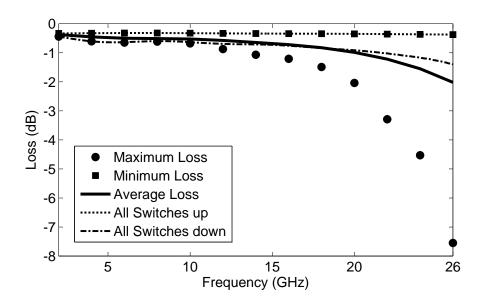

| 5.16 | and (b) the insertion loss                                                                                                                     | 125          |

|      | all the switches are in the up- and down-state positions, the minimum,                                                                         |              |

|      | maximum, and average loss for all the possible states                                                                                          | 127          |

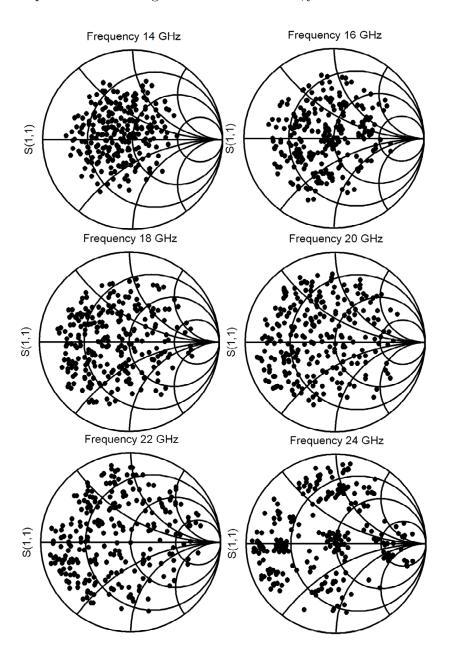

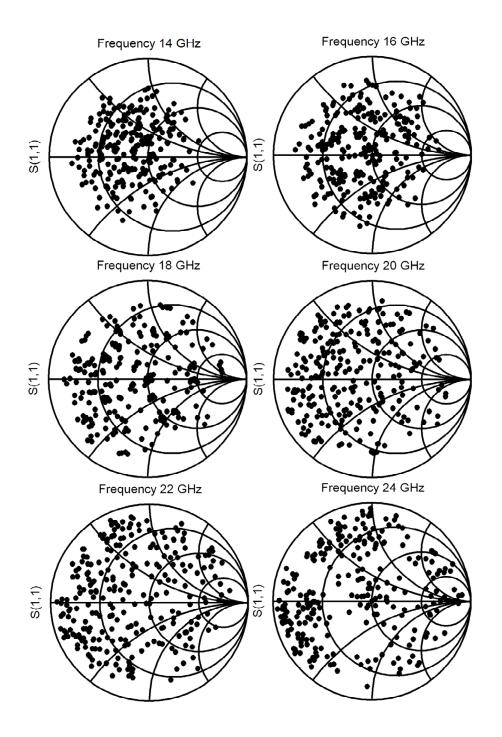

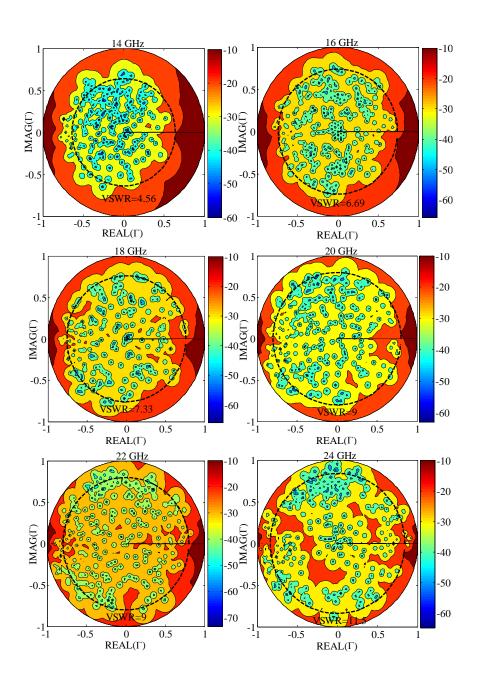

| 5.17 | Measured impedance coverage of the fabricated DMTL impedance matching network from 16 to 26 GHz                                                | 128          |

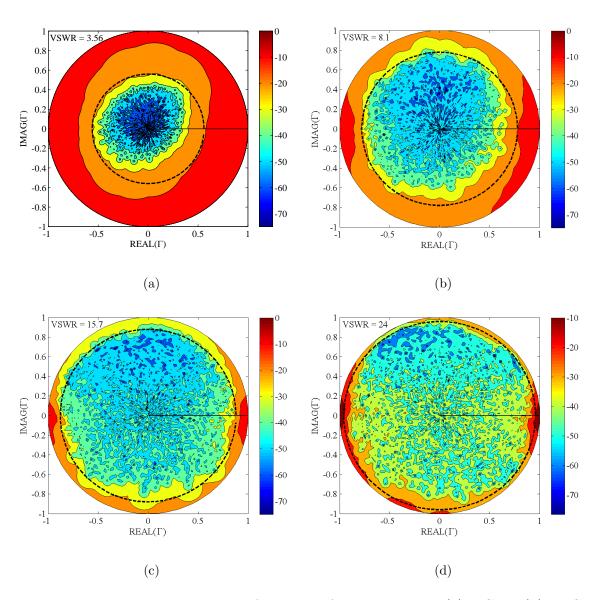

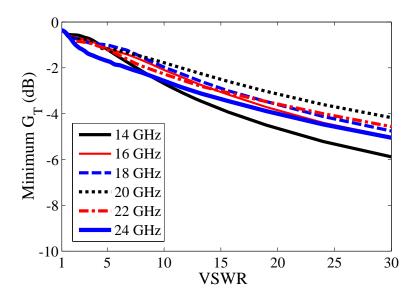

| 5.18 | Measured return loss performance of the fabricated network. The maximum                         |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | VSWR with an impedance match better than 10 dB is 4.56, 6.69, 7.33, 9, $$                       |     |

|      | 9, and 11.5 at 14, 16, 18, 20, 22, and 24 GHz respectively                                      | 129 |

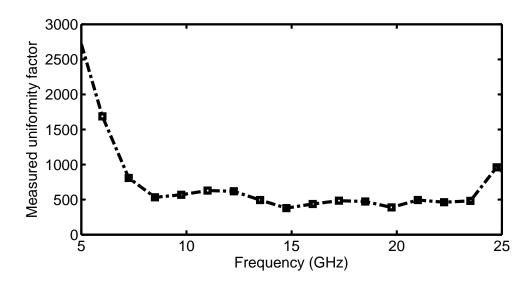

| 5.19 | Measured uniformity factor of the fabricated DMTL impedance matching                            |     |

|      | network                                                                                         | 130 |

| 5.20 | Minimum measured power transfer ratio $G_T$ of the network versus VSWR                          |     |

|      | at different frequencies                                                                        | 131 |

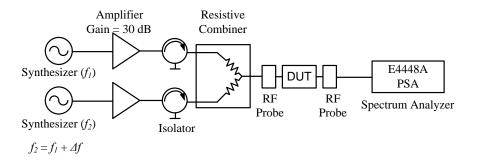

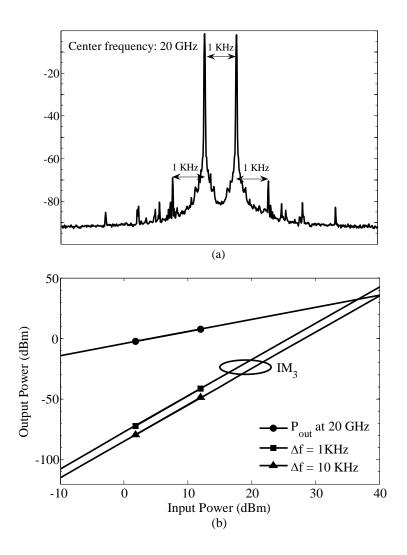

| 5.21 | Two-tone intermodulation distortion measurement setup                                           | 131 |

| 5.22 | (a) Measured output spectrum for $f=20$ GHz and $\Delta f=1$ kHz, (b) IM3                       |     |

|      | products versus the input power and $\Delta f$                                                  | 132 |

| 5.23 | CMOS-MEMS processing steps required to integrate the MEMS parallel-                             |     |

|      | plate capacitors in the 0.18- $\mu m$ CMOS technology                                           | 134 |

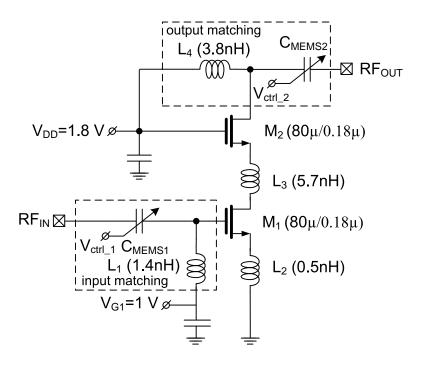

| 5.24 | Schematic of the 5.2 GHz single-stage cascode amplifier                                         | 135 |

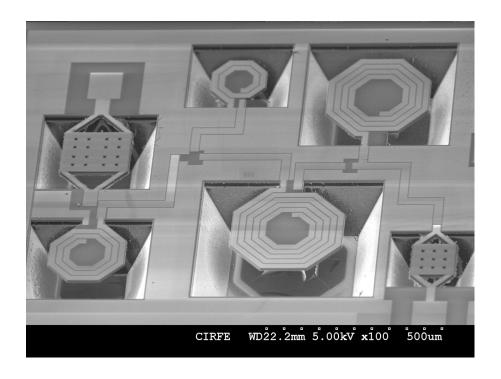

| 5.25 | SEM image of the amplifier circuit with integrated CMOS-MEMS capacitors                         |     |

|      | and inductors                                                                                   | 136 |

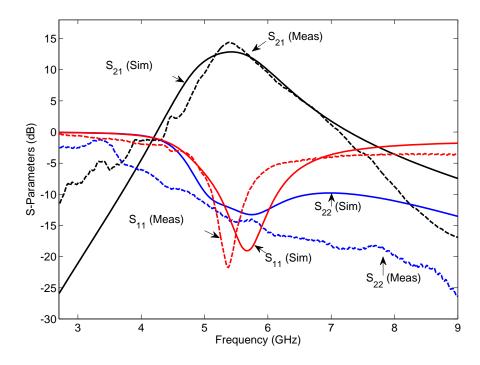

| 5.26 | Measured and simulated S-parameters of the reconfigurable amplifier when                        |     |

|      | the load/source impedance is 50 $\Omega$                                                        | 137 |

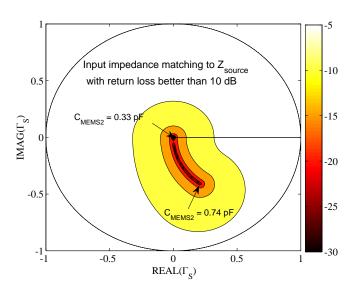

| 5.27 | Measured Smith chart coverage of the input impedance matching network                           |     |

|      | when used to match non-50 $\Omega$ source impedances to $Z_{source} = (22+j67) \Omega$ .        | 139 |

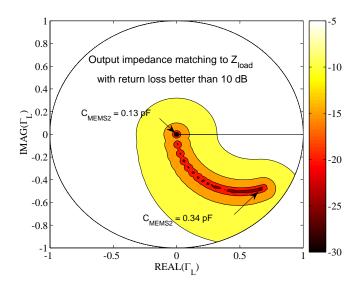

| 5.28 | Measured Smith chart coverage of the output impedance matching network                          |     |

|      | when used to match non-50 $\Omega$ load impedances to $Z_{load} = (52 + \mathrm{j}239)~\Omega.$ | 139 |

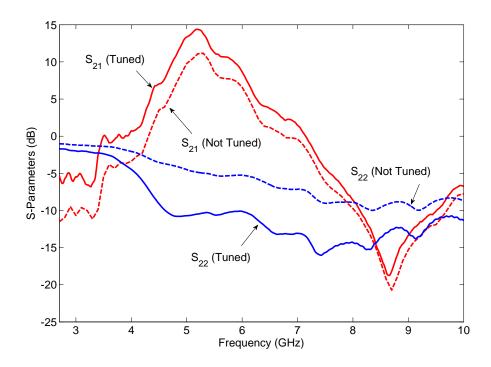

| 5.29 | Measured gain and output reflection coefficient of the reconfigurable ampli-                    |     |

|      | fier when the output port is terminated with a non-50 $\Omega$ load for both tuned              |     |

|      | and un-tuned states.                                                                            | 140 |

# Chapter 1

### Introduction

#### 1.1 Motivation

Multi-band RF front-ends based on reconfigurable integrated circuits have an important role in wireless communication systems. These systems are developed to support more than one frequency band of operation. In addition to multi-band functionality, they can dynamically adapt themselves to varying operational conditions such as temperature drift, and variations due to aging and manufacturing tolerances in active circuit elements.

Reconfigurable impedance matching networks are key components in any multi-band RF transceiver circuit. They are used to increase the overall system performance in terms of power efficiency and linearity by compensating for the input/output impedance variations between the different building blocks within an RF front-end such as power amplifiers (PAs), antennas and low noise amplifiers (LNAs) caused by switching the frequency band of operation or by adjusting the output power level. In today's wireless communication systems, the majority of tunable impedance matching networks are realized by solid-state varactors or switching p-i-n diodes. Ferroelectric barium strontium titanate (BST) varactor technology has also been utilized in the realization of tunable matching networks. Using

this technology a better RF linearity can be achieved compared to the solid-state varactors. However, at millimeter-wave frequencies, the increased loss of the matching networks due to the low quality factor of the solid-state devices and BST capacitors becomes an important issue. Another drawback of the solid-state tuning elements is the increased nonlinearity and noise at higher RF power levels.

microelectromechanical systems (MEMS) technology has the capability to provide a major impact on existing communication systems by reducing size, cost, weight and power dissipation. With the use of RF MEMS technology, reconfigurable matching networks with improved impedance tuning range, power handling capability, compact size and lower insertion loss suitable for high-frequency, high-power applications can be realized.

The current MEMS-based adaptive RF front-ends rely on multi-chip solutions where the active circuitry and the MEMS network are put together in a hybrid integration approach. The realization of a fully integrated one-chip solution would be possible by developing a process which enables the integration of the MEMS devices employing the standard processes used for RF integrated circuits (RFICs). Among the mainstream RFIC technologies, silicon-based CMOS processes have become the most favorable technology for the implementation of wireless communication systems due to their mature fabrication process, higher levels of integration and lower manufacturing cost.

#### 1.2 Objectives

The purpose of this thesis is to investigate the feasibility of utilizing MEMS technology to design and implement innovative reconfigurable impedance matching networks with improved impedance coverage and higher power handling capability. Such matching networks would enable a new class of RF front-ends with unprecedented performance, agility and functionality. The realization of this class of networks will be possible due to advances in

the fields of MEMS technology and CMOS-MEMS integration techniques. The stages of this research include:

- Development, modeling and fabrication of novel MEMS impedance matching networks: Novel RF MEMS reconfigurable impedance matching networks are developed to meet several requirements such as wide tuning range, lower insertion loss, compact size and higher power handling capability. The first RF MEMS impedance matching network is based on dual-beam RF MEMS capacitive switches with 3 different states. The application of the proposed tri-state switch results in increasing the operational frequency band of the matching network with a wide impedance coverage. The second impedance matching network consists of MEMS series-contact switches and periodic defected-ground-structures (DGSs). The proposed structure achieves an improved insertion loss and power handling capability compared to the traditional RF MEMS impedance matching networks by utilizing MEMS switches placed on the ground planes. Both networks are fabricated using a seven-mask process developed at the University of Waterloo for the fabrication of RF MEMS devices.

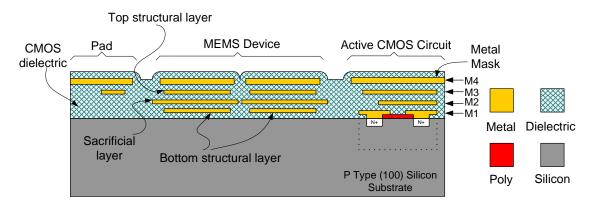

- Development of a novel CMOS-MEMS post-processing and integration technique: A novel CMOS-MEMS post-processing technique is developed that can be used to integrate tunable RF MEMS devices within a chip fabricated using commercial standard CMOS processes. The MEMS structures are formed out of the metal and dielectric layers available in the CMOS process without any need to extra film deposition or lithographic patterning steps. Using the proposed technique, different types of RF MEMS tunable capacitors with parallel-plate structure and electrostatic actuation have been developed. These capacitors can achieve very high quality factor at millimeter wave frequencies. A tunable microwave band-pass filter with tunable center frequency and bandwidth is also designed and fabricated by

employing the proposed RF MEMS tunable capacitors.

- Implementation of RF MEMS switches integrated in CMOS technology: CMOS-MEMS capacitive type switches for microwave and millimeter-wave applications are investigated. The switches are fabricated using the 2P4M (double poly, four metal) TSMC 0.35-µm CMOS process. The mask-less CMOS-MEMS post-processing technique developed for the fabrication of parallel-plate electrostatically actuated microstructures at the University of Waterloo is utilized. An integrated monolithic CMOS implementation of these RF MEMS switches will result in low cost single chip RF multi-band systems with enhanced performance and functionality by eliminating the packaging parasitics present in the hybrid integration approaches.

- Design and implementation of RF MEMS impedance matching networks using standard CMOS technology: The integration of MEMS-based reconfigurable impedance matching networks in standard CMOS technologies is investigated. An 8-bit reconfigurable impedance matching network based on the distributed MEMS transmission line (DMTL) concept is presented. The network is fabricated in a standard 0.35-µm CMOS technology and using a CMOS-MEMS integration technique that is optimized for the fabrication of MEMS switched capacitors. The proposed network is optimized using a novel design procedure to improve the impedance coverage of the network on the Smith chart.

- Development of reconfigurable amplifier using integrated CMOS-MEMS adaptive matching networks: A reconfigurable amplifier is designed with tunable input and output matching networks which can be tuned to provide matching for variable source and load impedances and to yield an optimum operation of the amplifier. Design issues and circuit simulations for both the MEMS matching network and active circuitry are discussed. The amplifier is implemented using the standard TSMC 0.18-µm CMOS technology and the MEMS adaptive matching network is con-

structed using the proposed CMOS-MEMS integration technique on the same CMOS chip.

#### 1.3 Thesis Outline

Following the motivation and objectives given in Chapter 1, Chapter 2 presents an overview of the different technologies available to realize tunable impedance matching networks with a focus on MEMS technology. Furthermore, the current advances related to the integration of MEMS devices using standard silicon-based CMOS technologies are addressed. In Chapter 3, two types of reconfigurable impedance matching networks that are fabricated using a conventional MEMS fabrication process are investigated. Chapter 4 presents the development of the CMOS-MEMS integration approach. Parallel-plate tunable capacitors with electrostatic actuation integrated on a CMOS chip are presented. The monolithic integration of a tunable band-pass filter with MEMS tunable capacitors as the tuning elements is investigated. A novel capacitive-type RF MEMS switch integrated in CMOS technology is also presented in this chapter. A reconfigurable DMTL impedance matching network utilizing switched MEMS capacitors implemented using standard CMOS technology is introduced in Chapter 5. The integration of tunable lumped-element impedance matching networks with an amplifier module on a single CMOS chip is presented in this chapter. Finally, a brief summary of the contributions of the thesis with an outline of the proposed future research are given in Chapter 6.

## Chapter 2

# Literature Survey

#### 2.1 Reconfigurable Impedance Matching Networks

Reconfigurable impedance matching networks and impedance tuners are a critical component in many wireless communication systems, specially in multiband applications where there is a need to change the frequency band of operation, the output power level or the antenna patterns. Changing these parameters involves tuning of the impedance matching networks between different building blocks of the system in order to obtain an optimum power transfer and the highest system efficiency. In some other cases, there is an impedance change due to variable ambient conditions. These variations must be compensated for using adaptive impedance matching networks. Over the last few decades, tunable impedance matching networks have been realized using different technologies. With the development of micromachining techniques, tunable matching networks based on MEMS technology have attracted a great deal of interest during the last few years. Based on their tuning mechanisms, most tunable impedance matching networks presented in the literature fall into three basic types: MEMS tuning, electronic tuning, and tuning using ferroelectric materials. Tunable impedance matching networks, based on MEMS technology, are cat-

egorized as a separate category due not only to their multi-discipline tuning mechanism, but also to their potential use in the next generation multiband communication systems.

#### 2.1.1 MEMS Tuning Method

Various MEMS components including tunable MEMS capacitors, MEMS capacitive switches, capacitor banks using MEMS switches, and distributed MEMS transmission line (DMTL), have been implemented in reconfigurable impedance matching networks and impedance tuners. The most straight forward approach to design reconfigurable impedance matching networks by employing MEMS technology is to replace the traditional varactors and inductors with their MEMS counterparts in lumped-element LC-networks. Lumped-element LC matching networks are the easies to implement. In addition to their simplicity, the use of lumped elements in a lower frequency range results in a more compact circuit compared to distributed-element networks. Fig. 2.1 shows block diagram of an adaptive LC impedance matching module with a 5-bit MEMS capacitor array that can be used to compensate the

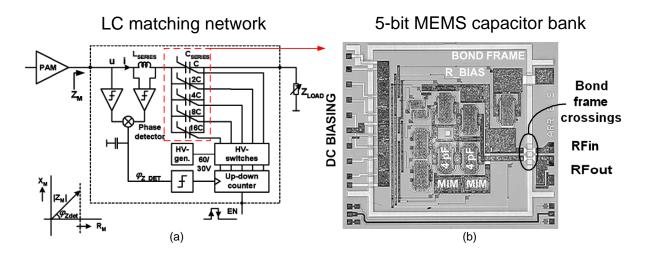

Figure 2.1: (a) Block diagram of an adaptive LC matching network and (b) die photograph of the MEMS capacitor bank [1].

imaginary part of the antenna impedance in a multi-standard mobile phone [1]. The measured MEMS array capacitance tuning ratio is almost a factor of 10. The module shows a maximum impedance correction of  $-75j\Omega$  at 900 MHz and the measured insertion loss is approximately 0.5 dB at both low-band (900 MHz) and high-band (1800 MHz).

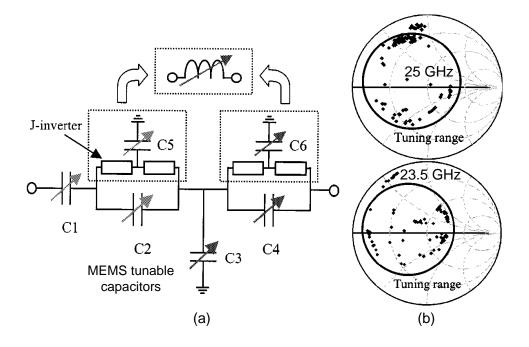

Impedance tuners using LC resonant unit-cells realized by MEMS tunable capacitors is presented in [2]. Since the capacitance variation of the MEMS capacitors is limited to 30%, resonant unit-cells operating near the resonance frequency are employed to extend the impedance tuning range needed for tuner operation as shown in Fig. 2.2. The large reactance change near the resonant frequency makes it possible to obtain a relatively large impedance variation. The tuner is capable of generating impedances in the second and third quadrants of the Smith chart from 25 GHz to 23.5 GHz with a maximum voltage standing wave ratio (VSWR) of 21.2 at 25 GHz.

Figure 2.2: (a) Schematic circuit diagram and (b) measured impedance coverage of the analog impedance tuner in [2].

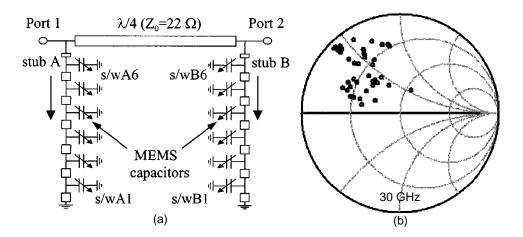

Although the LC-matching networks are easy to fabricate using MEMS devices, they have a narrow operating bandwidth and limited impedance coverage. Another most commonly used impedance matching technique, referred to as stub matching, employs shortor open-circuit transmission lines as stubs where both the effective electrical length and the distance between the stubs can be adjusted using MEMS tuning elements. The digital type impedance tuner in [2] consists of a  $\lambda/4$  low-impedance line and two short-circuited stubs each one loaded with 6 MEMS capacitive switches as presented in Fig. 2.3. By actuating the MEMS capacitive switches, the loading capacitance and thus the effective electrical length of the lines are increased, resulting in subsequent impedance tuning. The measured results for this tuner shows an impedance coverage of the second quadrant of the Smith chart from 29-32 GHz with a maximum VSWR of 32.3 measured at 30 GHz. Single-. double- and triple-stub impedance tuners and matching networks using MEMS switches and switched capacitors have been reported by Papapolymerou et al. and Heikkila et al. [3, 4, 5, 6]. The switched capacitors were distributed at discrete points along the stubs as well as the sections between the stubs. This will generate more impedance points and a better coverage compared to the case where the switched capacitors are present only at

Figure 2.3: (a) Schematic circuit diagram and (b) measured impedance coverage of the digital impedance tuner in [2].

the end of the stubs. Fig. 2.4 illustrates the MEMS single-stub impedance tuner in [4] consisting of 10 switched MEMS capacitors and producing 1024 (2<sup>10</sup>) different impedance states. Capacitively loaded lines were added before and after the stub in order to improve the impedance coverage and bandwidth. The tuner demonstrated good impedance coverage over a frequency band from 20 GHz to 50 GHz with a maximum VSWR of 32.3 at 40 GHz. Double- and triple-stub MEMS impedance tuners operating at W-band were also reported in [5]. Similar to the single-stub tuner, both the stubs and the connecting transmission lines are loaded and adjusted using switched MEMS capacitors located at discrete points. These tuners achieve a maximum VSWR of 24 at 100 GHz. Other configurations of broadband RF impedance tuners with four and ten stubs loaded with tuning varactors

Figure 2.4: Photograph of (a) single-stub impedance tuner and (b) switched MEMS capacitor (c) circuit diagram and (d) impedance coverage at 40 GHz [4].

are presented in [7] and [8], respectively.

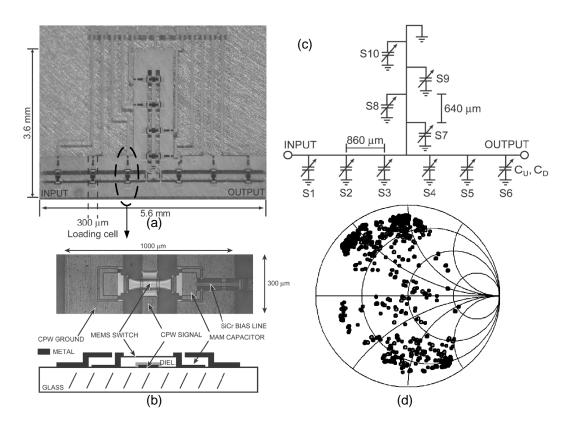

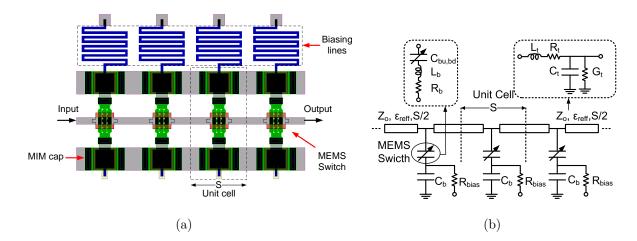

Besides the stub matching networks, switched MEMS capacitors can be used in distributed MEMS transmission line (DMTL) structures for impedance matching and tuning applications. Both the effective electrical length and characteristic impedance of such a transmission line is adjusted by switching the MEMS capacitors on and off. The advantage of DMTL networks over stub matching networks is their lower insertion loss and smaller size which makes them suitable for impedance matching applications. Reconfigurable RF MEMS impedance matching networks based on DMTL structure with N=4-8 MEMS switched capacitors are reported by Heikkila  $et\ al.$  in [9, 10]. Fig. 2.5 illustrates the photograph and the impedance coverage of the reconfigurable matching network with 8 switched MEMS capacitors. The 8 element matching network produces 256 (28) different impedance states and is only  $1\times2.5\ \mathrm{mm}^2$  in size on a glass substrate. The matching network is capable of matching power amplifiers with 10-20  $\Omega$  output impedance to 50  $\Omega$  system reference impedance over a frequency band from 20 GHz to 50 GHz with an impedance matching

Figure 2.5: (a) Photograph and (b) impedance coverage of the reconfigurable impedance matching network based on DMTL structure with 8 switched MEMS capacitors at 40 GHz [9].

better than 10 dB. The measured insertion loss of the network when used to match a 10  $\Omega$  load to 50  $\Omega$  was better than 1.2 dB up to 40 GHz. An impedance tuner based on DMTL structure and optimized for both impedance coverage and power handling was reported in [11, 12]. Novel contact-less MEMS varactors were used instead of the switched MEMS capacitors. These capacitors can handle more than 3.5 W of RF power without self-actuation. The power handling capability of the tuner was further improved by optimum placement of the MEMS varactors along the transmission line so that the maximum voltage swing across all the varactors is equalized. Fig. 2.6 shows a picture and measured impedance coverage of the fabricated impedance tuner on a high-resistivity silicon substrate. The tuner occupies an area of  $0.49 \times 0.12$  mm<sup>2</sup> and demonstrates wide impedance tuning at 30 GHz.

Double-slug reconfigurable impedance matching networks based on a minimal-contact

Figure 2.6: (a) SEM of the impedance tuner with high-power MEMS varactors, (b) the measured impedance coverage at 30 GHz, and (c) a cross section of the MEMS varactor [11, 12].

Figure 2.7: (a) SEM and (b) cross-section view of the minimal-contact varactor [13].

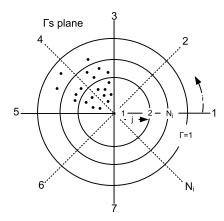

RF MEMS varactor was reported by Shen et al. [13, 14]. This varactor eliminates the dielectric charging, stiction, and low power handling capability of the conventional switched MEMS capacitors. Fig. 2.7 depicts the cross-sectional view of the minimal-contact varactors. Stand-offs on the bottom side of the bridge were used to limit its range of downward motion and avoid any contact with the signal line similar to the capacitive RF MEMS switches reported by Blondy et al. [15]. As shown in the schematic diagram of the doubleslug tuner in Fig. 2.8, it consists of two quarter wavelength impedance tuner sections or slugs and two sections of transmission lines with a characteristic impedance  $Z_o$  and effective electrical length of  $\Theta_1$  and  $\Theta_2$ . The electrical length of the 90° slugs is used to tune the frequency of operation while  $\Theta_1$  and  $\Theta_2$  define the load impedance on the Smith chart that can be matched to the source impedance. The network is designed by loading a high-impedance coplanar waveguide (CPW) line with minimal-contact varactors, each having an individual biasing line. When the switches are in the up-state, the characteristic impedance of the loaded line section is designed to be 50  $\Omega$  ( $Z_o$ ) and when the switch is in its down-state position the local CPW line impedance is 25  $\Omega$  ( $Z_m$ ), and this section of the line will act as a 90° slug. By actuating a different number of switches, it is possible to

Figure 2.8: (a) Topology and (b) schematic diagram of the double-slug impedance tuner, (c) measured impedance coverage at 27.8 GHz [13].

change the length of the slugs and  $\Theta_1$  and  $\Theta_2$ . Measurement results demonstrate coverage of all four quadrants of the Smith chart from 10 to 30 GHz with a maximum VSWR of 12 and an insertion loss better than 3 dB.

#### 2.1.2 Electronic Tuning Method

Electronic tuning of impedance matching networks is achieved by employing semiconductor varactors [16, 17, 18, 8] switches [19, 20] and p-i-n diodes [21]. This method offers a fast tuning speed, compact size, low cost and light weight. A reconfigurable impedance tuner in the 380-400 MHz frequency band and based on lumped and electronically tunable elements was reported by Mingo  $et\ al.$  [21]. The tuner is used to construct automatic matching system for antenna input impedance. The network is based on the generic low-pass  $\Pi$  matching network implemented using tunable capacitors. Each tunable capacitor consists

Figure 2.9: (a) Circuit diagram of the impedance tuner for ISM 2.4 GHz band and (b) system block diagram of the antenna tuning unit (ATU) [22].

of a set of fixed value capacitors that are selected by p-i-n diodes.

An adaptive impedance tuning unit implemented in 0.35-µm CMOS technology for the industrial-scientific-medical (ISM) 2.4 GHz band is reported in [22]. The circuit is based on shunt switched capacitor banks and external series inductors crating a ladder network as shown in Fig. 2.9. The switches used are CMOS transistors operating in the triode region. In total, there are 8 switches yielding 2<sup>8</sup>=256 different switch combinations for this impedance tuner. A controller unit can switch the matching network through all possible combinations in order to obtain the best performance to match the antenna input impedance.

Transmission lines loaded with active tuning elements similar to the DMTL structure can also be used as impedance matching and tuning networks. The first electronically reconfigurable impedance tuner for tuning of microwave monolithic integrated circuits (MMICs) was reported by Bishoff et al. [18]. The proposed tuner consists of a transmission line loaded with 4 capacitors each in series with a High Electron Mobility Transistor (HEMT) switch monolithically implemented on a GaAs substrate. The proposed tuner was applied to a narrow band amplifier operating at 27 GHz in order to compensate the process deviations. A reconfigurable CMOS tuner based on a transmission line periodi-

Figure 2.10: (a) Structure of the CMOS tuner based on switched capacitors and (b) measured impedance coverage at 10 GHz for tuners with a transmission line length of 1.6 mm (blue asterisks) and 3.6 mm (red triangles) [23].

cally loaded with CMOS transistor switches in series with capacitors is presented in [23]. The 5 to 16-GHz tuner is implemented in a standard 0.13-µm CMOS technology and can be configured to 2<sup>20</sup> different impedances by an integrated 20-bit shift register. Although the proposed tuner has a relatively good impedance coverage as shown in Fig. 2.10, the high loss of the tuner impedes its application in high-performance programmable RF and microwave circuits.

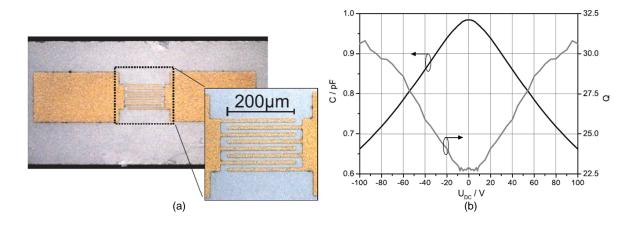

#### 2.1.3 Tuning Using Ferroelectric Varactors

The key drawbacks of electronic tuning using semiconductor devices are a relatively large insertion loss and a low power handling capability, which are attributed to the low quality factor and nonlinearity of the semiconductor switches and varactor didoes, respectively. A solution is to use thin-film ferroelectric varactors such as barium strontium titanate (BST) varactors. The capacitance of BST varactors can be varied by changing the dielectric constant of the ferroelectric material with the aid of an external DC bias voltage. BST varactors can be fabricated either in a parallel plate (metal-insulator-metal)

Figure 2.11: (a) A typical interdigitated BST varactor, (b) the measured C-V characteristic and Q-factor at 2 GHz [24].

fashion or an interdigitated configuration. Fig. 2.11 shows a typical interdigitated BST varactor fabricated on alumina (Al<sub>2</sub>O<sub>3</sub>) substrate and its characteristics at 2 GHz [24]. Typically, tunable impedance matching networks based on BST varactors fabricated on RF substrates, achieve an insertion loss from 0.3 dB to 6 dB with a centre frequency from 850 MHz to 1.95 GHz [25, 24, 26, 27, 28]. The linearity characterization of the impedance matching network in [24], reveals a third-order intercept point (IP3) of 52.8 dBm under the conventional two-tone intermodulation test with a maximum input power of 33 dBm at 1.95 GHz with 1 MHz of offset between the two inputs. Due to the compatibility of the fabrication process of BST varactors with traditional semiconductor processes, the size of the complete tunable impedance matching networks using this technology is near that of semiconductor-based matching networks. One disadvantage is the higher bias voltage used for BST varactors, such as 30 V in [25] and 100 V in [24]. Another drawback is the frequency limitation due to low quality factors beyond 2 GHz.

# 2.2 Adaptive Amplifiers and Automatic Matching Systems

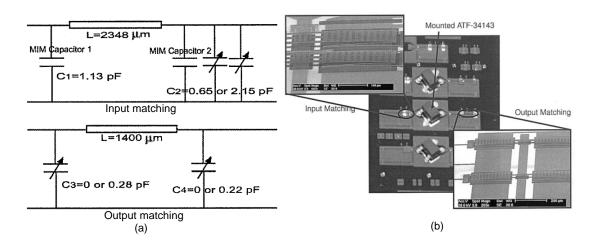

A compact implementation of adaptive amplifiers and automatic matching systems used in multiband RF front-ends is possible by integrating high efficiency microwave circuits with tunable RF MEMS impedance matching networks and tuners [29, 21, 16, 8, 30, 1]. A reconfigurable amplifier with an adaptive matching network based on RF MEMS shunt capacitive switches was reported by Lu et al. [29]. Double-stub tunable input and output impedance matching networks were used to provide matching at two different frequency bands (6 and 8 GHz) for optimum power added efficiency (PAE) and power gain. Fig. 2.12 shows the circuit diagram for the matching networks and the photograph of the fabricated tunable amplifier circuit. A pseudomorphic high electron mobility transistor (pHEMT) was mounted onto the silicon wafer and the matching circuits were connected to the transistor in a hybrid integration fashion. The amplifier demonstrated 7.2 dB gain with 26.4% PAE at 6 GHz and 6.1 dB gain with 16.7% PAE at 8 GHz.

Figure 2.12: (a) Circuit diagram of the double stub matching networks and the photograph of the adaptive amplifier [29].

An intelligent RF power amplifier with a reconfigurable output matching network is reported in [30]. The MEMS output matching network is based on a double-stub topology and consists of 4 MEMS switches, fixed capacitors and a varactor diode. The gain of the amplifier was optimized over a 4-GHz bandwidth at X-band by intelligently switching the MEMS switches and changing the bias voltage of the varactor. Each MEMS switch provides a capacitance ratio of 43:1 and can be used to tune the load impedance in a discrete manner with a total of 16 ( $2^4$ ) different states. For each state, the output impedance can also be fine tuned using the varactor diode. Fig. 2.13 shows the block diagram of the intelligent power amplifier consisting of GaAs pHEMT transistors, narrow-band filters used as the input matching, A/D converters, power sensors, and the MEMS output matching network. The system was fabricated in a hybrid configuration. Using intelligent control algorithms, the output power was maintained close to an optimum value for the frequency band from 7-11 GHz while the input power varied from 10 to 21 dBm. The system can also detect malfunctioning MEMS switches and reconfigure itself for this situation.

The adaptive multiband multimode power amplifier (PA) in [16] is continuously tunable

Figure 2.13: (a) Block diagram of the intelligent power amplifier, (b) picture of the overall system, (c) transistors and active circuitry (d) output MEMS matching network [30].

Figure 2.14: (a) Block diagram and (b) microphotograph of the multiband power amplifier in [16].

in operating frequency and output power level. The amplifier utilizes reconfigurable input and output impedance matching networks based on high-Q varactors (Q > 100 at 2 GHz) and a SiGe transistor as active device. It demonstrates an output power of 27-28 dBm at the 900, 1800, 1900, and 2100 MHz bands with reasonable efficiencies. Fig. 2.14 shows a microphotograph of the final implemented PA module where the active device and the matching networks are put together in a hybrid integration approach.

Reconfigurable impedance matching networks are also employed in intelligent automatic impedance matching systems that can be used for a wide variety of wireless applications such as antenna matching [21, 8]. Although good results in terms of band switching, efficiency and power control range, have been achieved for the adaptive amplifiers and automatic matching systems described in this section, there is still significant room for improvements at the technology level and integration of the active circuitry with the tunable matching networks. Consequently, even higher performance can be obtained for the future fully-integrated implementations.

### 2.3 Integrated CMOS-MEMS Devices

There has been an intensive research on RF-MEMS and RF-CMOS technologies in order to develop multiband RF transceivers. A single-chip implementation of these multiband RF transceivers will be possible by fusion of these two technologies. From this perspective, several researchers have studied the integration of MEMS devices with standard CMOS technologies. The main advantage of this integration process will be the low-cost fabrication of MEMS-based RF transceivers using a standard CMOS process and easy and rapid transfer to industry.

A low-temperature (below 310°C) CMOS-compatible fabrication process for the RF CMOS-MEMS switches is presented in [31]. The process features multilevel gold layers and formation of a capsule sealing the MEMS devices to ensure their stable operation, as depicted in Fig. 2.15. A single-pole 8-through (SP8T) contact-type RF MEMS switch stacked on a CMOS chip is fabricated using the proposed process. The switch is controlled directly by the underlying CMOS control circuitry operating at 3.3 V CMOS

Figure 2.15: Process flow for the CMOS-compatible MEMS process in [31].

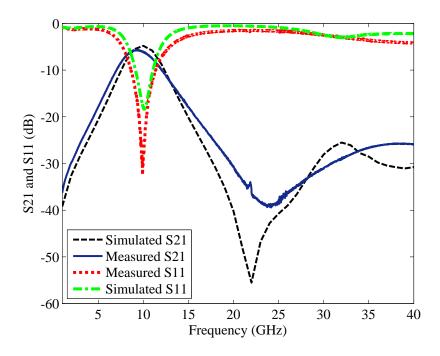

Figure 2.16: (a) Schematic view, (b) SEM image and (c) measured S-parameters of the CMOS-MEMS switch [31].

supply voltage. The switch offers single-chip integration capability and an RF performance higher than that of conventional p-i-n diode and transistor switches. Fig. 2.16 shows the schematic diagram and SEM image of the switch implemented on a 0.6- $\mu$ m CMOS chip, which contains a 3-bit address decoder circuit and an IO circuit for switch actuation. The switch is actuated by a 3.3 V DC external voltage source. The insertion loss and the isolation of the switch are 2 dB and higher than 40 dB from DC to 10 GHz, respectively, as shown in Fig. 2.16(c).

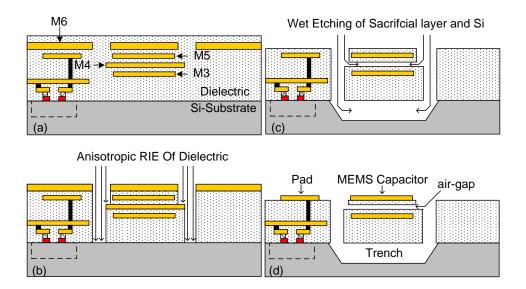

A CMOS-MEMS processing for the fabrication of electrostatically actuated microstructures with lateral motion was pioneered by Fedder et al. at Carnegie Mellon University

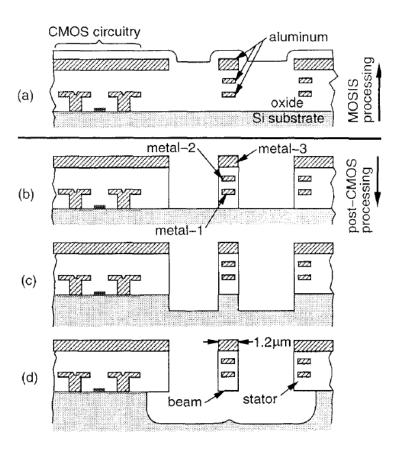

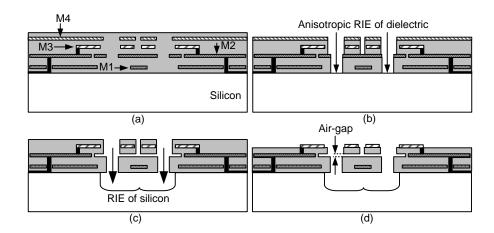

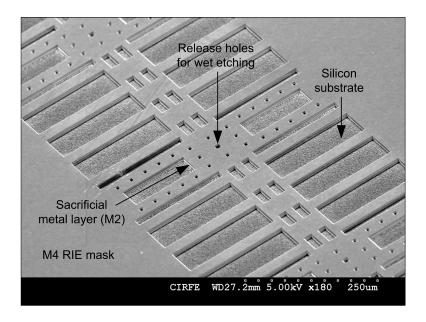

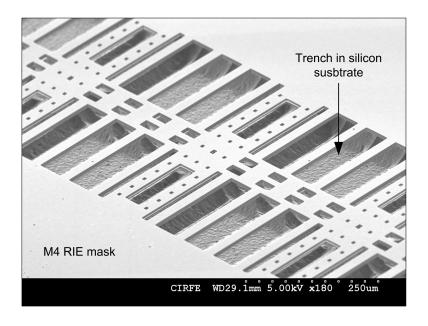

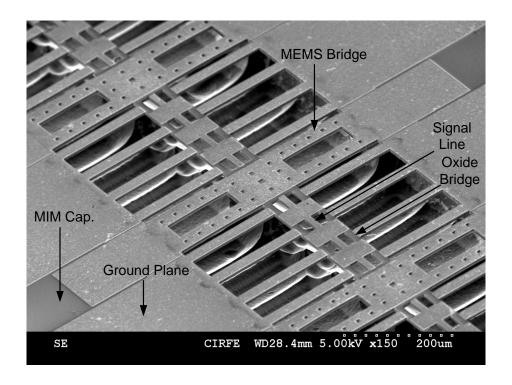

(CMU) [32]. The proposed process consists of a sequence of maskless dry etching steps as depicted in Fig. 2.17. The processing starts with a CMOS chip fabricated using a standard CMOS technology. Then one or multiples of CMOS metallization layers is used as an etch resistant mask to define the microstructures. The microstructures are released by removing the CMOS dielectric layer and the silicon substrate underneath using dry etching steps. Several RF-MEMS devices including high-Q micromachined inductors [33], RF-MEMS tunable capacitors [34, 35] and micromechanical resonators [36, 37] have been fabricated using this process.

Figure 2.17: Process flow for CMOS-MEMS processing at CMU (a) before applying the processing (b) after anisotropic oxide etching (c) after anisotropic silicon etching and (d) after isotropic etching of the silicon substrate and release [32].

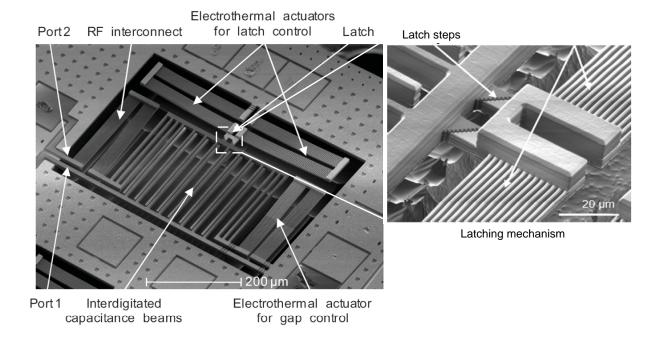

A CMOS-MEMS variable capacitor with a tuning ratio of 6.9:1, a Q-factor of 28 at 3 GHz, and a self-resonant frequency of 11 GHz is reported in [35]. The capacitor was fabricated in a standard 0.35-µm BiCMOS and micro-machined using the CMU CMOS-MEMS processing. The capacitor consists of two sets of interdigitated capacitance beams; one fixed and the other is movable as shown in Fig. 2.18. Electrothermal actuators are used to control the lateral (in-plane) gap, and hence capacitance of the device. A mechanical latching mechanism is also utilized to hold the movable beams at six different positions without consuming DC power.

Figure 2.18: SEM image of the CMOS-MEMS tunable capacitor [35].

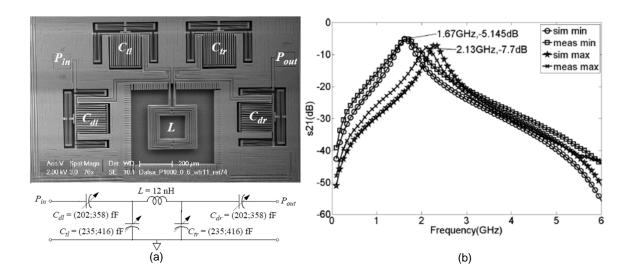

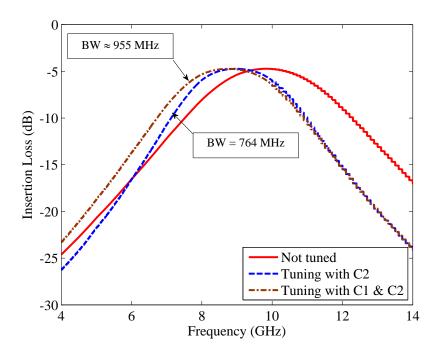

CMOS-MEMS tunable filters are reported in [38] using CMOS-MEMS tunable capacitors and micromachined inductors implemented by the CMU CMOS-MEMS processing. Fig. 2.19 shows the SEM image and the S-parameters of the tunable bandpass filter fabricated using foundry Jazz Semiconductor 0.35-µm BiCMOS process. The tuning range of the filter is from 1.67 GHz to 2.13 GHz (24%). The measured insertion loss varies from

Figure 2.19: (a) SEM image and circuit diagram of the tunable bandpass filter (b) S-parameters [38].

5.1 dB to 7.7 dB and the measured filter bandwidth is 450 MHz (Q = 3.7) and 350 MHz (Q = 6) across the tuning range.

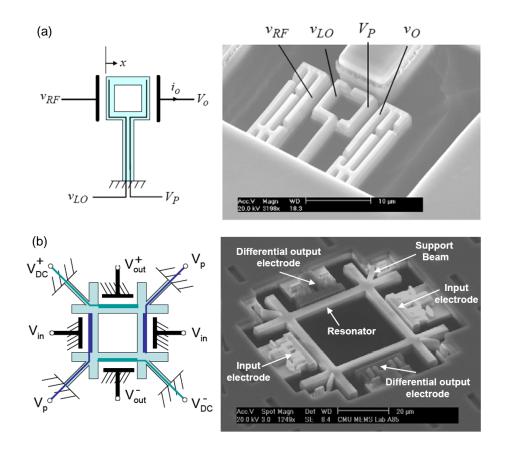

Micromechanical resonators, filters, and mixers were also made by micromachining composite metal and dielectric interconnect layers within foundry CMOS processes [37, 39, 40]. Fig. 2.20(a) shows a cantilever beam CMOS-MEMS resonator. The measured response at 10 mTorr vacuum shows that the cantilever has a primary resonance at  $f_o = 435$  kHz with a Q around 1400. Mixing at RF frequencies can be achieved using the proposed micromechanical resonator over a wide local oscillator (LO) frequency range from 10 MHz to 3.2 GHz. A differential square frame resonator operating at 6.184 MHz and 17.63 MHz for the fundamental and 2nd harmonic modes, respectively fabricated using CMOS-MEMS technology is also presented in Fig. 2.20(b). The resonator exhibits a quality factor of 996 in vacuum at the fundamental resonant frequency.

An RF-MEMS capacitive-type switch integrated in CMOS was reported by Zhang *et al*. [41]. The switch consists of two sets of interdigitated beams for capacitive coupling between

Figure 2.20: (a) Cantilever micromechanical resonator and (b) square frame resonators fabricated by CMOS-MEMS technology [37, 39].

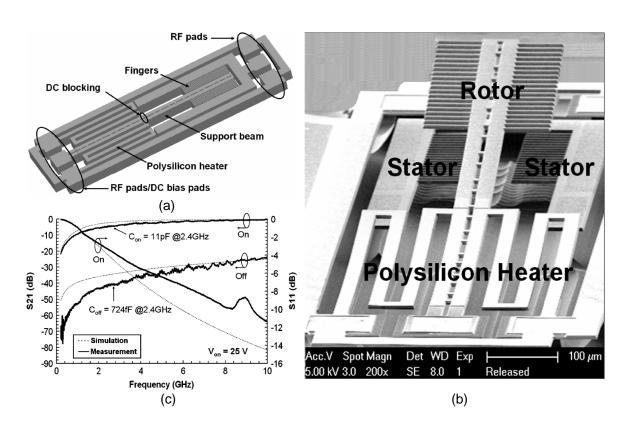

the RF ports in a CPW configuration as shown in Fig. 2.21. A thermal actuator with polysilicon heater is used for switch actuation. The switch is integrated in a commercial CMOS AMI 0.6-µm process using a CMOS-MEMS processing similar to CMU's process. Measurement results reveal an insertion loss of 1.6 dB and an isolation of 33 dB at 5.4 GHz as shown in Fig. 2.21(c). However, the size of the switch is too big due to the interdigitated beam structure, also the use of thermal actuators results in high DC power consumption if a suitable latching mechanism is not utilized for the proposed switch.

Figure 2.21: (a) 3-D view, (b) SEM image and (c) S-parameters of the CMOS RF MEMS switch [41].

# Chapter 3

# RF MEMS Tunable Impedance Matching Networks

#### 3.1 Introduction

Intelligent RF front-ends with multi-band functionality that can support different wireless standards have an important role in communication systems. In these systems, there is often an impedance mismatch between the different building blocks such as the antenna and the power amplifier due to the operation in different frequency bands or due to the varying operational conditions. A tunable impedance matching network with a wide impedance coverage, bandwidth and low insertion loss is required within these RF front-ends to ensure an optimum power transfer between the blocks and to increase the battery life time. In addition to tunable impedance matching in multi-band RF front-ends, reconfigurable matching networks capable of producing a multitude of impedance points are necessary for use in characterization of active semiconductor devices such as load-pull and noise parameter measurement setups [5]. In this case the matching network is used as an impedance tuner to manipulate the impedance conditions under which the device under test (DUT)

or transistor is tested.