# Evaluation of a Direct Detection Selenium-CMOS 8×8 Passive Pixel Sensor Array for Digital X-Ray Imaging Applications

by

#### Bahman Hadji

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2010

© Bahman Hadji 2010

#### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Digital imaging systems for medical applications use amorphous silicon thin-film transistor (TFT) technology due to its ability to be manufactured over large areas, making it useful for X-ray imaging, which requires imagers to be the size of the subject, unlike optical imaging. TFT technology is used to make imaging arrays coated with an X-ray detector called amorphous selenium (a-Se), which can be grown easily over large areas by being evaporated on a substrate. However, TFT technology is far inferior to crystalline silicon CMOS technology in terms of the speed, stability, noise susceptibility, and feature size. Where CMOS technology falls short is its inability to be manufactured in large wafers at a competitive cost, allowing TFT technology to continue to be dominant in the medical imaging field, unlike the optical imaging industry.

This work investigates the feasibility of integrating an imaging array fabricated in CMOS technology with an a-Se detector. The design of a CMOS passive pixel sensor (PPS) array is presented, in addition to how it is integrated with the amorphous selenium detector. Results show that the integrated Selenium-CMOS PPS array has good responsivity to optical light and X-rays, leaving the door open for further research on implementing CMOS imaging architectures going forward. Demonstrating that the PPS chips using CMOS technology can use a-Se as a detector is thus the first step in a promising path of research which should yield substantial and exciting results for the field. Though area may still prove challenging, larger

CMOS wafers can be manufactured and tiled to allow for a large enough size for certain diagnostic imaging applications and potentially even large area applications like digital mammography.

#### **Thesis Organization**

Chapter 1 gives general background information on large area digital imaging pixel architectures and amorphous selenium as an X-ray detector, setting up the motivation for this work. Chapter 2 outlines the design of the CMOS PPS array as well as how the a-Se detector was fabricated and integrated with the CMOS chip. Chapter 3 introduces the design of the printed circuit board used to test the PPS array. Chapter 4 discusses the results of testing the PPS array with the a-Se detector on several different fronts. Chapter 5 summarizes the work presented in the thesis and leaves the reader with an idea of where the research path might go from here.

#### **Acknowledgements**

It is standard cliché for the acknowledgements section in a graduate-level thesis to begin with the student thanking their supervisor, but after having nearly reached the end of the journey at the time of this writing, I truly understand why. And so I must begin by profoundly thanking Professor Karim S. Karim for his providing his unconditional support, guidance, encouragement, and resources during my time as a master's student and for generally being the best supervisor a graduate student could ask for. From the first time we talked when I was considering graduate studies two years ago, I was immediately taken in by his enthusiasm for research and for taking the time to explain every project the group was undertaking. Over the past two years, under Prof Karim's supervision, I have been able to gain valuable experience and participate in several different research projects through his guidance, all of which were fulfilling, and one of which ended up being this thesis project. I would like to thank Professor Ajoy Opal and Dr. Bill Bishop for agreeing to be readers of my thesis.

This work could not have been possible without funding from DALSA Corporation and the Ontario Centres of Excellence, and the enormous help of several people. First and foremost, I have to thank Amir Goldan, who has been a mentor to me from the time I started my graduate studies and one of the brightest and most organized people I know. This project was his brainchild starting with the layout and fabrication of the chip and I was merely lucky enough to join the research group at a time when it made sense for him to shift his focus back towards his main doctoral thesis projects. Still, he made time for this project and we worked together from the design and logistics all the way through to the testing phase, and without his insight, I would have never been able to reach this point.

I would also like to recognize Dr. Hasib Majid, who joined our research group in 2009 and brought with him his enormous expertise on everything to do with selenium. Hasib was tremendously helpful and was instrumental in getting the setup right for testing the array once the selenium had been deposited on the chips. Collaborating with somebody who is so knowledgeable about the topic at hand really makes it enjoyable to work on a project.

I am extremely thankful to a few other people who were integral to this work getting done: Dr. George Belev, who spent countless hours in the preparation and successful deposition of selenium on the tiny chips at the University of Saskatchewan; Nick Allec, whose knowledge of and proficiency with detector physics simulation allowed us to thoroughly analyze the photogeneration in the sensor; Hadi Izadi, the jack of all trades in our research group, who performed the delicate wirebonding of the chips in the G2N Lab (and I cannot forget our battling that microcontroller together until we finally

tamed it); and Andy Barber from the MME Department, who lent his masterful surface mount soldering skills to us whenever we inquired. I should also mention the rest of the STAR group including Dali Wu, Mohammad Yazdandoost, Chris Hristovski, Dr. Nader Safavian, and Umar Shafique, who have each helped me in some way in getting to this point.

I would be remiss if I neglected to mention the incredible experience I've had as a teaching assistant during my time as a graduate student, which actually helped with research. Having been able to teach material every term that I enjoyed likely had a lot to do with how fulfilling the role ended up being for me – it truly never felt like a job, and maybe I even made a few students love circuits. So I'd like to thank the ECE Department as well as the instructors for whom I had the pleasure of TAing for giving me the chance to do so: Dr. David Rennie, whose friendly advice I've been able to count on for years, on everything from teaching, to research, to career decisions; and Professor Jim Barby and Professor Ajoy Opal, both of whom were pleasures to work with in every aspect.

On a personal note, I'd also like to thank and wish the best of luck to my friends Jay Shirtliff, Adam Neale, Elena Bassiachvili, and Dan Miller, all of whom are also finishing their master's degrees here, as we all started around the same time after graduating from the 2008 ECE class. Having a good core group of friends who could relate to my experience definitely made it easier to complete my work. I also appreciate the support of my close friends away from academia including Roger Bourret, Ben Smith, Ryan Hutchins, Jason Fice, and Phil Lamoureux, who were always there to lift my spirits and take my mind off work when I needed it. And I can't forget to mention the ECE Graduate Office staff, and especially Wendy Boles, our wonderful Graduate Studies Coordinator, for being so helpful and having an answer for everything on the logistical side of things, from the time I was an undergraduate student trying to figure out acceptance and enrollment into graduate studies to the very day my thesis acceptance form was handed in (it really was a piece of cake).

Lastly, I would not be here were it not for my family's loving support – my mom and dad, and my two sisters. I am forever grateful for your never-ending encouragement, which really does make me believe in myself.

As my time at the University of Waterloo winds down, I can look back and say it was the best time of my life and my education, contacts, and experiences were truly invaluable. So I want to thank the University, the Faculty of Engineering, and the ECE Department again. While the time has come to move on, I'll always think of Waterloo as home and I'm extremely proud to be a twice-alumnus of this fine institution.

And with that, I think it's finally time to stop hitting the snooze button...

#### **Table of Contents**

| AUTHOR'S DECLARATION                                                              | ii  |

|-----------------------------------------------------------------------------------|-----|

| Abstract                                                                          | iii |

| Acknowledgements                                                                  | v   |

| Table of Contents                                                                 | vii |

| List of Figures                                                                   | ix  |

| List of Tables                                                                    | xii |

| Chapter 1 Background.                                                             | 1   |

| 1.1 Introduction to Digital X-Ray Imaging                                         | 1   |

| 1.1.1 Large Area Medical Imaging                                                  | 2   |

| 1.1.2 Passive Pixel Sensor Architecture                                           | 3   |

| 1.1.3 Active Pixel Sensor Architectures                                           | 8   |

| 1.2 Amorphous Selenium as an X-Ray Detector                                       | 12  |

| 1.2.1 Operation of Radiation Detectors                                            | 13  |

| 1.2.1.1 Indirect Radiation Detection                                              | 14  |

| 1.2.1.2 Direct Radiation Detection                                                | 15  |

| 1.3 Integration of CMOS and Selenium: Motivation for a Selenium-CMOS X-ray Sensor | 16  |

| Chapter 2 Design and Implementation of Integrated Selenium-CMOS PPS Array         | 18  |

| 2.1 Design and Layout of CMOS 8×8 PPS Array                                       | 18  |

| 2.2 Amorphous Selenium: Structure, Fabrication, and Integration with PPS Chip     | 27  |

| 2.2.1 The Structure of a-Se as an X-ray Detector                                  | 27  |

| 2.2.2 Deposition via Vacuum Evaporation                                           | 29  |

| 2.2.2.1 Potential Issues during Deposition                                        | 31  |

| 2.2.3 Integration of a-Se Detector with CMOS PPS Array                            | 32  |

| 2.2.3.1 Post-Deposition Preparation                                               | 34  |

| Chapter 3 Design and Assembly of PPS Readout Printed Circuit Board                | 38  |

| 3.1 Voltage Regulators                                                            | 39  |

| 3.1.1 5 V Regulator                                                               | 40  |

| 3.1.2 1.8 V Regulator                                                             | 40  |

| 3.1.3 -5 V Regulator                                                              | 40  |

| 3.2 Microcontroller                                                               | 41  |

| 3.3 Buffers                                                                       | 41  |

| 3.3.1 1.8 V Gate Driver Buffer                    | 42 |

|---------------------------------------------------|----|

| 3.3.2 5 V Reset Signal Buffer                     | 42 |

| 3.4 Digital-to-Analog Converters                  | 42 |

| 3.5 Charge Amplifiers                             | 43 |

| 3.6 Instrumentation Amplifier                     | 44 |

| 3.7 Low-Pass Filter                               | 44 |

| 3.8 Test Circuitry and Miscellaneous Features     | 45 |

| 3.9 PCB Layout                                    | 47 |

| 3.9.1 MCU Oscillator and IRQ/RST Modifications    | 49 |

| Chapter 4 Testing Results and Analysis            | 52 |

| 4.1 Validation of CMOS PPS Array                  | 52 |

| 4.2 Testing of Integrated Selenium-CMOS PPS Array | 56 |

| 4.2.1 Electric Field Bias                         | 58 |

| 4.2.2 Optical Light                               | 61 |

| 4.2.2.1 Linearity                                 | 65 |

| 4.2.3 Protective Epoxy Leakage Test               | 68 |

| 4.3 Testing of PPS Readout Board and Array        | 70 |

| 4.3.1 PPS Array Testing on Readout Board          | 78 |

| 4.4 X-Ray Testing of Array                        | 83 |

| 4.4.1 Analysis of X-ray Photocurrent              | 87 |

| Chapter 5 Conclusion                              | 93 |

| 5.1 Summary                                       | 93 |

| 5.2 Future Research Paths and Recommendations     | 94 |

| References                                        | 96 |

### **List of Figures**

| Figure 1: Passive Pixel Sensor (PPS) architecture for general purpose image sensing           | 3         |

|-----------------------------------------------------------------------------------------------|-----------|

| Figure 2: PPS architecture using a-Se detector for digital imaging, with off-array charge     |           |

| amplifier shown                                                                               | 5         |

| Figure 3: Three-transistor active pixel sensor architecture                                   | 9         |

| Figure 4: Four-transistor active pixel sensor architecture                                    | 11        |

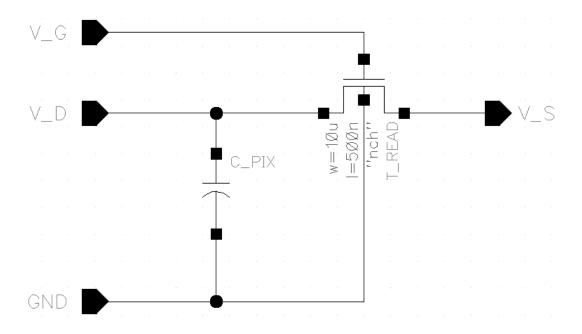

| Figure 5: Cadence schematic of a single PPS pixel cell                                        | 19        |

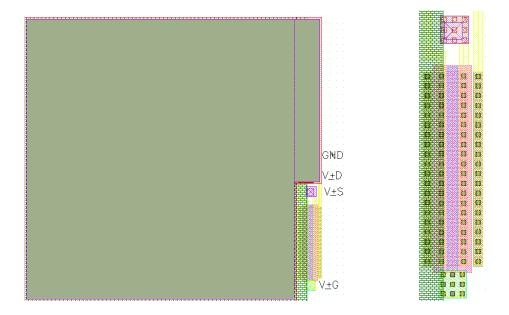

| Figure 6: Layout of a single CMOS PPS pixel. A closeup of the PPS transistor in the bot       | tom       |

| right corner of the pixel is shown on the right.                                              | 20        |

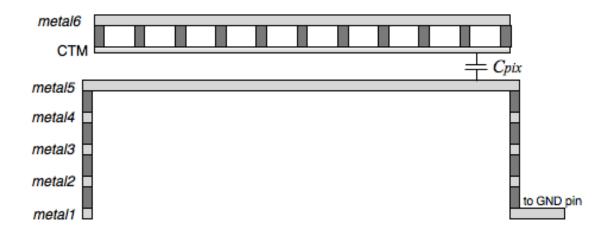

| Figure 7: Cross-section illustration of a pixel on the CMOS die showing $C_{pix}$ implemented | d as an   |

| integrated MIM capacitor between the top electrode and ground.                                | 22        |

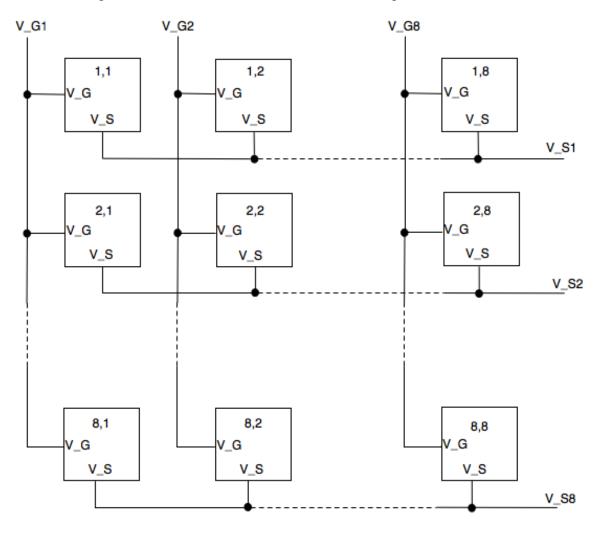

| Figure 8: 8×8 PPS array interconnections                                                      | 23        |

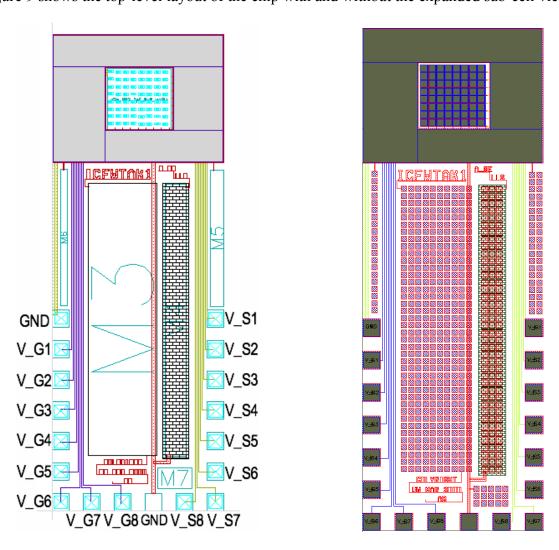

| Figure 9: Full layout of PPS chip in Cadence; with expanded sub-cells (right)                 | 24        |

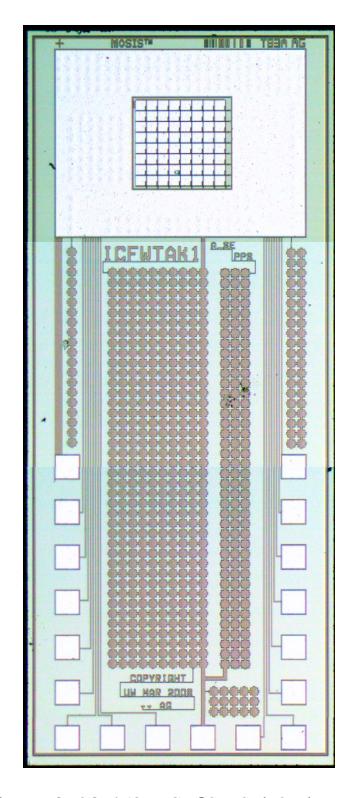

| Figure 10: Micrograph of the 0.18 μm CMOS PPS die fabricated through CMC                      | 26        |

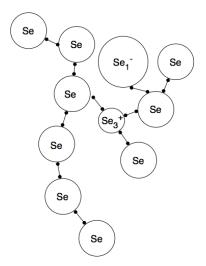

| Figure 11: The structure of an amorphous selenium (a-Se) chain, showing its charge defe       | ects and  |

| amorphous nature (adapted from [14])                                                          | 27        |

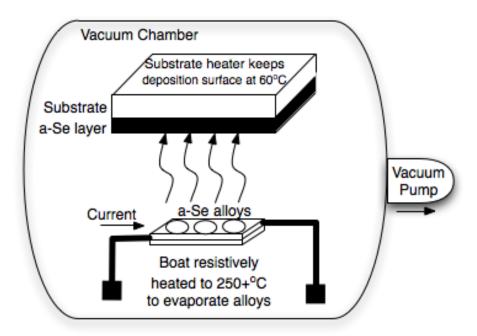

| Figure 12: Amorphous selenium is evaporated and deposited as a film on the target subst       | rate, the |

| flat panel imager.                                                                            | 30        |

| Figure 13: Amorphous selenium on top of the 8×8 active array area. The lighter circular       | area is   |

| the chromium top contact used to apply the electric field bias.                               | 33        |

| Figure 14: PCB substrate (daughterboard) used to hold the CMOS image sensor                   | 34        |

| Figure 15: Wirebonding diagram used for connecting bond pads to the daughterboard             | 35        |

| Figure 16: CMOS PPS chip wirebonded to daughterboard and encapsulated in protective           | non-      |

| conductive transparent epoxy                                                                  | 37        |

| Figure 17: Block diagram of the PCB used for testing the PPS array                            | 39        |

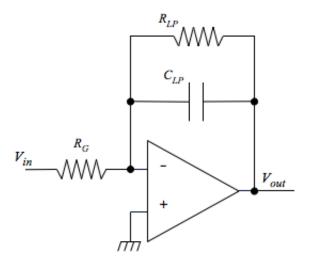

| Figure 18: Low-pass filter used to eliminate high-frequency noise                             | 45        |

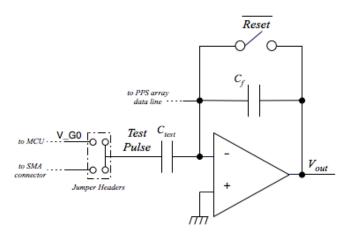

| Figure 19: Test capacitor at the input of the charge amplifier, with a jumper choosing the    | driving   |

| mechanism                                                                                     | 46        |

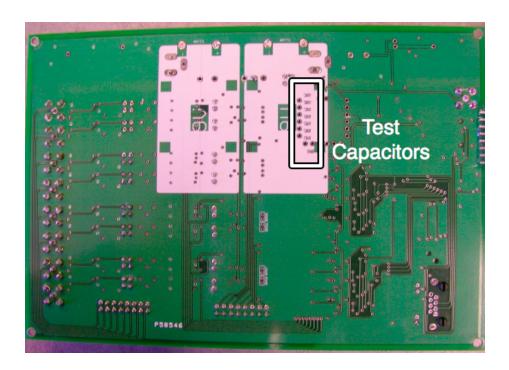

| Figure 20: PPS readout PCB after population of components                                     | 47        |

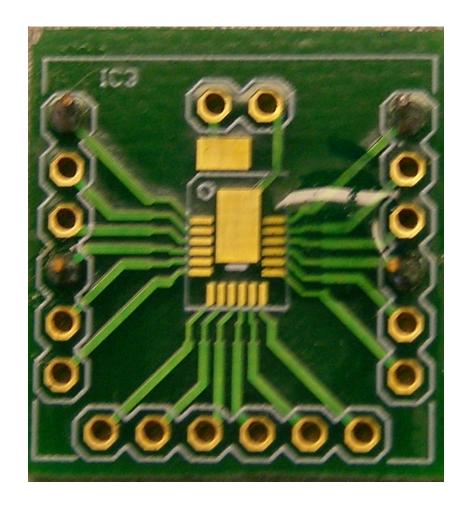

| Figure 21: Backside of PCB, with test capacitors labeled                                      | 48        |

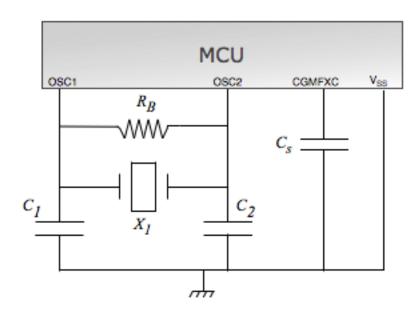

| Figure 22: Crystal oscillator and external circuitry, with the MCU's associated pins          | 49        |

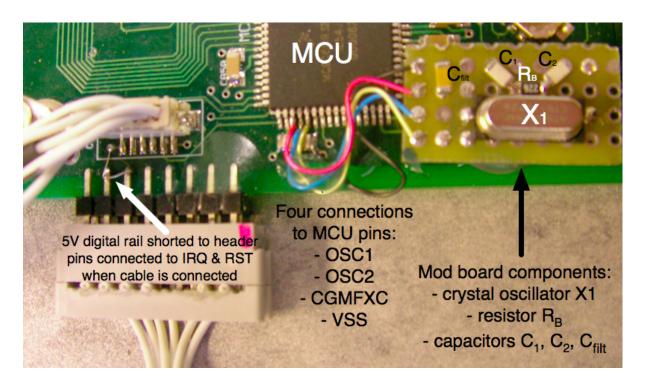

| Figure 23: Post-fabrication modifications to the PCB associated with the MCU.                 | 51        |

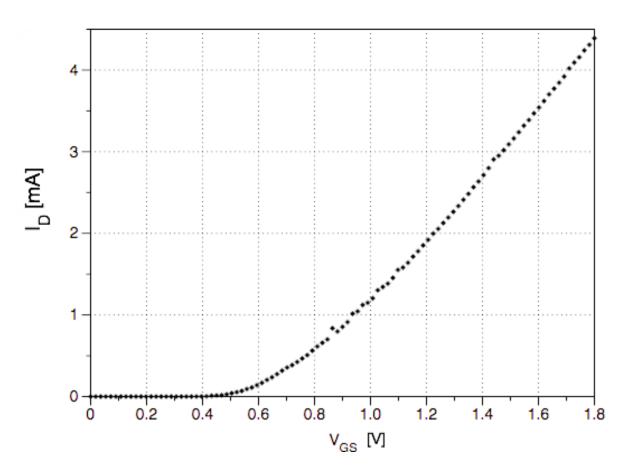

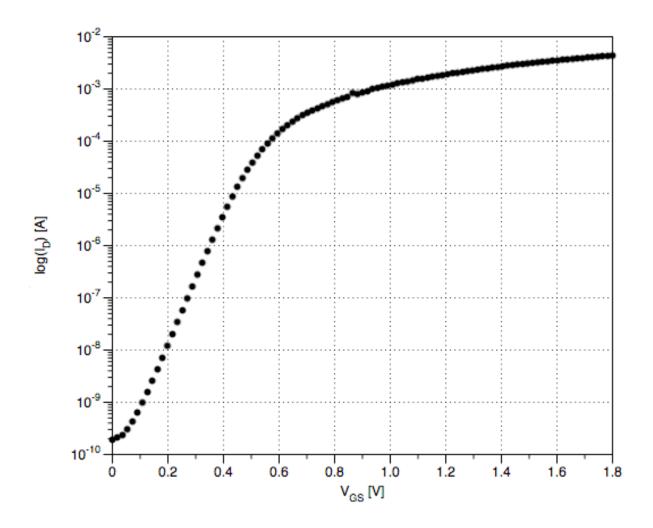

| Figure 24: $I_D$ vs. $V_{GS}$ graph for an on-pixel transistor in the CMOS PPS array, with $V_D$ =1.8 V.   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Figure 25: $I_D$ vs $V_{GS}$ curve from Figure 25 with $I_D$ plotted logarithmically to show sub-threshold |  |  |  |  |

| leakage in the NMOS transistor55                                                                           |  |  |  |  |

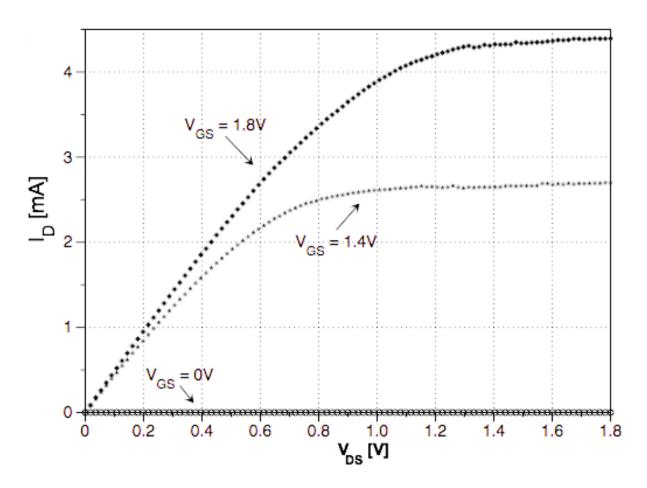

| Figure 26: $I_D$ vs $V_{DS}$ graph for an on-pixel transistor in the CMOS PPS array, with varying $V_{GS}$ |  |  |  |  |

| values56                                                                                                   |  |  |  |  |

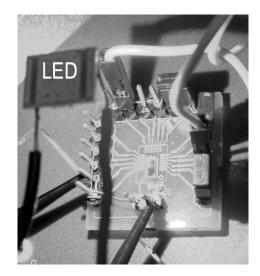

| Figure 27: Test equipment setup, with the high-voltage source (top left), test fixture (top right),        |  |  |  |  |

| and Semiconductor Parameter Analyzer (bottom). A PC (out of frame) controls the SPA,                       |  |  |  |  |

| which is connected to the test fixture holding the sample.                                                 |  |  |  |  |

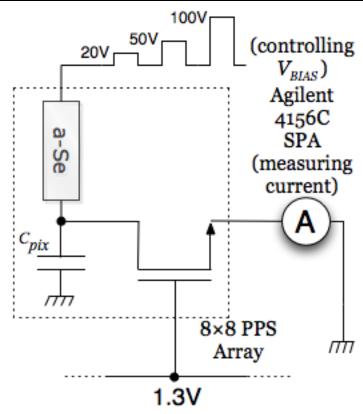

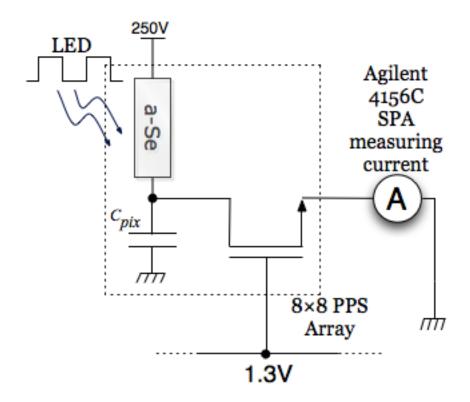

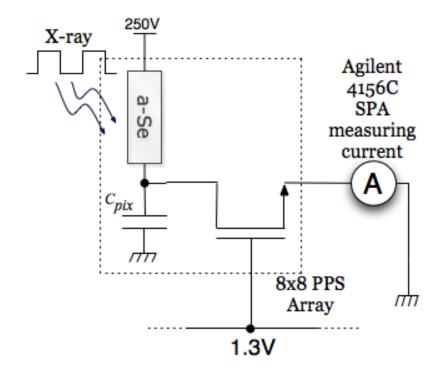

| Figure 28: Measurement setup for electric field bias dark current test                                     |  |  |  |  |

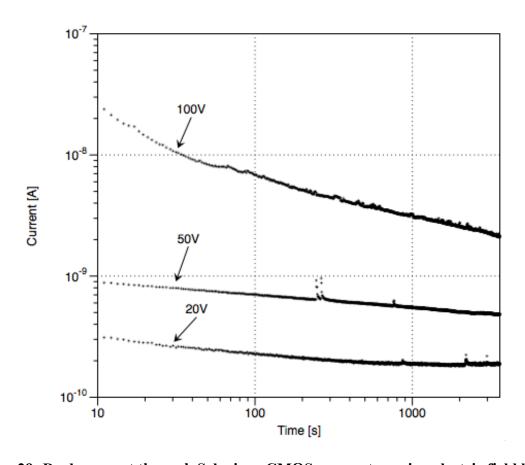

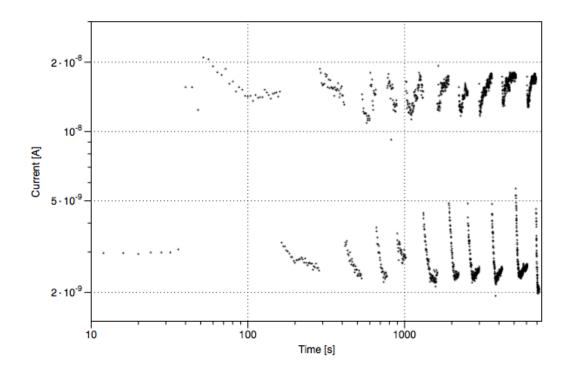

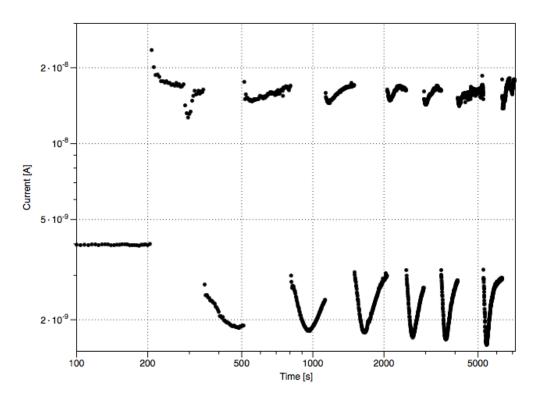

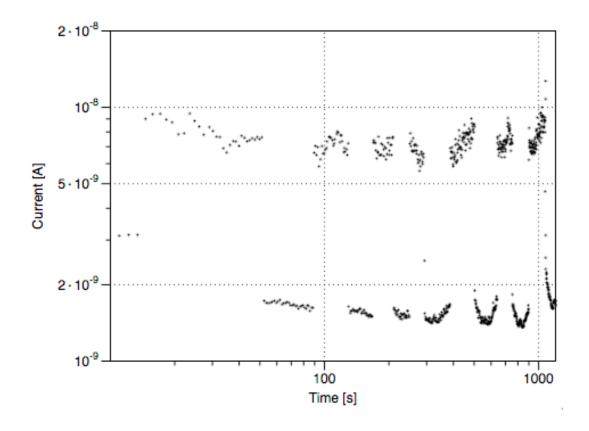

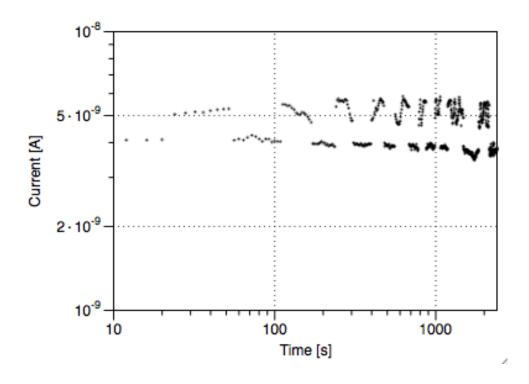

| Figure 29: Dark current through Selenium-CMOS array at varying electric field biases                       |  |  |  |  |

| Figure 30: The PPS array was tested inside a test fixture with LEDs positioned above it to test its        |  |  |  |  |

| photoconductivity61                                                                                        |  |  |  |  |

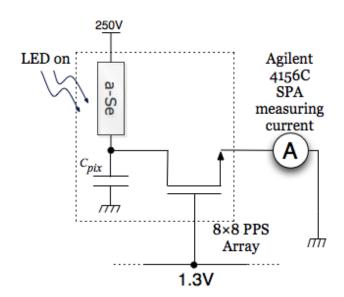

| Figure 31: Pulsed optical photocurrent test setup                                                          |  |  |  |  |

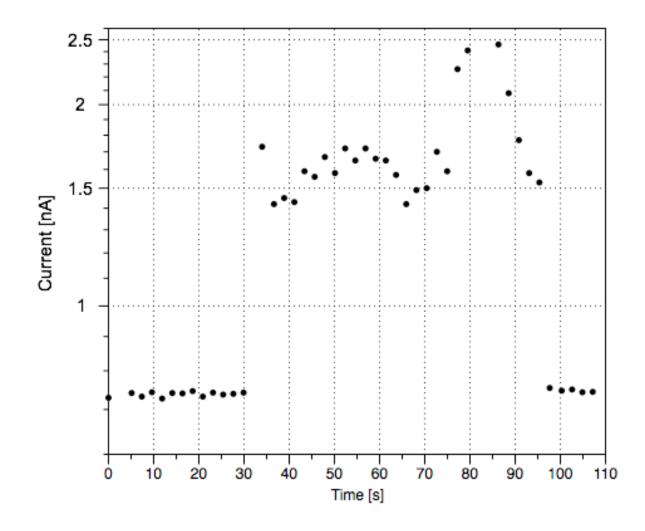

| Figure 32: Pulsed photocurrent through PPS array under blue light at 3.33 V/μm63                           |  |  |  |  |

| Figure 33: Pulsed photocurrent through PPS array under green light at 3.33 V/μm63                          |  |  |  |  |

| Figure 34: Pulsed photocurrent through PPS array under red light at 3.33 V/μm                              |  |  |  |  |

| Figure 35: Photoconductance linearity test setup                                                           |  |  |  |  |

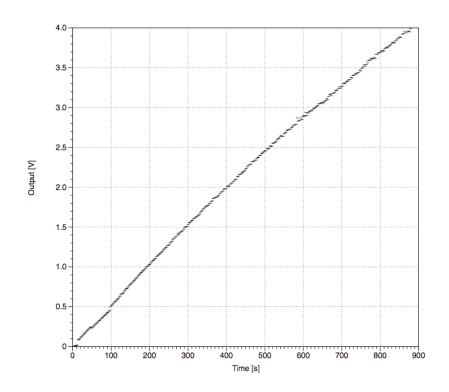

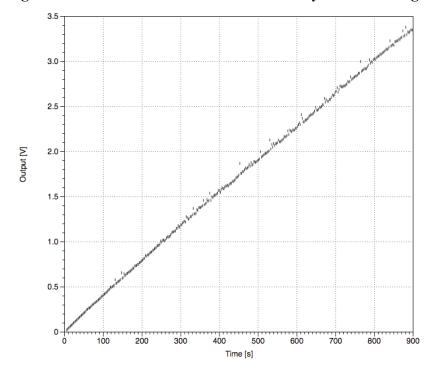

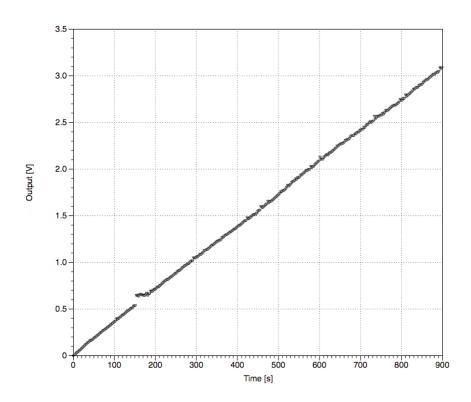

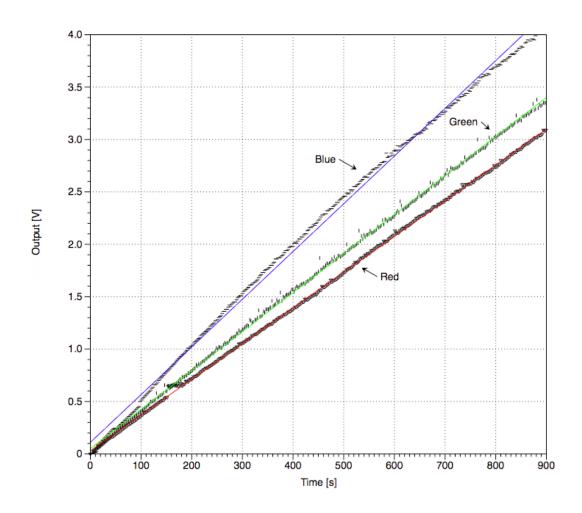

| Figure 36: Selenium-CMOS detector linearity under blue light                                               |  |  |  |  |

| Figure 37: Selenium-CMOS detector linearity under green light                                              |  |  |  |  |

| Figure 38: Selenium-CMOS detector linearity under red light                                                |  |  |  |  |

| Figure 39: Selenium-CMOS PPS array output linearity under optical light wavelengths                        |  |  |  |  |

| Figure 40: Daughterboard used to measure leakage through PCB and transparent encapsulating                 |  |  |  |  |

| epoxy69                                                                                                    |  |  |  |  |

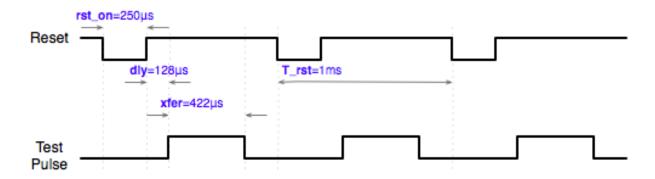

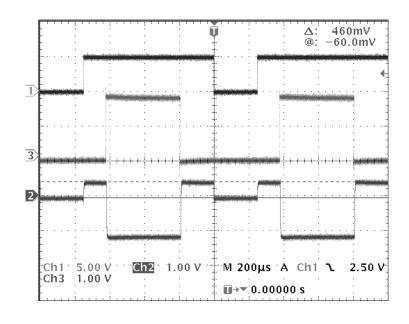

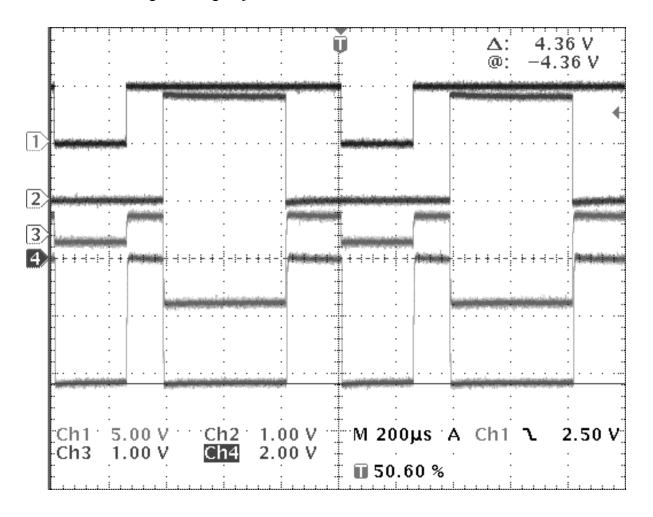

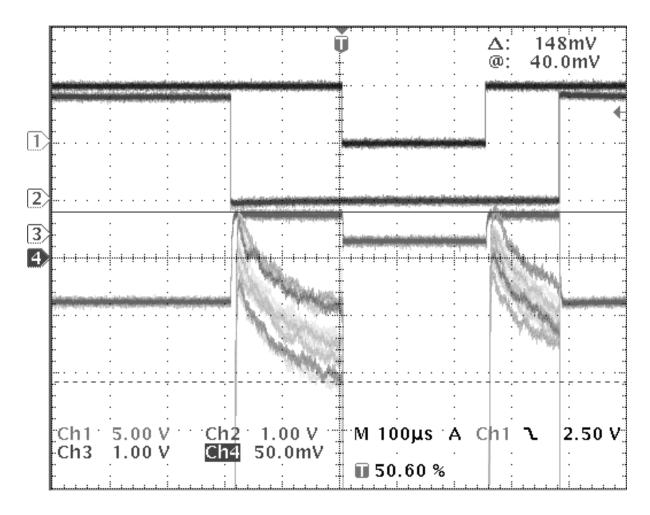

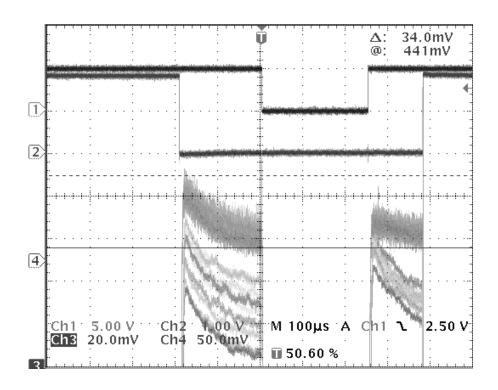

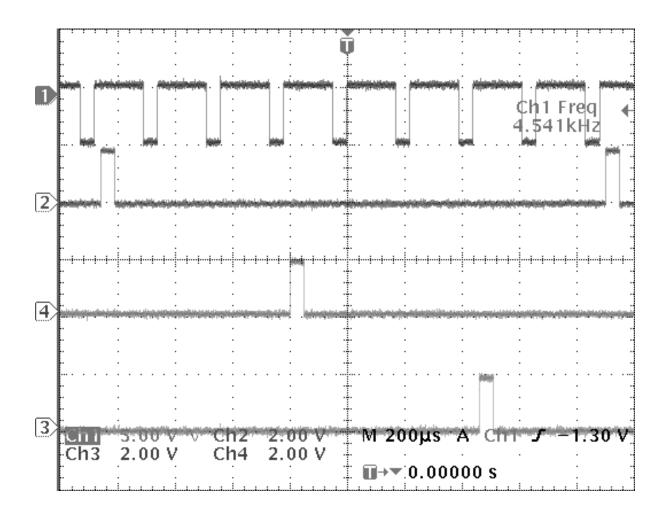

| Figure 41: Timing diagram for driving reset signal and test input to charge amplifiers71                   |  |  |  |  |

| Figure 42: Charge amplifier output being driven by a test pulse from the MCU71                             |  |  |  |  |

| Figure 43: Charge injection due to reset switch toggling at the channel 0 charge amplifier output          |  |  |  |  |

| 72                                                                                                         |  |  |  |  |

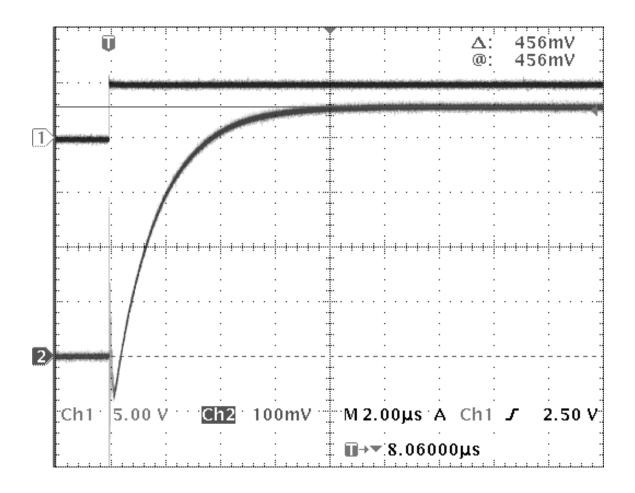

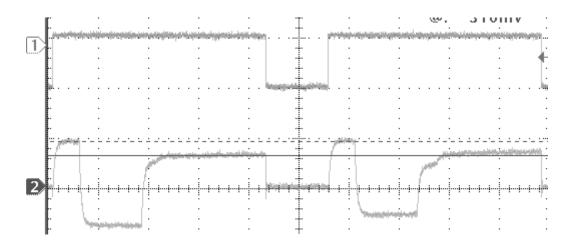

| Figure 44: Charge gain of the channel 0 charge amplifier output                                            |  |  |  |  |

| Figure 45: A closer look shows that the charge amplifier output was not decaying due to loss of            |  |  |  |  |

| charge, but because the input signal had an undershoot                                                     |  |  |  |  |

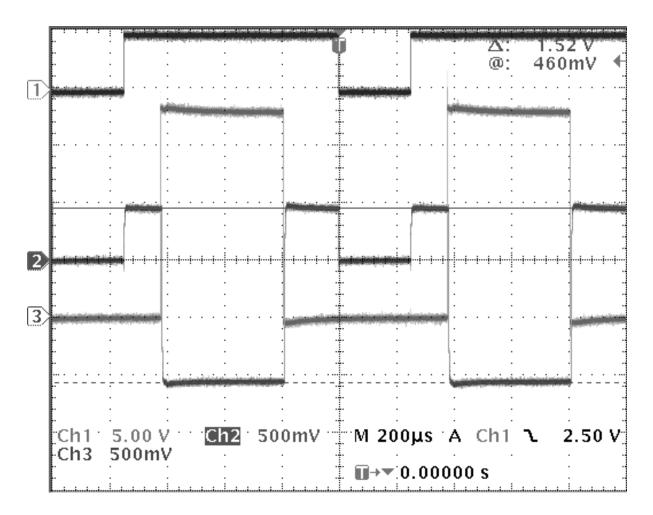

| Figure 46: The instrumentation amplifier eliminates the charge injection seen in the charge                |  |  |  |  |

| amplifier output                                                                                           |  |  |  |  |

| Figure 47: The instrumentation amplifier's 0 V level fluctuates because it tracks the charge  | <b>:</b> |

|-----------------------------------------------------------------------------------------------|----------|

| amplifier's output.                                                                           | 76       |

| Figure 48: Instrumentation amplifier output shown in perspective with charge amplifier output | ıtput77  |

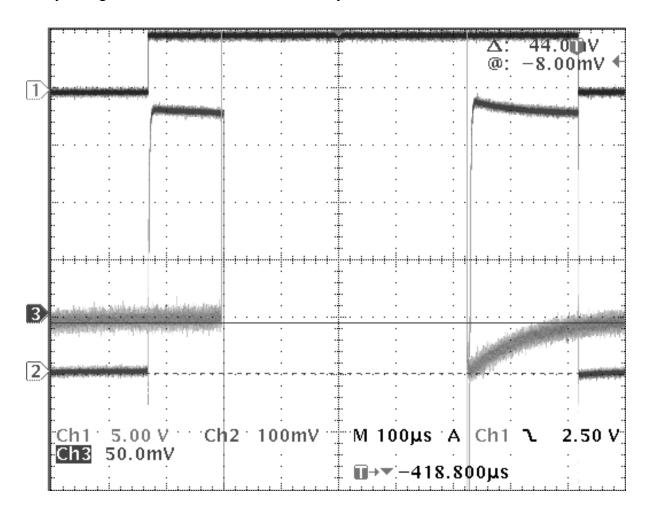

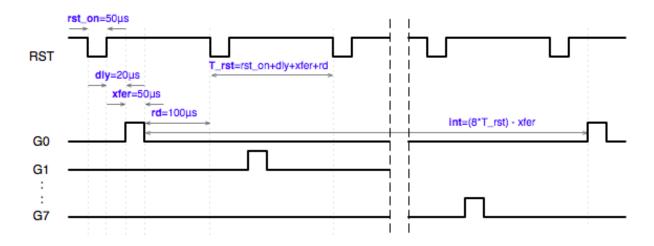

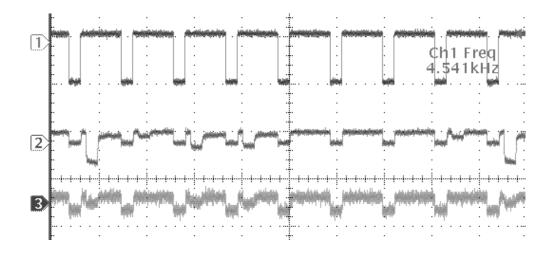

| Figure 49: PPS array timing diagram                                                           | 79       |

| Figure 50: Stimulus for the PPS array, showing the reset signal and three read lines          | 80       |

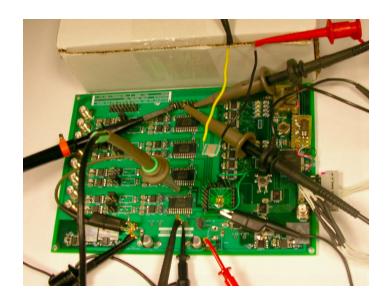

| Figure 51: Setup for testing Selenium-CMOS PPS array on readout board                         | 81       |

| Figure 52: Output for two different channels with PPS array on board                          | 81       |

| Figure 53: Output showing integration/readout cycles on data line for two adjacent pixels     | 82       |

| Figure 54: X-ray System used to test Selenium-CMOS PPS array                                  | 83       |

| Figure 55: Pulsed X-ray current test setup                                                    | 84       |

| Figure 56: Pulsed photocurrent through Selenium-CMOS array under exposure to 40kVp            | X-ray    |

| beam                                                                                          | 85       |

| Figure 57: Transient response to single one-minute pulse of 40 kVp X-ray beam                 | 86       |

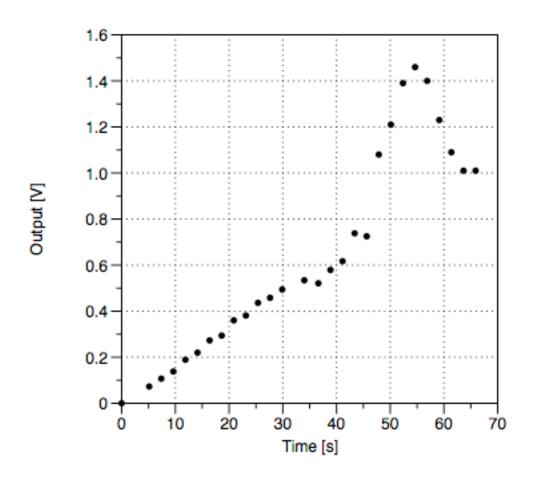

| Figure 58: Selenium-CMOS detector linearity under 40 kVp X-ray beam                           | 87       |

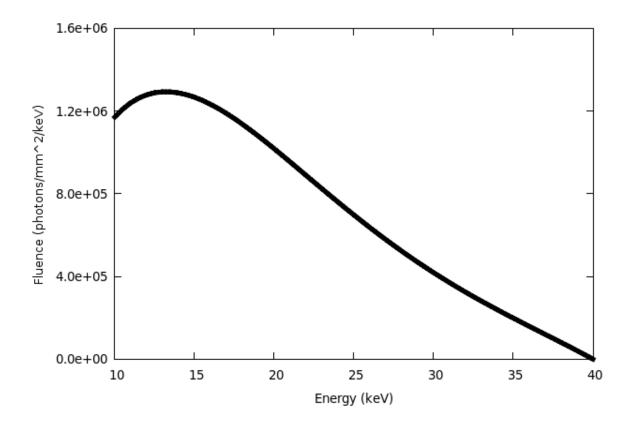

| Figure 59: Simulated spectrum of 40 kVp X-ray beam on the Selenium-CMOS detector              | 89       |

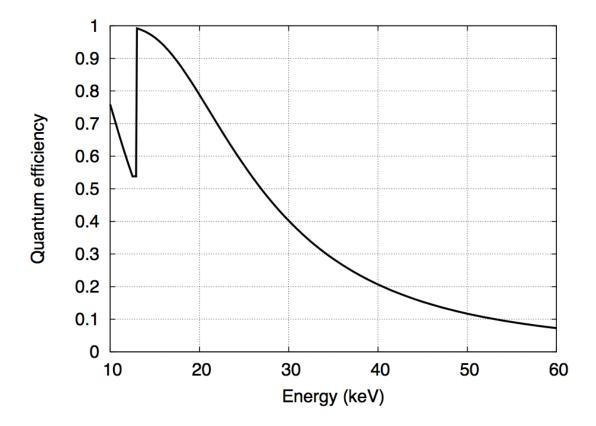

| Figure 60: 75 µm a-Se detector quantum efficiency                                             | 90       |

#### **List of Tables**

| Table 1: Comparing readout time constants using typical process parameters for TFT an | nd CMOS |

|---------------------------------------------------------------------------------------|---------|

| technology                                                                            | 7       |

| Table 2: A comparison of different direct radiation detectors' properties             | 16      |

| Table 3: Electric field bias test sequence                                            | 59      |

## Chapter 1

# **Background**

#### 1.1 Introduction to Digital X-Ray Imaging

The field of medical imaging has seen a remarkable evolution in the past two decades. While film screen-based X-ray radiography systems proved resilient over the bulk of the 20th century, the technological advances in the semiconductor industry that allowed engineers to revolutionize so many other fields during this time eventually heralded an elegant solution to allow for the development of a digital X-ray imaging system. Materials that could convert X-ray photons into electric charge had already been identified and once the capability to integrate these detectors with readout electronics became possible, a digital imaging system was developed with wide-ranging advantages over the traditional film-screen system – higher resolution images which result in a smaller chance of false positive and false negative diagnoses, instant access to an on-screen X-ray image, and the elimination of stacks of film archives, all while exposing the patient to lower doses of potentially harmful radiation.

#### 1.1.1 Large Area Medical Imaging

Optical imaging and X-ray imaging have a major difference which has a significant consequence on the architecture of the devices used to capture the respective types of images. The image of a large, beautiful landscape can be projected on and captured with an imaging device the size of a fingernail inside the camera, since light can be refracted through a lens. But X-rays cannot be focused the way light can be, meaning that to take an X-ray image of an object the size of a hand, an imager of the same size is required. This makes it difficult to take advantage of crystalline silicon CMOS technology for the electronic imaging system because large silicon wafers cannot be manufactured while maintaining crystallinity throughout, and their production is extremely costly.

As a result, digital imagers in the medical field use amorphous silicon thin-film transistor (TFT) technology, despite its lower carrier mobility and poorer noise performance compared to CMOS technology. This is because TFT wafers can be manufactured with ease over a large area as the amorphous technology does not need to maintain crystallinity and can be easily deposited on a substrate. The most prevalent imaging system of this type is called a flat panel active matrix array. A typical imager of this type contains an X-ray detector on top of an array of individual pixels of repeated circuitry (fabricated in TFT technology). The circuitry is used to read the electric charge collected by the X-ray detector as a result of the incident X-ray photons, and the pixels' digitized values are put together as part of the array to make up a high-resolution digital image. The conversion of the X-ray photons into electric charge can be done via a direct detection scheme, where the detector converts X-ray photons directly into electric charge, or an indirect detection scheme, where the detector converts X-

ray photons to light photons and uses a photodetector to convert the optical photons into electric charge.

#### 1.1.2 Passive Pixel Sensor Architecture

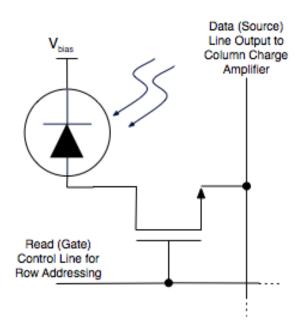

The passive pixel sensor (PPS), first reported by Rudolph Dyck and Gene Weckler [1] in the late 1960s, is the prevalent pixel architecture standard for flat panel arrays in the medical imaging industry, due to its compact structure and ease of fabrication. The pixel architecture, shown in Figure 1, consists of a photodetector which converts incoming photons into electric charge, accumulating and giving rise to a voltage at the pixel detector node due to the capacitance present there. The detector is connected to the drain of a transistor, which acts as a switch when its gate is asserted to read out the stored charge at the end of each integration cycle. The word *passive* comes from the fact that this transistor acts as a switch and does not provide any on-pixel gain to the signal stored at the detector node.

Figure 1: Passive Pixel Sensor (PPS) architecture for general purpose image sensing

In the case of optical imaging, silicon itself can act as the detector due to its photoreceptive properties, and so a simple p-n photodiode is sufficient. However, for X-ray imaging, the detector needs to be thick enough to absorb a large portion of the incoming X-ray photons and convert them into electric charge. Since the detector's capacitance is inversely proportional to its thickness, a thick detector results in a small capacitance. For a typical amorphous selenium (a-Se) panel, the capacitance of the a-Se detector for a pixel is given by the following equation:

$$C_{det} = \frac{\varepsilon_0 \varepsilon_{a-Se} A_{pix}}{t_{det}},\tag{1}$$

where  $C_{det}$  is the effective detector capacitance for each pixel,  $\varepsilon_0 = 8.85 \times 10^{-12} \,\mathrm{F/m}$ ,  $\varepsilon_{\text{a-Se}}$  is the dielectric constant of amorphous selenium (3.6),  $A_{pix}$  is the area of the pixel, and  $t_{det}$  is the thickness of the a-Se detector. For a 150  $\mu$ m x 150  $\mu$ m pixel with an a-Se detector 500  $\mu$ m thick,  $C_{det}$  is only about 1 fF. This small capacitance means that the photocurrent can result in a buildup of voltages that are large enough to break down the transistor during integration, since the voltage on a capacitor is equal to the charge on it divided by its capacitance:

$$V_{pix} = \frac{Q_{ph}}{C_{dot}}. (2)$$

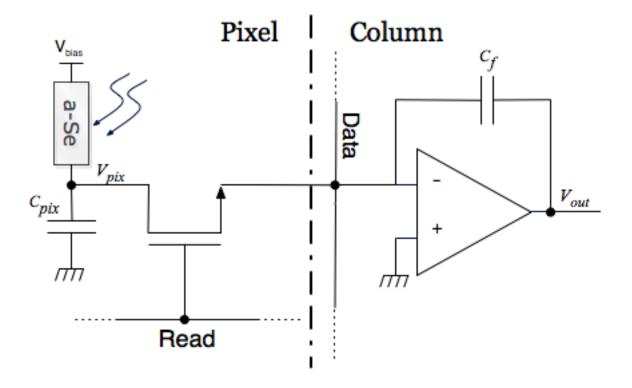

As a result, the PPS architecture used in medical imaging requires the presence of an on-pixel capacitor  $C_{pix}$  (typically 1 pF) to store the charge  $Q_{ph}$  and ensure that  $V_{pix}$  does not exceed the technology's threshold. The effective capacitance at the node is then the sum of  $C_{pix}$  and  $C_{det}$ , which is effectively  $C_{pix}$  due to the fact that it is orders of magnitude larger than  $C_{det}$ . A typical PPS architecture using amorphous selenium as a detector is shown in Figure 2.

Figure 2: PPS architecture using a-Se detector for digital imaging, with off-array charge amplifier shown

A charge amplifier is used to convert the charge that is read out through the transistor into a stable voltage to allow for digitization and processing externally. The output voltage of the charge amplifier  $V_{out}$  is directly due to the charge  $Q_{ph}$  accumulated on the pixel capacitor during integration and transferred during readout, and as such can be given by the following equation:

$$V_{out} = \frac{Q_{ph}}{C_f}. (3)$$

Thus, it follows from the two preceding equations that if the feedback capacitor  $C_f$  is equal to the pixel capacitor  $C_{pix}$ , the charge amplifier output voltage will be equal to  $V_{pix}$ , the voltage which is accumulated on  $C_{pix}$  during integration.

The operation of a PPS array consists of the two aforementioned cycles – the integration cycle and the readout cycle. The individual pixels in the array are connected in a way that allows for columnar readout of the imaging signals such that during readout, all of the pixels in an addressed column are read out in parallel, with a single charge amplifier per column. The gate of the PPS transistor is connected to a gate addressing or *read* line, shared by every pixel in the same row in the array, and the source of the transistor is connected to a *data* line, shared by every pixel in the same column in the array.

During the integration cycle, the gate line is deasserted such that the transistor is turned off, allowing for charge to integrate on the pixel capacitor proportional to the incident X-ray radiation on that pixel. The integration cycle is followed by the readout cycle, where the gate line is asserted so that the transistor turns on and transfers the stored charge from the pixel capacitor to the data line, where it will be amplified and digitized off-array by a charge amplifier and subsequent readout circuitry. The readout cycle also resets the pixel capacitor node, as its voltage is set to the voltage connected to the positive terminal of the charge amplifier (virtual ground) before the transistor is turned off and the next integration cycle begins. This means that the two cycles can be repeated back-to-back because the PPS architecture has destructive readout, and the pixel capacitor node is reset while readout is done.

The PPS transistor operates in the linear region during readout to provide a low onresistance and quick charge transfer, and in the cutoff region during integration to provide a high off-resistance and allow for the accumulation of charge on the pixel capacitor. It should however be noted that there exists a leakage current through the channel of the transistor during integration while it is turned off, which can accumulate charge on the pixel capacitor and result in the presence of noise in addition to the signal integrated on the capacitor.

During readout, the pixel is discharged with a time constant  $\tau_{readout}$  which is the product of the capacitance of the pixel and the on-resistance of the transistor  $(R_{on})$ :

$$\tau_{readout} = R_{on} C_{nix}. \tag{4}$$

The on-resistance of a transistor operating in the linear region is provided by the following equation:

$$R_{on} = \left[\frac{W}{L} k' (V_{GS} - V_t)\right]^{-1},\tag{5}$$

where W is the width of the transistor, L is its channel length, k' is a process constant which is the multiple of the effective carrier mobility ( $\mu_{eff}$ ) and gate capacitance per unit area ( $C_G$ ) for a TFT or carrier mobility ( $\mu_n$ ) and gate oxide capacitance per unit area ( $C_{ox}$ ) for a CMOS transistor,  $V_t$  is the transistor's threshold voltage, and  $V_{GS}$  is the gate voltage applied to the transistor while it is turned on. Table 1 shows typical values for these constants as well as the resulting  $R_{on}$  and  $\tau_{readout}$  values for both amorphous silicon TFT technology and 0.18  $\mu$ m CMOS technology, for two identically sized transistors and a  $C_{pix}$  of 1 pF [2,3].

Table 1: Comparing readout time constants using typical process parameters for TFT and CMOS technology

|      | k'                    | $V_{GS}$ | $V_t$  | W/L          | $R_{on}$ | $	au_{readout}$ |

|------|-----------------------|----------|--------|--------------|----------|-----------------|

| TFT  | $12.5 \text{ nA/V}^2$ | 12 V     | 2 V    | 10 μm / 5 μm | 4 MΩ     | 4 ms            |

| CMOS | $387 \mu A/V^2$       | 1.8 V    | 0.48 V | 10 μm / 5 μm | 979 Ω    | 4.895 ns        |

Complete charge readout (99%) requires readout to last five times the time constant ( $5\tau_{readout}$ ), so it can be deduced that pixel readout time here using TFT technology would be 20 ms while it would be about 5 ns for CMOS technology, which is six orders of magnitude faster! The much lower on-resistance of CMOS technology is thus one of its advantages over TFT technology, as it directly results in a much higher frame rate to be realizable for imaging applications, which is a distinct advantage for real-time medical imaging applications like digital fluoroscopy [4].

#### 1.1.3 Active Pixel Sensor Architectures

To address the problems associated with the PPS architecture in terms of its susceptibility to noise, a great deal of research has been done into developing active pixel sensor (APS) architectures, which use additional transistors on the pixel to convert the signal integrated by the detector into a voltage or current at the output. While adding additional circuitry to the pixel decreases the area that is actually used to collect charge generated by the detector (i.e., the *active* area), the performance tradeoffs can be beneficial.

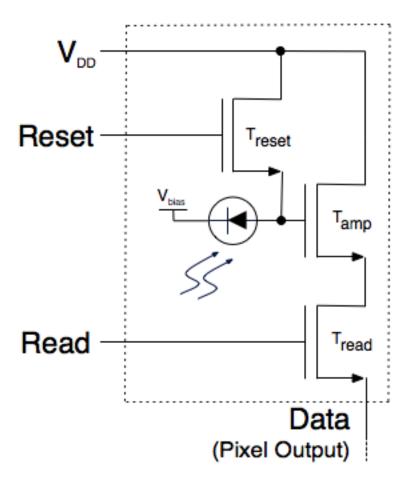

The most basic of the APS designs is the three-transistor (3T) current-mode structure shown in Figure 3, which introduces two additional transistors, one which acts as a source-follower amplifier to buffer the voltage accumulated on the detector node to be read out, and another to reset the detector node at the end of each integration cycle [5].

Figure 3: Three-transistor active pixel sensor architecture

The effective capacitance seen at the detector node of the APS structure is the detector's own capacitance in addition to the gate capacitance of the amplifying transistor ( $T_{amp}$ ), which stores the charge collected by the detector. The operation of the APS pixel is more complicated than the PPS pixel due to the need for an additional timing signal. The operation requires a reset cycle first, where the reset signal is asserted to turn on the reset transistor ( $T_{reset}$ ) and set the voltage at the detector node to the line voltage  $V_{DD}$ . This is followed by the integration cycle, where the reset signal is deasserted, and the incoming photons which generate current in the detector discharge the pixel capacitance by a  $\Delta Q$  in

charge proportional to the dose, which in turn lowers the voltage at the node by a  $\Delta V$  that is proportional to the radiation. Following integration, readout is done by asserting the read signal to turn on the read transistor ( $T_{read}$ ) and read out the current generated by the pixel through the source of the amplifying transistor to the data line, which is connected to a charge amplifier. The source-follower amplifier in the form of  $T_{amp}$  plays a key role in improving signal-to-noise ratio because it provides a charge gain while buffering the signal voltage at its gate to its source.

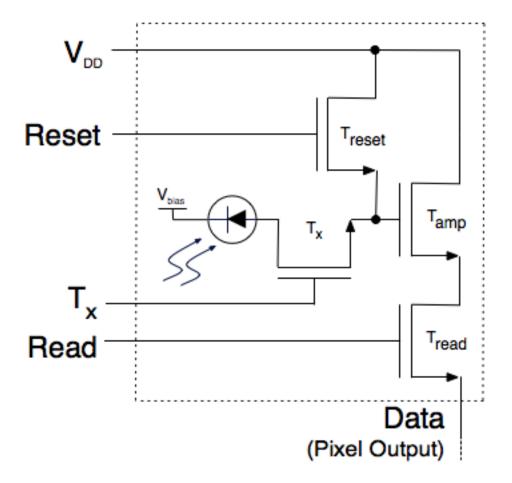

Though APS pixel architectures have shown very promising results, they have for the most part been fabricated and tested as single pixels in amorphous silicon TFT technology for the purposes of noise analysis and comparison of different architectures [6]. Due to their added complexity, it is difficult to fabricate reliable APS arrays and as such there are no commercialized flat panel arrays using APS technology, though as of 2010 there are now reports of results using fabricated APS prototype arrays in academic literature [7]. This is in stark contrast to the optical imaging field, where the PPS architecture has long since been replaced by the APS architecture, which has itself seen advancements. Since its introduction into the optical imaging field, CMOS technology has begun to surpass its competing technology, charge-coupled device (CCD), taking into account cost and performance. The forerunner of pixel architectures in CMOS digital cameras is the four-transistor (4T) APS architecture shown in Figure 4.

Figure 4: Four-transistor active pixel sensor architecture

The operation of the 4T APS architecture is very similar to the 3T architecture, but it has an additional timing signal which is associated with the additional transistor ( $T_x$ ). The addition of this transistor helps overcome some of the noise problems suffered by the 3T pixel [8]. By separating the detector node from the pixel node at the gate of  $T_{amp}$  via the  $T_x$  transistor, the architecture allows for on-pixel correlated double sampling (CDS). CDS eliminates deterministic sources of noise by sampling the signal twice – once before integration and once after – and subtracting the difference to get the true signal and eliminate the reset noise injected at the output. It also allows for the dynamic range/conversion gain

tradeoff to be addressed because the two are now independent of each other as a result of the separation of the detector node and the pixel node. Finally, the 4T pixel also eliminates the problem of kTC noise, a phenomenon which causes a random charge variation on a capacitor that is read out through a switch each time it is sampled. By turning on the  $T_x$  transistor as well as the read transistor while readout is done, the problem of sampling a capacitor after a switch is turned off is eliminated.

It is apparent that the medical imaging field would be better served by image sensors that go beyond the simple PPS structure and benefit from the very same ideas that have allowed CMOS APS image sensors to overtake traditional charge-coupled device (CCD) image sensors in cameras. The underlying factor that currently limits this evolution for medical imaging is the amorphous silicon TFT technology in which the large-area arrays are fabricated.

#### 1.2 Amorphous Selenium as an X-Ray Detector

Selenium is a substance that occurs naturally in the earth's crust, as well as being a byproduct of copper refining – meaning it is available in great abundance. The photoconducting properties of amorphous selenium have long been put to use by engineers and scientists – with its ability to be prepared in large areas, a-Se was found to be fruitful as a photoreceptor on the drums of photocopiers as early as the 1970s, which had black powder (toner) adhere to the parts of a surface that remained electrically charged after exposure to light [9]. Selenium's relatively high atomic number (indicating a good level of X-ray absorption) coupled with its photoconductivity made the detector also useful in large-area

xeroradiography, which is in simple terms the photocopying of body parts onto paper by using an X-ray source in place of xerography's light source.

The use of a-Se in both of these applications was doomed, however, for different reasons. In the case of the former, anthropogenic photoconductors of the organic form were found to be more economically advantageous for use as xerographic photoreceptors than a-Se, and as such xerographic photocopying lived on without the use of a selenium-based detector. In the case of the latter, though, the application itself was the root cause of failure, not a-Se and its photoconductive properties. Xeroradiography was simply too problematic due to the difficulties and noise associated with the toner-based method of developing the image [10]. But with the development of electronic readout mechanisms to capture digital images in the form of active matrix flat panel arrays in the 1990s, there was rekindled interest in a-Se as an X-ray detector for reasons that will be evident to the reader shortly.

#### 1.2.1 Operation of Radiation Detectors

There are various properties which are desirable in a radiation detector. A detector generates electron-hole pairs (EHP) when it is given a dose of radiation. The charge carriers of each type are then propelled to opposing electrodes via an electric field, thus creating a net flow of charge, or electric current, which can be stored on a capacitor. It is clear that the detector's sensitivity is directly proportional to the amount of EHPs generated per unit of radiation, which should be as high as possible. But equally as important as sensitivity is the detection efficiency — a high percentage of the incoming X-ray photons should be detected and converted. Further, it is imperative that there is minimal recombination of EHPs during transit through the detector and that the longest carrier transit time is not severely limiting to

the application. The detector should also have a very minimal amount of dark current, meaning when there is no exposure to X-ray radiation, carriers should not be generated and charge not be collected. Detectors are also desired to have a high spatial resolution [11]. Finally, there is a rather important constraint for the use of detectors with flat panels for medical imaging: It is preferable that the detector layer be able to be easily coated onto the panel rather than having to be individually bonded to pixels in the array.

Radiation detectors can generally be split into two categories: direct conversion detectors and indirect conversion detectors (or, simply, direct and indirect detectors).

#### 1.2.1.1 Indirect Radiation Detection

Indirect detectors are named as such because they inherently take an indirect process to convert X-ray radiation to electrical charge, by first using a scintillating screen to convert X-ray photons to photons (light), and then converting the generated light to charge by a photodetector. The scintillator's light intensity is proportional to the light intensity, so the charge is proportional to the X-ray radiation. Thus, the indirect process involves at least two layers of material. There are various implementations of indirect detectors; one such system prototyped by University of Michigan Medical Center researchers uses a thallium-doped cesium iodide (CsI:Tl) scintillator and a hydrogenated amorphous silicon (a-Si:H) p-i-n photodiode as an indirect detector [12].

This design uses, for the photodiode, a patterned n-layer per pixel and continuous iand p-layers across the array. The photodiode is followed by an indium tin oxide (ITO) metal layer. The CsI:Tl scintillator, grown separately, is then positioned in close contact with the flat panel array using a faceplate. The scintillator converts X-ray photons to light photons, which then shine on the photodiode to generate EHPs for charge transport. But the fact that the scintillator is placed on top of another rigid surface results in some inevitable air gaps due to non-uniformities, and possible optical coupling and lateral spread between pixels, lowering the spatial resolution of the detector as a result of this crosstalk. It is also apparent that purely from a fabrication and makeup perspective, this is a fairly convoluted solution to the problem of converting X-ray photons to charge when compared to a direct detector like a-Se, which is presented next.

#### 1.2.1.2 Direct Radiation Detection

Unlike indirect detectors, direct conversion detectors use a single layer to convert X-ray photons to electrical charge. This means that the radiation itself generates EHPs which are then propelled by an applied electric field across the detector. Direct detection materials usually have a high resistivity, leading to low dark currents, and are operated at large electric fields. In addition, direct detectors provide the highly desired property of good spatial resolution even at very low pitch pixel sizes, due to their inherent structure producing minimal lateral diffusion and producing high and well-defined electric fields.

Examples of materials that have the characteristics of a direct detector in response to X-rays include cadmium zinc telluride (CdZnTe), mercury iodide (HgI<sub>2</sub>), lead oxide (PbO), and amorphous selenium (a-Se). Table 2 shows a comparison of these materials, displaying typical values for the detectors' performance figures of merit, which include electric field operation, resistivity, and charge yield [11].

Table 2: A comparison of different direct radiation detectors' properties

| Property                                        | a-Se                                 | PbO                                  | $HgI_2$                              | CdZnTe               |

|-------------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|----------------------|

| Typical Operating<br>Electric Field [V/μm]      | 10 to 20                             | 5                                    | 1 to 2                               | 0.1                  |

| Resistivity [Ω-cm]                              | 10 <sup>14</sup> to 10 <sup>16</sup> | 10 <sup>12</sup> to 10 <sup>13</sup> | 10 <sup>12</sup> to 10 <sup>13</sup> | 3 × 10 <sup>10</sup> |

| Charge Yield [e <sup>-</sup> /keV of radiation] | 20 to 30                             | 60                                   | 100                                  | 200                  |

As shown, though it has a lower charge yield (also called conversion gain in literature) than the other detectors, a-Se has the highest resistivity, which makes it extremely appealing for low noise tolerance applications such as breast cancer imaging. This is in addition to the fact that a-Se can be vacuum evaporated and deposited as a uniform thick film in large areas over top of the readout electronics in flat panel imagers. Competing detectors are mired in difficulties that don't allow them to be mass-produced or used over a large area. CdZnTe, for example, which has a crystalline structure, suffers from an expensive and pooryield process and can only be grown in small sizes. These advantages have led to a-Se being the single prevalent direct detector of choice for commercial X-ray imaging.

# 1.3 Integration of CMOS and Selenium: Motivation for a Selenium-CMOS X-ray Sensor

The discussion so far leads to the conclusion that an imaging solution that integrates CMOS technology for the pixel architecture with amorphous selenium as an X-ray detector would have very promising results for the field of medical imaging. It would allow for pixel architectures such as the APS ones illustrated in this chapter to be fabricated at small pixel

sizes to allow for high-resolution images with fast readout and low noise susceptibility, taking advantage of the reliability and robustness of CMOS technology. Indeed, the purpose of this research is to take the first step towards a CMOS-based array integrated with a-Se serving as a high-performance imager for medical applications.

# Chapter 2

# Design and Implementation of Integrated Selenium-CMOS PPS Array

This chapter begins by illustrating the design and layout of the 8×8 array fabricated in 0.18 µm CMOS technology. It follows by detailing how the amorphous selenium X-ray detector was deposited on the chip after providing background on how the detectors are fabricated, as well as detailing the final integration steps taken to get the device ready to be tested.

#### 2.1 Design and Layout of CMOS 8×8 PPS Array

To show the feasibility of a CMOS readout array integrated with an a-Se detector, a CMOS chip had to be fabricated. The PPS architecture was chosen for the array due to its simplicity and to serve as a first step in showing that CMOS technology can be integrated with a-Se.

The chip was designed and laid out using Cadence Design Systems's electronic design automation software suite, commonly known as Cadence, and fabricated in the  $0.18\,\mu m$  process through CMC Microsystems, which is the de facto official manufacturer for silicon designs in academia in Canada. Based on the wafer space granted by CMC for this project, the  $8\times8$  array was chosen to have a  $40\,\mu m$  pixel pitch. The  $0.3\,m m$ -thick CMOS die would have an area of  $1.0\,m m\times2.8\,m m$ , which meant an  $8\times8$  array of  $40\,\mu m$  pixels could be nicely laid out at the top portion of the chip, leaving plenty of space for the bond pads.

Like any other large design, a bottom up process was used to create single cells that could then be instantiated repeatedly as part of the overall block. The array design began with the schematic and layout of a single PPS pixel. The screenshot of the Cadence schematic of the cell is shown in Figure 5.

Figure 5: Cadence schematic of a single PPS pixel cell

This block contains the PPS read transistor as well as the pixel capacitor, and has four pins: V\_G (the read line, connected to the gate of the PPS transistor), V\_S (the data line, connected to the source of the transistor), V\_D (the pixel detector node on top of which the detector will be placed), and GND, which is to be connected to ground in order to ensure proper operation of the NMOS transistor by grounding its substrate.

The layout of the single pixel cell is shown in Figure 6. The NMOS transistor was laid out in the bottom right corner of the pixel, with a channel width of 10 µm and a channel length of 5 µm. The drain contact of the transistor was connected to the top metal layer of the CMOS process, the *metal6* layer, which was made to exist over the entire active area of the pixel. This layer, which also made up the top electrode of the pixel capacitor (explained further below), was exposed by forgoing the top layer protective oxide over this area, to allow for the a-Se detector to be deposited on top of it and accumulate charge on the node.

Figure 6: Layout of a single CMOS PPS pixel. A closeup of the PPS transistor in the bottom right corner of the pixel is shown on the right.

The shaded gray area in Figure 6 represents the area for which the *metal6* layer of the CMOS process was exposed, which also represents the actual *active* area of the pixel which collects charge generated by photons striking the detector. Thus, the Fill Factor of the pixel, which quantifies the active area of the pixel in proportion to its total area, can be calculated by the following expression:

$$Fill \ Factor (\%) = \frac{Active \ Pixel \ Area}{Total \ Pixel \ Area} \times 100. \tag{6}$$

The total pixel area was  $1600\,\mu\text{m}^2$ , while the active pixel area was  $1585.7\,\mu\text{m}^2$ , since a small portion of the pixel area had to be used for the layout of the PPS transistor. This led to a pixel *Fill Factor* of 99.1%.

The pixel capacitor was made using the CTM layer of the CMOS process, with the area being 30 µm × 30 µm. The CTM layer is a special layer exclusively meant for making MIM (Metal-Insulator-Metal) capacitors integrated in the CMOS process. The CTM layer was connected to the *metal6* layer by placing several vias in an array throughout the 30 µm x 30 µm area, while the *metal5* layer was laid out over the entire pixel area. From here, the *metal4*, *metal3*, *metal2*, and *metal1* layers were only laid out around the perimeter of the pixel, as guard rings, and connected to each layer above through vias, meaning *metal5* was connected down to *metal1*. The *metal1* layer was then routed on the right side to the pixel's ground pin, causing the pixel capacitor to exist between the CTM layer and the *metal5* layer (ground) through the interlayer dielectric separating the two. Figure 7 shows a cross section of a pixel (not to scale) to illustrate how the capacitor was formed between the top electrode and ground. The vias are illustrated by the dark gray oblong vertical sections in between adjacent layers.

Figure 7: Cross-section illustration of a pixel on the CMOS die showing  $C_{pix}$  implemented as an integrated MIM capacitor between the top electrode and ground.

The pixel capacitor was desired to have a value of 1 pF. The capacitance of the pixel capacitor can be calculated by the following formula:

$$C_{pix} = \frac{\varepsilon_0 \varepsilon_{IMD5a} A_{CTM}}{d_{M5-CTM}},\tag{7}$$

where  $\varepsilon_0 = 8.85 \times 10^{-12}$  F/m,  $\varepsilon_{IMD5a}$  (3.7) is the dielectric constant of the inter-metal dielectric separating the *metal5* and CTM layers,  $A_{CTM}$  is the area of the top electrode of the capacitor (900 µm<sup>2</sup>), and  $d_{M5-CTM}$  is the distance separating the two layers (30 nm) [13]. This resulted in an expected capacitance value of 982.35 fF. Following parasitic extraction of the layout view of the pixel cell in Cadence, the capacitance was given to be 951.75 fF.

The single PPS cell was then instantiated 64 times, in eight rows and eight columns to form the 8×8 array. The V\_G nodes of every cell in a row were connected to each other while the V\_S nodes of every cell in a row were connected to each other, such that the array had eight *read* line inputs – V\_G1 through V\_G8 – and eight *data* line outputs – V\_S1 through V\_S8. The array also had 64 V\_D inputs, which would be where each pixel

accumulates charge on its pixel capacitor at the drain of the PPS transistor and corresponding to each individual cell's V\_D pin. Figure 8 shows the arrangement of the 8×8 array's interconnections. This figure was drawn using schematic software as opposed to taking a screenshot in Cadence, which would not have been legible due to the amount of detail involved. Note that the V\_D pins for each cell have been omitted as each pixel had its own, and the GND pins, which are common connected for all 64 pixels, have also been omitted.

Figure 8: 8×8 PPS array interconnections

The layout of the array was made by instantiating the layout of the single PPS cell 64 times and interconnecting the pins in the same way as was done for the schematic cell. This made up the array cell in the bottom up design approach of the array. The last step was to instantiate this cell in the top level layout, which required bond pads for the input and output pins, and which was required to meet CMC's design rule constraints (DRC) which place minimum and maximum constraints on the density of each layer for proper mask fabrication. Figure 9 shows the top-level layout of the chip with and without the expanded sub-cell views.

Figure 9: Full layout of PPS chip in Cadence; with expanded sub-cells (right)

The chip required 18 bond pads to be placed around the perimeter of the lower half of the chip, comprising of the eight read lines, eight data lines, and two additional ground bond pads. The *metal1* layer was used for routing the read lines (the gate nodes) to the left side of the chip and the *metal2* layer was used for routing the data lines (the source nodes) to the right side of the chip. The first bond pad on the left side of the chip was connected to the guard ring that was placed around the array area as well as the ground pins of the PPS array, which were connected to the capacitor's bottom electrode and the substrate contacts of the transistors as described earlier and shown in Figure 7.

This was followed around the perimeter by the eight read lines V\_G1 through V\_G8. A number of metal fills had to be placed in each layer to meet DRC, all of which were connected to the next bond pad, which was to be grounded. This made up a significant portion of the area in the middle of the chip, as seen by the large rectangular boxes comprising of the metal fill cells in the un-flattened cell view in Figure 9 (M3, M5, etc). The remaining eight bond pads were used for the eight data lines V\_S1 through VS\_8, which were organized with V S8 on the bottom and V S1 at the top.

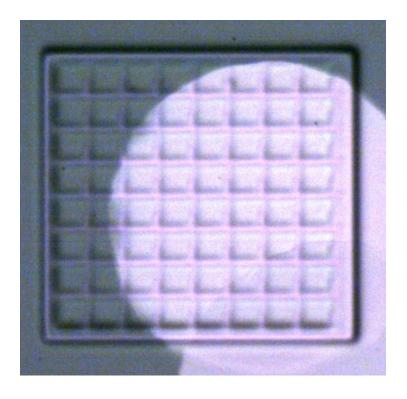

Figure 10 is a die micrograph of the chip fabricated by CMC, taken under a high-magnification microscope at the University of Waterloo Giga-to-Nanoelectronics Lab.

Figure 10: Micrograph of the 0.18  $\mu m$  CMOS PPS die fabricated through CMC

# 2.2 Amorphous Selenium: Structure, Fabrication, and Integration with PPS Chip

Amorphous selenium is deposited as a film onto a substrate using vacuum evaporation. When it is struck by X-ray photons, electron-hole pairs (EHPs) are generated inside its structure, which can then be separated via an electric field to generate photocurrent. The following section describes in detail the structure of amorphous selenium, how it is prepared for the vacuum evaporation process, and its integration with the CMOS PPS chip in order to allow for testing of the 8×8 array.

#### 2.2.1 The Structure of a-Se as an X-ray Detector

Amorphous selenium's structure contains under- and over-coordinated charged defects called valence alteration pairs (VAPs), which cause its amorphous nature. These VAPs are illustrated in Figure 11 below.

Figure 11: The structure of an amorphous selenium (a-Se) chain, showing its charge defects and amorphous nature (adapted from [14])

The under-coordinated charged defects correspond to a singly bonded negatively charged centre (Se<sub>1</sub><sup>-</sup>) and the over-coordinated charged defects correspond to a triply bonded positively charged centre (Se<sub>3</sub><sup>+</sup>). These VAPs are present in the absence of dangling bonds and contribute to the optoelectronic properties of a-Se. This is why selenium only maintains its photodetective properties in its amorphous state, and not its crystalline state. Unfortunately, the structure of a-Se, left to itself without encapsulation, is prone to crystallization over time (ranging from months to years based on ambient conditions), causing its performance as a detector to degrade until it loses its photogenerative properties completely [14].

Extensive research has been done in the study of alloying a-Se to prevent this unwanted crystallization, while also improving its charge transport characteristics to prevent trapping of the generated EHPs (thus increasing carrier lifetime) [15]. It has since become established that alloying a-Se with a small amount of arsenic (As) in the range of a few tenths of a percent, and doping it with a few parts per million (a microscopic amount) of a halogen like chlorine (Cl) combine to give the desired performance from the detector. The As and Cl in the specified amounts alter the structure of a-Se to provide the correct balance of VAP charge defects to result in good carrier transport and increased consistency to prevent crystallization. The a-Se structure that is used in flat-panel detectors is referred to as stabilized a-Se and contains 0.2% to 0.5% As doped with 10 to 40 parts per million Cl [14]. The alloying of selenium with these impurities has to be done prior to vacuum evaporation to form solid, stabilized selenium pellets which can then be evaporated and deposited.

### 2.2.2 Deposition via Vacuum Evaporation

Vacuum evaporation involves heating an evaporant in a vacuum by employing a large current through a container in which it is placed. For the fabrication of amorphous selenium detectors, the evaporant comes in the form of alloyed a-Se pellets which have been refined and alloyed to the desired composition. There are vendors that specialize in making these alloyed a-Se pellets with different compositions to suit their customers' needs. The process of making these a-Se pellets begins with the purification and refinement of selenium, the horizontal zone refining method [16]. A quantity of solid selenium is melted into a continuous solid mass to be vacuum distilled. This is done in a vacuum with the material being heated to over 100°C in order to remove residue water vapour and organic contaminants. The selenium is then melted into an oblong ingot (a metal mold) at a temperature of about 250°C for two hours and stretched over a foot in length, which is then cropped by removing the impure ends mechanically, leaving the purified selenium ready for use in the synthesis of the alloyed a-Se.

The refined selenium is placed with previously synthesized Se-As and Se-Cl alloys and mixed thoroughly within an alloying reactor, which is heated in a controlled manner to well above the melting point of selenium. The melt is homogenized by a rapidly rotating impeller, and then slightly cooled, though still remaining above 300°C. Shotting is then performed on the melt on a cold shotter plate (kept at a few degrees Celcius). This quenches the melt due to the rapid decrease in temperature, which allows it to form an amorphous structure. This produces the alloyed a-Se pellets, which can now be used in the vacuum evaporation deposition process.

Vacuum evaporation converts the solid a-Se pellets from their condensed state to their vaporous phase to be deposited as a film on top of the target surface. This method of depositing a-Se as a thick film using conventional thermal evaporation in a vacuum coater has been used extensively to fabricate a-Se since the 1960s, when it was the photoreceptor of choice in photocopiers [17]. The deposition of a-Se onto flat-panel thin-film transistor flat-panel arrays is done in the same basic way, and in industry, large vacuum reactors are used to coat multiple panels at the same time, making the process highly efficient. Figure 12 below shows the process that takes place inside such a vacuum chamber.

Figure 12: Amorphous selenium is evaporated and deposited as a film on the target substrate, the flat panel imager.

The chamber is kept at a pressure of 10<sup>-6</sup> torr during this process. Alloyed a-Se pellets are placed into a stainless steel boat which is resistively heated by having current driven through it. The boat is heated to upwards of 250°C while the deposition surface is maintained

at about 60°C to 65°C. The latter condition must be maintained to allow the selenium vapour to form a film, since its glass transition temperature is about 55°C. The vapour from the evaporation of the pellets settles onto the panel acting as the substrate for deposition, forming the a-Se X-ray detecting layer. With the evaporation temperature of a-Se being relatively low at about 230°C, the flat-panel array is not damaged, and furthermore, the process is over with rather quickly, as deposition rates are on the order of 2 µm to 4 µm per minute. This means that a 200µm film can be coated in under an hour. This is one of the advantages of a-Se as an X-ray detector – panels can be manufactured separately and/or independently and then sent for a-Se deposition. While a-Se is not the only photodetector that can be deposited in this manner, other semiconductors often result in polycrystalline films and require high-temperature annealing to eliminate defects.

### 2.2.2.1 Potential Issues during Deposition

It should be noted that this process is not without its problems. During the evaporation and deposition process, changes take place in the vapour as well as the film composition as the material is continuously evaporated from the boat. Temperature non-uniformities in the boat, finite material thermal conductivity, and limited diffusion in the source material all contribute to a detrimental effect in the deposition called fractionation [14]. Fractionation refers to the fact that the concentration of As is higher at the surface of the photoconductor film than the rest instead of being uniform throughout.

This fractionation effect has been examined and qualitatively explained [18,19]. The source material becomes inhomogeneous as the selenium-rich initial vapour leaves its surface region, leaving behind a surface rich in As. Methods to minimize this effect have also been

proposed through trial and error, with one study showing that when the initial source material (the a-Se pellets) has its surface crystallized by vigorous tumbling, the effects of As fractionation are severely reduced. The fractionation of Cl, however, is not practical to investigate since the concentration is so small, and no studies have been done to directly investigate the doping profile of Cl in the grown a-Se film.

## 2.2.3 Integration of a-Se Detector with CMOS PPS Array

The fabrication of the a-Se detector on top of the CMOS PPS chips was done at the Electronic Materials and Devices Research Centre at the University of Saskatchewan. The deposition of the a-Se detector was done in two layers. The composition of the alloyed selenium used for the first layer of evaporation was 0.3% As and 2.5 ppm Cl, known to be a very stable composition with good charge transport properties. The substrate temperature was kept at 60°C while the boat temperature for evaporating the alloy was 295°C. Deposition was done for 22 minutes to deposit a layer of a-Se from this alloy that was 67 μm to 68 μm thick. The second layer used a slightly different alloy composition, at 2% As and doped with an Alkali metal as opposed to Cl. This alloy was evaporated for four minutes while the substrate was kept at 60°C and the boat was kept at 310°C, resulting in a layer of about 8 μm to 9 μm being deposited on top of the previous layer. This gave a total thickness for the a-Se detector of about 75 μm. The use of the higher As-rich alloy for the much thinner top layer trades off charge transport in exchange for higher resistivity at the surface, which keeps the leakage current of the a-Se detector low.

Masks had to prepared to ensure that a-Se was not deposited on the entire chip, as only the active array area was the target, and the lower portion of the chip needed to be left

exposed so that the bond pads connected to the read and data lines of the PPS array could be accessed for wirebonding. Additionally, a secondary mask was required to place the  $4\,\mu m$  to  $5\,\mu m$  thin, transparent chromium (Cr) contact on top of the a-Se film, to allow for an electric field bias voltage to be applied on the detector. This mask had to ensure that the electric field was not applied on the entire a-Se surface, as around the edges the thickness of the film was less than  $75\,\mu m$ , which could result in the breakdown of the detector. A mask with a circular opening diameter roughly equal to the array area was used and positioned on top of the array as the Cr contact was deposited over top of the active array surface in a metal evaporator. Figure 13 is a high-resolution micrograph of the sample's active area after the a-Se detector was deposited on the CMOS chip and returned from Saskatchewan.

Figure 13: Amorphous selenium on top of the 8×8 active array area. The lighter circular area is the chromium top contact used to apply the electric field bias.

#### 2.2.3.1 Post-Deposition Preparation

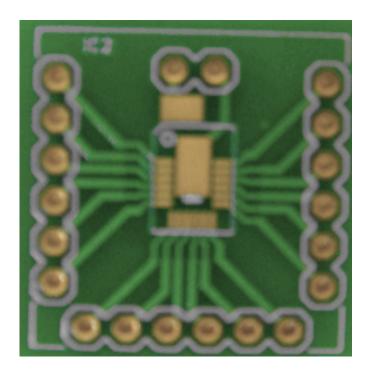

Now that the a-Se detector had been coated onto the chip, it had to be placed on a specially designed printed circuit board (PCB) substrate, or daughterboard, such that it could be held in place while being wirebonded and to allow for easy integration with the testing environment. The daughterboard is shown in Figure 14 below, designed and fabricated alongside the test PCB which will be described in Chapter 3. The pads around the edges of the large pad at the centre correspond to the bond pads on the chip, which comprise the read and data lines of the passive pixel sensor array.

Figure 14: PCB substrate (daughterboard) used to hold the CMOS image sensor.

The contacts on the daughterboard were coated with gold to ensure minimal contact resistance and good adhesion for wirebonding. The large pad at the centre of the daughterboard is the cavity, where the die was placed. To affix the die to the daughterboard,

an epoxy was required which was conductive (to ground the bottom surface, the body of the die) and could cure at room temperature (since a-Se can crystallize at temperatures as low as 45°C). The solution used was Colloidal Silver Paste made by PELCO, which provides high adhesion while being electrically conductive and curable at room temperature. A small drop of the silver paste was placed using a syringe needle tip in the middle of the cavity and allowed to settle as the die was placed on top of it. The paste was given 24 hours to cure at room temperature, per the manufacturer's instructions.

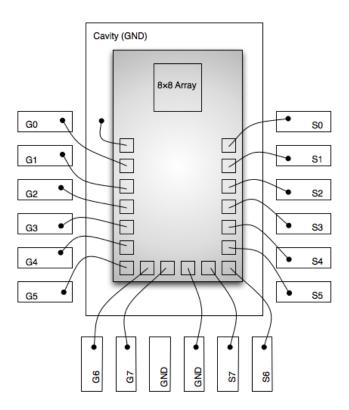

Once the die was confirmed to have been solidly attached to the daughterboard, it was ready for wirebonding, which was done in the Giga-to-Nanoelectronics Lab at the University of Waterloo. Figure 15 shows the wirebonding diagram used (not to scale).

Figure 15: Wirebonding diagram used for connecting bond pads to the daughterboard

The pads labeled G0 through G7 are the eight read lines of the array connected to the PPS gates (V\_G1 to V\_G8) which need to be asserted for readout, and the pads labeled S0 through S7 are the eight data lines of the array connected to the PPS sources (V\_S1 to V\_S8), which will be connected to the charge amplifiers externally. The remaining two wirebonds are used to ground the metal guard ring around the array and the substrate contacts (bonded to the grounded cavity) and the metal fills on the chip (bonded to the ground pad at the bottom).

Next, the pad above the cavity had to be connected to the top contact of the a-Se layer on the chip so that a high-voltage contact could be made to bias the detector during operation. This was an intricate process and took several different attempts before an optimal solution was reached. The material used to make the contact could not be too thick or it would block the active area of the array, and once it was placed on top of the array, it had to stay there without drifting from its place or being lifted off the contact.

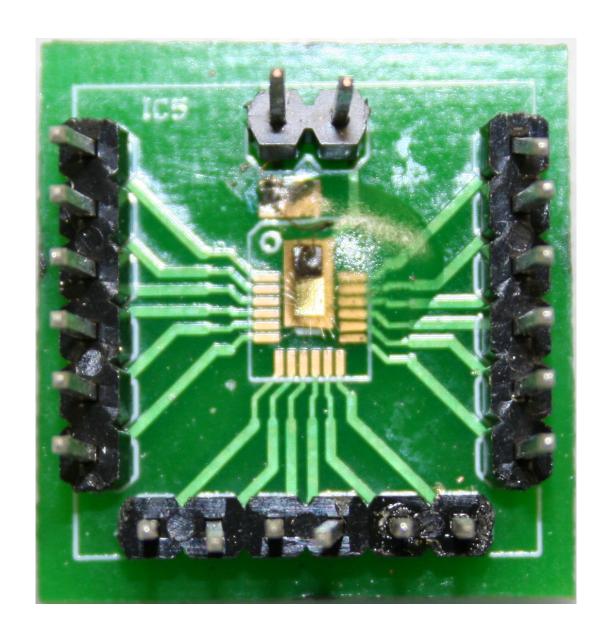

To accomplish this, a single strand of a solder wick strip was soldered to the daughterboard pad, while the other end was carefully placed on top of the Cr contact using tweezers under a microscope. To ensure it stayed properly in place, a drop of a transparent, non-conductive Lepage epoxy made by mixing a drop of the epoxy's resin and hardener was put on the sample. This encapsulated the top contact wire as well as the wirebonds, effectively protecting the entire sample. Finally, single-strip header pins were soldered to the daughterboard's output connection vias to allow for easy probing of the pins during testing. Figure 16 shows the CMOS chip wirebonded to the daughterboard and encapsulated with the transparent epoxy, ready to be tested.

Figure 16: CMOS PPS chip wirebonded to daughterboard and encapsulated in protective non-conductive transparent epoxy

## Chapter 3

## **Design and Assembly of PPS**

## **Readout Printed Circuit Board**

A printed circuit board (PCB) was designed and fabricated in order to allow for the driving stimulus for the PPS array and to capture its output with readout circuitry. This chapter outlines the parts used in the design and how they were integrated together on the PCB. CadSoft's EAGLE software was used for the schematic design and board layout.

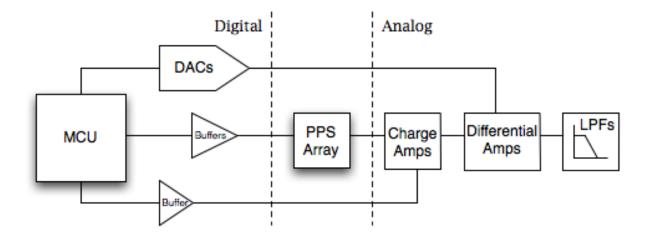

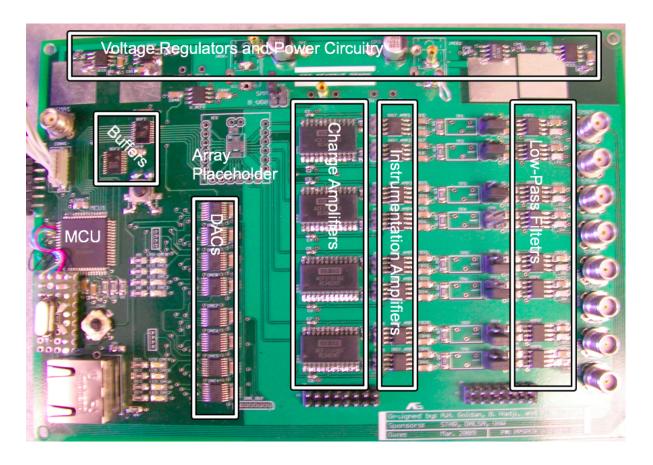

The design process involved outlining the requirements of the test system, selecting the components that were required and creating an EAGLE library to use them, and, following schematic entry, doing the PCB layout and sending it to fabrication. The design used surface mount (SMD) components almost exclusively to allow for a clean and compact layout. Figure 17 shows a generalized top-level block diagram of the PCB to illustrate the major components and how they interact with each other.

Figure 17: Block diagram of the PCB used for testing the PPS array.

## 3.1 Voltage Regulators

The operation of chips on the PCB requires the existence of DC voltage sources, implemented by voltage regulators which take a DC input voltage and regulate it at the required supply voltage. Digital parts on the PCB required positive voltages of 1.8 V and 5 V, while analog parts required differential voltages of +/-5 V to allow for signals to swing above and below zero volts. Thus, a DC input to the board of +/-9 V would suffice to allow for the required voltages, utilizing large decoupling capacitors of 220 µF.

Mixed-signal design convention calls for separating analog and digital power supplies and ground planes to isolate noise, current draws, and other crosstalk between the devices. Hence, four voltage regulators were required to generate 1.8 V, 5 V (digital), 5 V (analog), and -5 V. The former two were connected to a digital ground plane which was separated from the analog ground plane serving the latter two. The digital and analog ground planes would

be used for the parts requiring each respective type of power in conjunction with their voltage rail.

## 3.1.1 5 V Regulator

Since the PCB required 5 V to be generated twice, two instances of the same part could be placed on the board to generate the digital and analog 5 V rails separately. The part chosen was the ADP3303 in the 8-pin surface mount SOIC package, made by Analog Devices, which provides a stable output of +5 V (+/-0.8%) for input ranges 3.2 V to 12 V. A decoupling capacitor of  $0.7\,\mu\text{F}$  was used at the 5 V output to keep the voltage stable.

## 3.1.2 1.8 V Regulator

The  $1.8\,V$  supply was required for several of the digital parts. The part used was Texas Instruments's TPS766 in the 8-pin surface mount SOIC package, which provides a stable output of  $+1.8\,V$  for input ranges  $3.3\,V$  to  $10\,V$ . A decoupling capacitor of  $0.7\,\mu F$  was used to ensure output voltage stability.

## 3.1.3 -5 V Regulator

While negative voltage regulators are rarer in existence than their positive counterparts, Linear Technology's LT1175 in the 8-pin surface mount SOIC package was eventually chosen as the solution for providing a -5 V rail for the dual-supply analog parts on the PCB. A decoupling cap of  $0.7 \,\mu\text{F}$  was placed between its output and ground (with the positive electrode connected to the ground plane).

#### 3.2 Microcontroller

At the heart of the digital side of the PCB is a microcontroller, which governs the operation of the chip by providing the input signals. The microcontroller chosen was the MC68HC908MR32, part of the M68HC08 family of microcontrollers made by Freescale Semiconductor, in the 64-pin QFP package. The microcontroller (MCU) uses an 8 MHz system clock, two separate timer modules comprising of six channels together, and a serial-peripheral interface (SPI) module for easy interfacing. It uses the digital 5 V power supply.

The software running on the MCU was written in assembly using a laptop running the Metroworks CodeWarrior software development kit. Interfacing from the laptop to the MCU on the board was done using the FSICEBASE support board, which connects to the laptop via USB and to the PCB through a 6-pin programming cable. This allowed for assembly code to be written, compiled, and programmed onto the MCU's programmable read-only memory (PROM) for standalone operation, as well as real-time step through debugging while connected to the laptop through the FSICEBASE.

#### 3.3 Buffers

Two buffering chips were used in between the MCU and the targets it was used to drive. The buffers were necessary to protect the MCU from sinking too much current through its output pins. The buffers would also allow for shifting of the high logic level from the MCU's 5V level to the PPS array's 1.8V level.

#### 3.3.1 1.8 V Gate Driver Buffer

The PPS array was fabricated using 0.18 µm CMOS technology, for which the high logic level is 1.8 V. As such, the stimulus signals – the read lines connected to the gates of the PPS transistors in the array – needed to be shifted down to 1.8 V logic from 5 V logic, which the MCU uses. This was done via Toshiba's TC74LCX541 chip containing eight buffers in a 20-pin TSSOP package, which used the 1.8 V digital power rail. All eight buffers were used to convert the eight read signals to 1.8 V logic, which could then be connected to the array safely.

## 3.3.2 5 V Reset Signal Buffer

The other stimulus signal the MCU was responsible for outputting was the Reset signal to the charge amplifiers on the analog readout side, which had to be done after each integration cycle to reset their output level. This signal was buffered using Toshiba's TC74VHC541 chip containing eight buffers in a 20-pin TSSOP package, which used the 5 V digital power rail, one of which was used to buffer the reset signal.

#### 3.4 Digital-to-Analog Converters