# Post-mapping topology rewriting for FPGA area minimization

by

Lei Chen

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2009

© Lei Chen 2009

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Circuit designers require Computer-Aided Design (CAD) tools when compiling designs into Field Programmable Gate Arrays (FPGAs) in order to achieve high quality results due to the complexity of the compilation tasks involved. Technology mapping is one critical step in the FPGA CAD flow. The final mapping result has significant impact on the subsequent steps of clustering, placement and routing, for the objectives of delay, area and power dissipation. While depth-optimal FPGA technology mapping can be solved in polynomial time, area minimization has proven to be NP-hard.

Most modern state-of-the-art FPGA technology mappers are structural in nature; they are based on cut enumeration and use various heuristics to yield depth and area minimized solutions. However, the results produced by structural technology mappers rely strongly on the structure of the input netlists. Hence, it is common to apply additional heuristics after technology mapping to further optimize area and reduce the amount of structural bias while not harming depth. Recently, SAT-based Boolean matching has been used for post-mapping area minimization. However, SAT-based matching is computationally complex and too time consuming in practice.

This thesis proposes an alternative Boolean matching approach based on NPN equivalence. Using a library of pre-computed topologies, the matching problem becomes as simple as performing NPN encoding followed by a hash lookup which is very efficient. In conjunction with Ashenhurst decomposition, the NPN-based Boolean matching is allowed to handle up to 10-input Boolean functions. When applied to a large set of designs, the proposed algorithm yields, on average, more than 3% reduction in circuit area without harming circuit depth. The priori generation of a library of topologies can be difficult; the potential difficulty in generating a library of topologies represents one limitation of the proposed algorithm.

#### Acknowledgements

I would like to thank Prof. Andrew Kennings for supervising this work and for giving me the chance to step into the EDA industry. Without all the help he gave me, this thesis would not have come into existence. I would also like to thank my family and friends for their support over these years.

# Contents

|          |      | of Tables                           |    |  |

|----------|------|-------------------------------------|----|--|

|          |      | of Figures                          |    |  |

| 1        | Arc  | hitecture and CAD for FPGAs         | 1  |  |

|          | 1.1  | Introduction                        | 1  |  |

|          | 1.2  | FPGA Architecture Overview          | 2  |  |

|          |      | 1.2.1 LUT-based FPGAs               | 3  |  |

|          | 1.3  | FPGA CAD Flow                       | 5  |  |

|          |      | 1.3.1 High-level Synthesis          | 7  |  |

|          |      | 1.3.2 Logic Synthesis               | 7  |  |

|          |      | 1.3.3 Clustering                    | 9  |  |

|          |      | 1.3.4 Placement and Routing         | 9  |  |

|          | 1.4  | Contributions of the Thesis         | 10 |  |

|          | 1.5  | Summary                             | 10 |  |

| <b>2</b> | Tecl | hnology Mapping for LUT-based FPGAs | 12 |  |

|          | 2.1  | Background                          | 13 |  |

|          | 2.2  | Cut Enumeration                     | 14 |  |

|          | 2.3  | Timing Analysis                     | 16 |  |

|          | 2.4  | Practical Technology Mapping        | 17 |  |

|          | 0.5  | C                                   | 20 |  |

| 3            | SA                                        | Γ-Based Boolean Matching             | 21        |

|--------------|-------------------------------------------|--------------------------------------|-----------|

|              | 3.1                                       | Boolean Matching                     | 21        |

|              | 3.2                                       | Post-Technology Mapping Optimization | 25        |

|              | 3.3                                       | Summary                              | 26        |

| 4            | NP                                        | N-based Boolean Matching             | 27        |

|              | 4.1                                       | Matching Via Hash Table Lookups      | 28        |

|              | 4.2                                       | NPN Equivalence                      | 30        |

|              | 4.3                                       | Essential Bits                       | 32        |

|              | 4.4                                       | Practical Bits                       | 36        |

|              | 4.5                                       | Numerical Results                    | 38        |

|              | 4.6                                       | Functional Decomposition             | 40        |

|              | 4.7                                       | Summary                              | 44        |

| 5            | NPN-based Post-mapping Topology Rewriting |                                      |           |

|              | 5.1                                       | Top-level Rewriting Algorithm        | 46        |

|              | 5.2                                       | Revised Cut Computation              | 49        |

|              | 5.3                                       | Numerical Results                    | 52        |

|              | 5.4                                       | Summary                              | 53        |

| 6            | Cor                                       | nclusions and Future Work            | <b>55</b> |

|              | 6.1                                       | Conclusions                          | 55        |

|              | 6.2                                       | Future Work                          | 56        |

| $\mathbf{A}$ | PPE                                       | NDICES                               | 58        |

| $\mathbf{A}$ | Glo                                       | ssary of Terms                       | 59        |

| В            | List                                      | of LUT Topologies                    | 60        |

| Bi           | bliog                                     | graphy                               | 68        |

# List of Tables

| 4.1 | The number of practical bits of 3-input LUTs             | 37 |

|-----|----------------------------------------------------------|----|

| 4.2 | The number of practical bits of 4-input LUTs             | 37 |

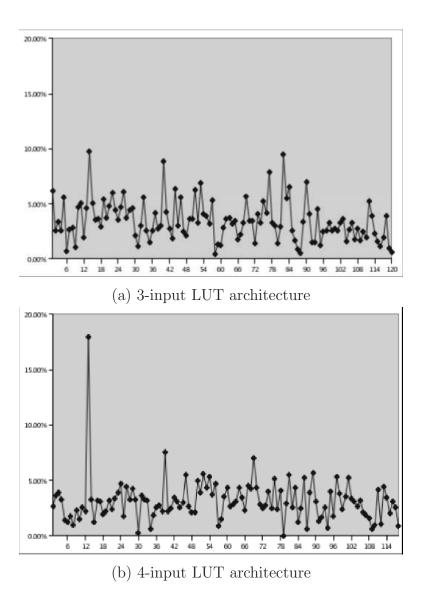

| 4.3 | Numerical Results for Topologies of 3-input LUTs         | 39 |

| 4.4 | Numerical Results for Topologies of 4-input LUTs         | 39 |

| 4.5 | Number of $k$ -input topologies with different structure | 40 |

| 4.6 | A list of decompositions for $k$ -input logic functions  | 44 |

| 5.1 | Experiment result of post-mapping topology rewriting     | 53 |

# List of Figures

| 1.1 | Modern FPGA architecture                                             | 3  |

|-----|----------------------------------------------------------------------|----|

| 1.2 | Simplified FPGA architecture                                         | 4  |

| 1.3 | Simplified configurable logic block                                  | 5  |

| 1.4 | Simplified basic logic element                                       | 6  |

| 1.5 | A lookup table                                                       | 6  |

| 1.6 | Simplified FPGA routing architecture                                 | 7  |

| 1.7 | Typical FPGA CAD flow                                                | 8  |

| 2.1 | Illustration of cut enumeration                                      | 15 |

| 2.2 | The typical FPGA technology mapping flow                             | 18 |

| 2.3 | Pseudocode for area recovery mapping procedure                       | 19 |

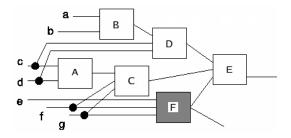

| 3.1 | Boolean matching example                                             | 22 |

| 3.2 | SAT-based matching example                                           | 23 |

| 3.3 | Using matching to reduce area                                        | 25 |

| 4.1 | Topology simulation                                                  | 29 |

| 4.2 | Topology simulation with encoding                                    | 31 |

| 4.3 | Equivalent topologies with complementation                           | 33 |

| 4.4 | Equivalent topologies with permutation                               | 34 |

| 4.5 | A 6-input topology of LUTs with bridged input pins                   | 35 |

| 4.6 | Topology simulation with encoding using essential bits               | 36 |

| 4.7 | Topology simulation with encoding using essential and practical bits | 38 |

| 4.8 | Ashenhurst decomposition                                             | 42 |

| 4.9  | Functional decomposition of a 9-input Boolean function | 43 |

|------|--------------------------------------------------------|----|

| 4.10 | Seven missed 8-input topologies of 4-input LUTs        | 45 |

| 5.1  | Top-level rewriting algorithm                          | 48 |

| 5.2  | Topology selection for rewriting                       | 49 |

| 5.3  | Cut computation for topology rewriting                 | 50 |

| 5.4  | Cut expansion                                          | 51 |

| 5.5  | An example of cut weight calculation                   | 52 |

| 5.6  | Experiment result of post-mapping topology rewriting   | 54 |

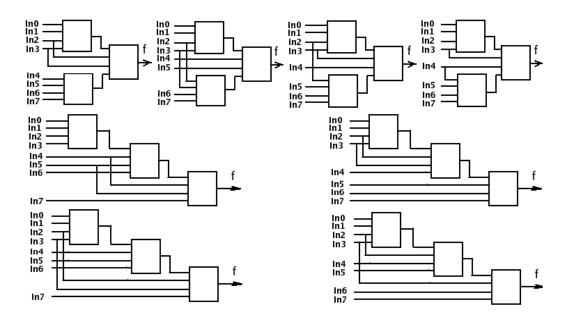

| В.1  | 5-input topologies of 3-input LUTs                     | 60 |

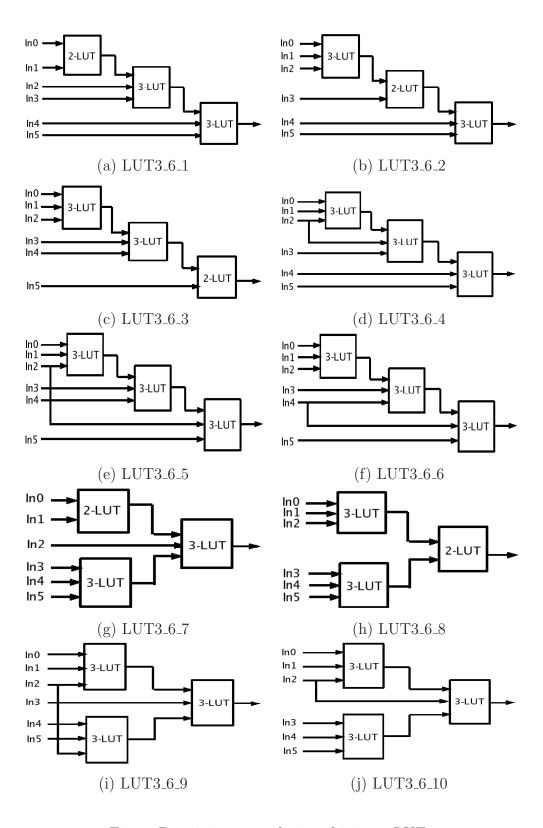

| B.2  | 6-input topologies of 3-input LUTs                     | 61 |

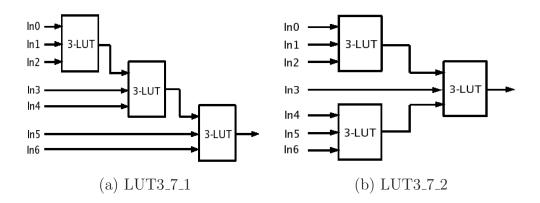

| В.3  | 7-input topologies of 3-input LUTs                     | 62 |

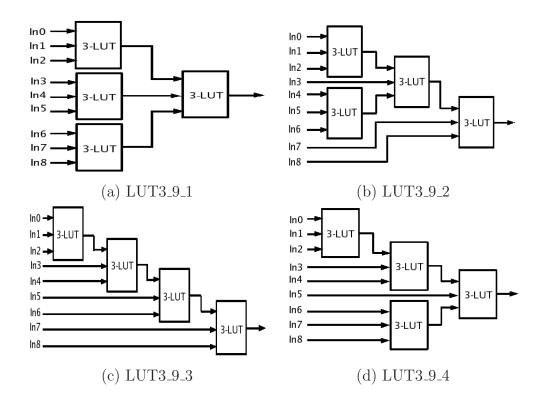

| B.4  | 9-input topologies of 3-input LUTs                     | 62 |

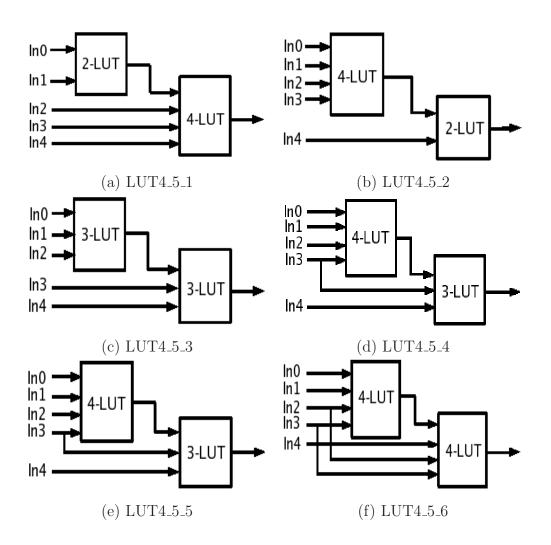

| B.5  | 5-input topologies of 4-input LUTs                     | 63 |

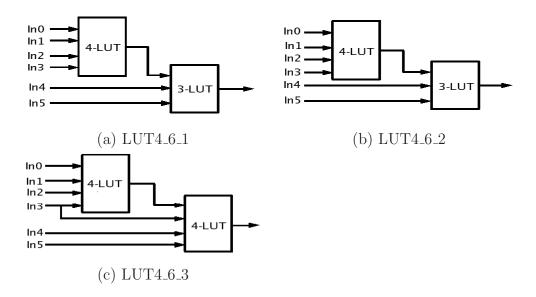

| B.6  | 6-input topologies of 4-input LUTs                     | 64 |

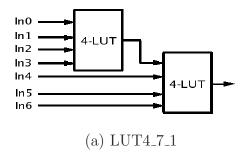

| B.7  | 7-input topologies of 4-input LUTs                     | 64 |

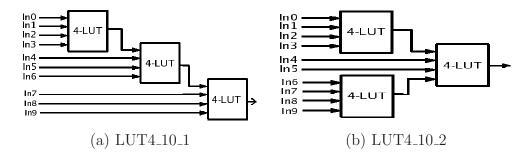

| R 8  | 10-input topologies of 4-input LUTs                    | հ4 |

# Chapter 1

### Architecture and CAD for FPGAs

#### 1.1 Introduction

Application-Specific Integrated Circuits (ASICs) and Field Programmable Gate Arrays (FPGAs) are two primary platforms for integrated circuit design. FPGAs are programmable semiconductor fabric that are based on an array of prebuilt Configurable Logic Blocks (CLBs) and programmable interconnects. As opposed to ASICs which are built and customized for one particular design, FPGAs can be programmed to the desired application. Although one-time programmable FPGAs are available, the dominate types are those that can be reprogrammed a large number of times as the design evolves.

FGPAs and ASICs have different value propositions, and the following are the pros and cons of each platform. First, the ASIC is fixed once manufactured, whereas the FPGA is completely reconfigurable. The reconfigurability of the FPGA allows easy modification of its application. In the case of ASICs, new chips must be manufactured again and old ones have to be discarded, with any change required in the circuit design. However, if the circuit design is based on the FPGA, the design can be updated by simply reconfigurating the FPGA. There are no non-recurring expenses (NREs) for FPGA designs. For this reason, FPGAs are very suitable for ASIC prototyping, and ASICs tend to be reserved for high volume products in the future. Second, FPGAs also have an advantage over traditional ASICs in terms of simpler design cycle and faster time-to-market. The ASIC chip manufacturing process can take months, whereas FPGAs are pre-fabricated and provide off-the-shelf ap-

plications. Even though FPGAs seem a compelling proposition for circuit designs in many situations, FPGAs are not without drawbacks. Because programmable logic blocks and routing resources are not fully utilized, PFGAs usually consumes larger silicon area, which leads to higher per-unit cost and larger power consumption. Besides, FPGAs have slower circuit speed compared with their ASIC counterpart, under the constraints of their logic blocks and routing resources [28, 29]. For applications that require high performance and have strict power consumption requirement, ASICs are still the preferred choice.

#### 1.2 FPGA Architecture Overview

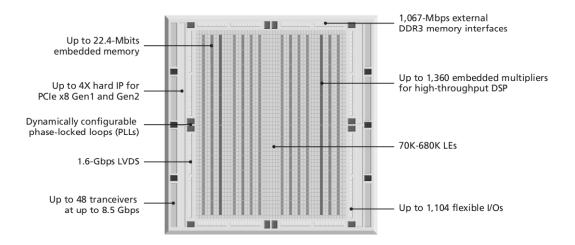

Traditionally, FPGAs include programmable logic blocks which implement logic functions, programmable routing blocks to interconnect these functions and input/output (I/O) blocks to make off-chip connections. They can be programmed to implement any logic functions. However, today's FPGAs have evolved far beyond the basic capabilities present in their predecessors, and incorporated blocks of commonly used functionalities such as embedded memories, embedded processors, Phase-Locked Loops (PLLs), Digital Signal Processing (DSP) units and other special feature blocks. These features make it possible to build a System on Chip (SoC) inside of a single FPGA. An example of modern FPGA architecture is the Altera Stratix IV device, as shown in Figure 1.1.

Every FPGA relies on the underlying programming technology that gives FPGAs their programmability. FPGA vendors offer three fundamental programming technologies for modern FPGAs. SRAM-based FPGAs are widely used and can be found in devices such as Xilinx Virtex-5 [8] and Altera Stratix IV [7]. Non-volatile flash-based technology is used in Actel ProASIC devices [4] and antifuse-based technology is used in Actel Axcelerator devices [3]. SRAM programming technology has become dominant for FPGAs for its re-programmability and use of standard CMOS manufacturing processes. Although, flash-based devices offer benefits in terms of power consumption due to their technology and antifuse-based devices are popular for aerospace and military applications due to their radiation tolerance.

Figure 1.1: Example of a modern FPGA architecture consisting of many different types of resources; e.g., the Altera Stratix IV architecture [6].

#### 1.2.1 LUT-based FPGAs

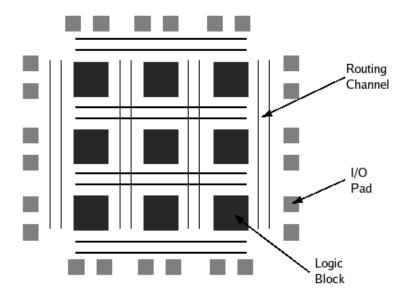

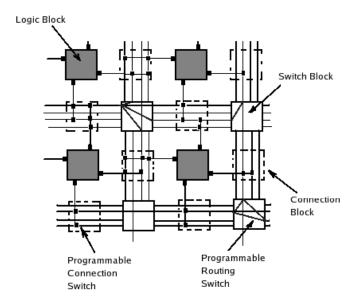

A simplified model of the architecture of an FPGA is illustrated in Figure 1.2. In Figure 1.2, the FPGA is arranged in an island-style structure based on an array of identical programmable logic blocks surrounded by routing channels with the I/O pads evenly distributed around the perimeter of the FPGA [5].

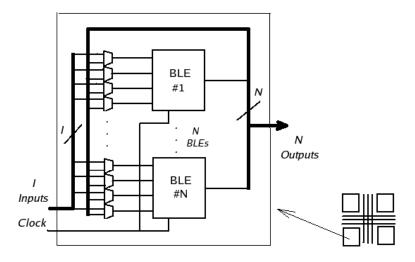

The logic blocks consist of circuitry for implementing the functionality of the given circuit. Logic blocks are also called logic clusters, or configurable logic blocks (CLBs). The structure of a simplified cluster-based logic block is illustrated in Figure 1.3. Each cluster contains N Basic Logic Elements (BLEs). Typically, the number of input pins on the CLB is less than the sum of the number of inputs of the contained BLEs. Therefore, if the BLEs within the CLB are to be fully utilized, some of the BLEs will need share inputs. Typically, the BLE outputs are fed back to the BLE inputs within the cluster; i.e., BLEs within the same CLB can drive each other's inputs without having to go outside of the CLB. Because the delay of intra-CLB connections is typically much less than the delay of inter-CLB connections (it is unnecessary to use external routing resources when making intra-CLB connections), it is preferable to group BLEs together that share many

Figure 1.2: A simplified view of an island-styled FPGA consisting of CLBs. [1]

interconnections. Increasing the number of inputs to each logic block can increase the number of logic functions realized by each logic block as well as improve the performance of the logic block. However, this comes on the expense of wasted resources because not all the logic blocks will have all of their inputs fully utilized. The Altera Stratix and Xilinx Virtex FPGA devices are commercial examples of FPGA architectures that use the idea of BLEs clustered together inside of CLBs [7, 8].

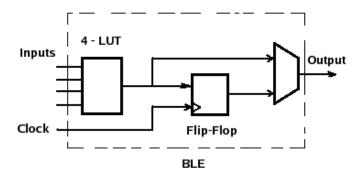

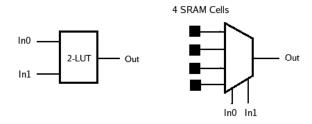

The simplified architecture of a BLE is shown in Figure 1.4. Each BLE consists of a k-input Look-Up Table (LUT) for implementing combinational logic and a register for implementing sequential logic. A multiplexer permits either the LUT or the register to feed the output of the BLE. A k-input LUT consists of  $2^k$  configuration bits and can realize any Boolean logic function of up to k variables by programming the truth table of the Boolean logic function directly into the memory bits of the LUT (the programming of the LUT is done during the configuration of the FPGA). Figure 1.5 shows a two-input LUT with 4 programmable memory bits and a multiplexer to select one of the memory bits based on the two select lines which serve as inputs to the 2-input logic function. In commercial LUT-based architectures, k typically varies from 3 to 6.

Figure 1.3: A simplified illustration of a Configuration Logic Block (CLB).

In the island-style FPGA architecture, each BLE can be connected to other BLEs via horizontal and vertical routing channels. A generic FPGA routing architecture is illustrated in Figure 1.6. Switch boxes connect horizontal and vertical channels through programmable switches. Connection boxes are used to connect routing channels to the CLBs [41]. The routing architecture of an FPGA is prefabricated and most modern FPGA architectures use various wires of different segment lengths to achieve the optimal performance in terms of circuit delay, routability or both. Finally, in addition to programmable routing for the purposes of connecting logic blocks, modern FPGAs also contain dedicated global routing networks for the purpose of distributing low skew clocks and control signals throughout the programmable logic fabric.

#### 1.3 FPGA CAD Flow

FPGAs have become very popular in recent years, due to their programmability and fast time-to-market. With the advances in process technology, the number of gates and features on a single FPGA device has increased dramatically to compete with capabilities that have traditionally only been offered through ASIC devices. To effectively use FPGAs, circuit

Figure 1.4: A simplified illustration of a Basic Logic Element (BLE).

Figure 1.5: An illustration of a 2-input LUT.

designers must resort to and rely on Computer-Aided Design (CAD) tools. These tools play a critical role in delivering high-quality results when implementing a circuit via an FPGA. Since designs and devices continue to increase in size and capability, CAD tools must continually be improved in order to achieve high-quality results with reasonable computational effort.

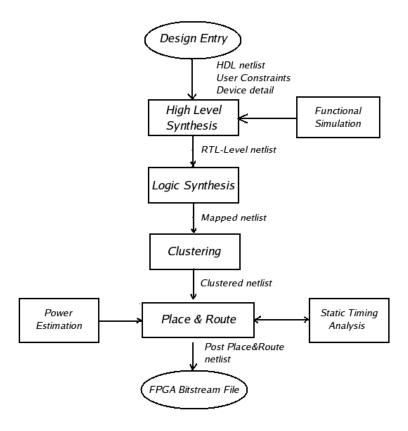

Today, most FPGA vendors provide a fairly complete set of design tools that automatically transform design specification, entered either as a schematic or using a hardware description language (HDL), such as Verilog or VHDL, all the way down to a stream of "1"s or "0"s that program the FPGA chip during the configuration time. The main steps of the FPGA CAD flow are illustrated in Figure 1.7 and are described below.

Figure 1.6: An illustration of the programmable routing architecture in an FPGA.

#### 1.3.1 High-level Synthesis

High-level synthesis (HLS) is the process of interpreting an algorithmic description of a desired behaviour and creating hardware that implements the algorithm [32, 24, 22]. This process involves tasks such as identifying and instantiating datapaths and control logic (e.g., finite state machines) that implement the desired circuit behaviour. High-level synthesis also performs logic scheduling and resource binding subject to any provided architectural constraints. The output of HLS is typically a Register-Transfer Level (TRL) netlist consisting of combinational logic, registers and, finally, clock and control signals.

#### 1.3.2 Logic Synthesis

Logic synthesis takes an RTL netlist and performs both technology independent and technology dependent netlist optimizations. Technology independent optimization is typically referred to as logic optimization and technology dependent optimization is typically referred to as technology mapping.

Figure 1.7: A typical FPGA CAD flow.

Logic optimization performs tasks such as the removal of redundant logic and simplification of logic functions in a technology independent fashion. It may also perform sequential optimizations including register retiming. Generally, the purpose of logic optimization is to generate an optimized netlist without the use of any technology dependent information which is useful for transforming the circuit netlist into something more suitable for the subsequent technology mapping phase.

Technology mapping is the phase in which a circuit netlist is converted, or mapped, into a netlist which is realizable within the target technology. For FPGA designs, this means conversion of combinational logic into k-input LUTs. Technology mapping is not only responsible for converting the netlist into something which is implementable within

the given target technology, but it is also responsible for performing optimizations; i.e., minimizing circuit depth, area and any other important objectives. The topic of this thesis involves FPGA technology mapping. Hence, technology mapping is described in greater detail later on in this thesis.

#### 1.3.3 Clustering

In the clustering phase, LUTs and registers are first packed into BLEs. Then, a set of CLBs are generated from the set of BLEs. The clustering phase has to consider specific parameters of the target FPGA architecture, such as the maximum number of BLEs inside of a CLB as well as other architectural limitations/constraints on the CLBs. The objective of the clustering algorithm is to minimize the number of logic blocks and/or minimize the delay. Certainly, commercial FPGA CAD tools perform clustering. Examples of academic clustering tools would include VPack or T-VPack [10].

#### 1.3.4 Placement and Routing

In the placement phase, the packed logic blocks are assigned to specific physical logic blocks in the prefabricated two-dimensional array. In the case of island-style FPGAs, CLBs are moved around to determine the best location for each CLB. After the placement step, every CLB is assigned an X and Y location which represents its physical location. The procedure tries to minimize the delay along the critical path and enhance the routability of the resulting circuit [10].

The routing phase assigns the nets that connect CLBs in the placed netlist to specific segmented wires in the routing channels. Routing for FPGAs is complicated by the fact that the amount of routing resources in the FPGA device is fixed. Generally, routing can be divided into two steps: global routing and detailed routing [11, 12]. Global routing selects the channel for every net. Next, detailed routing assign each net to a specific wire in the channel. The objective of the routing algorithm is to minimize the delay along the critical path and avoid congestion in the FPGA routing resources.

Finally, the mapped, placed, and routed design generates the bit-stream file to program the logic and interconnect resources to implement the desired logic design on the target FPGA device.

#### 1.4 Contributions of the Thesis

The topic of this thesis involves the technology mapping stage of the FPGA CAD flow. In particular, this thesis focuses on post-technology mapping for area minimization subject to depth (i.e., delay) constraints. Hence, technology mapping is described in greater detail later in this thesis. Stated succinctly, the contributions of this thesis are as follows:

- An algorithm is proposed for performing area minimization on a technology mapped netlist. Essentially, the algorithm is based on the idea of circuit rewriting which replaces, or rewrites, cones of LUTs with alternative topologies of LUTs which serve to reduce circuit area (as measured in terms of the number of LUTs). Circuit functionality and delay are always preserved.

- The aforementioned algorithm requires the off-line creation of a library of topologies of LUTs. This turns out to be a potential time and space consuming task. The thesis proposes several strategies to improve the time and space efficiency of the off-line library generation.

- The thesis presents numerical results on a large set of design circuits to demonstrate the potential efficacy of the proposed algorithm in terms of its effectiveness at area minimization and in terms of runtime.

#### 1.5 Summary

This introductory chapter has provided some background on FPGA architectures and the importance of the FPGA CAD flow. The remainder of this thesis is as follows. Chapter 2 provides additional background on the problem of FPGA technology mapping. Background on SAT-based Boolean matching as a means of determining if a particular topology of LUTs can implement a function is described in Chapter 3. The use of SAT-based Boolean matching as a post-technology mapping optimization algorithm is also described.

Thesis contributions are described in the following chapters. Chapter 4 describes the use of NPN equivalence classes for performing Boolean matching. Prior to the use of NPN equivalence classes for matching, it is shown that a topology of LUTs must be simulated and encoded. This procedure is shown to be complex in terms of both space and time. The idea of essential bits and practical bits are introduced as a means of reducing both the space and time complexity of the procedure. In Chapter 5, the overall algorithm for post-technology mapping area minimization based on NPN equivalence classes is proposed. Numerical results on a large suite of designs are also provided to demonstrate the efficacy of the proposed algorithm. Finally, the contributions of the thesis are described in Chapter 6. Future research possibilities are also described.

# Chapter 2

# Technology Mapping for LUT-based FPGAs

The purpose of FPGA technology mapping is to convert a netlist composed of simple logic gates into a netlist composed of k-input LUTs. The mapping procedure attempts to minimize some combination of area and delay. Other objectives, including power dissipation and routability may also be taken into account.

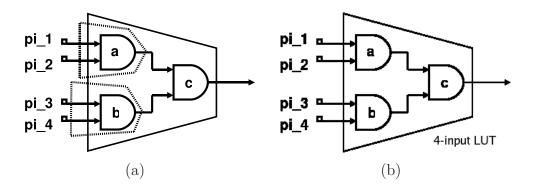

Modern FPGA technology mappers can be divided into functional mappers and structural mappers. Functional mappers perform Boolean decomposition of the logic functions of the nodes into sub-functions of limited support size realizable by individual LUTs [37]. Since functional mappers explore a larger solution space, they tend to be time-consuming, which limit their use to small designs. Structural mappers find a covering of the circuit graph with k-input subgraphs which correspond to k-input LUTs [17]. Due to both their efficiency and effectiveness, most modern state-of-the-art FPGA technology mappers are structural mappers.

Structural technology mappers typically proceed as follows: A circuit netlist is first converted into a simple network which consists of 2-input logic gates; e.g., a network such as an And-Inverter Graph (AIG) [17, 33]. This network is typically referred to as the subject graph. Subsequently, for mapping to an FPGA architecture consisting of k-input LUTs, all cuts of size k or less are computed for every node in the subject graph. This step is known as cut enumeration. Finally, the best cuts for a subset of nodes are selected

to form k-input LUTs which cover all the gates in the subject graph. In performing the covering of the subject graph, the covering is done in order to minimize some combination of delay and area (or other objectives). Technology mapping for minimum circuit depth is known to be polynomial, but not for other objectives such as area. Hence, technology mapping is performed using a variety of heuristics during the covering of the subject graph.

The purpose of this chapter is provide background information on technology mapping. This includes cut enumeration and the different heuristics used by modern state-of-the-art technology mappers to select a set of cuts to cover the input subject graph.

#### 2.1 Background

A combinational Boolean circuit can be represented as a directed acyclic graph (DAG) G = (V, E) in which a node v represents a logic gate, and a directed edge e corresponds to a wire that connects two gates. A primary input (PI) is a node without incoming edges and a primary output (PO) is a node without outgoing edges. Inputs and outputs of flip-flops (FFs) can be treated as additional cases of POs and PIs. If there is a path from node v to node v to node v is a predecessor of v and v is a predecessor of v. The topological order exists in the DAG, such that each node appears after all its predecessors and before all its successors in the ordering.

For any node v, fanin(v) denotes the set of nodes which are fanins of node v. Similarly, fanout(v) denotes the set of nodes which are fanouts of node v. A primary input node has no fanins and a primary output node has no fanouts. A node is k-feasible if  $|fanin(v)| \leq k$ . If every node in a graph is k-feasible, then the graph is k-bounded. A subject graph is typically the terminology reserved for the 2-bounded network which is used as input for the technology mapper. Subject graphs are typically represented as And-Inverter Graphs (AIGs) which are networks consisting of 2-input AND gates and inverters.

A cone of logic  $C_v$ , rooted at node v, is a sub-graph composed of v and some of its non-PI predecessors such that any node  $u \in C_v$  has a path to v which is entirely included in  $C_v$ . We use  $fanin(C_v)$  to denote the set of nodes outside of  $C_v$  which drives nodes inside of  $C_v$ . The set of fanins to a cone is also known as a cut in the graph. There is a one-to-one correspondence between a cut and a cone. The notion of k-feasibility also applies to cones

and cuts. A  $fanin\ (fanout)\ cone$  of node v is a cone that consists of all nodes reachable through the fanin (fanout) edges from the node v. A  $maximum\ fanout\ free\ cone\ (MFFC)$  of node v is a subset of the fanin cone, such that every path from a node in the subset to the POs passes through v. Hence, the MFFC of a node contains all the logic used by the node.

The level of a node v, denoted as level(v), is the number of edges on the longest path from a PI to v. The level for a PI node is zero. Often, the terminology level and depth are used interchangeably. The network depth is the largest level of an internal node in the network. The depth and area of a technology mapped netlist is measured by the depth of the network and the number of LUts in the network, respectively.

#### 2.2 Cut Enumeration

Cut enumeration is the process of determining all different cones (or cuts) of logic that can be used to implement the function at node v such that each cut is k-feasible. Cuts for a node v are created by using the cuts from its fanin nodes and combining them to form cuts for node v. An example of this is shown in Figure 2.1(a) where, to generate a cut for node c, two cuts from nodes a and b are duplicated and combined to form a larger cut that includes nodes a, b and c. Modern FPGAs consist of an array of k-input LUTs connected together through programmable interconnect. Since a k-input LUT can implement any function of fewer than k variables, in technology mapping it suffices to find all k-feasible cuts of each node v. The correspondence of k-input LUTs and k-feasible cuts is shown in Figure 2.1(b).

Let  $u_1, u_2, \dots, u_t$  denote the fanins of node v and let  $S_{u_i}$  denote the set of all k-feasible cuts for node  $u_i$  for  $1 \le i \le t$ . The set operation called *merge* is defined as follows [40]:

$$merge(S_{u_1}, S_{u_2}, \dots, S_{u_t}) =$$

$$\{s = s_1 \cup s_2 \cup \dots s_t | s_i \in S_{u_i} \text{ and } || s || \le k\}.$$

(2.1)

The set of k-feasible cuts for node v, denoted by  $S_v$  is equal to  $merge(S_{u_1}, S_{u_2}, \ldots, S_{u_t}) \cup \{v^0\}$  where  $\{v^0\}$  represents the trivial cut containing node v only. Hence, if all k-feasible cuts of the fanins of a node v are given, we can find all non-trivial k-feasible cuts of the

Figure 2.1: An illustration of cut enumeration: (a) A larger cut for node c derived from the cross product of the cutsets for nodes a and b; (b) a 4-LUT derived from the 4-input cut.

node v using the merge operation. This suggests that cut enumeration works by visiting each node in the network in topological order from PIs to POs and applying the merge operation to each node v. Any newly formed cuts that are not k-feasible are discarded during the process. Note that PIs only have a trivial cut. Cut enumeration as described is not scalable to larger cut sizes (e.g., k > 7) and for cuts containing a large degree of reconvergent paths.

In the process of merging the cut sets to form the resulting cut set, it is necessary to delete duplicated cuts and remove dominated cuts. Removing useless cuts before computing the cuts for the next node reduces the number of cut pairs considered without impacting the quality of mapping. In practice, the total number of cut pairs tried during the merging greatly exceeds the number of k-feasible cuts found. This makes checking k-feasibility of the unions of cut pairs, and testing duplication and dominance of individual cuts, the performance bottleneck of the cut enumeration.

The most serious problems in cut enumeration are the high time and space complexities. For a circuit with n nodes, the number of cuts of size k can be as large as  $O(n^k)$  [21] and computing all cuts can take significant runtime. For small cuts (i.e. k = 6 or 7), the enumerative procedure is feasible to compute all cuts. But for large cuts, the enumerative procedure fails simply because there are too many cuts. Fortunately, modern FPGAs are built using LUTs with  $\leq 6$  inputs.

There are some heuristic approaches to make cut enumeration more manageable. In [21], this problem is addressed by selectively pruning cuts that seems to be useless. However, for large cut sizes, pruning tends to remove many valuable cuts in the following mapping solution. In [14], the notion of *cut factorization* is introduced where one enumerates both global and local cuts and uses these cuts to generate other cuts. It is possible to generate any cut from the factor cuts (i.e., complete factorization), but this is still an expensive operation. Partial factorization can also be used, but in this scheme there is no guarantee of generating all cuts from the factor cuts. In [16, 36], the notion of prioity cuts is introduced. In this scheme, only the most promising set of cuts for any given node are kept and propagated through the network. This reduces the runtime and memory requirements of cut enumeration, but can prevent some good cuts from being generated. Nevertheless, priority cuts are empirically demostrated to be useful for mapping to k-inputs LUTs. Given the cutset for a node v, each cut  $C_v$  is ranked according to several different criteria, such as (1) the logic depth of the cut, (2) area of the cut, (3) number of inputs of the cut |fanin(v)|. Since cuts are computed in topological order, the depth of a cut is computed easily by finding the maximum depth of the inputs of the cut. The area of the cut is a measure of the effectiveness of the cut in covering the underlying subject graph. Finally, the number of inputs of the cut is also a useful metric since those cuts which have good depth and large area, but only a small number of inputs, are likely to result in good mappings.

#### 2.3 Timing Analysis

In order to optimize performance, technology mappers must have some concepts of circuit delay. Although arbitrary delay models can be used during technology mapping, it is most often the case that exact layout information is not available (i.e., placement and/or routing has not yet been performed). Hence, it is common for technology mappers to use a *unit delay* model to measure performance. In this model, each LUT contributes one unit of delay to any circuit path that passes through the LUT. Hence, under the unit delay assumption, the delay of a network becomes synonymous with circuit depth (or circuit level).

Under the unit delay model, and assuming that cut enumeration has been performed,

it is possible to compute the optimal delay for any given node in the subject graph. Subsequently, the optimal delay for the mapped network can be computed; i.e., the best achievable circuit delay is known. The minimum delay at any node v, denoted by arrival(v), can be calculated by

$$arrival(v) = min[max[arrival(u_i)] + 1], \forall C_v \in cutset(v), u_i \in fanin(C_v)$$

(2.2)

where  $C_v$  represents a cut in the cutset for node v and  $arrival(u_i)$  is the arrival time on the fanin  $u_i$  of  $C_v$ . The calculation of arrival times is computed in topological order from the PIs towards to POs of the network. The worst arrival time at any of the POs represents the worst case delay of the entire circuit; i.e., the optimal (minimum) worst case delay of the circuit.

Given a selected set of cuts which cover the subject graph, the required time at any node v, denoted as required(v), can be computed. The required time denotes the largest delay allowed at the node v in order to achieve the best network delay. Required times are computed in reverse topological order from POs backward toward the PIs of the network. The required time at any node v is computed by

$$required(v) = min[required(v), required(n) - 1], n \in fanout(v)$$

(2.3)

where n is a fanout of node v. Finally, the slack can be computed for each node in the technology mapped network. The slack for any node v in the mapped network, denoted by slack(v) is computed in terms of its arrival and required times by

$$slack(v) = required(v) - arrival(v).$$

(2.4)

Slack gives an indication of how far away a node is from being considered as timing critical. Nodes with slack > 0 are not on the critical path; i.e., they are not timing critical. Nodes with slack  $\le 0$  are timing critical nodes and are important for performance.

#### 2.4 Practical Technology Mapping

As mentioned, modern FPGA technology mapping algorithms [17, 18, 15, 31, 35] are based on cut enumeration. This is because every k-input cut maps directly into a k-input LUT.

Procedure: TECHNOLOGY MAPPING

**Inputs:** An And-Inverter netlist N and LUT architecture K

Outputs: A mapped LUT-based net list  $N^\prime$

- 1 Perform cut enumeration and save all K-feasible cuts at each node;

- Find a depth-optimal cut at each node and mark it as the representative;

- 3 Modify the representative cut at each node on the non-critial paths to save area;

- 4 Replace each representative cut with a corresponding LUT;

- Return the netlist N' of LUTs as the result of the final mapping;

Figure 2.2: The typical FPGA technology mapping flow.

Based on the previous descriptions of cut enumeration and timing analysis, it is possible to develop an intuitive approach for the objectives of any technology mapping solution. The overall flow of technology mapping is described in Figure 2.2. Specifically, the goal of any technology mapper is to select the "correct" set of cuts such that (1) the delay of the circuit is minimized (delay optimal) while (2) requiring a minimum number of cuts (area optimal) to cover the original network. Intuitively, selecting a set of cuts which yield a delay optimized solution is straightforward (select the delay minimizing cut for each node v from the cutset for node v). In fact, the depth-optimal technology mapping problem can be solved in polynomial time using a dynamic programming procedure known as FlowMap [17]. Conversely, the area minimization problem has been shown to be NP-hard for k-input LUTs of size  $k \geq 3$  [23]. The selection of a set of cuts which minimizes area is not straightforward.

Thus, heuristics are necessary to solve the area-minimization problem. The area minimizing mapping procedure based on depth relaxation is shown in Figure 2.3. Before the area minimizing procedure, the new required time is computed on each node in reverse topological order. The node with slack larger than 0 is claimed to be on the non-critical path, and the representative cut on the node can be changed to minimize local mapping area without violating the timing constraints. As discussed in IMap [31] and ABC [36, 35], two complementary heuristic measures of area cost are applied as guidance to good practical results. The first heuristic area flow has a global view and selects logic cones with more shared logic. It can be computed in one pass over the network from the PIs to the POs. Area flow for the PIs is set to 0, and area flow at node v is:

$$AreaFlow(v) = [Area(v) + \sum_{i} AreaFlow(fanin_{i}(v))] / numFanouts(v)$$

(2.5)

```

Procedure: Area Recovery Heuristics

Inputs: A optimum-depth netlist, N

Returns: A mapped netlist with area recovery, N'

1

Update the required times from POs to PIs for the last mapping;

2

for each node n in topological order from PIs to POs do

3

for each cut C at node n do

C_r is the current representative cut;

4

5

if Arrival\_Time(C) \le Required\_Time(n) then

6

if AreaFlow(C) < AreaFlow(C_r) then

7

C_r = C; continue;

8

end if

if LocalArea(C) < LocalArea(C_r) and AreaFlow(C) == AreaFlow(C_r) then

9

C_r = C; continue;

10

end if

11

12

end if

13

end do

14

end do

15

return N';

```

Figure 2.3: Pseudocode for area recovery mapping procedure.

where AreaFlow(v) is the number of LUTs needed to cover the representative cut at the node v.  $fanin_i(v)$  is the i-th fanin of the representative cut at v, and numFanouts(v) is the number of fanouts of node v in the last mapping solution. The second heuristic local area looks at the area added to the mapping by locally modifying the representative cut at a node. The local area is equal to the sum of the LUTs in the MFFC of the cut, i.e. the LUTs to be added to the mapping if the cut is selected as the representative cut. It has a local view by minimizing the area exactly at each node. In one pass of area recovery, area flow is used as the primary metric and local area as a secondary metric to break the tie. The heuristic area minimizing procedure will run several iterations until no area improvement happens. At last, one pass of LUT covering is done in reverse topological order. For each PO, the representative cut is chosen and a LUT is constructed in the mapped netlist to implement it. Then, recursively for each fanin node of the LUT, this procedure is repeated until the whole netlist is covered by LUTs.

#### 2.5 Summary

This chapter has introduced the concept of cut enumeration and has described the typical flow of state-of-the-art structural FPGA technology mappers. These technology mappers are capable of producing delay optimized solutions given the structure of the provided subject graph. However, they make local decisions based on depth relaxation and various heuristic measures of area cost (e.g., area flow and exact local area evaluation) in order to minimize area. Further, because these technology mappers are structural in nature and cut enumeration is performed on the provided subject graph, the ability of the technology mappers is somwhat restricted by the structure of the provided subject graph. Hence, because of the limitations imposed based on the structure of the subject graph and due to the heuristic nature of the area minimization, it is quite likely that the technology mapped netlists can be further improved if additional post-processing is applied directly to the technology mapped netlist.

# Chapter 3

# SAT-Based Boolean Matching

As mentioned in Chapter 2, structural technology mappers suffer from two main issues with respect to area minimization. First, the results produced by structural mappers depend strongly on the structure of the initial subject graph. Second, these mappers make local choices when selecting a cut for any given node; choices are made based on either local or heuristic measures of area. Hence, the LUT netlists produced by structural mappers can be further optimized by post-technology mapping improvement techniques which target the minimization of area under delay constraints [33, 30, 43, 20, 26].

This chapter describes how LUT netlists can be further optimized through the use of Boolean matching. The Boolean matching problem is described. Subsequently, it is demonstrated how the Boolean matching problem can be solved via the solution of a Boolean Satisfiability (SAT) problem. These approaches are computationally demanding and too slow for practical purposes.

#### 3.1 Boolean Matching

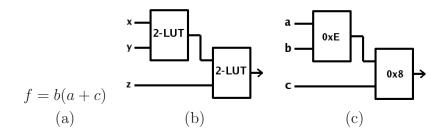

For the purposes of this thesis, the problem of Boolean matching can be stated as follows. Can a logic function f of n variables, e.g., expressed in terms of its truth table, be implemented by some topologies of LUTs? For example, Figure 3.1(a) shows a 3-input logic function f = b(a + c). The question to be answered is whether or not this function can be implemented by the topology of LUTs illustrated in Figure 3.1(b). In this example, the

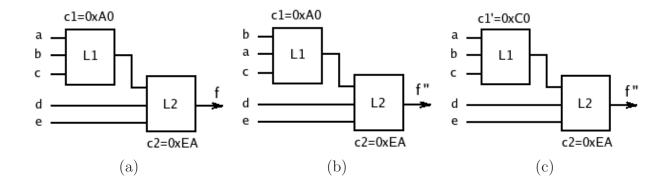

Figure 3.1: An example of Boolean matching: (a) A 3-input logic function f; (b) A topology of LUTs consisting of two 2-input LUTs; (c) An implementation of f.

function can be implemented as showing in Figure 3.1(c) by connecting the function inputs as shown and setting the configuration bits of the LUTs appropriately; other solutions are also possible and are obtained by permutation of the inputs and changing the values of the configuration bits for the LUTs.

Within the FPGA community, the problem of determining whether or not a logic function f can be implemented via a topology of LUTs has been formulated as a SAT problem. This is accomplished as follows: First, an expression representing the topology of LUTs is created in Conjunctive Normal Form (CNF). Second, this CNF expression is duplicated once for each row of the truth table of f. Finally, the conjoined CNF expression is passed to a SAT solver. If the SAT solver returns false, then the logic function can not be implemented by the topology of LUTs. On the other hand, if the SAT solver returns true, then the logic function f can be implemented by the topology of LUTs. Further, the solution to the SAT problem provides the proper permutation for connecting the inputs of the logic function and the proper configuration bits for the LUTs within the topology.

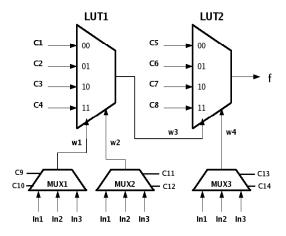

To illustrate this process, consider the problem of determine whether or not a logic function f with  $\leq 3$  inputs can be implemented by the LUT topology consisting of two 2-input LUTs shown in Figure 3.1(b). To create the CNF for the topology, it is necessary to break down the topology into individual circuit elements and compute the CNFs for each individual element. The individual CNFs can then combine to form the CNF for the entire topology. In order to account for input permutations, it is necessary to add *virtual multiplexers* at the inputs of the topology. These multiplexers do not exist in the topology and are "artifically" added into the SAT problem in order to support the permutation

Figure 3.2: Illustrating of the CNF creation for a particular topology of LUTs. Virtual multiplexers are included to allow for input permutation.

of the logic function inputs. The topology consisting of two, 2-input LUTs in Figure 3.1 is illustrated in terms of its basic logic elements in Figure 3.2. The addition of virtual multiplexers to allow for input permutation is also illustrated in Figure 3.2.

In Figure 3.2, the CNF for LUT1, denoted by  $G_{LUT1}(\vec{x}, \vec{C}, f)$ , involves the two inputs  $w_1w_2 = \vec{x}$ , the configuration bits  $C_1C_2C_3C_4 = \vec{C}$ , and the output  $w_3 = f$  and is given by

$$G_{LUT1} = (w_1 + w_2 + \overline{C_1} + w_3) \cdot (w_1 + w_2 + C_1 + \overline{w_3}) \cdot (w_1 + \overline{w_2} + \overline{C_2} + w_3) \cdot (w_1 + \overline{w_2} + C_2 + \overline{w_3}) \cdot (\overline{w_1} + w_2 + \overline{C_3} + w_3) \cdot (\overline{w_1} + w_2 + C_3 + \overline{w_3}) \cdot (\overline{w_1} + \overline{w_2} + \overline{C_4} + w_3) \cdot (\overline{w_1} + \overline{w_2} + C_4 + \overline{w_3})$$

$$(3.1)$$

Similarly, The CNF for MUX1, denoted by  $G_{MUX1}(\vec{x}, \vec{C}, f)$ , involves inputs  $i_1 i_2 i_3 = \vec{x}$ , the configuration bits  $C_9 C_{10} = \vec{C}$ , and output the  $w_1 = f$ .

$$G_{MUX1} = (C_9 + C_{10} + \overline{i_1} + w_1) \cdot (C_9 + C_{10} + i_1 + \overline{w_1}) \cdot (C_9 + \overline{C_{10}} + \overline{i_2} + w_1) \cdot (C_9 + \overline{C_{10}} + i_2 + \overline{w_1}) \cdot (\overline{C_9} + C_{10} + \overline{i_3} + w_1) \cdot (\overline{C_9} + C_{10} + i_3 + \overline{w_1}) \cdot (\overline{C_9} + \overline{C_{10}})$$

$$(3.2)$$

As mentioned, since MUX1 is a virtual multiplexer, its configurations bits are used to determine which of the logic function inputs should be connected to  $w_1$ ; the configuration bits are not required for the programming of any LUT.

Now combining these two equations according to Figure 3.2, along with similar equations for the other LUTs and virtual multiplexers, yields the CNF equation given by

$$G_{Total} = G_{MUX1}(i_1 i_2 i_3, C_9 C_{10}, w_1) \cdot G_{MUX2}(i_1 i_2 i_3, C_{11} C_{12}, w_2) \cdot G_{MUX3}(i_1 i_2 i_3, C_{13} C_{14}, w_4) \cdot G_{LUT1}(w_1 w_2, C_1 C_2 C_3 C_4, w_3) \cdot G_{LUT2}(w_3 w_4, C_5 C_6 C_7 C_8, f)$$

$$(3.3)$$

which represents the input for the entire LUT topology with inputs  $i_1i_2i_3$  and output f.

In order to test whether function f could be implemented by the LUT configuration,  $G_{Total}$  would have to be duplicated for each of the possible  $2^3$  inputs (for an n-input function, the  $G_{Total}$  would need to be duplicated  $2^n$  times). Each copy of  $G_{Total}$  corresponds to one specific row of the function's truth table and has appropriate values substituted for the input variables and the output variable in the CNF. The conjunction of the  $2^3$  duplicates of  $G_{Total}$  represent the CNF equation specific to the function f which is being tested against the generic topology of LUTs. This CNF equation can be fed into a SAT solver to determine whether or not the function f can be implemented by the topology.

The SAT-based approach for Boolean matching is complete and guarantees to find a match if it exists. It can be easily customized to different topologies of LUTs and therefore offers great flexibility. However, it suffers from excessive runtime due to high computational complexity even with improvements [43, 20, 26]. The complexity of SAT-based Boolean matching increases dramatically with the number of inputs in the topology; e.g., it can take seconds or minutes to solve a problem involving the matching of a 10-input logic function. With an imposed timing limit, the SAT-based Boolean matching procedure becomes incomplete with only a limited success rate; e.g., as shown in [20], only 50% Boolean matching problems are solved for 10-input Boolean functions under the timeout limit of 60 seconds.

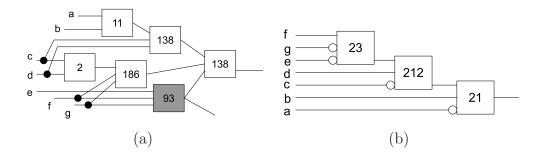

Figure 3.3: Using matching to reduce area: (a) A 7-input logic cone implementing a logic function f which can be implemented by (b) an alternative circuit.

#### 3.2 Post-Technology Mapping Optimization

The procedure for SAT-based Boolean matching can be used to post-process technology mapped netlists to perform further area minimization without harming the delay of the mapped netlist. This is accomplished as follows. In turn, each node in the technology mapped netlist (i.e., a netlist of LUTs) can be examined. This examination can be done randomly or in some specific order such as in a topological order. For any selected node v, an n-input cone of logic C rooted at node v can be computed for some reasonable n(typically  $n \leq 10$ ). Once the cone of logic is selected, it can be simulated to determine its logic function f. Subsequently, assuming a topology of LUTs is provided with  $\geq n$  inputs, a SAT problem can be formulated to determine if the function f of the cone C can be implemented by the topology of LUTs. If f cannot be implemented, either another cone of logic is attempted for node v, or the algorithm proceeds to another node in mapped netlist. If, however, f can be implemented by the topology of LUTs, this topology provides an alternative circuit structure that can be used to replace the original cone of logic C without changing the function f. If the new circuit topology for implementation of f reduces the number of required LUTs in the network and does not cause the slack at node v to become negative, then the topology of LUTs is a suitable replacement for the cone of logic which reduces the total number of LUTs in the mapped network without impacting the worstcase network delay. An example of replacing a cone of logic with an alternative topology of LUTs is illustrated in Figure 3.3. In Figure 3.3(a), a 7-input cone of logic is identified in the technology mapped netlist. Here, the unsigned integer values inside of each LUT indicate the configuration bits of the LUT. The selected logic cone consists of 6 LUTs. Note that one of the LUTs in the logic cone has multiple fanouts; it cannot be removed by replacing the logic cone. In Figure 3.3(b), an alternative implementation for the logic cone is shown and was obtained by matching the logic function to a topology of three, 3-input LUTs connected serially. Here, the unsigned integers again represent the LUT configuration bits. The bubbles represent inversions which can be absorbed into the LUTs. This alternative topology requires only 3 LUTs. Hence, assuming that the delay at the output of the new topology does not worsen the worst-case delay of the network, the alternative circuit structure in Figure 3.3(b) can be used to replace the original implementation of the logic function in Figure 3.3(a) while removing two LUTs from the mapped netlist.

#### 3.3 Summary

This chapter has described the Boolean matching problem and shown that it can be solved by formulating a SAT problem. Further, this chapter has described how Boolean matching can be used in an algorithm applied to post-technology mapping optimization. Although very general, the SAT-based approach to Boolean matching is rather time consuming which makes it less attractive and an actual optimization algorithm applied after technology mapping.

# Chapter 4

# NPN-based Boolean Matching

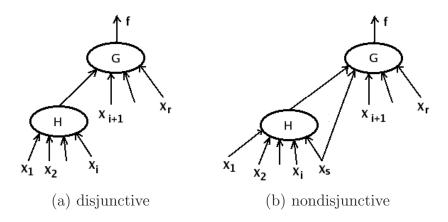

As discussed in Chapter 3, SAT-based Boolean matching is not feasible for practical applications due to the time complexities involved in formulating and solving the necessary SAT problem each time a function is matched. In this chapter, an alternative approach based on the use of precomputed libraries of implementable functions and NPN equivalence classes is proposed. The NPN-based Boolean matching approach finds matches through simple hash table lookups in a pre-computed library of implementable functions created a priori from the analysis of different topologies of LUTs. Since hash table lookups are fast, the resulting Boolean matching is fast enough for practical application. The proposed approach requires a library of topologies of LUTs and the explicit need to determine all of the implementable functions. The creation and storage of the library of implementable functions is time consuming and memory intensive; it is the potential inability to create a library that limits the practicality of the approach. However, if the library can be created, then the proposed method is fast and efficient for performing Boolean matching.

This chapter describes how a pre-computed library of implementable functions, created by the analysis of a set of topologies of LUTs, can be used along with the idea of NPN equivalence classes as an alternative to SAT-based Boolean matching. Some critical improvements on computation time and memory usage are proposed to make the a priori library creation more efficient and practical.

### 4.1 Matching Via Hash Table Lookups

Intuitively, SAT-based Boolean matching is an implicit way to answer the question whether or not a logic function f with  $\leq k$  inputs can be implemented by a k-input topology of LUTs; i.e., given a topology of LUTs, all implementable functions with  $\leq k$  inputs are implicitly represented by a set of Boolean clauses. Determining whether or not a logic function f is implementable involves tailoring the SAT problem to the particular function and performing a search (accomplished via the SAT solver) through the clauses for a solution.

However, there is an alternative way to answer the question of whether or not a k-input logic function f is implementable by a k-input topology of LUTs. Specifically, given a k-input topology of LUTs, all implementable k-input functions can be enumerated explicitly via a priori simulation and stored (e.g., via a hash table) for future reference. Consequently, the Boolean matching problem is simplified to the problem of looking to see if f is found in the hash table.

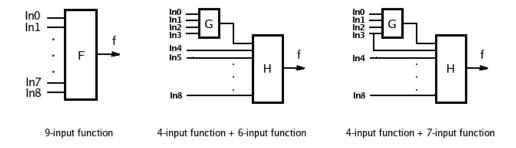

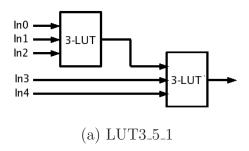

Unlike the SAT-based Boolean matching, the proposed alternative approach is only capable of matching a k-input logic function to a k-input topology of LUTs. This restriction stems from the use of hash table lookups and that everything in the proposed alternative approach is explicit rather than implicit (In SAT-based Boolean matching, it is the use of virtual multiplexers that allows a single variable to be connected to multiple inputs on the topology, c.f. Chapter 3. The use of virtual multiplexers is yet another example of the representation of implicit information). This restriction, however, is not a problem and is easily addressed by creating a library of topologies of LUTs in which each topology has a different number of inputs. The connection of a single logic function input to multiple inputs on a topology is accomplished by matching the function to the proper topology of LUTs. Without further detail, illustrations of the topologies of LUTs used in this thesis are provided in Appendix B. Topologies of LUTs obey the naming convention "LUTx\_y\_v", where "x" means a x-LUT architecture (i.e., the architecture consists of x-input LUTs), "y" represents the number of inputs of the topology, and "v" represents the version of the structure in the topology. For example, the topologies "LUT3\_6\_1" and "LUT3\_6\_4" are the names of two different 6-input topologies for an architecture which consists of 3-input LUTs.

```

Procedure: Enumeration of Implementable Logic Functions

Inputs: A LUT Topology T

Returns: A Hash Table, H.

1

for each set of configuration bits (c_1, c_2, \ldots, c_n) in the topology T do

2

Simulate the current logic function f that is implemented by the topology T;

if f does not exist in the hash table H then

3

4

Insert f and (c_1, c_2, \ldots, c_n) into the hash table H;

5

end if

6

end do

7

return H;

```

Figure 4.1: Enumeration of implementable logic functions for a particular topology of LUTs using simulation.

Hence, the proposed alterative approach to Boolean matching can be described as follows for matching a k-input logic function f to a k-input topology of LUTs: (1) create a library of k-input topologies of LUTs suitable for the target architecture; (2) determine through simulation all logic functions implementable by each topology of LUTs and insert these functions into a hash table; (3) determine which, if any, k-input topologies are capable of implementing the logic function f through hash table lookups.

When simulating a set of topologies of LUTs, a hash table is built for each separate topology of LUTs. Each hash key corresponds to a logic function, and the associated hash value corresponds to a set of configuration bits of LUTs necessary to implement the simulated logic function. The pseudo-code of the exhaustive enumeration procedure for a topology composed of n LUTs is described in Figure 4.1. For each set of configuration bits  $(c_1, c_2, \ldots, c_n)$ , the given topology can be simulated to determine its current logic function f. If the logic function f does not exist in the hash table, it is inserted into the table, with the current set of configuration bits.

Obviously, in the proposed approach, the use of hash tables makes the matching of logic functions extremely fast when compared to SAT-based matching. Whereas SAT-based matching amortizes the matching time over all matching problems, the proposed approach pushes all computational effort to the a priori determination of all implementable functions. Hence, while the exhaustive simulation of a topology of LUTs can be very expensive both in terms of time and memory usage, it only needs to be performed once and can therefore be treated as an off-line process. After the exhaustive enumeration, the functions (along

with configuration bit information) which are implementable are saved to data files. Prior to Boolean matching, these data files are loaded into memory.

However, the Boolean matching approach based on hash lookups proposed above is still facing several severe problems:

- The number of implementable logic functions in a topology is extremely large, due to the flexibility of LUTs. It results in consuming a large portion of memory to keep hash tables online.

- The enumeration of all implementable logic functions for topologies with large number of inputs is time consuming. Runtime improvement is indispensable for precomputation of some topologies.

- The pre-computed library is requested to contain a large number of topologies with different structure, which has a large impact on both computation time and memory usage.

In the following sections, these problems are discussed in detail and relevant solutions are proposed.

### 4.2 NPN Equivalence

The issue of memory usage may be addressed by relying on the concept of NPN equivalence classes to reduce the size of the hash tables required to store those functions implementable by a particular topology of LUTs. Any k-input logic function can be represented through its NPN equivalence class in a canonical way. Specifically, two Boolean functions f and g are said to belong to the same NPN equivalence class if f can be derived from g (or visaversa) by negating (N) and permuting (P) inputs and negating (N) the output [9]. For example, functions f = ab + cd and g = ac + bd are NPN equivalent because swapping b and c makes them functionally equivalent. However, functions f = ab + cd and g = abc + d are not NPN equivalent because any permuting and complementing of variables can not make them functionally equivalent. A canonical form, denoted as the NPN equivalence class  $f_{npn}$  can be used to check NPN equivalence between functions f and g by testing under all input permutations/complementations and output complementation.

```

Procedure: NPN Equivalence Class Enumeration

Inputs: A LUT Topology T

Returns: A Hash Table, H.

1

for each set of configuration bits (c_1, c_2, \ldots, c_n) of LUTs in the topology T do

2

Simulate the current logic function f that is implemented by the topology T;

3

Obtain its NPN equivalence class f_{npn} using a NPN encoder

4

if f_{npn} does not exist in the hash table then

5

Insert f_{npn}, configuration bits, and complementation/permutation information into the hash table

6

7

end do

8

return H;

```

Figure 4.2: Enumeration of implementable logic functions for a particular topology of LUTs using simulation. Only one representative logic function is recorded for each NPN equivalence class.

When simulating a topology of LUTs, rather than inserting all implementable logic functions into a hash table, it is only necessary to store one representative logic function for each NPN equivalence class found during simulation. This requires an extra NPN encoding step in the procedure for the simulation of a topology of LUTs. Specifically, for each set of configuration bits  $(c_1, c_2, \ldots, c_n)$  of LUTs, the topology is simulated to determine the current logic function f. This is followed by an efficient NPN encoding step [2, 13] to obtain the NPN equivalence class,  $f_{npn}$ , of f. If the NPN equivalence class  $f_{npn}$  does not exist in the hash table, it is inserted into the table, with the current set of configuration bits and the specific permutations/complementations on inputs and output provided by the NPN encoder as its associate hash value. Thus, all NPN equivalence classes are enumerated after going through all sets of configuration bits of LUTs. The pseudo-code of the enumeration of NPN equivalence classes for a given topology is described in Figure 4.2. The compressed hash table with all NPN equivalence classes are saved into a data file that corresponds to the name of the given topology. In this way, the number of hash keys maintained in the hash table significantly decreases. For example, for a k-input topology of LUTs, there are as many as  $2^{2^k}$  logic functions possible. However, the number of NPN equivalence classes can be significantly less. As one specific example, there are 65536 possible logic functions for a simple 4-input topology of LUTs. However, there are at most 222 NPN equivalence classes for 4-input logic functions [39].

While the use of NPN equivalence classes effectively reduces the memory usage required to store the hash tables, it does affect the matching process itself. Specifically, given a function f, it is no longer "just sufficient" to look for the function f in the hash table of implementable functions; this is because the hash table only stores equivalence class representatives. Rather, to determine if some arbitrary logic function f is implementable, it is now (additionally) necessary to encode the function and compute the necessary inversions and/or permutations to arrive at a matching for the function. Finally, it is important to note that the permutations and/or inversions do not increase the complexity of the match in terms of the number of LUTs in the topology. Permutations are handled simply by connecting signals as is appropriate. Inversions, rather than creating explicit inverters in the circuit, are simply absorbed into the LUTs within the topology (which corresponds to simple and straight-forward changes to the LUT configuration bits).

Numerical results are presented later in this chapter to demonstrate that the use of NPN equivalence classes results in fairly compact encoding of the logic functions implementable by different topologies of LUTs.

#### 4.3 Essential Bits

Although the use of NPN equivalence classes addresses the potential storage issues, it does not address the runtime implications of determining all of the logic functions implementable by a topology of LUTs. The enumeration of all NPN equivalence classes is time consuming, due to the heavy computation tasks of simulating a topology for a particular set of configuration bits and NPN encoding the resulting simulated function for each set of configuration bits. The complexity of enumerating the implementable logic functions for a topology of LUTs increases dramatically with both the number of topology inputs, the number of LUTs in the topology and the number of LUT inputs. For example, as shown in Table 4.3, it takes about 20 hours to enumerate and encode all implementable logic functions for a 7-input topology composed of three 3-input LUTs (c.f. topology "LUT3\_7\_1" in Table 4.3 and in Appendix B).

However, during the enumeration of the topology, it is possible that certain values of the configuration bits for certain LUTs can be *skipped* and those bits which can be skipped

Figure 4.3: Three NPN equivalent topologies with complementation: (a) Topology  $\{f, c_1, c_2\}$ ; (b) Topology  $\{f', c_1, c_2\}$ ; (c) Topology  $\{f', c_1', c_2\}$

can be determined a priori. Of course, skipping many configuration bits is beneficial, because it will reduce the total amount of simulation and NPN encoding required during the enumeration of the topology to find the implementable functions. Those configuration bits which *cannot* be skipped during enumeration are referred to as the *essential bits* while those bits which can be skipped are referred to as *redundant bits*.

The question arises as to which bits are essential bits and which bits are redundant for a particular LUT in any given topology. Redundant and essential bits follow from the definition of NPN equivalence; based on the definition of NPN equivalence, it is possible to know a priori that two different logic functions implemented by two different sets of configuration bits will lead to the same NPN equivalence class, without knowing which particular equivalence class. Thus, since we only need to store one representative for any particular equivalence class, only one of the two functions needs to be simulated and NPN encoded, thus reducing the overall computational effort required to enumerate the topology. Further, skipping configuration bits in the fashion described will yield the same results as performing full enumeration of the topology (i.e., not skipping any bits).

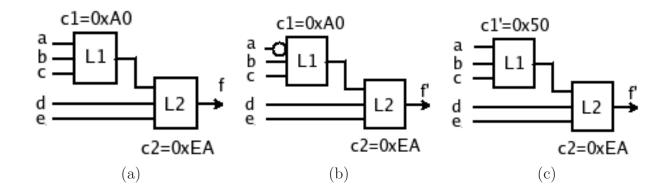

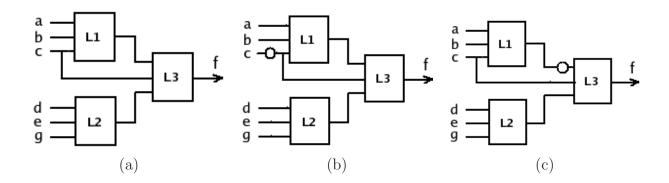

A simple example is used to illustrate the methodology of determining which configuration bits can be skipped for each LUT in a topology. Consider the 5-input topology consisting of two 3-input LUTs illustrated in Figure 4.3(a). The configuration bits for these two 3-input LUTs named  $L_1$  and  $L_2$  are denoted as  $c_1$  and  $c_2$ , respectively. The

Figure 4.4: Three NPN equivalent topologies with permutation: (a) Topology  $\{f, c_1, c_2\}$ ; (b) Topology  $\{f'', c_1, c_2\}$ ; (c) Topology  $\{f'', c_1', c_2\}$

logic function implemented by the above 5-input topology is denoted as f. Assume that configuration bit  $c_1 = 0$ xA0 and  $c_2 = 0$ xEA. This yields a logic function  $f = abc + a\bar{b}c + de$ . In Figure 4.3(b), an inverter represented as a bubble is manually added on the first input pin a of  $L_1$ . In this case, the implementable logic function, denoted as f', is given by  $f' = \bar{a}bc + \bar{a}\bar{b}c + de$ . According to the concept of NPN equivalence, f and f' are NPN equivalent since one is obtained from the other by inversion of an input. Hence, the NPN encoding of both functions would lead to the same NPN equivalence class. Finally, in Figure 4.3(c), the inverter is absorbed into into the LUT  $L_1$ , which modify the configuration bit of  $L_1$  from  $c_1$  to  $c_1'$  with  $c_1' = 0$ x50. Since two logic functions f and f' belong to the same NPN equivalence class, it is not necessary to simulate and NPN encode both the circuit shown in Figure 4.3(a) and Figure 4.3(c); it is guaranteed that none of the NPN equivalence classes will be lost if one of  $\{c_1, c_2\}$  or  $\{c_1', c_2\}$  is skipped during the enumeration of the topology.

Similarly, input permutation and output complementation can also be used to find out the sets of configuration bits which implement NPN equivalent logic functions. Consider Figure 4.4(a) and Figure 4.4(b) where the first two inputs pins a and b are swapped. The logic function in Figure 4.4(b), denoted by f'', has logic function  $f'' = abc + \overline{a}bc + de$  and is NPN equivalent to f in Figure 4.4(a). In Figure 4.4(c), to absorb the permutation of a and b into LUT  $L_1$ , the configuration bit  $c_1$  of  $L_1$  changes from  $c_1$  to  $c_1''$  ( $c_1'' = 0 \times C0$ ), so as to maintain the same logic function f''. Thus, the configuration bits  $\{c_1'', c_2\}$  can

Figure 4.5: A 6-input topology of LUTs illutrating situations where complementation is not permitted to find essential and redundant bits; (a) Original topology; (b) Complementation not allowed on bridged inputs; (c) Complementation not allowed on internal inputs.

also be skipped during the enumeration of the topology as long as the configuration bits  $\{c_1, c_2\}$  are not skipped. In summary, for the preceding examples,  $c_1'$  and  $c_1''$  are defined as redundant bits for LUT  $L_1$ , while  $c_1$  ( $c_1 = 0$ xA0) is defined as the essential bit of  $c_1'$  ( $c_1' = 0$ x50) and  $c_1''$  ( $c_1'' = 0$ xC0) for LUT  $L_1$ .

The pseudo-code of the enumeration of NPN equivalence classes using essential bits for a given topology is described in Figure 4.6. Numerical results demonstrating the benefits of essential bits in reducing the amount of computational effort required to enumerate topologies of LUTs are presented later in the chapter.

```

Procedure: NPN Equivalence Class Enumeration Using Essential Bits

Inputs: A LUT Topology T

Returns: A Hash Table, H.

1

Enumerate all essential bits for each LUT in the topology T;

2

for each set of essential configuration bits (c_1, c_2, \ldots, c_n) of LUTs in the topology T do

3

Simulate the current logic function f that is implemented by the topology T;

Obtain its NPN equivalence class f_{npn} using a NPN encoder;

4

5

if f_{npn} does not exist in the hash table then

6

Insert f_{npn}, configuration bits, and complementation/permutation information into

7

the hash table;

8

end if

9

end do

10

return H;

```

Figure 4.6: Enumeration of implementable logic functions for a particular topology of LUTs using essential bits

#### 4.4 Practical Bits

The NPN-based approach for Boolean matching is *complete* and guarantees to find a match if it exists, as long as the enumeration of NPN equivalence classes is complete. However, the enumeration of NPN equivalence classes still suffers excessive runtime using essential bits. Based on the practical observation, some values of the configuration bits for certain LUTs rarely show up in practical circuit designs, due to the large flexibility of LUTs. Hence, certain values of the configuration bits can also be skipped, and it further reduces the total amount of simulation and NPN encoding required during the enumeration of the topology to find the implementable functions, at the expense of some implementable functions missed. As a result, the NPN-based Boolean matching approach becomes *incomplete*.

The popularity of a configuration bit refers to the frequency of its appearance in practical circuits. Certain configuration bits are denoted as practical bits when their popularities are above a particular threshold value. To find out appropriate practical bits, the following work is done on a large set of practical circuits. First, all k-feasible (k = 3 or 4) cuts are computed on the AIG of each practical circuit. Next, each k-feasible cut is simulated to determine its implementable logic functions. Obviously, the truth table of the logic function corresponds to the configuration bit of a k-input LUT. Last, all configuration bits of LUTs are collected from the set of practical circuits. The popularity of a particular config-

uration bit is calculated using the number of its appearance divided by the total number of appearance for all configuration bits. The threshold value for picking up practical bits has to be chosen carefully. If the threshold moves up, more configuration bits can be skipped and more possible implementable functions will be missed during enumeration. For the 3-input LUT architecture, the threshold value is set as 0.00%, 0.01%, 0.02%, 0.03%, 0.04% and 0.05% individually. For the 4-input LUT architecture, the threshold value is set as 0.0%, 0.1% and 0.01% individually. The numbers of practical bits whose popularities above different threshold values are shown in the table 4.1 and table 4.2.

Table 4.1: The number of practical bits of 3-input LUTs

| 3-input LUT architecture                       |  |  |  |  |  |  |  |

|------------------------------------------------|--|--|--|--|--|--|--|

| Popularity 0.00% 0.01% 0.02% 0.03% 0.04% 0.05% |  |  |  |  |  |  |  |

| # of Practical Bits 243 126 111 102 93 84      |  |  |  |  |  |  |  |

Table 4.2: The number of practical bits of 4-input LUTs

| 4-input LUT architecture |                  |     |     |  |  |  |

|--------------------------|------------------|-----|-----|--|--|--|

| Popularity               | 0.00% 0.01% 0.1% |     |     |  |  |  |

| # of Practical Bits      | 8376             | 774 | 140 |  |  |  |

It is clear that the use of both essential bits and practical bits can significantly reduce computation time and memory usage further. The practical bits are collected and saved in a data file. During the enumeration for topologies of LUTs, practical bits are loaded into memory. The essential bits for each LUT are enumerated on the basis of its practical bits, instead of all its configuration bits. Hence, less essential bits are necessary to be fed into the following simulation and NPN encoding steps. However, some valuable NPN equivalence classes are possibly missed and it leads to the incomplete Boolean matching. The pseudo-code of the enumeration of NPN equivalence classes using essential bits for a given topology is described in Figure 4.7. The efficacy of practical bits is presented later in the chapter, which shows that the use of practical bits significantly speeds up the simulation and NPN encoding steps, and also results in loss of some NPN equivalence classes.

```

Procedure: NPN Equivalence Class Enumeration Using Essential and Practical Bits

Inputs: A LUT Topology T

Returns: A Hash Table, H.

1

Load the practical bits for the LUTs in the topology;

2