# Design Methodologies and CAD Tools for Leakage Power Optimization in FPGAs

by

#### Hassan Hassan

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Hassan Hassan 2008

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The scaling of the CMOS technology has precipitated an exponential increase in both subthreshold and gate leakage currents in modern VLSI designs. Consequently, the contribution of leakage power to the total chip power dissipation for CMOS designs is increasing rapidly, which is estimated to be 40% for the current technology generations and is expected to exceed 50% by the 65nm CMOS technology. In FPGAs, the power dissipation problem is further aggravated when compared to ASIC designs because FPGA use more transistors per logic function when compared to ASIC designs. Consequently, solving the leakage power problem is pivotal to devising power-aware FPGAs in the nanometer regime. This thesis focuses on devising both architectural and CAD techniques for leakage mitigation in FPGAs. Several CAD and architectural modifications are proposed to reduce the impact of leakage power dissipation on modern FPGAs.

Firstly, multi-threshold CMOS (MTCMOS) techniques are introduced to FP-GAs to permanently turn OFF the unused resources of the FPGA, FPGAs are characterized with low utilization percentages that can reach 60%. Moreover, such architecture enables the dynamic shutting down of the FPGA idle parts, thus reducing the standby leakage significantly. Employing the MTCMOS technique in FPGAs requires several changes to the FPGA architecture, including the placement and routing of the sleep signals and the MTCMOS granularity. On the CAD level, the packing and placement stages are modified to allow the possibility of dynamically turning OFF the idle parts of the FPGA. A new activity generation algorithm is proposed and implemented that aims to identify the logic blocks in a design that exhibit similar idleness periods. Several criteria for the activity generation algorithm are used, including connectivity and logic function. Several versions of the activity generation algorithm are implemented to trade power savings with runtime. A newly developed packing algorithm uses the resulting activities to minimize leakage power dissipation by packing the logic blocks with similar or close activities together. By proposing an FPGA architecture that supports MTCMOS and developing a CAD tool that supports the new architecture, an average power savings of 30% is achieved for a 90nm CMOS process while incurring a speed penalty of less than 5\%. This technique is further extended to provide a timing-sensitive version of the CAD flow to vary the speed penalty according to the criticality of each logic block.

Secondly, a new technique for leakage power reduction in FPGAs based on the use of input dependency is developed. Both subthreshold and gate leakage power

are heavily dependent on the input state. In FPGAs, the effect of input dependency is exacerbated due to the use of pass-transistor multiplexer logic, which can exhibit up to 50% variation in leakage power due to the input states. In this thesis, a new algorithm is proposed that uses bit permutation to reduce subthreshold and gate leakage power dissipation in FPGAs. The bit permutation algorithm provides an average leakage power reduction of 40% while having less than 2% impact on the performance and no penalty on the design area.

Thirdly, an accurate probabilistic power model for FPGAs is developed to quantify the savings from the proposed leakage power reduction techniques. The proposed power model accounts for dynamic, short circuit, and leakage power (including both subthreshold and gate leakage power) dissipation in FPGAs. Moreover, the power model accounts for power due to glitches, which accounts for almost 20% of the dynamic power dissipation in FPGAs. The use of probabilities in the power model makes it more computationally efficient than the other FPGA power models in the literature that rely on long input sequence simulations. One of the main advantages of the proposed power model is the incorporation of spatial correlation while estimating the signal probability. Other probabilistic FPGA power models assume spatial independence among the design signals, thus overestimating the power calculations. In the proposed model, a probabilistic model is proposed for spatial correlations among the design signals. Moreover, a different variation is proposed that manages to capture most of the spatial correlations with minimum impact on runtime. Furthermore, the proposed power model accounts for the input dependency of subthreshold and gate leakage power dissipation. By comparing the proposed power model to HSpice simulation, the estimated power is within 8% and is closer to HSpice simulations than other probabilistic FPGA power models by an average of 20%.

#### Acknowledgements

I would like to express my sincere gratitude to my supervisors Prof. Mohamed Elmasry and Dr. Mohab Anis for their guidance and expertise. Without their knowledge and support, this work would not have been possible. I would also like to thank Prof. Farid Najm, Prof. Anthony Vannelli, Prof. Catherine Gebotys, and Prof. John Vanderkooy for reviewing this work as well as their valuable comments to make the thesis come out in this current form.

I am also grateful to Prof. Andrew Kennings who first introduced me to FPGA CAD design in the ECE647, which was one of the most interesting courses I attended during my study at Waterloo. I am thankful to Prof. James Barby, whose guidelines in teaching and course management will always be in mind if I ever get the chance to teach a course in the future.

I have been fortunate to work with many wonderful people in the VLSI research group in the University of Waterloo. I am thankful to all of them for their time and ideas that made this work more productive and my time spent at Waterloo memorable. I always remember the funny as well as informative discussions I used to have with some of my friends in the lab, including Ayman Hassan, Mohamed Abu Rahma, and Mohamed Elsaid. During my PhD studies in the University of Waterloo, I interacted with a wide group of interesting people that will always be my friends, including, Mohamed El-Abd, Shady Hassan, and Hatem Elbehiry.

I would like to thank Dr. Nizar Abdallah and Dr. Julien Dunoyer of Actel Corp. for their valuable discussion and support during my visit to Actel headquarters in 2007.

Moreover, I would like to express my deepest gratitude to my parents for going through so much in supporting my academic choices, even though it meant being away from them. Finally, I am deeply thankful to my wife who joined and supported me in the final and rough stages of this journey. I really appreciate her support during my defense exam.

# Contents

| Li | ist of Tables x |          |                                      |     |  |

|----|-----------------|----------|--------------------------------------|-----|--|

| Li | st of           | Figure   | es ·                                 | xii |  |

| Li | st of           | Algori   | thms                                 | xvi |  |

| 1  | Intr            | oduction | on                                   | 1   |  |

|    | 1.1             | Motiva   | ation                                | 1   |  |

|    | 1.2             | Thesis   | Contributions                        | 2   |  |

|    | 1.3             | Thesis   | Organization                         | 3   |  |

| 2  | FP              | GA Ove   | erview: Architecture and CAD         | 4   |  |

|    | 2.1             | Introdu  | uction                               | 4   |  |

|    | 2.2             | FPGA     | Logic Resources Architecture         | 5   |  |

|    |                 | 2.2.1    | Altera Stratix III Logic Resources   | 6   |  |

|    |                 | 2.2.2    | Xilinx Virtex-5 Logic Resources      | 6   |  |

|    |                 | 2.2.3    | Actel ProASIC3/IGLOO Logic Resources | 8   |  |

|    | 2.3             | FPGA     | Routing Resources Architecture       | 8   |  |

|    | 2.4             | CAD fo   | for FPGAs                            | 9   |  |

|    |                 | 2.4.1    | Logic Synthesis                      | 10  |  |

|    |                 | 2.4.2    | Packing                              | 10  |  |

|    |                 | 2.4.3    | Placement                            | 11  |  |

|    |                 | 2.4.4    | Timing Analysis                      | 12  |  |

|   |     | 2.4.5   | Routing                                                        | 13 |

|---|-----|---------|----------------------------------------------------------------|----|

|   | 2.5 | Versat  | ile Place and Route (VPR) CAD Tool                             | 13 |

|   |     | 2.5.1   | VPR Architectural Assumptions                                  | 14 |

|   |     |         | 2.5.1.1 VPR Logic Architecture                                 | 14 |

|   |     |         | 2.5.1.2 VPR Routing Resources Architecture                     | 15 |

|   |     | 2.5.2   | Basic Logic Packing Algorithm: VPack                           | 17 |

|   |     | 2.5.3   | Timing-Driven Logic Block Packing: T-VPack                     | 19 |

|   |     | 2.5.4   | Placement: VPR                                                 | 20 |

|   |     | 2.5.5   | Routing: VPR                                                   | 22 |

|   |     |         | 2.5.5.1 Routability-Driven Router                              | 22 |

| 3 | Lea | kage P  | Power in Modern FPGAs                                          | 23 |

|   | 3.1 | Dynan   | nic Power Reduction Techniques in FPGAs                        | 23 |

|   | 3.2 | CMOS    | S Technology Scaling Trends and Leakage Power in VLSI Circuits | 24 |

|   | 3.3 | CMOS    | S Devices Leakage Mechanisms                                   | 27 |

|   | 3.4 | Currer  | nt Situation of Leakage Power in Nanometer FPGAs               | 28 |

|   | 3.5 | Leakag  | ge Power Reduction Techniques in FPGAs                         | 29 |

|   |     | 3.5.1   | Leakage Power Reduction in the Logic Blocks                    | 29 |

|   |     | 3.5.2   | Leakage Power Reduction in Routing Circuitry                   | 31 |

|   | 3.6 | Power   | Reduction Techniques in Commercial FPGAs                       | 33 |

|   |     | 3.6.1   | Altera Stratix III Power Reduction Techniques                  | 33 |

|   |     | 3.6.2   | Xilinx Virtex-5 Power Reduction Techniques                     | 34 |

|   |     | 3.6.3   | Actel IGLOO Power Reduction Techniques                         | 34 |

| 4 | Pow | ver Est | imation in FPGAs                                               | 35 |

|   | 4.1 | Introd  | uction                                                         | 36 |

|   | 4.2 | Power   | Estimation in VLSI: An Overview                                | 37 |

|   |     | 4.2.1   | Simulation-Based Power Estimation Techniques                   | 37 |

|   |     | 4.2.2   | Probabilistic-Based Power Estimation Techniques                | 39 |

|   | 4.3   | A Sur                    | vey of FP  | GA Power Estimation Techniques                                              | 41       |  |  |  |

|---|-------|--------------------------|------------|-----------------------------------------------------------------------------|----------|--|--|--|

|   |       | 4.3.1                    | Commer     | cial FPGA Power Estimation Techniques                                       | 44       |  |  |  |

|   |       |                          | 4.3.1.1    | Spreadsheet Power Estimation Tools                                          | 44       |  |  |  |

|   |       |                          | 4.3.1.2    | CAD Power Estimation Tools                                                  | 45       |  |  |  |

|   | 4.4   | Spatia                   | l Correlat | ion and Signal Probabilities Calculations                                   | 45       |  |  |  |

|   | 4.5   | Explo                    | ration Ph  | ase: Locating Spatial Correlation                                           | 46       |  |  |  |

|   | 4.6   | Propos                   | sed Signa  | l Probabilities Calculation Algorithm Under Spatial                         |          |  |  |  |

|   |       | Correl                   | ation      |                                                                             | 47       |  |  |  |

|   | 4.7   | Power                    | Calculati  | ons due to Glitches                                                         | 51       |  |  |  |

|   | 4.8   | Signal                   | Probabil   | ities and Power Dissipation                                                 | 52       |  |  |  |

|   |       | 4.8.1                    | Dynamic    | Power Dissipation                                                           | 53       |  |  |  |

|   |       | 4.8.2                    | Leakage    | Power Dissipation                                                           | 54       |  |  |  |

|   |       | 4.8.3                    | Gate Lea   | akage Power Dissipation                                                     | 56       |  |  |  |

|   | 4.9   | Result                   | s and Dis  | cussions                                                                    | 56       |  |  |  |

|   | 4.10  | Conclu                   | usion      |                                                                             | 65       |  |  |  |

| 5 | L.pal | kaga P                   | ower Re    | duction in FPGAs Using MTCMOS Techniques                                    | 66       |  |  |  |

| J | 5.1   | Ü                        |            |                                                                             | 66       |  |  |  |

|   | 5.2   | MTCMOS FPGA Architecture |            |                                                                             |          |  |  |  |

|   | 5.3   |                          |            |                                                                             |          |  |  |  |

|   | 0.0   | -                        |            | ansistor Sizing                                                             | 72<br>72 |  |  |  |

|   |       | 5.3.2                    |            | y Exclusive Discharge Current Processing                                    | 75       |  |  |  |

|   |       | 5.3.3                    | ·          | ased Discharge Current Processing                                           | 76       |  |  |  |

|   |       | 5.3.4                    | _          | ical Sorting and Discharge Current Addition                                 | 77       |  |  |  |

|   | 5.4   |                          |            | Generation                                                                  | 80       |  |  |  |

|   | 0.4   |                          | v          |                                                                             |          |  |  |  |

|   |       | 5.4.1                    |            | ion-based Activity Profile Generation Algorithm (CAP)                       | 82       |  |  |  |

|   |       | 5.4.2                    |            | sed Activity Profile (LAP) Generation                                       | 86       |  |  |  |

|   |       |                          | 5.4.2.1    | Activity Vectors                                                            | 86       |  |  |  |

|   |       |                          | 5.4.2.2    | Hamming Distance: A Measure of the Correlation<br>Between Activity Profiles | 88       |  |  |  |

|   |             |        | 5.4.2.3    | The LAP Algorithm Operation                                 | 89       |

|---|-------------|--------|------------|-------------------------------------------------------------|----------|

|   |             |        | 5.4.2.4    | Reverse Logic Activity Profile (R-LAP) Generation Algorithm | 91       |

|   | 5.5         | Activi | ty Packin  | g Algorithms                                                | 93       |

|   |             | 5.5.1  | Activity   | T-VPack (AT-VPack)                                          | 93       |

|   |             | 5.5.2  | Force-ba   | ased Activity T-VPack (FAT-VPack)                           | 95       |

|   |             | 5.5.3  | Timing-    | Driven MTCMOS (T-MTCMOS) AT-VPack                           | 96       |

|   | 5.6         | Power  | Estimati   | on                                                          | 97       |

|   | 5.7         | Result | ts and Dis | scussions                                                   | 98       |

|   |             | 5.7.1  | Experim    | nental Setup                                                | 99       |

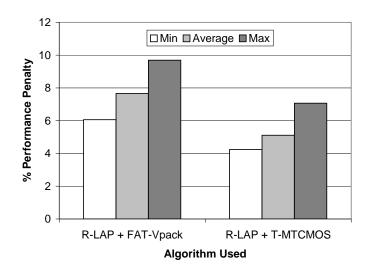

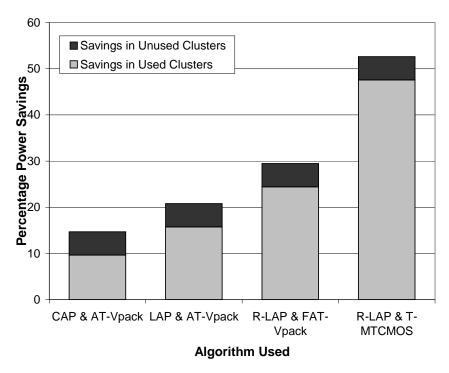

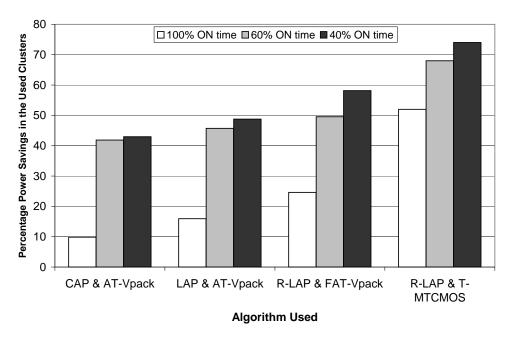

|   |             | 5.7.2  | Algorith   | ams Comparison                                              | 100      |

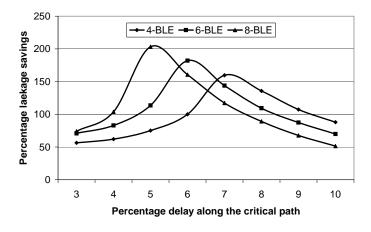

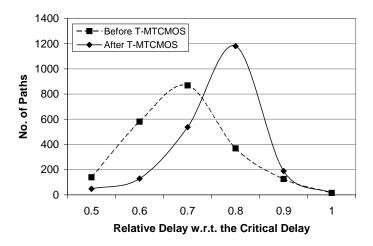

|   |             | 5.7.3  | Impact     | of Activity Packing on Performance                          | 101      |

|   |             | 5.7.4  | Leakage    | Savings Breakdown                                           | 104      |

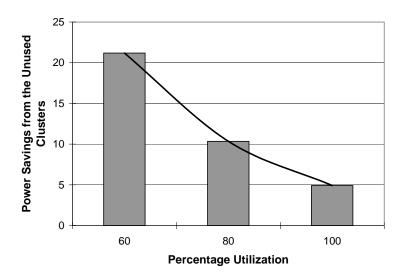

|   |             | 5.7.5  | Impact of  | of Utilization and ON Time on Leakage Savings               | 105      |

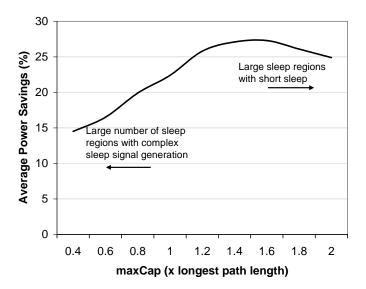

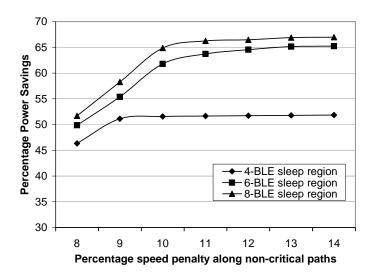

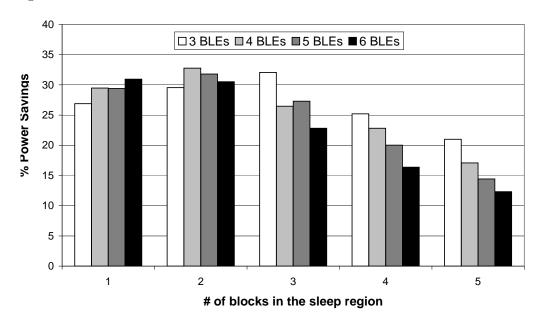

|   |             | 5.7.6  | Impact of  | of the Sleep Region Size                                    | 107      |

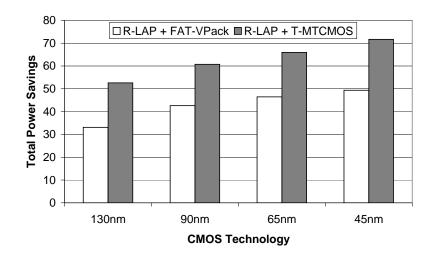

|   |             | 5.7.7  | Scalabili  | ity of the Proposed Algorithms with Technology Scaling      | g107     |

|   | 5.8         | Concl  | usions .   |                                                             | 108      |

| 0 | т .         |        |            |                                                             |          |

| 6 | Lea<br>ing  | kage P | ower Re    | eduction in FPGAs Through Input Pin Reorder-                | -<br>109 |

|   |             | Leaka  | ge Power   | and Input State Dependency in FPGAs                         | 110      |

|   |             | 6.1.1  |            | shold Leakage Current                                       |          |

|   |             |        | 6.1.1.1    | Drain Induced Barrier Lowering (DIBL)                       |          |

|   |             |        | 6.1.1.2    | Body Effect                                                 |          |

|   |             | 6.1.2  |            | akage                                                       | 113      |

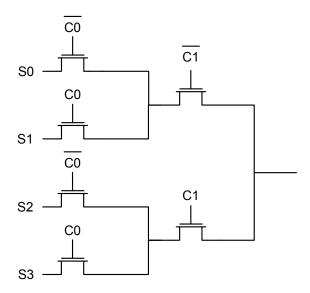

|   |             | 6.1.3  |            | akage States in Pass-Transistor Multiplexers                | 113      |

|   |             | 6.1.4  |            | Power in Inverters/Buffers                                  | 115      |

|   | 6.2         |        |            | Pin Reordering Algorithm                                    |          |

|   | J. <b>2</b> | 6.2.1  |            | in Reordering (LPR) Algorithm                               |          |

|   |             | 0.2.1  |            |                                                             | * * 1    |

|    |       |         | 6.2.1.1   | Input Pins Padding                      | 117 |

|----|-------|---------|-----------|-----------------------------------------|-----|

|    |       |         | 6.2.1.2   | Input Pins Swapping                     | 117 |

|    |       |         | 6.2.1.3   | Most Probable States                    | 119 |

|    |       |         | 6.2.1.4   | Unutilized Logic Resources              | 120 |

|    |       | 6.2.2   | Routing   | Switches Pin Reordering (RPR) Algorithm | 121 |

|    |       |         | 6.2.2.1   | Input Pins Padding                      | 121 |

|    |       |         | 6.2.2.2   | Most Probable States                    | 121 |

|    |       |         | 6.2.2.3   | Unutilized Routing Resources            | 122 |

|    | 6.3   | Exper   | imental F | Results                                 | 122 |

|    |       | 6.3.1   | Pin Reo   | rdering and Performance                 | 124 |

|    |       | 6.3.2   | Pin Reo   | rdering and Technology Scaling          | 126 |

|    | 6.4   | Concl   | usion     |                                         | 126 |

| 7  | Cor   | ıclusio | ns and H  | Suture Work                             | 129 |

|    | 7.1   |         |           |                                         |     |

|    | 7.2   |         |           |                                         |     |

|    |       |         |           |                                         |     |

| Bi | bliog | graphy  | •         |                                         | 132 |

# List of Tables

| 2.1 | VPR temperature update schedule [28]                                                                       | 21  |

|-----|------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Constant field scaling of the CMOS process                                                                 | 26  |

| 3.2 | FPGA leakage power for typical designs and design-dependent variations [48]                                | 28  |

| 4.1 | Relative error in the switching activity from the proposed algorithm when compared to [92]                 | 58  |

| 4.2 | Relative error in the switching activity from the proposed algorithm when compared to [92]                 | 58  |

| 4.3 | Small benchmark circuits                                                                                   | 59  |

| 4.4 | Percentage change in power estimation under spatial correlation when compared to spatial independence      | 62  |

| 5.1 | Leakage power Savings for the different activity profile packing algorithms across several FPGA benchmarks | 100 |

| 6.1 | Leakage current in a minimum-sized inverter                                                                | 115 |

| 6.2 | Leakage savings by the proposed pin reordering algorithm across several FPGA benchmarks                    | 123 |

# List of Figures

| 2.1  | Modern FPGA fabric                                                                                                                                                                  | 5  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Altera's Stratix III ALM architecture [10]                                                                                                                                          | 7  |

| 2.3  | Xilinx's Vertex-5 slice architecture [11]                                                                                                                                           | 7  |

| 2.4  | Actel's ProASIC3/IGLOO VersaTile architecture [12]                                                                                                                                  | 8  |

| 2.5  | Routing resources in island-style FPGAs                                                                                                                                             | 9  |

| 2.6  | A typical FPGA CAD flow                                                                                                                                                             | 10 |

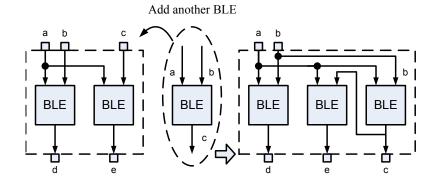

| 2.7  | An example of packing                                                                                                                                                               | 11 |

| 2.8  | Building blocks of SRAM programmable FPGAs used by VPR. $$                                                                                                                          | 14 |

| 2.9  | VPR BLE architecture                                                                                                                                                                | 15 |

| 2.10 | VPR logic cluster architecture                                                                                                                                                      | 15 |

| 2.11 | VPR FPGA routing architecture. $chan\_width\_x = 1$ , $chan\_width\_y = 1$ , $chan\_width\_io = 0.5$ , $io\_rat = 2$ , $F_{c,input} = 3$ , $F_{c,output} = 1$ , and $F_{c,pad} = 2$ | 16 |

| 2.12 | Switch topologies supported by VPR                                                                                                                                                  | 17 |

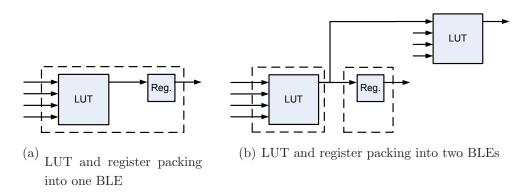

| 2.13 | Packing LUTs and registers into BLEs [28]                                                                                                                                           | 19 |

| 2.14 | Adding a BLE to a cluster can decrease the number of used cluster                                                                                                                   |    |

|      | inputs [28]                                                                                                                                                                         | 20 |

| 2.15 | FPGA model assumed by the VPR placer                                                                                                                                                | 21 |

| 3.1  | Gate length scaling of CMOS technologies [1]                                                                                                                                        | 25 |

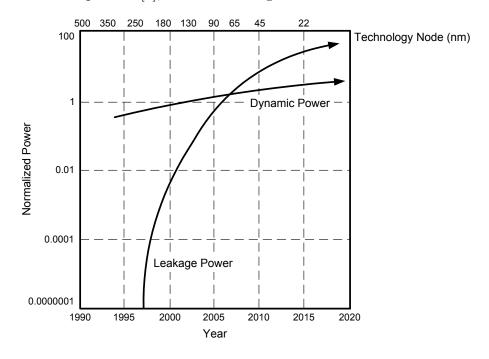

| 3.2  | Leakage power contribution to the total chip power [1]                                                                                                                              | 26 |

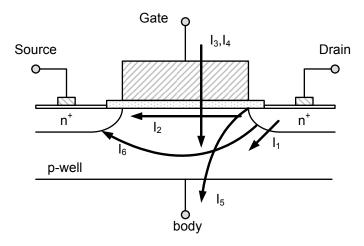

| 3.3  | Leakage current mechanisms of deep submicron devices [46]                                                                                                                           | 27 |

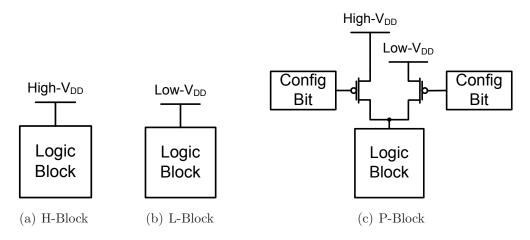

| 3.4  | $V_{DD}$ programmable low-power FPGA resources [49]                                                                                                                                 | 30 |

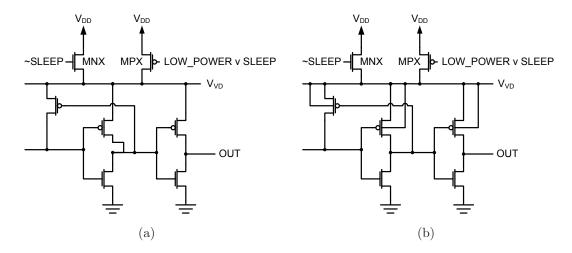

| 3.5  | Programmable low-power routing switches [58]                                                                                                       | 32 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | A circuit that exhibits spatial correlation through reconvergent paths.                                                                            | 46 |

| 4.2  | A graph representation of the circuit in Figure 4.1                                                                                                | 47 |

| 4.3  | A circuit that exhibits spatial correlation                                                                                                        | 49 |

| 4.4  | A 2:1 pass transistor logic multiplexer                                                                                                            | 54 |

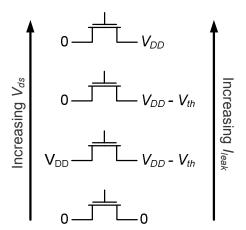

| 4.5  | $\label{eq:decomposition} \mbox{DIBL impact on subthreshold leakage in FPGA pass transistor devices.}$                                             | 55 |

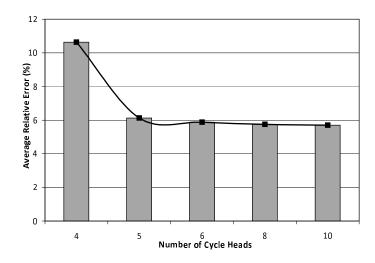

| 4.6  | Average relative error in estimating the signal probabilities under spatial correlation by varying the number of cycles considered                 | 59 |

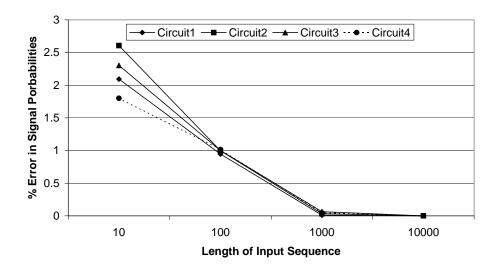

| 4.7  | Percentage error in estimating the signal probabilities under spatial correlation when compared to HSpice versus the length of the input sequence. | 60 |

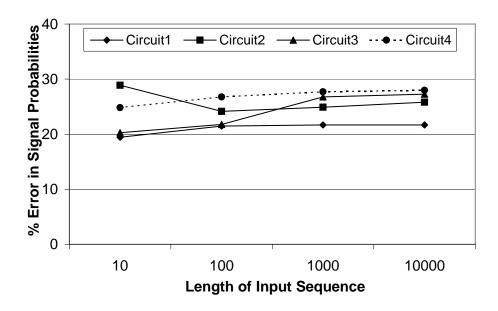

| 4.8  | Percentage error in estimating the signal probabilities under spatial independence when compared to HSpice versus the length of the input sequence | 61 |

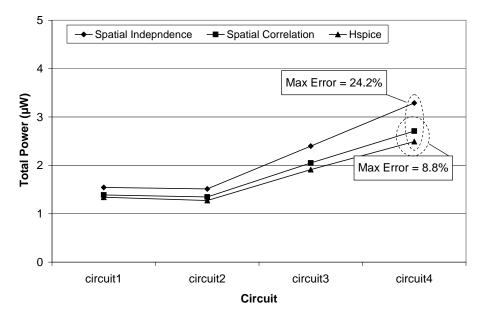

| 4.9  | Percentage error between power estimated with and without spatial correlation when compared to HSpice                                              | 61 |

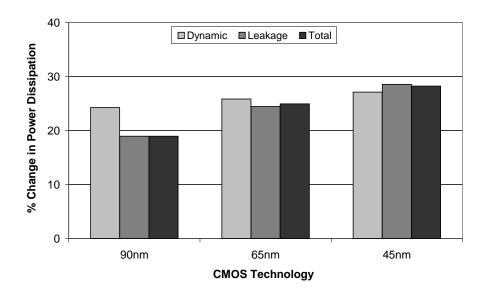

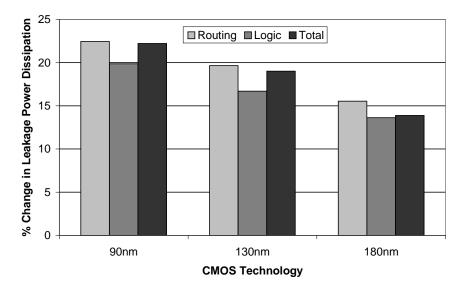

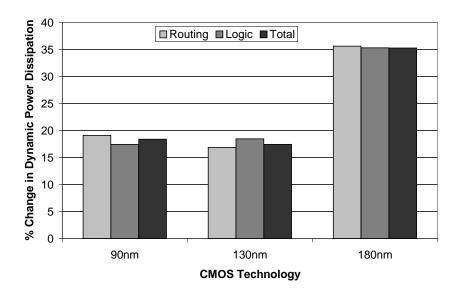

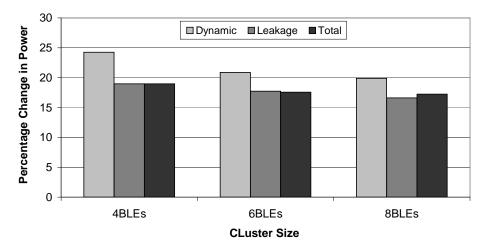

| 4.10 | Average percentage change in power dissipation to account for spatial correlation for different technology nodes                                   | 64 |

| 4.11 | Average percentage change in leakage power dissipation with and without spatial correlation for different technology node                          | 64 |

| 4.12 | Average percentage change in dynamic power dissipation with and without spatial correlation for different technology node                          | 65 |

| 4.13 | Percentage change in power dissipation between spatial correlation and independence versus the cluster size                                        | 65 |

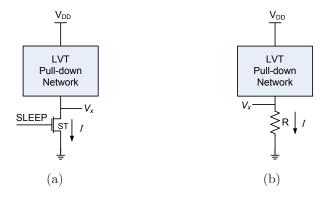

| 5.1  | MTCMOS architecture. (a) General MTCMOS architecture, (b) Equivalent ST circuit in the active mode                                                 | 67 |

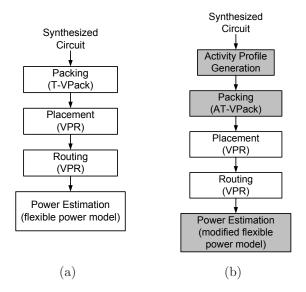

| 5.2  | FPGA CAD flowchart. (a) Conventional VPR flowchart. (b) Proposed CAD flowchart integrated in the VPR flow                                          | 68 |

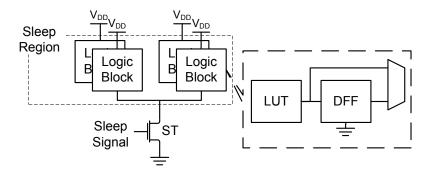

| 5.3  | MTCMOS FPGA architecture. The logic blocks connected to one sleep transistor are called sleep region                                               | 69 |

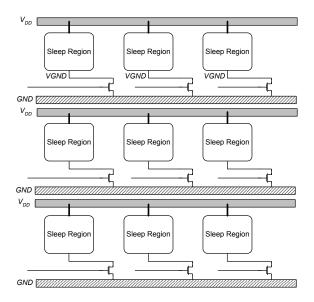

| 5.4  | MTCMOS-based FPGA fabric with sleep transistors                                                                                                    | 71 |

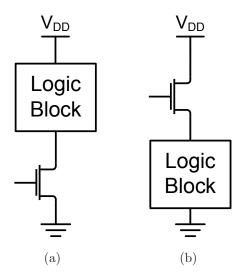

| 5.5  | Sleep transistor implementations. (a) NMOS footer. (b) PMOS header                                                                                                                                                                                                                                                          | 71  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

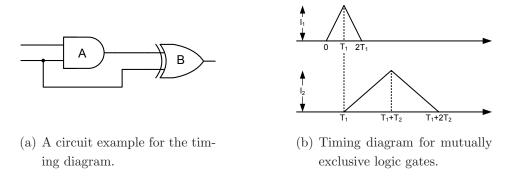

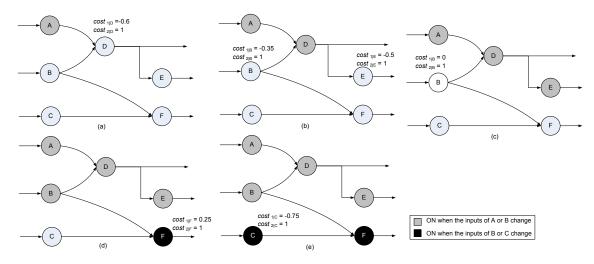

| 5.6  | Mutually exclusive discharge current processing                                                                                                                                                                                                                                                                             | 75  |

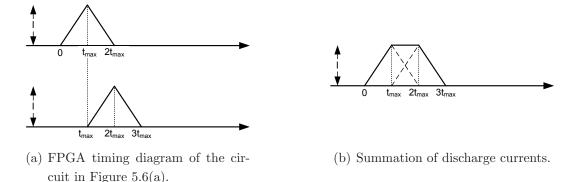

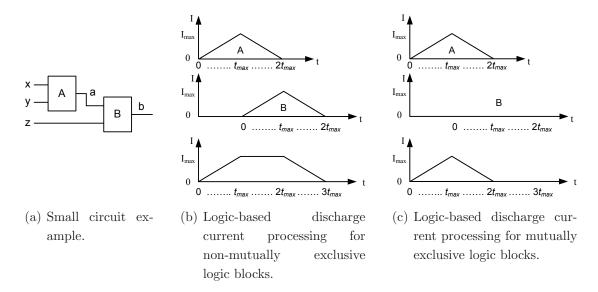

| 5.7  | Mutually exclusive discharge current processing                                                                                                                                                                                                                                                                             | 76  |

| 5.8  | Linear vector approximation of discharge current and logic-based current vectors summation                                                                                                                                                                                                                                  | 77  |

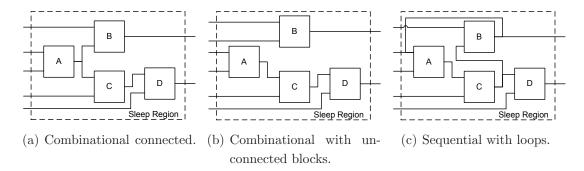

| 5.9  | Different types of sleep regions                                                                                                                                                                                                                                                                                            | 78  |

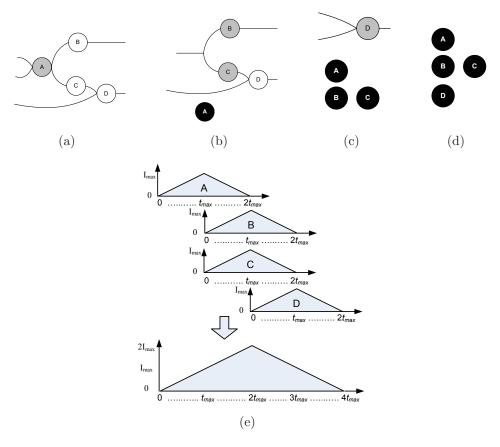

| 5.10 | Steps of the current feasibility check for a combinational connected sleep region. (a) A is selected to be deleted, (b) A is ordered in the first position and B and C are selected for deletion, (c) B and C are ordered in the same position, (d) Final ordering, (e) Current vectors summation                           | 79  |

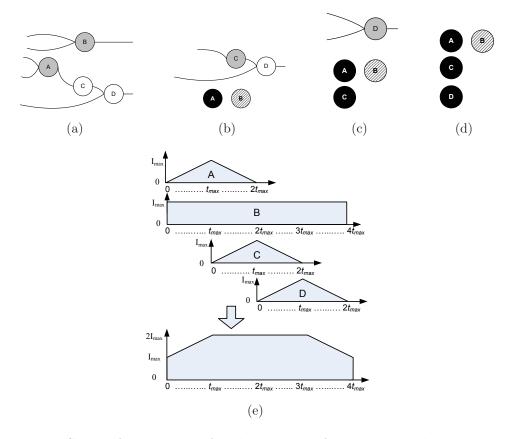

| 5.11 | Steps of the current feasibility check for a sequential connected sleep region. (a) Both A and B are selected for deletion, (b) A and B are ordered on the same position, with B an unconnected node and C is marked for deletion, (c) C is ordered in the next position, (d) Final ordering, (e) Current vectors summation | 80  |

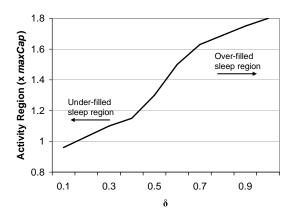

| 5.12 | Leakage power savings vs the maximum activity region capacity                                                                                                                                                                                                                                                               | 84  |

| 5.13 | Average activity region size across several benchmarks vs. $\delta.$                                                                                                                                                                                                                                                        | 85  |

| 5.14 | CAP activity generation flow for $maxCap = 4$ and $\delta = 0.2$                                                                                                                                                                                                                                                            | 85  |

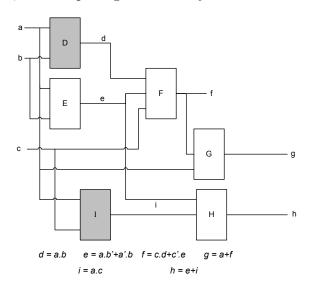

| 5.15 | A circuit example.                                                                                                                                                                                                                                                                                                          | 87  |

| 5.16 | Speed penalty experienced in the different benchmarks due to the use of sleep transistors                                                                                                                                                                                                                                   | 102 |

| 5.17 | 's298' leakage savings vs maximum speed penalty for the R-LAP and T-MTCMOS combination                                                                                                                                                                                                                                      | 103 |

| 5.18 | 's298' leakage savings vs minimum speed penalty for the R-LAP and T-MTCMOS combination                                                                                                                                                                                                                                      | 103 |

| 5.19 | Critical path distribution for timing-driven MTCMOS designs                                                                                                                                                                                                                                                                 | 104 |

| 5.20 | Leakage power savings breakdown                                                                                                                                                                                                                                                                                             | 105 |

| 5.21 | Percentage savings in power for different FPGA fabric utilizations using the combination of R-LAP and T-MTCMOS                                                                                                                                                                                                              | 106 |

| 5.22 | Percentage savings in power for different utilizations and operational |     |

|------|------------------------------------------------------------------------|-----|

|      | time using the combination of R-LAP and T-MTCMOS                       | 106 |

| 5.23 | Impact of the sleep region size on the leakage savings                 | 107 |

| 5.24 | Impact of technology scaling on power savings                          | 108 |

| 6.1  | DIBL effect in a 90nm CMOS process                                     | 112 |

| 6.2  | DIBL impact on subthreshold leakage in FPGA pass-transistor devices.   | 112 |

| 6.3  | Gate leakage dominant states in FPGA pass-transistor devices           | 113 |

| 6.4  | Total leakage dominant states in FPGA pass-transistor devices          | 114 |

| 6.5  | Inputs to pass-transistors pairs                                       | 114 |

| 6.6  | Gate leakage dominant states in FPGA pass-transistor devices           | 116 |

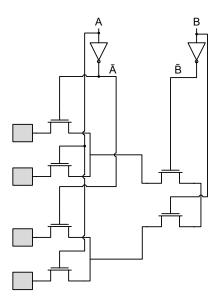

| 6.7  | VPR CAD flow with the proposed pin reordering algorithms               | 116 |

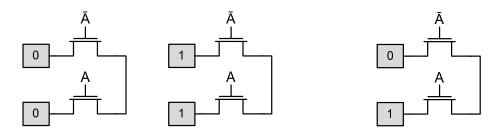

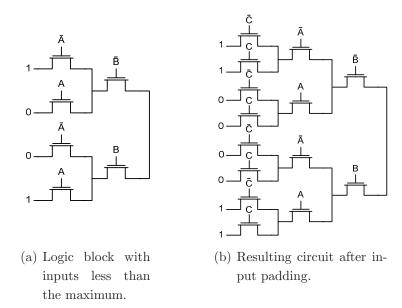

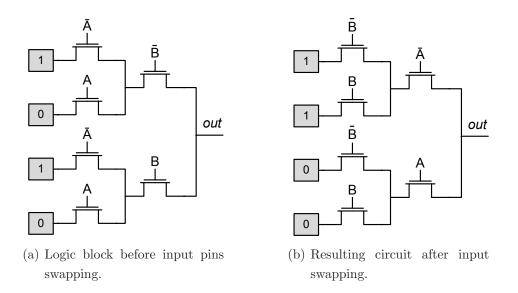

| 6.8  | Input padding for logic blocks with inputs less than the maximum.      | 118 |

| 6.9  | Input pin swapping for logic blocks to minimize leakage power dissi-   | 110 |

|      | pation                                                                 | 119 |

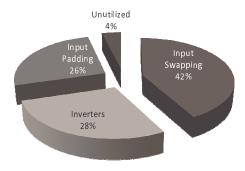

| 6.10 | Leakage savings breakdown in logic blocks                              | 123 |

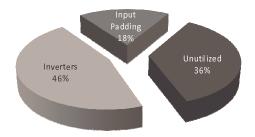

| 6.11 | Leakage savings breakdown in the routing resources                     | 124 |

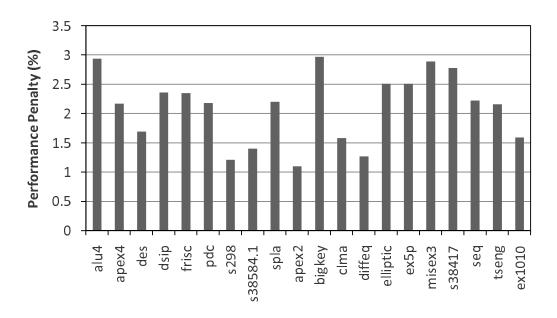

| 6.12 | Performance penalty due to the proposed algorithm                      | 125 |

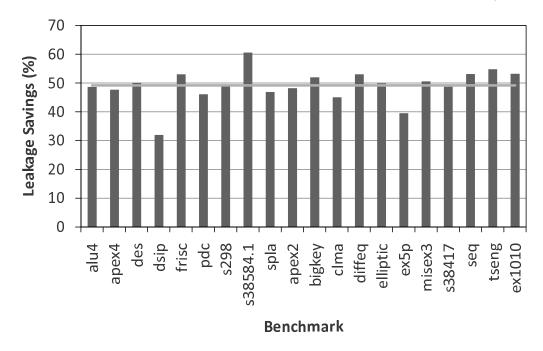

| 6.13 | Leakage savings to avoid affecting the performance                     | 125 |

| 6.14 | Trading leakage savings to reduce critical path delay in RCP           | 127 |

| 6.15 | Leakage current vs. technology                                         | 128 |

| 6.16 | Total leakage dominant states in FPGA pass transistor devices.         | 128 |

# List of Algorithms

| 2.1 | SA generic placer pseudocode                                         | 12 |

|-----|----------------------------------------------------------------------|----|

| 2.2 | VPack pseudocode [28]                                                | 18 |

| 4.1 | The exploration phase pseudocode used to identify reconvergent paths |    |

|     | in a circuit                                                         | 48 |

| 4.2 | Probabilities calculation under spatial correlation algorithm        | 50 |

| 5.1 | Pseudocode of the proposed logic-based discharge current processing  |    |

|     | algorithm                                                            | 81 |

| 5.2 | Pseudocode of the proposed CAP algorithm                             | 86 |

| 5.3 | Pseudocode of LAP                                                    | 91 |

| 5.4 | Pseudocode of the proposed R-LAP                                     | 93 |

| 5.5 | Pseudocode for the AT-VPACK algorithm                                | 95 |

## Chapter 1

### Introduction

#### 1.1 Motivation

Fueled by the increase in functionality and size of modern Field Programmable Gate Arrays (FPGAs), the market for FPGAs has witnessed a notable expansion in the past few years. This increase in demand has pushed FPGA vendors to design modern FPGAs using state-of-the-art CMOS technologies. Consequently, modern FPGAs suffer greatly from the deep submicron issues that affected the ASIC industry earlier along the technology scaling road. The biggest deep submicron challenge that hurdles further expansions of the use of FPGAs in the VLSI industry is leakage power dissipation. In order for FPGAs to continue competing with the ASIC industry, FPGA vendors must tackle this issue using architectural and/or CAD techniques.

The continuous scaling of the CMOS process has attracted FPGA vendors to integrate more and more devices on the same chip to increase the chip functionality. As a result, the power dissipation of modern FPGAs increased significantly. Much of this increase in power dissipation is attributed to the increase in leakage power dissipation which is expected to exceed 50% of the FPGA power dissipation as modern FPGAs start using the 65nm CMOS process [1]. In addition, the excessive scaling of the MOS gate oxide thickness  $t_{ox}$  resulted in a significant increase in the gate oxide tunneling current, thus exacerbating the leakage problem. In recent experiments, it was found that both the subthreshold and gate leakage power dissipation increase by about 5X and 30X, respectively, across successive technology generations [2].

Traditionally, FPGA vendors were concerned with performance and area opti-

mization to reduce the gap between FPGAs and ASIC designs. In the past few years, a shift in the industry towards power optimization has been witnessed as new power efficient FPGAs are introduced to the market. However, these power efficient FPGAs are mainly concerned with dynamic power reduction. With the expected dominance of leakage power dissipation, FPGA vendors are starting to move towards developing low-leakage FPGA devices.

#### 1.2 Thesis Contributions

This thesis will provide several CAD and architectural modifications to FPGA designs to reduce the impact of leakage power dissipation on modern FPGAs.

Leakage reduction techniques have been applied in ASIC designs for the past few years. One of the most successful techniques is the use of Multi-threshold CMOS (MTCMOS). MTCMOS employs a high threshold voltage  $V_{th}$  (HVT) device, called sleep transistor (ST), in a circuit that is made of low- $V_{th}$  devices (LVT). Hence, the design benefits from the high performance of the LVT devices and the reduced leakage power dissipation of the HVT device. In this thesis, MTCMOS techniques will be employed in FPGAs for leakage power reduction. Moreover, this architecture will enable shutting down the unused or idle parts of the FPGA, thus reducing their standby leakage significantly. Employing this technique in FPGAs requires several changes to the FPGA architecture, including the placement of the sleep transistors; location and connections to the sleep transistors, as well as the CAD design flow. The packing and placement stages of the CAD flow will be changed to reflect the addition of the sleep transistor and allow the possibility of turning OFF the idle parts of the FPGA. Furthermore, a new step is added in the CAD flow to identify the logic blocks that share common idleness periods so they can be collectively turned OFF during their idle periods.

Leakage power is characterized by being significantly state dependent. Depending on the input vector, the leakage power dissipation can vary by about 50%. In this thesis, a new methodology for leakage power optimization in FPGAs is proposed that depends on the state dependency of leakage power. By varying the order of the inputs to the logic blocks, the logic block leakage power is noticeably reduced. Moreover, the algorithm changes the deign configuration to put the FPGA components in the lowest leakage power mode.

In order to measure the leakage power savings from the proposed power optimization techniques, a newly proposed accurate power model for FPGAs is explained in this thesis. The power model takes into consideration the spatial correlation among the design signals. In addition, the power model developed is very flexible in terms of being able to estimate power dissipation in different FPGA architectures.

#### 1.3 Thesis Organization

This thesis is organized as follows: an overview of the architecture; logic and routing architecture, and CAD flow of FPGAs is presented in Chapter 2. Chapter 3 discusses the current status of leakage power dissipation in modern FPGAs as well as some of the methods proposed in the literature to address power dissipation in FPGAs. Chapter 4 presents the newly proposed accurate power modeling technique for FPGAs. The proposed MTCMOS implementation of FPGAs is discussed in Chapter 5. The input reordering leakage power minimization methodology is proposed in Chapter 6. Finally, this thesis is concluded in Chapter 7 and possible future work is discussed.

## Chapter 2

# FPGA Overview: Architecture and CAD

#### 2.1 Introduction

Fueled by the increase in the time-to-market pressures, the rise in ASIC mask and development costs, and increase in the Field Programmable Gate Arrays (FP-GAs) performance and system-level features, more and more traditionally ASIC designers are migrating their designs to programmable logic devices. Moreover, programmable logic devices progressed both in terms of resources and performance. The latest FPGAs have come to provide platform solutions that are easily customizable for system connectivity, *Digital Signal Processing* (DSP), and/or data processing applications. These platform building tools accelerate the time-to-market by automating the system definition and integration phases of the *System on Programmable Chip* (SoPC) development.

The market of programmable logic devices is dominated by two main products; FPGAs and Complex Programmable Logic Devices (CPLDs). FPGAs mostly employ a look-up table approach to implement logic functions, while CPLDs use sum-of-products for logic implementation. Recently, FPGA vendors provided a comprehensive alternative to FPGAs for large volume demands called *structured ASICs* [3, 4]. Structured ASICs offer a complete solution from prototype to high-volume production, and maintain the powerful features and high-performance architecture of their equivalent FPGAs with the programmability removed. Structured ASIC solutions not only provide performance improvement, but also result in significant high-volume cost reduction over FPGAs.

FPGAs consist of programmable logic resources embedded in a sea of programmable interconnects. The programmable logic resources can be configured to implement any logic function, while the interconnects provide the flexibility to connect any signal in the design to any logic resource. The programming technology for the logic and interconnect resources can be Static Random Access Memory (SRAM), flash memory [5], or antifuse [6,7]. SRAM-based FPGAs offer in-circuit reconfigurability at the expense of being volatile, while antifuse are write-once devices. Flash-based FPGAs provide an intermediate alternative by providing reconfigurability as well as non-volatility. The most popular programming technology in state-of-the-art FPGAs is SRAM.

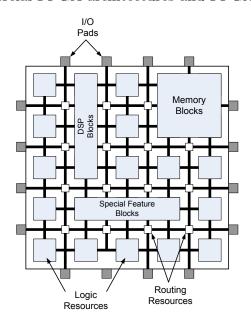

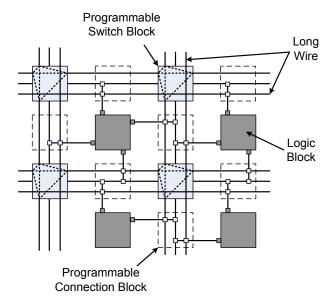

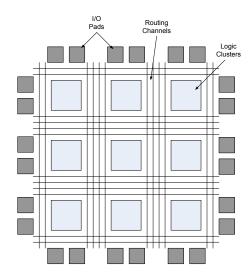

Traditionally, FPGAs consist of input/output pads, logic resources, and routing resources. However, state-of-the-art FPGAs usually include embedded memory, DSP blocks, *Phase-Locked Loops* (PLLs), embedded processors, and other special feature blocks, as shown in Figure 2.1. These features allowed FPGAs to be an attractive alternative for some SoPC designs. The next Sections shed light on some of the available commercial FPGA architectures and FPGA CAD flow.

Figure 2.1: Modern FPGA fabric.

#### 2.2 FPGA Logic Resources Architecture

The logic blocks in FPGAs are responsible for implementing the functionality needed by each application. Increasing the functional capability of the logic blocks increases the number of logic functions that can be packed into it. Moreover, increasing the size of logic blocks, *i.e.*, increasing the number of inputs to each logic block, increases the number of logic functions performed by each logic block as well as improving the area/delay performance of the logic block [8]. However, this comes on the expense of wasted resources because not all of the blocks will have all of their inputs fully utilized.

Most commercial FPGAs employ look-up tables (LUTs) to implement the logic blocks. A k-input LUT consists of  $2^k$  configuration bits in which the required truth table is programmed during the configuration stage. The almost standard number of inputs for LUTs is four, which was proven optimum for area and delay objectives [9]. However, this number can vary depending on the targeted application by the vendor. Moreover, modern FPGAs utilize a hierarchial architecture where every group of basic logic blocks are grouped together into a bigger logic structure, logic cluster. The remaining of this Section describes the programmable logic resources in three of the most popular commercial FPGAs.

#### 2.2.1 Altera Stratix III Logic Resources

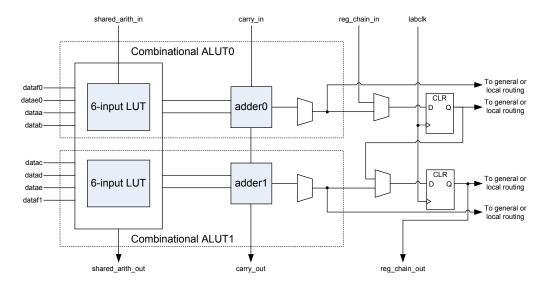

The logic blocks in Altera's Stratix III are called Adaptive Logic Modules (ALMs). An 8-input ALM contains a variety of LUT-based resources that can be divided between two adaptive LUTs [10]. Being adaptive, ALMs can perform the conventional 4-input LUT operations as well as implementing any function of up to 6-inputs and some 7-input functions. Besides the adaptive LUTs, ALMs contain two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Using these components, ALMs can efficiently perform arithmetic and shift operations. A detailed view of an ALM is shown in Figure 2.2. Every eight ALMs are grouped together to form a Logic Array Block (LAB).

#### 2.2.2 Xilinx Virtex-5 Logic Resources

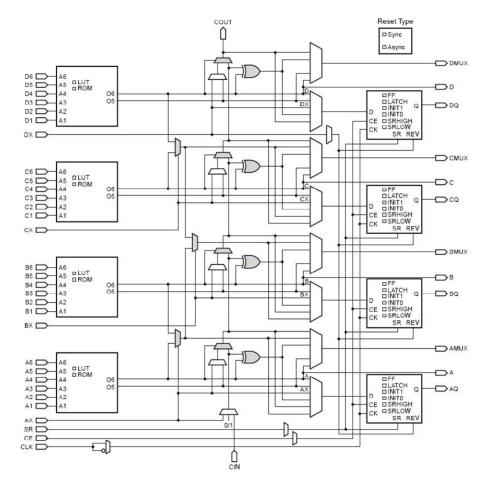

The slice is the basic logic resource in Xilinx Virtex-5 FPGAs. Slices consist of four LUTs, wide function multiplexers, and carry logic [11]. Figure 2.3 shows the architecture of a typical Virtex-5 slice. The slices employ four 6-LUTs that are capable of performing any 6-input logic function. Functions with up to 8-inputs can be implemented using multiplexers to combine the output of two LUTs. Every two interconnected slices are grouped together in a *Configurable Logic Block* (CLB) [11].

Figure 2.2: Altera's Stratix III ALM architecture [10].

Figure 2.3: Xilinx's Vertex-5 slice architecture [11].

#### 2.2.3 Actel ProASIC3/IGLOO Logic Resources

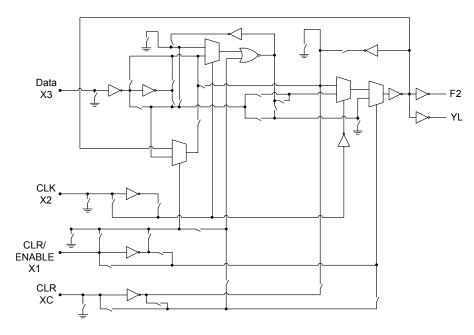

Actel ProASIC3/IGLOO FPGAs employ a flash-based architecture, instead of the conventional SRAM-based FPGAs used by both Altera and Xilinx, to store the configuration bits. The flash architecture provides the FPGAs with both reconfigurability and non-volatility. The ProASIC3/IGLOO FPGAs employ the VersaTile 3-input logic block that can implement any 3-input logic function as well as sequential functionality, as shown in Figure 2.4 [12]. Furthermore, the hierarchal architecture is not employed in the ProASIC3/IGLOO FPGAs and the output of each VersaTile can be directly routed to either the fast local lines or long routing resources. Another interesting characteristic of the VersaTile is that it does not adopt the conventional LUT architecture in FPGAs, as shown in Figure 2.4.

Figure 2.4: Actel's ProASIC3/IGLOO VersaTile architecture [12].

#### 2.3 FPGA Routing Resources Architecture

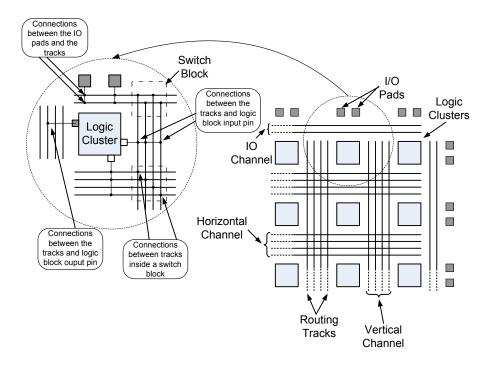

Routing resources in FPGAs can be divided into two components; segmented local routing and dedicated routing. Segmented local routing is used to provide connection among the logic blocks. As depicted in Figure 2.5, the segmented wires are prefabricated in channels to provide programmable connections between switch blocks, connection blocks, and logic blocks. The number of wires in one channel is usually denoted by W [13].

Figure 2.5: Routing resources in island-style FPGAs.

The I/O of the logic blocks are dynamically connected to the segmented routing channels on all four sides using connection blocks. The number of wires in each channel to which a logic block pin can connect to is called the connection block flexibility  $F_c$ . In addition, the switch blocks provide programmable connectivity between the horizontal and vertical wires. The switch block flexibility  $F_s$  is defined as the number of wires to which each incoming wire can connect to in a switch block. The segment length of a certain wire segment is defined as the number of logic blocks spanned by the routing wire. Modern FPGAs use a combination of wires of different segment lengths to achieve the optimum performance in terms of routability, delay, or both.

Dedicated routing is used for global signals that fan out to a large number of logic blocks, e.g., clock and reset, thus providing low-skew. Moreover, some commercial FPGAs employ PLLs and Delay-Locked Loops (DLLs) for further skew reduction. Modern FPGAs have the flexibility to provide different clock domains inside the FPGA to enable asynchronous designs.

#### 2.4 CAD for FPGAs

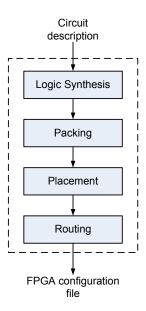

FPGAs are implemented using a huge number of programmable switches that are used to implement a certain logic function. The CAD tools of FPGAs transform the design, entered either as a schematic or using a hardware description language,

to a stream of '1's and '0's that program the FPGA during the configuration time. The flow chart in Figure 2.6 shows the different steps involved in the CAD flow for a typical FPGA design.

Figure 2.6: A typical FPGA CAD flow.

#### 2.4.1 Logic Synthesis

In the *synthesis* phase, the circuit description is converted to a netlist of basic logic gates. This phase is usually divided into two different stages; *logic optimization* and *technology mapping* [14–17].

Logic optimization is a technology-independent stage that involves simplifying the logic function of the design without the use of any technology information. Any redundant logic is removed at this stage. The optimized user circuit is then mapped into LUTs and flip-flops in the technology mapping stage, where each k-bounded logic function in the circuit is mapped into a k-LUT. This step resolves to finding a set of k-feasible cuts that include all the nodes in the circuit in such a way to minimize the delay, area, and/or power dissipation of the final implementation. The process of technology mapping is often treated as a covering problem.

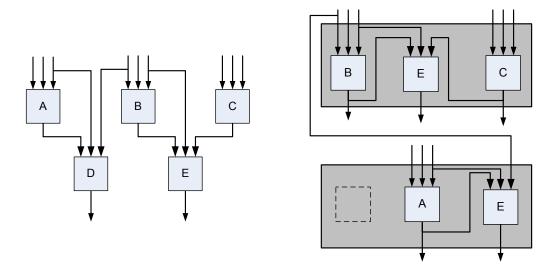

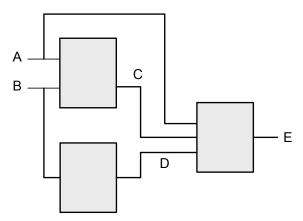

#### 2.4.2 Packing

The packing phase converts the netlist of LUTs and flip-flops into a netlist of logic blocks, as shown in Figure 2.7. The input netlist is converted into clusters of

logic blocks that can be mapped into the physical logic blocks of the FPGA. Most packing algorithms minimize the number of resulting logic blocks, the number of connections between them, and/or the delay along the critical path. The packing algorithm has to consider the physical limitations of the actual logic blocks of the FPGA in terms of the maximum number of LUTs in a logic block and the number of distinct input signals and clocks a logic block has.

Figure 2.7: An example of packing.

Packing algorithms can be categorized as either bottom-up [14, 18–20] or top-down [21,22]. Bottom-up packing algorithms build each cluster individually around a seed LUT until the cluster is full. However, top-down packing approaches partition the LUTs into clusters by successive circuit subdivision. Bottom-up algorithms are much faster and simpler than top-down approaches because they only consider local connections. However, this comes at the expense of solution quality.

#### 2.4.3 Placement

In the placement phase, the packed logic blocks are distributed among the physical logic blocks in the FPGA fabric. Placement algorithms try to minimize the delay along the critical path and enhance the resulting circuit routability. Available placement algorithms can be classified into three categories; min-cut [23, 24], analytic [25, 26], and simulated annealing [27–29] based algorithms. Most of the commercial placement tools for FPGAs employ simulated annealing-based algorithms because of their flexibility to adapt to a wide variety of optimization goals.

Simulated annealing (SA) placement tools depend on the SA algorithm, which is derived from the annealing process used to cool molten metals [30]. Initially, a random initial placement for all the logic blocks is generated. Afterwards, pairs of logic blocks are selected at random as candidates for swapping to improve the cost function. If the swap results in a decrease in the cost function, it is directly allowed, otherwise, it is only allowed with a probability that decreases as the algorithm progresses, thus allowing less worsening swaps after every iteration. A pseudocode for the SA placer is listed in Algorithm 2.1.

#### Algorithm 2.1 SA generic placer pseudocode.

```

S = RandomPlacement()

T = InitialTemperature()

while ExitCriterion() == False do

/* Outer loop */

while InnerLoopCriterion () == False do

/* Inner loop */

S<sub>new</sub> = GenerateViaMove(S)

\[ \Delta C = \text{Cost}(S_{new}) - \text{Cost}(S) \]

\[ \text{r} = \text{random}(0,1) \]

\[ \text{if } \text{r} < \text{e}^{-\Delta C/T} \text{ then} \]

\[ S = S_{new} \]

\[ \text{end if} \]

end while

\[ T = \text{UpdateTemp}() \]

end while

```

#### 2.4.4 Timing Analysis

Timing analysis [31] is used to guide placement and routing CAD tools in FPGAs to: (1) determine the speed of the placed and routed circuit and (2) estimate the slack of each source-sink connection during routing to identify the critical paths. Timing analysis is usually performed on a directed graph representing the circuit, where the nodes represent LUTs or registers and the edges represent connections.

The minimum required clock period of the circuit can be determined by a breadth first search through the graph, starting from the primary inputs, to find the arrival time at node i using the following relation

$$T_{arrival}(i) = \max_{\forall j \in fanin(i)} \{ T_{arrival}(j) + delay(j, i) \}, \qquad (2.1)$$

where delay(j, i) is the delay on the edge between j and i. The required time at node i is calculated by a breadth-first search of the graph, starting from the primary outputs, and using the following relation

$$T_{required}(i) = \min_{\forall j \in fanout(i)} \{ T_{required}(j) + delay(i, j) \}.$$

(2.2)

Afterwards, the slack on the connection between node i and j is calculated as

$$slack(i,j) = T_{required}(j) - T_{arrival}(i) - delay(i,j)$$

(2.3)

Connections with a zero slack are critical connections, while those with a positive slack are non-critical ones that can be routed using longer routes.

#### 2.4.5 Routing

The routing phase assigns the available routing resources in the FPGA to the different connections between the logic blocks in the placed design [28]. The objective of a typical routing algorithm is to minimize the delay along the critical path and avoid congestions in the FPGA routing resources. Generally, routing algorithms can be classified into *global routers* and *detailed routers*. Global routers consider only the circuit architecture without paying attention to the number and type of wires available, while detailed routers assign the connections to specific wires in the FPGA.

#### 2.5 Versatile Place and Route (VPR) CAD Tool

The CAD flow used in this thesis is based on the Versatile Place and Route (VPR) CAD tool. VPR is a popular academic placement and routing tool for FPGAs [28]. Moreover, VPR is the core for Altera's Modeling Toolkit (FMT) CAD tool [32,33]. VPR is usually used in conjunction with T-VPack [18,27], a timing-driven logic block packing algorithm. VPR consists of two main parts; a placer and router and an area and delay model. These two components interact together to find out the optimum placement and routing that satisfies a set of conditions. This Section describes the FPGA architecture supported by VPR as well as giving a quick overview about the tool flow.

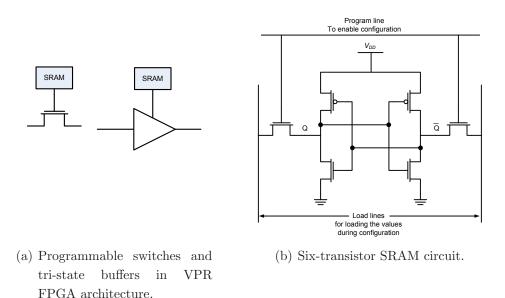

#### 2.5.1 VPR Architectural Assumptions

VPR assumes an SRAM-based architecture, where SRAM cells hold the configuration bits for all the pass-transistors multiplexers and tri-state buffers in the FPGA in both logic and routing resources, as shown in Figure 2.8(a). The SRAMs used are the six-transistor SRAM cell made of minimum size transistors, as shown in Figure 2.8(b). Moreover, an island-style FPGA is assumed by VPR, where the logic clusters are surrounded by routing tracks from all sides. VPR uses an architecture file to describe the underlying FPGA architecture used. The architecture file contains information about the logic block size, wire segment length, connection topologies, and other information used by VPR. The use of the architecture file allows VPR to work on a wide range of FPGA architectures. However, there are some general architectural assumptions made by VPR which are discussed in this Section.

Figure 2.8: Building blocks of SRAM programmable FPGAs used by VPR.

#### 2.5.1.1 VPR Logic Architecture

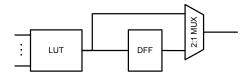

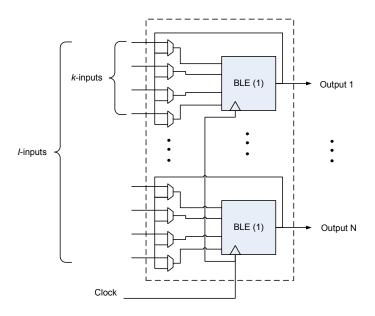

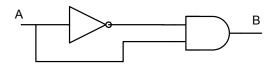

VPR targets the hierarchal or cluster-based logic architecture, where every N of the smallest logic element, called  $Basic\ Logic\ Element$  (BLE), are grouped together to a form a  $Cluster\ of\ Logic\ Blocks$ . Each BLE consists of a k-LUT, a D flip-flop (DFF), and a 2:1 multiplexer (MUX), as shown in Figure 2.9. Such configuration allows both the registered and unregistered versions of the output to be readily

available. Local routing resources are used to connect the BLEs inside each logic cluster to each other and to the inputs/outputs of the logic cluster, as shown in Figure 2.10. As noticed in Figure 2.10, not all of the BLE inputs are accessible from outside. However, any of the BLEs inputs can be connected to any of the BLEs outputs or any of the external inputs.

Figure 2.9: VPR BLE architecture.

Figure 2.10: VPR logic cluster architecture.

A logic cluster is defined in the architecture file by four main parameters: (1) the size of its LUTs k, (2) the number of BLEs in the cluster N, (3) the number of external inputs to the cluster I, and (4) the number of external clock inputs  $M_{clk}$ . It should be noted that VPR assumes minimum-sized transistors are used to implement the LUTs, as a result, the capacitances of these transistors are ignored. However, VPR accounts for the capacitance of the internal routing tracks within the logic cluster.

#### 2.5.1.2 VPR Routing Resources Architecture

VPR divides the routing resources characterization into three categories: channel, switch block, and wire parameters. The channel information specifies the channel

width and the connections between between the IO pads and logic blocks from one side and the routing tracks from the other side. The channel width parameters include the width of horizontal  $(chan\_width\_x)$  and vertical  $(chan\_width\_y)$  routing channels, the width of the IO channel  $(chan\_width\_io)$ , and the number of IO pads that fit in one row or column of logic clusters  $(io\_rat)$ . The connections between the routing tracks and either the logic blocks or IO pads are defined by the number of tracks connected to each logic block input  $(F_{c,input})$  and output  $(F_{c,output})$  and the number of tracks connected to each IO pad  $(F_{c,pad})$ . As an example, Figure 2.11 shows a high-level view of a sample VPR FPGA routing model and the values of the parameter used to describe the channel.

Figure 2.11: VPR FPGA routing architecture.  $chan\_width\_x = 1$ ,  $chan\_width\_io = 0.5$ ,  $io\_rat = 2$ ,  $F_{c,input} = 3$ ,  $F_{c,output} = 1$ , and  $F_{c,pad} = 2$ .

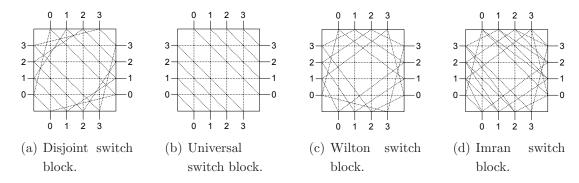

Switch blocks are used to provide programmable connectivity between the horizontal and vertical routing tracks, as shown in Figure 2.11. VPR characterizes switch blocks by their resistance (R), input capacitance  $(C_{in})$ , output capacitance  $(C_{out})$ , intrinsic delay  $(T_{del})$ , connection flexibility  $(F_s)$ , switch type (whether buffered or not), and the switch block topology. The connection flexibility of a switch is defined as the number of connections available for each pin to other pins on the other sides of the switch. Figure 2.8(a) shows the unbuffered and buffered versions of the switch blocks supported by VPR. Four different topologies of switches can be used within VPR: Disjoint [34], Universal [35], Wilton [36], and Imran [37],

as shown in Figure 2.12.

Figure 2.12: Switch topologies supported by VPR.

Finally, VPR describes wire segments by: the usage frequency of the segment in the FPGA ( $segment\_frequency$ ), the number of logic clusters spanned by the wire ( $segment\_length$ ), the resistance ( $R_{metal}$ ) and capacitance ( $C_{metal}$ ) per unit length, the switch type that connects the wire and logic clusters ( $opin\_switch$ ), the switch type that connects the wire with other wires ( $wire\_switch$ ).

#### 2.5.2 Basic Logic Packing Algorithm: VPack

VPack is a logic packing algorithm that converts an input netlist of LUTs and registers into a netlist of logic clusters. The packing is done in a hierarchial manner in two stages: packing LUTs and registers into BLEs and packing a group of N, or less, BLEs into logic clusters. The pseudocode for VPack is listed in Algorithm 2.2.

The first stage of VPack is a pattern matching algorithm that packs a register and a LUT into one BLE when the output of the LUT fans out to *only* one register, as shown in Figure 2.13. The second phase packs the BLEs into logic blocks to achieve two objectives: (1) fill the logic clusters to their full capacity N and (2) minimize the number of inputs to each cluster. These two objectives originate from the two main goals of packing: area reduction and improving routability. Packing starts by putting BLEs into the current cluster sequentially in a greedy manner while satisfying the following hard constrains:

- 1. the number of BLEs must be less than or equal to the cluster size N,

- 2. the number of externally generated signals, and used inside the cluster, must be less than or equal to the number of inputs to the cluster I,

#### Algorithm 2.2 VPack pseudocode [28].

```

Let: UnclusteredBLEs be the set of BLEs not contained in any cluster

- C be the set of BLEs in the current cluster

- LogicClusters be the set of clusters (where each cluster is a set of BLEs)

UnclusteredBLEs = PatternMatchToBLEs (LUTs, Registers)

LogicClusters = NULL

while UnclusteredBLEs != NULL do

/* More BLEs to cluster */

C = GetBLEwithMostUsedInputs (UnclusteredBLEs)

while |C| < N do

/* Cluster is not full */

BestBLE = MaxAttractionLegalBLE (C, UnclusteredBLEs)

if BestBLE == NULL then

/* No BLE can be added to cluster */

break

end if

UnclusteredBLEs = UnclusteredBLEs - BestBLE

C = C \cup BestBLE

end while

if |C| < N then

/* Cluster not full — try hill-climbing */

while |C| < N do

BestBLE = MINClusterInputIncreaseBLE (C, UnclusteredBLEs)

C = C \cup BestBLE

UnclusteredBLEs = UnclusteredBLEs - BestBLE

end while

if ClusterIsIllegal (C) then

RestoreToLastLegalState (C, UnclusteredBLEs)

end if

end if

LogicClusters = LogicClusters \cup C

end while

```

3. the number of distinct clock signals needed by the cluster must be less than or equal to the number of clock inputs  $M_{clk}$ .

A seed BLE is selected for each cluster such that it has the maximum number of inputs among the unclustered BLEs. Other unclustered BLEs B are attracted to

Figure 2.13: Packing LUTs and registers into BLEs [28].

the cluster C in such a way as to maximize the attraction() objective function

$$Attraction(B) = |Nets(B) \cap Nets(C)|, \qquad (2.4)$$

where Nets(x) are the nets connected to BLE (or cluster) x. This process continues until the cluster is filled to its maximum capacity N.

If the cluster does not reach its maximum capacity, but the number of inputs used by the BLEs inside it reaches I, a hill-climbing stage is invoked. In this stage, unclustered BLEs are added to the cluster in such a way to minimize the increase in the number of inputs to the cluster, an example of that is depicted in Figure 2.14. This is achieved by minimizing the following cost function

$$\Delta_{\text{cluster inputs}}(B) = |Fanin(B)| - |Nets(B) \cap Nets(C)|. \tag{2.5}$$

It is worth mentioning that the hill-climbing stage allows violating the number of inputs constraint while executing, but does not permit violating the clock inputs constraint. The hill-climbing phase terminates when the cluster size reaches N. If the cluster is infeasible, *i.e.*, its inputs are more than I, the algorithm retracts to the last feasible cluster. Afterwards, VPack selects a new seed BLE and constructs a new cluster.

#### 2.5.3 Timing-Driven Logic Block Packing: T-VPack

T-Vpack [18, 27] is a modified version of the VPack algorithm that attempts to minimize the number of inter-cluster connections along the critical path, besides packing the clusters to their maximum capacity. This achieves speed up along the critical path as local interconnects (intra-cluster connections) are faster than intercluster interconnects. T-VPack employs a timing analyzer to calculate the slack

Figure 2.14: Adding a BLE to a cluster can decrease the number of used cluster inputs [28].

along the connections in the design and identify the critical path(s). The *criticality* measure of a connection is calculated as

$$ConnectionCriticality(i) = 1 - \frac{slack(i)}{MaxSlack}, \qquad (2.6)$$

where MaxSlack is the largest slack in the circuit.

In T-VPack, the BLE with the highest *criticality*, *i.e.*, the BLE connected to the nets with the highest *ConnectionCriticality*, is selected as the seed BLE for the cluster. Afterwards, BLEs are attracted to the cluster to maximize a modified version of the *Attraction()* function in Eq. (2.4), given by

$$Attraction(B) = \lambda \times Criticality(B) + (1 - \lambda) \times \frac{Nets(B) \cap Nets(C)}{MaxNets}, \quad (2.7)$$

where MaxNets is and  $\lambda$  is Criticality(B)

#### 2.5.4 Placement: VPR

VPR models that the FPGA as a block array of logic clusters bounded by routing tracks, as shown in Figure 2.15. Simulated Annealing (SA) is used as the optimization algorithm for placement in VPR using an adaptive annealing schedule to adapt to the current placement at any time instant.

The initial temperature is selected from the basic features of the circuit. Assume that the total number of logic clusters in the design is  $N_{\text{clusters}}$ . After the initial random placement is evaluated,  $N_{\text{clusters}}$  pairwise swaps are performed and the initial temperature is calculated as 20 times the standard deviation of the cost of the different  $N_{\text{clusters}}$  combinations evaluated. Moreover, the number of inner moves

Figure 2.15: FPGA model assumed by the VPR placer.

performed at each temperature is evaluated as

$$MovesPerTemperature = InnerNum \times N_{clusters}^{4/3}$$

, (2.8)

where *InnerNum* is a constant and usually set to 10.

Another feature of the adaptive SA algorithm used in VPR is the way the temperature is updated. In conventional SA, almost all of the moves are accepted at high temperatures, while at low temperatures, only improving moves are accepted. In the adaptive SA [28], the cooling scheme tries to prolong the time spent in these cost improving temperatures (medium and low temperatures) at the expense of possibly cost worsening temperatures (high temperatures) using the following temperature update relationship

$$T_{new} = \gamma \times T_{old} , \qquad (2.9)$$

where  $\gamma$  is evaluated with respect to the percentage of moves accepted  $(\alpha)$ , according to Table 2.1.

Table 2.1: VPR temperature update schedule [28].

| $\alpha$                | $\gamma$ |

|-------------------------|----------|

| $0.96 < \alpha$         | 0.5      |

| $0.8 < \alpha \le 0.96$ | 0.9      |

| $0.15 < \alpha \le 0.8$ | 0.95     |

| $\alpha \le 0.15$       | 0.8      |

### 2.5.5 Routing: VPR

VPR incorporates two different routing algorithms; a routability-driven router and a timing-driven router.

#### 2.5.5.1 Routability-Driven Router

The VPR routability-driven router is based on the Pathfinder algorithm [38]. The Pathfinder algorithm repeatedly rips-up and re-routes every net in the circuit during each routing iteration until all congestions are removed. Initially, all nets are routed to minimize the delay, even if this results in congestion. Afterwards, routing iterations are applied to overused routing resources to resolve such congestions. In VPR, the cost of using a routing resource n when it is reached by connecting it to routing resource m is given by

$$Cost(n) = b(n) \times h(n) \times p(n) + BendCost(n, m), \qquad (2.10)$$

where b(n), h(n), and p(n) are the base cost, historical congestion, and present congestion, respectively. b(n) is set to the delay of n, delay(n). h(n) is incremented after each routing iteration in which n is overused. p(n) is set to '1' if routing the current net through n will not result in congestion and increases with the amount of overuse of n. The BendCost(n, m) is used to penalize bends in global routing to improve the detailed routability.

#### 2.5.5.1.1 Timing-Driven Router

The timing-driven router in VPR is based on the Pathfinder, but timing information is considered during every routing iteration. Elmore delay models are used to calculate the delays, and hence, timing information in the circuit. In order to include timing information, the cost of including a node n in a net's routing is given by

$$Cost(n) = Crit(i, j) \times delay(n, topology) + [1 - Crit(i, j)] \times b(n) \times h(n) \times p(n) ,$$

$$(2.11)$$

where a connection criticality Crit(i, j) is given by

$$Crit(i,j) = \max \left\{ \left[ MaxCrit - \frac{slack(i,j)}{D_{max}} \right]^{\eta}, 0 \right\},$$

(2.12)

where  $D_{max}$  is the critical path delay and  $\eta$  and MaxCrit are parameters that control how a connection's slack impacts the congestion-delay tradeoff in the cost function.

## Chapter 3

## Leakage Power in Modern FPGAs

The tremendous growth of the semiconductor industry in the past few decades is fueled by the aggressive scaling of the semiconductor technology following Moore's Law. As a result, the industry witnessed an exponential increase in the chip speed and functional density with a significant decrease in power dissipation and cost per function [39]. However, as the CMOS devices enter the nanometer regime, leakage current is becoming one of the main hurdling blocks to Moore's law. According to Moore himself, the key challenge for continuing process scaling in the nanometer era is leakage power reduction [40]. Thus, circuit designers and CAD engineers have to work hand in hand with device designers to deliver high-performance and low-power systems for future CMOS devices.

In this Chapter, the leakage power problem is discussed in the VLSI industry in general and in FPGAs in particular. Moreover, the proposed techniques in the literature to combat both dynamic and leakage power dissipation in FPGAs are presented and their advantages and disadvantages are discussed.

# 3.1 Dynamic Power Reduction Techniques in FP-GAs

Most of the low-power design techniques proposed for FPGAs targeted dynamic power dissipation. These works were motivated by the fact that dynamic power dissipation constituted most of the power dissipation in old CMOS technologies, 180nm and before. In [41], a hierarchal interconnect architecture is proposed to reduce dynamic power dissipation in the interconnect multiplexers. The basic idea

behind this work was to reduce the capacitance of the interconnects by reducing the number of wire segments connected to each switch box. Moreover, the authors proposed the use of lower supply voltage to reduce the total power dissipation.

A low swing signalling scheme was proposed in [42] for FPGAs for total power reduction. The authors used level converters at both sides of long interconnects that reduces the voltage of the transmitted signal. Moreover, the authors proposed a symmetric mesh architecture for the FPGA interconnects that reduces the total wire capacitance.

An efficient power-aware CAD flow was implemented in [43]. The authors introduced power figures of merits to the cost function at every level of the FPGA CAD design flow. The main idea of the work is to minimize the capacitance of signals with high switching activity. In the technology mapping phase, the authors include the switching activity of the feasible cuts evaluated during mapping. The clustering phase tries to cluster the logic blocks connected to a high activity net together to reduce the net capacitance. Similarly, during the placement stage, clusters connected to high activity nets are placed close to each other.

A power-aware technology mapping methodology for FPGAs was proposed in [44] that aims to keep nets with high switching activity out of the FPGA routing network and takes an activity-conscious approach to logic replication. As result, the wire capacitance of high activity nets is reduced significantly.

A methodology to reduce glitching power in FPGAs was proposed in [45] that relies on adding extra programmable delays to balance path delays. By adding extra delays to nets with positive slacks, the authors managed to equalize the delays at most of the inputs to each logic block in the design. As a result, glitching power is reduced to almost zero.

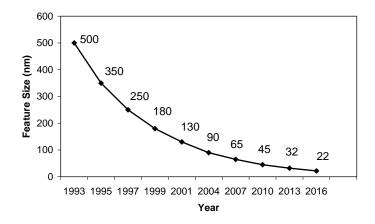

## 3.2 CMOS Technology Scaling Trends and Leakage Power in VLSI Circuits

The main driving forces that govern the CMOS technology scaling trend are the overall circuit requirements; the maximum power dissipation, the required chip speed, and the needed functional density. The overall device requirements such as the maximum MOSFET leakage current, minimum MOSFET drive current, and desired transistor size are determined to meet the overall circuit requirements. Similarly, the choices for MOSFET scaling and design, including the choice of

physical gate length  $L_g$  and equivalent oxide thickness of the gate dielectric  $t_{ox}$ , etc., are made to meet the overall device requirements. Figure 3.1 depicts the scaling trend for the CMOS feature size across several technology generations as well as some future predictions according to the semiconductor roadmap published by the International Technology Roadmap for Semiconductors (ITRS) [1].

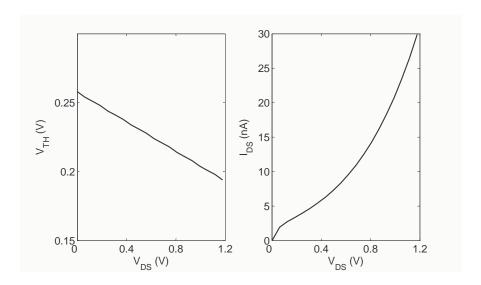

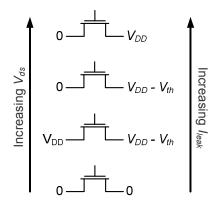

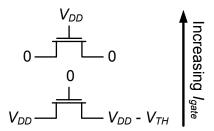

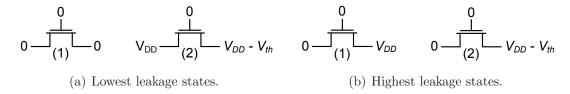

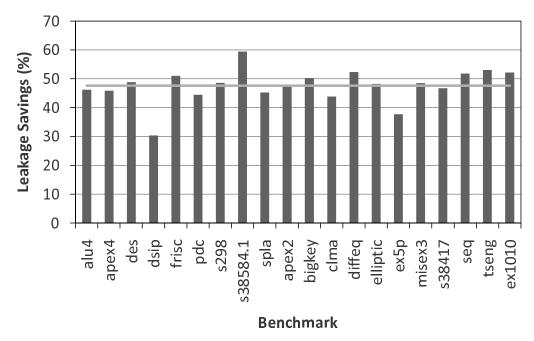

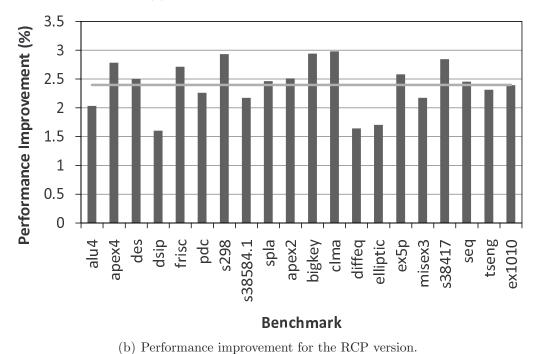

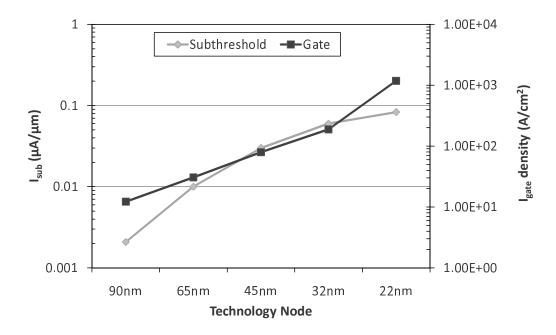

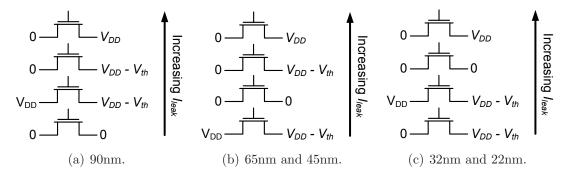

Figure 3.1: Gate length scaling of CMOS technologies [1].