# Power Management for Deep Submicron Microprocessors

by

Ahmed Youssef

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Ahmed Youssef 2008

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

As VLSI technology scales, the enhanced performance of smaller transistors comes at the expense of increased power consumption. In addition to the dynamic power consumed by the circuits there is a tremendous increase in the leakage power consumption which is further exacerbated by the increasing operating temperatures. The total power consumption of modern processors is distributed between the processor core, memory and interconnects. In this research two novel power management techniques are presented targeting the functional units and the global interconnects.

First, since most leakage control schemes for processor functional units are based on circuit level techniques, such schemes inherently lack information about the operational profile of higher-level components of the system. This is a barrier to the pivotal task of predicting standby time. Without this prediction, it is extremely difficult to assess the value of any leakage control scheme. Consequently, a methodology that can predict the standby time is highly beneficial in bridging the gap between the information available at the application level and the circuit implementations.

In this work, a novel Dynamic Sleep Signal Generator (DSSG) is presented. It utilizes the usage traces extracted from cycle accurate simulations of benchmark programs to predict the long standby periods associated with the various functional units. The DSSG bases its decisions on the current and previous standby state of the functional units to accurately predict the length of the next standby period. The DSSG presents an alternative to Static Sleep Signal Generation (SSSG) based on static counters that trigger the generation of the sleep signal when the functional units idle for a prespecified number of cycles.

The test results of the DSSG are obtained by the use of a modified RISC superscalar processor, implemented by SimpleScalar, the most widely accepted open source vehicle for architectural analysis. In addition, the results are further verified by a Simultaneous Multithreading simulator implemented by SMTSIM. Leakage saving results shows an increase of up to 146% in leakage savings using the DSSG versus the SSSG, with an accuracy of 60-80% for predicting long standby periods.

Second, chip designers in their effort to achieve timing closure, have focused on achieving the lowest possible interconnect delay through buffer insertion and routing techniques. This approach, though, taxes the power budget of modern ICs, especially those intended for wireless applications. Also, in order to achieve more functionality, die sizes are constantly increasing. This trend is leading to an increase in the average global interconnect length which, in turn, requires more buffers to achieve timing closure.

Unconstrained buffering is bound to adversely affect the overall chip performance, if the power consumption is added as a major performance metric. In fact, the number of global interconnect buffers is expected to reach hundreds of thousands to achieve an appropriate timing closure.

To mitigate the impact of the power consumed by the interconnect buffers, a powerefficient multi-pin routing technique is proposed in this research. The problem is based on a graph representation of the routing possibilities, including buffer insertion and identifying the least power path between the interconnect source and set of sinks.

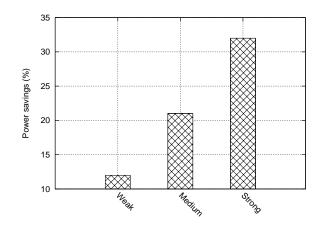

The novel multi-pin routing technique is tested by applying it to the ISPD and IBM benchmarks to verify the accuracy, complexity, and solution quality. Results obtained indicate that an average power savings as high as 32% for the 130-nm technology is achieved with no impact on the maximum chip frequency.

#### Acknowledgements

All praise is due to Allah for guiding me throughout my life and giving me the ability to complete this work. I am at a loss of words to express my gratitude to my family for their continuous love and support.

This thesis would not be possible without the support of many individuals, to whom I would like to express my gratitude. I will always be indebted to my supervisors Prof. Mohamed Elmasry and Prof. Mohab Anis, for their key role in my development as a person and as a researcher. They offered me support, encouragement, guidance, and most importantly trust. Their input and guidance was invaluable to the quality and contribution of the work presented in this thesis, as well as in other publications. Their trust and support was instrumental in giving me confidence to achieve many accomplishments.

I would like also to thank many faculty members of the University of Waterloo, most notably my committee members, Prof. John Yeow, Prof. Mark Aagaard, and Prof. Manoj Sachdev, for their valuable input and suggestions. I would like also to thank Prof. Shawki Areibi and Prof. Mohamed Zahran for valuable discussions and ideas. I wish to thank many of my colleagues at the VLSI Lab, especially Mohamed Elsaid, Muhammad Nummer, Mohamed Elgebaly, Hassan Hassan, Ayman Ismail, and Mohamed Hassan, for valuable discussions and feedback. I am grateful to Wendy Boles for her help on administrative issues and to Phil Regier for his great computing resources support.

I would like to thank NSERC for their financial support. I would like to thank Hazem Shehata, Shady Shehata, Mohamed El-Abd, Ismael El-Samahy, Mohamed El-Dery, and Hatem Zeineldin for being such great friends.

My wife, Wessam, shared with me every day throughout the course of this work. Her love, support, and understanding played a major role in helping me finish this thesis. I am also grateful to my sister, Amira, for her love, support, and encouragement.

My deepest gratitude to my mother and father for their ever continuous support, encouragement, and prayers. No words of appreciation could ever reward them for all they have done for me. I am, and will ever be, indebted to them for all achievements in my life. Dedication

To my wife Wessam, my sister Amira, my Father Mohamed and Mother Eman. with love and appreciation.

# Contents

| 1 | Introduction |         |                                             | 1  |

|---|--------------|---------|---------------------------------------------|----|

|   | 1.1          | Motiva  | ation                                       | 1  |

|   |              | 1.1.1   | Leakage Power in Processor Functional Units | 2  |

|   |              | 1.1.2   | Dynamic Power in Global Interconnects       | 4  |

|   | 1.2          | Thesis  | Organization                                | 6  |

| 2 | CM           | OS Pow  | ver Consumption                             | 8  |

|   | 2.1          | Techno  | ology Scaling                               | 8  |

|   | 2.2          | Source  | es of Power Consumption                     | 9  |

|   |              | 2.2.1   | Switching Power                             | 10 |

|   |              | 2.2.2   | Short-Circuit Power                         | 11 |

|   |              | 2.2.3   | Leakage Power                               | 11 |

|   | 2.3          | Manag   | ging CMOS Power Consumption                 | 13 |

|   |              | 2.3.1   | Dynamic Power Management                    | 13 |

|   |              | 2.3.2   | Leakage Power Management                    | 14 |

| 3 | Mic          | roproce | essor Leakage Power Management              | 15 |

|   | 3.1          | Microp  | processor Architecture                      | 15 |

|   |              | 3.1.1   | Pipelined Processors                        | 16 |

|   |              | 3.1.2   | Superscalar Processors                      | 17 |

|   |              | 3.1.3   | SMT Processors                              | 22 |

|   | 3.2          | Leakag  | ge Power Management Techniques              | 25 |

|   |      | 3.2.1     | Leakage Power Management Overview                                                  | 25 |

|---|------|-----------|------------------------------------------------------------------------------------|----|

|   |      | 3.2.2     | Circuit-Level Leakage Control Techniques                                           | 27 |

|   |      | 3.2.3     | System-Level Leakage Control Techniques                                            | 33 |

|   |      | 3.2.4     | Program Profiling                                                                  | 40 |

|   |      | 3.2.5     | Phase Extraction                                                                   | 41 |

|   |      | 3.2.6     | Discussion                                                                         | 42 |

|   | 3.3  | Summ      | ary                                                                                | 42 |

| 4 | Prec | lictive S | leep Signal Generation                                                             | 43 |

|   | 4.1  | Sleep S   | Signal Generation                                                                  | 43 |

|   | 4.2  | Propos    | ed Dynamic Sleep Signal Generation                                                 | 45 |

|   |      | 4.2.1     | The DSSG architecture                                                              | 47 |

|   | 4.3  | Sleep S   | Signal Generation for Superscalar Processors                                       | 51 |

|   |      | 4.3.1     | Superscalar Simulation Environment                                                 | 52 |

|   |      | 4.3.2     | DSSG and SSSG Circuit Implementation and Power Consumption                         | 54 |

|   |      | 4.3.3     | Accuracy of the Sleep Signal Generators on Superscalar Processors                  | 61 |

|   |      | 4.3.4     | DSSG and SSSG Design Issues                                                        | 65 |

|   |      | 4.3.5     | Superscalar Leakage Saving Potential for Sleep Signal Generators                   | 66 |

|   | 4.4  | Summ      | ary                                                                                | 70 |

| 5 | Арр  | lication  | of Sleep Signal Generation on SMT Processors                                       | 72 |

|   | 5.1  | SMT E     | Experimental Setup                                                                 | 73 |

|   | 5.2  | Predict   | tive Sleep Signal Generation on SMT processors                                     | 74 |

|   |      | 5.2.1     | DSSG and SSSG Circuit Implementation and Power Consump-<br>tion for SMT processors | 75 |

|   |      | 5.2.2     | Accuracy of the Sleep Signal Generators on SMT Processors                          | 77 |

|   |      | 5.2.3     | The Sleep Signal Generators Workload Dependence on SMT<br>Processors               | 79 |

|   |      | 5.2.4     | SMT Leakage Savings Potential for Sleep Signal Generators                          | 82 |

|   | 5.3  | Archite   | ectural Dependence of Predictive Sleep Signal Generation                           | 85 |

|    |        | 5.3.1           | Floating Point ALU                                           | 86  |

|----|--------|-----------------|--------------------------------------------------------------|-----|

|    |        | 5.3.2           | Floating Point Multiply                                      | 86  |

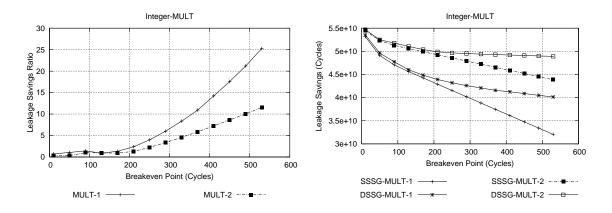

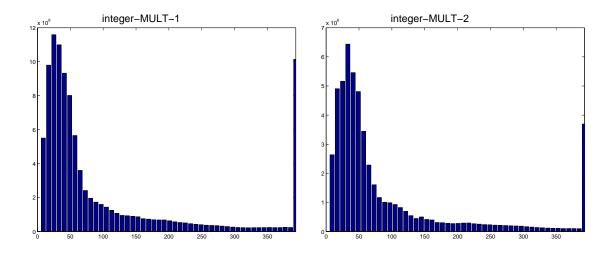

|    |        | 5.3.3           | Integer Multiply                                             | 89  |

|    |        | 5.3.4           | Memory Latency                                               | 90  |

|    |        | 5.3.5           | Load Store Queue (LSQ)                                       | 91  |

|    | 5.4    | Embec           | Ided Processors                                              | 92  |

|    | 5.5    | Summ            | ary                                                          | 92  |

| 6  | Mul    | <b>ti-Pin I</b> | nterconnect Power Optimization                               | 93  |

|    | 6.1    | Power           | Driven Routing                                               | 93  |

|    | 6.2    | Introdu         | uction                                                       | 95  |

|    |        | 6.2.1           | Global Routing: Unified Timing and Congestion Minimization . | 95  |

|    |        | 6.2.2           | Buffer Insertion-Based Methods                               | 96  |

|    | 6.3    | Prelim          | inaries                                                      | 98  |

|    |        | 6.3.1           | Global Routing Problem                                       | 98  |

|    |        | 6.3.2           | Global Routing Techniques                                    | 99  |

|    |        | 6.3.3           | Interconnect Modeling                                        | 100 |

|    | 6.4    | Power           | -Efficient Multi-pin ILP Based Global Routing                | 103 |

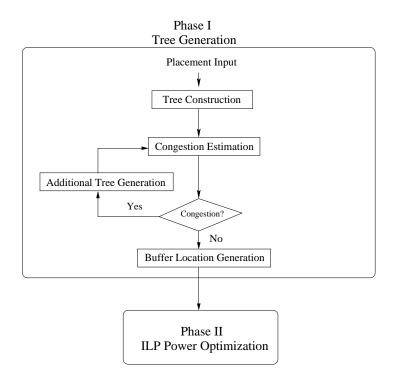

|    |        | 6.4.1           | PIRT Phases                                                  | 103 |

|    |        | 6.4.2           | Phase I (Initialization)                                     | 103 |

|    |        | 6.4.3           | Phase II (Power Minimization)                                | 107 |

|    | 6.5    | Experi          | mental Results                                               | 109 |

|    |        | 6.5.1           | Experimental Results for Multi-Pin Nets                      | 110 |

|    | 6.6    | Summ            | ary                                                          | 115 |

| 7  | Con    | clusion         | s and Future Work                                            | 117 |

|    | 7.1    | Contri          | butions                                                      | 118 |

|    | 7.2    | Future          | Work                                                         | 119 |

| Pu | ıblica | tions           |                                                              | 121 |

| Re | eferen | ces             |                                                              | 122 |

# **List of Tables**

| 2.1  | Constant field scaling                                        | 9  |

|------|---------------------------------------------------------------|----|

| 2.2  | Power management                                              | 13 |

| 4.1  | SPEC:GZIP integer multiply usage patterns                     | 48 |

| 4.2  | SPEC:MESA integer divide usage patterns                       | 48 |

| 4.3  | Functional units in the superscalar test processor.           | 54 |

| 4.4  | Superscalar test processor architecture                       | 55 |

| 4.5  | Breakeven point with no overheads.                            | 58 |

| 4.6  | Power consumption of the sleep signal generators              | 59 |

| 4.7  | Breakeven point with overheads                                | 60 |

| 4.8  | SPEC2000 benchmarks.                                          | 62 |

| 4.9  | Leakage savings potential for SSSG and DSSG                   | 68 |

| 4.10 | Miss ratio.                                                   | 69 |

| 4.11 | Leakage savings for the DSSG                                  | 69 |

| 4.12 | Hit penetration.                                              | 70 |

| 5.1  | SMT test processor architecture.                              | 74 |

| 5.2  | Functional units in the SMT test processor.                   | 74 |

| 5.3  | SMT simulation workloads                                      | 75 |

| 5.4  | Power consumption of the sleep signal generators              | 76 |

| 5.5  | Breakeven point with no overheads.                            | 76 |

| 5.6  | Breakeven point with overheads.                               | 77 |

| 5.7  | Leakage savings potential for SSSG and DSSG on SMT processors | 84 |

| 5.8 | Energy savings for SSSG and DSSG on SMT processors             | 85  |

|-----|----------------------------------------------------------------|-----|

| 5.9 | Architectural modifications to the base processor              | 85  |

| 6.1 | ISPD98, IBM, and ISPD2007 benchmark statistics.                | 109 |

| 6.2 | Model parameters for global interconnects.                     | 110 |

| 6.3 | Comparison of delay minimization and power minimization models | 114 |

| 6.4 | Computation time comparison.                                   | 115 |

| 6.5 | Computation time comparison with power driven routers          | 116 |

# **List of Figures**

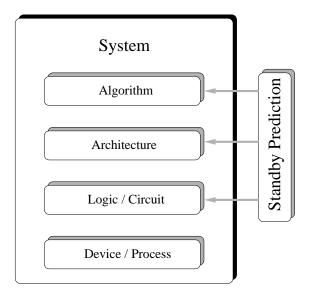

| 1.1  | System design space.                                         | 2  |

|------|--------------------------------------------------------------|----|

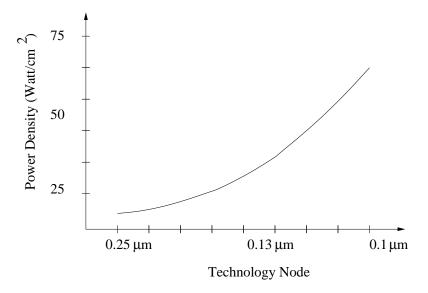

| 2.1  | Trends of processors' power density.                         | 9  |

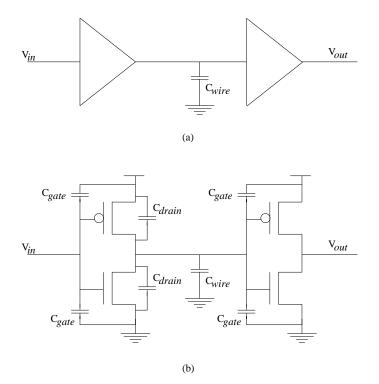

| 2.2  | Sources of output load capacitance.                          | 10 |

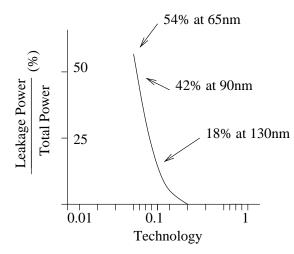

| 2.3  | Leakage power with technology scaling.                       | 12 |

| 3.1  | Pipelined processor.                                         | 16 |

| 3.2  | Generic superscalar pipeline.                                | 18 |

| 3.3  | O-o-O superscalar processor.                                 | 19 |

| 3.4  | Reservation station.                                         | 21 |

| 3.5  | Fine grained Multithreading.                                 | 23 |

| 3.6  | Coarse grained Multithreading.                               | 24 |

| 3.7  | Simultaneous Multithreading                                  | 24 |

| 3.8  | SMT resource sharing.                                        | 24 |

| 3.9  | Dynamic leakage control.                                     | 26 |

| 3.10 | Dynamic leakage control mechanisms.                          | 26 |

| 3.11 | Breakeven point.                                             | 27 |

| 3.12 | Two input NAND gate.                                         | 28 |

| 3.13 | Adaptive body biasing technique                              | 30 |

| 3.14 | Power gating within the framework of a power management unit | 31 |

| 3.15 | Sleep transistor in power gating circuits.                   | 31 |

| 3.16 | O-o-O superscalar processor.                                 | 34 |

| 3.17 | Branching in pipelined processors.                           | 36 |

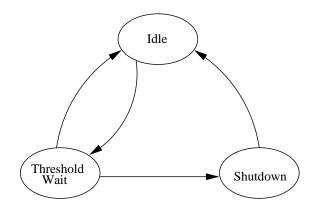

| 4.1                                                                                                     | Static Sleep Signal Generator state machine.                           | 46                                                                                 |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------|

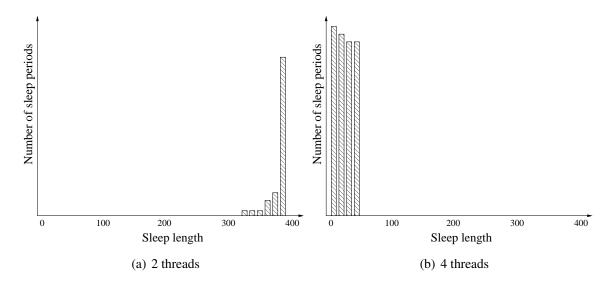

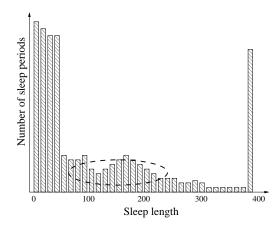

| 4.2                                                                                                     | Floating point multiplier unit standby trace histogram                 | 47                                                                                 |

| 4.3                                                                                                     | Sample standby trace                                                   | 48                                                                                 |

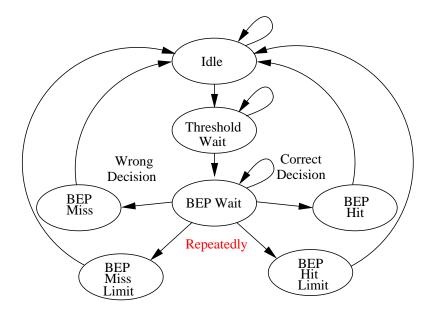

| 4.4                                                                                                     | Dynamic Sleep Signal Generator state machine.                          | 49                                                                                 |

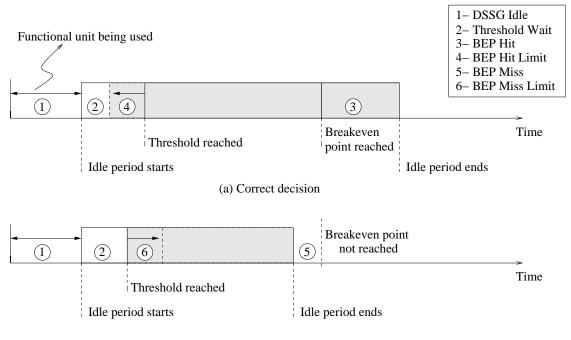

| 4.5                                                                                                     | The DSSG timing diagram.                                               | 50                                                                                 |

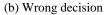

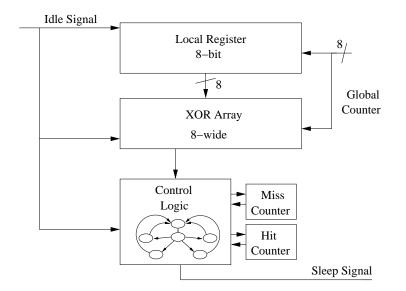

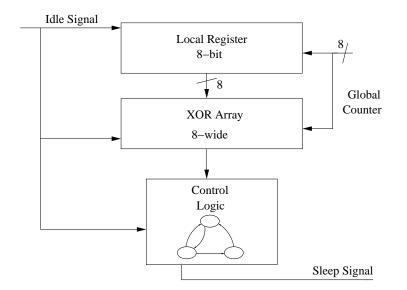

| 4.6                                                                                                     | The DSSG implementation                                                | 51                                                                                 |

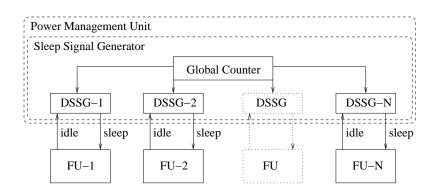

| 4.7                                                                                                     | Issue and operational latency.                                         | 53                                                                                 |

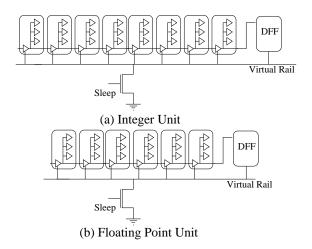

| 4.8                                                                                                     | DSSG circuit implementation.                                           | 56                                                                                 |

| 4.9                                                                                                     | SSSG circuit implementation.                                           | 57                                                                                 |

| 4.10                                                                                                    | FO4 inverter chain.                                                    | 58                                                                                 |

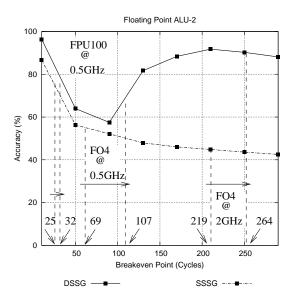

| 4.11                                                                                                    | DSSG and SSSG average prediction accuracy FP-ALU                       | 63                                                                                 |

| 4.12                                                                                                    | DSSG and SSSG average prediction accuracy FP-ALU-2                     | 64                                                                                 |

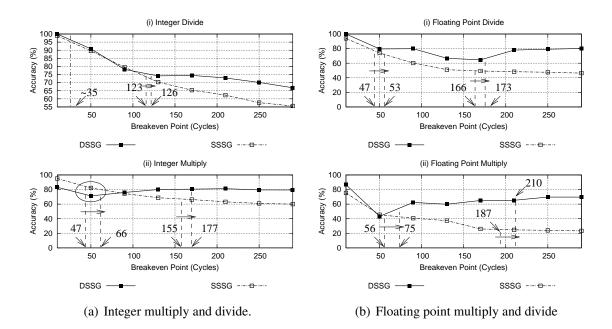

| 4.13                                                                                                    | DSSG and SSSG average prediction accuracy multiply and divide units.   | 64                                                                                 |

| 4.14                                                                                                    | Impact of DSSG parameters on accuracy.                                 | 65                                                                                 |

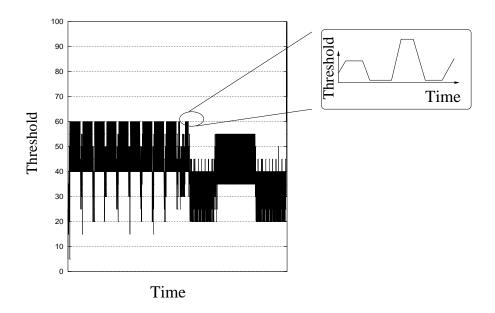

| 4.15                                                                                                    | The threshold value for the integer ALU unit running the MESA program. | 66                                                                                 |

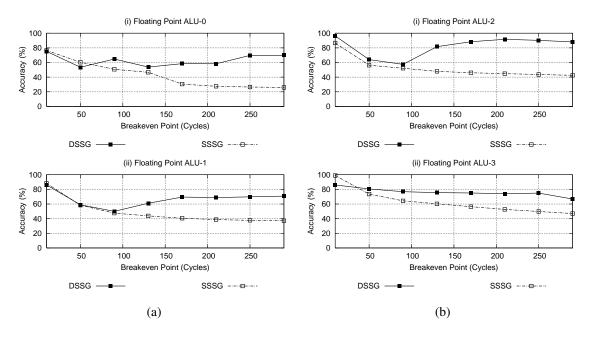

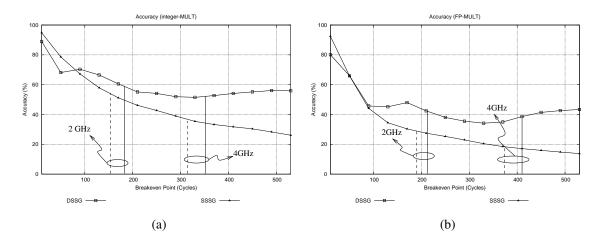

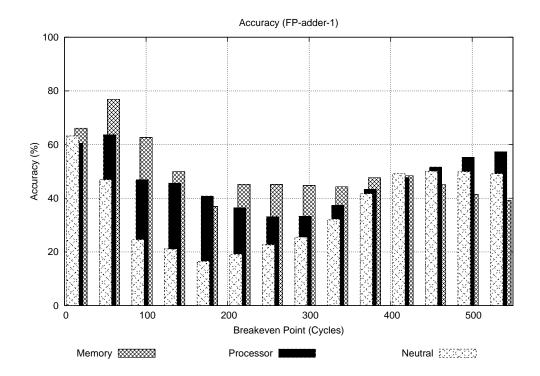

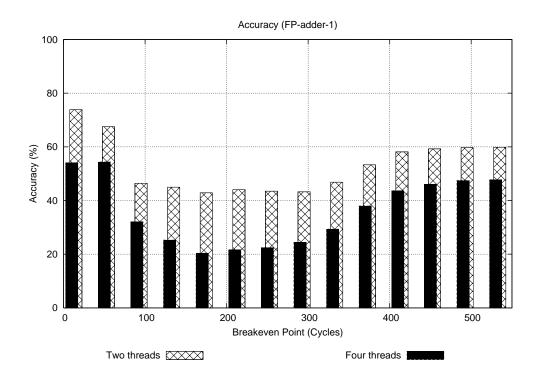

| 5.1                                                                                                     | DSSG vs. SSSG prediction accuracy FP-ALU.                              | 78                                                                                 |

| 5.2                                                                                                     | DSSG vs. SSSG prediction accuracy multiply units                       | 79                                                                                 |

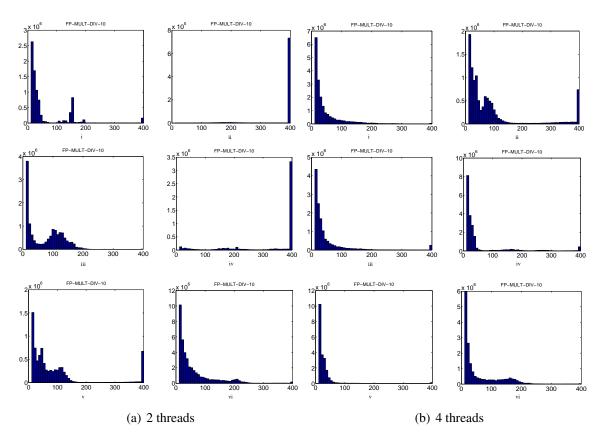

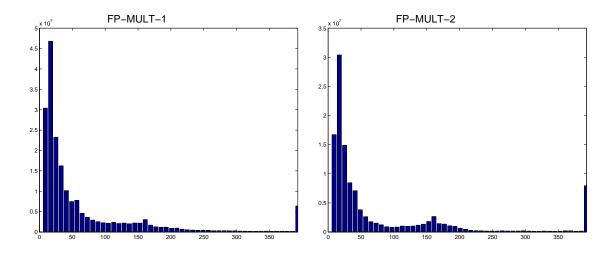

| 5.3                                                                                                     | Floating point multiplier unit standby trace histogram.                | 80                                                                                 |

|                                                                                                         |                                                                        | 00                                                                                 |

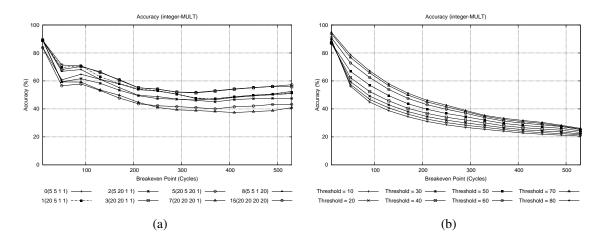

| 5.4                                                                                                     | Prediction accuracy for the integer multiplier unit.                   | 80                                                                                 |

| 5.4<br>5.5                                                                                              |                                                                        |                                                                                    |

|                                                                                                         | Prediction accuracy for the integer multiplier unit                    | 80                                                                                 |

| 5.5                                                                                                     | Prediction accuracy for the floating point multiplier Unit.            | 80<br>81                                                                           |

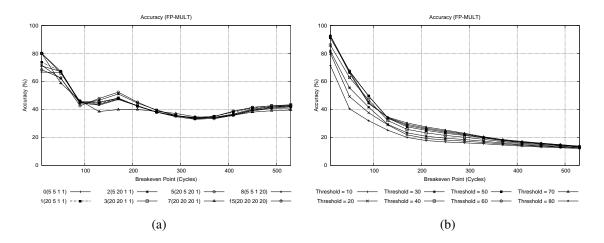

| 5.5<br>5.6                                                                                              | Prediction accuracy for the integer multiplier unit                    | 80<br>81<br>82                                                                     |

| 5.5<br>5.6<br>5.7                                                                                       | Prediction accuracy for the integer multiplier unit                    | 80<br>81<br>82<br>83                                                               |

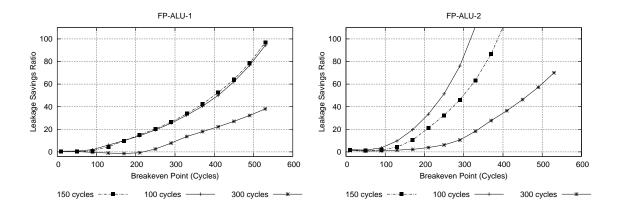

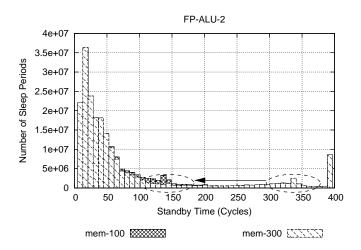

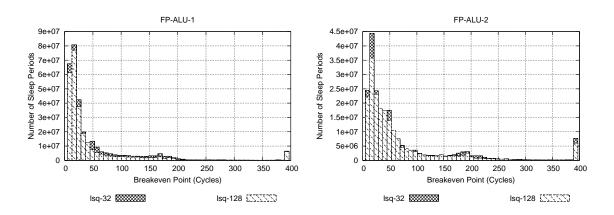

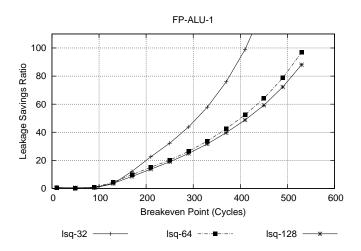

| <ol> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> </ol>                             | Prediction accuracy for the integer multiplier unit                    | <ul> <li>80</li> <li>81</li> <li>82</li> <li>83</li> <li>87</li> </ul>             |

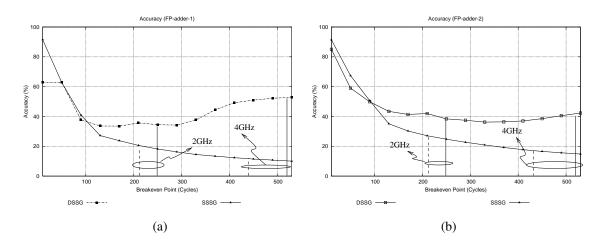

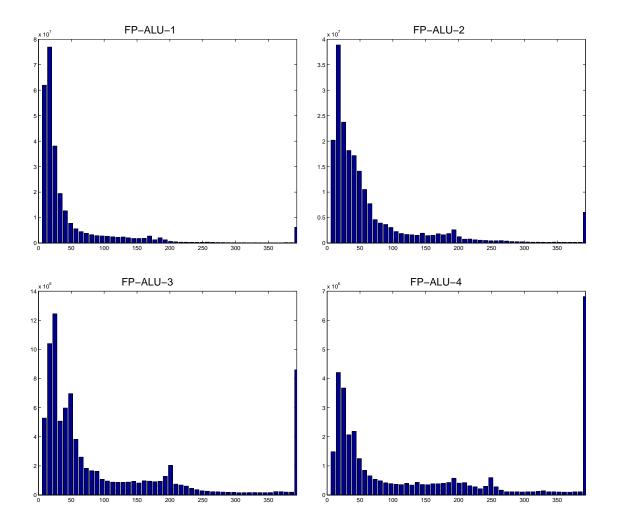

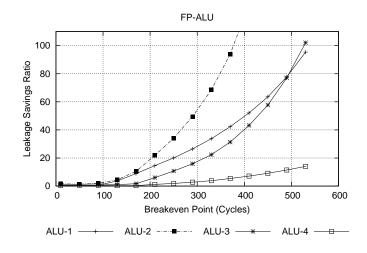

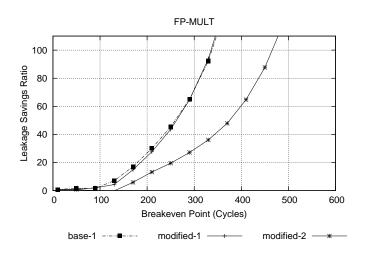

| <ol> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>5.10</li> </ol>               | Prediction accuracy for the integer multiplier unit                    | <ul> <li>80</li> <li>81</li> <li>82</li> <li>83</li> <li>87</li> <li>87</li> </ul> |

| <ol> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>5.10</li> <li>5.11</li> </ol> | Prediction accuracy for the integer multiplier unit                    | 80<br>81<br>82<br>83<br>87<br>87<br>88                                             |

| 5.14 | DSSG vs. SSSG with the change of memory latency (floating point ALUs) | 90  |

|------|-----------------------------------------------------------------------|-----|

| 5.15 | Histograms of the execution traces with memory latency variation      | 90  |

| 5.16 | Histograms of the execution traces on the floating point ALU          | 91  |

| 5.17 | Leakage Savings for FP-MULT.                                          | 91  |

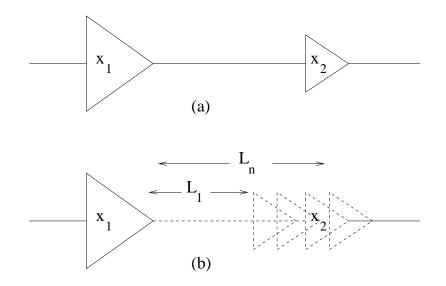

| 6.1  | Buffer insertion and sizing.                                          | 96  |

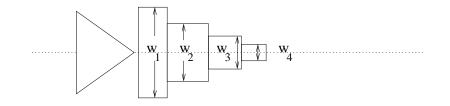

| 6.2  | Wire sizing.                                                          | 97  |

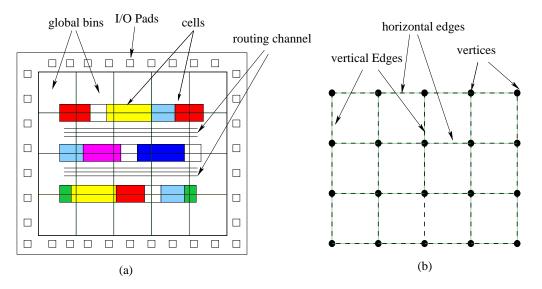

| 6.3  | Grid graph for standard-cell based designs.                           | 98  |

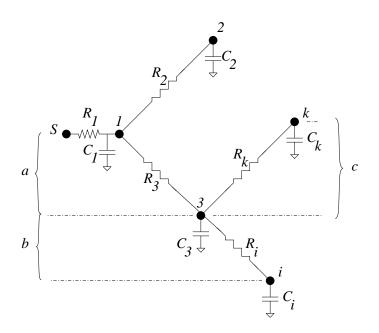

| 6.4  | RC tree                                                               | 101 |

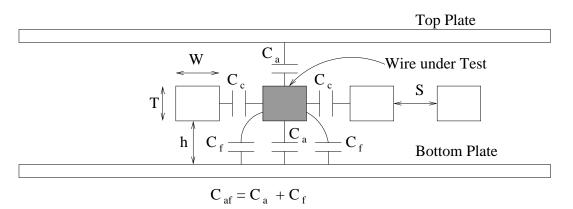

| 6.5  | Wire structure for capacitance extraction.                            | 101 |

| 6.6  | PIRT flow chart                                                       | 104 |

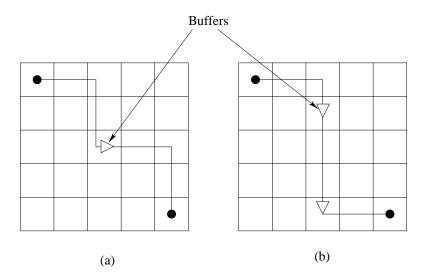

| 6.7  | Buffer insertion for two-terminal nets.                               | 105 |

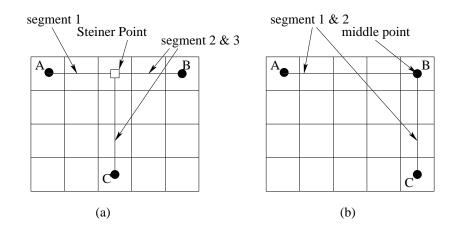

| 6.8  | Buffer insertion for three terminal nets                              | 106 |

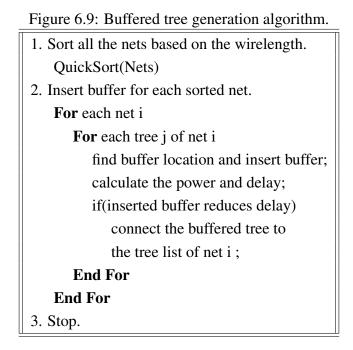

| 6.9  | Buffered tree generation algorithm.                                   | 107 |

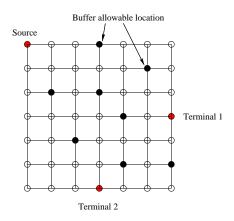

| 6.10 | Buffer location generation.                                           | 112 |

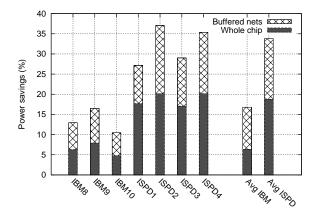

| 6.11 | Power savings by PIRT                                                 | 112 |

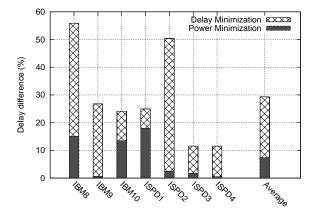

| 6.12 | Delay variation due to PIRT                                           | 113 |

| 6.13 | Average power reduction over different buffer sizes                   | 114 |

# **Glossary of Terms**

**BBV** Basic Block Vector

**BTB** Branch Target Buffer

**CISC** Complex Instruction Set Computer

**CPI** Cycles per Instruction

CMOS Complementary Metal Oxide Semiconductor

**DSM** Deep Submicron

**DSSG** Dynamic Sleep Signal Generator

**DVS** Dynamic Voltage Scaling

**DIBL** Drain Induced Barrier Lowering

**EDA** Electronic Design Automation

**FO4** Fanout of 4

**FP** Floating-point Unit

FU Functional Unit

**ID** Instruction Decode

**IE** Instruction Execute

**IF** Instruction Fetch

ILP Instruction Level Parallelism

**IPC** Instructions per Cycle

**ITRS** International Technology Roadmap for Semiconductors

- ISA Instruction Set Architecture

- MTCMOS MultiThreshold CMOS (Power Gating)

- NOP No Operation

- **NP-hard** Non deterministic polynomial hard problems are a subset of combinatorial problems which are not solvable in polynomial time

- O-o-O Out-of-Order

- **PDP** Power Delay Product

- **RAS** Return Address Stack

- **RAW** Read after Write (Data Hazard)

- **RF** Register File

- **RISC** Reduced Instruction Set Computer

- **ROB** Reorder Buffer

- **RUU** Register Update Unit

- **SMT** Simultaneous MultiThreading

- SOC System on Chip

- SSSG Static Sleep Signal Generator

- TK/NT Taken versus Not Taken branch

- TLB Translation Look-aside Buffer

- VTCMOS Variable Threshold CMOS

- WAR Write after Read (Data Hazard)

- WAW Write after Write (Data Hazard)

# Chapter 1

# Introduction

Microprocessors determine the sophistication of many consumer electronics applications [1]. Particularly, portable equipment not only requires more processing power, but also a very stringent power envelope. Accordingly, modern microprocessors must handle increased throughput, complex algorithms, and real time requirements. At the same time, though, the VLSI complexity must remain within the bounds of low area and power consumption.

# 1.1 Motivation

As the demand for faster and more complex applications increases, the semiconductor industry has been aggressively scaling the silicon technology in order to match the continuous increase in chip requirements. Dynamic and leakage power has consistently increased with every technology generation. The processor core, memory and global interconnects power consumption constitute the majority of the power budget of modern processors.

In this research, two power management techniques are proposed to handle leakage power consumption in the processor core as well as the dynamic power consumption of the global interconnects. Section 1.1.1 details the motivation behind the implementation of a standby predictor for managing leakage power for processor cores, while Section 1.1.2 presents the motivation behind a low power multi-pin global routing methodology that handles the dynamic power consumption of the processor interconnects.

#### **1.1.1 Leakage Power in Processor Functional Units**

The continuous reduction of the transistor dimensions, entailed by technology scaling, has created many challenges to chip designers. One of the major challenges is the reduction of the supply voltage due to smaller gate oxides that cannot withstand the traditional 3.3V and 5V supplies [2]. Reducing the supply voltage necessitates the reduction of the transistor threshold to maintain an adequate overdrive voltage. In turn, the reduction of the threshold voltage increases the transistor's subthreshold conduction, which translates into an increase in leakage power consumption.

Due to the significant increase in leakage power, research has focused on the reduction of the core leakage [3–5]. Research in [3] shows that managing leakage power in the microprocessor core can save up to 18% of the total power when power gating and adaptive body biasing is employed.

To deal with the increased leakage power and to maintain the complexity of modern processors, low power techniques are necessary throughout the design process. If the process is divided into levels, as depicted in Fig. 1.1, it is imperative to consider the combined effect of all these levels in order to exploit the full potential of leakage management [6]. Many circuit and system-level techniques have been proposed to deal with leakage power. However, very few of them focus on crossing the level boundaries, limiting their leakage saving capabilities.

Figure 1.1: System design space [6].

Circuit level leakage control techniques should reduce the leakage power, and ensure that the intended logic operation is performed correctly. However, these circuit techniques are characterized by their inability to predict the circuit usage patterns. These usage patterns can be obtained by answering questions such as how many times was the circuit accessed during a certain number of cycles?, how many times were the neighboring circuit blocks used?, and was there any regularity in the usage of the circuit?. Knowing the answers to these questions can significantly enhance the design process.

To deduce the usage patterns, the architecture needs to keep track of the standby periods of the various circuit blocks. These periods, defined as the length of time that the circuit stays idle, can be used as indicators of the circuits' usage profiles. Fortunately, for microprocessors, and programmable DSPs in particular, the information about the standby periods can be obtained from the executed code. Accordingly, a standby prediction methodology is expected to enhance the performance of the various circuit level techniques by supplying the circuits with standby information extracted from the algorithm.

The objective of this research is to introduce the concept of standby prediction by developing a Dynamic Sleep Signal Generator (DSSG). The new DSSG uses the high-level information found in the running application code to predict the standby profile of the processor functional units.

#### Contributions

The following outlines the main contributions of the proposed DSSG

- 1. Contrary to compiler-based low leakage techniques that are bound to a specific Instruction Set Architecture (ISA), the DSSG depends on only the information about current and previous standby periods.

- 2. Phase extraction techniques that are concerned with the coarse granularity prediction of program phases are not adequate for the task of low leakage management. These techniques are generally slow and perform complex tasks, prohibiting the techniques' application in small-scale leakage management. In contrast, the DSSG focuses on a fine granularity analysis (a few hundred cycles) of the profile information.

- 3. Current circuit techniques for leakage power reduction depend on detecting when the circuit is actually in standby, which leaves the techniques prone to erroneous decisions regarding very short standby periods, since the techniques lack the ability to predict the length of the period ahead of time [3–5]. Accordingly, the proposed

DSSG should eliminate these short periods from the decision tree of these techniques

- 4. The proposed DSSG and the associated finite state machine are capable of tracking the executed program behavior across different time segments and predict the length of the standby periods accordingly. This leads to a high accuracy in asserting the sleep signal when it is most likely to achieve a net increase in the total power savings. This is accomplished with minimal power overhead.

- 5. The DSSG is a simple hardware based approach. This allows the incorporation of the DSSG in existing microprocessors (General purpose and embedded) with minimal design overheads.

- 6. The DSSG finite state machine does not rely on any memory like structure reducing the layout footprint and the overall power consumed to achieve the higher prediction accuracy targeted by the DSSG.

- 7. The DSSG exhibits low power consumption, in the order of 300  $\mu W$  to achieve accuracies up to 80% in predicting the length of the standby period.

In summary, the principal objective of this part of the research is to devise an accurate prediction methodology that allows circuit designers to explore novel low leakage power management schemes.

### **1.1.2** Dynamic Power in Global Interconnects

Global interconnects are gradually dominating the performance of deep sub-micron chips. In fact, the number of interconnects and buffers for achieving timing closure are one of the primary challenges facing designers for sub-90nm ICs. This is attributed to the continual increase in the number of logic blocks, due to the continuous shrinking of device dimensions. To mitigate the impact of the interconnects, designers have shifted their focus to interconnect centric designs, where the wire is the center of the chip design flow [7].

The interconnect problem is a multi-objective optimization problem, where delay, power, and routing are core objectives. Traditionally, delay and routing have been the focus of most optimization efforts [7]. However, the power consumption of the interconnects is becoming a crucial factor in determining the overall chip performance [8]. Research in [9] shows that global signaling nets can consume up to 21% of the total dynamic power [10]. To address the interconnect bottleneck, researchers have developed several subproblems that deal with the various aspects of the interconnects. These problems begin with the simple problem of *buffer insertion*, determining the number and the positions of buffers to minimize delay [11], and increase in complexity up to *Optimal Power Maze Routing*, where a combined routing and power optimization under relaxed delay constraints is introduced [12, 13].

Research in [12-19] focused on the low power interconnect problem through optimum buffer insertion. The main limitation facing many of the interconnect power minimization efforts is the lack of simultaneous optimization of the various interconnect performance metrics. As an example, the work in [14, 15] focuses on only single net optimization which inherently implies a net ordering effect. The net ordering effect means that for successful chip timing closure the nets has to be ordered according to their importance. This ordering limits the ability of the technique to find globally optimum solution. In the meantime, the research in [16–19] focuses on the optimum buffer insertion assuming prerouted nets. This in turn limits the ability of the technique to prevent congestion in general and especially buffer related congestion where the availability of buffer insertion locations is contested by several nets. Finally, to address some of the limitations, the work in [12, 13]<sup>1</sup> simultaneously routes the interconnects while inserting the buffers to optimize for the power consumption. However, the effort in [12] focuses only on two-pin nets while the work in [13] is characterized with excessively long runtime.

On the other hand, analytical solutions to the power optimization problem [20–22] are also limited in their ability to simultaneously optimize the various metrics since they depend on mathematically differentiating some cost function with respect to one parameter. In addition, these techniques are incapable of accommodating the buffer blockage arising from the preplaced blocks.

In order to address the limitation of the previous techniques, a formulation for a power-efficient interconnect optimization technique is proposed in this work. The goal is to find a solution through the formulation of a Power-Efficient multi-pin Integer linear programming based global Routing Technique (*PIRT*). The new formulation simultaneously solves for a minimum power tree for each global net in the chip without affecting the chips maximum frequency requirements.

#### Contributions

The technical contributions of the newly formulated PIRT can be summarized as follows

<sup>&</sup>lt;sup>1</sup>This work is the authors pervious contributions in the power optimal interconnect optimization.

- 1. Unlike previous approaches, the newly developed approach is capable of timing optimization, buffer insertion and power reduction simultaneously with routability consideration.

- 2. The optimization of power consumption and simultaneously accounting for the buffer blockage, which has not been considered in previous analytical formulations of the power optimization problem, is formulated.

- 3. The optimization of the power consumption without affecting the chip's maximum frequency.

- 4. The problem is formulated so that it is independent of the delay and the power models used, allowing for more flexibility in applying the new technique to scaled technologies.

- 5. PIRT is capable of simultaneously routing and power optimizing the chip with runtime less than 0.1 second per net.

In conclusion, the goal of the novel multi-pin power optimization methodology is to devise a fast, yet accurate technique to reduce the power consumption of global interconnects while maintaining the chip's maximum clock frequency.

## **1.2 Thesis Organization**

To formulate the concept of standby prediction and the multi-pin global routing problem, it is important to explore relevant topics. Accordingly, in Chapter 2, the physical nature of the VLSI power consumption problem is described.

Chapter 3 presents the architecture of generic superscalar and SMT processors, exploring the various building blocks of state-of-the-art microprocessors. After a discussion of the concepts of power consumption and microprocessor architecture, the most popular circuit-level leakage control techniques are reviewed in Chapter 3. This is followed by a description of the various system-level techniques available for the reduction of microprocessor power consumption. The focus is on low-power pipelines and low-power software design. Chapter 3 is concluded by reviewing some of the profile prediction literature.

In Chapter 4 after the concept of standby prediction is introduced, the results of applying the DSSG to the SPEC2000 benchmark suite on a Superscalar processor are

given. These results are obtained by modifying the SimpleScalar performance simulator in order to extract the functional units' usage patterns.

Chapter 5 details the results of running the DSSG on an SMT architecture using the SMTSIM simulator to extract the functional units' usage patterns. Chapter 5 also presents the results of applying the SSSG and the DSSG on several microprocessor architectures.

Chapter 6 starts by reviewing the state-of-the-art techniques for power optimal interconnect optimizations. Then, the chapter presents the new formulation of the low power global routing problem (PIRT). In addition, the results of running PIRT on the IBM and ISPD floorplan benchmarks is discussed.

Lastly, the thesis is concluded by outlining the major contributions of this research and the potential enhancement in future work.

# Chapter 2

# **CMOS Power Consumption**

CMOS circuits are the foundation for most modern microprocessors. The CMOS technology offers high density, high performance with low power consumption. To tackle the microprocessor power management problem it is imperative is to explore the physical nature of CMOS power consumption. Accordingly, this Chapter presents the fundamentals behind the sources of power consumption in CMOS circuits.

## 2.1 Technology Scaling

The semiconductor industry has been aggressively pursuing an ever shrinking minimum feature size. The shrinking minimum feature size allowed for lower cost per function, higher frequencies and compact light-weight electronics [23].

Constant field scaling proposed by Dennard et al. in [24] entails the continuous reduction of the vertical and horizontal dimensions while simultaneously scaling the applied voltages to maintain constant electric fields across the smaller devices [25]. The constant electric field scaling ensures the reliability of the scaled devices by limiting hot carrier injection. Table 2.1 shows the constant field scaling rules for some device and chip parameters.

Due to the continuous increase in die sizes the dynamic power consumption is increasing with each technology node. Moreover, the leakage power consumption is also exponentially increasing due to the reduced threshold voltages. In fact it is projected that a huge increase in the power density will occur with each technology node [26, 27]. Fig. 2.1 presents the projected increase in chip's power density [26]. Due to the impact of the increased dynamic and leakage power consumption modeling and understanding the

| Technology Parameter              | Scaling Factor |  |

|-----------------------------------|----------------|--|

| Device Dimension $(t_{ox}, L, W)$ | 1/S            |  |

| Voltage                           | 1/S            |  |

| Doping Concentration              | S              |  |

| Electric Field                    | 1              |  |

| Carrier velocity                  | 1              |  |

| Gate Capacitance                  | 1/S            |  |

| Drift Current                     | 1/S            |  |

| Circuit Delay                     | 1/S            |  |

| Dynamic Power Dissipation         | $1/S^{2}$      |  |

| Leakage Dissipation               | exponential    |  |

| Circuit Density ( $\alpha 1/A$ )  | $S^2$          |  |

| Power Density                     | 1              |  |

Table 2.1: Constant field scaling

nature of the CMOS power consumption is an important prerequisite before any further discussion of processor power management.

Figure 2.1: Trends of processors' power density [26].

# 2.2 Sources of Power Consumption

With the continuous scaling of CMOS technology, the semiconductor industry is slowly shifting towards more power centric designs. Typically, the total power dissipation of

CMOS circuits  $(P_{total})$  is given by [11]

$$P_{total} = P_{switching} + P_{short-circuit} + P_{leakage}, \tag{2.1}$$

where  $P_{switching}$  is the switching power,  $P_{short-circuit}$  is the short-circuit power, and  $P_{leakage}$  is the leakage power.

## 2.2.1 Switching Power

The switching power is the component of power consumption that is associated with the charging and discharging of the capacitances of the CMOS gate. A simple yet accurate estimation of the switching power of the gate is given by [6]

$$P_{switching} = \alpha V_{dd}^2 f_{clk} (C_{gate} + C_{wire}), \qquad (2.2)$$

where  $\alpha$  is the switching factor of the gate,  $V_{dd}$  is the supply voltage,  $f_{clk}$  is the clock frequency,  $C_{gate}$  is drain diffusion capacitance at the output and the total input gate capacitances of the subsequent gates, and  $C_{wire}$  is the total wire capacitance at the fan-out of the gate. Fig. 2.2 presents the basic capacitive sources in a CMOS inverter.

Figure 2.2: Sources of output load capacitance.

It is interesting to note that the switching power consumption is quadratically dependant on the supply voltage [28]. This dependence motivates different approaches to reduce the switching power by scaling the supply voltage. However, the scaling of the supply voltage means an increase in the leakage power, since the reduction of the supply requires a corresponding reduction in the threshold voltage. This reduction in the threshold voltage causes an exponential increase in the subthreshold leakage current.

### 2.2.2 Short-Circuit Power

Due to the fact that for actual CMOS circuits there are finite rise and fall times the PMOS and NMOS transistors are briefly on, simultaneously. This results in short circuit current flowing due to the direct path through both transistors [11].

The average short circuit power can be calculated using

$$P_{short-circuit} = t_{sc} V_{DD} I_{peak} f_{clk}$$

(2.3)

where  $t_{sc}$  is the period of time when both devices are conducting,  $V_{DD}$  is the supply voltage,  $I_{peak}$  is the peak current flowing during the period of  $t_{sc}$ , and  $f_{clk}$  is the clock frequency

### 2.2.3 Leakage Power

The quadratic dependence of the switching power on the supply voltage can be utilized to reduce the switching power [28]. In fact, the reduction of the supply voltage is also bound to the scaling of the device's dimensions. For example, the reduction of the gate oxide thickness limits the value of the maximum electric field tolerated on the gate, which imposes an upper bound on the supply voltage. Nevertheless, reducing the supply voltage forces the reduction of the threshold voltage of the devices in order to maintain the overdrive voltage ( $V_{GS} - V_{th}$ ). This leads to an exponential increase in the subthreshold leakage current [29].

Indeed, leakage power is expected to dominate the overall power consumption as the technology scales [28]. This is confirmed by the trend reflected in Fig. 2.3, where the leakage power will constitute more than 50% of the total power consumption for the technologies beyond 65nm if it is not properly addressed.

The leakage power consumption due to the subthreshold current can be calculated using the expression,

$$P_{leakage} = V_{dd}I_{sub},\tag{2.4}$$

Figure 2.3: Leakage power consumption as a percentage of the total power for various technology nodes [29].

where  $I_{sub}$  is the subthreshold current which is computed by the following [30]:

$$I_{sub} = I_0 e^{(V_{gs} - V_{th})/mV_T} (1 - e^{-V_{ds}/V_T}),$$

(2.5)

where m is the subtreshold swing coefficient,  $V_{th}$  is the threshold voltage, and  $V_T = KT/q$  is the thermal voltage.

Although this research focuses on subthreshold leakage control techniques, the following section describes briefly the various sources of leakage current in today's CMOS circuits.

#### 2.2.3.1 Sources of Leakage Current

The various components of the leakage current can be summarized as follows [28]

- *PN junction reverse leakage*; this occurs due to the minority carrier drift near the depletion region, this current is usually small and can be neglected. However, if the electric field across the reverse biased PN junction reaches  $10^6 V/m$ , significant current will flow due to band to band tunneling [31].

- *Drain induced barrier lowering*; due to the relative size of the drain/source depletion width in the vertical dimension to the channel size, the source drain potential affects the band bending over a significant portion of the device width. Higher drain potential in effect reduces the transistor threshold, increasing its leakage [30].

- *Gate induced drain leakage*; this occurs at negative  $V_G$  and high  $V_D$ , which causes a high electric field under the gate drain overlap region causing significant band to band tunneling.

- *Gate oxide tunneling*; this is due to the tunneling of electrons through the gate oxide especially when the electric field is very high coupled with small oxide thickness.

- *Subthreshold leakage*; this is the current flowing between the source and the drain when the transistor is in the weak inversion and the gate voltage is below the threshold voltage. This component is exponentially dependent on the threshold voltage, currently making it the most critical component of leakage power consumption.

# 2.3 Managing CMOS Power Consumption

Several techniques have been envisioned to manage the increasing strain on the chip power budget. These techniques vary based on the time of application between design time, sleep mode and runtime power management schemes [11]. Table 2.2 summarizes some of the major vehicles of power management available to processor designers.

|               | Design Time                        | Sleep Mode   | Run Time |

|---------------|------------------------------------|--------------|----------|

|               | Lower $V_{dd}$ , Multi- $V_{dd}$ , |              | Dynamic  |

| Dynamic Power | Sizing,                            | Clock Gating | Voltage  |

|               | Logic optimization                 |              | Scaling  |

| Laskaga Dowar | Multi- $V_{th}$                    | VTCMOS,      | VTCMOS   |

| Leakage Power |                                    | MTCMOS       |          |

Table 2.2: Power management

## 2.3.1 Dynamic Power Management

To reduce the dynamic power consumption of a microprocessor core chip designers resort to several techniques that focuses on manipulating the various parameters in equation 2.2. Transistor sizing and logic optimization targets the reduction of the total capacitance that is switched each cycle. Logic optimization can also help reduce the dynamic power consumption due to glitching. Reducing the supply voltage as mentioned earlier quadratically influences the overall power consumption. Low- $V_{dd}$  designs in portable and medical applications tremendously extends the battery lifetime at the expense of slower performance.

On the other hand Multi- $V_{dd}$  designs allows for the reduction of the power consumption of non-critical components while maintaining the performance of mission critical logic. Multi- $V_{dd}$  designs face challenging requirements with respect to their power delivery network, where multiple supply rails are required in addition to level converters between voltage islands.

Dynamic voltage scaling (DVS) allows the designers to scale the voltage down when the application requirements are low and increase it when the demand is high. Similar to Multi- $V_{dd}$ , the power delivery and level converters are some of the limitation for DVS techniques. In addition to DVS, clock gating is a very effective technique to reduce the dynamic power when the logic is not utilized. However, clock gating does not tackle leakage power consumption.

Since both DVS and clock gating techniques act at the circuit level they require system level policies to ensure the power-performance trade off is maintained across various workload requirements.

## 2.3.2 Leakage Power Management

Multi- $V_{th}$  technologies allow designers the flexibility of using low-threshold high-leakage devices to build the logic of critical paths while using high-threshold low-leakage devices in non-critical paths. Multi- $V_{th}$  designs require careful attention to path selection since the slow down introduced to non-critical paths might cause them to become the critical paths in the design.

VTCMOS techniques allow the designer to change the threshold of the devices during runtime or sleep mode. Changing the threshold allows the logic to manage its leakage at the expense of some performance loss. MTCMOS designs allow for an aggressive shutdown of the supply network to limit the overall leakage. MTCMOS and VTCMOS design also require system level policies to ensure maximum performance.

In this research the dynamic sleep signal generator technique will target the management of leakage power in standby mode while the interconnect optimization effort targets the design time dynamic power minimization. In the following chapter, an overview of the state-of-the-art microprocessors' architectures is presented. In addition, a more detailed survey of the low leakage circuit and system-level techniques is conducted.

# Chapter 3

# Microprocessor Leakage Power Management

In order to establish the background necessary for the advanced leakage management technique proposed in this thesis, the study of the modern microprocessor architecture is crucial. In addition, modern leakage management techniques need to be investigated.

# 3.1 Microprocessor Architecture

State-of-the-art general purpose processors result from pursuing the latest techniques that can enhance the execution throughput. Microprocessors, from the software perspective, are designed to perform as a sequential engine,<sup>1</sup> capable of handling sequential sets of instructions and producing sequential output that matches the program order of instructions. This is simply described by considering pipelined processor architectures. These architectures divide the tasks, corresponding to the code execution, among a set of hardware blocks.

Single pipelined processors are especially useful for embedded applications, where the processors satisfy the computational requirements without the need for the more complicated superscalar architectures. In contrast to single pipelined processors, superscalar processers are capable of handling more than one instruction in each cycle. This nature allows the superscalar processor to increase its throughput by exploiting some of the inherent Instruction Level Parallelism (ILP) in the application code [1]. Finally, Si-

<sup>&</sup>lt;sup>1</sup>This statement excludes explicitly parallel coding techniques that expect a multi-engine architecture. This multi-engine includes multi-processors and multi-core chips.

multaneous Multithreading (SMT) processors enhances the performance of superscalar processors by running multiple applications simultaneously.

### **3.1.1 Pipelined Processors**

Pipelining is a means of fully utilizing the hardware capabilities. It allows for a slightly increased latency in the processor operation, while significantly increasing the processor throughput.

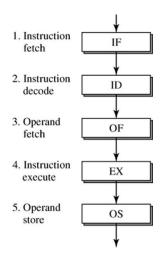

Fig. 3.1 illustrates a simple pipelined processor. Each stage is attached to the next by a latch that is capable of storing the results of stage n that are used by stage (n + 1), while stage n is performing the next task.

Figure 3.1: Pipelined processor [1].

Perfect pipelining requires that the executed code be divisible in a uniform set of steps that requires, approximately, similar execution times. Consequently, the latency of the various stages is expected to be approximately equal, ensuring that the pipelined stages are utilized to their maximum without any one stage completing the job ahead of the others. This is not naturally achievable, since some pipeline stages such as multipliers and dividers are inherently slower than other stages.

In addition to the divisibility, perfect pipelines assume that the code is generally repetitive. This translates into similar resource requirements for each executed instruction. In reality, executed instructions vary in their resource requirements, causing the pipeline stages to idle when not in use.

Finally, the major goal of the pipeline design is to minimize the inter-instruction dependencies. These dependencies cause the pipeline to stall, where stage n waits for

stage (n-1) to finish its job, because stage n needs the results of stage (n-1) [1].

In order to address some of the limitations of scalar pipelines, superscalar processors are discussed.

### 3.1.2 Superscalar Processors

Superscalar processors are an attempt by processor architects to increase the performance of the scalar pipeline. The main challenges of scalar pipelines can be summarized as follows [1].

- The performance of the scalar pipeline can be enhanced by reducing the number of instructions per program, reducing the number of Cycles per Instruction (CPI), or by increasing the clock frequency. However, the upper bound on the average Instruction per Cycle (IPC) is always one, since only one instruction can be fetched per cycle.

- The unified resource nature of a scalar pipeline proves inefficient when the instructions are not similar. For example, floating point, integer, and memory instructions are inherently difficult to unify, since they require fundamentally different resources.

- A pipeline that stalls due to data dependency is also a major deficiency. Since many of the stalls are avoidable if the pipeline is able to jump the stalled instruction and proceed to execute the non-dependent instructions.

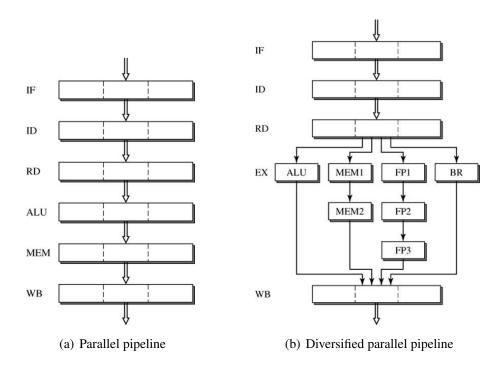

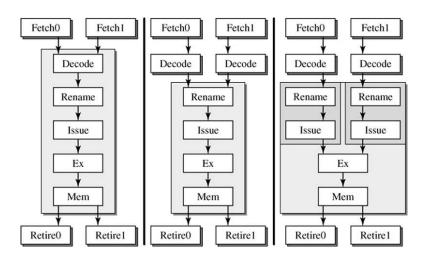

The first approach to enhance the performance by increasing the IPC is to use simple replicates of a scalar pipeline, represented in Fig. 3.2(a). This ensures that the processor is capable of issuing more than one instruction per cycle, and in theory, raises the bound on the IPC to *s*, where *s* is the number of the parallel stages. However, simply replicating the pipeline does not solve the problem of the diversified requirements of the executed instructions. As a result, diversifying the pipelines is more adequate, since it allows for the customization of the instruction path to the instructions' resource requirements (Fig. 3.2(b)). To diversify the pipelines, the processor employs different functional units at the execution stage, allowing the processor to route the instructions in the pipeline depending on their requirements.

Early generation superscalars employed diversified pipelines, where the instructions are issued, decoded, and then forwarded to the execution stages without buffering, as

Figure 3.2: Generic superscalar pipeline [1].

long as the instructions are not dependent on other instructions. Processors such as the Alpha 21064, PowerPC 601, and the Pentium adopted such *direct issue* designs [32]. However, the major bottleneck for direct issue designs, is the blocking of the issue stage, when existing instructions are waiting for the unresolved dependencies.

Another major problem introduced by superscalar pipelines is the increased requirements in the cache bandwidth. Superscalar processors are capable of issuing more than one instruction per cycle, implying that for an *s*-wide pipeline, a corresponding *s*-wide Instruction Cache (I-Cache) is needed. In addition, a multi-port Data Cache (D-Cache) is needed, since more than one instruction may be requesting a read or write operation.

In addition to the memory bandwidth issue, branch misprediction penalties increase with wider pipelines. Branch penalties are the cost of recovery from mispredicted branches. The wider pipelines can increase the frequency of the branches per cycle, and thus, increase the chance of misprediction [32].

For later generations of superscalar processors, the solution for the problem of direct issue involved employing an Out-of-Order (O-o-O) execution. In the O-o-O scheme, the instructions, in theory, are only bound in their sequence of issuance, if they have data dependencies. In practice, Superscalar processors employ the hybrid technique denoted in Fig. 3.3, where the front end of the superscalar processor is an in-order fetch-decode-dispatch, followed by a reservation station, and then an out-of-order execution stage with

a reorder buffer, and finally, an in-order backend.

Figure 3.3: O-o-O superscalar processor [1].

### 3.1.2.1 Superscalar Pipeline Stages

The superscalar architecture can be explored by following the steps of an instruction execution in an s-wide processor [1]. This is composed of five steps

- Instruction Fetch (IF)

- Instruction Decode (ID)

- Instruction dispatch

- Instruction Execution (IE)

- Instruction completion and retirement

**Step 1: Instruction Fetch (IF)** The goal of the instruction fetch stage is to communicate with the I-Cache as quickly as possible to maximize the fetch bandwidth and attempt to fetch *s* instructions per machine cycle. The I-Cache is organized in blocks, containing consecutive instructions of the program. The program counter is used to search the I-Cache to determine if the requested instruction is in the I-Cache (cache hit) or not (cache miss) [33].

Typically, the fetch rate, measured in instructions per cycle, must match the maximum decode and execution rate, and in practice, is designed to be slightly higher to allow for cache misses or situations when fewer than the maximum instructions can be fetched. These situations arise when there is a misalignment of the fetched instructions block<sup>2</sup> with the cache boundaries. This causes the fetch stage to fetch only the instructions within the cache boundary in one cycle, then fetch the rest of the instruction block in the following cycle. This problem can be solved through a compile time I-Cache alignment or run-time hardware alignment [1].

**Step 2: Instruction Decode (ID)** The ID is responsible for identifying the instructions, determining the instruction types, and detecting the inter-instruction dependencies for the instructions that have been fetched but not yet dispatched.

In the Reduced Instruction Set Computer (RISC) architectures, the decode stage is simple, since it does not need to check for instruction boundaries. This substantially simplifies the decode operation and allows it to be merged with the register reading. In addition, the ID stage of a RISC processor is responsible for quickly identifying the control flow instructions in the fetch block in order to provide prompt feedback to the IF stage.

Contrary to the RISC, the Complex Instruction Set Computer (CISC) ID is quite complex. Besides the primary responsibility of the ID to identify the instructions, the CISC ID needs to identify the unfixed instruction boundaries. Moreover, the ID must translate the CISC instruction to its RISC-like operations, corresponding to the micro-operations ( $\mu$ OPs) in the Intel and RISC operations (ROP) in AMD.

Predecoding is sometimes useful to reduce the burden on the CISC ID. The CISC instructions are partially decoded on their way from the memory to the I-Cache. These instructions and a set of pre-decode bits are saved in the I-Cache, simplifying the decode operations. However, predecoding introduces two problems: an increased I-Cache miss penalty due to the increased overhead and extra storage requirements for the pre-decode bits.

<sup>&</sup>lt;sup>2</sup>A fetch instruction block is the set of instructions that needs to be fetched together by the IF stage.

Another task for the ID stage is register renaming. This is required because modern processors contain physical register files that are larger than the architectural register files [33]. The physical registers can be used to solve false data dependencies. Data dependencies will be revisited in more detail in Section 3.2.3.1.

**Step 3: Instruction Dispatch** Contrary to scalar processors, superscalar processors need an instruction dispatch stage to route instructions to the corresponding functional units, depending on the resource requirements of these instructions.

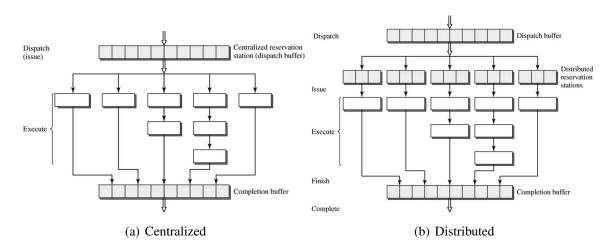

Instruction dispatching uses a reservation station which is a temporary buffer that holds the instructions that have been decoded, but not all its operands are ready. For example, those instructions that are dependent on an earlier instruction write to the register file (RF).

Reservation stations can be centralized, similar to the one denoted in Fig. 3.4(a). These stations provide the full capability of an O-o-O execution processor, since any instruction can be dispatched to any functional unit. However, the underlying complexity of the routing fabric limits the practicality of such stations in a wide superscalar processor. On the other hand, distributed stations in Fig. 3.4(b) are a partial solution to this problem. They allow the functional units to have their own buffers for queuing purposes, and keep a smaller dispatch buffer to perform the global routing of the instructions to the functional units' buffers. This reduces the routing complexity without eliminating the advantages of the O-o-O execution.

Figure 3.4: Reservation station [1].

**Step 4: Instruction Execution (IE)** In this stage, the instructions utilize the resources of the functional units to perform the intended task of each instruction.

The trend is towards massively parallel IE stages, and the specialization of the functional units. This allows for more performance efficiency, since the dedicated functional units are used instead of a general purpose alternative.

The R10000 MIPS superscalar processor is a good example of such diversity. The integer execution stage of the R10000 contains two integer ALUs. The first ALU consists of a 64-bit adder and branch condition logic; the second ALU has a partial integer multiplier array and an integer divide logic. The floating-point execution stage contains a floating-point adder for addition, subtraction, comparison, and conversion, besides a floating-point multiplier for the multiplication and move operations. Finally, the R10000 contains a dedicated floating-point divide and a square root unit [34].

**Step 5: Instruction Completion and Retirement** After execution, the instructions are stored in the completion buffer, and are allowed to retire when they are done writing to the memory.

In this stage, the in-program order of the instructions is restored through the reorder buffer. The need for reordering is evident when the interrupt and exception handling is taken into account. Both interrupts and exceptions require that the processor retains its architectural machine state, and presents it as if the program is executed in order.

The reorder buffer is employed to handle this situation. The instructions enter the reorder buffer out-of-order and exit in-program order. The instructions that cause exceptions are flagged, and when they reach the exit of the reorder buffer, they are held until all the previous instructions are retired. Then, all ensuing instructions are discarded.

## 3.1.3 SMT Processors

To address the main limitation of Superscalar processors namely the absolute dependence on the instruction flow from a single application, SMT processors are devised. The applications running on a superscalar architecture do not make the best use of the available resources due to the latencies introduced by the memory system, branch mispredictions, and dependencies on high latency instructions.

Because of these latencies, the application remains idle, waiting for the data to arrive or the dependence to be resolved. This idleness results in a low usage of pipeline resources in superscalar processors that has led to the SMT architecture [35].

Such architectures execute several applications on the same pipeline and at the same time. This results in a better usage of the available resources, and serves also as a latency hiding technique. When an application is on hold, waiting for the data to arrive from the memory, for example, another application continues to be executed. Therefore, the SMT architecture has a higher throughput with a system that combines a superscalar capability and multithreading.

However, when several applications are simultaneously run on the processor, the behavior is entirely different from that of a single application workload. When several applications share the pipeline resources, two things occur. The first is that the utilization of these resources is expected to increase, increasing the power dissipation. The second thing is that the behavior of these resources, in terms of the busy and idle periods, becomes less predictable.

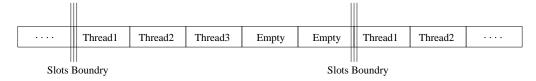

#### 3.1.3.1 SMT scheduling and resource sharing

**SMT scheduling:** The goal of multi-threaded processors is to maximize the sharing of the processor resources between requesting threads. Earlier implementation of fine-grained multithreading included round robin techniques which allotted specific time slots to each thread [1]. This implementation has maximum utilization of the resources if the number of threads are equal to the available time slots, otherwise the processor will idle during the empty time slots (Fig. 3.5). In addition, single thread performance is heavily impacted due to the unnecessary latency associated with the round robin implementation. To mitigate the drawbacks of fine-grained multithreading coarse-grained multithreading is introduced where the processor switches between threads when the pipeline stalls on long latency events. Hence, the processor pipeline is utilized by an alternate thread while the initial thread awaits the resolution of the stall (Fig. 3.6). The challenge for the course-grained processor is to make sure that each thread enjoys a fair chance in getting execution resources, a tough task when the stall profile of the executing threads is different.

Figure 3.5: Fine grained Multithreading.

Simultaneous multithreading (SMT) combines a fine-grained implementation with the ability to dynamically switch between instructions from multiple threads as shown in Fig. 3.7. The SMT is very well suited to run on out-of-order processors since the instructions are already decoupled in their execution from the program order.

| <br>Thread1 | Thread2 |  |

|-------------|---------|--|

| Λ./*        |         |  |

Long latency stall

Figure 3.6: Coarse grained Multithreading.

|  | Thread1 | Thread2 | Thread3 | Thread2 | Thread2 | Thread1 | Thread2 |  |  |

|--|---------|---------|---------|---------|---------|---------|---------|--|--|

|--|---------|---------|---------|---------|---------|---------|---------|--|--|

Figure 3.7: Simultaneous Multithreading.

**Resource sharing:** In order to implement an SMT processor the resources available to the threads has to be modified to allow multiple threads to proceed in the processor pipelines [1]. The choice between the various implementations in Fig. 3.8 is controlled based on the efficiency of sharing each processor block between the various threads.

Figure 3.8: SMT resource sharing [1].

Designing the SMT pipeline requires the designers to choose between a single shared pipeline stage versus a partitioned stage. A single shared pipeline stage allows for maximum single thread performance since the pipeline stage is completely available to each thread. Partitioning the pipeline stage limits the single thread performance when there are no competing threads. However it significantly simplifies the design of the pipeline stage. The main limitation of the sharing of the fetch stage lies in the instruction cache [1]. Accordingly, modern SMT implantation similar to SUN's Niagara processor uses a shared fetch stage while multiplexing the requests to the instruction cache [36]. Using the same thread multiplexing logic, a decode stage can be shared overriding the complexity of extending a single interleaved decode stage between threads and the associated difficulty of resolving the instruction dependencies of unrelated threads [36]. Since the register re-

naming involves the translation of the architectural registers to the shared pool of physical registers, simultaneous accesses can be easily accommodated. The execution stage with its diversified resources can very well be simultaneously accessed from multiple threads with minimum overheads.

Sharing the memory is fairly straightforward using multi-port caches. However, the complexity of sharing the load-store queue might warrant the partitioning of the queues based on the number of threads. Finally, the retire stages is better partitioned between threads [1]. In summary, the decision of sharing each of these resources is a tradeoff between single thread performance and the hardware complexity. An interleaved stage allows for better single thread performance at the expense of a complex hardware to resolve the thread specific information and vice versa.

In order to complete the background of processor power consumption, the following section presents an overview of the leakage power management techniques available for state-of-the-art processors.

# **3.2 Leakage Power Management Techniques**

As mentioned in Section 1.1, to successfully design a low power microprocessor, the designer needs to consider the combined effects of the system, the algorithm, and the circuits. Accordingly, to formulate the proposed standby prediction methodology, it is also important to explore the most popular circuit and system-level leakage control techniques. In the following Sections, various dynamic low leakage circuit techniques available to VLSI designers are explored. In particular, power gating is further discussed since it is later used as a test vehicle for the dynamic sleep signal generators. Then, in Section 3.2.3, the combined application of these circuit techniques and system-wide measures to exploit the power saving potential is explained. Finally, building on the circuit and system low-power foundation, Section 3.2.4 introduces some of the compiler and architecture-based program profiling techniques that are relevant to the task of standby prediction.

## 3.2.1 Leakage Power Management Overview

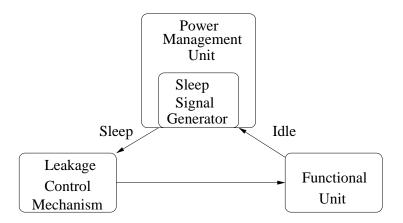

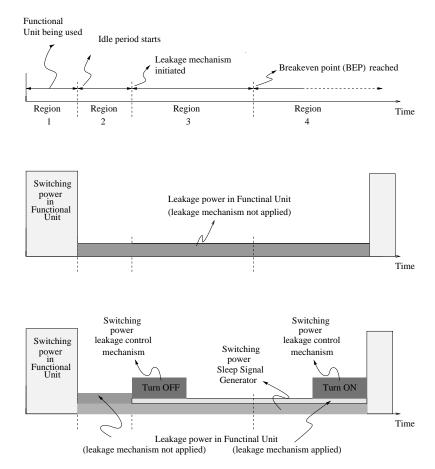

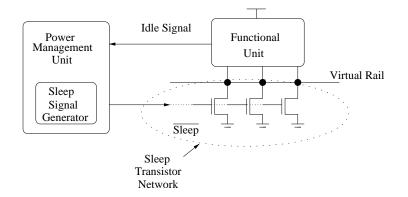

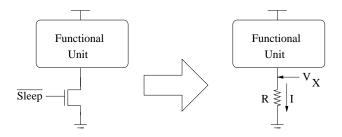

Referring to Fig. 3.9, the task of leakage control is divided between two major components; the leakage control mechanism, and the sleep signal generator.

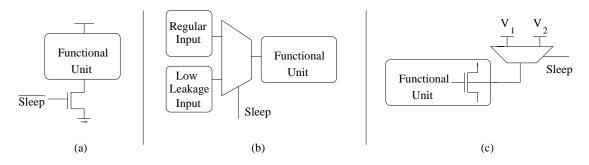

Many leakage control mechanisms have been studied [3, 28, 30, 37–40]. Power gating circuit techniques are based on shutting down parts of the circuit which employ high

Figure 3.9: Dynamic leakage control.

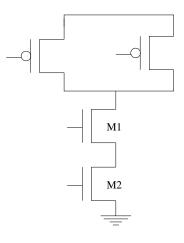

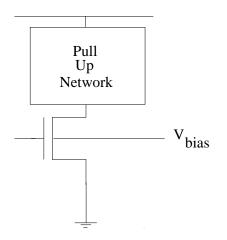

threshold transistors between the functional units and the supply rail (Fig. 3.10(a)) [28]. The high threshold transistors exhibit 10 times less leakage than low threshold transistors [30]. Accordingly, turning off these transistors during standby reduces leakage of the whole functional unit [37]. Alternatively, input vector activation is based on changing the inputs of the circuit to reduce its leakage (Fig. 3.10(b)). The leakage reduction results from the dependence of the transistor leakage on the number of OFF transistor between the supply and ground. Accordingly, maximizing the number of OFF transistors in standby reduces the overall leakage [38]. Finally, since transistor leakage is exponentially related to the transistor threshold voltage, adaptive body biasing techniques reduce the functional units' leakage in standby by raising the transistor threshold voltage (Fig. 3.10(c)). Raising the threshold voltage is achieved by applying a reverse bias to the transistor body [3, 39, 40].

Figure 3.10: Dynamic leakage control mechanisms a) Power gating. b) Input vector activation. c) Adaptive body biasing.