# Integrated MEMS-Based Phase Shifters

by

Reena Al-Dahleh

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Reena Al-Dahleh, 2008

## **Author's Declaration**

I hereby declare that I am the sole author of this thesis.

This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Reena Al-Dahleh

### Abstract

Multilayer microwave circuit processing technology is essential in developing more compact radio frequency (RF) electronically scanned arrays (ESAs) for the next generation radar and space-based systems. ESAs are typically realized using the hybrid connection of four discrete components: the RF manifold (combining network), phase shifters or Butler matrices, antennas and T/R modules. The hybrid connection of these separate and conventional components increases the system size, packaging cost and introduces parasitic effects that result in higher losses. In order to eliminate these drawbacks, there is a need to integrate these components on the same substrate, forming a monolithic phased array. With the recent advancements in the field of microelectromechanical systems (MEMS) and micromachining technology, miniaturized RF MEMS components including switches and phase shifters have been demonstrated with superior performance. RF MEMS technology enables the monolithic integration of the ESA components into one highly integrated multifunctional module, thereby enhancing ESA designs by significantly reducing size, fabrication cost and interconnection losses.

In passive ESAs, the RF combining network and phase shifters are placed between the T/R module, which contains low noise amplifiers (LNAs) and power amplifiers (PAs), and the antenna elements. The insertion loss of the phase shifter and of the combining network is a key design consideration as it directly impacts the transmitted power and the receiver's noise figure. Conventional wide-band digital true-time-delay phase shifters are mostly built using switches made of p-i-n diodes, MESFETs or high electron-mobility transistors (HEMTs), and the insertion loss is usually in the range of 4 to 6 dB at X-band for a 4-bit design. The use of high loss phase shifters necessitates that the T/R module compensates for this loss with a higher transmit RF power. This in turn results in more DC power consumption and the use of a larger size and a higher cost T/R module. MEMS switches exhibit a lower loss and lower DC power consumption in comparison to their semiconductor counterparts. Therefore, they can be used for the realization of a MEMS phase shifter with a performance that is far superior than that of existing commercial semiconductor phase shifters.

For the first time, a novel capacitive shunt MEMS switch design is presented that utilizes warped beams to enhance its RF performance without drastically influencing the mechanical performance. Various capacitive switch spring configurations using the proposed warped beam concept are investigated both theoretically and experimentally. A dual-warped beam MEMS switch with an off-to-on capacitive ratio of almost 170 is achieved without the need for thin dielectrics or high dielectric constant materials. It exhibits excellent RF performance and mechanical reliability with isolation better than 40dB and switching speeds as low as  $6\mu$ s. These MEMS switches are implemented into single pole three throw (SP3T) and single pole four throw (SP4T) configurations.

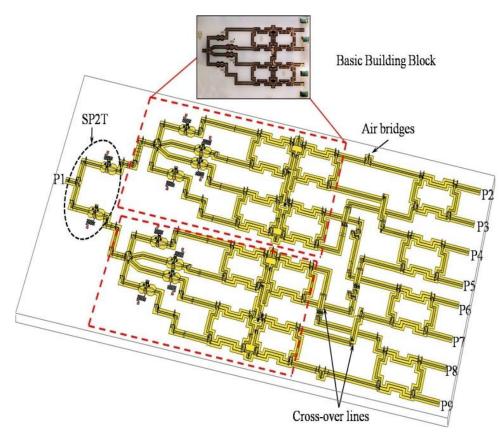

A novel 3-bit finite ground coplanar (FGC) waveguide switched delay line MEMS phase shifter is developed with four cascaded SP3T dual-warped beam capacitive switches to achieve low-loss performance and simplify the ESA design. The fabricated prototype unit for the MEMS phase shifter exhibits an insertion loss of  $2.5\pm0.2$ dB with an rms phase error of  $\pm6^{\circ}$ . Moreover, a compact 4 x 4 Butler matrix switchable with the use of a MEMS single-pole four-throw (SP4T) switch is investigated as an alternative passive beamforming method. The overall beam-switching network is monolithically integrated within a real-estate area of only 0.49cm<sup>2</sup>. Air-bridge crossovers are implemented to maintain compatibility with the MEMS fabrication process utilized for the SP4T MEMS switch. This technique provides a unique approach to fabricate the entire beamforming network (BFN) monolithically. It also demonstrates the potential for scalability to larger more complex systems.

An 8-mask fabrication process is developed that allows the monolithic integration of the MEMS phase shifters and the RF combining network on one substrate. This modular approach integrates the capacitive-coupled interconnects, a 3-bit MEMS phase shifter and a power divider, thereby achieving a significant breakthrough in size, weight and cost while maintaining good RF performance. This novel monolithic integration process reduces fabrication costs in offering low packaging and assembly complexity. The wafer-scale three-dimensionally integrated ESA prototype unit has an area of 2.2cm<sup>2</sup>. It serves as the basic building block to construct larger scanning array modules and introduces a new level of functionality previously achieved only by the use of larger, heavier and expensive systems.

### Acknowledgements

I wish to express sincere appreciation and gratefulness to my advisor Professor Raafat Mansour for his knowledge, insight, valuable guidance and contagious enthusiasm throughout this research. Indeed, my gratitude to him cannot be expressed in a few words and it was an honor to be his student. I have gained a life-long role model to which I look up to and hope to follow in his footsteps. I am also grateful to Professor Sivoththaman and Professor Nieva for sharing their expertise and knowledge in processing and mechanical modeling. I would like also to thank Professor Antar, Professor Chaudhuri, Professor Sivoththaman, and Professor Nieva for serving on my committee and for their constructive criticism and feedback. Financial support was provided by the Natural Science and Engineering Research Council of Canada (NSERC) and COMDEV. Their contribution is greatly appreciated.

I would like to recognize my officemate Paul Laforge for putting up with me for those four years; I will forever remember the many great conversations we've had about all subjects in life. He will make an excellent professor and mentor one day. Thanks to Bill Jolley, Roger Grant and Stella Chang for their constant support and guidance, and for giving me those laughs when I needed them the most. I would like to especially thank Siamak Fouladi for his laid back attitude and for admitting that I'm always right! My eternal gratitude to KarMun Cheng, Tiana Robinson, Cherilyn Carrara and Amira Aker, whose humor, unconditional support and strength made every day enjoyable, and I am profoundly thankful.

Last but certainly not least I have to express my everlasting gratitude to my Dad and Mum who have inspired me to be the best that I can be. They gave me all the tools in life to be able to succeed, and taught me never to stop achieving, and to never settle for less than best. I derive my strength from the strength they exuded through all their battles in life. I am eternally indebted to my brother, my best friend and rock throughout the grueling past few years; he made me believe that I can be a great professor one day. Thank you to my sister for bringing in one of my biggest joys into this world, my nephew Jad, which I hope I will one day inspire to be the best that he can be. I would also like to recognize my fiancé Fareed who made the last tough stages a breeze.

### **Dedication**

I would like to dedicate this thesis to my mother Narrivana Al-Dahle and my father Jihad Al-Dahle for their infinite love and support.

I would also like to dedicate this thesis to my biggest inspiration, my cousin Mohammed Dahleh, who was robbed of reaching his full potential of being an excellent researcher and engineering professor at the young age of 39 by colon-liver cancer. I hope I can follow in his path of being a wealth of knowledge, a dynamic and creative personality with a calming presence.

## **Table of Contents**

| 3.3.1 Design                                               | 72  |

|------------------------------------------------------------|-----|

| 3.3.2 Measured Results                                     | 74  |

| Chapter 4 ESA Individual Components                        | 75  |

| 4.1 Introduction                                           | 75  |

| 4.2 MEMS Integrated Phase Shifter                          | 76  |

| 4.2.1 Design                                               | 76  |

| 4.2.2 Fabrication Process                                  | 78  |

| 4.2.3 Measured Results                                     | 81  |

| 4.3 Power Dividers                                         | 83  |

| 4.3.1 Design                                               | 83  |

| 4.3.2 Results                                              |     |

| 4.4 Capacitive Coupled Interconnect                        | 90  |

| 4.4.1 Design                                               | 91  |

| 4.4.2 Results                                              | 92  |

| 4.5 FGC 4 x 4 Butler Matrix                                | 93  |

| 4.5.1 Design                                               | 93  |

| 4.5.2 Fabrication Process                                  | 98  |

| 4.5.3 Results                                              |     |

| Chapter 5 MEMS Integrated Phase Shifter Modules            |     |

| 5.1 Introduction                                           |     |

| 5.2 Integrated Electronically Scanned Phase Shifter Module |     |

| 5.2.1 Design                                               |     |

| 5.2.2 Fabrication Process                                  |     |

| 5.2.3 Results                                              |     |

| 5.3 MEMS Integrated Phase Scanned Phased Array Module      | 116 |

| 5.3.1 Design                                               |     |

| 5.3.2 Results                                              |     |

| Chapter 6 Conclusions and Future Work                      |     |

| 6.1 Thesis Contributions                                   |     |

| 6.2 Future Work                                            |     |

| Appendix A Integrated Module Fabrication Process           |     |

| Appendix B Polyimide Characterization and Processing       |     |

| Appendix C Thin Film Resistor Characterization and Processing | 140 |

|---------------------------------------------------------------|-----|

| List of Acronyms                                              | 148 |

| Bibliography                                                  | 149 |

## List of Figures

| Figure 1.1: Proposed 3-D integrated ESA module. A 1024 element ESA can be subdivided into an                                             |

|------------------------------------------------------------------------------------------------------------------------------------------|

| array of tiles. Each tile consists of the hybrid connection of the RF feed network (transmission lines                                   |

| and power dividers), phase shifters, antennas and T/R modules1                                                                           |

| Figure 1.2: Comparison of the different integration methods. (a) Hybrid integration using two                                            |

| processed substrates and gold connectors. (b) Hybrid integration using an LTCC-processed substrate                                       |

| and surface mounted phase shifters. (c) The proposed integration method using a single substrate and                                     |

| capacitive interconnects                                                                                                                 |

| Figure 1.3: Comparison of the power requirements of a system designed with a FET phase shifter and                                       |

| a system designed with a MEMS phase shifter. Both phase shifters consume very little DC power3                                           |

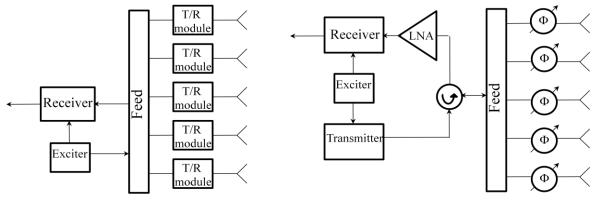

| Figure 2.1: Functional block diagram of electronic scanning methods. (a) The electronic feed                                             |

| switching method. (b) The phase scanning method [1]8                                                                                     |

| Figure 2.2: There are two types of ESA.s (a) Active ESA. (b) Passive ESA [1]                                                             |

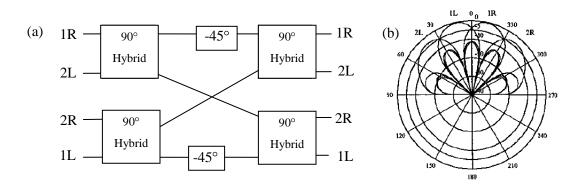

| Figure 2.3: The BM consists of four $90^{\circ}$ hybrids, two $45^{\circ}$ fixed delay lines and crossover lines. (a)                    |

| The 4 x 4 BM layout. (b) The associated radiation pattern of a 4 x 4 BM9                                                                 |

| Figure 2.4: Switched beam phased array with an SP8T PIN diode routing switch by Savium                                                   |

| Technologies [2]10                                                                                                                       |

| Figure 2.5: Hybrid 8x8 Butler matrix connected to the 8x2 microwave switch matrix [3]10                                                  |

| Figure 2.6: 16-element phased array antenna using Ba <sub>0.6</sub> Sr <sub>0.4</sub> TiO <sub>3</sub> . This ferrite-based phased array |

| requires actuation voltages of up to 250V and is 11.9cm long [4]11                                                                       |

| Figure 2.7: Layout of a phased array antenna using single-crystal YIG phase shifters [5]12                                               |

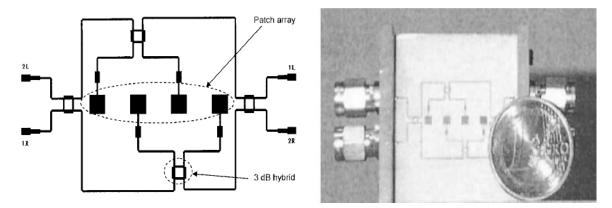

| Figure 2.8: Four-element phased array integrated monolithically on a silicon substrate [6]                                               |

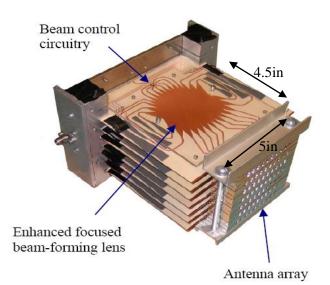

| Figure 2.9: Examples of 3-D multilayer 'stacked', monolithically integrated phased array modules.                                        |

| (a)An LTCC processed substrate with stacked functional layers [8]. (b) A 3-D phased array module                                         |

| vertically integrated with 22µm thick polyimide layers [9]14                                                                             |

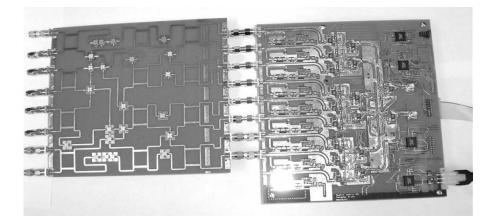

| Figure 2.10: Top view and cross-sectional view of the PCB MEMS-based ESA [10]14                                                          |

| Figure 2.11: SEM image of the switch designed by Raytheon. (a)The switch in 'on' state with no DC                                        |

| bias applied. (b) The switch in 'off' state with a DC voltage applied [12]                                                               |

| Figure 2.12: University of Michigan's low spring-constant MEMS switch [13]18                                                             |

| Figure 2.13: Side view and top view of the University of Michigan's switch with enhanced power                                           |

| handling capabilities [14]                                                                                                               |

| Figure 2.14: Lincoln Laboratories in-line MEMS-series switch in a (a) metal-metal contact, (b)               |

|--------------------------------------------------------------------------------------------------------------|

| capacitive configuration and (c) SEM of the metal-metal contact switch [18]                                  |

| Figure 2.15: Raytheon's 4-bit X-band MEMS phase shifter designed using 3dB Lange couplers                    |

| integrated on a silicon substrate [19]22                                                                     |

| Figure 2.16: Rockwell Scientific/ University of Michigan 4-bit MEMS phase shifter [21]                       |

| Figure 2.17: Layout of the slot-coupled coupler and 4 x 4 Butler matrix. The crossover lines are             |

| realized by coupling through the slot from layer to the next [23]23                                          |

| Figure 2.18: Layout and photo of the 4 x 4 Butler matrix network without any crossovers using a 0-           |

| dB branch-line coupler in order to reduce circuit fabrication complexity [24]24                              |

| Figure 2.19: 4 x 4 compact Butler matrix layout and realized structure. The structure is low-loss and        |

| compact using low-loss foam-suspended strip line [26]                                                        |

| Figure 3.1: Shunt capacitive MEMS switch structure in its two states. (a) Capacitive shunt switch in         |

| 'on' state. (b) Capacitive shunt switch in 'off' state                                                       |

| Figure 3.2: (a) Conventional switch. (b) Proposed dual-warped beam switch                                    |

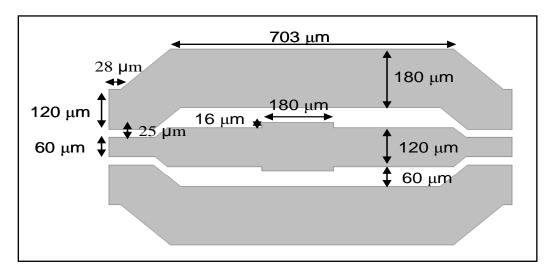

| Figure 3.3: CPW layout and dimensions                                                                        |

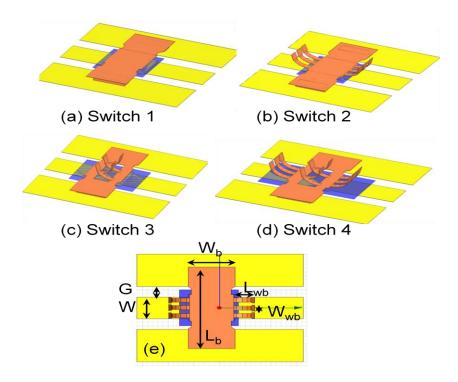

| Figure 3.4: Schematic views of (a) Switch 1, (b) Switch 2, (c) Switch 3, (d) Switch 4 and (e) the top        |

| view of Switch 2                                                                                             |

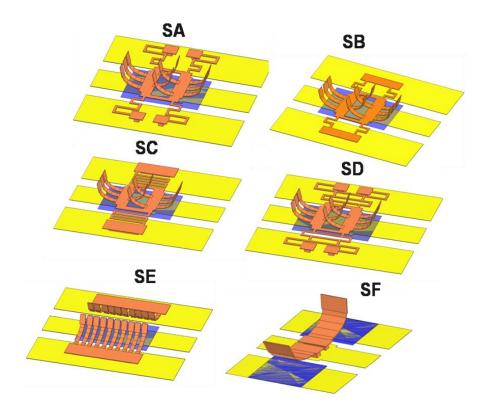

| Figure 3.5: Different capacitive switch spring designs using the warped-beam concept32                       |

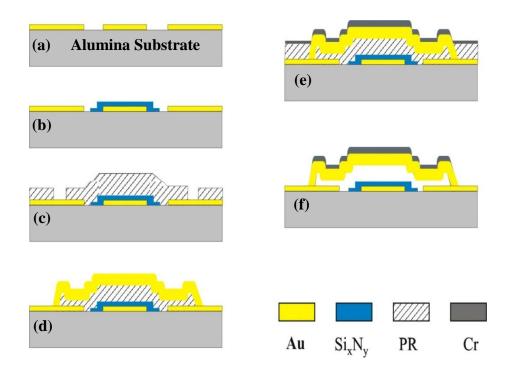

| Figure 3.6: The 5-mask fabrication process for all the switch designs                                        |

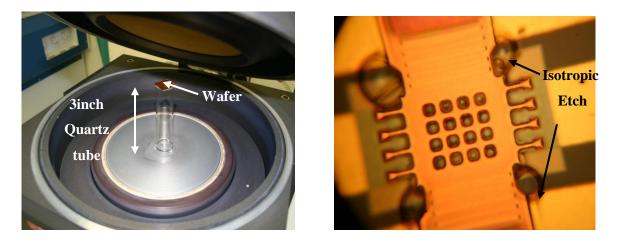

| Figure 3.7: Dry release set-up and captured image of the isotropic etch                                      |

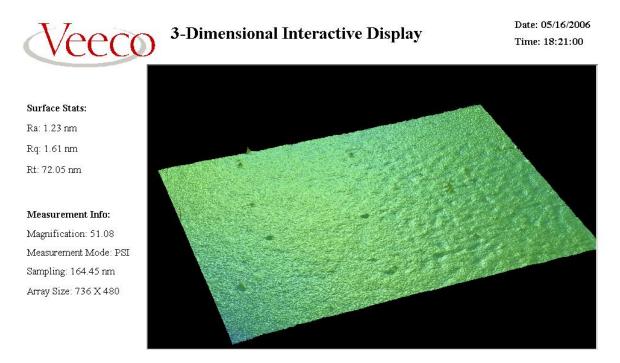

| Figure 3.8: Surface profile for the1800Å thick Nitride layer PECVD deposited at 250°C35                      |

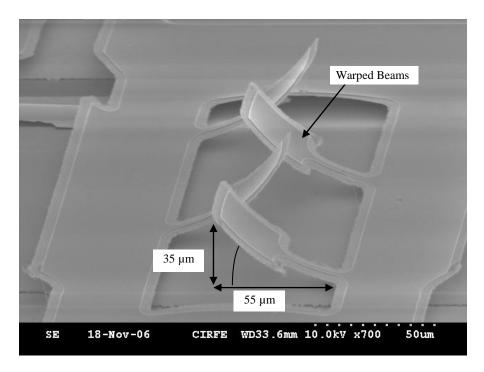

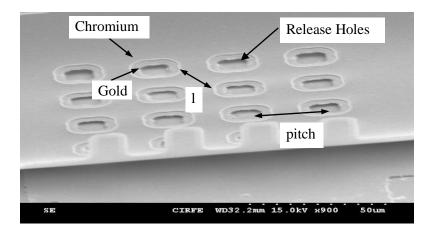

| Figure 3.9: SEM of Switch 3 with center warped bimetallic beams. These center beams warp up to               |

| approximately a 35° angle from the switch's surface plane when depositing a 150Å thick Cr layer36            |

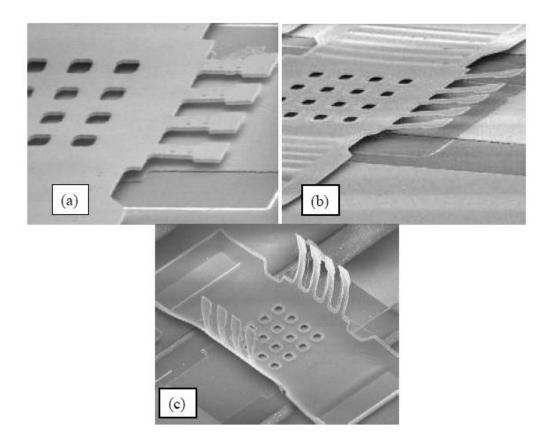

| Figure 3.10: SEM photos of the different degrees of beam curling as a function of metal thickness and        |

| effective residual stress. (a) E-beam deposited gold results in flat beam structures. (b) 150Å thick Cr      |

| results in a reasonable amount of warping. (c) 400Å thick Cr results in warping the switch structure.        |

|                                                                                                              |

| Figure 3.11: SEM of the fabricated capacitive MEMS switch with bi-layer of Au – Cr                           |

| Figure 3.12: A SEM of the capacitive MEMS Switch 2 using 400Å of Cr as a top layer. A 30 $\mu$ m thick       |

| high resistivity Cr line is routed to the switch electrode in order to isolate the RF signal and to bias the |

| switch externally using a DC probe                                                                           |

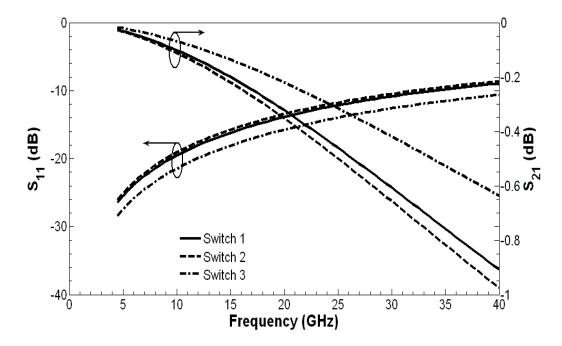

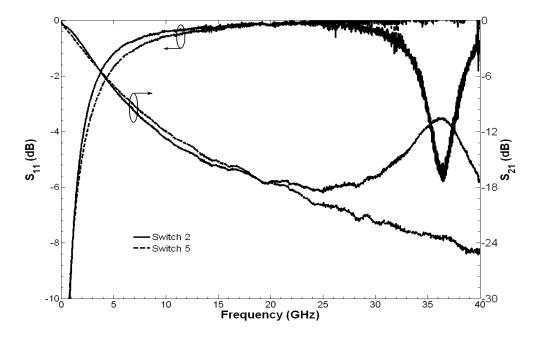

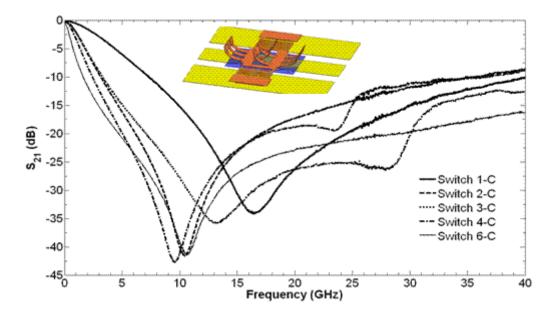

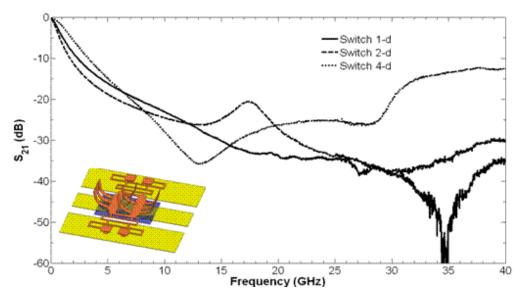

| Figure 3.28: Comparison of the measured results of the 5 variations of Switch C in 'off' state           |

|----------------------------------------------------------------------------------------------------------|

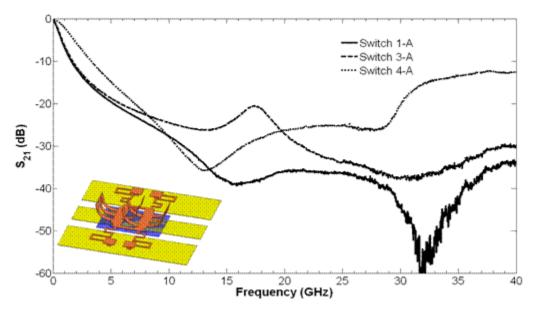

| Figure 3.27: Comparison of the measured results of Switch A in 'off' state                               |

|                                                                                                          |

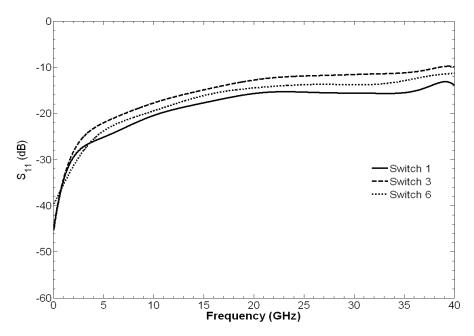

| Figure 3.26: Comparison of the measured responses of Switch 1, Switch 3 and Switch 6 in 'on' state.      |

| Connecting the center beam across the width of the switch removes the resonance                          |

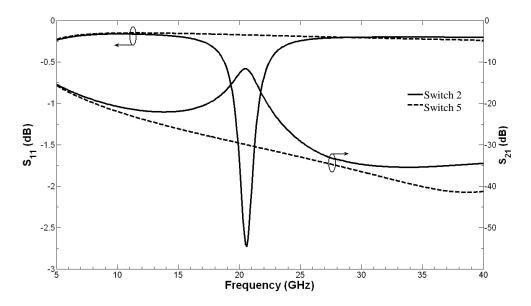

| Figure 3.25: Comparison of the measured responses of Switch 2 and Switch 5 in 'off' state.               |

| Figure 3.24: Switch 6 improved dual-warped beam switch with meandered springs and center connected beam  |

| tolerances and switch conformity with the electrode                                                      |

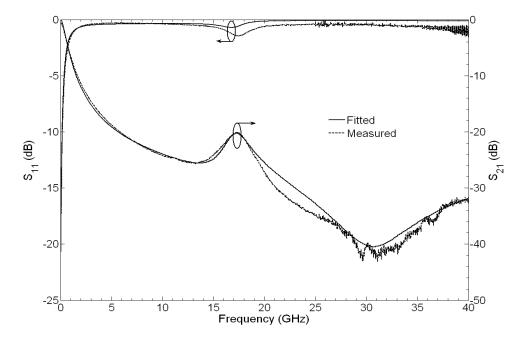

| ADS response of Switch 2 in 'off' state. Any discrepancies present can be a result of fabrication        |

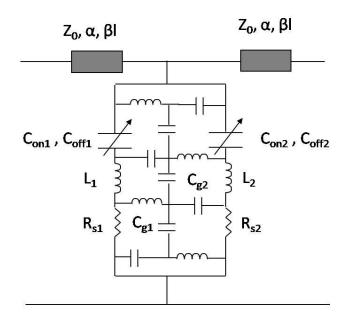

| Figure 3.23: A comparison between the measured response and the equivalent CLR circuit simulated         |

| Figure 3.22: The equivalent CLR circuit of the center warped-beam Switch 2                               |

| presence of these center-warped beams results in a resonance at 20GHz                                    |

| Figure 3.21: Comparison of the simulated responses of Switch 2 and Switch 5 in 'off' state. The          |

| capacitance                                                                                              |

| measured up-state capacitance decreases from 121fF to 59.5fF, half the original 'on' state               |

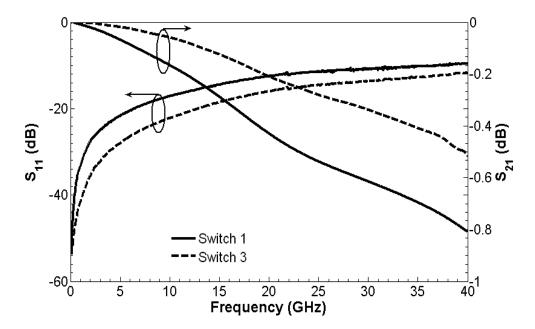

| Figure 3.20: Comparison of the measured response of Switch 3 and Switch 1 in 'on' state. The             |

| state capacitance improves from 4.25pF to 10pF                                                           |

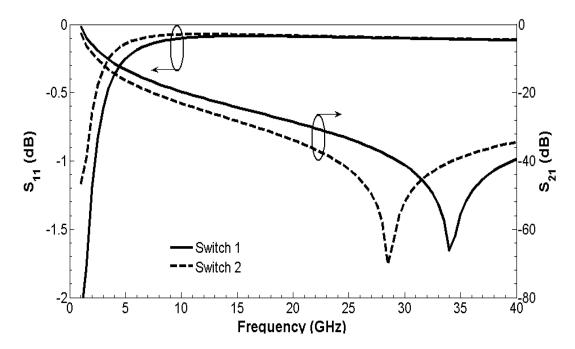

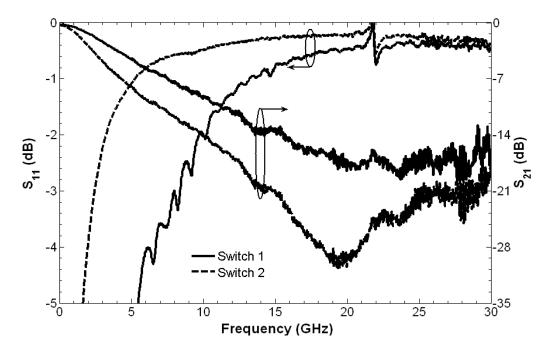

| Figure 3.19: Comparison of the measured responses of Switch 1 and Switch 2 in 'off' state. The 'off'     |

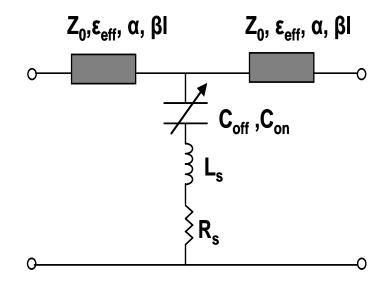

| $C_{off}$ , series inductance $L_s$ and series resistance $R_s$ parameters                               |

| Figure 3.18: Equivalent circuit model used to extract the switch's on and off capacitances, $C_{on}$ and |

| The presence of these warped beams reduces the 'on' state capacitance by 20% to 63.6fF at 10GHz47        |

| Figure 3.17: Comparison of the simulated responses of Switch 1, Switch 2 and Switch 3 in 'on' state.     |

| switch, Switch 1                                                                                         |

| state capacitance of 9.12pF at 10GHz is measured; two times the 'off' state capacitance of the basic     |

| Figure 3.16: Comparison of the simulated responses of Switch 1 and Switch 2 in 'off' state. An 'off'     |

| fixed-fixed beam structures used to measure deflection and curvature                                     |

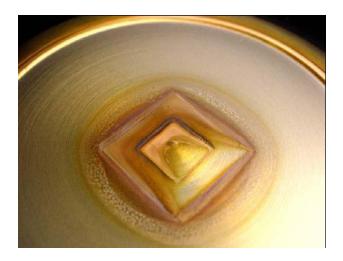

| Figure 3.15: Optical profilometer captured image of the Switch 2 and the some of the cantilever and      |

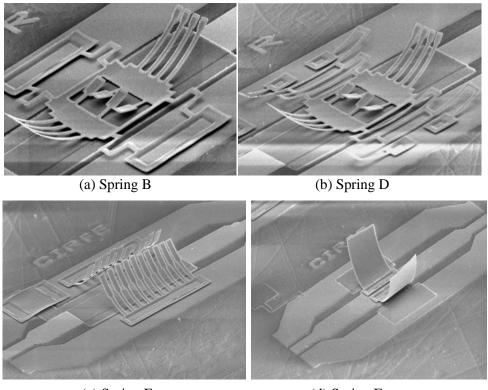

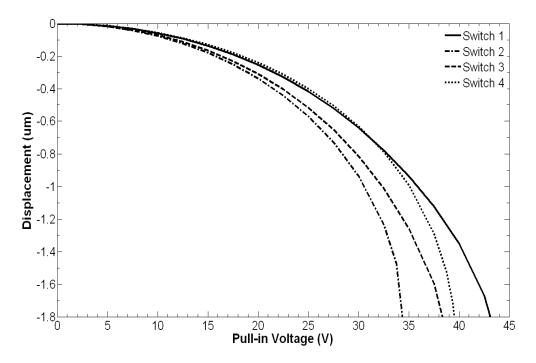

| Figure 3.14: Comparison of the simulated pull-in voltages of Switches 1 to 440                           |

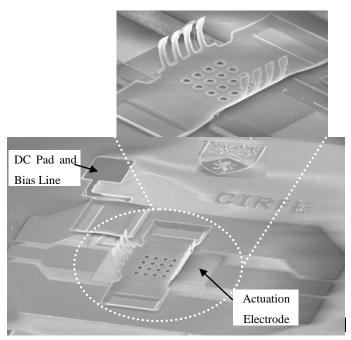

| D, (c) Spring E and (d) Spring F                                                                         |

| Figure 3.13: SEM photos of the fabricated bimetallic warped-beam switches. (a) Spring B, (b) Spring      |

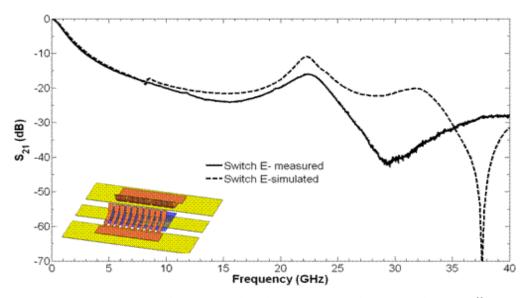

| Figure 3.30: Comparison of the simulated and measured results of Switch E in 'off' state                     |

|--------------------------------------------------------------------------------------------------------------|

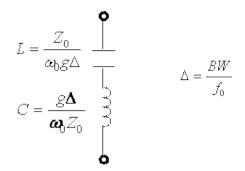

| Figure 3.31: The equivalent circuit of a bandstop resonator                                                  |

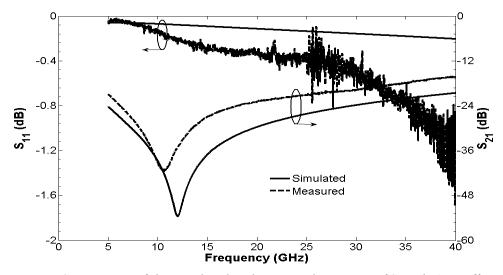

| Figure 3.32: Comparison of the simulated and measured response of Switch 6 in 'off' state60                  |

| Figure 3.33: Comparison of the simulated and measured response of Switch 6 in 'on' state60                   |

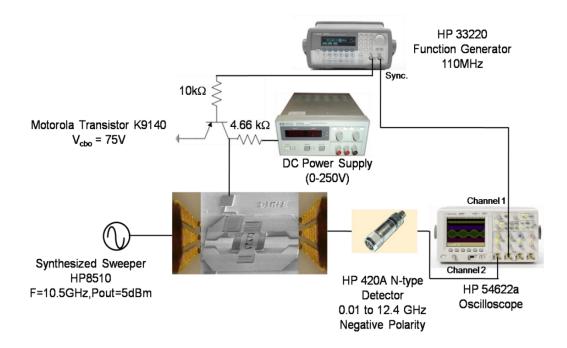

| Figure 3.34: Switch speed measurement setup62                                                                |

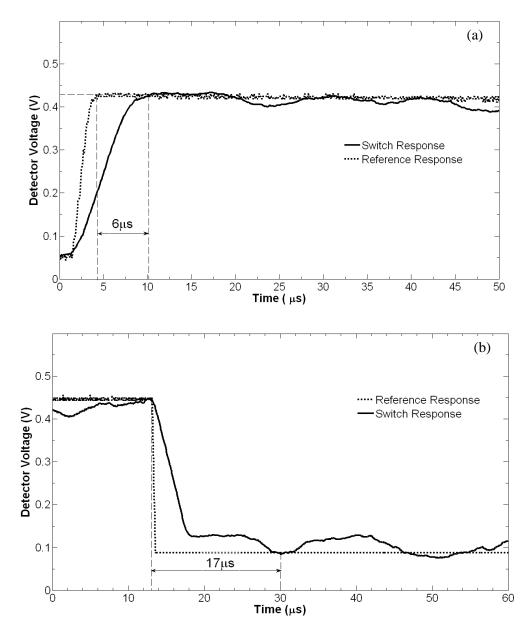

| Figure 3.35: Switch's measured (a) rising-edge and (b) falling-edge response time. The 4µs delay             |

| contributed by the transistor switching circuit is de-embedded from the results                              |

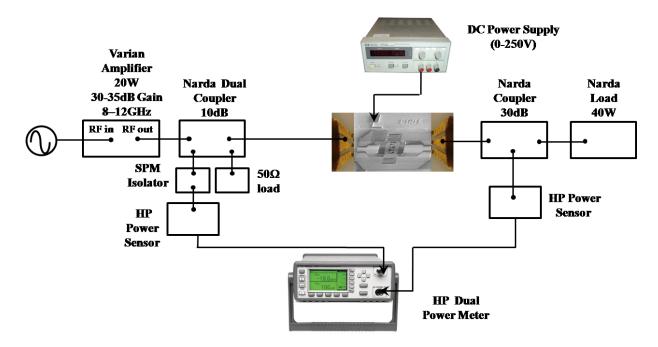

| Figure 3.36: High power measurement setup. The switch is biased during 'hot switching' using a DC            |

| power supply. Output power levels are measured using a dual power meter                                      |

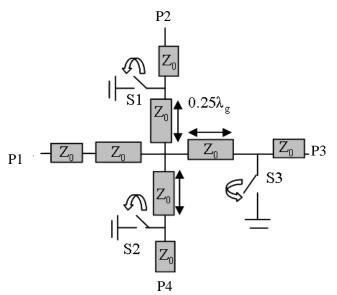

| Figure 3.37: Equivalent circuit layout of the SP3T capacitive shunt switch                                   |

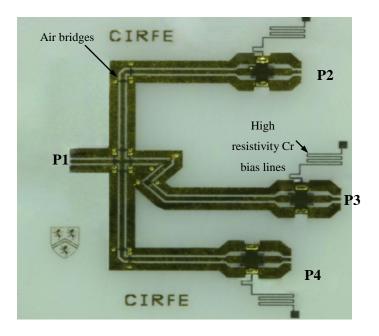

| Figure 3.38: The fabricated Single-Pole Triple-Throw (SP3T) circuit.                                         |

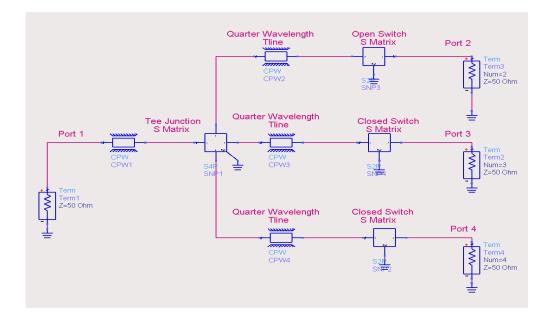

| Figure 3.39: Equivalent circuit set-up in HP-ADS <sup>®</sup> . The EM simulated S matrix of the T-junction, |

| quarter wave transmission lines and 'on' and 'off' states of the switch obtained from Sonnet and             |

| HFSS simulations are used in the ADS circuit simulator to optimize and obtain the simulated                  |

| response of the SP3T switch                                                                                  |

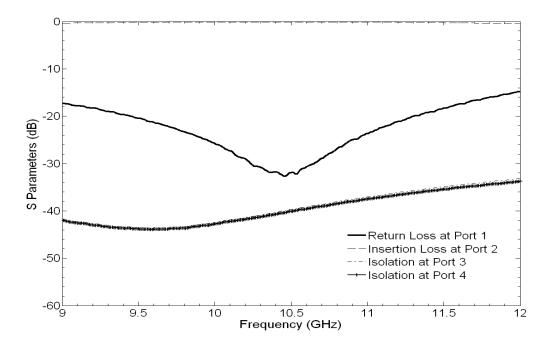

| Figure 3.40: Simulated results of the SP3T switch circuit with Port 2 open (switch is un-actuated to         |

| remain in 'on' state) and Ports 3 and 4 are closed (switches are actuated to 'off' state)70                  |

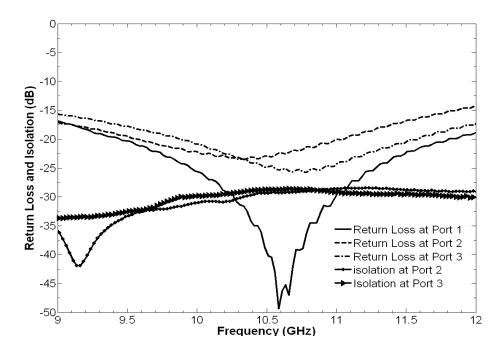

| Figure 3.41: Measured return loss and isolation across the SP3T output ports for the different               |

| activated ports71                                                                                            |

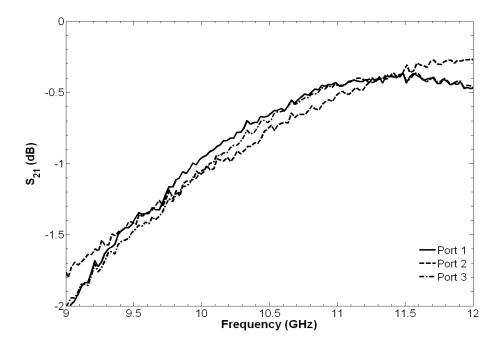

| Figure 3.42: Measured insertion loss across the SP3T output ports when each switch is kept in 'on'           |

| state71                                                                                                      |

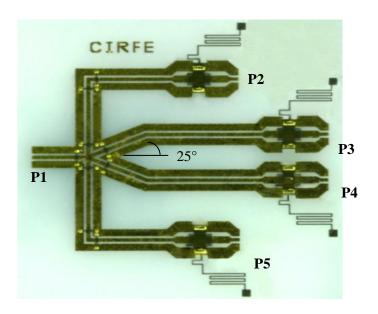

| Figure 3.43: The Single-Pole Four-Throw (SP4T) circuit72                                                     |

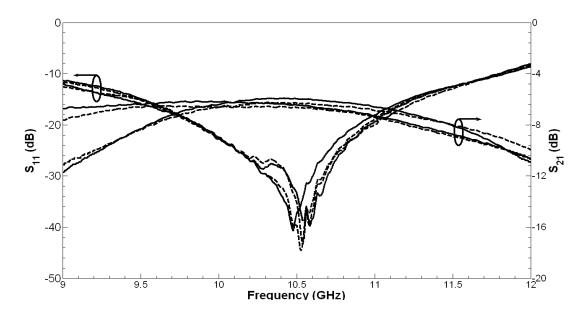

| Figure 3.44: (a) Simulated, (b) measured return loss and (c) insertion loss for the SP4T73                   |

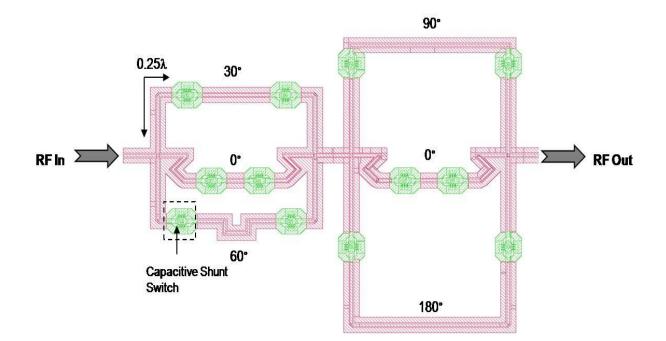

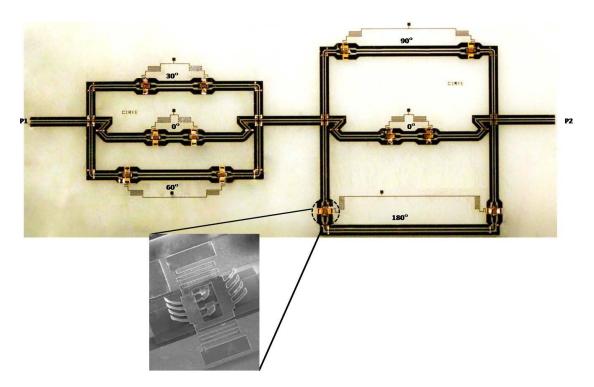

| Figure 4.1: Proposed digital phase shifter. It consists of four cascaded SP3T capacitive shunt switches      |

| with varying delay line lengths. The phase shifter has nine switchable77                                     |

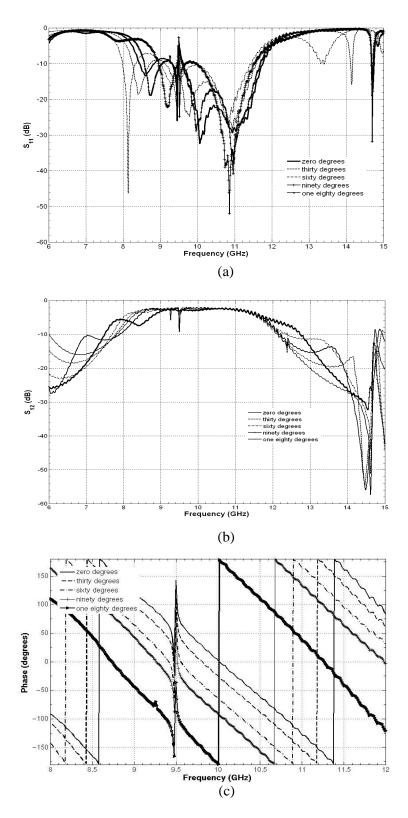

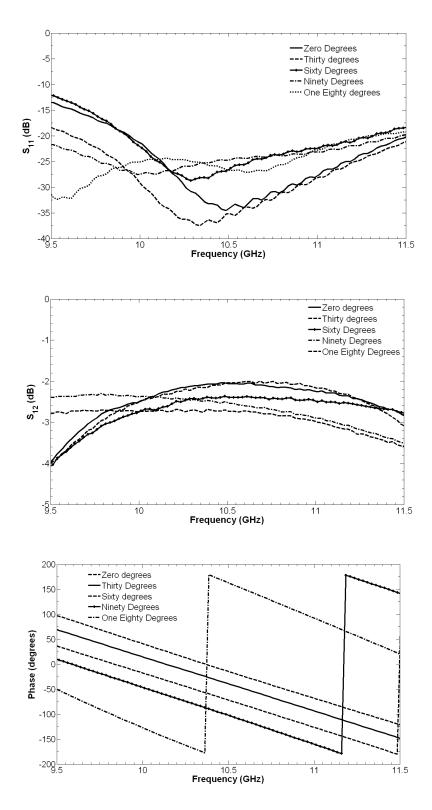

| Figure 4.2: Fabricated MEMS integrated phase shifter78                                                       |

| Figure 4.3: 3-bit phase shifter's simulated (a) return loss, (b) insertion loss and (c) phase                |

| Figure 4.4: 3-bit phase shifter measured (a) return loss, (b) insertion loss and (c) phase                   |

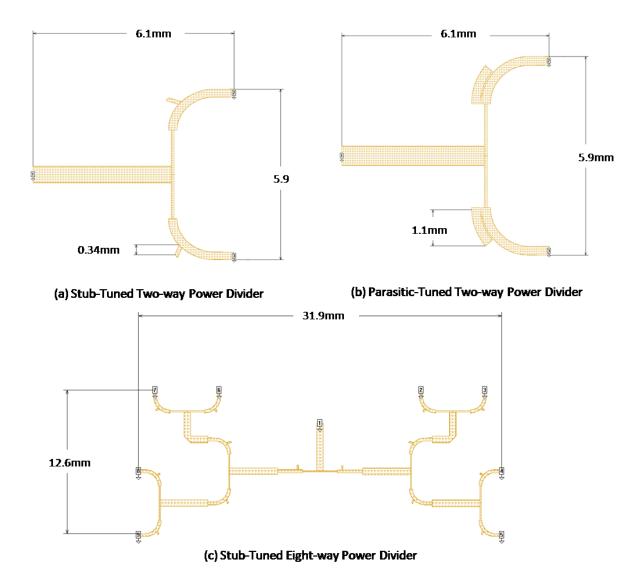

| Figure 4.5: The two proposed designs of the T-junction power divider. The power dividers are                 |

| optimized to have a wideband performance by implementing open-circuited stubs and parasitic                  |

| elements along the divider's output branch lines                                                             |

|                                                                                                              |

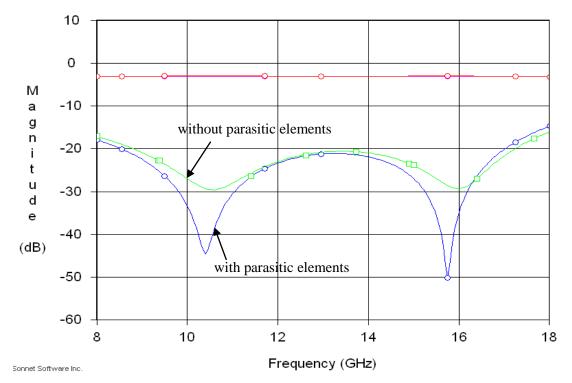

| Figure 4.6: Reflection and insertion loss responses of the two-way power divider with parasitic              |

|--------------------------------------------------------------------------------------------------------------|

| elements. Return loss is improved to better than 40dB, the insertion loss is slightly improved by            |

| 0.02dB, and the -20dB bandwidth is increased to 84%85                                                        |

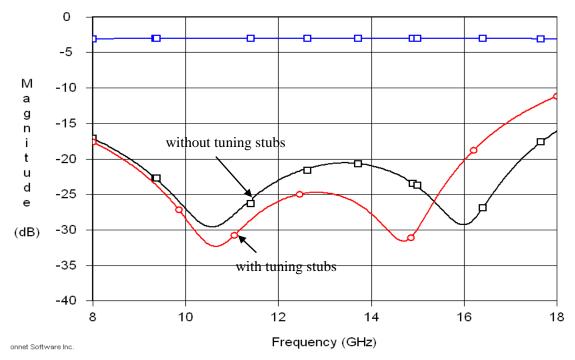

| Figure 4.7: Reflection and insertion loss of the two way power divider with tuning stubs. Increasing         |

| the length of the stubs is found to enhance the matching of the higher resonance frequency and               |

| deteriorate the lower resonance frequency                                                                    |

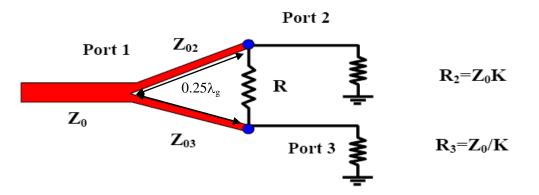

| Figure 4.8: Schematic of a typical Wilkinson power divider [50]                                              |

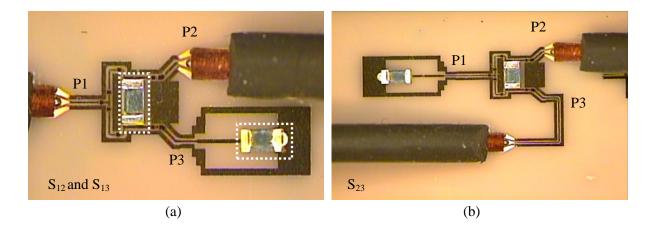

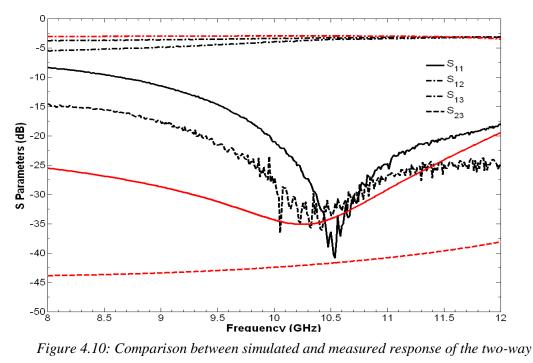

| Figure 4.9: Fabricated equal-split two-way Wilkinson power dividers. (a) The first layout is for             |

| measuring the power divider's insertion loss and return loss. (b) The second layout is for measuring         |

| the power divider's isolation at the output ports                                                            |

| Figure 4.10: Comparison between simulated and measured response of the two-way Wilkinson power               |

| divider90                                                                                                    |

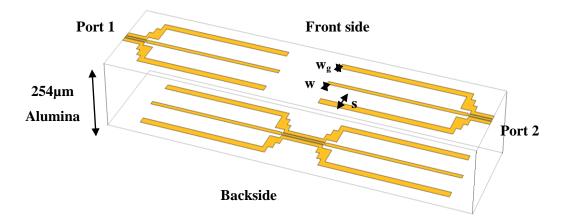

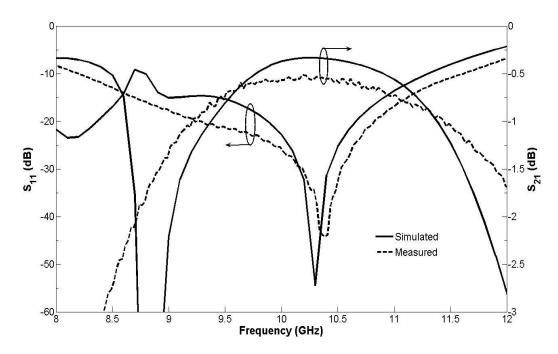

| Figure 4.11: Layout of a dual-path EM interconnect with a total circuit area of 0.15cm <sup>2</sup> 91       |

| Figure 4.12: Comparison between the simulated and measured results for the dual-path interconnects.          |

|                                                                                                              |

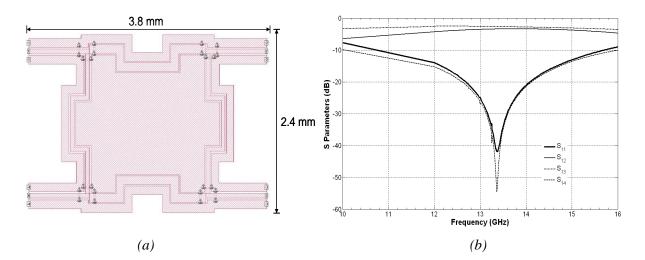

| Figure 4.13: (a) The FG-CPW folded coupler and (b) the EM simulated response [74]94                          |

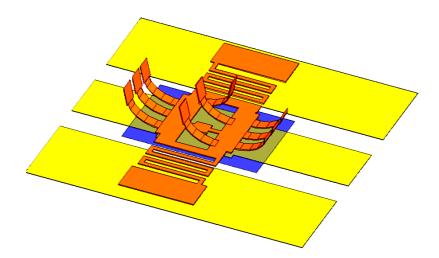

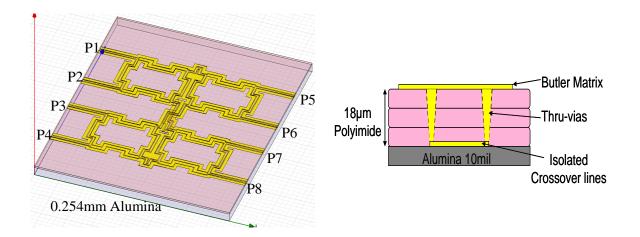

| Figure 4.14: Proposed 4 x 4 Butler matrix layout and cross section [74]                                      |

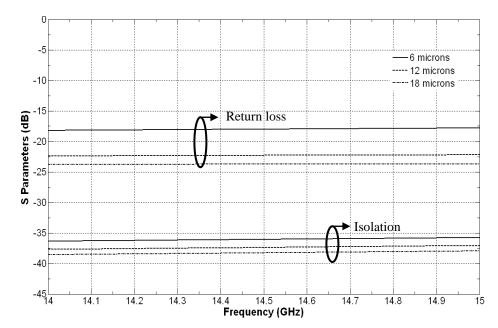

| Figure 4.15: Crossover lines return loss and isolation as a function of polyimide thickness [74]96           |

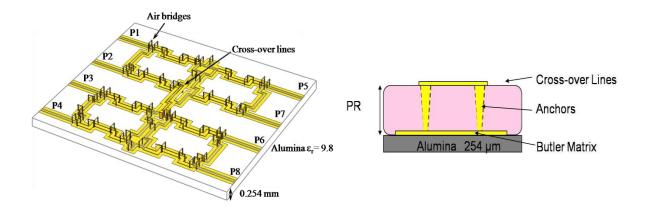

| Figure 4.16: 4 x 4 Butler matrix layout and cross-section                                                    |

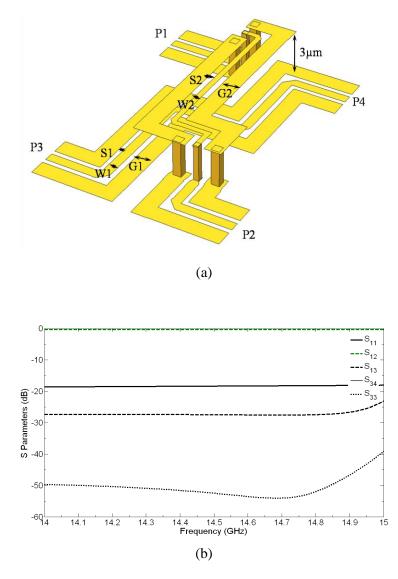

| Figure 4.17: (a) The layout of the FGC bridge crossover bridge in Sonnet and (b) the simulated EM            |

| response. The overlapping FGC air bridge lines (S2, W2, G2) are at an impedance slightly higher than         |

| that of (S1, W1, G1) to improve matching and reduce reflections97                                            |

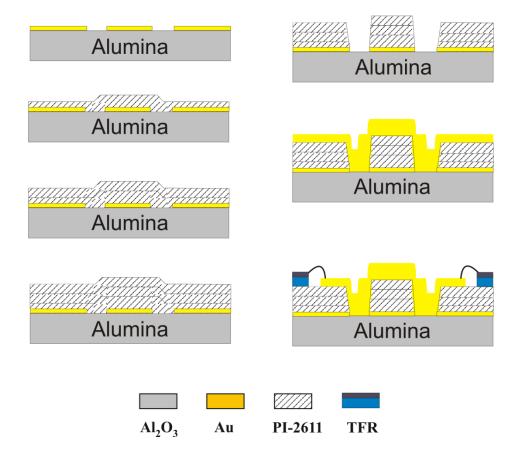

| Figure 4.18: 4 x 4 polyimide-integrated Butler matrix fabrication process                                    |

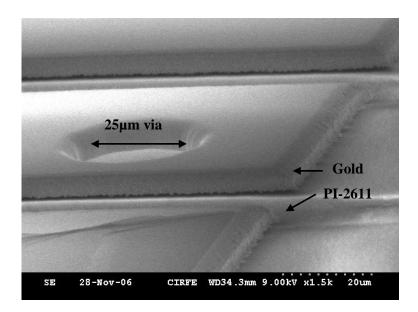

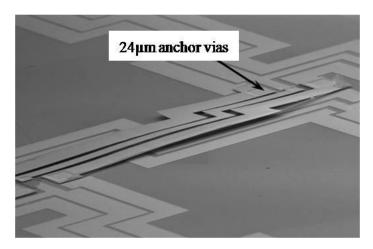

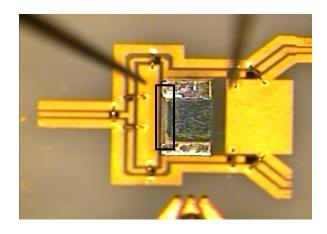

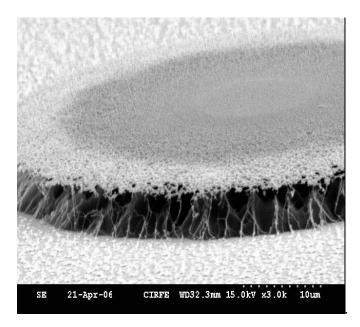

| Figure 4.19: SEM of the Butler Matrix's etched via profile. The vias have a total area of 25 x $25\mu m^2$ . |

|                                                                                                              |

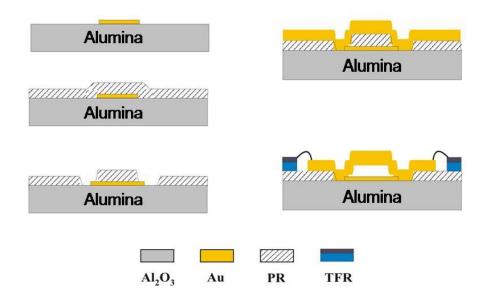

| Figure 4.20: 5-mask fabrication process of the 4 x 4 MEMS integrated Butler matrix circuit 101               |

| Figure 4.21: SEM image of the crossover lines suspended 3µm above the wafer101                               |

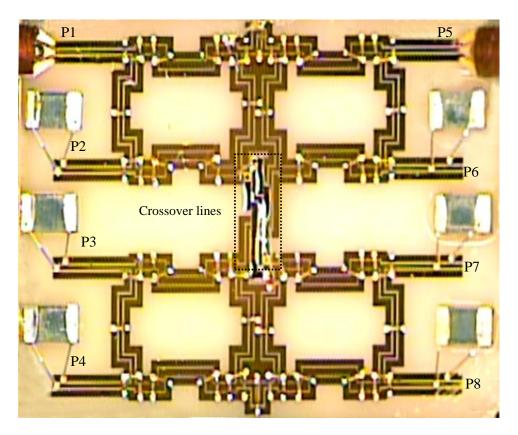

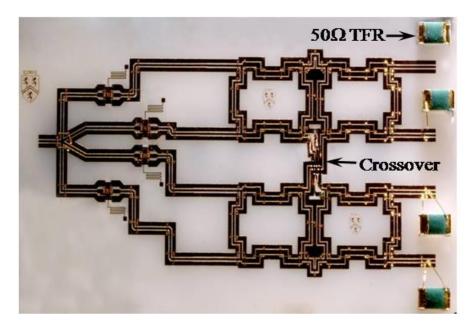

| Figure 4.22: Fabricated Butler matrix with hybrid integrated thin film resistors                             |

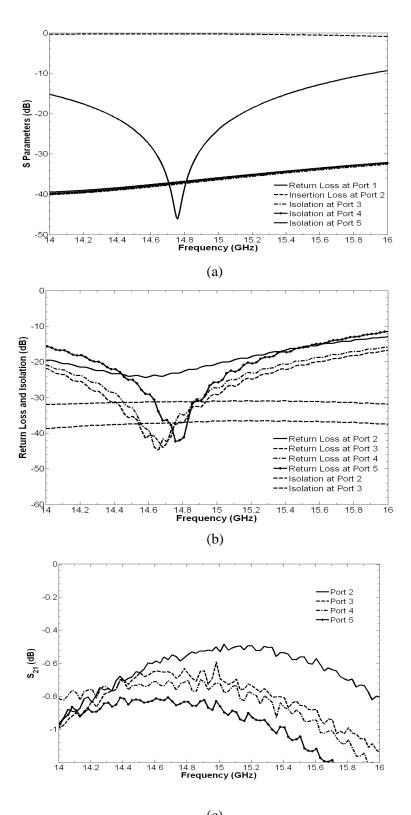

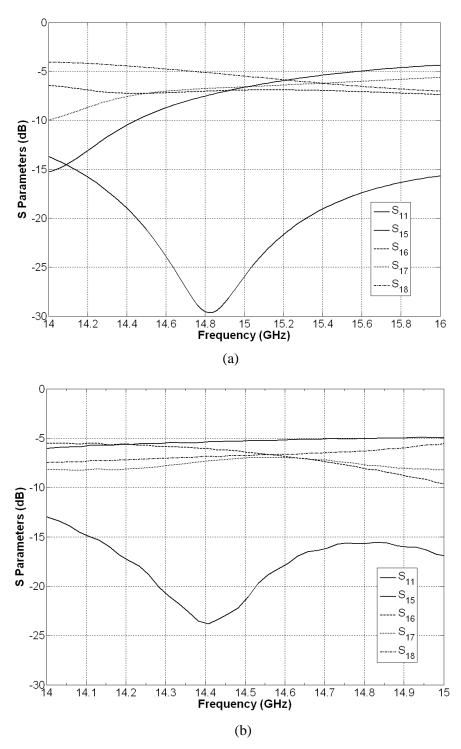

| Figure 4.23: Comparison of the polyimide-integrated S-parameter results. (a) Simulated S-parameters.         |

| (b) Measured S-parameters                                                                                    |

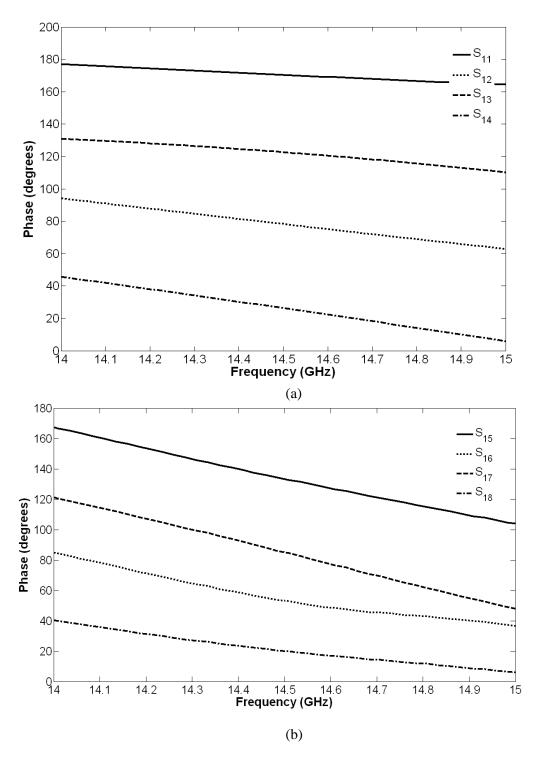

| Figure 4.24: Comparison of the polyimide-integrated BM phase results. (a) Simulated phase. (b)               |

| Measured phase104                                                                                            |

| Figure 4.25: Fabricated Butler matrix with gold air bridge crossovers10                                 | 5  |

|---------------------------------------------------------------------------------------------------------|----|

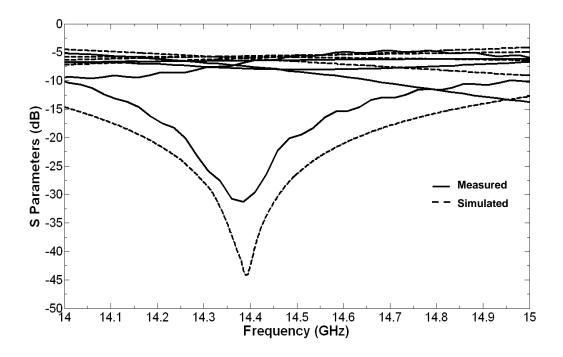

| Figure 4.26: 4 x 4 Butler matrix simulated (dashed line) measured (solid line) return loss and insertio | n  |

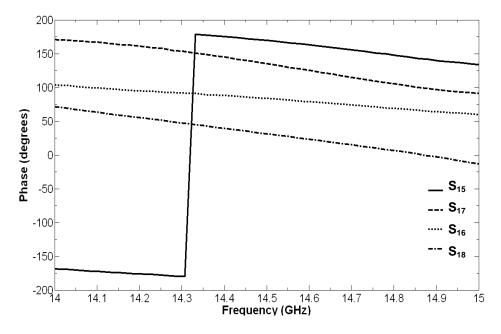

| loss when input is at Port 110                                                                          | 6  |

| Figure 4.27: 4 x 4 Butler matrix measured phase response10                                              | 6  |

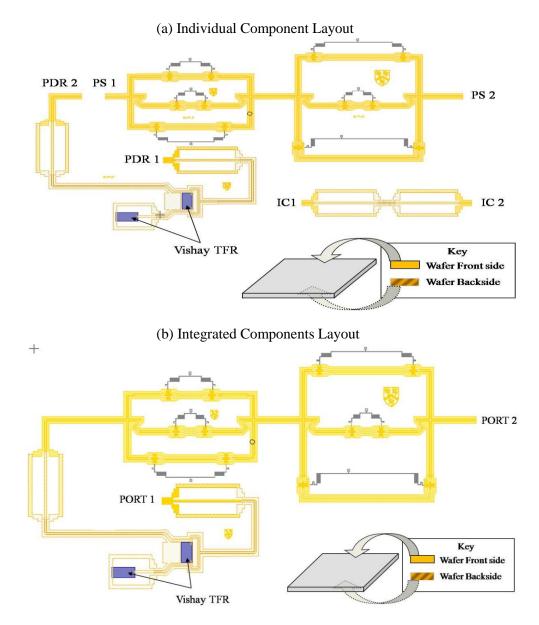

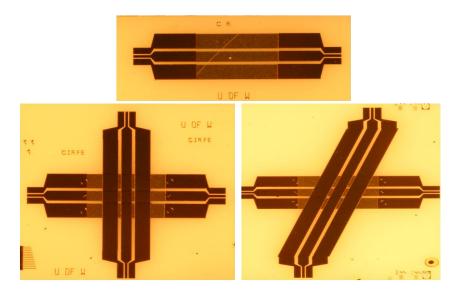

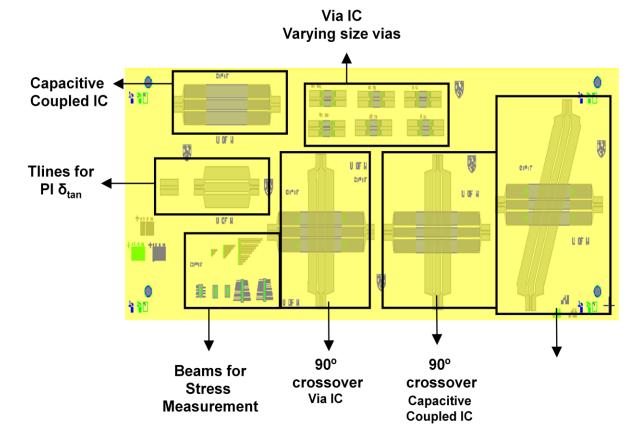

| Figure 5.1 ESA component layouts11                                                                      | 0  |

| Figure 5.2: Two basic types of ESA sub-array architectures. (a) The in-line sub-array architecture      | re |

| consists of stacked substrates where each substrate/layer performs a number of functions. (b) The       | ie |

| layered sub-array architecture consists of several layers where each layer with only one specific       | ic |

| function11                                                                                              | 1  |

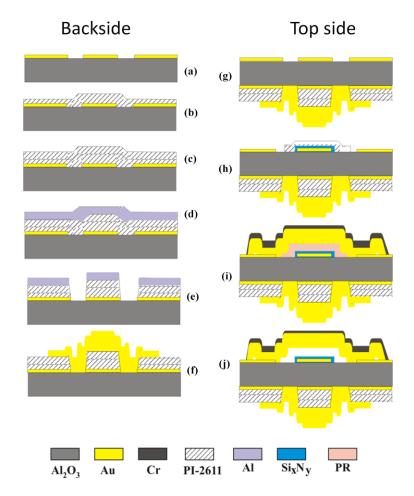

| Figure 5.3: 8-mask integrated module fabrication process for the backside and top side of the wafe      | r. |

|                                                                                                         | 2  |

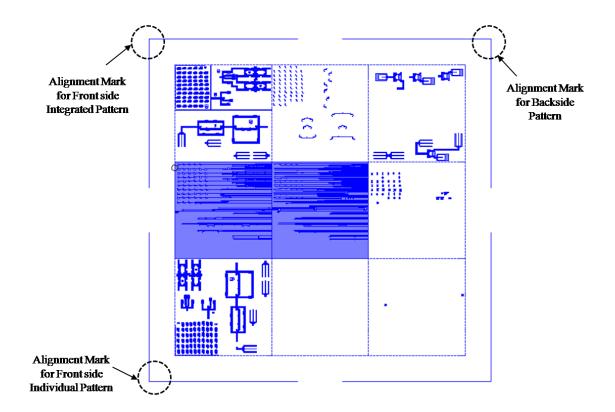

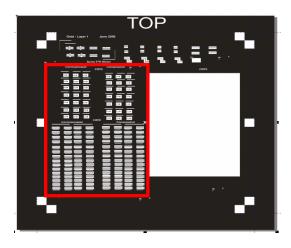

| Figure 5.4: Mask layout with alignment marks required for backside to front side alignment              | 3  |

| Figure 5.5: Fabricated integrated ESA module11                                                          | 4  |

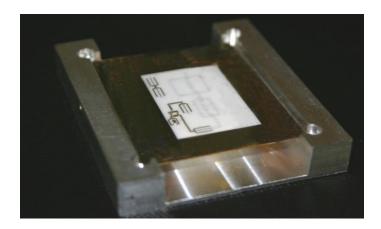

| Figure 5.6: Aluminum machined holder used in order not to short the circuit on the backside of the      | ie |

| wafer during measurements on the cascade wafer chuck11                                                  | 5  |

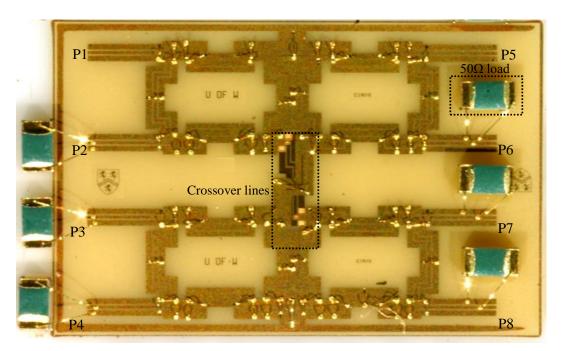

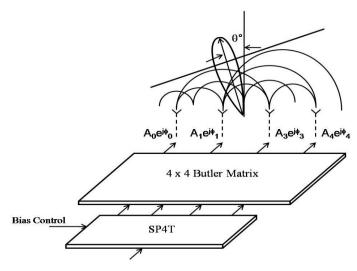

| Figure 5.8: Block diagram of the proposed MEMS-switched integrated beamfomming network 11               | 7  |

| Figure 5.9: Realized integrated MEMS 4x 4 Butler matrix. NiCr Vishay thin film resistors (TFRs) at      | e  |

| placed at the Butler matrix's four output ports and wire bonded to the ports not being measured as      | a  |

| matched 50Ω load11                                                                                      | 8  |

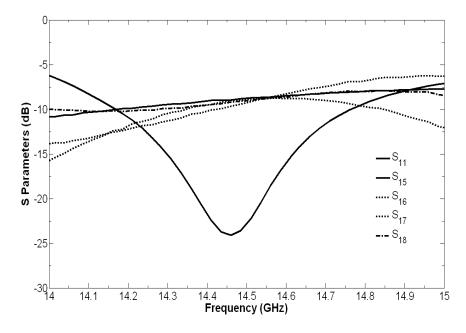

| Figure 5.10: Measured S-parameters when Port 1 is selected in the MEMS 4x4 Butler matrix. The           | ie |

| switch at Port 1 is kept in 'on' state whereas the switches at Port 2, Port 3 and Port 4 are actuated t | 0  |

| 'off' state                                                                                             | 9  |

| Figure 5.11: 8x8 folded Butler matrix layout12                                                          | 0  |

| Figure A.6.1: RIE etch result of the hybrid Vishay thin film resistor                                   | 1  |

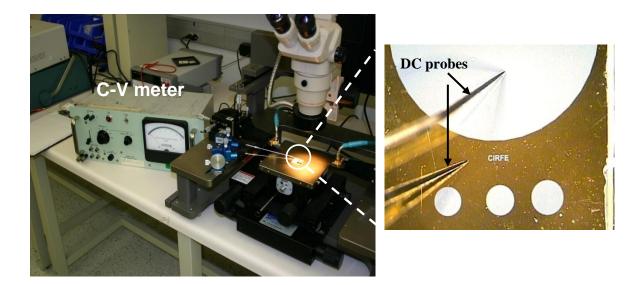

| Figure B.6.2: C-V measurement setup                                                                     | 2  |

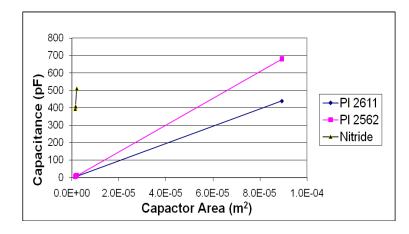

| Figure B.6.3: Capacitance versus area for PI-2611, PI-2562 and PECVD Silicon Nitride13                  | 3  |

| Figure B.6.4: Overlapping circuits designed with a 6µm thick PI-2611 inter-dielectric layer             | 3  |

| Figure B.6.5: Chromium mask layout for PI-2611 characterization                                         | 4  |

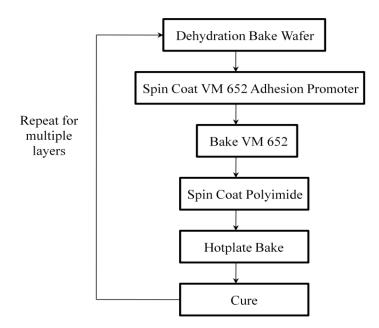

| Figure B.6.6: Flow chart of the polyimide application process                                           | 5  |

| Figure B.6.7: SEM image of PI 2562 after etching in KOH with an Al mask [70]                            | 7  |

| Figure B.6.8: Photograph of remnant residue left on the RIE's electrode after etching polyimide PI                             |

|--------------------------------------------------------------------------------------------------------------------------------|

| 2611 with $SF_6$ and $O_2$ . This residue was extremely difficult to remove and did not appear with $CF_4/O_2$                 |

| and pure O <sub>2</sub> recipes                                                                                                |

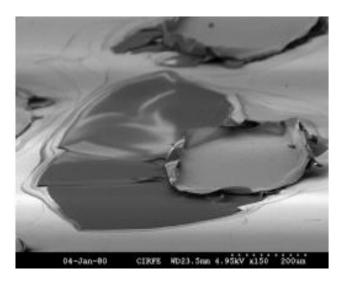

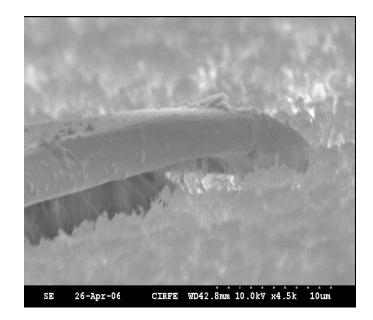

| Figure B.6.9:: SEM image of the residue referred to as "grass" as a result of re-deposited unetched                            |

| polyimide during RIE etching PI 2611 in O <sub>2</sub> /CF <sub>4</sub> . This etch recipe left considerably more residue than |

| a pure O <sub>2</sub> etch                                                                                                     |

| Figure B.6.10: SEM image of a $6\mu$ m-thick polyimide PI 2611 film etched in O <sub>2</sub> using a $1\mu$ m-thick            |

| $SiO_2$ mask. Pinholes developed in the $SiO_2$ due to a low selectivity RIE etch recipe causes a highly                       |

| undercut film with rough edges. An Al etch mask consistently gives smooth edges with less undercut.                            |

|                                                                                                                                |

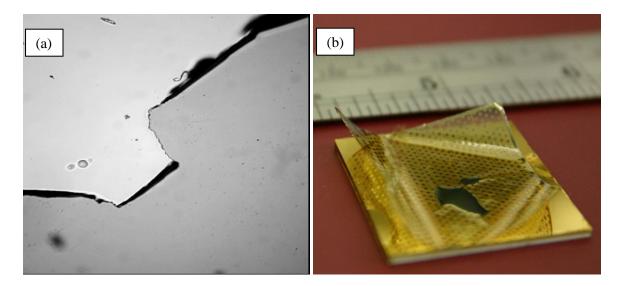

| Figure B.6.11: (a) SEM image of a 1µm thick gold layer lifting off the polyimide PI 2611 film due to                           |

| poor adhesion. (b) Photograph of a polyimide PI 2611 layer lifting off the gold again due to poor                              |

| adhesion and absence of an adhesion layer                                                                                      |

| Figure C.6.12: Emulsion mask used for the design of series and shunt TFRs                                                      |

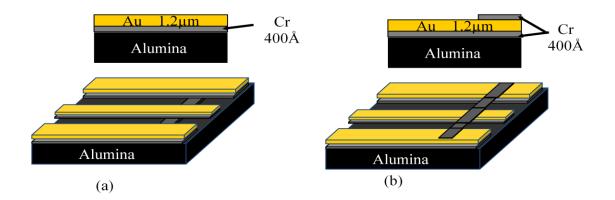

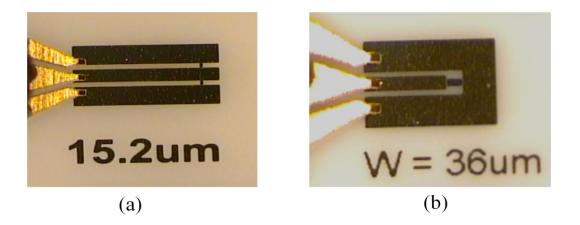

| Figure C.6.13: Two types of resistors tested using (a) a wet etch process and (b) using lift off for                           |

| higher reliability and repeatability                                                                                           |

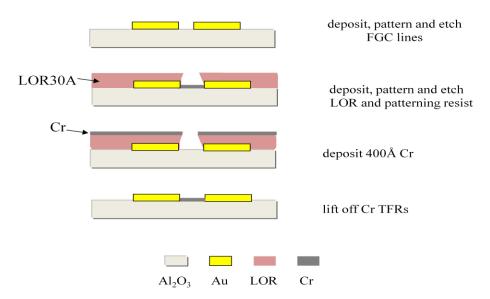

| Figure C.6.14: Process flow for fabricated Cr thin film resistors                                                              |

| Figure C.6.15: Two types of resistors tested (a) a shunt parallel resistor, (b) a series resistor                              |

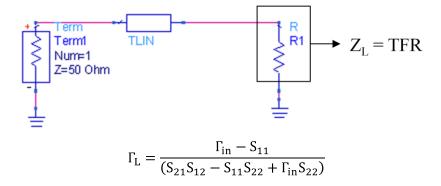

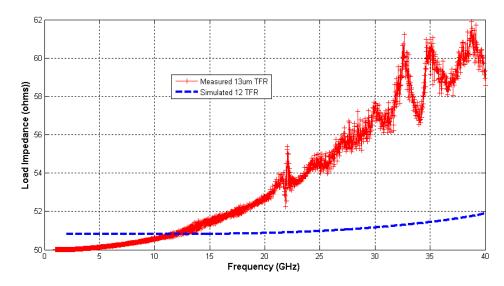

| Figure C. 6.16: Equivalent circuit and equation used to extract the TFR resistance value                                       |

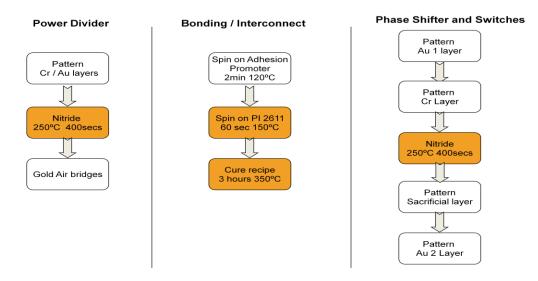

| Figure C.6.17: High temperature steps present in the 8 mask process                                                            |

## List of Tables

| Table 2.1: Performance comparison of FETs, PIN diode and RF MEMS Electrostatic Switches [11].         |

|-------------------------------------------------------------------------------------------------------|

|                                                                                                       |

| Table 2.2: 4-bit Phase Shifter Loss and Cost Comparison [11].    21                                   |

| Table 3.1: Summary of capacitive shunt switches reported in literature compared to the proposed       |

| design                                                                                                |

| Table 3.2: Dimensions of MEMS switch and circuit in µm                                                |

| Table 3.3: Material variables and their respective values.    40                                      |

| Table 3.4: Simulated switch pull-in voltages and spring constants                                     |

| Table 3.5: Measured residual in-plane stress for the switch's structural layers.       45             |

| Table 3.6: Fitted simulated parameters using the equivalent CLR model                                 |

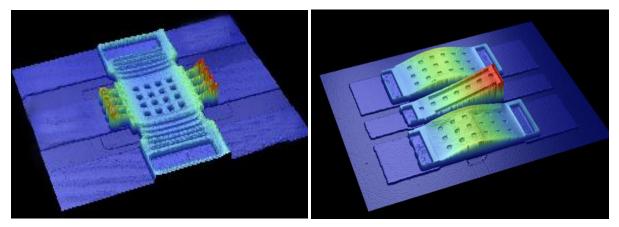

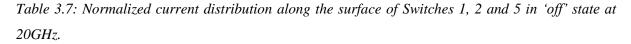

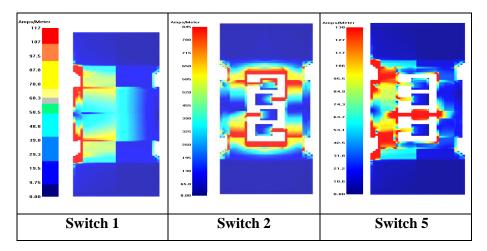

| Table 3.7: Normalized current distribution along the surface of Switches 1, 2 and 5 in 'off' state at |

| 20GHz                                                                                                 |

| Table 3.8: Comparison of switch bandwidth when varying its inductance and capacitance                 |

| Table 4.1: Phase shifter target specifications [47]                                                   |

| Table 4.2: Summary of the power divider simulated results obtained.       86                          |

| Table 5.1: A summary of total measured insertion loss of the individual ESA components compared       |

| to the total insertion loss of the integrated module [75]116                                          |

## Chapter 1 Introduction

### **1.1 Motivation**

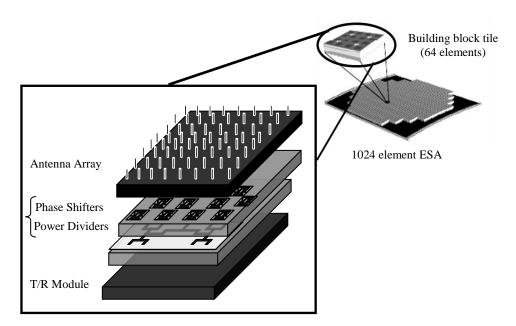

Next generation electronically scanned arrays (ESAs) aim to reduce both deployment and operational expenses by employing scalable, lightweight arrays assembled using low-cost, monolithically-integrated modules [1]. ESAs are an integral part of space-based radar systems and are realized with the hybrid connection of the RF feed network (transmission lines and power dividers), phase shifters, antennas and T/R modules, as shown in Figure 1.1. ESAs steer the beam electronically by controlling the relative phase shift in each radiating array element. This enables the system to track fast-moving and multiple targets, necessary for radar applications such as surface detection, tracking and satellite communication. Electronic scanning also eliminates mechanical complexity and reliability issues involved with conventional mechanically scanned arrays. Current integrated ESA technology has several disadvantages such as high assembly and integration cost and high DC power consumption, preventing its implementation in many phased array applications.

Figure 1.1: Proposed 3-D integrated ESA module. A 1024 element ESA can be subdivided into an array of tiles. Each tile consists of the hybrid connection of the RF feed network (transmission lines and power dividers), phase shifters, antennas and T/R modules.

With the recent exciting advancements in the field of microelectromechanical systems (MEMS) and micromachining technology, miniaturized MEMS phase shifters have shown to offer a superior RF performance in comparison to their semiconductor counterparts. The main objective of this research is to develop a new technique for integration at the module level that combines the MEMS phase shifters and feed networks into a highly integrated multifunctional chip, which can then be connected to the antenna array and T/R modules, as illustrated in Figure 1.1.

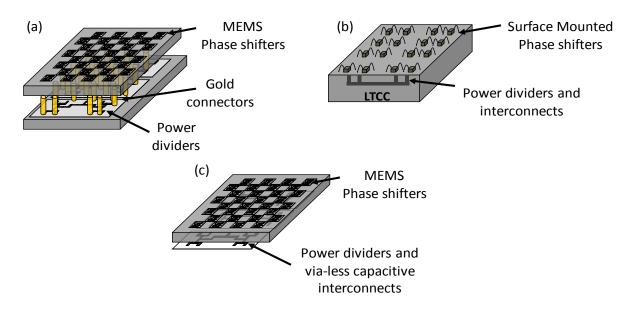

In today's large sized phased arrays for radar systems the key attributes include low insertion loss and drive power as well as light weight and low production cost. Consider a space-based radar system which consists of 182,400 phase shifters. The ESA can be subdivided into an array of tiles. Each tile consists of an array of 64 elements integrated into one module, serving as the building block for the entire system. Traditionally the phase shifter networks and the power divider networks are integrated as shown in Figure 1.2(a) and Figure 1.2(b). In the first technique illustrated in Figure 1.2(a), the MEMS phase shifter networks and the power divider networks are processed on two separate substrates and connected using gold connectors.

Figure 1.2: Comparison of the different integration methods. (a) Hybrid integration using two processed substrates and gold connectors. (b) Hybrid integration using an LTCC-processed substrate and surface mounted phase shifters. (c) The proposed integration method using a single substrate and capacitive interconnects.

The second method uses Low Temperature Co-fired Ceramics (LTCC) processing where the hybrid phase shifters are surface mounted to the LTCC-processed substrate and connected to the power divider networks using gold interconnects. If 8-way power dividers are integrated with these phase shifters monolithically, the 64 phase shifters and the associated feed network can be potentially integrated on a single 6 inch wafer. The proposed integration method shown in Figure 1.2(c) uses the double side of a single wafer with via-less capacitive interconnects to connect the two networks. These via-less capacitive interconnects use capacitive coupling through a thin substrate to connect the circuits on either side of the wafer. In space-based systems mass is a critical factor and a saving of 1gram per phase shifter by using monolithic and via-less integration can translate to a significant mass cutback.

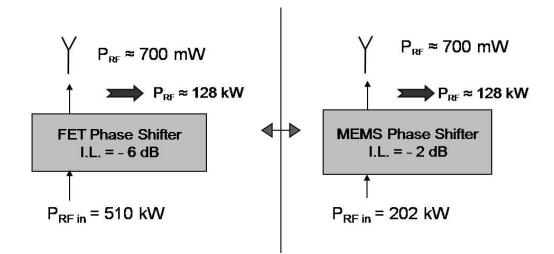

Recently, MEMS switches implemented in phase shifters have demonstrated exceptional performance at microwave frequencies including low insertion loss (less than 1dB), high isolation and low DC drive power consumption. Although a FET phase shifter consumes low power, its insertion loss is at least 4dB higher than that of a MEMS phase shifter. The signal would require amplification to correct this loss. To demonstrate, consider a simple transmitter module that consists of a phase shifter terminated with a radiating antenna element as shown in Figure 1.3. The FET phase shifter exhibits an insertion loss of about 6dB, whereas a MEMS phase shifter exhibits an insertion loss of about 2dB.

Figure 1.3: Comparison of the power requirements of a system designed with a FET phase shifter and a system designed with a MEMS phase shifter. Both phase shifters consume very little DC power.

As mentioned earlier, typical implementations of space-based radar systems have an excess of 182,400 antenna elements. Therefore, to deliver about 700mW to each of the antenna elements, the system with the FET phase shifter would require 510kW of RF power. In comparison, the MEMS phase shifter would only require 202kW. Assuming that the power amplifiers have 50% efficiency, the DC power required for the semiconductor-based system would be 1020kW, while that required by the MEMS-based system would be 404kW. That calculates a saving of 50% in DC power consumption.

The final and often deciding factor in ESA fabrication is the cost of hybrid integration of the devices. Monolithic integration of these components into one substrate will reduce cost of assembly and integration which typically contributes to a large part of the phased array cost. RF MEMS technology enables the monolithic integration of the ESA components into one module, thereby enhancing ESA designs by significantly reducing size, fabrication cost, and interconnection losses and enhancing overall system performance.

In this research, a MEMS-based phase shifting network (tunable 3-bit MEMS phase shifter and passive 4 x 4 Butler beam forming network) and feed network are integrated into one versatile compact prototype chip that can then be connected to the antenna array and T/R modules. In addition to saving in assembly and integration cost as well as a reduction in DC power consumption, this integration concept offers high yield as well as low packaging and assembly complexity.

### 1.2 Objectives

The objective of this thesis is to design and fabricate a novel integrated module with RF MEMS components into one feasible prototype chip using micromachining technology. This innovative module introduces a new level of integration, previously achieved only by the use of larger, heavier and expensive systems. The stages of research and design include:

## • Development, modeling and fabrication of novel n-throw dual-warped beam capacitive MEMS switches

A novel MEMS capacitive shunt switch is developed to meet array system requirements with high isolation and low actuation voltage (~26V). By introducing warped bimetallic beams within the switch's geometry, the effective capacitive area is optimized to fine-tune the switch's RF performance in the 'off' state without influencing the switch's 'on' state performance. As a result, measurements show a drastic improvement where the 'off' state capacitance is doubled and the 'on' state capacitance is halved. Using this technique, a dual-warped switch with an off-to-on capacitive ratio of almost 170 is achieved without the need for thin dielectrics or high dielectric constant materials, exhibiting excellent RF performance and mechanical reliability. The mechanical and electrical modeling of this switch is examined in detail. This switch is also implemented in a three-throw (SP3T) and four-throw (SP4T) switch configuration for signal routing in the beam forming networks.

#### • Development of the 3-bit MEMS Phase Shifter and the feed network

Using the switches conceived in the previous stage of research, a 3-bit switched delay-line MEMS phase shifter is developed. Critical parameters such as low insertion loss and phase linearity are the focus of this design. FGC lines are employed in the design of the phase shifter to incorporate the shunt capacitive MEMS switches that have higher power handling capabilities than their metal-to-metal series switch counterparts. Two-way power dividers are designed to meet criteria such as low insertion loss and compact size. Integrated Butler matrices designed using FGC waveguides are also examined and tested as a passive beamforming network alternative to the active phased array.

### • Fully Integrated ESA Module

A wafer-scale integration technique using micromachining processes is developed to combine the ESA's RF components to form novel and versatile ESA modules on one chip, taking into consideration discontinuities and interconnection losses. Using an 8-mask process, X-band 3-bit MEMS phase shifters, Wilkinson power dividers and via-less capacitive interconnects are integrated on a double-sided wafer to produce the prototype module. In this monolithic approach, the choice of substrate, alignment and circuit component layouts are explored. Several design and processing challenges are encountered and circumvented in integrating these RF components onto one substrate. This integration technology offers high yield and low cost batch fabrication as well as low packaging and assembly complexity. The wafer-scale three-dimensionally integrated ESA prototype unit has an area of 2.2cm<sup>2</sup> and is an enabling building block of integrated sub-system arrays for lightweight large space-based phased arrays.

### 1.3 Outline

Following the motivation and objectives given in Chapter 1, Chapter 2 presents an overview of the different technologies available to realize integrated ESA modules. ESA module component technology is also examined where the most current RF MEMS switches and MEMS phase shifters are surveyed. In Chapter 3, a novel dual-warped capacitive MEMS switch is reported. Several configurations and designs are presented including a single-pole three-throw (SP3T) and single-pole four-throw (SP4T) switch. The monolithic fabrication of these designs along with mechanical analysis and measured data is presented. Other ESA components designed for the integrated module including the 3-bit MEMS switched delay-line phase shifter, power dividers, via-less capacitive interconnects, and 4x4 Butler matrices are introduced in Chapter 4. Chapter 5 presents the integration process used to fabricate the designed integrated ESA module on one chip. Finally, a brief summary of the contributions of the thesis with an outline of proposed future research is given in Chapter 6.

## Chapter 2 Background

The roadmap given in this chapter will describe the extensive work documented on each individual component of ESAs and the different integration and assembly techniques developed to meet the changing demands of radar and satellite systems. The first part of this chapter describes the different methods of phase scanning in ESAs and presents the most current work reported on integrated ESAs. In the second part of this chapter, a review of the ESA active and passive components including MEMS switches, phase shifters and Butler matrices is given including the use of RF MEMS technology from the perspective of its enabling technologies including fabrication.

### 2.1 Integrated ESAs

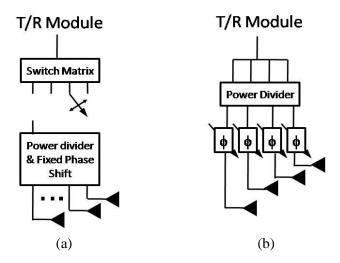

An ESA's beam is electronically scanned by varying the relative phase shift in each radiating array element with the use of phase shifters and switches. There are two main electronic scanning techniques: phase scanning and electronic feed switching. The electronic feed switching method uses multiple fixed directional beams with narrow beam widths, whereas the phase scanning technique positions the beam electronically by adjusting the differential phase between elements of an array in a predetermined manner, continuously steering the beam towards the desired direction, as illustrated in Figure 2.1. Comparing the two systems, a phase-scanning array system can cover an expansive, more uniform area with the same power levels as a simple switched beam system at a higher cost and increased system complexity due to the necessity of tunable active phase shifters [1]. Whereas the electronic feed switched system consists of switches, interconnecting Butler matrices and fixed phase delays. The disadvantage of Butler matrices is that with larger arrays, the interconnecting requirements and layout gets increasingly complex.

Figure 2.1: Functional block diagram of electronic scanning methods. (a) The electronic feed switching method. (b) The phase scanning method [1].

Moreover, the different types of ESAs can be classified as active and passive. The block diagram in Figure 2.2 shows the architectural differences between both systems [1]. While the active ESAs use a T/R module containing a low noise amplifier (LNA) and power amplifier (PA) for each radiating element to minimize the contribution of RF losses to the system noise figure and transmitting efficiency, the passive ESA uses a single PA and LNA for all radiating elements. In this thesis, the design is based on the passive ESA approach where the use of MEMS low-loss phase shifters allows the design to migrate towards a passive ESA.

(a) Active ESA

(b) Passive ESA

Figure 2.2: There are two types of ESA.s (a) Active ESA. (b) Passive ESA [1].

### 2.1.1 Integrated Electronic Feed Switched ESAs

The Butler matrix (BM) is one of the most commonly used beamforming networks (BFNs) and uses passive hybrids and fixed phase delays to produce successive multiple beams. An N x N BM produces N beams directed in different paths with an N-element array. When a signal approaches the input port of the Butler matrix, it produces a set of progressive inter-element phase shifts between output ports given by:

$$\Delta \phi = \pm (2k - 1)\frac{\pi}{2N} \qquad k \in [1, N]$$

(2.1)

where N is the number of ports of the matrix. Consider the 4 x 4 BM array shown in Figure 2.3(a) that consists of four  $90^{\circ}$  hybrids and two fixed phase shifters. When one of the input ports is excited by an RF signal, all output ports feeding the array elements are equally excited with an increasing phase difference, resulting in a beam at a specific angle as shown by the radiation pattern in Figure 2.3(b). If multiple beams are required, two or more input ports need to be excited simultaneously.

Figure 2.3: The BM consists of four 90° hybrids, two 45° delay lines and crossover lines. (a)The 4 x 4 BM layout. (b) The associated radiation pattern of a 4 x 4 BM.

A high-power handling routing multiplexer or switch matrix is required to select the different inputs of the BFN, resulting in a switchable phased array system. Most common implementations for routing the signal into the matrix use coaxial or multi-throw MMIC switches. Savium Technologies uses a single-pole eight-throw (SP8T) PIN diode switch matrix to route signals through the Rothman beamforming lens as shown in Figure 2.4 [2].

Figure 2.4: Switched beam phased array with an SP8T PIN diode routing switch by Savium Technologies [2].

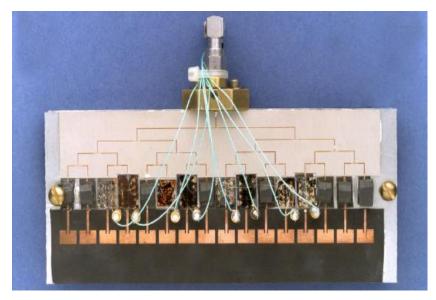

Another system is presented [3] in which a hybrid 8 x 8 BM is connected to an 8 x 2 microwave switch matrix. The resultant system is bulky and large in nature, as shown in Figure 2.5.

Figure 2.5: Hybrid 8x8 Butler matrix connected to the 8x2 microwave switch matrix [3].

To our knowledge, there has been no report of integrating a MEMS routing switch to the Butler matrix input for input port selection. The use of a multi-throw SPNT switch can allow for the design and fabrication of a purely monolithic, switchable BFN that requires very little driving DC power.

### 2.1.2 Integrated Phase Scanning ESAs

There have been many notable attempts to develop planar, integrated phased array antenna systems employing phase shifters for beam steering. Some technologies have used hybrid integration of the ESA components; however more current reports use multilayer processes and organics for the monolithic integration of these RF components.

Romanofsky et al. reported a prototype K-band linear 16-element scanning phased array based on thin ferroelectric film coupled microstripline phase shifters and microstrip patch radiators as shown in Figure 2.6, with bias voltages up to 350 V and is 11.9 cm long [4].

Figure 2.6: 16-element phased array antenna using Ba<sub>0.6</sub>Sr<sub>0.4</sub>TiO<sub>3</sub>. This ferrite-based phased array requires actuation voltages of up to 250V and is 11.9cm long [4].

These hybrid systems however may not be appropriate for constructing a large phased array antenna system since they generally require several thousand elements fed by a phase shifter as well as a switch for every antenna element. This can complicate assembly, not to mention the parasitic losses introduced and increase in size.

Monolithic systems using single and multilayer processing have recently been reported to meet current phased array system demands such as lighter weight and compact size. How et al. also presented a steerable phased array antenna using single-crystal yttrium-iron-garnet (YIG) phase shifters, illustrated in Figure 2.7. This array antenna tuned the input phases to the antenna elements by varying the bias magnetic field [5].

Figure 2.7: Layout of a phased array antenna using single-crystal YIG phase shifters [5].

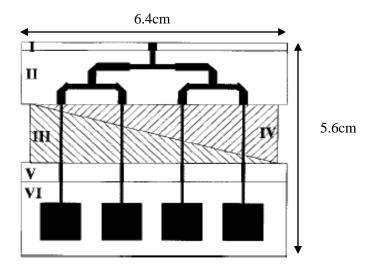

Shown in Figure 2.8 is a four element array monolithically implemented on single high resistivity silicon (HRS) substrate, and consists mainly of Wilkinson power dividers,  $Ba_xSr_{1-x}TiO_3$  (BST) true time delay (TTD) phase shifters, and microstrip radiating patches. In this case, DC bias voltages of up to 300V were required to vary the phase. The phased array has a total area of 4.6cm x 5.3cm and an operational bandwidth of 8.7% [6].

Figure 2.8: Four-element phased array integrated monolithically on a silicon substrate [6].

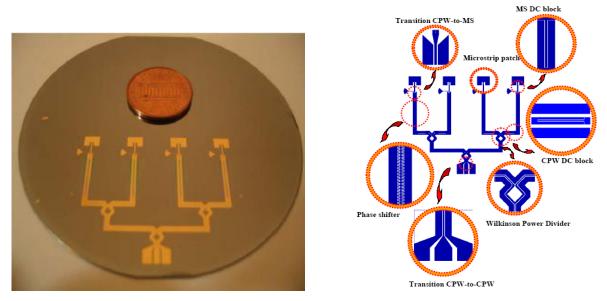

Three-dimensional Microwave Monolithic Integrated Circuits (MMICs) involve stacking multiple layers of functional modules in a limited estate. With the rising need for more compact ESA modules, this technology can be extended to multilayer ESAs. The array's components are processed and interconnected through the several layers to obtain shorter path lengths. One of the most common multilayer processes used to produce integrated ESAs is the Low Temperature Co-fired Ceramics (LTCC) process. LTCC is a high temperature process that produces multilayer circuits from ceramic substrate tapes or sheets. Conductive, dielectric, and resistive pastes are applied on each sheet or tape as needed, and the sheets are then laminated together and fired at temperatures up to 850°C in one step. The drawbacks of this technology are significant including poor thermal conductivity and shrinkage during the firing process which results in inherent feature size limitations especially at higher frequencies [7]. An LTCC-processed module consisting of single sheets with specific functions such as phase shifting, polarization, and grounding all have to be laminated together and fired in one step, as shown in Figure 2.9(a) [8]. Spin-on organics such as Benzocyclobutene (BCB) and Polyimide (PI) have also been used in designing vertically integrated ESA modules. Figure 2.9(b) illustrates a proposed 3-D vertically integrated phased array module where the layers consist of 22µm thick PI layers that are isolated with trenches and ground plane layers [9]. The issues that arise in forming this integrated module include "outgassing" defects, edge-bead effects, as well as the

planarity and leveling of polyimide over deep-via structures and layer-delaminating as a result of multi-layer stress.

(a) LTCC-processed module

(b) Polyimide-processed module

Figure 2.9: Examples of 3-D multilayer 'stacked', monolithically integrated phased array modules. (a)An LTCC processed substrate with stacked functional layers [8]. (b) A 3-D phased array module vertically integrated with 22µm thick polyimide layers [9].

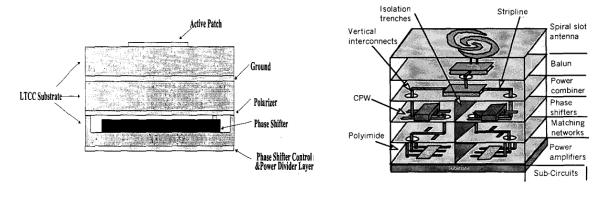

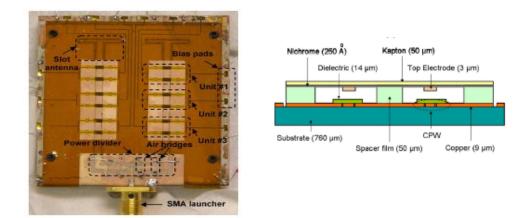

In [10], a MEMS-based ESA fabricated using printed circuit processing is reported. The loaded-line phase shifters and feed network are monolithically integrated on a Duroid substrate and operates at 9.1GHz. The ESA is composed of three stacked layers of Kapton tape, RT/Duroid substrate and a Polyflon bonding film that are laminated with thermocompression bonding to obtain the ESA prototype, as illustrated in Figure 2.10. The total area of the ESA is about 29cm<sup>2</sup>.

Figure 2.10: Top view and cross-sectional view of the PCB MEMS-based ESA [10].

Therefore, the conventional methods used to integrate ESA components have several disadvantages such as wasted area and volume, outgassing of organics and limited feature resolution. There is a need to develop a new approach for integration that will achieve breakthroughs in size, weight and cost and minimize any process variations.

### 2.2 MEMS and Micromachined ESA Components

This section will present in detail the most current developments and designs in ESA module components including RF MEMS capacitive switches, MEMS phase shifters and Butler matrices.

### 2.2.1 RF MEMS Switches

RF switches are used in a wide array of commercial, aerospace and defense application areas including satellite communications systems, wireless communications systems and radar systems. In this thesis, capacitive RF MEMS switches are designed and optimized for their implementation in an X-Band 3-bit phase shifter, and are a vital component of the final integrated phased array module. In order to choose an appropriate RF switch for this application, the required performance specifications must first be considered. These include the switch's capacitance ratio, isolation and insertion losses, power handling capabilities, switching speed, and cost of fabrication.

Traditional switches such as waveguide and coaxial switches show low insertion loss, high isolation, and good power handling capabilities but are power-consuming, slow and unreliable for prolonged applications. Current solid-state RF technologies such as the PIN diode and FET are favored for their high switching speeds, commercial availability, low cost and ruggedness. Some commercially available RF switches can support high power handling, but require large, massive packages and high power consumption. In spite of their design flexibility, two major areas of concern with solid-state switches persist: nonlinearity and bandwidth limits at higher frequencies. When operating at high RF power which is the case in satellite space-based radar systems (SBR), nonlinear switch behavior leads to spectral re-growth; this interferes with the energy outside of its allocated frequency band and causes adjacent channel jamming. An additional strong driving mechanism for

pursuing new RF technologies is the fundamental degradation of insertion loss and isolation at signal frequencies above 1-2 GHz.

The development of MEMS technology enables the fabrication of electromechanical and microelectronics components in a single chip with enhanced RF performance. MEMS RF switches combine the advantages of traditional electromechanical switches (low insertion loss, high isolation, high linearity) with those of solid-state switches (low power consumption, low mass, long lifetime). These devices are typically operated with electrostatic forces and they draw no current other than a very small leakage current. The low loss dielectrics and high conductivity metals used to construct these switches enable them to have low losses. Table 2.1 shows a comparison of MEMS, PIN diode and FET switch parameters. A disadvantage of RF MEMS switches is their actuation voltages (30-80V) which necessitate the use of CMOS up converters to raise the input 3-5V control voltage to the actuation voltage [11]. Despite that, all the advantages exhibited by RF MEMS switches as well as their potential for high reliability long lifetime operation make them a promising solution to existing low-power RF technology limitations.

| Parameter                      | RF MEMS   | PIN-Diode | FET        |

|--------------------------------|-----------|-----------|------------|

| Voltage (volts)                | 20-80     | ± 3-5     | 3-5        |

| Current (mA)                   | 0         | 0-20      | 0          |

| Power Consumption (mW)         | 0.5-1     | 5-100     | -0.5 - 0.1 |

| Switching speed                | 5-60µs    | 1-100ns   | 1-100ns    |

| C <sub>off</sub> (series) (fF) | 1-6       | 40-80     | 70-140     |

| $R_{s}$ (series) ( $\Omega$ )  | 0.5 - 2   | 2-4       | 4-6        |

| Capacitance Ratio              | 40-500    | 10        | n/a        |

| Isolation (1-10GHz)            | Very high | High      | Medium     |

| Isolation (10 – 40GHz)         | Very High | Medium    | Low        |

| Isolation (60 – 100GHz)        | High      | Medium    | None       |

| Power Handling (W)             | <1        | <10       | <10        |

Table 2.1: Performance comparison of FETs, PIN diode and RF MEMS Electrostatic Switches [11].

The primary goals of the capacitive MEMS switch performance for ESAs include: low actuation voltage, low insertion loss and high isolation, high power handling capability and fast switching speed. By manipulating the switch dimensions and parameters, these parameters can be fine-tuned, however there are tradeoffs. In ESA design, the two essential design requirements include fast switching speed and high power handling capability. In the design of the integrated ESA module, each switch would have to be capable of handling up to 700mW of power. Capacitive switches have a large contact area that allows them to handle more RF power typical of radar systems than metal-to-metal contact switches [11].

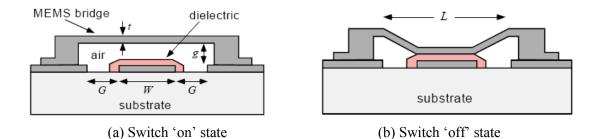

The capacitive switch typically consists of a metal bridge suspended over a driving electrode, typically coated with a thin dielectric for DC isolation when the bridge is actuated in downstate. The switch has two states – with no bias applied, the bridge remains in the upstate and is referred to the 'on' state because it allows the signal to pass through. However, when a DC voltage is applied, the switch membrane is pulled down, introducing a high capacitance and resulting in a reflective switch where the signal is not allowed to pass through; also referred to as the 'off' state. In order to obtain high isolation switches, large 'off' state capacitances and small negligible 'on' state capacitances are required to produce large capacitive ratios ( $C_{off}/C_{on}$ ). Moreover, to lengthen the switch's lifetime, it is necessary to try to reduce the actuation voltage required to pull-down the membrane into 'off' state. There has been extensive work done on MEMS switches specifically the capacitive shunt and series switches. Switch research and development focus is on different design parameters including high isolation (large capacitance ratios), lower actuation voltages, faster switching speed or enhanced power handling capability.

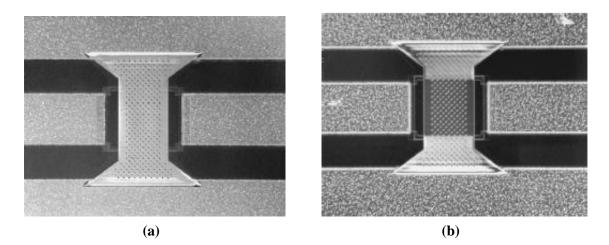

Raytheon's capacitive low-loss shunt switch, also referred to as the Texas Instrument's switch, has been used in X-band and K-band phase shifters as shown in Figure 2.11. Its performance included actuation voltages ranging between 30-50V, switching speeds as low as  $3-5\mu$ s, with a loss of only 0.07dB at frequencies ranging between 10 – 40GHz [12]. The capacitance ratio observed was approximately 80 with isolation better than only -20dB at 10GHz.

Figure 2.11: SEM image of the switch designed by Raytheon. (a)The switch in 'on' state with no DC bias applied. (b) The switch in 'off' state with a DC voltage applied [12].

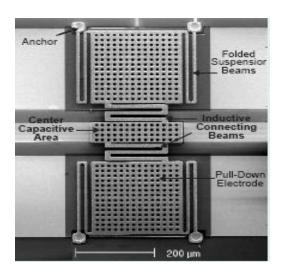

The University of Michigan has developed a shunt capacitive switch with a lower springconstant membrane. In Figure 2.12, the membrane is connected using a folded spring to the anchors lowering the spring constant to about 1-3N/m, and resulting in a pull down voltage of about 8-15V [13].

Figure 2.12: University of Michigan's low spring-constant MEMS switch [13].

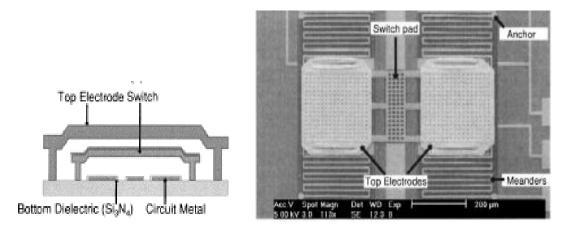

In terms of high power handling, the University of Michigan improved their design further by introducing a top electrode [14], as shown in Figure 2.13. These electrodes are 2-2.5µm above the

actuation pads and were used to pull the switch from the down state to the up state. These electrodes improved switch stability and substantially increased the RF power range over which the switch can withstand during hot switching.

Figure 2.13: Side view and top view of the University of Michigan's switch with enhanced power handling capabilities [14].

Several attempts have been reported to achieve high isolation such as using complex tuned switches [15] or by placing several MEMS switches in series [16], limiting miniaturization capabilities. Researchers have also proposed the use of high dielectric-constant ceramics such strontium-titanate oxide to achieve high isolation performance with a capacitance ratio of 600 [17]. Fabrication methods such as reducing the dielectric thickness and increasing the dielectric constant are limited due to effects such as dielectric breakdown, charge trapping and pin-hole defects.

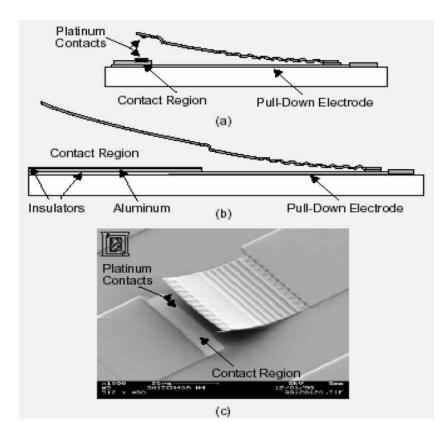

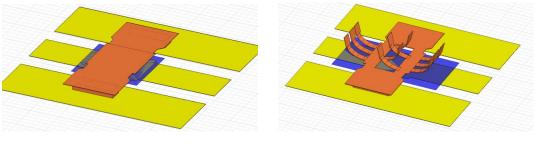

A corrugated cantilever arm in [18] is used to design a metal-to-metal contact switch as well as a capacitive coupling switch. Figure 2.14 denotes the structure of the corrugated beam. This switch is relatively small ( $55\mu$ m by  $45\mu$ m) and the pull-down electrode is in the RF path directly beneath the cantilever. To minimize the parasitic effects of the pull-down electrode, it is constructed from a high sheet resistivity metal. In the 'off' state, this switch curls up creating a relatively large separation distance of approximately 10-15 $\mu$ m, which results in a high isolation and at the same time creates an increase in the pull-in voltage. It has been reported that about 80V is required for a good contact resistance whereas the primary actuation voltage is around 35V. The capacitance ratio achieved with this design is 141:1.

Figure 2.14: Lincoln Laboratories in-line MEMS-series switch in a (a) metal-metal contact, (b) capacitive configuration and (c) SEM of the metal-metal contact switch [18].

## 2.2.2 MEMS Phase Shifters

Phase shifters are critical components in the electronic steering of antenna beams in phasedarray antennas. In the passive ESA, each T/R module usually feeds several phase shifters, which are each placed directly behind the radiating element, thus directly contributing to the noise figure of the system. The transmit power is also directly reduced by the loss of the phase shifters. The advantage is that a simpler and lower cost system results due to the smaller number of T/R modules and other components required. However, this is feasible only if the phase shifters are of very low loss since the T/R modules must compensate for the loss in the phase shifters. A high loss in the phase shifters means that the T/R module needs to be much higher in transmit power, larger in size and more costly, thus defeating the purpose of achieving a simplified design with a passive array. The phase shifter's performance can be greatly enhanced with reduced complexity and cost using RF MEMS technology.

The MEMS switch's desirable characteristics have led to their implementation in phase shifters. There are several approaches to MEMS-based phase shifters such as the switched-line circuit (also referred to as the true-time delay circuit), the distributed-line circuit, and the reflected-line circuit. There has been widespread work done on phase shifters based on MEMS by organizations such as Raytheon, Rockwell and many others.

For ESAs, the three choices for phase shifters are ferrite, PIN diode or MEMS-based phase shifters. Table 2.2 shows a comparison of loss and approximate cost of a 4-bit phase shifter [16]. Ferrite phase shifters contribute very low RF losses but can add significantly to weight and cost. PIN diode phase shifters have higher RF loss and require significant driving power. MEMS phase shifters are an attractive alternative to the conventional options since they are small, lightweight, inexpensive, and contribute smaller RF losses. Moreover, since MEMS phase shifters are electrostatically actuated, they require essentially no DC current, minimizing power consumption. The average loss of MEMS phase shifters is 2dB. This in turn translates to improvements in radar or a two-way telecommunication system. Therefore, one can eliminate an amplifier stage in the T/R chain, also resulting in a power reduction of 20-100mW per element at X-band frequencies.

| Phase Shifter | Loss (dB) | <b>Cost (\$)</b> |

|---------------|-----------|------------------|

| Ferrite       | 0.5       | 75               |

| PIN Diode     | 3.0       | 40               |

| MEMS          | 2.0       | 2                |

Table 2.2: 4-bit Phase Shifter Loss and Cost Comparison [11].

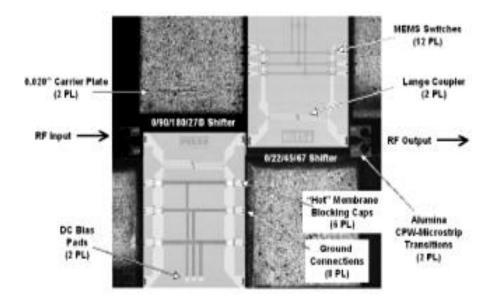

The aforementioned capacitive switches have been implemented in a 2-bit and 4-bit microstrip X-band MEMS phase shifter using Lange couplers integrated on a silicon substrate. An average loss of 1.3dB is observed between the frequencies of 8-10GHz and a limited bandwidth of 7 – 11GHz due to the use of Lange couplers in the design. The phase shifter described is illustrated in Figure 2.15 [19].

Figure 2.15: Raytheon's 4-bit X-band MEMS phase shifter designed using 3dB Lange couplers integrated on a silicon substrate [19].

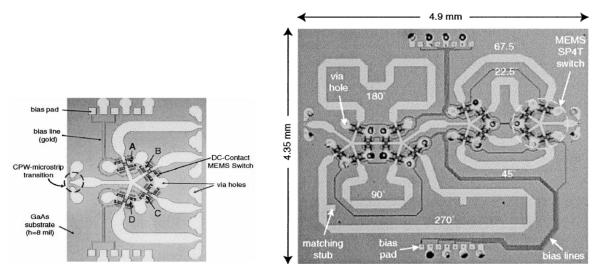

Rockwell Science Center created a wideband 4-bit switched-line phase shifter using a SP4T (single-pole four-throw) MEMS switch shown in Figure 2.16. The switches used in this case are series capacitive switches in a microstrip line configuration. This phase shifter represents the smallest area (4.9mm by 4.25mm) MEMS phase shifter developed to date with very low insertion loss performance (0.25 - 0.35dB/bit at X-band) [20, 21].

Figure 2.16: Rockwell Scientific/ University of Michigan 4-bit MEMS phase shifter [21].

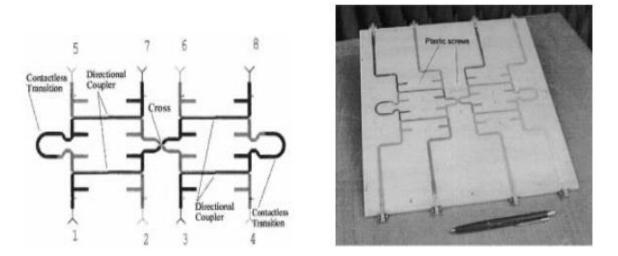

#### 2.2.3 Butler Matrices

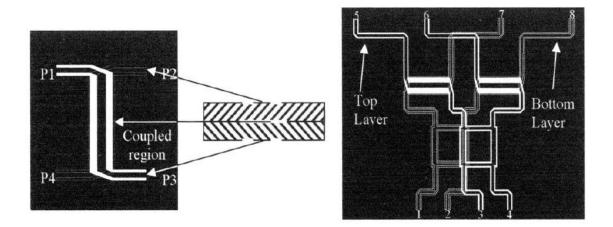

Design challenges faced when designing and fabricating Butler matrices include the realization of the crossover lines and the minimization of matrix real estate without jeopardizing circuit performance and complicating circuit fabrication. Several efforts have been reported to achieve compact Butler matrices with simple crossover lines. A microstrip-slot-microstrip approach is used in [22, 23] where the matrix is printed on two distinct substrate layers with a ground plane in between, as shown in Figure 2.17. The crossover lines are realized by coupling through the slot from one layer to the next. This technique introduces fabrication complexities and requires accurate substrate alignment.

*Figure 2.17: Layout of the slot-coupled coupler and 4 x 4 Butler matrix. The crossover lines are realized by coupling through the slot from layer to the next [23].*

In [24 and 25], the need for crossovers is eliminated by replacing the crossing with a 0dB branch-line coupler as shown in Figure 2.18. Even though this design greatly simplifies the fabrication and assembly of the BM, the circuit's real estate is drastically increased.

*Figure 2.18: Layout and photo of the 4 x 4 Butler matrix network without any crossovers using a 0dB branch-line coupler in order to reduce circuit fabrication complexity [24].*

A 4 x 4 compact BM developed in [26] uses a new bi-layer structure and is illustrated in Figure 2.19. The structure is low-loss and compact using foam-suspended strip line. Transitions between the two layers were achieved using contact-less coupling and the crossovers occur on the opposite sides of the suspended substrate with increased characteristic impedances lines to reduce the coupling capacitance between the overlapping lines.

Figure 2.19: 4 x 4 compact Butler matrix layout and realized structure. The structure is low-loss and compact using low-loss foam-suspended strip line [26].

Current research shows that there is a need to develop a process to achieve a compact integrated Butler matrix reducing the complexity of crossover design and matrix fabrication without compromising wafer real estate and matrix RF performance.

# Chapter 3 SPNT Capacitive Shunt Dual-Warped Beam Switches

Space-Based Radar (SBR) systems applications require single-pole n-throw (SPNT) switches with reduced actuation voltages, fast switching speeds, compact size, high isolation and low insertion loss. This section will introduce a novel design approach to capacitive MEMS switches using warped bimetallic beams with low-loss and high isolation over X-band frequencies. The fabrication process flow for attaining such a switch structure will also be presented. Mechanical modeling obtained of this structure will be discussed followed by a detailed description of the measured results.

#### 3.1 SPST Dual Warped-Beam Capacitive MEMS Switch

In general, MEMS switches can be classified into two main categories: metal-to-metal and capacitive switches. Shunt capacitive switches are chosen for the design of the integrated ESAs because their large contact area can handle more RF power than metal-to-metal contact switches [11], an essential requirement for space-based applications. The electrostatically actuated MEMS switches outperform solid state switches such as FETs, HEMTs and PIN diodes [15]. MEMS switches have low insertion loss and do not exhibit the nonlinearities associated with semiconductor junctions in PIN and FET devices. This improves their distortion characteristics and power handling capabilities, an important consideration in phased array systems that contain a large number of switches and limited power resources.

The physical structure of the electrostatic-type shunt capacitive MEMS switch in its two states, 'on' and 'off', is shown in Figure 3.1. In this thesis, the terms 'on' and 'off' states, which correspond to the switch in "upstate" and "downstate" respectively, will be used to describe and characterize the switch's behavior. The MEMS switch is electrostatically actuated with fixed-fixed metal bridges suspended over the center conductors of the FGC transmission line. When no DC bias is applied, the switch presents a very small shunt capacitance between the center conductor and ground planes. This state is referred to as the 'on' state and the switch behaves as a through switch allowing the RF signal to propagate through with negligible loss. When a DC voltage is applied between these two metal layers, the electrostatic force starts to pull the bridge towards the lower conductor. The bias is then increased until a threshold voltage is reached at which point the bridge's spring force is overcome and the bridge collapses down on top of the signal line separated by a thin dielectric isolation layer. The switch emulates a short circuit by introducing a large capacitance and reflects the signal back. This state is referred to as the 'off' state.

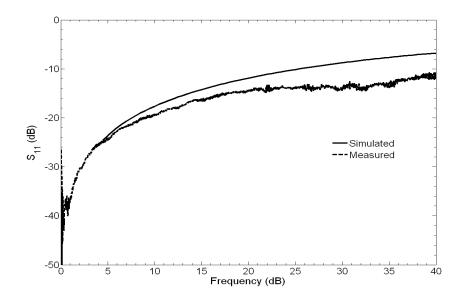

Figure 3.1: Shunt capacitive MEMS switch structure in its two states. (a) Capacitive shunt switch in 'on' state. (b) Capacitive shunt switch in 'off' state.