## A Multiple-objective ILP based Global Routing Approach for VLSI ASIC Design

by

Zhen Yang

A thesis

presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008 ©Zhen Yang 2008 I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

A VLSI chip can today contain hundreds of millions transistors and is expected to contain more than 1 billion transistors in the next decade. In order to handle this rapid growth in integration technology, the design procedure is therefore divided into a sequence of design steps. Circuit layout is the design step in which a physical realization of a circuit is obtained from its functional description. Global routing is one of the key subproblems of the circuit layout which involves finding an approximate path for the wires connecting the elements of the circuit without violating resource constraints. The global routing problem is NP-hard, therefore, heuristics capable of producing high quality routes with little computational effort are required as we move into the Deep Sub-Micron (DSM) regime.

In this thesis, different approaches for global routing problem are first reviewed. The advantages and disadvantages of these approaches are also summarized. According to this literature review, several mathematical programming based global routing models are fully investigated. Quality of solution obtained by these models are then compared with traditional Maze routing technique. The experimental results show that the proposed model can optimize several global routing objectives simultaneously and effectively. Also, it is easy to incorporate new objectives into the proposed global routing model. To speedup the computation time of the proposed ILP based global routing approach. The experimental results indicate that the bottom-up global routing method can reduce the computation time effectively with a slight increase of maximum routing density.

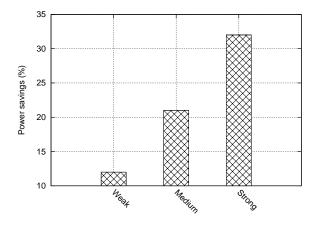

In addition to wire area, routability, and vias, performance and low power are also important goals in global routing, especially in deep submicron designs. Previous efforts that focused on power optimization for global routing are hindered by excessively long run times or the routing of a subset of the nets. Accordingly, a power efficient multi-pin global routing technique (PIRT) is proposed in this thesis. This integer linear programming based techniques strives to find a power efficient global routing solution. The results indicate that an average power savings as high as 32% for the 130-nm technology can be achieved with no impact on the maximum chip frequency.

## Acknowledgements

I would like to take this opportunity to express my sincere appreciation and thanks to my supervisor professor Anthony Vannelli and professor Shawki Areibi for their guidance and assistance. Many thanks to professor Mohab Anis, professor Geatherinc H. Gebotys, professor Samir Elhedhi and professor Richard Shi for reviewing this thesis. Their invaluable comments made this work a much better one. The work in this thesis has been founded by National Resources of Canada. I would like to thank this institution for supporting me during my studies and making this work possible.

I want to especially thank my husband Wenxin Wang, my sister, my parents and my parents in-law for their continuous encouragement and support.

And finally, many thanks to all my friends and well-wishers who exhorted me to work dedicatedly towards the fulfilment of the objectives of this research.

### To

## my family

whose love and encouragement helped accomplish this  ${\it thesis}.$

## Contents

| 1 | Intr | oducti | ion                                      | 1  |

|---|------|--------|------------------------------------------|----|

|   | 1.1  | Resear | rch Motivations                          | 4  |

|   |      | 1.1.1  | Interconnect in DSM Design               | 4  |

|   |      | 1.1.2  | Hierarchical ILP based Global Routing    | 6  |

|   |      | 1.1.3  | Multi-objective Global Routing           | 7  |

|   |      | 1.1.4  | Power-Efficient ILP based Global Routing | 8  |

|   |      | 1.1.5  | Overview of Research Approaches          | 9  |

|   | 1.2  | Contri | ibutions                                 | 10 |

|   | 1.3  | Thesis | S Organization                           | 11 |

| 2 | Bac  | kgroui | nd                                       | 12 |

|   | 2.1  | Physic | cal Design                               | 13 |

|   |      | 2.1.1  | Circuit Partitioning                     | 14 |

|   |      | 2.1.2  | Circuit Floorplanning and Placement      | 14 |

|   |      | 2.1.3  | Global and Detailed Routing              | 16 |

|   | 2.2  | Layou  | t Styles                                 | 17 |

|   |      | 2.2.1  | Gate Array Layout                        | 18 |

|   |            | 2.2.2                                    | Full-Custom Layout                           | 19                               |

|---|------------|------------------------------------------|----------------------------------------------|----------------------------------|

|   |            | 2.2.3                                    | Standard Cell Layout                         | 20                               |

|   |            | 2.2.4                                    | Mixed Size Layout                            | 22                               |

|   | 2.3        | Globa                                    | l Routing                                    | 23                               |

|   |            | 2.3.1                                    | Problem Overview                             | 24                               |

|   |            | 2.3.2                                    | Route Construction                           | 25                               |

|   |            | 2.3.3                                    | Global Routing Cost Functions                | 26                               |

|   | 2.4        | Multi-                                   | objective based Optimization                 | 32                               |

|   |            | 2.4.1                                    | General multi-objective Optimization Problem | 32                               |

|   | 2.5        | Test C                                   | Circuits                                     | 35                               |

|   |            | 2.5.1                                    | Software Packages Used                       | 35                               |

|   | 2.6        | Summ                                     | ary                                          | 36                               |

| 3 | Lite       | rature                                   | Review                                       | 38                               |

|   |            | Sequential Global Routing                |                                              |                                  |

|   | 3.1        | Seque                                    | ntial Global Routing                         | 39                               |

|   | 3.1<br>3.2 |                                          | rrent Global Routing                         | 39<br>44                         |

|   |            |                                          |                                              |                                  |

|   |            | Concu                                    | rrent Global Routing                         | 44                               |

|   |            | Concu                                    | rrent Global Routing                         | 44<br>44                         |

|   |            | Concu<br>3.2.1<br>3.2.2<br>3.2.3         | Integer Programming based Global Routing     | 44<br>44<br>49                   |

|   |            | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4         | Integer Programming based Global Routing     | 44<br>44<br>49<br>54             |

|   | 3.2        | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Meta | Integer Programming based Global Routing     | 44<br>44<br>49<br>54<br>55       |

|   | 3.2        | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Meta | Integer Programming based Global Routing     | 44<br>44<br>49<br>54<br>55<br>59 |

| 4 | Flat | t Mult  | i-objective Global Routing                       | 71  |

|---|------|---------|--------------------------------------------------|-----|

|   | 4.1  | Rectil  | inear Spanning Tree Construction                 | 72  |

|   | 4.2  | Addit   | ional Tree Construction                          | 74  |

|   |      | 4.2.1   | Additional Tree Construction for 3-terminal Nets | 74  |

|   | 4.3  | Model   | Formulation                                      | 78  |

|   |      | 4.3.1   | Wirelength Model (WLM)                           | 78  |

|   |      | 4.3.2   | Edge Capacity Model (ECM)                        | 81  |

|   |      | 4.3.3   | Via Minimization Model (VMM)                     | 82  |

|   |      | 4.3.4   | Combined Model-1 (WVEM)                          | 84  |

|   |      | 4.3.5   | Combined Model-2 (WVZM)                          | 87  |

|   | 4.4  | A Nev   | w Global Routing Framework (RNWO)                | 88  |

|   | 4.5  | Summ    | nary                                             | 93  |

| 5 | Hie  | rarchio | cal ILP Based Global Routing                     | 95  |

|   | 5.1  | Top-d   | own Global Routing With Net Refinement           | 96  |

|   |      | 5.1.1   | Coarsening Process                               | 96  |

|   |      | 5.1.2   | Coarsest Level                                   | 99  |

|   |      | 5.1.3   | Uncoarsening Process                             | 99  |

|   |      | 5.1.4   | Experimental Results                             | 101 |

|   | 5.2  | Top-d   | own Global Routing Without Net Refinement        | 103 |

|   |      | 5.2.1   | Experimental Results                             | 104 |

|   | 5.3  | Botto   | m-up Global Routing Without Net Refinement       | 108 |

|   |      | 5.3.1   | Experimental Results                             | 109 |

|   | 5 4  | Summ    | iarv                                             | 117 |

| 6            | Pow             | ver-effi                  | cient ILP based Global Routing                | 119 |

|--------------|-----------------|---------------------------|-----------------------------------------------|-----|

|              | 6.1             | Prelin                    | ninaries                                      | 120 |

|              |                 | 6.1.1                     | Interconnect Modeling                         | 120 |

|              | 6.2             | Power                     | -Efficient Multi-pin ILP Based Global Routing | 123 |

|              |                 | 6.2.1                     | PIRT Phases                                   | 124 |

|              |                 | 6.2.2                     | Phase I (Initialization)                      | 125 |

|              |                 | 6.2.3                     | Phase II (Power Minimization)                 | 129 |

|              | 6.3             | Exper                     | imental Results                               | 131 |

|              |                 | 6.3.1                     | Power Savings                                 | 133 |

|              |                 | 6.3.2                     | Routing Quality                               | 138 |

|              |                 | 6.3.3                     | Computation Time                              | 139 |

|              | 6.4             | Summ                      | nary                                          | 139 |

| 7            | Con             | clusio                    | ns                                            | 141 |

|              | 7.1             | Flat N                    | Multi-objective Global Routing                | 142 |

|              | 7.2             | Hierar                    | rchical ILP based Global Routing              | 142 |

|              | 7.3             | Power                     | Aware ILP based Global Routing                | 143 |

|              | 7.4             | Future                    | e Work                                        | 144 |

| $\mathbf{A}$ | Glo             | ssary                     |                                               | 146 |

| В            | Geo             | $\mathbf{Stein} \epsilon$ | er & Flute                                    | 148 |

| Bi           | ibliography 150 |                           |                                               |     |

## List of Tables

| 2.1  | MCNC Tested Circuit Statistics                                     | 36  |

|------|--------------------------------------------------------------------|-----|

| 2.2  | ISPD98 IBM Benchmark & ISPD2007 Benchmark Statistics $\ .\ .\ .$ . | 36  |

| 4.1  | Tree Construction for Long Nets                                    | 75  |

| 4.2  | Comparison of Different Adding Trees Methods                       | 75  |

| 4.3  | Comparison of Different Additional Tree Conditions                 | 78  |

| 4.4  | Comparison of WLM and WVEM model                                   | 85  |

| 4.5  | Comparison of VMM and WVEM model                                   | 86  |

| 4.6  | Comparison of ECM and WVEM model                                   | 86  |

| 4.7  | Comparison of ECM and WVZM model                                   | 88  |

| 4.8  | Results Comparison of Different Routers                            | 89  |

| 4.9  | Results of RNWO Model                                              | 90  |

| 4.10 | Results Comparison of Different Routers                            | 92  |

| 4.11 | Results Comparison for Different Routers                           | 93  |

| 5.1  | Comparison of Flat Level Routing and Top-down Routing              | 102 |

| 5.2  | Computation Time of Top-down Routing with Refinement (4 Levels)    | 103 |

| 5.3  | ECM Model: Flat Level Routing vs Top-down Routing (2,3,4 levels)   | 104 |

| 5.4  | ECM Model: Flat Level Routing vs Top-down Routing (4,5,6 levels)            | 105 |

|------|-----------------------------------------------------------------------------|-----|

| 5.5  | WLM Model: Flat Level vs Top-down Routing (2,3,4 levels) $$                 | 106 |

| 5.6  | WLM Model: Flat Level vs Top-down Routing (4,5,6 levels) $$                 | 106 |

| 5.7  | VMM Model: Flat Level vs Top-down Routing (2,3,4 levels) $$                 | 106 |

| 5.8  | VMM Model: Flat Level vs Top-down Routing $(4,5,6,$ levels)                 | 107 |

| 5.9  | WVEM Model: Flat Level vs Top-down Routing (2,3,4 levels) $$                | 107 |

| 5.10 | WVEM Model: Flat Level vs Top-down Routing (4,5,6 levels) $$                | 107 |

| 5.11 | Comparison of Top-down Routing for Different Models                         | 108 |

| 5.12 | ECM Model: Flat Level Routing vs Bottom-up Routing $(4,5,6 \text{ levels})$ | 110 |

| 5.13 | WLM Model: Flat Level vs Bottom-up Routing (2,3,4 levels)                   | 112 |

| 5.14 | WLM Model: Flat Level vs Bottom-up Routing (4,5,6 levels)                   | 112 |

| 5.15 | VMM Model: Flat Level vs Bottom-up Routing (2,3,4 levels)                   | 113 |

| 5.16 | VMM Model: Flat Level vs Bottom-up Routing (4,5,6 levels)                   | 113 |

| 5.17 | WVEM Model: Flat Level vs Bottom-up Routing $(2,3,4 \text{ levels})$        | 113 |

| 5.18 | WVEM Model: Flat Level vs Bottom-up Routing $(4,5,6 \text{ levels})$        | 113 |

| 5.19 | Comparison of Bottom-up Routing for Different Models (ILP results)          | 114 |

| 5.20 | Comparison of Flat Level, Top-down and Bottom-up routing                    | 114 |

| 5.21 | Flat Routing & Top-down Routing (5-level)                                   | 116 |

| 5.22 | Flat Routing & Bottom-up Routing (5-level)                                  | 116 |

| 6.1  | Technology & Equivalent Circuit Model Parameters for Global In-             |     |

|      | terconnets                                                                  | 132 |

| 6.2  | Comparison of Delay Minimization and Power Minimization Models              | 138 |

| 6.3  | CPU Time Comparison of PIRT Method for Buffer Size 15 x 130nm.              | 139 |

$B.1 \ \ Results \ Comparison \ for \ Different \ Initial \ Steiner \ Tree \ Construction \ . \ \ 149$

# List of Figures

| 1.1  | VLSI Design Flow                                        | 2  |

|------|---------------------------------------------------------|----|

| 1.2  | Interconnect and Gate Delay                             | 5  |

| 1.3  | Overall Research Approaches                             | 9  |

| 2.1  | Physical Design Cycle                                   | 13 |

| 2.2  | Different Layout Styles for Digital Integrated Circuits | 17 |

| 2.3  | Gate Array Layout                                       | 18 |

| 2.4  | Full Custom Layout                                      | 19 |

| 2.5  | Standard Cell Layout                                    | 20 |

| 2.6  | Mixed Size Layout                                       | 23 |

| 2.7  | Grid Graph for Standard-cell Layout Style               | 24 |

| 2.8  | Four-terminal net and its Hanan grid                    | 25 |

| 2.9  | Total Wire Length                                       | 27 |

| 2.10 | Total Number of Bends                                   | 29 |

| 2.11 | Example of Congestion Measure                           | 30 |

| 2.12 | Optimization Problem with Two Objectives                | 33 |

| 3.1  | Different Approaches for Global Routing Problem         | 38 |

| 3.2  | Maze Routing Algorithm                              | 39  |

|------|-----------------------------------------------------|-----|

| 3.3  | Line Probe Routing Algorithm                        | 40  |

| 3.4  | Flow Chart of the Global Routing Methodology        | 46  |

| 3.5  | Additional Tree Construction                        | 49  |

| 3.6  | Hierarchical Decomposition                          | 50  |

| 3.7  | Bottom Up Hierarchical Routing                      | 51  |

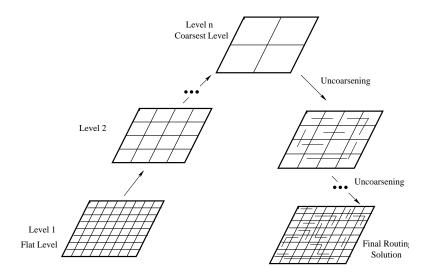

| 3.8  | Multilevel Routing Flow                             | 52  |

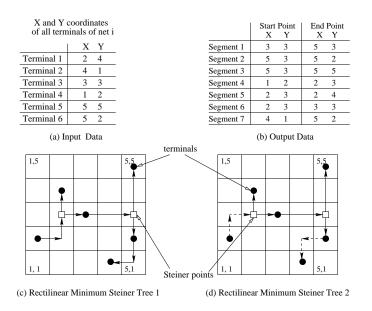

| 4.1  | Generate Rectilinear Minimum Steiner Tree           | 73  |

| 4.2  | Spanning Tree Construction for Long Nets            | 74  |

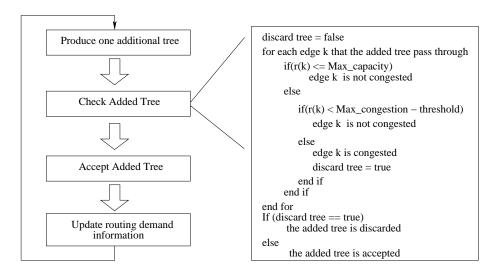

| 4.3  | Pseudocode of Relaxed Adding Tree Condition         | 77  |

| 4.4  | Example of Wirelength Minimization Model            | 80  |

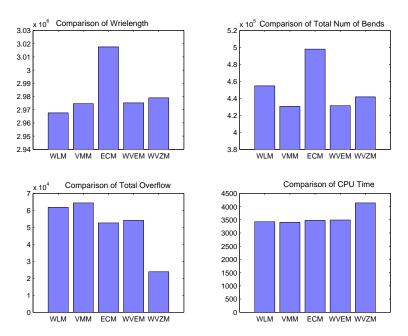

| 4.5  | Comparison of Different Models                      | 89  |

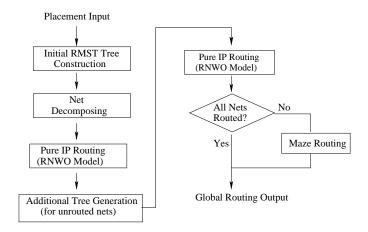

| 4.6  | New Framework of ILP based Router                   | 92  |

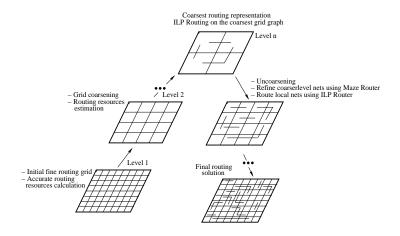

| 5.1  | Top-down Global Routing with Net Refinement         | 96  |

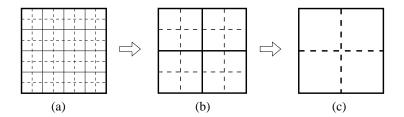

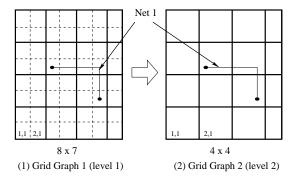

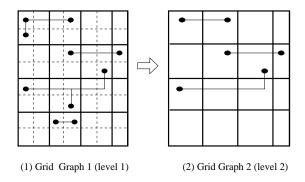

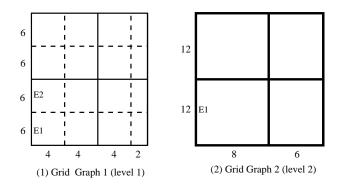

| 5.2  | Merging of Grid Cells                               | 97  |

| 5.3  | New Net-list Generation                             | 98  |

| 5.4  | Routing Resource Estimation                         | 98  |

| 5.5  | Different type of nets at refinement stage          | 99  |

| 5.6  | Refinement of coarser level nets                    | 100 |

| 5.7  | Top-down Hierarchical Global Routing                | 104 |

| 5.8  | Bottom-up Hierarchical Global Routing               | 109 |

| 5.9  | Bottom-up Routing of Different Levels for ECM Model | 111 |

| 5.10 | Bottom-up & Top-down Routing                        | 116 |

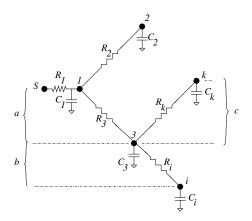

| 6.1  | RC Tree [Raba03a]                                                                          | 120 |

|------|--------------------------------------------------------------------------------------------|-----|

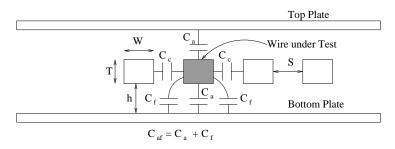

| 6.2  | Wire structure for capacitance extraction                                                  | 121 |

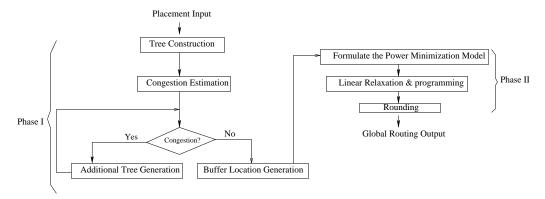

| 6.3  | PIRT flow chart                                                                            | 124 |

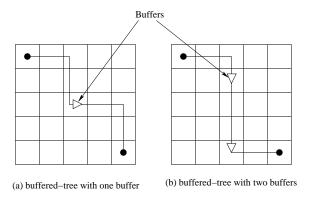

| 6.4  | Buffer insertion for two-terminal nets (a) buffered-tree with one buffer.                  |     |

|      | (b) buffered-tree with two buffers                                                         | 127 |

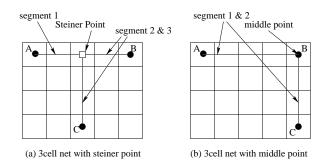

| 6.5  | Buffer insertion for three terminal nets (a) 3cell net with Steiner                        |     |

|      | point. (b) 3cell net with middle point                                                     | 128 |

| 6.6  | Buffer Insertion Algorithm                                                                 | 128 |

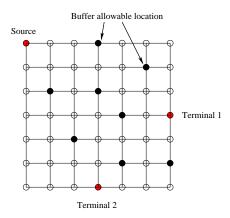

| 6.7  | Buffer location generation                                                                 | 133 |

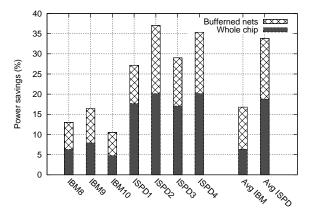

| 6.8  | Power savings by PIRT and the average for IBM and ISPD bench-                              |     |

|      | marks (strong buffer size.)                                                                | 135 |

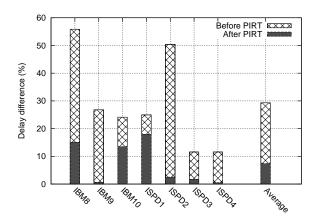

| 6.9  | Delay difference for the second longest net before and after PIRT. $$ .                    | 137 |

| 6.10 | Average power reduction over different buffer sizes $(5,10 \text{ and } 15 \text{ times})$ |     |

|      | the minimum sized buffer)                                                                  | 137 |

## Chapter 1

## Introduction

The last few decades brought explosive growth in the electronics industry due to the rapid advances in integration technologies and the different benefits of large-scale system design. As a result, System-on-Chip (SoC) designs have become one of the main drivers of the semiconductor technology in recent years. By employing third party intellectual property (IP) cores, designers today can improve design productivity and cut development costs and time. However, as more and more complex functions are integrated into a small package, State-of-the-art VLSI chips, such as the INTEL Pentium IV or Itanium II, tend to contain hundreds of millions transistors [Kang03]. Designing such a multi-million transistor chip and ensuring that it operates correctly when the first silicon returns is a daunting task that is virtually impossible without the help of Computer Aided Design (CAD) tools [Raba03b].

The phrase associated with the task of automatically designing a circuit using CAD tools is called Design Automation (DA). The ultimate goal of the DA research

field is to fully automate the tasks of designing, verifying, and testing a circuit. Unfortunately, there is still a long way from achieving this goal. No CAD design flow is currently capable of handling the enormous and often contradicting design goals required by the modern VLSI circuits. For such a complicated problem, the feasible approach is to use a divide-and-conquer strategy in which the whole design task is broken down into several sub-tasks that are more manageable for a single design tool.

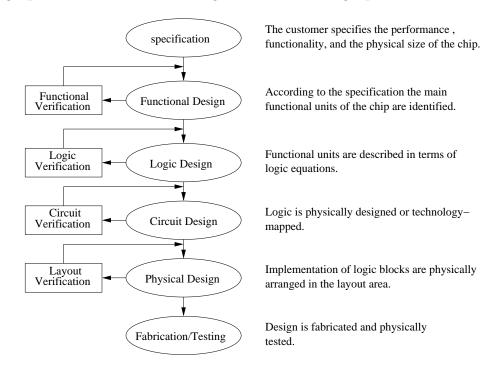

The VLSI design cycle starts with a formal specification of a VLSI chip that follows a series of steps, and eventually produces a packaged chip. A typical VLSI design process is illustrated in Figure 1.1. The design process of a VLSI circuit

Figure 1.1: VLSI Design Flow

begins with a formal specification of the circuit. The factors to be considered in

this process include: performance, functionality, and physical dimensions. The end results are specifications for the size, speed, power, and functionality of the VLSI circuit. The basic architecture of the circuit is also specified.

Following the specification step, the main functional units of the circuit are determined. In the functional design step the interconnect requirements between the units, area, power, and other parameters of each unit are also identified and estimated [Sher99]. These functional units could either be implemented using Application Specific Integrated Circuits (ASIC) or Field Programmable Gate Arrays (FPGA) design styles. The description of this design step is a high-level description and usually expressed as Register Transfer Logic (RTL).

In the logical design stage, the functional units are described in terms of primitive logic operations (NAND, NOT, etc.). This description could be expressed in a Hardware Description Language (HDL), such as VHDL and Verilog, which can be used in simulation and verification [Sher99].

Following the logical design, a technology-dependent description of the circuit is created. At this design level, the whole circuit is implemented as transistors. In some implementation topologies, logic equations are broken down and mapped to available physical circuit blocks in the circuit topology (called *technology mapping*), or pre-designed logic circuit implementations (e.g., a standard-cell library) [Thom00].

The physical design step involves converting the circuit representation of each component into a geometric representation (also called a layout). Connections between different components are also expressed as geometric patterns. The end result of physical design is a placed and routed design, from which the photolithography

masks can be derived for chip fabrication [Sher99]. Since the physical design problem is an NP-hard problem it is usually broken down into several sub-problems, referred to as partitioning, placement and routing. This thesis is mainly concerned with the global routing stage.

Finally, the wafer is manufactured and diced in a fabrication facility. Each chip is then packaged and tested to ensure that it meets all design specifications and that it functions properly.

Note that in Figure 1.1 the *verification* following each design step plays a very important role in the entire design cycle. The failure to properly verify a design in its early phases typically causes significant and expensive re-design at later stages, which ultimately tend to increase the time-to-market [Kang03]. In addition, although the design procedure has been described as a sequence of steps, the individual design steps are not mutually exclusive. Each step influences subsequent steps, and the results of any step may be used as feedback information to revise an earlier step. Several iterations of the design procedure may be required to obtain a satisfactory design for any given Integrated Circuit.

### 1.1 Research Motivations

In this section, we will highlight the main motivations driving the PhD research.

### 1.1.1 Interconnect in DSM Design

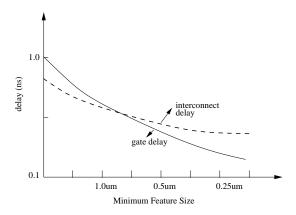

In deep sub-micron (DSM) regimes, the shrinking geometries and increasing average wirelength due to the increasing design complexities make interconnect capacitance  $C_{wire}$  become dominant over gate capacitance  $C_{gate}$ . It has been reported that the interconnection delay consumes a major portion of the clock cycle today and is projected to continue to do so in the future [Asso97], as illustrated in Figure 1.2. Apart from the circuit delay, wire capacitance also dominates the switched

Figure 1.2: Interconnect and Gate Delay

capacitance power, as shown in equation 1.1.

$$P_{switching} = \alpha_{0 \to 1} \cdot V_{dd}^2 \cdot f_{clk} \cdot (C_{qate} + C_{wire}) \tag{1.1}$$

Since wire load has an important impact on circuit delay and power, global routing which determines the approximate path for each net plays critical role in today's performance-driven low-power VLSI design.

Yet, another important implication of decreasing devices and wire geometries is that the number of wires used to connect the components in the circuits has grown exponentially. As a result, a global routing heuristic that produces excellent results for small size problem may take days or weeks to obtain a good result. Obviously, a computationally expensive technique is often useless to the modern just-in-time fabrication mentality.

#### 1.1.2 Hierarchical ILP based Global Routing

Since the computation time of a global routing algorithm must be appropriate for today's large circuits, an approach that operates in a reasonable amount of time, while still achieving good solutions is desirable. When solving the global routing problem, sequential approaches, such as Maze router [Kast], tend to route one net at time. Once a net has been routed, it may block other nets which are yet to be routed, and in the worst case, it may lead to unroutable solutions. Therefore, these methods are highly dependent on the order in which the nets are routed. Also, when a sequential approach does find a solution, it is not known whether or not this solution is optimal, or how far it is from the optimal solution. Modeling the global routing problem as a mathematical optimization problem gives a global view of the routing problem and eliminates the dependency on the ordering of the nets. In addition, the evaluation of optimality of solutions becomes possible. However, global routing approaches that operate on flat large circuits tend to have a scaling problem. Accordingly, a hierarchical global routing approach becomes essential to shorten the design period. The hierarchical global routing problem has been studied in the literature [Burs83b, Luk87, Heis91, MS84, Hu85, Gegu00, Cong01a, L02] and the general approaches have been developed: the top-down method, the bottom-up method, and the multilevel method. The hierarchical nature of the multilevel algorithm makes it very scalable to large designs. Moreover, a multilevel hierarchical algorithm is more flexible than other hierarchical approaches. In the coarsening passes, more routing resources information can be obtained, which provides a good

guide to the coarse level path searching. During the uncoarsening process, the fine level router has the flexibility to refine the coarse level result based on more detailed information about local resource and congestion. All these features make the multilevel method attractive to achieve good solutions efficiently. Hence, one motivation of this research is to identify the effectiveness of the multilevel hierarchical techniques on solutions obtained by the proposed flat ILP based global routing technique.

#### 1.1.3 Multi-objective Global Routing

With the maturity of DSM technology, more and more complex circuits and functions with tens to hundreds of millions transistors can be integrated into a single chip. For these circuits, area and routability become the fundamental goals of global routing. The shrinking of geometries also makes the interconnect capacitance a dominant factor in determining circuit speed and switching power dissipation. At the global routing stage, which determines how signal nets will finally be connected, it is necessary to consider the wire delays and power so that the overall chip performance can be maximized accurately. Meanwhile, to satisfy the increasing needs of interconnect, over-the-cell (OTC) multi-layer (more than two layers) routing is becoming more popular. As a result, a large number of vias are introduced to connect the wire segments on different layers. However, it is desirable to reduce the number of vias because they not only increase the interconnect area, but also increase the manufacturing cost and cause several problems in reliability and performance. Clearly, in the DSM regime, not only is global routing required to optimize the fundamental objectives (e.g. area and routability), but it also needs

to address other important design factors (e.g. timing, via minimization, power dissipation, crosstalk). Therefore, another motivation of this research is to develop an effective multi-objective modeling method to solve the global routing problem that has several conflicting goals.

### 1.1.4 Power-Efficient ILP based Global Routing

In fact, the number of interconnects and buffers used to achieve timing closure are becoming one of the major challenges facing designers in the sub-90nm ICs. This is attributed to the continuous increase of the number of logic blocks facilitated by the continuous shrinking of device dimensions. In order to mitigate the impact of these interconnects, designers have shifted their focus to interconnect centric designs pioneered by Cong et. al. [Cong96], where the wire is the center of the chip design flow.

Traditionally, delay and routing were the focus of most optimization efforts of the interconnect problem. However, the power consumption of the interconnects is becoming a crucial factor in determining the overall chip performance [Bane02]. In order to tackle the interconnect bottleneck, researchers have developed several subproblems that deal with the various aspects of the interconnects. These problems start from the simple problem of buffer insertion determining the number and the positions of buffers to minimize delay and increase in complexity up to the multi-objective maze routing, where a combined routing and power optimization under relaxed delay constraints is introduced. The drawbacks of these power-aware routing methods are their inability or inefficiency to find the routing tree for multi-pin

nets. These nets approximately represent 30-40% of the interconnects on a modern chip [Cong01b]. Due to such drawbacks, another motivation of this research is to develop an approach that is capable of timing optimization, buffer insertion and power reduction simultaneously with routability consideration.

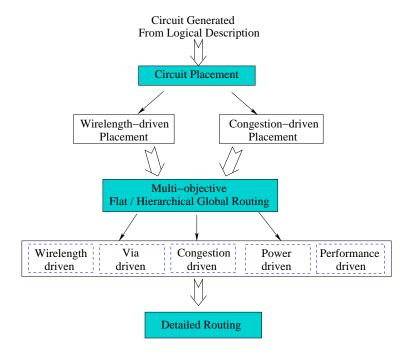

#### 1.1.5 Overview of Research Approaches

The overall research approaches used to tackle the circuit layout problem is separated into two stages (i.e. wirelength-driven or congestion-driven placement and multi-objective flat/hierarchical global routing) as illustrated in Figure 1.3. The re-

Figure 1.3: Overall Research Approaches

search first attempts to investigate several mathematical models and explore their effectiveness (introduced in Chapter 4). Following that, a hybrid global routing

framework that combines a pure IP model with a traditional sequential router is proposed. Quality of solution obtained by this routing framework is then compared with state-of-the-art routers. In addition, several hierarchical global routing methods are combined with the flat ILP based global router to reduce the computation time. Finally, power optimization problem is considered in the global routing stage and the performance of power-efficient ILP based global routing model is evaluated.

#### 1.2 Contributions

The main contributions of the thesis can be summarized as:

- Investigating novel flexible ILP based global routing models (WVEM & WVZM) to optimize several design objectives simultaneously and efficiently.

- Proposing a novel pure IP based model to route 98% of nets without generating any overflow and combining it efficiently with a sequential router to provide better solutions with fast runtime.

- The hybrid model proposed is almost 8x faster than the multi-commodity flow approach [Albe01] and achieves better quality in terms of wirelength.

- Integrating a flat ILP based global routing approach with a top-down and bottom-up hierarchical methods which differs from traditional methods that seek to use Maze router within the flow [L02].

- Proposing a power-efficient ILP based global routing method to perform the timing optimization, buffer insertion and power reduction simultaneously with routability consideration.

## 1.3 Thesis Organization

Chapter 2 provides essential background on the physical design automation problem, the global routing sub-problem and the multi-objective optimization techniques. In addition, all benchmarks used to evaluate the performance of the proposed global routing results are introduced. The different layout styles that affect physical design are also described. Chapter 3 reviews state-of-the-art global routing approaches and different buffer insertion techniques. In Chapter 4 a flat ILP based global routing method with different formulations is introduced. A hybrid global routing framework that combines a pure IP model with a traditional sequential router is also presented. Chapter 5 introduces two hierarchical global routing methods and gives the experimental results. Chapter 6 presents a power-efficient multi-pin ILP based global routing method. Finally, Chapter 7 provides conclusions and a summary of the future work.

## Chapter 2

## Background

In the combinatorial sense, physical design automation is a constrained optimization problem [Sher99]. We are given a circuit (usually a module-wire connection-list called a *netlist*) which is a description of switching elements and their connecting wires. We seek an assignment of X and Y coordinates of the circuit components (in the plane or in one of a few planar layers) that satisfies the requirements of the fabrication technology (sufficient spacing between wires, restricted number of wiring layers, and so on) and that minimizes certain cost criteria. Practically, all aspects of the physical design problem as a whole are intractable; that is, they are NP-hard [Hach89]. Consequently, we have to resort to heuristic methods to solve this complex problem. One of these methods is to break up the problem into subproblems (partitioning, placement and routing), which are then solved one after the other. Another technique that is used to simplify the complexity of physical design automation is to narrow the search to localized regions of the search space through circuit clustering.

This chapter gives a detailed background on physical design automation in general and the global routing in particular.

## 2.1 Physical Design

Physical Design of VLSI circuits is a process of determining the location of devices and connecting them inside the boundary of a VLSI chip. It is one of many interrelated complex tasks in VLSI circuit design. Not surprisingly, this complex task is handled by dividing the original task into more tractable sub-tasks such that a physical design can be realized in reasonable amount of time. These sub-tasks may be performed in a slightly different order, iterated or omitted depending on the layout style used, the desired time, the desired chip size, and so on. The different stages of physical design cycle are shown in Figure 2.1.

Figure 2.1: Physical Design Cycle

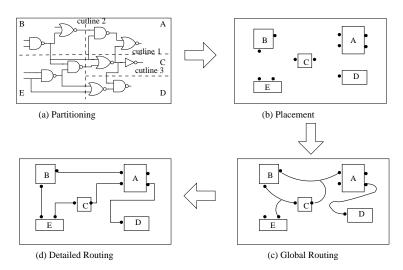

#### 2.1.1 Circuit Partitioning

A chip may contain millions of transistors. Layout of the entire circuit cannot be handled due to the limitation of memory space as well as computation power available. Therefore, it is normally partitioned by grouping the components into blocks/subcircuits. The actual partitioning process considers many factors such as, the size of the blocks, number of blocks, and number of interconnections between the blocks. The output of partitioning is a set of blocks and the interconnections required between the blocks. Figure 2.1(a) shows that the input circuit is partitioned into five blocks (i.e. a,b,c,d and e). In large circuits, the partitioning process is hierarchical and at the topmost level a chip may have 5 to 25 blocks. Each block is then partitioned recursively into smaller blocks [Sher99].

Partitioning has been an active area of research for at least a quarter of a century and many algorithmic techniques for other sub-tasks of physical design, such as placement are originated in application to partitioning. For a recent survey on the partitioning problem, see [Kuca04].

### 2.1.2 Circuit Floorplanning and Placement

Following the partitioning stage, the next step in the physical design cycle is to determine the shapes and locations of the partitioned subcircuits (i.e. blocks). The process of determining block shapes and positions with area minimization objective and aspect ratio requirement is referred to as Floorplanning. Floorplanning is a critical step, since it sets up the ground work for a good layout. However, it is computationally hard due to the unfixed shape of blocks. A common strategy for

blocks floorplanning is to determine, in the first phase, the relative location of the blocks to each other based on connection-cost criteria. In the second step, block sizing is performed with the goal of minimizing the overall chip area and the location of each block is finalized.

As a restricted version of the floorplanning problem, circuit placement attempts to assign locations to fixed shape blocks on a layout surface such that the wirelength and area are minimized. Figure 2.1(b) shows that five blocks have been placed. Note that some space between the blocks is intentionally left empty to allow interconnections between blocks. It has been shown that placement is an NP-hard problem[Chan99]. When a large number of components are involved an optimal solution can not be obtained by using the exhaustive search method in reasonable amount of time. Therefore, heuristic algorithms are often used to obtain good solutions that satisfy certain computation time.

The quality of the placement will not be evident until the routing phase has been completed. A good routing and circuit performance will heavily depend on the outcome of the placement tool. For example, traditional placement algorithms mainly focus on minimizing total estimated wirelength to obtain better routability and smaller layout area [AD85, Sun93, Klei91]. However, a placement with less total wirelength but highly congested regions often leads to routing detours around the region, in turn resulting in a larger routed wirelength [Yang01b]. Congested areas can also downgrade the performance of global routers, and in the worst case, create an unroutable placement in the fix-die regime [Cald00]. Although the congestion problem is often addressed in routing stage, the optimization performance is constrained because very little can be done to improve the routing and the overall

circuit performance if the positions of cells are fixed. Hence, considering routability in the placement stage is becoming an important objective for VLSI circuit placement.

#### 2.1.3 Global and Detailed Routing

Following the placement stage, interconnections between components are physically assigned to allowable routing regions. Due to the complexity of this problem, traditional routing is separated into two phases. The first phase is called Global Routing and generates a "rough" route for each net. In fact it assigns a list of routing regions to each net without specifying the actual geometric layout of wires, as shown in Figure 2.1(c). The second phase, refereed to as Detailed Routing, attempts to find the actual geometric layout of each net within assigned routing regions. Unlike Global Routing, which considers the entire layout, a detailed router considers just one region at a time [Sher99]. A detailed routing corresponding to the global routing is shown in Figure 2.1(d).

Physical design is iterative in nature and many steps are repeated several times to obtain a better layout. For example, an unroutable layout might need to be re-placed or re-partitioned several times such that routing can be completed successfully. Clearly, earlier steps have more influence on the overall solution quality. In this sense, partitioning and placement tend to play an important role in determining the area and chip performance, as compared to routing.

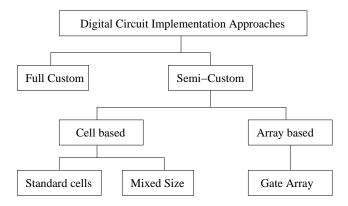

### 2.2 Layout Styles

Physical design is an extremely complex process and even after breaking the entire process into several conceptually easier steps, it has been shown that each step is computationally hard. However, market requirements demand a quick time-to-market and high yield [Raba03b]. As a result, restricted models and design styles are used in order to reduce the complexity of physical design. An overview of the different layout styles are shown in Figure 2.2. The design styles can be broadly classified as either Full-Custom or Semi-Custom. In a Full-Custom layout, the entire circuit is designed by hand. On the other hand, in Semi-Custom layout, some parts of a circuit are predesigned and placed on some specific location on the chip. The popular Semi-Custom layout styles include Standard-cells, Mixed size, and Gate Arrays.

Figure 2.2: Different Layout Styles for Digital Integrated Circuits

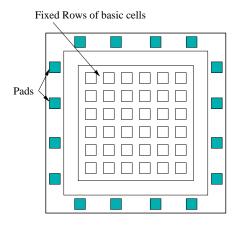

#### 2.2.1 Gate Array Layout

Gate array layout is a term given to a set of topologies, such as sea-of-gates, maskable gate array and a number of other gate array topologies. Gate array layout style are highly structured topologies, generally consisting of a grid array of prefabricated generalized logic blocks, as shown in Figure 2.3.

Figure 2.3: Gate Array Layout

All the blocks have identical size and are separated by vertical and horizontal spaces called vertical and horizontal channels. A special case of the gate array is the *Field Programmable Gate Array*, or FPGA. The feature that makes FPGA stand out among gate array topologies is that, instead of effecting a design with a photo-mask, all wires and interconnections are manufactured on the chip, and programmable fuse are fabricated into the interconnections. The desired design can be implemented by programming the interconnections between the wires and gates. The low cost of implementation and short time needed to physically realize a given design provide enormous advantages over traditional approaches which have to completed in foundries. However, FPGA is not very space-efficient, because

all the wires and interconnections are purposely generic to allow a variety of uses. Further more, the total cost increases largely for the high-density FPGA products compared to the traditional full-custom or standard-cell based design.

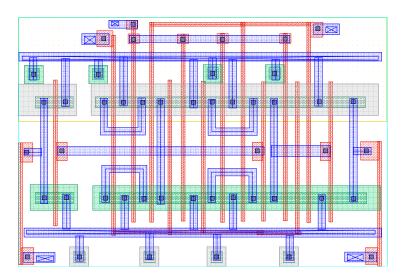

#### 2.2.2 Full-Custom Layout

When performance or area is of primary importance, handcrafting the circuit topology and physical design seems to be the only option. The chip topology for this style of design is called full-custom layout. An example of full-custom design is shown in Figure 2.4. Full-custom design has the greatest flexibility and results in

Figure 2.4: Full Custom Layout

the smallest chip area. However, it is also the most complicated, and therefore most time-consuming layout style. Because of the prohibitive design cost involved, this layout style is inappropriate for very large circuits unless performance is of utmost importance. Usually, Full-custom is used for microprocessor layouts [Sher95].

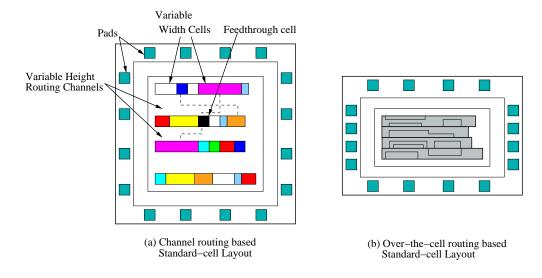

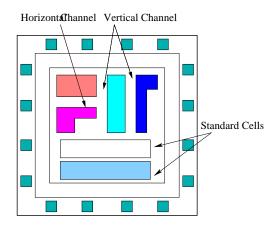

#### 2.2.3 Standard Cell Layout

Standard-cell layout style (shown in Figure 2.5) is a topology between full-custom based and gate array based layout styles. Initially, a circuit is partitioned into

Figure 2.5: Standard Cell Layout

several smaller blocks each of which is equivalent to some predefined sub-circuit (cell). The functionality and the electrical characteristics of each pre-defined cell are tested, analyzed, and specified. A collection of these cells is called a cell library. Terminals on cells may be located either on the boundary or distributed throughout the cell area. All standard cells in the library are restricted to having the same height, but their width can be chosen by the standard-cell library designer to accommodate the area of the functional block design. Once a circuit is mapped the cells are laid out in rows within the chip boundaries. In the traditional single-or two-metal-layer technology, all connections were restricted to the area between standard cell rows, called routing channel. If two cells to be interconnected lie

in the same row or in adjacent rows, then the channel between the rows is used for interconnection. However, if two cells to be connected lie in two non-adjacent rows, then their interconnection wire passes through an empty space (also called Feedthrough) as shown in Figure 2.5(a). With the advent of the N-metal-layer process (N > 3), it is possible to route all nets in the unused metal layers over the cell. In Standard-cell designs, the problem of Over-The-Cell routing refers to routing a subset of nets over the cell regions to minimize the overall layout area. The objective is to eliminate channel areas by maximizing the routing in the Over-The-Cell areas [Sher95]. An example of Over-The-Cell routing based Standard-cell layout style is illustrated in Figure 2.5(b).

#### Fixed-die versus Variable-die

Standard-cell based placement and routing can be performed in two ways: variable-die or fixed-die. For traditional 2-metal-layer process, the variable-die placement and routing is appropriate. In this methodology, the inter-row spacings (that is the space between two adjacent rows), row lengths and sometimes even the number of rows may not be fixed before the placement, but rather are determined during placement and routing. Congestion is relieved by increasing the inter-row spacings. The fixed-die methodology is becoming popular due to the presence of N-metal-layer technologies (N > 3), mixed-size layout style, fixed power and clock distribution networks, etc. It is typically applied to design blocks rather than whole chips. For such a regime, the design block geometry, area, inter-row space and available cell sites in cell rows are fixed before placement and routing. Therefore, congestion analysis and hot-spot removal becomes paramount [Cald00].

The standard-cell design style provides a compromise between good design time and production size because it uses pre-designed standard cell library. It is also well-suited for automated design because the topology has a great deal of structure. However, the variable-width aspect causes complications in automation, and the final result must be fully fabricated. Current State-of-art processors, such as the Pentium IV make full use of standard cell within their design.

# 2.2.4 Mixed Size Layout

From above discussion, it is obviously that different styles have advantages, but they suffer from some drawbacks as well. To produce a circuit with high performance, good reusability and lower cost, a combined design style, called "Mixed Size Layout" is used. Normally in the mixed layout style, a design is laid-out as blocks of other layout styles, where each block is matched to the layout style which best represents it. For example, a logic array might be laid-out as a gate-array, while a memory array most likely be laid-out by hand for speed and space efficiency, as illustrated in Figure 2.6. In Mixed layout style, the irregular sizes of general blocks introduce complexity to the placement problem. But the number of modules involved is usually much less than standard cells. Mixed layout style can be a very powerful design style, and is the style used in industry for very large and very high production chip design, such as personal computer microprocessors.

Figure 2.6: Mixed Size Layout

# 2.3 Global Routing

Following the placement stage, the exact location of cells are determined. The goal of global routing is to decide the connection pattern for each net and satisfy different objectives. The input to the global routing problem consists of a netlist that indicates the interconnections between terminals and placement information including the terminal positions and the location of wiring channels in between them. The typical objective of global routing involves wirelength and congestion minimization. In order to fit more functionality into a given chip area and reduce the capacitive delays associated with longer nets and speed up the operation of the chip, we need to optimize the chip area usage. In order to improve the routability and therefore, make the routing stage more manageable, we need to minimize the congestion areas in the global routing stage. For high performance design, the total wirelength may not be a major concern. Instead, the interconnect delay of some critical nets is minimized to maximize the chip's performance.

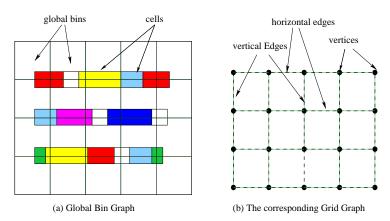

### 2.3.1 Problem Overview

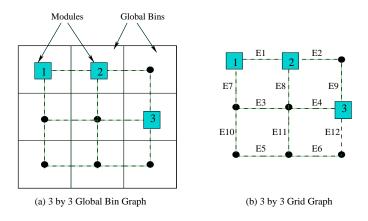

The global routing problem is typically presented as a graph problem, where the routing regions and the module connections are modeled using a grid graph [Leng90]. Initially, a given chip is partitioned into a set of rectangular regions, called global bins. The cells are placed into these bins and each cell is assumed to be placed in the center of the global bin, as shown in Figure 2.7 (a). It is easy to see that the global bins and edges can be transformed by a grid graph (Figure 2.7 (b)). The vertices of the graph represent possible positions of net terminals, and the horizontal and vertical edges (called grid edge) that lie between two adjacent vertices represent channels along or regions through which wiring can be routed. A net is an unordered set of points on the grid graph. A route (or tree) of a net is a set of grid edges used to connect all the terminals of the net. As there is finite routing resources, each grid edge has a capacity. With such a graph representation, one can solve the graph version of the global routing problem instead of the original problem.

Figure 2.7: Grid Graph for Standard-cell Layout Style

### 2.3.2 Route Construction

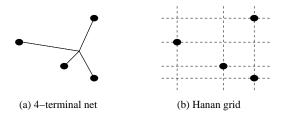

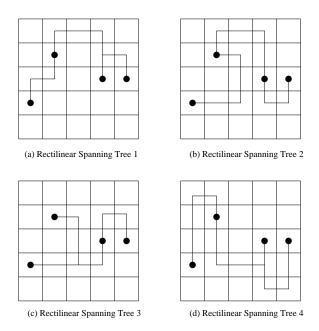

In the practical circuit, the terminals in a net are connected by the horizontal and vertical wires. These routes can be defined by Rectilinear Spanning Trees (RSTs). The number of the RSTs grows exponentially with the number of terminals in a net. Therefore, only the RSTs that have some special feature, such as minimum length or limited number of vias are considered as the acceptable routes.

In [Hana66], it is proved that any Steiner Minimum Tree can be built on a grid obtained by drawing horizontal and vertical lines that pass through the vertices of the graph. This grid is usually referred to as Hanan grid. Figure 2.8 illustrates an example of 4-terminal net and its Hanan grid. The problem of finding Rectilin-

Figure 2.8: Four-terminal net and its Hanan grid

ear Steiner Minimum Trees (RSMTs) is NP-hard [Gare77]. Most of the heuristic algorithms take the minimum RSTs as an approximation for the RSMTs due to the special relationship between these two types of trees. In the case of a Steiner tree, a route can branch at any Steiner point so that the total length of the tree is minimum, while in the case of minimum spanning tree, branching is allowed only at the terminal point locations. It has been proved by Hwang [Hwan76] that the ratio of the cost of minimum Spanning tree (MST) to that of an optimal rectilinear Steiner tree is no greater than  $\frac{3}{2}$ . A minimum spanning tree for a given net can

be found in polynomial time [Tarj83]. Therefore, to produce a RSMT, a minimum spanning tree is first built for each net. Then, a near RSMT can be obtained by linearizing each edge of the minimum spanning tree. This linearizion is done by changing each non-rectilinear edge of the minimum spanning tree to either an L shape or a Z shape tree.

# 2.3.3 Global Routing Cost Functions

Every global routing method depends on the evaluation metric employed to measure the goodness of the technique. There are two traditional primary objectives in the automated global routing problem: minimizing chip area and achieving routable designs. For the standard-cell layout style, since the total chip area is approximately equal to the area of the modules plus the area occupied by the interconnect, minimizing the wire-length is approximately equivalent to minimizing the chip area [Shah91]. Congestion minimization is another important objective of global routing. Each connection may have multiple possible paths, and by selecting an appropriate set, the routing demand in any given area can be reduced such that all the nets can be routed without exceeding the track capacity of each routing channel. As the routing layers have been increased to more than two, the number of vias or vias plays a vital role in the routability and timing of the nets. Minimizing the number of vias tends to reduce the number of metal contacts in the routing, therefore, improving the performance of the circuit.

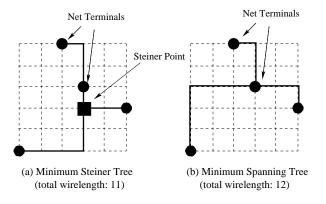

### Total Wire Length

Almost all automatic routing tools use Manhattan geometry; that is, only horizontal and vertical lines are used to connect any two points. (i.e. two layers are used such that horizontal lines are allowed in one layer and vertical lines in the other). Usually, a Rectilinear Steiner tree or spanning tree based wirelength is used in the global routing. The shortest route for connecting a set of pins together is a *Steiner Tree* [Shah91] (Figure 2.9a). For a Steiner tree, a wire can branch at any Steiner point along its length so that the total route is minimum, while for a minimal Spanning tree (Figure 2.9b) connections allow branching only at the pin locations. Hence, the pins are connected in the form of the minimal spanning tree of a graph.

Figure 2.9: Total Wire Length

The Minimum Rectilinear Steiner Tree (MRST) problem is one of the fundamental problems in VLSI computer aided design. A lot of work has been devoted to designing good exact and heuristic algorithms. The MRST problem is NP-hard [Gare77], therefore any exact algorithm is expected to have an exponential worst case running time. However, the *GeoSteiner* algorithm presented by Warme et al.

in [Warm97, Warm01] has made a spectacular progress on the exact methods for MRST problem. On the other hand, many heuristic algorithms have been developed to produce near minimum Steiner trees fast. It has been proved by Hwang [Hwan76] that the ratio of the cost of minimum Spanning tree to that of an optimal rectilinear Steiner tree is no greater than  $\frac{3}{2}$ . Based on Hwang's result, Ho et al. generate a Steiner tree by improving a minimum spanning tree topology [Ho90]. In [Kahn92], a Batched Iterated 1-Steiner heuristic by Kahng and Robins produces the best quality solution among MRST heuristics. An improved implementation is presented in [Grif94] with computation time of  $O(n^3)$ . A more efficient approach was later proposed by Borah et al. [Bora94]. The performance of their algorithm is similar to the iterated 1-Steiner algorithm [Kahn92], while the worst case running time is  $\Theta(n^2)$ . The most recently effort in this field is a new heuristic by Zhou [Zhou04], which is based on the edge-substitution approach of Borah et al. [Bora94] and Zhou et al.'s spanning graph. The experimental results show that the performance of [Zhou04] is close to that of the 1-Steiner algorithm and the worst case running time is O(nlogn).

### Total Number of Vias

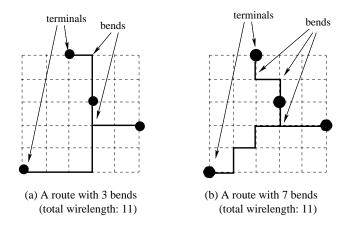

To minimize the number of vias in a layout, admissible routes in the global routing are limited to those that have lower number of vias. The total number of vias of a tree is equal to the sum of the number of vias between any two terminals, which equals to the route direction change from horizontal to vertical or vice versa. Figure 2.10(a) and (b) shows an example on how to calculate the total number of vias of a route.

Figure 2.10: Total Number of Bends

## Congestion

Congestion in a layout indicates that there are too many nets routed in a local area, which leads to routing detours around the region, in turn resulting in a larger routed wirelength. In the worst case, the detailed router may not be able to find a feasible routing solution. The congestion problem has been widely addressed in several global routing algorithms [Hads03, Agni03, Yan04, Hu02, Jing04]. One of the most important issues for interconnect management is the ability to accurately and efficiently predict the routability of a given design. There are many interconnect estimation techniques, such as *Rent's rule based methods* [Yang01b], *Probabilistic based methods* [Lou01, Chen04], and *Simple bounding box based method* [Chen94], and so on.

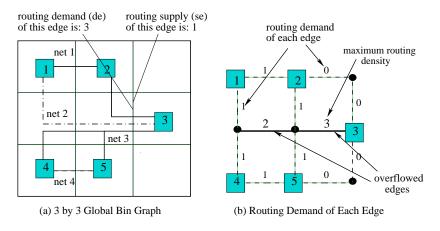

To examine the effectiveness of the congestion minimization, different measures are used to evaluate the results. The most commonly used congestion metrics are congestion map, the maximum routing density of all the grid edges, and the total overflow [Lou01, Hads03, Chen04, Gegu00, Yan04, Hu02, Jing04]. A congestion map

visually plots the congestion in the design by assigning different colors to different congestion costs. A lighter color usually means the higher congestion cost. For a given routing graph G=(V,E), the routing demand  $d_e$  of edge e, is the number of wires crossing e, the routing supply  $s_e$  is the number of wires that are allowed to cross edge e. The difference between routing demand and supply is formally described as:  $overflow_e = \begin{cases} d_e - s_e & \text{if } d_e > s_e; \\ 0 & \text{if } d_e \leq s_e. \end{cases}$  The total overflow of a layout is defined as the summation of the overflow for all global edges. The amount of total overflow reflects the amount of total shortage of routing resources in the layout. The maximum routing density  $Max_{rd}$  can be described as:  $Max_{rd} = max_{e \in E}\{d_e\}$ . Figure 2.11 shows a grid graph of a simple circuit. The circuit has 5 modules and 4 nets. If the routing supply of all the edges is set to 1, then the total overflow is 3 and the maximum routing density is 3.

Figure 2.11: Example of Congestion Measure

### Switching Power

As interconnect capacitance dominates gate capacitance in DSM technologies, minimizing power dissipation due to the interconnects becomes another important objective of routing. Switched capacitance power (a type of dynamic power) is the dominant factor of power dissipation in most CMOS digital circuits [Deng94]. It depends on the gate transition activity factor  $\alpha_{0\rightarrow 1}$ , the supply voltage  $V_{dd}^2$ , the clock frequency  $f_{clk}$  and the load capacitance  $C_{load}$  (i.e.  $P_{switch} = C_{load}\alpha_{0\rightarrow 1}f_{clk}V_{dd}^2$ ). Traditionally, the load capacitance consists of two components: the gate capacitance  $C_{gate}$  and the wire (i.e. interconnect) capacitance  $C_{wire}$ . However, as the geometrics continuously scaling down, the coupling capacitance which occurs between adjacent wires on the same metal routing layer make up an ever growing amount of the total capacitance [Zube05]. Since the produce of switching frequency and square of the supply voltage of the gate is invariant after logic synthesis, we can use a constant  $C_i$  to represent it as  $C_i = \alpha_{0\rightarrow 1}f_{clk}V_{dd}^2$ . Accordingly, the switched capacitance power of net k can be expressed as [Zube05]:

$$P_{net_k} = \sum_{i} C_i l_i (\frac{1}{d_{li}} + \frac{1}{d_{ri}})$$

(2.1)

where  $l_i$  is the length of the *ith* wire segment of net k, and  $d_{li}$  and  $d_{ri}$  are the left and right distances to the next metal objects, respectively.

# 2.4 Multi-objective based Optimization

With the continuous and rapid increase in complexity of VLSI designs and fabrication technologies, global routing problem becomes more difficult to solve. Different and conflicting design objectives need to be considered in the global routing stage. Thus, modeling the global routing problem with several conflicting objectives, as well as maintaining the simplicity and efficiency of the models becomes an important issue for today's complex and large VLSI circuit design.

## 2.4.1 General multi-objective Optimization Problem

Multi-objective optimization problem can be defined as the problem of finding a vector of decision variable which satisfies constraints and optimizes a vector function whose elements represent the objective functions. The term "optimize" means finding such a solution which would give the values of all the objective functions acceptable to the designer [Osyc85]. A general multi-objective optimization problem can be expressed as follows [Ande99]:

Minimize

$$F(X) = (f_1(X), f_2(X), \dots, f_k(X))^T$$

$s.t. \ X \in S$

$X = (x_1, x_2, \dots, x_n)^T$  (2.2)

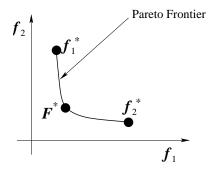

where  $f_1(X), f_2(X),...,f_k(X)$  are the k objective functions,  $(x_1, x_2,...,x_n)$  are the n optimization parameters, and S is the solution space. Figure 2.12 provides a visualization of the two-objective optimization problem.  $f_1^*, f_2^*$  represent the minima of the respective objective function. The ideal solution for these two-objective prob-

lem is defined as  $F^* = (f_1^*, f_2^*)^T$ . Usually, the vector  $X^*$  is called Pareto optimal (or efficient point) if there exists no feasible vector X that scores at least as well in all objective functions and strictly better in one. The Pareto optimum almost always gives a set of solutions, known as the Pareto optimal frontier P [Coel00] (as shown in Figure 2.12). The Pareto optimal frontier forms the boundary of the region defined by objective values for feasible solutions. When the behavior of the

Figure 2.12: Optimization Problem with Two Objectives

different objective functions is more or less known and the preference information can be obtained prior to the optimization, the most common way of conducting multi-objective optimization is by aggregating the different objectives into one single figure of merit. The popular aggregating approaches include: Weighted Sum Approach, Lexicographic Optimization and Goal Programming. A weighted sum approach consists of adding all the objective functions using different weighting coefficients for each one. The typical formulation of this method is as follows:

$$\operatorname{Min} \sum_{i=1}^{K} \beta_{i} f_{i}(x) c_{i}

s.t \quad X \in S

\sum_{i}^{k} \beta_{i} = 1$$

(2.3)

where  $\beta_i$  are the weighting coefficients representing the relative importance of the objectives. As the objective functions are generally of different magnitudes, so  $c_i$  is used as a constant multipliers that will scale the objectives properly. This method can be applied to generate strongly Pareto optimal solution. But it is difficult to decide the appropriate weights because there is no clear relation between the weights and the obtained multi-objective solution [Ande99]. As an alternative scheme, lexicographic method performs multi-objective optimization by considering objectives one at a time. The designer ranks the objectives in order of importance. The most important objective is first optimized, then the second most important is optimized subject to a requirement that the first objective achieve its optimal value, and so on. Lexicographic approaches place very great emphasis on the highest-priority objective, with all later steps of other objectives optimization limited to alternative optima of the highest-priority objective. In some cases, when alternative optima of the highest-priority objective are rare, this method is actually optimizing the priority objective while ignoring all the others [Rard98]. In stead of minimizing or maximizing the objective functions, goal programming approaches solve the multiobjective optimization problem by minimizing the deviations from the targets or goals to the objectives. In the beginning, designers have to specify the goals that they wish to achieve for each objective. These values are then incorporated into the problem as additional constraints. Finally, the objective function attempts to find a solution that has the smallest deviation from the Utopian solution. It may be a very efficient approach if the desired goals are known. However, it still involves finding appropriate weights or priorities for the objectives [Coel00].

# 2.5 Test Circuits

Table 2.1 shows the general information of benchmarks used to measure the performance of the global routing algorithms in this research. The circuits used are the MCNC'91 benchmarks [MCNC91]. This test set consists of seven circuits ranging in size from 125 cells to over 25,000 cells The circuits have been grouped into three categories according to size: small, medium and large, indicated by horizontal lines in Table 2.1. Column "Short Nets" lists the number of 2-terminal and 3-terminal nets, while column "Long Nets" lists the number of remaining nets. The column "H/V Cap" lists the horizontal and vertical edge capacity and the last column shows the total number of columns and rows of the grid graph. To further illustrate the performance of the proposed ILP based global routing algorithms, the ISPD98/IBM benchmarks [ISPD98] and ISPD2007 benchmarks [ISPD07] are also used. The statistic information of ISPD98/IBM benchmarks and ISPD2007 benchmarks is listed in table 2.2. It is important to notice that 2-terminal and 3-terminal nets constitute the majority of the nets in all the test benchmarks.

# 2.5.1 Software Packages Used

The proposed techniques are implemented in 'C++' programming language on a 900MHz Sun Blade 2000 workstation with 1GB memory. Originally, GeoSteiner3.1 package [Warm01] is used to construct the steiner minimal trees. A much faster and accurate rectilinear steiner minimal tree algorithm [Chu04] is adopted later. The comparison of these two packages is shown in Appendix B. In addition, a commercial solver iLog Cplex10.0 is used to solve the Linear Programming and

| T /      | т ·    | D .         | 1 1       |

|----------|--------|-------------|-----------|

| Integer  | Linear | Programming | problems  |

| 11100501 | Lincar | Programming | problems. |

|          |        |             |           |

| Bench     | Tot   | Tot   | Short | % Short | Long | % Long | H/V   | Grid  |

|-----------|-------|-------|-------|---------|------|--------|-------|-------|

| $\max$ ks | Cells | Nets  | Nets  | Nets    | Nets | Nets   | Cap   | size  |

| Fract     | 125   | 147   | 114   | 77.55%  | 33   | 22.45% | 4/4   | 8x8   |

| Prim1     | 752   | 876   | 698   | 79.68%  | 178  | 20.32% | 6/6   | 19x19 |

| Struct    | 1888  | 1920  | 1888  | 98.33%  | 32   | 1.67%  | 5/5   | 21x21 |

| Ind1      | 2271  | 2478  | 2002  | 80.79%  | 476  | 19.21% | 10/10 | 15x15 |

| Prim2     | 3014  | 3136  | 2307  | 73.57%  | 829  | 26.43% | 10/10 | 26x26 |

| Ind2      | 12142 | 13419 | 11436 | 85.22%  | 1983 | 14.78% | 11/11 | 72x72 |

| avq.large | 25114 | 25384 | 23050 | 90.81%  | 2334 | 9.19%  | 9/9   | 86x86 |

Table 2.1: MCNC Tested Circuit Statistics

| Bench  | Tot    | Routed | Short  | %Short | Long  | %Long | H/V   | Grid    | Chip      |

|--------|--------|--------|--------|--------|-------|-------|-------|---------|-----------|

| Marks  | Net    | Nets   | Nets   | Nets   | Nets  | Nets  | Cap   | Size    | Size(um)  |

| ibm01  | 11507  | 9128   | 6299   | 69%    | 2829  | 31%   | 14/12 | 64x64   | 655x655   |

| ibm02  | 19291  | 14270  | 8708   | 61%    | 5562  | 39%   | 34/22 | 64x80   | 754x750   |

| ibm03  | 21621  | 15289  | 11316  | 74%    | 3973  | 26%   | 30/20 | 64x80   | -         |

| ibm04  | 26163  | 19738  | 14337  | 72%    | 5401  | 28%   | 23/20 | 64x96   | -         |

| ibm05  | 27777  | 21135  | 12351  | 58%    | 8784  | 42%   | 63/42 | 64x128  | -         |

| ibm06  | 33354  | 25797  | 18129  | 70%    | 7668  | 30%   | 33/20 | 64x128  | -         |

| ibm07  | 44394  | 34378  | 24104  | 70%    | 10274 | 30%   | 36/21 | 64x192  | 1142x1139 |

| ibm08  | 47944  | 35195  | 24548  | 70%    | 10611 | 30%   | 32/21 | 64x192  | 1224x1224 |

| ibm09  | 50393  | 39592  | 27957  | 71%    | 11635 | 29%   | 28/14 | 64x256  | 1231x1209 |

| ibm10  | 64227  | 49491  | 30663  | 62%    | 18828 | 38%   | 40/27 | 64x256  | 1579x1577 |

| ispd01 | 219794 | 176715 | 122973 | 70%    | 53742 | 30%   | 70/70 | 324x324 | 500x500   |

| ispd02 | 260159 | 207972 | 160466 | 77%    | 47506 | 23%   | 80/80 | 424x424 | 500x500   |

| ispd03 | 466295 | 323887 | 249037 | 77%    | 74850 | 23%   | 92/92 | 474x479 | 498x502   |

| ispd04 | 515304 | 357104 | 287215 | 80%    | 69889 | 20%   | 92/92 | 474x479 | 498x502   |

Table 2.2: ISPD98 IBM Benchmark & ISPD2007 Benchmark Statistics

# 2.6 Summary

The VLSI design process is broken down into several smaller and tractable sub-tasks to manage the high complexity of the task. One of these sub-tasks is physical design,

which is still incredibly complex. As a result, this complexity is handled by dividing the physical design task into more tractable sub-tasks and circuit placement is one of such sub-tasks. Physical design automation highly depends on the layout style used. Different layout styles, such as full-custom, gate-array, and standard-cell layouts can achieve different trade offs among speed, cost, fabrication time, and degree of design automation.

The layout topology used to demonstrate the research work in this proposal is the standard-cell layout style. The most commonly used metric that measures the quality of a global routing solution is the total wirelength for all the nets, the total number of vias (i.e. bends), the maximum routing density of all the grid edges, and the total overflow. In addition, the multi-objective optimization problem and several aggregating approaches are also introduced in this chapter.

In the following chapter, different global routing techniques are reviewed and their advantages and drawbacks are also analyzed.

# Chapter 3

# Literature Review

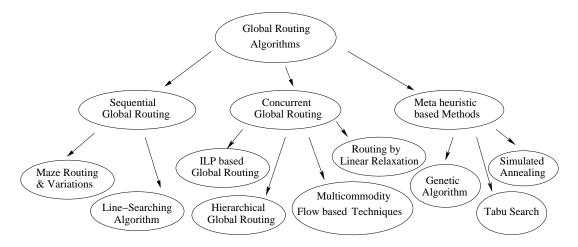

Since all versions of the global routing problem are NP-hard [Sher99], a variety of heuristic algorithms have been developed for it, as shown in Figure 3.1. Basically, these algorithms can be classified into three classes: Sequential global routing, Concurrent global routing and Meta heuristic based methods.

Figure 3.1: Different Approaches for Global Routing Problem

# 3.1 Sequential Global Routing

The most common approach to global routing is sequential routing. In such an approach, nets are first ordered according to their importance, then based on the ordering nets are routed sequentially. Sequential Routing can be grouped into two types: *Maze routing algorithms (with variations)* and *Line-Probe Algorithms*.

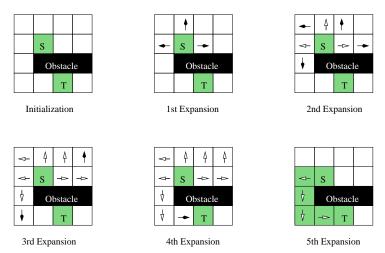

In 1961, a maze routing algorithm for finding a shortest path between two points on a grid graph was first introduced by Lee [Lee61]. The searching in Lee's algorithm is conducted by using the breath-first search technique (BFS). In order to find the shortest path between a source point "S" and a target "T", the maze global router first constructs several initial paths at "s" and then expands them until one path reaches "T" (as seen in Figure 3.2). The reason of the popularity of Lee's maze

Figure 3.2: Maze Routing Algorithm

router is its simplicity and its guarantee of finding an optimal solution if one exists. However, the spacing and computation time requirements of Lee's maze router is also large. For an  $N \times N$  grid plane, the time and space complexity is  $O(N^2)$  [Sait95]. To reduce the problem of storage, a coding scheme for labeling of grid cells have been proposed in [Aker67]. Several authors discuss goal-directed search techniques in [Souk78] and [Hadl75] to speed up maze routing algorithms. The major drawback of Lee's maze routing algorithm and many of their variations is that the information data must be kept for each vertex. Thus, a very large memory space is needed for solving a large grid graph. To further reduce the space requirement, line-probe algorithms have been introduced by Hightower [High69] and Mikami [Mika68]. In line-probe algorithms, the routing is performed by a bidirectional searching. Straight search lines are extended from both source point "S" and target point "T" in all four directions, as shown in Figure 3.3. If a search line extended from source meets a line extended from target, then a path is constructed. When these trial lines hit some obstacles, new directions are extended for some base points on the trial lines. The time and space complexities of these algorithms is O(L),

Figure 3.3: Line Probe Routing Algorithm

where L is the number of segments produced by these algorithms. Clearly, Line-

Searching algorithms are faster than maze routing algorithms and require much less memory. However, they do not guarantee finding the shortest path between two points.

The maze routing and line-probe algorithms are not designed to route multiterminal nets. In [Sche86], the multi-terminal nets are decomposed into several two-terminal nets and the resulting two-terminal nets are routed by a maze routing or line-probe algorithms. For any sequential approach, once a net has been routed it may block other nets which are yet to be routed. As a result, these approaches highly depend on the order in which the nets are processed. However, it is hard to decide which net ordering is better than others [Abel72]. In practice, a technique called "rip-up and reroute" is often used after the sequential routing to remove blockages when further routing of nets is not possible [Aosh83, Ting83, Nair87, Lee 91]. In [Hads 03], an amplified congestion estimate is used to influence a rip-up and reroute approach. During each rip-up and reroute iteration, the congestion information is obtained by a feed-back loop to guide the maze router to avoid the congested areas in the subsequent reroute process. The congestion estimation consists of two parts: the static congestion given by a probabilistic algorithm and the dynamic congestion obtained from the previous iterations of rip-up and reroute process. The congestion estimation is amplified in the early rip-up iterations to strongly influence the routes in the congested areas and scaled down in the later iterations to decrease the impact on the total wirelength. Compared to the global routing work of [Kast01], the proposed approach produces shorter wirelength and lower overflow with less computation time.

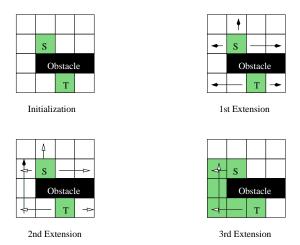

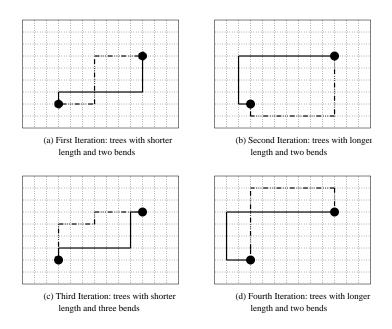

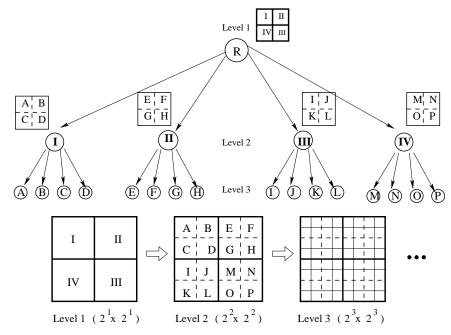

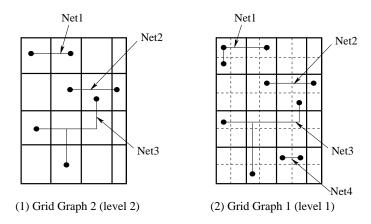

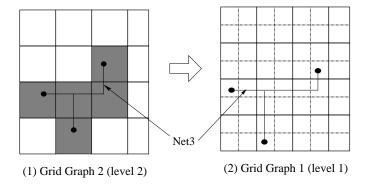

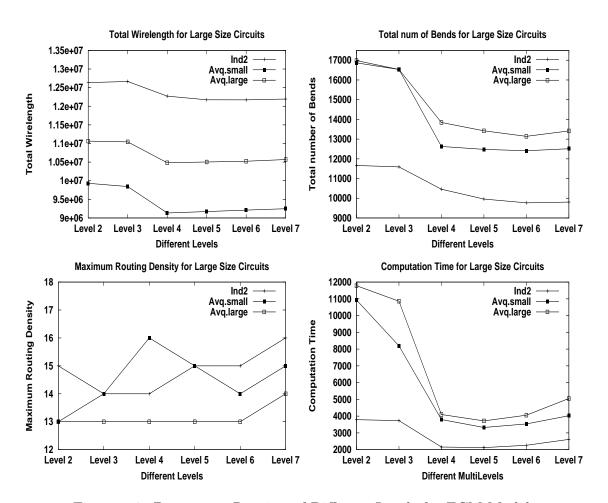

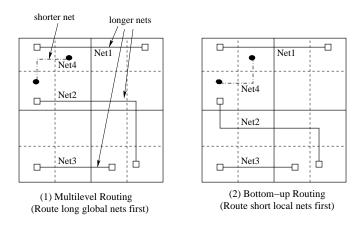

A minimum-length Steiner tree is not appropriate when it traverses through