# Analysis and Design of Robust Multi-Gb/s Clock and Data Recovery Circuits

by

David J. Rennie

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2007

©David J. Rennie 2007

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

David J. Rennie

#### Abstract

The bandwidth demands of modern computing systems have been continually increasing and the recent focus on parallel processing will only increase the demands placed on data communication circuits. As data rates enter the multi-Gb/s range, serial data communication architectures become attractive as compared to parallel architectures. Serial architectures have long been used in fibre optic systems for long-haul applications, however, in the past decade there has been a trend towards multi-Gb/s backplane interconnects. The integration of clock and data recovery circuits into monolithic integrated circuits is attractive as it improves performance and reduces the system cost, however it also introduces new challenges, one of which is robustness.

In serial data communication systems the CDR circuit is responsible for recovering the data from an incoming data stream. In recent years there has been a great deal of research into integrating CDR circuits into monolithic integrated circuits. Most research has focused on increasing the bandwidth of the circuits, however in order to integrate multi-Gb/s CDR circuits robustness, as well as performance, must be considered.

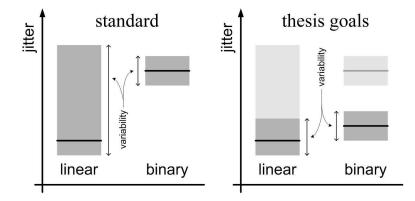

In this thesis CDR circuits are analyzed with respect to their robustness. The phase detector is a critical block in a CDR circuit and its robustness will play a significant role in determining the overall performance in the presence of process non-idealities. Several phase detector architectures are analyzed to determine the effects of process non-idealities. Static phase offsets are introduced as a figure of merit for phase detectors and a mathematical framework is described to characterize the negative effects of static phase offsets on CDR circuits. Two approaches are taken to improve the robustness of CDR circuits. First, calibration circuits are introduced which correct for static phase offsets in CDR circuits. Secondly, phase detector circuits are introduced which have been designed to optimize both performance and robustness. Several prototype chips which implement these schemes will be described and measured results will be presented. These results show that while CDR circuits are vulnerable to the effects of process non-idealities, there are circuit techniques which can mitigate many of these concerns.

### Acknowledgements

A PhD is in many way a solitary endeavor, however it is never completed alone. I am indebted to a great many people, and I thank all those who have helped me complete this journey.

I thank my supervisor Manoj Sachdev for many years of patience, advice and encouragement. This thesis would not have been possible without his guidance and support, and I am deeply grateful.

I have been blessed with many friends who have made the long road a little shorter, providing both much needed help and much needed distractions at just the right times. I can never repay them for all they have contributed to my life, but I can, and do, say a heartfelt thank you.

I have also been greatly blessed with a wonderful family, and I thank them. They have given me unconditional love and unfailing support, put up with my erratic schedule, and only rarely asked when I was going to be finished!

Finally, I give thanks to God, who set my feet upon this path, and was faithful in leading me through; to Him be the glory.

The race is not to the swift or the battle to the strong, nor does food come to the wise or wealth to the brilliant or favor to the learned; but time and chance happen to them all. Ecclesiastes 9:11

# Contents

| 1 | Intr | roduction                                | 1        |

|---|------|------------------------------------------|----------|

|   | 1.1  | CMOS Integration of CDR Circuits         | 2        |

|   | 1.2  | Motivation                               | 3        |

|   | 1.3  | Thesis Overview                          | 4        |

| 2 | Clo  | ock and Data Recovery                    | <b>5</b> |

|   | 2.1  | Serial Digital Data Communication        | 5        |

|   |      | 2.1.1 Data Modulation                    | 6        |

|   |      | 2.1.2 Data Encoding                      | 8        |

|   | 2.2  | Wireline Data Communication              | 9        |

|   |      | 2.2.1 Optical Data Communication Systems | 9        |

|   |      | 2.2.2 Copper Data Communication Systems  | 11       |

|   | 2.3  | CDR Circuit Architecture                 | 14       |

|   |      | 2.3.1 Phase Detector                     | 15       |

|   |      | 2.3.2 Charge Pump                        | 23       |

|   |      | 2.3.3 Loop Filter                        | 26       |

|   |      | 2.3.4 Voltage Controlled Oscillator      | 26       |

|   | 2.4  | CML in Multi-Gb/s CDR Circuits           | 30       |

|   |      | 2.4.1 Architecture                       | 31       |

|   |     | 2.4.2   | CDR Circuits Using CML                        | 33 |

|---|-----|---------|-----------------------------------------------|----|

|   | 2.5 | Figure  | es of Merit                                   | 34 |

|   |     | 2.5.1   | CDR System Analysis                           | 34 |

|   |     | 2.5.2   | Jitter                                        | 39 |

|   |     | 2.5.3   | Frequency Domain FOM                          | 43 |

|   |     | 2.5.4   | Time-Domain FOM                               | 54 |

|   | 2.6 | Model   | ling Binary Phase Detector Based CDR Circuits | 56 |

|   |     | 2.6.1   | Basic Binary Control: Example                 | 57 |

|   |     | 2.6.2   | Basic Binary Control: Analysis                | 58 |

|   |     | 2.6.3   | Second Order CDR Systems                      | 63 |

|   | 2.7 | Summ    | nary                                          | 73 |

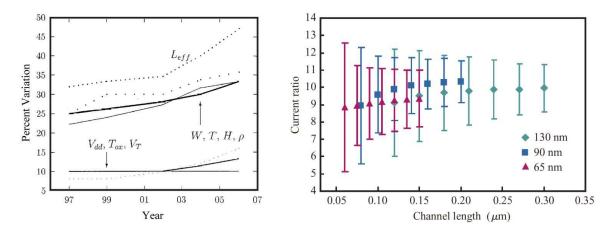

| 3 | Rob | oustnes | ss Considerations in CDR Circuits             | 74 |

|   | 3.1 |         | tness                                         | 74 |

|   |     | 3.1.1   | Definition of Robustness                      | 76 |

|   |     | 3.1.2   | Robustness in This Thesis                     | 76 |

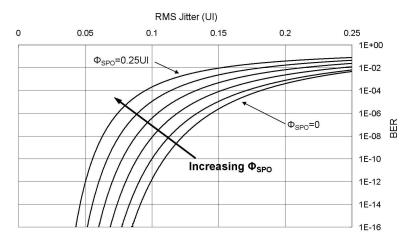

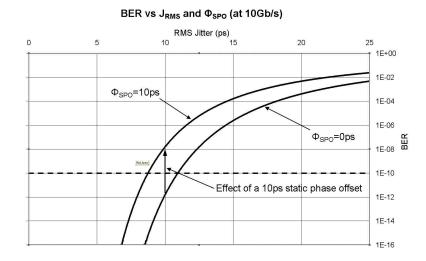

|   | 3.2 | Mathe   | ematical Analysis of Static Phase Offset      | 79 |

|   |     | 3.2.1   | Static Phase Offsets in a Phase Detector      | 79 |

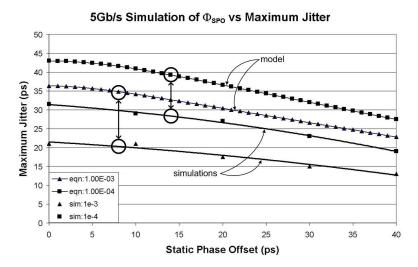

|   |     | 3.2.2   | Simulation Results                            | 85 |

|   | 3.3 | DFF A   | Analysis                                      | 86 |

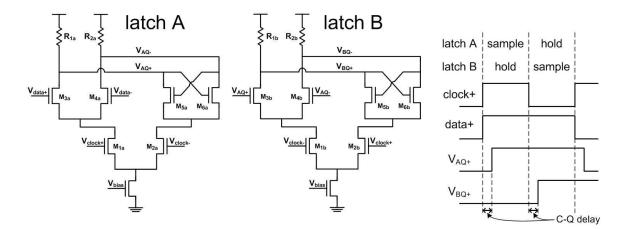

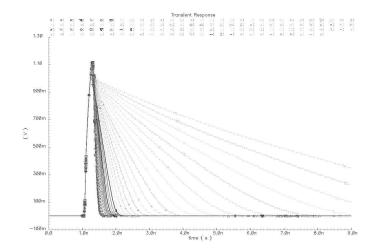

|   |     | 3.3.1   | Metastability in a DFF                        | 87 |

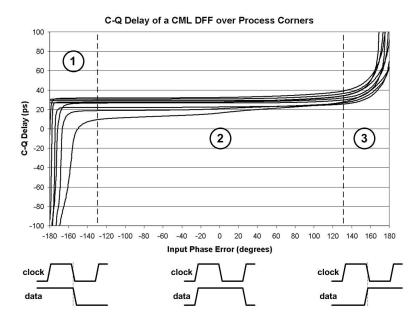

|   |     | 3.3.2   | Hogge Phase Detector Gain                     | 89 |

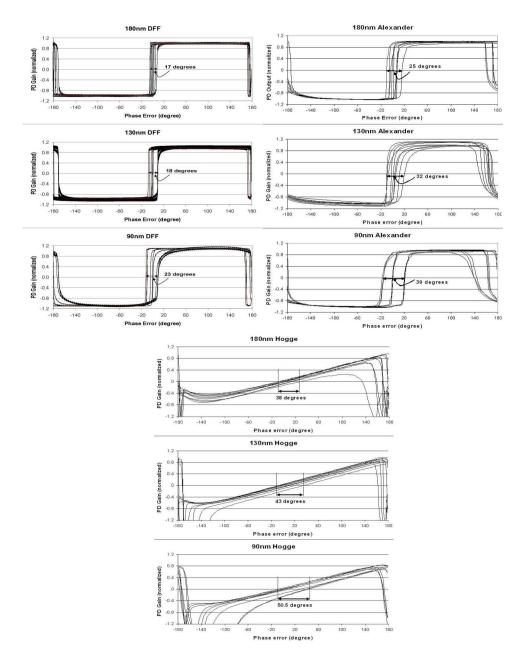

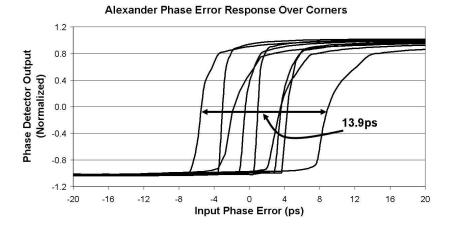

|   |     | 3.3.3   | Alexander Phase Detector Gain                 | 90 |

|   |     | 3.3.4   | DFF Phase Detector Gain                       | 92 |

|   | 3.4 | Effect  | of Non-Idealities on Phase Detectors          | 93 |

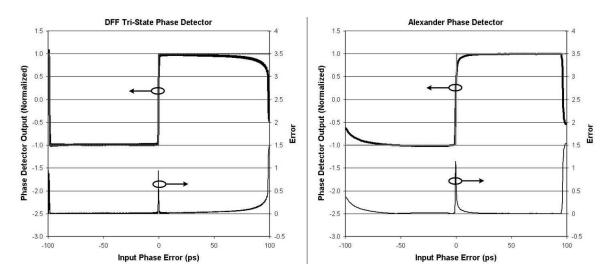

|   |     | 3.4.1   | Analysis Setup                                | 93 |

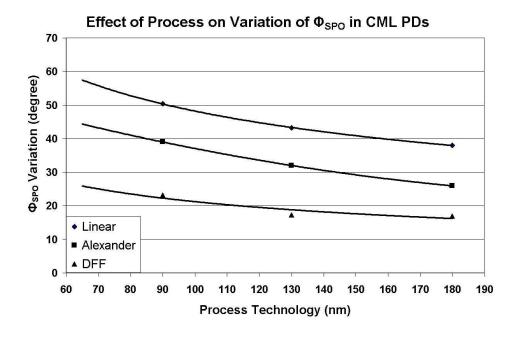

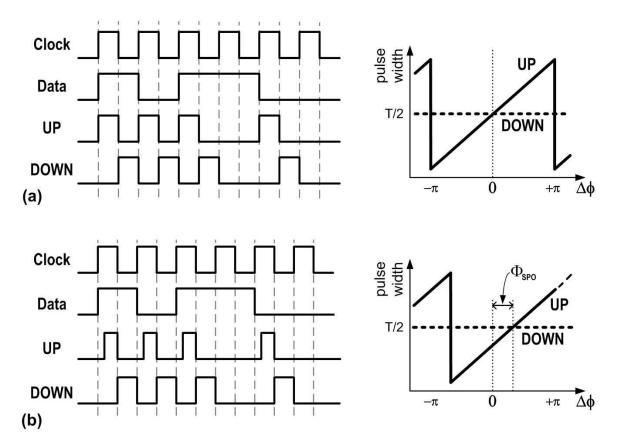

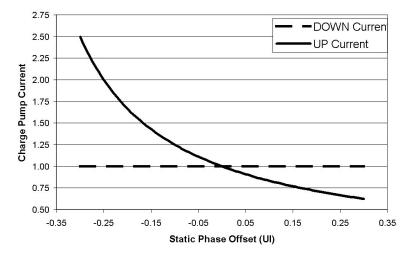

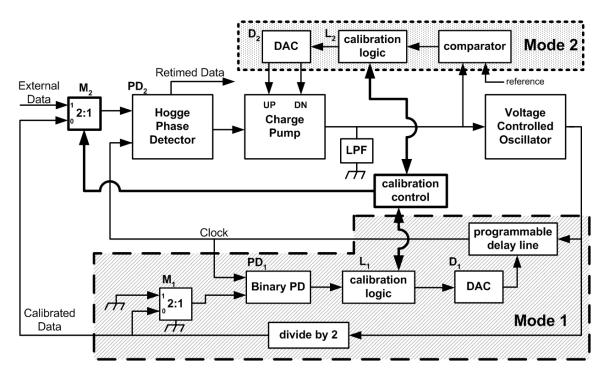

|   |     | 3.4.2   | Analysis Results                              | 95 |

|   | 3.5  | Summ    | ary                                                  | 98  |

|---|------|---------|------------------------------------------------------|-----|

| 4 | Cali | ibratio | on Techniques for Robust CDR Circuits                | 100 |

|   | 4.1  | Calibr  | ation in CDR Circuits                                | 101 |

|   |      | 4.1.1   | Correction of Static Phase Offsets Using Calibration | 101 |

|   |      | 4.1.2   | Linear Phase Detectors in CDR Circuits               | 105 |

|   | 4.2  | Offline | e Calibration Architecture                           | 106 |

|   |      | 4.2.1   | Calibration Algorithm                                | 106 |

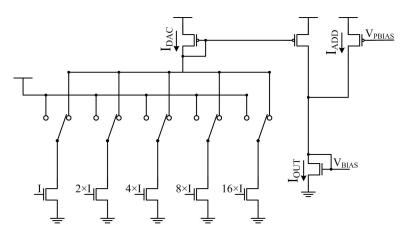

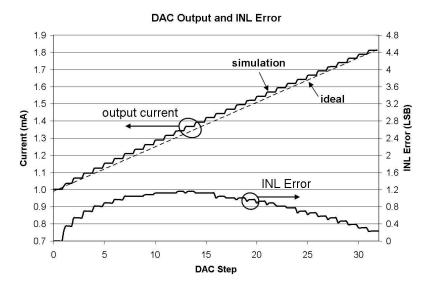

|   |      | 4.2.2   | Implementation                                       | 109 |

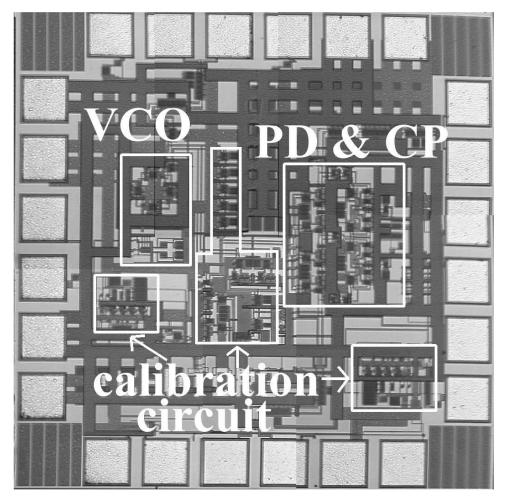

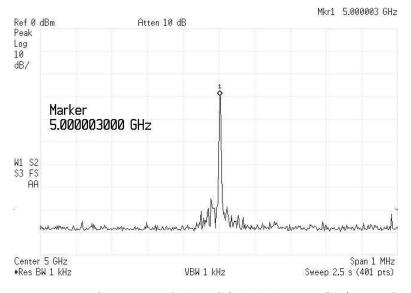

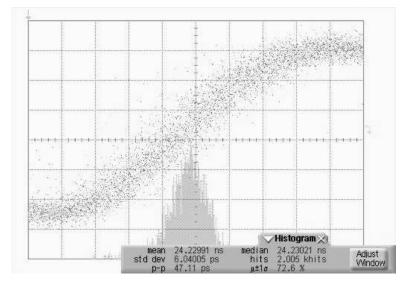

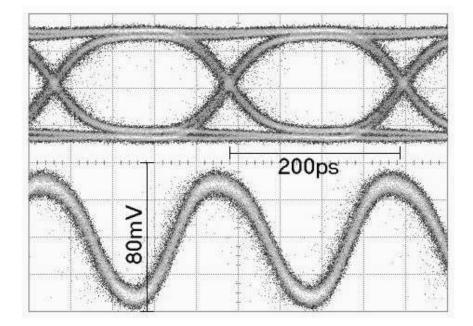

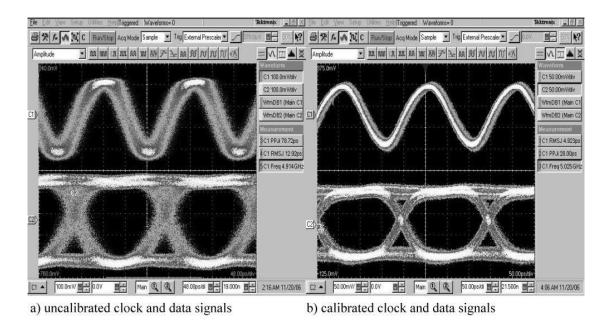

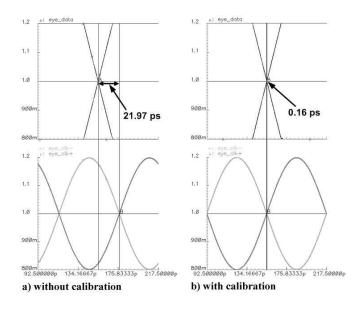

|   |      | 4.2.3   | Measured Results                                     | 115 |

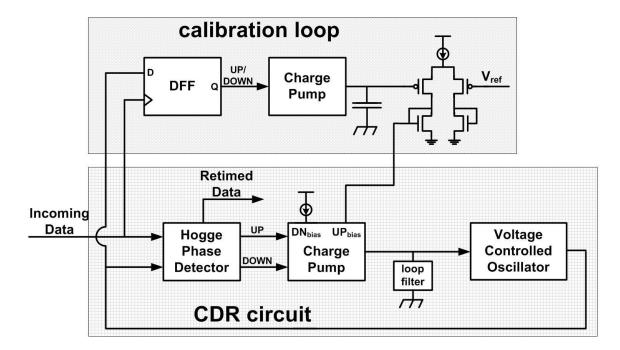

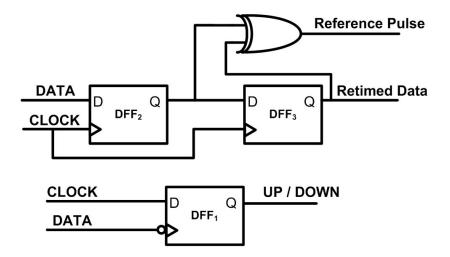

|   | 4.3  | Online  | e Analog Calibration Architecture                    | 120 |

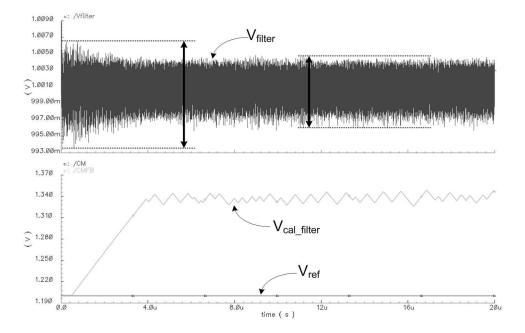

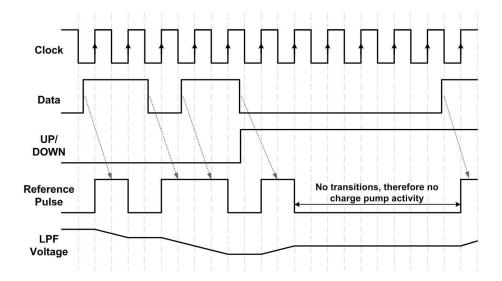

|   |      | 4.3.1   | Calibration Architecture                             | 120 |

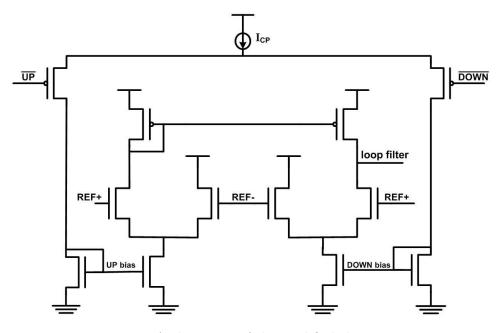

|   |      | 4.3.2   | Implementation                                       | 123 |

|   |      | 4.3.3   | Measured Results                                     | 126 |

|   | 4.4  | Summ    | ary                                                  | 128 |

| 5 | Pha  | ise Det | tector Design for Robust CDR Circuits                | 129 |

|   | 5.1  | Tri-Sta | ate DFF Phase Detector                               | 130 |

|   |      | 5.1.1   | Architecture of Tri-State DFF Phase Detector         | 130 |

|   |      | 5.1.2   | Robustness of the Tri-State DFF Phase Detector       | 132 |

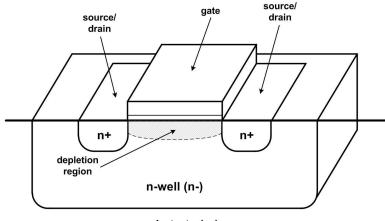

|   |      | 5.1.3   | Implementation                                       | 134 |

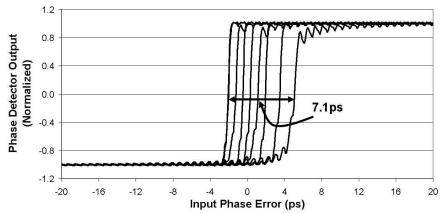

|   |      | 5.1.4   | Measured Results                                     | 137 |

|   | 5.2  | Pulsed  | l DFF Binary Phase Detector                          | 140 |

|   |      | 5.2.1   | Monolithic Second Order Loop Issues                  | 140 |

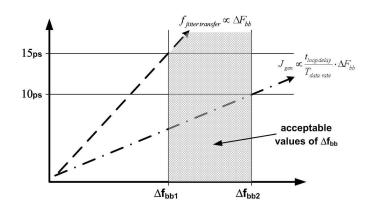

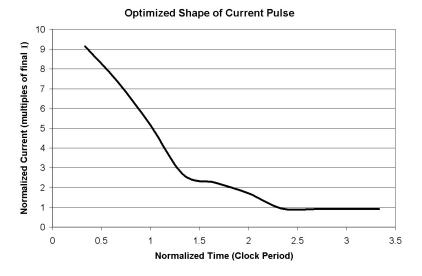

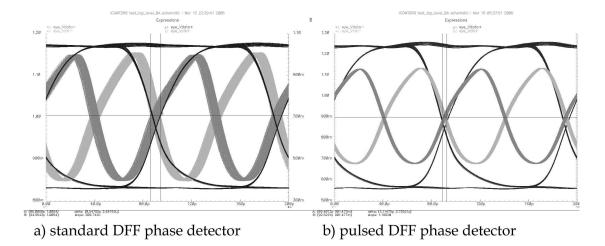

|   |      | 5.2.2   | Proportional Path Optimization                       | 141 |

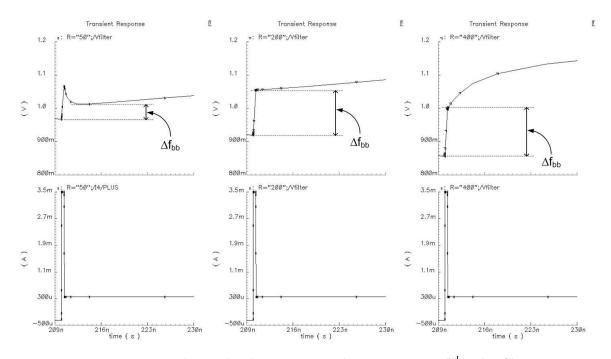

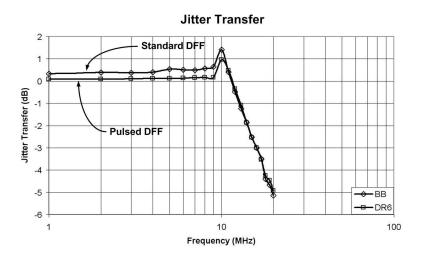

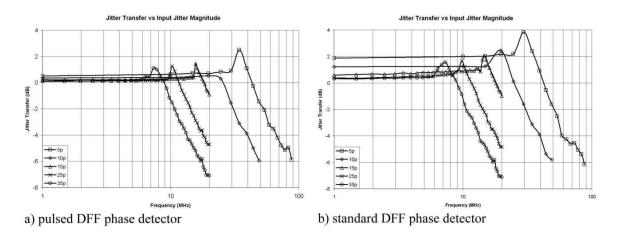

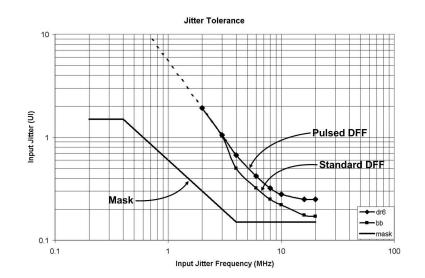

|   |      | 5.2.3   | Simulation Results                                   | 145 |

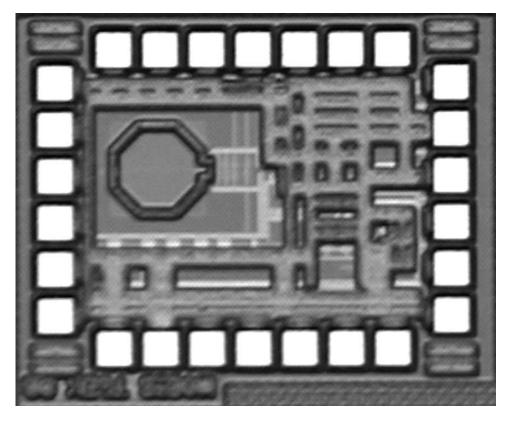

|   |      | 5.2.4   | Implementation                                       | 148 |

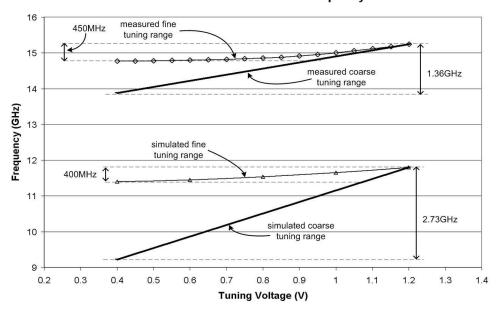

|   |     | 5.2.5   | Measured Results                       | . 153 |

|---|-----|---------|----------------------------------------|-------|

|   | 5.3 | Bandy   | width Enhanced Linear Phase Detector   | . 158 |

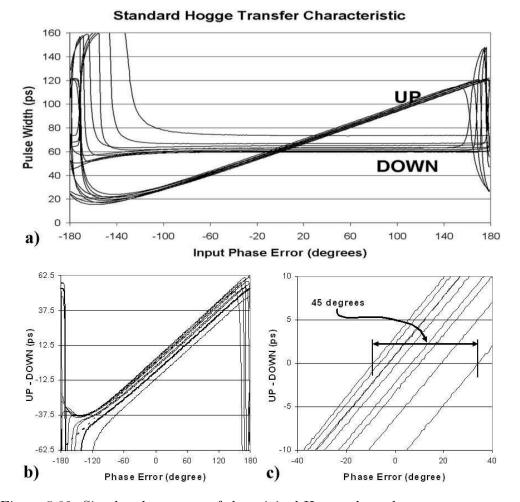

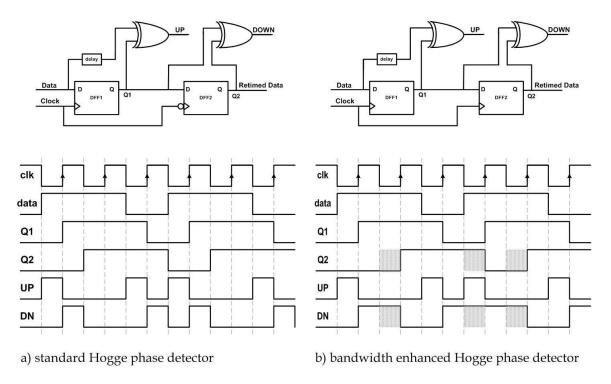

|   |     | 5.3.1   | Robustness in the Hogge Phase Detector | . 158 |

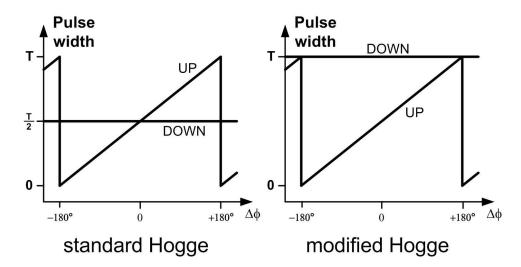

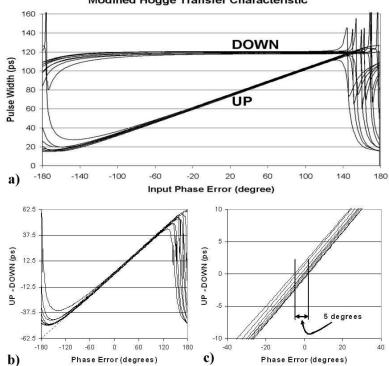

|   |     | 5.3.2   | Modified Hogge Phase Detector          | . 160 |

|   |     | 5.3.3   | Charge Pump Currents                   | . 162 |

|   | 5.4 | Summ    | nary                                   | . 164 |

| ~ | G   |         |                                        |       |

| 6 | Con | nclusio | ns                                     | 165   |

|   | 6.1 | Major   | Contributions                          | . 166 |

|   | 6.2 | Future  | e Work                                 | . 168 |

## List of Tables

| 2.1 | Data rates for SONET/SDH                                           | 11  |

|-----|--------------------------------------------------------------------|-----|

| 3.1 | Simulation data for process normalization                          | 93  |

| 4.1 | Measured calibrated and uncalibrated BER for various data patterns | 118 |

# List of Figures

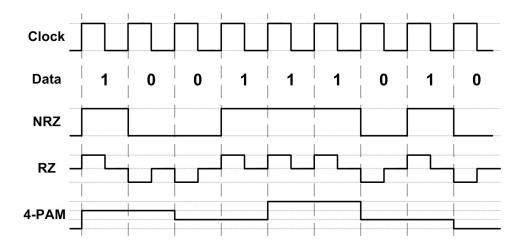

| 2.1  | Example of several line codes which could be used for data communication $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

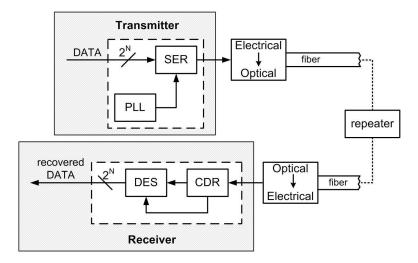

| 2.2  | Architecture of an optical data communication system $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9  |

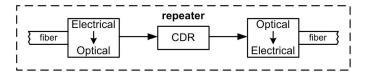

| 2.3  | Architecture of a repeater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10 |

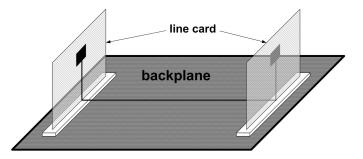

| 2.4  | Data communication over a backplane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12 |

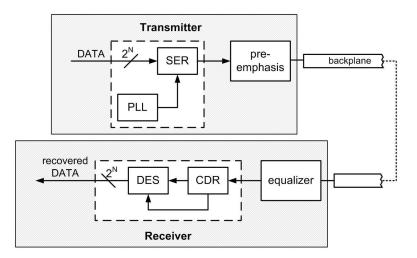

| 2.5  | Architecture of a backplane data communication system $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 |

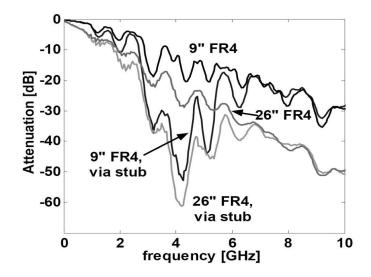

| 2.6  | Frequency attenuation over an FR4 backplane $[1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13 |

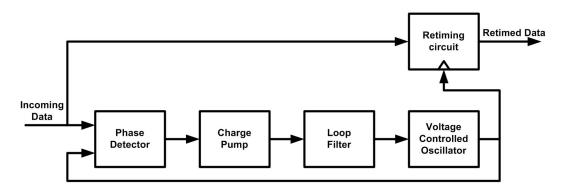

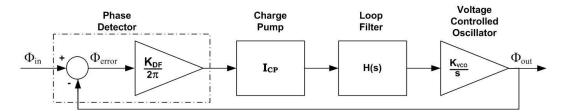

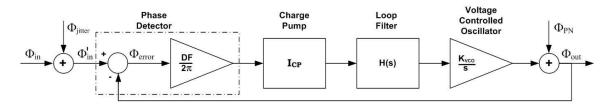

| 2.7  | Architecture of a PLL based CDR circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14 |

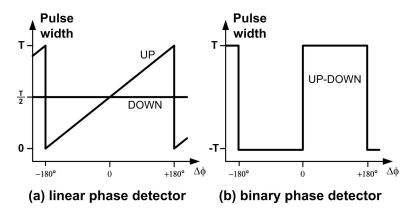

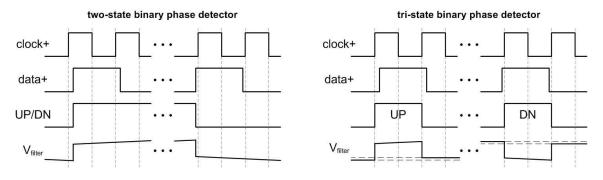

| 2.8  | Gain of a binary and linear phase detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 |

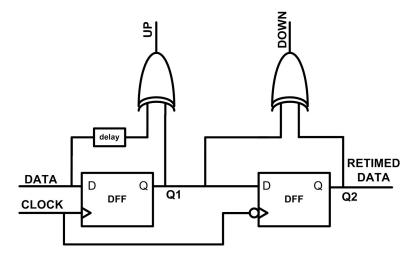

| 2.9  | Architecture of the Hogge phase detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16 |

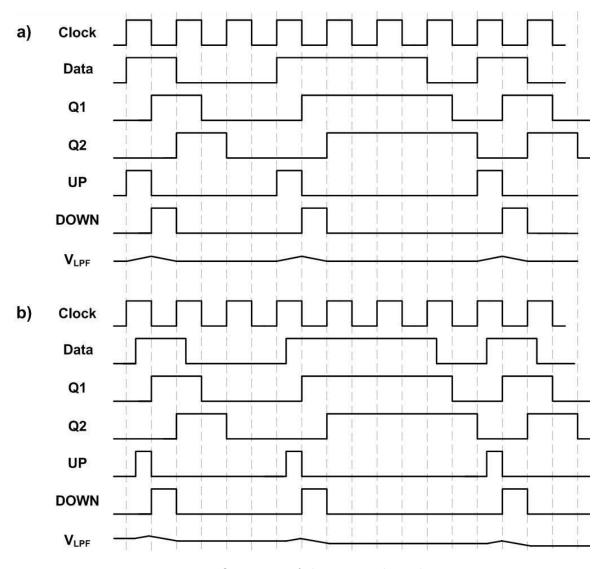

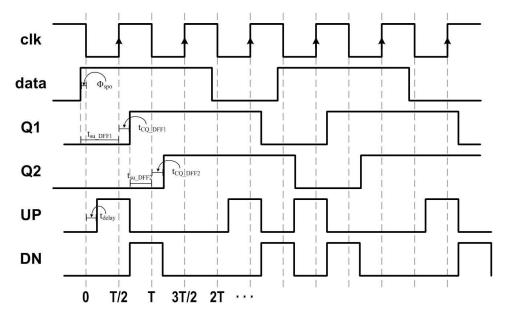

| 2.10 | Operation of the Hogge phase detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17 |

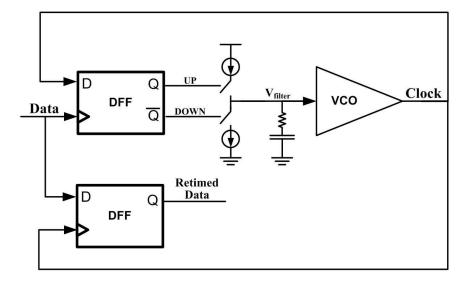

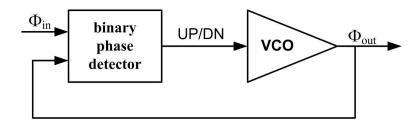

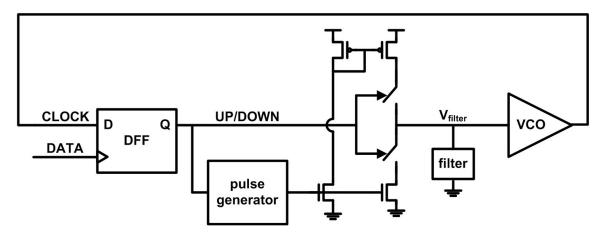

| 2.11 | A CDR circuit with a DFF as the phase detector $\hdots \hdots \h$ | 19 |

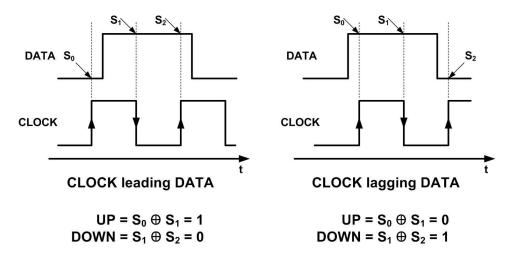

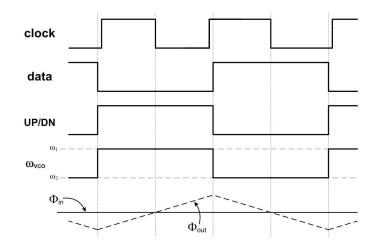

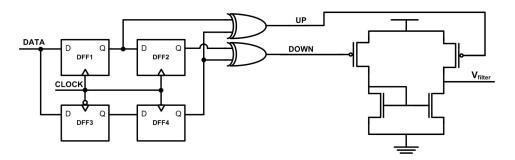

| 2.12 | The sampling behavior of an Alexander phase detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 |

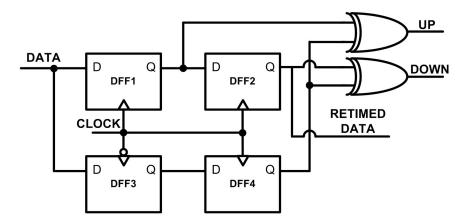

| 2.13 | Architecture of the Alexander phase detector $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 |

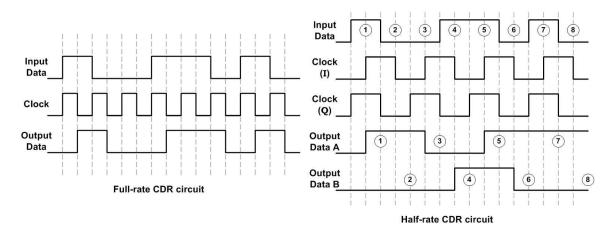

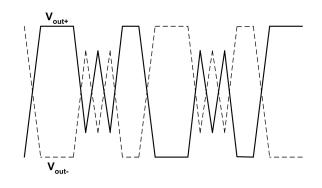

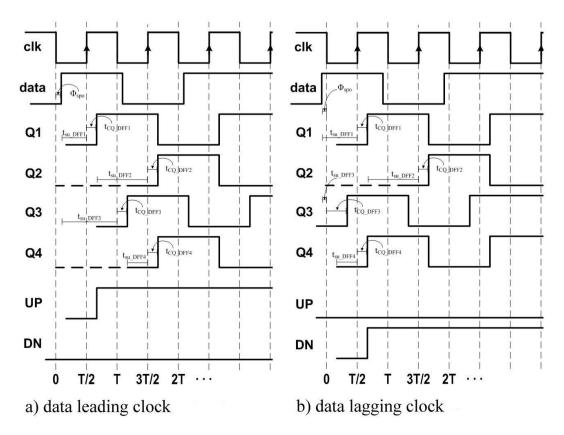

| 2.14 | Waveforms of full-rate and half-rate CDR circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22 |

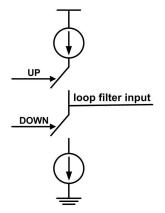

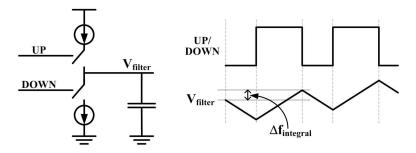

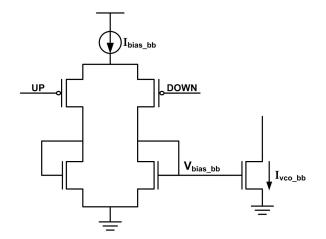

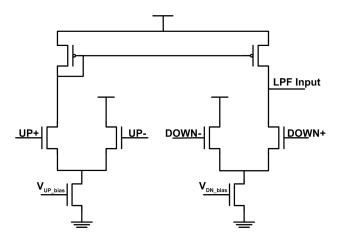

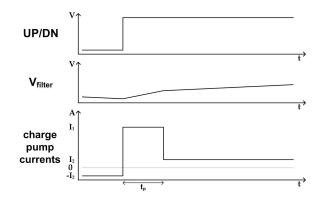

| 2.15 | Basic architecture of a charge pump $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23 |

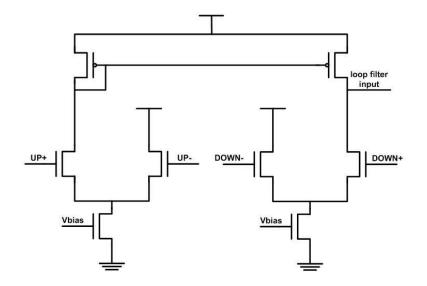

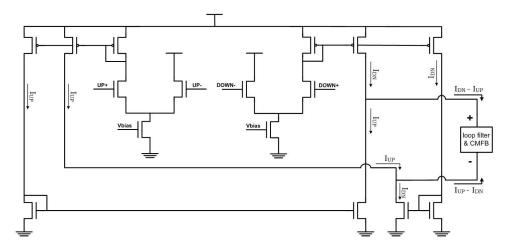

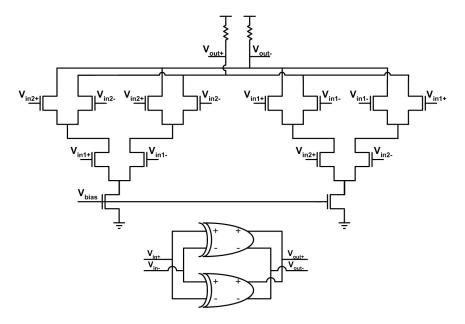

| 2.16 | Current steering charge pump with differential inputs $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24 |

| 2.17 | Differential implementation of a charge pump $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25 |

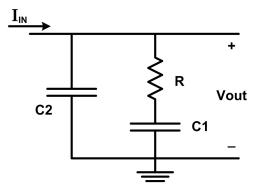

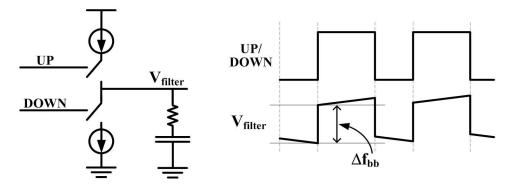

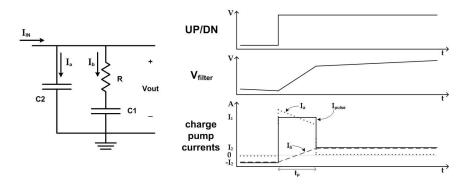

| 2.18 | Second order low pass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26 |

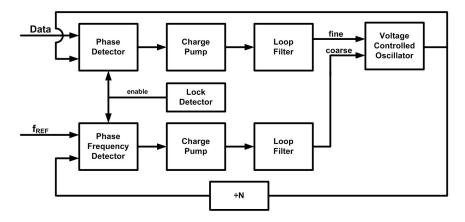

| 2.19 | Architecture of a CDR circuit with a dual loop structure and an external reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27 |

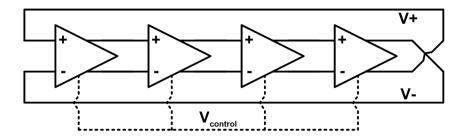

| 2.20 | Architecture of a four stage ring oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

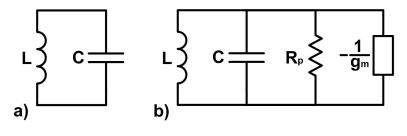

| 2.21 | (a)Ideal LC-tank (b)LC-tank with parasitics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29 |

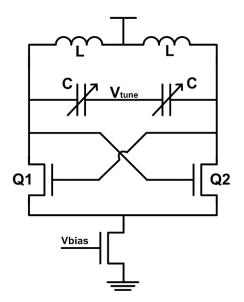

| 2.22 | LC-tank oscillator with NMOS cross-couple pair $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30 |

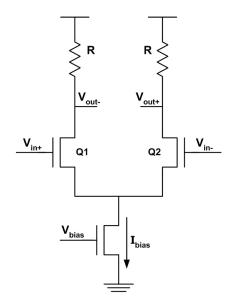

| 2.23 | CML implementation of a buffer $\hfill \ldots \hfill \ldots \hfilt$ | 31 |

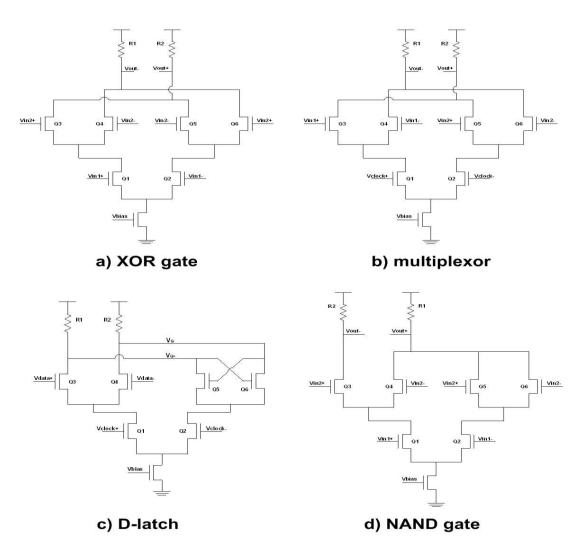

| 2.24 | CML implementation of four different logic gates $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

| 2.25 | Frequency domain mathematical model of a CDR circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34 |

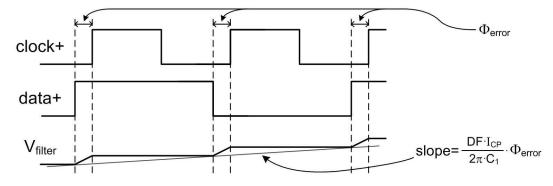

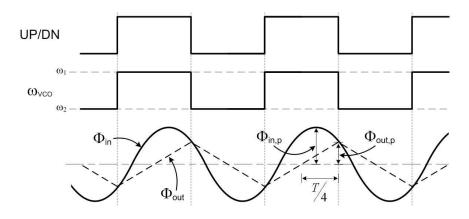

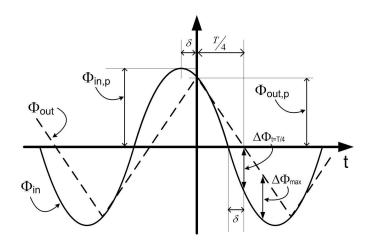

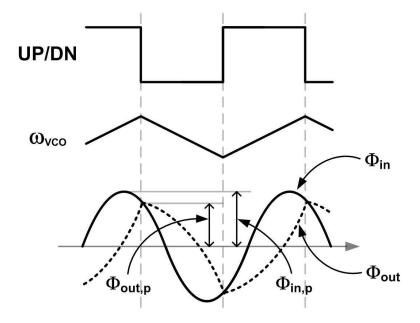

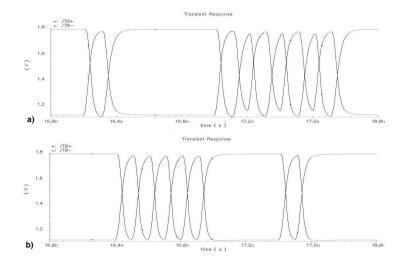

| 2.26 | Output waves from a CDR circuit with a capacitor for a loop filter $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35 |

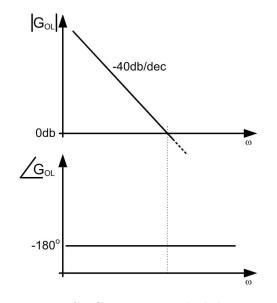

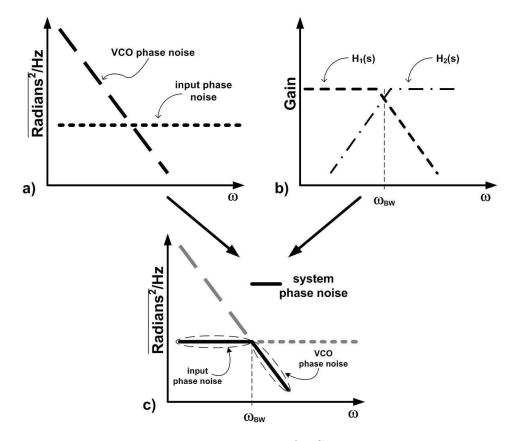

| 2.27 | Frequency response of a CDR circuit which has a capacitor as the loop filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36 |

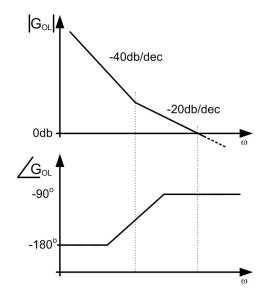

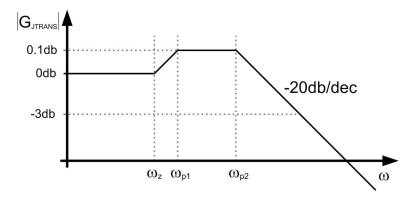

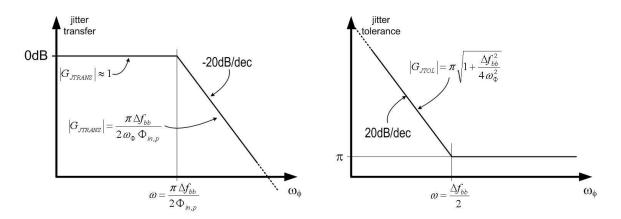

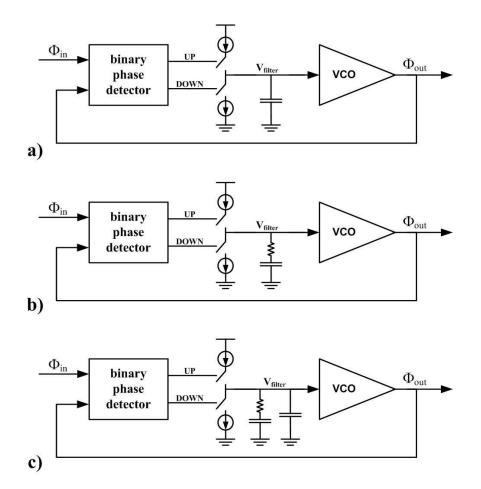

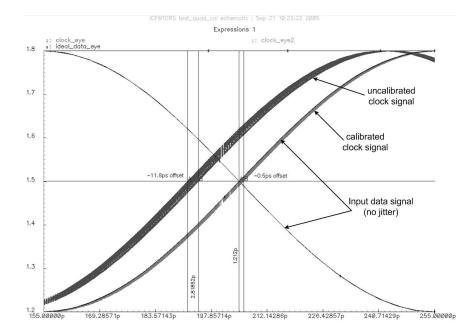

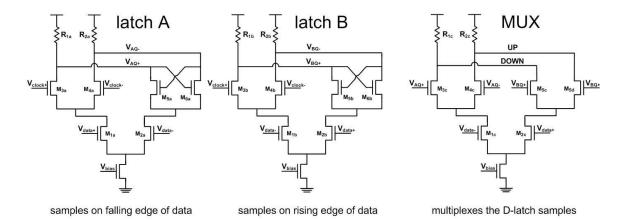

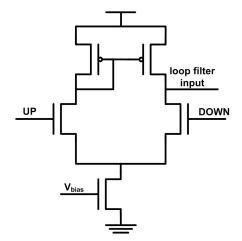

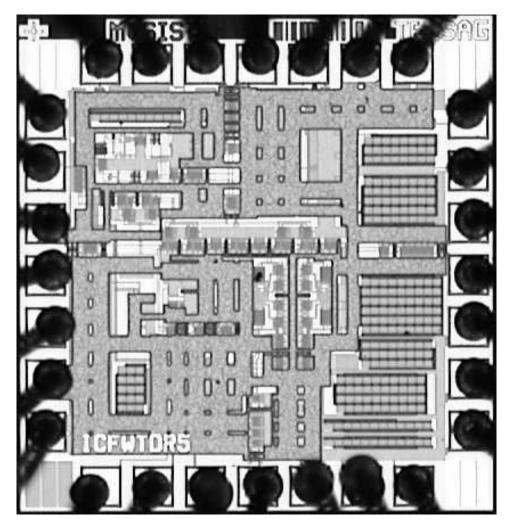

| 2.28 | Frequency response of a CDR circuit which has a first order loop filter $\ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |