# Dynamic HW/SW Partitioning: Configuration Scheduling and Design Space Exploration

by

Santheeban Kandasamy

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2007

©Santheeban Kandasamy, 2007

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Santheeban Kandasamy

### Abstract

Hardware/software partitioning is a process that occurs frequently in embedded system design. It is the procedure of determining whether a part of a system should be implemented in software or hardware. This dissertation is a study of hardware/software partitioning and the use of scheduling algorithms to improve the performance of dynamically reconfigurable computing devices. Reconfigurable computing devices are devices that are adaptable at the logic level to solve specific problems [Tes05]. One example of a reconfigurable computing device is the field programmable gate array (FPGA). The emergence of dynamically reconfigurable FPGAs made it possible to configure FPGAs at runtime. Most current approaches use a simple on demand configuration scheduling algorithm for the FPGA configurations. The on demand configuration scheduling algorithm reconfigures the FPGA at runtime, whenever a configuration is needed and is found not to be configured. The problem with this approach of dynamic reconfiguration at runtime. Configuration caches and partial configuration have been proposed as possible solutions to this problem, but these techniques suffer from various limitations.

The emergence of dynamically reconfigurable FPGAs also made it possible to perform dynamic hardware/software partitioning (DHSP), which is the procedure of determining at runtime whether a computation should be performed using its software or hardware implementation. The drawback of performing DHSP using configurations that are generated at runtime is that the profiling and the dynamic generation of configurations require profiling tool and synthesis tool access at runtime. This study proposes that configuration scheduling algorithms, which perform DHSP using statically generated configurations, can be developed to combine the advantages and reduce the major disadvantages of current approaches. A case study is used to compare and evaluate the tradeoffs between the currently existing approach for dynamic reconfiguration model is developed to examine the performance of the various configuration scheduling algorithms. First, the difference in the execution time between the different approaches is analyzed. Afterwards, other important design criteria such as power consumption, energy consumption, area requirements and unit cost are analyzed and estimated. Also, business and marketing considerations such as time to market and development cost are considered.

The study illustrates how different types of DHSP configuration scheduling algorithms can be implemented and how their performance can be evaluated using a variety of software applications. It is also shown how to evaluate when which of the approaches would be more advantageous by determining the tradeoffs that exist between them. Also the underlying factors that affect when which design alternative is more advantageous are determined and analyzed. The study shows that configuration scheduling algorithms, which perform DHSP using statically generated configurations, can be developed to combine the advantages and reduce some major disadvantages of current approaches. It is shown that there are situations where DHSP configuration scheduling algorithms can be more advantageous than the other approaches.

### Acknowledgements

First, I would like to thank my family – Mom, Dad, Brothers, Sisters, Uncles, Aunts and Diana. I could not have completed this without your support.

I would like to thank my supervisors Dr. Andrew Morton and Dr. Wayne Loucks. Thank you for making this experience into an interesting and enjoyable one. I am very glad that I had the opportunity to work with you. Thank you for your guidance, support and always being around when I needed help and advice.

Thanks to CMC Microsystems for providing the lab equipment and design tools. I am also thankful to Dr. Russell Tessier, Dr. William Bishop, Dr. Frank Vahid and Greg Stitt for their advice and guidance. Finally I would like to thank my friends for all the entertainment and sport events.

### **Table of Contents**

| 1 Introduction                                                        | 1  |

|-----------------------------------------------------------------------|----|

| 1.1 Dynamic Reconfiguration                                           | 1  |

| 1.2 Thesis Statement                                                  | 3  |

| 1.3 Thesis Contribution                                               | 3  |

| 1.4 Thesis Outline                                                    | 4  |

| 2 Background and Literature Review                                    | 5  |

| 2.1 Hardware/Software Co-Design                                       | 5  |

| 2.1.1 Design Flow                                                     | 5  |

| 2.1.2 System Synthesis                                                | 7  |

| 2.2 Reconfigurable Computing                                          | 9  |

| 2.2.1 Dynamic Reconfiguration                                         |    |

| 2.2.2 Dynamic Hardware/Software Partitioning                          | 13 |

| 2.3 Summary                                                           | 15 |

| 3 Execution Time and Configuration Scheduling                         | 17 |

| 3.1 Hardware/Software Partitioning                                    | 17 |

| 3.2 On Demand Configuration Scheduling Algorithm                      | 21 |

| 3.3 Configuration Scheduling Algorithms for DHSP                      |    |

| 3.3.1 Temporal Locality Configuration Scheduling Algorithm            |    |

| 3.3.2 Kernel Correlation Configuration Scheduling Algorithm           |    |

| 3.4 Summary                                                           | 43 |

| 4 Configuration Scheduling Algorithm Performance Evaluation           |    |

| 4.1 Case Study                                                        |    |

| 4.2 Simulation Model                                                  |    |

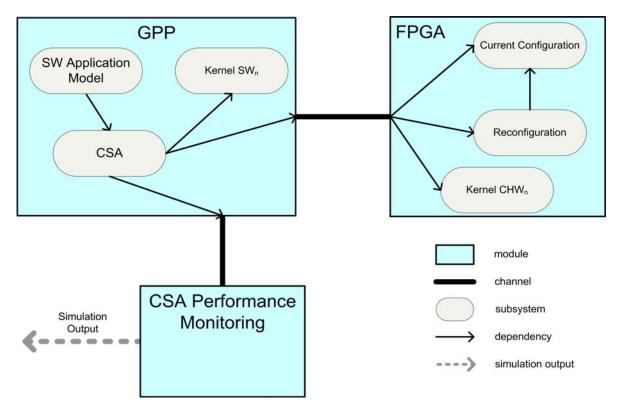

| 4.2.1 SystemC Modeling Framework                                      | 49 |

| 4.2.2 Model Architecture                                              |    |

| 4.2.3 Application Models                                              | 51 |

| 4.2.4 Configuration Scheduling Algorithm Implementation               | 53 |

| 4.3 Experiments, Results and Discussion                               | 55 |

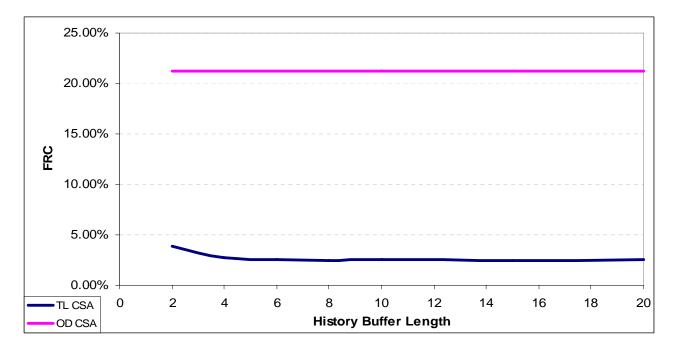

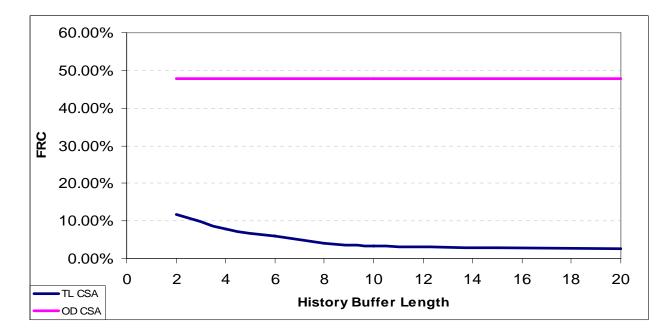

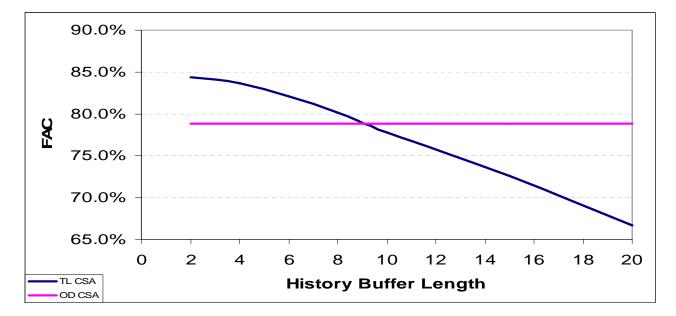

| 4.3.1 Frequency of Reconfiguration and History Buffer Length Analysis | 56 |

| 4.3.2 Execution Time Analysis                                         | 64 |

| 4.4 Summary                                                                       | 72  |

|-----------------------------------------------------------------------------------|-----|

| 5 Tradeoff Analysis and Design Space Exploration                                  | 74  |

| 5.1 Estimation                                                                    | 74  |

| 5.1.1 Power and Energy Consumption                                                | 75  |

| 5.1.2 Area Requirements and Unit Cost                                             | 81  |

| 5.2 Business and Marketing Considerations                                         | 86  |

| 5.2.1 Development Cost                                                            |     |

| 5.2.2 Time to Market                                                              |     |

| 5.3 Summary                                                                       |     |

| 6 Summary and Concluding Remarks                                                  | 90  |

| 6.1 Thesis Contributions and Conclusions                                          | 90  |

| 6.1.1 Execution Time and Configuration Scheduling Algorithm Performance Analysis. | 90  |

| 6.1.2 Tradeoff Analysis and Design Space Exploration                              | 92  |

| 6.2 Remarks on Further Studies                                                    | 93  |

| 6.2.1 Future Research                                                             | 93  |

| 6.2.2 Configuration Scheduling Algorithm Design Guidelines                        | 95  |

| 6.3 Final Observations                                                            | 96  |

| A Simulation Inputs                                                               | 104 |

| A.1 Application Models and Test Cases                                             | 104 |

| A.2 Timing Delays and Simulation Parameters                                       | 107 |

| B Simulation Results                                                              |     |

| B.1 Frequency Results                                                             |     |

| B.2 History Buffer Experiment Results                                             | 109 |

| B.3 Execution Time Results                                                        | 111 |

| C Glossary of Acronyms                                                            | 113 |

# **List of Figures**

| 2-1: Hardware/Software Co-Design Flow [Thi06]                                          |

|----------------------------------------------------------------------------------------|

| 2-2: System Synthesis                                                                  |

| 3-1: Kernel Implementation System Architectures                                        |

| 3-2: Hardware/Software Partitioning Timing Diagram                                     |

| 3-3: On Demand Configuration Scheduling Algorithm                                      |

| 3-4: Concurrent Reconfiguration                                                        |

| 3-5: Temporal Locality Configuration Scheduling Algorithm                              |

| 3-6: Kernel Correlation Configuration Scheduling Algorithm Timing Diagram              |

| 4-1: SystemC Model Software Architecture                                               |

| 4-2: Temporal Locality Test Case 2 - Frequency of Reconfiguration vs. Buffer Length    |

| 4-3: Temporal Locality Test Case 3 - Frequency of Reconfiguration vs. Buffer Length    |

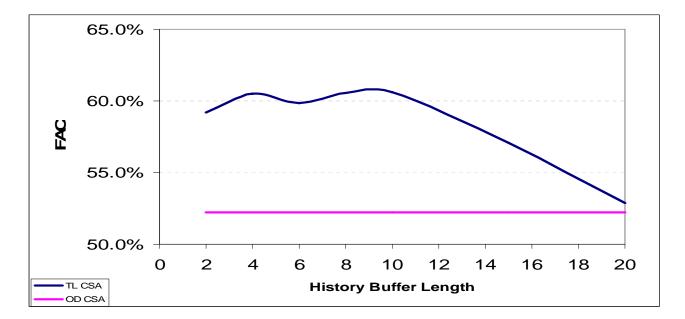

| 4-4: Temporal Locality Test Case 2 - Frequency of Already Configured vs. Buffer Length |

| 4-5: Temporal Locality Test Case 3 - Frequency of Already Configured vs. Buffer Length |

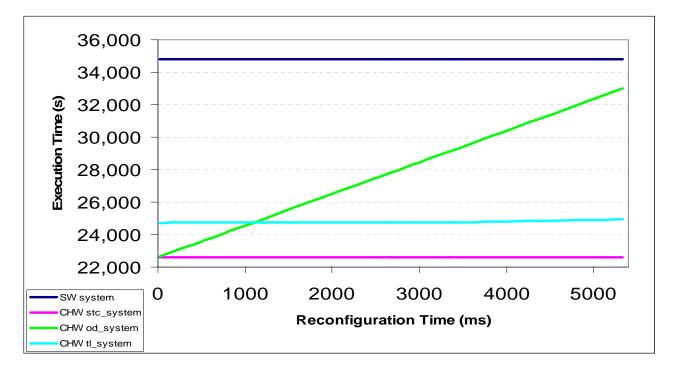

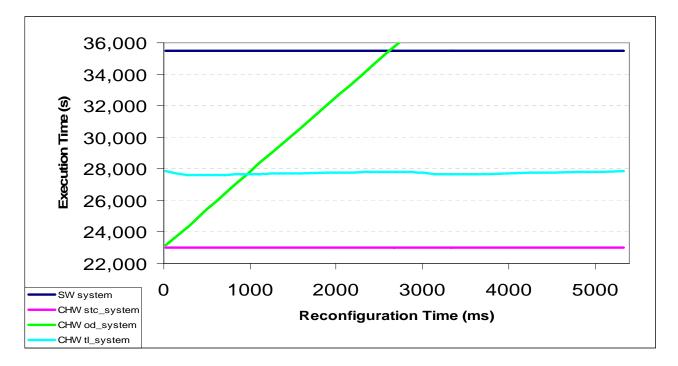

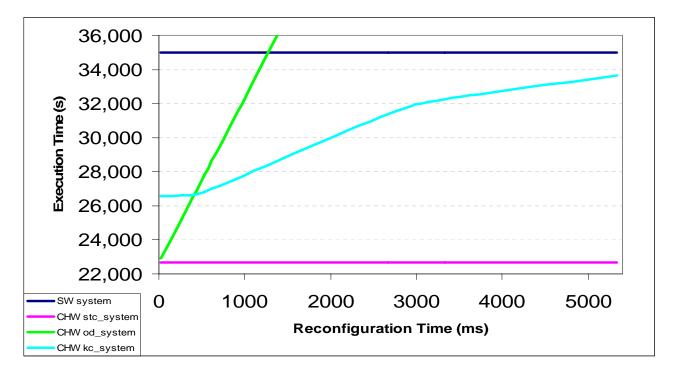

| 4-6: Temporal Locality Test Case 2 – Execution Time vs. Reconfiguration Time           |

| 4-7: Temporal Locality Test Case 3 – Execution Time vs. Reconfiguration Time           |

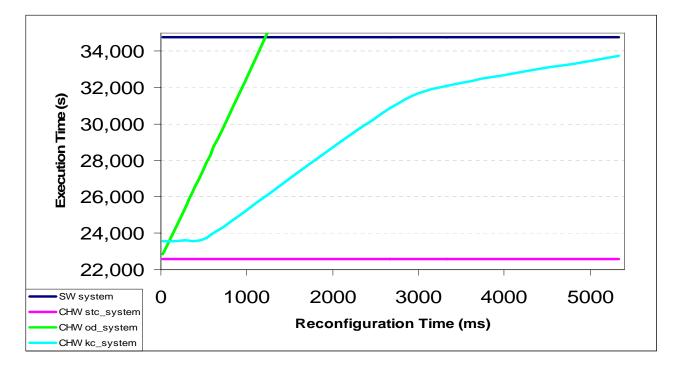

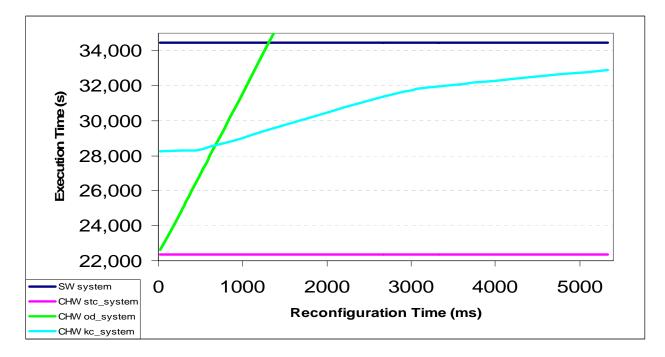

| 4-8: Kernel Correlation Test Case 1 – Execution Time vs. Reconfiguration Time          |

| 4-9: Kernel Correlation Test Case 2 – Execution Time vs. Reconfiguration Time          |

| 4-10: Kernel Correlation Test Case 3 – Execution Time vs. Reconfiguration Time         |

### List of Tables

| 3-1: Hardware/Software Partitioning Timing Parameters                            | 19  |

|----------------------------------------------------------------------------------|-----|

| 3-2: Equation 6 Timing Parameters                                                | 21  |

| 4-1: Software Application Models Summary                                         | 53  |

| 4-2: Temporal Locality Configuration Scheduling Algorithm History Buffer Example | 57  |

| 5-1: Power Estimation Parameters                                                 | 76  |

| 5-2: Component Mode Percentage Equations                                         | 77  |

| 5-3: Power Timing Calculations                                                   | 78  |

| 5-4: Temporal Locality Power and Energy Consumption Results                      | 79  |

| 5-5: Kernel Correlation Power and Energy Consumption Results                     | 79  |

| 5-6: Area Estimation Parameters                                                  |     |

| 5-7: FPGA Area Estimation                                                        |     |

| 5-8: ROM Area Estimation                                                         |     |

| 5-9: Area and Unit Cost Results                                                  |     |

| 5-10: SPP Hardware Design Relative Sizes                                         |     |

| 5-11: Unit Cost Estimation Parameters                                            | 85  |

| A-1: Temporal Locality Test Case 1                                               | 104 |

| A-2: Temporal Locality Test Case 2                                               | 104 |

| A-3: Temporal Locality Test Case 3                                               |     |

| A-4: Kernel Correlation Test Case 1                                              | 105 |

| A-5: Kernel Correlation Test Case 2                                              | 106 |

| A-6: Kernel Correlation Test Case 3                                              | 106 |

| A-7: Timing Delays and Parameter Values                                          | 107 |

| B-1: Temporal Locality Test Case 1 Frequency Results                             |     |

| B-2: Temporal Locality Test Case 2 Frequency Results                             |     |

| B-3: Temporal Locality Test Case 3 Frequency Results                             |     |

| B-4: Temporal Locality Test Case 2 History Buffer Results                        |     |

| B-5: Temporal Locality Test Case 3 History Buffer Results                        | 110 |

| B-6: Temporal Locality Test Case 1 Execution Time Results                        | 111 |

| B-7: Temporal Locality Test Case 2 Execution Time Results                        | 111 |

| B-8: Temporal Locality Test Case 3 Execution Time Results                        | 111 |

| B-9: Kernel Correlation Test Case 1 Execution Time Results  | 112 |

|-------------------------------------------------------------|-----|

| B-10: Kernel Correlation Test Case 2 Execution Time Results | 112 |

| B-11: Kernel Correlation Test Case 3 Execution Time Results | 112 |

# List of Algorithms

| 3-1: On Demand Configuration Scheduling Algorithm Pseudo Code          | 22 |

|------------------------------------------------------------------------|----|

| 3-2: Temporal Locality Configuration Scheduling Algorithm Pseudo Code  | 33 |

| 3-3: Kernel Correlation Configuration Scheduling Algorithm Pseudo Code | 39 |

| 4-1: Temporal Locality Monitoring Phase                                | 54 |

| 4-2: Kernel Correlation Monitoring Phase                               | 55 |

## Chapter 1 Introduction

This dissertation is a study of hardware/software partitioning and the use of scheduling algorithms to improve the performance of dynamically reconfigurable computing devices. Hardware/software partitioning is the procedure of determining whether subsystem should be implemented in software or hardware and it is one of the design stages of the hardware/software co-design flow. Hardware/software co-design is the simultaneous design of hardware and software to obtain an optimized system. It is frequently used for the design of embedded systems since it exploits the synergy of considering hardware and software design issues concurrently and therefore allows the design of highly optimized systems.

Reconfigurable computing devices are hardware devices that are adaptable at the logic level to solve specific problems [Tes05]. One example of a reconfigurable computing device is the field programmable gate array (FPGA), which is in wide use today for system customization, glue logic and rapid prototyping. FPGAs are configurable integrated circuits that have programmable interconnections and logic. They have the advantage of being very flexible and they do not have to be custom manufactured since they provide post fabrication customization.

#### **1.1 Dynamic Reconfiguration**

The emergence of dynamically reconfigurable FPGAs made it possible to configure FPGAs at runtime. Dynamic reconfiguration is useful in systems where only a subset of the configurations is needed at a time. One advantage of dynamic reconfiguration is that a single smaller FPGA can be time-multiplexed to support multiple configurations over time. In contrast, a statically configured system would require multiple FPGAs or a larger FPGA to hold all the configurations at all times. Dynamically reconfigurable systems therefore have a higher functional density due to the use of the smaller FPGA, which can result in reduced unit cost and area requirements. The configuration scheduling algorithm (CSA) is the algorithm that determines when a configuration is used for device reconfiguration. Most approaches use a simple on demand (OD) configuration scheduling algorithm. The on demand configuration is needed. The problem with this approach of dynamic reconfiguration is the reconfiguration time overhead, which is the time it takes to configure the FPGA with a new configuration at runtime.

To address the reconfiguration time overhead, configuration caches and dynamically programmable gate arrays (DPGAs) have been proposed in [BD94], [HW97] and [JC99]. Frequently used configurations can be kept in a configuration cache, which allows for fast reconfiguration and therefore reduces the reconfiguration time overhead. DPGAs are FPGAs with multiple contexts. These allow for fast switching between configurations. But up to now there has still not been any commercial implementation of a DPGA. This is due to the fact that the extra area and cost associated with the configuration caches and multiple contexts of DPGAs acts against one of the main objectives of dynamic reconfiguration, which is the goal of obtaining a higher functional density from a smaller FPGA. Another approach to reduce the reconfiguration of a portion of the FPGA while leaving the previous configuration for the rest of the FPGA. By only having to reconfigure parts of the FPGA the reconfiguration time is reduced. To take advantage of this approach it is required that the hardware designs to be configured in the FPGA have parts in common. Advanced electronic design automation (EDA) tools are often required and used in the industry to identify such common parts of the hardware designs, which results in additional development costs and an increase in time to market (TTM).

The emergence of dynamically reconfigurable FPGAs also made it possible to perform dynamic hardware/software partitioning (DHSP), which is the procedure of determining at runtime whether a computation should be performed using its software or hardware implementation. Modern EDA tools have the potential of fully automating the process of hardware/software partitioning and enable the possibility of moving hardware/software partitioning and the generation of the FPGA configurations from the design phase to the execution stages of the system. Such an approach was studied in [SL03] and [LV04] where the software is initially executed without any hardware acceleration, while the software is being profiled at runtime. After determining the portion of the software that would benefit most from hardware acceleration a coprocessor is generated for that part of the software at runtime. Since the decision of which part of the software should be executed using its software or hardware implementation is made at runtime, this approach is called dynamic hardware/software partitioning (DHSP). The drawback of performing DHSP using configurations that are generated at runtime is that the profiling and the dynamic generation of configurations require profiling tool access and synthesis tool access at runtime.

#### **1.2 Thesis Statement**

Many past research projects showed the advantages of DHSP and dynamic reconfiguration of FPGAs in general. But there have still not been any significantly successful applications of these technologies in industry, due to various weaknesses and limitations associated with them. Most current approaches for dynamic reconfiguration of FPGAs use a simple on demand configuration scheduling algorithm that reconfigures the FPGA at runtime, whenever a new configuration is needed. The problem with this approach of dynamic reconfiguration is the reconfiguration time overhead. The approach of performing DHSP using dynamically generated configurations has the drawback that the profiling and the dynamic generation of configurations require profiling tool access and synthesis tool access at runtime. It is my thesis that configuration scheduling algorithms, which perform DHSP using statically generated configurations, can be developed to combine the advantages and eliminate the major drawbacks of both the on demand configuration scheduling algorithm and DHSP using dynamically generated configurations. This new approach eliminates the need for profiling and synthesis tool access at runtime, by using statically generated configurations. By performing DHSP, the configuration scheduling algorithm can also reduce the reconfiguration time overhead.

#### **1.3 Thesis Contribution**

The main contributions of the study are:

- 1. illustration of how configuration scheduling algorithms can be used to perform DHSP using statically generated configurations,

- 2. implementation of different types of DHSP configuration scheduling algorithms and evaluation of how they perform on a variety of software applications,

- comparison and evaluation of the tradeoffs between the current approach for dynamic reconfiguration (on demand configuration scheduling algorithm) and the DHSP configuration scheduling algorithm based approach proposed in the study, and

- 4. analysis and determination of the underlying factors that affect when a design alternative is more advantageous than another.

In Chapter 6 these contributions are evaluated and the conclusions of the study are summarized.

#### 1.4 Thesis Outline

Chapter 2 introduces the research area of the study by reviewing the existing literature. An introduction to hardware/software co-design and reconfigurable computing is presented first, followed by a discussion on dynamic reconfiguration and hardware/software partitioning. Afterwards some of the current challenges that exist in these research areas are identified. Then the methods that are currently proposed in the literature to solve the problems examined in the study are analyzed and appraised. Chapter 3 first looks at the effects of hardware/software partitioning on the execution time of a software application. Then it is identified how the on demand configuration scheduling algorithm affects the application's execution time. Afterwards, the approach of performing DHSP using configuration scheduling algorithms is proposed. Some benefits of the DHSP configuration scheduling algorithm based approach and its impact on the application's execution time are illustrated and analyzed

Chapter 4 first presents a case study that is used to evaluate the different approaches and configuration scheduling algorithms. Afterwards the modeling framework and methodology that was chosen to examine the performance of the configuration scheduling algorithms is explained. After introducing the implementation of the model, simulation results are presented. The results are then examined and it is determined if they are consistent with the analysis and theory presented in Chapter 3. Finally the patterns and trends in the simulation results are identified and the insights gained from the experiments are summarized. Chapter 4 examines the difference in the execution time between the design alternatives. Chapter 5 first examines and estimates other important design criteria such as power consumption, energy consumption, area requirements and unit cost. Afterwards business and marketing considerations such as TTM and development cost are also considered. The goal of this chapter is to provide insight into how to evaluate when a design alternative is advantageous by determining the tradeoffs that exist in the design space. Chapter 6 first summarizes the contributions and observations made in the study. Afterwards suggestions on the direction of future research in the area of the study are provided.

# Chapter 2 Background and Literature Review

In this chapter, the research area of the study is introduced by reviewing the existing literature. First a brief introduction to hardware/software co-design and reconfigurable computing is presented, followed by a discussion on dynamic reconfiguration and hardware/software partitioning. After identifying some of the current challenges that exist in these research areas, methods, which are currently proposed in the literature to solve the problems examined in the study, are analyzed and appraised.

#### 2.1 Hardware/Software Co-Design

Hardware/software co-design is the process of designing hardware and software in parallel to obtain an optimized system. This section provides a brief introduction to the hardware/software co-design flow and illustrates where hardware/software partitioning falls in the design flow.

#### 2.1.1 Design Flow

Co-design is frequently used for the design of embedded systems, since they require optimization to satisfy various design constraints and objectives. Modern advances in electronic design automation (EDA) tools such as high level synthesis tools and simulation tools make it possible to explore both hardware and software design alternatives in parallel, to select the best alternative. One advantage of designing an embedded system using co-design is that it reduces the time to market (TTM), by allowing the development of hardware and software in parallel. Hardware/software co-design also exploits the synergy of considering hardware and software design issues concurrently and therefore allows the design of highly optimized systems.

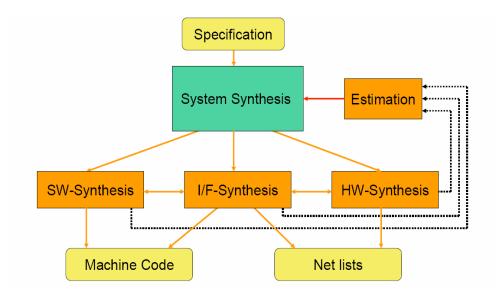

It is possible to design both hardware and software in parallel when designing embedded systems, since the workload, which is the work that needs to be performed by the system, is well defined at hardware design time. This is in sharp contrast to the way general purpose systems, such as personal computers (PCs) are designed. For such systems, the exact workload is not known at hardware design time and the hardware is designed well in advance before the software. The entire hardware/software co-design flow is illustrated in Figure 2-1.

Figure 2-1: Hardware/Software Co-Design Flow [Thi06]

Synthesis is the process of transforming a behavioral description of a system into a structural description by moving the description to a lower abstraction level. The system synthesis phase takes the specification, which describes the desired functionality of the system and determines a possible architecture of the system. This architecture is composed of the structural descriptions of the hardware, software and the interface between them. The software architecture is described using modules and their interaction and the hardware architecture is described using components and their interconnections. It is then possible to take this high level description of the system and synthesize the hardware and software to lower abstraction levels, such as machine code and net lists, using compilers and hardware synthesis tools. The synthesis output can then be used to estimate the values of important design criteria, which would be obtained if this particular design alternative was chosen. By iterating through various design alternatives the design space is explored and values of design criteria, which are of interest, are estimated. Finally the estimated values of the design criteria are used to select the best design alternative. This process of analyzing several functionally equivalent design alternatives to determine the most suitable one is known as design space exploration. For the purposes of the study the next section takes a closer look at the system synthesis phase and hardware/software partitioning in particular.

#### 2.1.2 System Synthesis

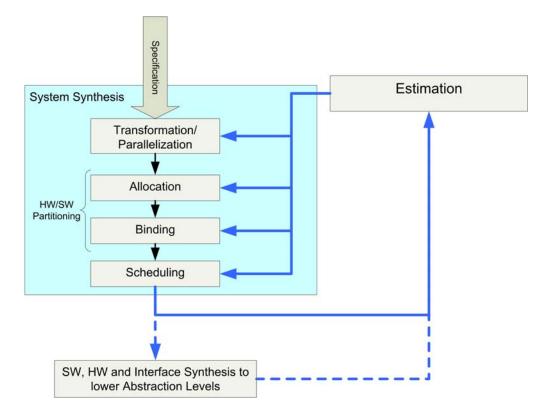

To show where hardware/software partitioning falls in the co-design flow the details of the system synthesis phase are presented in Figure 2-2 and each of the system synthesis stages are described thereafter.

Figure 2-2: System Synthesis

**Transformation/Parallelization:** During this stage complex systems are split up into multiple simpler processes that can be executed individually to satisfy the requirements of the entire system. At this design stage it is still unclear how the processes are implemented in the final system. These considerations are left to the later stages in the design flow. At this point, the only concern is about how to split the work up into smaller pieces using a divide and conquer strategy. The goal of parallelization is to improve performance by allowing work to be done concurrently but it also splits up the system into smaller more manageable pieces.

Allocation: Allocation is the process of selecting the hardware architecture that will be used for implementing the system. This involves selecting the number and types of processors that will be used. Selecting the memory architecture and interconnections between the various components is also part of this step. From the transformation/parallelization stage, a set of processes and the communication and synchronization that need to be present between the processes are defined. Now processors need to be selected to implement the processes. For the purposes of the study, processors can be categorized using the following classifications.

- <u>Processor Technologies</u>

- 1. General Purpose Processor (GPP) software implementation

- 2. Single Purpose Processor (SPP) hardware implementation using a coprocessor

- Integrated Circuit (IC) Technologies

- 1. Full Custom ASIC

- 2. Gate Array based ASIC

- 3. Field Programmable Gate Array (FPGA)

The main advantage of GPPs is that they are flexible since they can perform any type of computation. SPPs are not flexible and suffer from high development costs, but perform the computation that they are customized to execute at a higher speed than GPPs. Full custom ASIC technology has a high development cost due to the custom placement and routing that is required. Gate array based ASICs have pre-placed arrays of gates and therefore the only customization that is required is the routing between the gates. Gate array based ASICs are less optimal compared to full custom ASICs in terms of performance and power but the development cost of gate array based ASICs is significantly less. FPGAs are configurable ICs that have programmable interconnections and logic. This type of IC is the most flexible; it requires the least amount of hardware development cost and provides fast TTM, but it also provides the worst performance, power, and area requirements when compared to the other IC technologies. Any processor technology can be mapped to any type of IC technology.

**Binding:** A set of processes and the communication and synchronization that need to be present between the processes are now defined. Also the hardware architecture, which consists of a set of processors, other hardware components and their interconnections, is now defined. In the binding stage the processes are mapped to processors and the data and instructions are partitioned to memory.

**Scheduling:** Having the processes assigned to specific processors, it is necessary to schedule when each process executes on the processors. Scheduling the processes on the processors is the goal of this stage.

After introducing the system synthesis stages it can now be examined where hardware/software partitioning falls in the co-design flow. Hardware/software partitioning is the procedure of determining whether a part of a system should be implemented on a GPP (software) or SPP (hardware). Hardware/software partitioning can be thought of as taking place over the allocation and binding stages of system synthesis as shown in Figure 2-2. Since the hardware/software partitioning problem occurs frequently in embedded system design much research has been devoted to analyze this problem. Since hardware/software partitioning will be the main focus of the study, this section was dedicated to introduce where it falls into the broader research area of hardware/software co-design.

#### 2.2 Reconfigurable Computing

This section provides a brief introduction to reconfigurable computing followed by a discussion on dynamic reconfiguration and dynamic hardware/software partitioning (DHSP). Some of the current challenges that exist in these research areas are also presented. Also the techniques, which are currently proposed in the literature to solve the limitations of existing methods, are appraised.

Reconfigurable computing devices are hardware devices that are adaptable at the logic level to solve specific problems [Tes05]. One example of a reconfigurable computing device is the previously introduced FPGA, which is in wide use today for system customization, glue logic and IC prototyping. FPGAs are configurable ICs that have programmable interconnections and logic. They have the advantage of being very flexible and they do not have to be custom manufactured since they provide post fabrication customization. Due to this property, FPGAs require the least amount of hardware development cost and provide fast TTM. Due to the overhead of being reconfigurable, they provide the worst performance, power and area requirements when compared to full custom and application specific ICs. For the purposes of the study, FPGAs and reconfigurable computing devices in general can be categorized using the following classifications:

- FPGA coupling to Central Processing Unit (CPU)

- 1. FPGA/coprocessor connected to CPU through a bus loose coupling

- 2. CPU with a configurable functional unit (FU) tight coupling

- <u>Type of configuration</u>

- 1. Static configuration -FPGA is configured once before use and not at runtime

- 2. Dynamic configuration FPGA is reconfigured multiple times at runtime

#### 2.2.1 Dynamic Reconfiguration

One advantage of dynamic reconfiguration is that a single smaller FPGA can be time multiplexed to support multiple configurations over time. Dynamic reconfiguration is useful in systems where only one of the configurations is needed at a time. In contrast, a statically configured system would require multiple FPGAs or a larger FPGA to hold all the configurations at all times. Dynamically reconfigurable systems therefore have a higher functional density due to the smaller FPGA, which results in reduced unit cost and area.

One application of dynamic reconfiguration is to update systems and to fix problems with previous releases. It is possible, for example, to update the FPGA with a new configuration at runtime to support a newer communication protocol. Dynamic reconfiguration can also be used to increase the fault tolerance of a FPGA design. Once faulty locations have been detected in the FPGA, it is possible to reconfigure the device with an alternate and functionally equivalent configurations can be recompiled and generated at runtime based on fault location information or multiple configurations can be precompiled and stored in anticipation of faults. Generating alternate configurations at runtime requires access to synthesis tools and suffers from long system downtime due to the time it requires to generate the new configurations. Storing precompiled configuration and eliminates the need for synthesis tool access at runtime. In [HM01], multiple precompiled configurations of the same design with different unused columns of the FPGA are generated during the design phase. When a fault is discovered the FPGA is reconfigured with one of the precompiled configurations, which does not use the faulty column.

As mentioned previously, dynamic reconfiguration is also useful in applications with time-varying behavior. The FPGA can be reconfigured dynamically with an optimal configuration for a given time, in

response to changing environmental inputs to the system. In [ST02], this concept is illustrated using a dynamically reconfigurable adaptive Viterbi decoder that is implemented on a FPGA. The amount of computation, which needs to be performed to decode the transmitted data with an acceptable bit error rate, is proportional to the channel noise. The adaptive Viterbi decoder takes advantage of the fact that the channel noise varies over time. The decoder is configured such that it performs the minimum amount of computation needed at a given time depending on the amount of noise present in the channel. When an increase or decrease in the amount of channel noise is detected, the decoder is dynamically reconfigured to perform more or less computation respectively. This allows the decoder to adapt to the varying channel noise, instead of always assuming the worst case channel noise. Dynamic reconfiguration therefore allows the decoder to tune and adapt to varying channel conditions, which results in more efficient computation and the maximum performance possible at a given time.

Dynamic reconfiguration can be performed with both tightly and loosely coupled reconfigurable computing devices. The PRISC and Chimaera projects [Tes05] are examples of tightly-coupled reconfigurable functional units. These functional units are often used to augment the existing instruction set. They share the processor registers and depend on the processor for access to memory. Loosely-coupled reconfigurable computing devices on the other hand are independent coprocessors that have their own interface for memory access. Garp [HW97] is an example of a loosely-coupled system designed for streaming data applications. It consists of a MIPS processor with a reconfigurable configurations whenever a needed configuration is not present in the coprocessor. One-Chip [JC99] is a processor with a reconfigurable functional unit that has direct access to memory. It is therefore considered to be a hybrid between a reconfigurable functional unit and coprocessor. Here the software must first initialize a reconfiguration bits table, with memory addresses that indicate where the different configurations can be found in memory. Whenever a needed configuration is not currently configured, the hardware determines the address of the configuration data from the reconfiguration bits table and performs the reconfiguration.

The configuration scheduling algorithm (CSA) is the algorithm that determines when a configuration is used for device reconfiguration. The reconfigurable computing devices introduced so far use a simple on demand (OD) configuration scheduling algorithm. The on demand configuration scheduling algorithm reconfigures the reconfigurable computing device at runtime, whenever a new configuration is needed. A detailed discussion on configuration scheduling algorithms is the topic of Chapter 3.

One common problem with the all of the techniques examined so far is the time it takes to reconfigure the device with a new configuration as identified in [HW97], [Tes05] and [JC99]. This reconfiguration time overhead becomes a significant problem when the frequency of reconfiguration (FRC) increases. As the frequency of reconfiguration increases, the time intervals between device reconfiguration decreases, which magnifies the performance degradation due to the reconfiguration time overhead. It is possible to decrease the negative effects of the reconfiguration time overhead by decreasing the frequency of reconfiguration as shown in [ST02]. Reducing the frequency of reconfiguration can also have other positive benefits such as reducing the power consumption of the system. It should also be noted that reducing the frequency of reconfiguration is not a possibility in many systems due to the inherent inflexibility of the configuration scheduling algorithm employed. When using an on demand configuration scheduling algorithm, there is no other possibility than reconfiguring the device with a required configuration, when it is needed and is found not to be currently configured.

To address the reconfiguration time overhead, configuration caches and dynamically programmable gate arrays (DPGAs) have been proposed in [BD94], [HW97] and [JC99]. Frequently used configurations can be kept in a configuration cache, which allows for fast reconfiguration and therefore reduces the reconfiguration time overhead. DPGAs are FPGAs with multiple contexts, which allows for fast switching between configurations. But up to now there has still not been any real implementation of a DPGA. This is especially due to the fact that one could simply use a larger FPGA capable of holding all the configurations statically, instead of dealing with the problems associated with DPGAs, configuration caches and dynamic reconfiguration in general. The extra area and cost associated with the configuration caches and multiple contexts of DPGAs acts against one of the main objectives of dynamic reconfiguration, which is the goal of obtaining a higher functional density from a smaller FPGA.

Another approach to reduce the reconfiguration time overhead is to use partial reconfiguration. Partial reconfiguration involves the reconfiguration of parts of the FPGA while leaving the previous configuration for the rest of the FPGA. By only having to reconfigure parts of the FPGA the reconfiguration time is reduced. Some commercial FPGAs such as the Xilinx Virtex II support partial reconfiguration [Xil06a]. To take advantage of this approach it is required that the hardware designs to be configured in the FPGA have parts in common. Advanced EDA tools are often required to identify such common parts of the hardware designs, which results in additional development costs and an increase in the TTM.

#### 2.2.2 Dynamic Hardware/Software Partitioning

Most of the reconfigurable computing devices introduced so far use precompiled configurations, which are statically generated at design time and then used for dynamic reconfiguration at runtime. One exception to this is the generation of alternate configurations at runtime, to increase the fault tolerance of the FPGA as discussed in [HM01]. Here alternate configurations are generated dynamically based on fault location information, such that faulty locations of the FPGA stay unused. This approach suffers from the need for synthesis tool access at runtime. Dynamic reconfiguration can therefore be categorized into static and dynamic generation of configurations.

As pointed out previously hardware/software partitioning is the procedure of determining whether a part of a system should be implemented on a GPP (software) or SPP (hardware). The emergence of dynamically reconfigurable devices such as FPGAs made it possible to perform DHSP, which is the procedure of determining at runtime whether a computation should be performed on a GPP or SPP. Hardware/software partitioning can then be categorized using the following classifications.

- <u>Hardware/Software Partitioning</u>

- 1. Static Partitioning performed at design time

- 2. Dynamic Partitioning performed at runtime

Modern EDA tools have the potential of almost fully automating the process of static hardware/software partitioning. [HT04a], [HT04b] and [Cri05] introduce Critical Blue's automated tools, which take compiled software binary code as input and produce a coprocessor that accelerates the critical kernels of the software. The tool flow consists of first determining the critical kernels of the software the synthesis tools automatically generate a coprocessor that accelerates the critical kernels. The original software code is also automatically modified to perform communication with the coprocessor whenever the critical kernel needs to be executed. These tools therefore show that it is possible to fully automate hardware/software application as input. Advanced EDA tools such as these and the emergence of dynamically reconfigurable computing devices enabled the possibility of moving hardware/software partitioning and the generation of the coprocessors from the design phase to the execution stages of the system.

Such an approach was studied in [SL03] and [LV04]. Here the system architecture consists of a GPP, memory, a dynamic partitioning module and a reconfigurable logic module. Initially the GPP executes the software without any hardware acceleration, while the dynamic partitioning module profiles the software by monitoring the bus accesses between the GPP and the memory. After determining a suitable critical kernel the dynamic partitioning module generates a coprocessor for the critical kernel and configures the reconfigurable logic module with the coprocessor. The software executing on the GPP is also modified to communicate with the coprocessor for the software due to external inputs. Once a different critical kernel is found to be executing more frequently than the one accelerated through the current coprocessor, the reconfigurable logic module can be reconfigured with a new coprocessor to accelerate the more frequent critical kernel. Since the decision of whether a critical kernel should be executed using the GPP or a coprocessor is made at runtime, his approach is called dynamic hardware/software partitioning (DHSP).

One advantage of this approach is that the hardware acceleration of the software is performed seamlessly to the software developer. The software developer does not need to perform any profiling or synthesis of coprocessors. There is also no need to make any platform specific code changes, which preserves the portability of the software. Another advantage of this approach is that it reduces the frequency of reconfiguration and eliminates the reconfiguration time overhead. Always having the ability to execute the critical kernel using the GPP allows for the reconfiguration of the reconfigurable logic module to be performed concurrently, while the GPP executes the software without any hardware acceleration. Due to this, the reconfiguration time becomes a less crucial factor to the performance of the system. Some of the drawbacks of this approach are due to fact that the detection of critical kernels and the dynamic generation of coprocessors require profiling tool access and synthesis tool access at runtime. The approach in [SL03] and [LV04] attempts to solve this problem by using simplified synthesis tools and by using special reconfigurable logic architectures. The simplified synthesis tools were only able to generate coprocessors with purely combinational circuits. Also the extra area, cost and power consumption associated with the dynamic partitioning module outweighs the possible benefits of such an approach. A similar study with similar results and conclusions to [SL03] and [LV04] using a tightly coupled reconfigurable functional unit instead of a loosely-coupled coprocessor was performed in [BC05].

#### 2.3 Summary

This chapter introduced the research area of the study by reviewing the existing literature. First hardware/software co-design was presented as the process of designing hardware and software in parallel to obtain an optimized system. Then it was explained where hardware/software partitioning falls in the design flow and it was explained that hardware/software partitioning is the procedure of determining whether a part of a system should be implemented on a GPP or SPP.

Then an introduction to reconfigurable computing and dynamic reconfiguration was provided. Dynamic reconfiguration is useful in systems where only one configuration is needed at a time. One advantage of dynamically reconfigurable systems is the higher functional density due to the smaller FPGA. Afterwards some applications of dynamic reconfiguration such as runtime system updates, increasing fault tolerance and adaptive decoding were introduced. Dynamic reconfiguration was categorized into systems using statically or dynamically generated configurations. One common problem of dynamic reconfiguration using statically generated configurations is the reconfiguration time overhead. This overhead becomes a significant problem when the frequency of reconfiguration increases. Configuration caches and DPGAs are approaches to solving this problem, but the extra area and cost associated with them outweigh their benefits. Partial reconfiguration can only be used to address the reconfiguration time problem in situations when parts of the hardware designs to be configured in the FPGA are in common.

DHSP was then introduced and an approach using dynamic configuration generation was examined. One advantage of this approach is that it reduces the frequency of reconfiguration and eliminates the reconfiguration time overhead. One of the drawbacks of this approach is that it requires profiling and synthesis tool access at runtime. The extra area, cost and power consumption associated with the DHSP using dynamic configuration generation outweighs the possible benefits of such an approach.

Even though there have been a lot of research projects, which show the advantages of dynamic reconfiguration and DHSP, there have still not been any significantly successful applications of these technologies used in the industry, due to various weaknesses and limitations that were pointed out. Another weakness of these technologies, which was not mentioned earlier, is the lack of high-level simulation tools to evaluate the advantages and disadvantages of using dynamic reconfiguration and DHSP as compared to using static reconfiguration and static hardware/software partitioning respectively.

Currently most managers and system architects avoid using dynamic reconfiguration and DHSP, due to the difficulty of evaluating these techniques as possible design alternatives at the conceptual design phase.

The rest of the study addresses the reconfiguration time overhead and the high frequency of reconfiguration, which are some of the weaknesses and limitations of dynamic reconfiguration and DHSP that were identified in this chapter. The algorithm that determines when a configuration is used for device reconfiguration was defined as the configuration scheduling algorithm. It was pointed out that a simple on demand (OD) configuration scheduling algorithm is currently applied in most systems that use statically generated configurations. In the next chapter an approach for performing DHSP using a new type of configuration scheduling algorithm is proposed.

### **Chapter 3**

### **Execution Time and Configuration Scheduling**

This chapter first looks at the effects of hardware/software partitioning on the execution time of a software application. Then, it is identified how on demand configuration scheduling algorithms, which are used in many dynamically reconfigurable systems, affect the application's execution time. Later on, an approach for performing DHSP using a new type of configuration scheduling algorithm is proposed. After illustrating some benefits of the new configuration scheduling algorithm and analyzing its impact on the application's execution time, it is explained how the rest of the study was approached.

#### 3.1 Hardware/Software Partitioning

This section examines hardware/software partitioning and its impact on the execution time of a software application. As introduced previously, hardware/software partitioning is the procedure of determining whether a part of a system should be implemented on a GPP or SPP. The SPP could be implemented on any IC technology. In the study, a specific type of hardware/software partitioning problem, which arises frequently in embedded system design, is considered. A software application is considered, for which a software profiler is used to identify its critical kernels. Critical kernels are loops in the software code that consume a significant amount of computation time. On average, software applications spend most of their time executing critical kernels, which make up only a small portion of the software code. It is sometimes advantageous to implement the critical kernels using SPPs. This is mostly due to the speedup of the software application and other possible benefits such as reduced energy consumption.

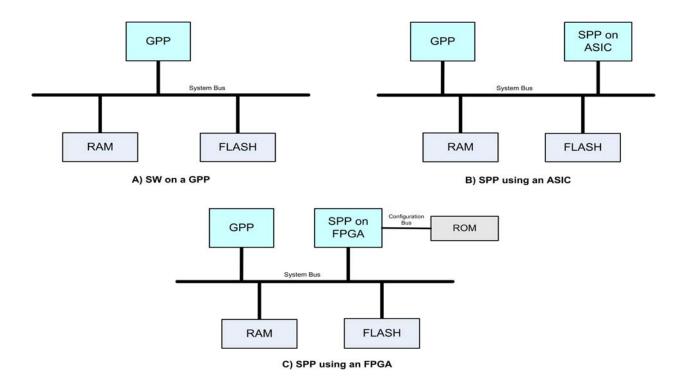

In the study, an embedded system that executes one single threaded software application with N critical kernels is considered. The kernels can either be implemented as software on a GPP or as a SPP using an ASIC or FPGA. The FPGA itself can either be statically or dynamically configured. The rest of the software application, which consists of everything except the critical kernels, is always executed on the GPP. The diagrams of the different system architectures resulting from how the critical kernels are implemented are shown in Figure 3-1. Each system consists of a volatile main memory and a non-volatile memory. In the study the main memory is a random access memory (RAM) and the non-volatile memory is a flash memory. The FPGA is considered to be static RAM (SRAM) based. After the system is powered on, the FPGA requires configurations to be loaded from an external non-volatile memory. In the study, this memory is considered to be a Read Only Memory (ROM).

**Figure 3-1: Kernel Implementation System Architectures**

First, the software application's execution time for the following three design alternatives is examined to analyze the effects of hardware/software partitioning.

- 1. *SW*<sub>system</sub> System with all critical kernels implemented as software on a GPP. This design alternative has the system architecture show in Figure 3-1-A.

- DHW<sub>system</sub> System with all critical kernels implemented as a SPP on a non-configurable, dedicated hardware (DHW). In the study, the DHW corresponds to the ASIC implementation. This design alternative has the system architecture shown in Figure 3-1-B.

- 3. *CHW<sub>stc\_system</sub>* System with all critical kernels implemented as a SPP on configurable hardware (CHW). The system is statically configured, which means that the FPGA is large enough to have all SPPs configured at all times. In the study, the CHW corresponds to the FPGA implementation. This design alternative has the system architecture shown in Figure 3-1-C.

Before the application's execution time for these three design alternatives can be determined, some of the timing parameters and terms used in the study are defined in Table 3-1.

| Term                         | Description                                                                                                                                                                      |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| N                            | Total number of critical kernels in the software application                                                                                                                     |  |  |

| n                            | Denotes a critical kernel out of the total $N$ kernels                                                                                                                           |  |  |

| SW <sub>n</sub>              | software implementation of critical kernel <i>n</i>                                                                                                                              |  |  |

| DHW <sub>n</sub>             | ASIC implementation of critical kernel <i>n</i>                                                                                                                                  |  |  |

| CHW <sub>n</sub>             | FPGA implementation of critical kernel <i>n</i>                                                                                                                                  |  |  |

| t <sub>total</sub>           | Total execution time for entire software application using the various design alternatives                                                                                       |  |  |

| t <sub>code</sub>            | Execution time of the entire software application, when all critical kernels are implemented in software, without any hardware acceleration                                      |  |  |

| $t_{SW_n}$                   | Average execution time of $SW_n$ executing on the GPP                                                                                                                            |  |  |

| $t_{DHW_n}$                  | Average execution time of $DHW_n$                                                                                                                                                |  |  |

| $t_{CHW_n}$                  | Average execution time of $CHW_n$                                                                                                                                                |  |  |

| $t_{start DHW_n / CHW_n}$    | Average time it takes the GPP to initialize the SPP, before the SPP starts executing.<br>This includes all communication overhead such as parameter passing.                     |  |  |

| $t_{finish_{DHW_n / CHW_n}}$ | Average time it takes the GPP to communicate with the SPP, after the SPP completes execution. This includes all communication overheads such as passing back results to the GPP. |  |  |

| NOE <sub>n</sub>             | Number of times $SW_n$ executes during execution of the entire software application                                                                                              |  |  |

| $R_{SW_n}$                   | Ratio of $t_{SW_n} \times NOE_n$ (the entire runtime of critical kernel <i>n</i> in software) to $t_{code}$                                                                      |  |  |

|                              | $R_{SW_n} = \frac{t_{SW_n} \times NOE_n}{t_{code}} $ (1)                                                                                                                         |  |  |

| R <sub>total</sub>           | Ratio of the entire runtime of all critical kernels in software to $t_{code}$                                                                                                    |  |  |

|                              | $R_{total} = \sum_{n=1}^{N} R_{SW_n} $ (2)                                                                                                                                       |  |  |

| $S_{SW_n / DHW_n}$           | Speedup of executing critical kernel $n$ using $DHW_n$ versus using $SW_n$                                                                                                       |  |  |

|                              | $S_{SW_n/DHW_n} = \frac{t_{SW_n}}{t_{DHW_n}} $ (3)                                                                                                                               |  |  |

| $S_{SW_n/CHW_n}$             | Speedup of executing critical kernel $n$ using $CHW_n$ versus using $SW_n$                                                                                                       |  |  |

|                              | $S_{SW_n/CHW_n} = \frac{t_{SW_n}}{t_{CHW_n}} $ (4)                                                                                                                               |  |  |

| <b>Table 3-1:</b> | Hardware/Softw | are Partitioning | Timing Parameters |

|-------------------|----------------|------------------|-------------------|

|                   |                |                  |                   |

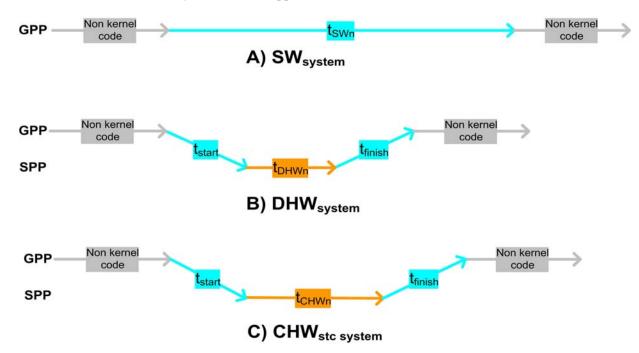

Figure 3-2 illustrates the timing that arises for the different design alternatives when one of the critical kernels needs to be executed by the software application.

Figure 3-2: Hardware/Software Partitioning Timing Diagram

The  $SW_{system}$  design alternative simply executes the kernel using the software implementation. The  $DHW_{system}$  and  $CHW_{stc\_system}$  design alternatives execute the kernel using a SPP implemented on an ASIC or FPGA respectively. By executing the kernel using a SPP, often a shorter execution time is obtained. Since the ASIC implementation of a SPP is faster than an FPGA implementation, the  $DHW_{system}$  design alternative has a shorter execution time than the  $CHW_{stc\_system}$  design alternative. In general, the following relationship can be observed for all critical kernels. It should be noted that when considering execution time the cost of the overheads should also be considered.

$$t_{SW_n} > t_{CHW_n} > t_{DHW_n}$$

(5)

Critical kernels can execute multiple times during the entire execution time of the software application. Using the timing behavior observed in Figure 3-2 and the parameters defined in Table 3-1 Equation 6 was derived to calculate  $t_{total}$  for the design alternatives.

$$t_{total} = t_{code} \left( 1 - R_{total} \right) + t_{comm \ overhead} + t_{HW \ execution}$$

(6)

$t_{comm \ overhead}$  is the total time spent for the communication between GPP and SPPs.  $t_{HW \ execution}$  is the total time the SPPs spend executing. Table 3-2 shows how these two terms can be calculated for each of design alternatives.

| System                       |                           | Equations                                                                                            |     |

|------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|-----|

| <b>DHW</b> <sub>system</sub> | $t_{\it comm\ overhead}$  | $= \sum_{n=1}^{N} \left[ \left( t_{start_{DHW_n}} + t_{finish_{DHW_n}} \right) \times NOE_n \right]$ |     |

|                              | $t_{HW\ execution}$       | $=\sum_{n=1}^{N}\left[t_{DHW_{n}}\times NOE_{n}\right]$                                              | (7) |

|                              |                           | $= \sum_{n=1}^{N} \left[ R_{SW_n} \times t_{code} \times \frac{1}{S_{SW_n / DHW_n}} \right]$         |     |

| CHW <sub>stc_system</sub>    | $t_{\it comm \ overhead}$ | $= \sum_{n=1}^{N} \left[ \left( t_{start_{CHW_n}} + t_{finish_{CHW_n}} \right) \times NOE_n \right]$ |     |

|                              | $t_{HW\ execution}$       | $=\sum_{n=1}^{N}\left[t_{CHW_{n}}\times NOE_{n}\right]$                                              | (8) |

|                              |                           | $=\sum_{n=1}^{N}\left[R_{SW_{n}}\times t_{code}\times\frac{1}{S_{SW_{n}/CHW_{n}}}\right]$            |     |

**Table 3-2: Equation 6 Timing Parameters**

#### 3.2 On Demand Configuration Scheduling Algorithm

When introducing dynamic reconfiguration in Chapter 2, the configuration scheduling algorithm was defined as the algorithm that determines which configuration is used for FPGA reconfiguration. It was pointed out that a simple on demand configuration scheduling algorithm is currently applied in most systems that use statically generated configurations. This section examines how a dynamically reconfigured system that utilizes an on demand configuration scheduling algorithm, effects the execution

time of the previously described software application. This design alternative is denoted as  $CHW_{od\_system}$ . This design alternative has a similar architecture to the  $CHW_{stc\_system}$  design alternative that was illustrated previously in Figure 3-1-C. The main difference of the  $CHW_{od\_system}$  design alternative is that a smaller FPGA is used to increase the functional density of the system. This smaller FPGA can only contain the configuration of one critical kernel's SPP at a time and dynamic reconfiguration is used during the execution of the application to reconfigure the FPGA with the required precompiled configurations. The on demand configuration scheduling algorithm simply reconfigures the FPGA at runtime, whenever a new configuration is needed and is found not to be configuration scheduling algorithm function. This includes a parameter that indicates the kernel the software application is requesting to execute. The pseudo code of the on demand configuration scheduling algorithm singly algorithm is presented in Algorithm 3-1 and the functions in the pseudo code are explained later.

```

/*kernel_required is the kernel the software application is requesting to

execute*/

OD_CSA(kernel_required)

{

if( kernel_required is not equal to currently_configured_kernel () )

{

initiate_reconfiguration(kernel_required)

while(kernel_required is not equal to currently_configured_kernel () )

{do nothing}

}

starting_communication_with_SPP(kernel_required))

wait_until_SPP_is_done_execution()

finishing_communication_with_SPP (kernel_required))

}

```

Algorithm 3-1: On Demand Configuration Scheduling Algorithm Pseudo Code

#### currently\_configured\_kernel()

This function returns the kernel whose SPP is currently configured in the FPGA. It is assumed that the GPP reads from a register in the FPGA to determine which kernel's configuration is currently configured in the FPGA. The execution time of the entire if-statement, which includes a call to this function is defined as  $t_{check}$ . This if-statement checks if the required kernel is currently configured.

#### initiate\_reconfiguration(kernel)

This function initiates the reconfiguration of the FPGA with a new kernel's configuration. In this study it is assumed that the FPGA can be reconfigured without any help from the GPP. Most commercial FPGAs such as the Xilinx Virtex II have this ability by allowing the FPGA to act as the master on the configuration bus [Xil06a]. It is assumed that the GPP writes to a register in the FPGA to set the kernel configuration to use for reconfiguration and to initiate the reconfiguration process of the FPGA. The GPP only initiates the reconfiguration process of the FPGA and is free to do any type of computation, while the FPGA is being reconfigured. The execution time of this function is called  $t_{initiate}$ , which is the time required to initiate the reconfiguration of the FPGA.

#### starting\_communication\_with\_SPP(kernel)

This function initializes the SPP, before the SPP starts executing. This includes all communication such as passing parameters to the SPP. The execution time of this function is  $t_{start_{crw_{s}}}$ .

#### wait\_until\_SPP\_is\_done\_execution()

This function simply waits until the SPP finishes executing. In this study, it is assumed that the GPP goes into a power down mode while the SPP executes and the completion of the SPP is communicated to the GPP via an interrupt. The execution time of this function is  $t_{CHW_a}$ .

#### finishing\_communication\_with\_SPP (kernel)

This function communicates with the SPP, after the SPP completes execution. This includes all communication such as reading back results from the SPP. The execution time of this function is  $t_{finish_{CHV_{e}}}$ .

A while-loop is used to wait until the FPGA is reconfigured with the required kernel's SPP. The execution time of the entire while-loop is called  $t_{config_{CHW_n}}$ , which is the time required to reconfigure the FPGA with CHW<sub>n</sub>.

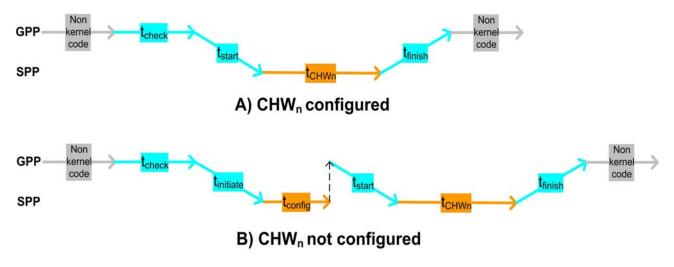

Figure 3-3 illustrates how the on demand configuration scheduling algorithm presented in Algorithm 3-1 behaves. It shows the two different scenarios that can arise for the  $CHW_{od\_system}$  design alternative, when one of the critical kernels needs to be executed by the software application.

Figure 3-3: On Demand Configuration Scheduling Algorithm

Figure 3-3-A shows the timing for the scenario when the required configuration is already configured in the FPGA. The timing for this scenario is similar to the timing of the  $CHW_{stc\_system}$  design alternative. Figure 3-3-B shows the timing for the scenario when the required configuration is not configured in the FPGA. In this scenario the on demand configuration scheduling algorithm first initiates the reconfiguration of the FPGA and then waits until the reconfiguration is completed. Afterwards the critical kernel is executed using the SPP configured on the FPGA. Whenever a critical kernel *n* is required, it causes the scenario in Figure 3-3-B to occur with a probability, which is defined as  $P_{CHW_n not cfg_{ODCSA}}$ . The probability of the scenario in Figure 3-3-A then simply becomes  $1 - P_{CHW_n not cfg_{ODCSA}}$ . Using the timing behavior observed in Figure 3-3 Equation 9 was derived to calculate  $t_{total}$  for the  $CHW_{od\_system}$  design alternative.

$$t_{total} = t_{code} \left(1 - R_{total}\right) + t_{check} \sum_{n=1}^{N} \left[NOE_{n}\right] + \sum_{n=1}^{N} \left[P_{CHW_{n} not \ cfg \ oDCSA} \times \left(t_{config \ CHW_{n}} + t_{initiate}\right) \times NOE_{n}\right] + t_{comm \ overhead} + t_{HW \ execution}$$

(9)

where

$$t_{comm \ overhead} = \sum_{n=1}^{N} \left[ \left( t_{start \ CHW_n} + t_{finish \ CHW_n} \right) \times NOE_n \right]$$

$$t_{HW \ execution} = \sum_{n=1}^{N} \left[ R_{SW_n} \times t_{code} \times \frac{1}{S_{SW_n}/CHW_n} \right]$$

$$= \sum_{n=1}^{N} \left[ t_{CHW_n} \times NOE_n \right]$$

It was pointed out previously that the benefit of using  $CHW_{od\_system}$  over  $CHW_{stc\_system}$  is the fact that the former has a higher functional density due to the smaller FPGA. The smaller FPGA is advantageous since it results in reduced unit cost, power and area. It is now possible to compare the  $CHW_{od\_system}$  and  $CHW_{stc\_system}$  design alternatives by looking at the software application's execution time of both systems. The  $CHW_{od\_system}$  design alternative has a longer execution time since it has some extra terms in its equation for  $t_{total}$ . These terms are shown in Equation 10, which simply subtracts Equation 6 from Equation 9.

$$t_{total_{CHW}} - t_{total_{CHW}} =$$

$$t_{check} \sum_{n=1}^{N} [NOE_{n}] +$$

$$\sum_{n=1}^{N} \left[ P_{CHW_{n}} \operatorname{not} cfg_{ODCSA} \times \left( t_{config_{CHW_{n}}} + t_{initiate} \right) \times NOE_{n} \right]$$

(10)

It is reasonable to neglect  $t_{initiate}$  and  $t_{check}$  in Equation 10, since it can be assumed that these terms are much smaller than  $t_{config_{CHW_n}}$ . By doing so Equation 11 is obtained, which shows the main factors that contributes to the difference in execution time between the  $CHW_{od\_system}$  and  $CHW_{stc\_system}$  design alternatives.

$$t_{total_{CHW}} - t_{total_{CHW}} \approx \sum_{n=1}^{N} \left[ P_{CHW_{n}} \operatorname{not} cfg_{ODCSA} \times t_{config_{CHW_{n}}} \times NOE_{n} \right]$$

(11)

Equation 11 shows that  $t_{config_{CHW_n}}$  is one of the main problems of the on demand configuration scheduling algorithm, which confirms the results in the current literature as pointed out in Chapter 2 as the reconfiguration time overhead. If  $t_{config_{CHW_n}}$  cannot be kept short, it increases the execution time of the  $CHW_{od\_system}$  design alternative over the execution time of the  $CHW_{stc\_system}$  design alternative to a point where the performance decrease of the former outweighs its benefits of providing higher functional density. This reconfiguration time overhead is especially a problem in embedded systems where tight timing constraints must be met. The reconfiguration time is a function of the architecture and size of the FPGA but the FPGA architectures used currently don't provide a short reconfiguration time [Tes05]. It is also not possible to reduce the size of the FPGA beyond a point where the hardware design of one of the SPPs becomes too large for the FPGA.

From Equation 11 it can be seen that another approach to reduce the main difference in execution time between the  $CHW_{od\_system}$  and  $CHW_{stc\_system}$  design alternatives is to reduce  $P_{CHW_n not cfg_{ODCSA}}$ . Reducing  $P_{CHW_n not cfg_{ODCSA}}$  corresponds to reducing the frequency of reconfiguration (FRC), which was already pointed out as a possible technique to reduce the negative effects of the reconfiguration time overhead in Chapter 2. It was also pointed out that due to the inherent inflexibility of the on demand configuration scheduling algorithm it is not possible to reduce the frequency of reconfiguration. The on demand configuration scheduling algorithm has no other alternative than to reconfigure the FPGA with the required configuration, when a configuration is needed and is found not to be currently configured in the FPGA. In the case of the  $CHW_{od\_system}$  design alternative, the frequency of reconfiguration is only a function of the behavior of the software application. A software application with a high frequency of

different critical kernels being executed after another will have a high frequency of reconfiguration. This is due to the fact that the on demand configuration scheduling algorithm has no alternative than to reconfigure the FPGA whenever the previously executed critical kernel differs from the current one. In order to address these weaknesses of the on demand configuration scheduling algorithm a new type of configuration scheduling algorithm is proposed in the next section.

### **3.3 Configuration Scheduling Algorithms for DHSP**

In the previous section, two of the major problems of the on demand configuration scheduling algorithm were pointed out. The first problem is the reconfiguration time overhead and the second one is the inherent inflexibility of the on demand configuration scheduling algorithm, which makes it impossible to reduce the frequency of reconfiguration. In this section, a configuration scheduling algorithm for performing DHSP is proposed to address the weaknesses of the on demand configuration scheduling algorithm are illustrated and then it is examined how the DHSP configuration scheduling algorithm affects the execution time of the previously described software application.

In Chapter 2, the approach in [SL03] and [LV04], which performs DHSP using dynamically generated configurations, was studied. When compared to the on demand configuration scheduling algorithm this approach has the advantage of being able to almost eliminate the reconfiguration time overhead. The ability of this approach to execute the critical kernel using both software and a SPP, allows for the reconfiguration of the FPGA to be performed concurrently, while the GPP executes the kernels in software without any hardware acceleration. Due to this fact the reconfiguration time becomes a less crucial factor to the performance of the system. The flexibility of being able to execute a critical kernel using software or using a SPP also makes it possible to adjust the frequency of reconfiguration. The major drawback of this approach is that it requires profiling and synthesis tool access at runtime.

When developing the DHSP configuration scheduling algorithm it was noted that the on demand configuration scheduling algorithm uses statically generated configurations and that the approach in [SL03] and [LV04] performs DHSP using dynamically generated configurations. It was then realized that DHSP can be further categorized by differentiating between statically and dynamically generated configurations as shown below:

# • Hardware/Software Partitioning

- 1. Static Partitioning performed at design time

- 2. Dynamic Partitioning performed at runtime

- a. Static generation Precompiled configurations

- b. Dynamic generation Configurations generated at runtime

It is then proposed that it is possible to develop a configuration scheduling algorithm to perform DHSP using statically generated configurations. This approach combines the advantages and eliminates the major drawbacks of both the on demand configuration scheduling algorithm and the approaches studied in [SL03] and [LV04]. The DHSP configuration scheduling algorithm eliminates the need for profiling and synthesis tool access at runtime, by using statically generated configurations. By performing DHSP, the configuration scheduling algorithm can also eliminate the reconfiguration time overhead and reduce the frequency of reconfiguration. Next these points are explained in further detail.

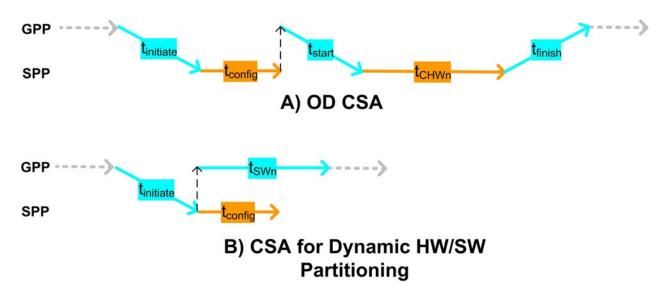

In the study DHSP is the procedure of determining at runtime whether a critical kernel should be executed using software or using a SPP. A design alternative is proposed, which utilizes a new configuration scheduling algorithm to perform DHSP using statically generated configurations. This design alternative has the same system architecture as the  $CHW_{od\_system}$  design alternative, which was explained previously. Therefore, it provides the same benefit of increased functional density from a smaller FPGA. And as for the  $CHW_{od\_system}$  design alternative this smaller FPGA can only contain the configuration of one critical kernel's SPP at a time. But the DHSP configuration scheduling algorithm is not as simple as the on demand configuration is needed. Instead, whenever the software application needs to execute a critical kernel, the configuration scheduling algorithm is responsible to select at runtime if it should be executed in software or using the SPP. The ability of this approach to execute the critical kernel using both the software and SPP, allows for the reconfiguration of the FPGA to be performed concurrently while the GPP executes the software without any hardware acceleration. This is illustrated in Figure 3-4 by comparing the scenario where a required configuration is not found in the FPGA.

**Figure 3-4: Concurrent Reconfiguration**