# Concurrent Implementation of Packet Processing Algorithms on Network Processors

$\mathbf{b}\mathbf{y}$

Mark Groves

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Mathematics in Computer Science

Waterloo, Ontario, Canada, 2006

©Mark Groves 2006

## AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A THESIS

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Mark Groves

## Abstract

Network Processor Units (NPUs) are a compromise between software-based and hardwired packet processing solutions. While slower than hardwired solutions, NPUs have the flexibility of software-based solutions, allowing them to adapt faster to changes in network protocols.

Network processors have multiple processing engines so that multiple packets can be processed simultaneously within the NPU. In addition, each of these processing engines is multi-threaded, with special hardware support built in to alleviate some of the cost of concurrency. This hardware design allows the NPU to handle multiple packets concurrently, so that while one thread is waiting for a memory access to complete, another thread can be processing a different packet. By handling several packets simultaneously, an NPU can achieve similar processing power as traditional packet processing hardware, but with greater flexibility.

The flexibility of network processors is also one of the disadvantages associated with them. Programming a network processor requires an in-depth understanding of the hardware as well as a solid foundation in concurrent design and programming. This thesis explores the challenges of programming a network processor, the Intel IXP2400, using a single-threaded packet scheduling algorithm, SI-WF<sup>2</sup>Q, as a sample case. SI-WF<sup>2</sup>Q is a GPS approximation scheduler with constant time execution. The thesis examines the process of implementing the algorithm in a multi-threaded environment, and discusses the scalability and load-balancing aspects of such an algorithm. In addition, optimizations are made to the scheduler implementation to improve the potential concurrency. The synchronization primitives available on the network processor are also examined, as they play a significant part in minimizing the overhead required to synchronize memory accesses by the algorithm.

#### Acknowledgments

First and foremost, I would like to thank my supervisor Martin Karsten. His guidance kept me on track through numerous setbacks and his insight into the problems I encountered was invaluable in finding solutions. I would also like to thank Peter Buhr for reviewing my early drafts and providing feedback that made this thesis more comprehensible, and my thesis readers for their comments on my completed work. Finally, I would like to thank my family and Alex for their love and support.

# Contents

| 1        | Intr                | oduction                                                                                                                                                                                                                                                                             |

|----------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1                 | Motivation                                                                                                                                                                                                                                                                           |

|          | 1.2                 | Outline                                                                                                                                                                                                                                                                              |

| <b>2</b> | Net                 | work Processors                                                                                                                                                                                                                                                                      |

|          | 2.1                 | General Architecture                                                                                                                                                                                                                                                                 |

|          |                     | 2.1.1 General NPU Architectures                                                                                                                                                                                                                                                      |

|          |                     | 2.1.2 Trade-Offs                                                                                                                                                                                                                                                                     |

|          | 2.2                 | Network Processors                                                                                                                                                                                                                                                                   |

|          |                     | 2.2.1 Agere Payload Plus 10                                                                                                                                                                                                                                                          |

|          |                     | 2.2.2 IBM PowerNP Series                                                                                                                                                                                                                                                             |

|          |                     | 2.2.3 Motorola C-5 Series 10                                                                                                                                                                                                                                                         |

|          |                     | 2.2.4 Intel IXP                                                                                                                                                                                                                                                                      |

|          | 2.3                 | Intel IXP2400                                                                                                                                                                                                                                                                        |

|          |                     |                                                                                                                                                                                                                                                                                      |

| 3        | Rela                | nted Work 15                                                                                                                                                                                                                                                                         |

| 3        | <b>Rel</b> a<br>3.1 | 15     15       Related Hardware     15                                                                                                                                                                                                                                              |

| 3        |                     |                                                                                                                                                                                                                                                                                      |

| 3        |                     | Related Hardware                                                                                                                                                                                                                                                                     |

| 3        |                     | Related Hardware    15      3.1.1    Coprocessors    15                                                                                                                                                                                                                              |

| 3        |                     | Related Hardware153.1.1Coprocessors153.1.2Graphics Processors16                                                                                                                                                                                                                      |

| 3        |                     | Related Hardware153.1.1Coprocessors153.1.2Graphics Processors163.1.3Cell Broadband Engine (BE)16                                                                                                                                                                                     |

| 3        | 3.1                 | Related Hardware153.1.1Coprocessors153.1.2Graphics Processors163.1.3Cell Broadband Engine (BE)163.1.4The Success of Compilers and Higher Level Languages20                                                                                                                           |

| 3        | 3.1                 | Related Hardware153.1.1Coprocessors153.1.2Graphics Processors163.1.3Cell Broadband Engine (BE)163.1.4The Success of Compilers and Higher Level Languages20Network Processor Applications20                                                                                           |

| 3        | 3.1                 | Related Hardware153.1.1Coprocessors153.1.2Graphics Processors163.1.3Cell Broadband Engine (BE)163.1.4The Success of Compilers and Higher Level Languages20Network Processor Applications203.2.1Video Streaming21                                                                     |

| 3        | 3.1                 | Related Hardware153.1.1Coprocessors163.1.2Graphics Processors163.1.3Cell Broadband Engine (BE)163.1.4The Success of Compilers and Higher Level Languages20Network Processor Applications203.2.1Video Streaming213.2.2Firewalls21                                                     |

| 3        | 3.1                 | Related Hardware183.1.1Coprocessors183.1.2Graphics Processors163.1.3Cell Broadband Engine (BE)163.1.4The Success of Compilers and Higher Level Languages20Network Processor Applications203.2.1Video Streaming213.2.2Firewalls213.2.3Software-Based Routers22                        |

| 3        | 3.1                 | Related Hardware153.1.1Coprocessors163.1.2Graphics Processors163.1.3Cell Broadband Engine (BE)193.1.4The Success of Compilers and Higher Level Languages20Network Processor Applications203.2.1Video Streaming213.2.2Firewalls213.2.3Software-Based Routers223.2.4Overlay Networks25 |

|          |      | 3.3.1  | Programming Language Research                                                                   |

|----------|------|--------|-------------------------------------------------------------------------------------------------|

|          |      | 3.3.2  | Task Partitioning    26                                                                         |

| 4        | Soft | ware ] | Development 29                                                                                  |

| _        | 4.1  |        | pping for the IXP2400                                                                           |

|          |      | 4.1.1  | IXA Portability Framework and Dispatch Loops                                                    |

|          |      | 4.1.2  | Programming Languages                                                                           |

|          |      | 4.1.3  | Thread Arbitration                                                                              |

|          | 4.2  |        | ronization Within a $\mu$ Engine                                                                |

|          |      | 4.2.1  | Signals                                                                                         |

|          |      | 4.2.2  | Content Addressable Memory                                                                      |

|          | 4.3  | Synch  | ronization Among $\mu$ Engines $\tilde{1}$                                                      |

|          |      | 4.3.1  | Signals                                                                                         |

|          |      | 4.3.2  | Shared Memory                                                                                   |

|          | 4.4  | Synch  | ronization Between $\mu$ Engines and the XScale Processor $\ldots \ldots \ldots \ldots 38$      |

|          |      | 4.4.1  | Shared Memory                                                                                   |

|          |      | 4.4.2  | Rings and Queues                                                                                |

|          |      | 4.4.3  | Variables and Registers                                                                         |

|          |      | 4.4.4  | Signals                                                                                         |

| <b>5</b> | Sch  | eduler | Architecture 41                                                                                 |

| -        | 5.1  |        | t Scheduling                                                                                    |

|          | 0    | 5.1.1  | A General Processor Sharing Scheduler                                                           |

|          |      | 5.1.2  | Timestamp Schedulers                                                                            |

|          |      | 5.1.3  | SI-WF <sup>2</sup> Q: A Fair Timestamp Scheduler with Constant Execution $\dots \dots \dots 42$ |

|          | 5.2  | Sched  | uler Operations                                                                                 |

|          |      | 5.2.1  | Insertion                                                                                       |

|          | 5.3  | Sched  | uler Versions                                                                                   |

|          |      | 5.3.1  | Original Scheduler                                                                              |

|          |      | 5.3.2  | Packet-Only High ISTW                                                                           |

|          |      | 5.3.3  | Low ISTW Only Scheduler                                                                         |

|          | 5.4  | Gener  | al Structure                                                                                    |

|          |      | 5.4.1  | Queues                                                                                          |

|          |      | 5.4.2  | Virtual Time                                                                                    |

|          |      | 5.4.3  | Memory                                                                                          |

|          | 5.5  | Partit | ioning the Microblocks                                                                          |

| 6        | Sch  | eduler | Implementation 57                                                                               |

|          | 6.1  |        | mentation of the Low-Only Scheduler                                                             |

|          |      | 6.1.1  | Inserting Packets into Flows                                                                    |

|          |      |        |                                                                                                 |

|   |     | 6.1.2 Low ISTW                                 | ;9         |

|---|-----|------------------------------------------------|------------|

|   |     | 6.1.3 Virtual Time Implementation              | 51         |

|   | 6.2 | Service Guarantees                             | 51         |

|   |     | 6.2.1 Terms and Definitions                    | 51         |

|   |     | 6.2.2 Service Rate Guarantees                  | 52         |

|   | 6.3 | Synchronization                                | <b>j</b> 4 |

|   |     | 6.3.1 Classifying flows                        | <b>j</b> 4 |

|   |     | 6.3.2 Accessing Flow Data                      | 55         |

|   |     | 6.3.3 Accessing the ISTW Buckets               | 5          |

|   |     | 6.3.4 Accessing the Stratified FIFO            | 6          |

|   |     | 6.3.5 Lock Hierarchy                           | ;7         |

|   | 6.4 | Data Parallelism                               | ;8         |

|   | 6.5 | Code Analysis                                  | ;8         |

|   | 6.6 | Optimizations                                  | ;9         |

|   |     | 6.6.1 Maximal Use of the SRAM Queue Controller | ;9         |

| 7 | Con | clusions and Future Work 7                     | '1         |

|   | 7.1 | Conclusions                                    | '1         |

|   | 7.2 | Experiences                                    | '2         |

|   | 7.3 | Future Work                                    | '3         |

|   |     | 7.3.1 Caching Flows                            | '3         |

|   |     | 7.3.2 Implementing the Packet-Only High ISTW   |            |

|   |     | 7.3.3 Future of Network Processors             |            |

|   |     |                                                |            |

# List of Tables

| 2.1 | Intel IXP2400 Memory Access Times                                            | 14 |

|-----|------------------------------------------------------------------------------|----|

| 5.1 | Packet Processing Operations and Number of Memory Accesses Required $\ldots$ | 53 |

| 6.1 | Contents of the Packet Data Structure                                        | 60 |

| 6.2 | Contents of the Flow Data Structure                                          | 60 |

| 6.3 | Number of Instructions and Memory Accesses per Scheduler Operation           | 69 |

| 6.4 | Number of Instructions and Memory Accesses for Optimized Scheduler           | 70 |

# List of Figures

| 2.1  | A General NPU Architecture with Data and Control Paths                          | 6  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Concurrent Execution Between 8 Threads                                          | 7  |

| 2.3  | Processor Configurations and Processing Latency                                 | 9  |

| 2.4  | Block diagram of the Intel IXP2400 Network Processor                            | 12 |

| 2.5  | Block diagram of an IXP2400 $\mu$ Engine                                        | 13 |

| 3.1  | Block Diagram of the Multiple Processors in a GPU                               | 16 |

| 3.2  | Interaction Layers of Graphics Programming Languages                            | 19 |

| 4.1  | Dispatch Loop Code Example                                                      | 30 |

| 4.2  | Dispatch Loop Block Example                                                     | 30 |

| 4.3  | Pseudocode for a CAM table locking mechanism                                    | 34 |

| 4.4  | Signalling within and among $\mu$ Engines to ensure ordered packet transmission | 36 |

| 4.5  | Pseudocode for a critical section lock using atomic memory operations           | 37 |

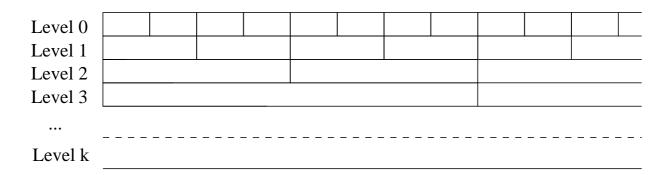

| 5.1  | Stratified Timer Wheels                                                         | 42 |

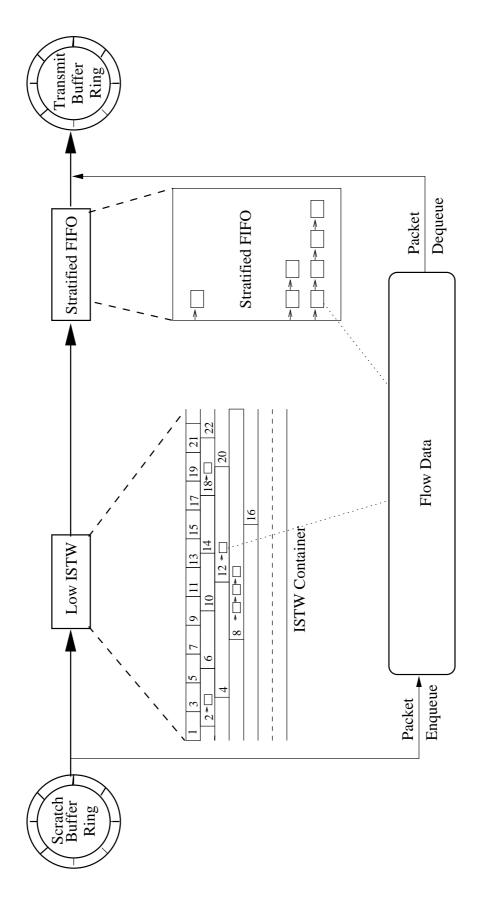

| 5.2  | The Interleaved Stratified Timer Wheels Data Structure                          | 43 |

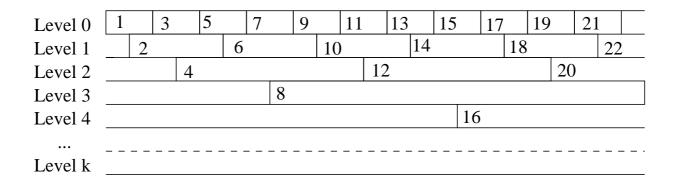

| 5.3  | Simplified Scheduler Structure                                                  |    |

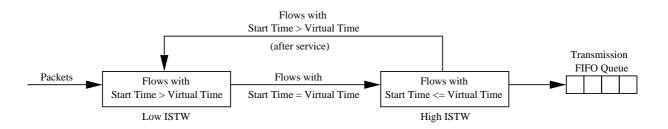

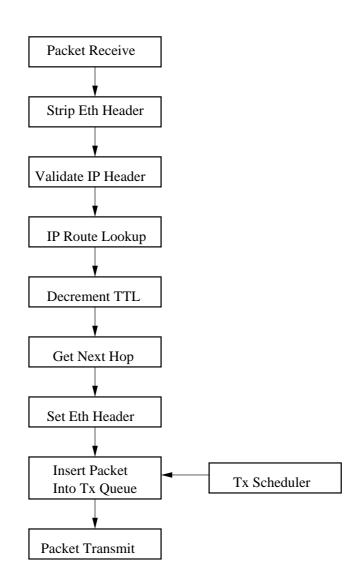

| 5.4  | Structure of the Packet-Only High ISTW Scheduler                                | 47 |

| 5.5  | Pseudocode for Simplified transfer_eligible on Low ISTW                         | 48 |

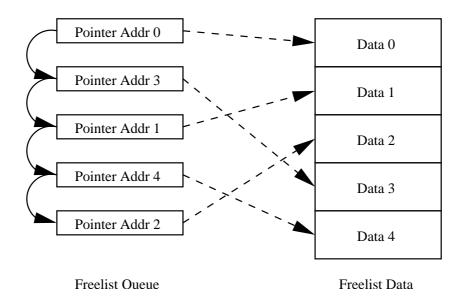

| 5.6  | Freelist using Queues                                                           | 51 |

| 5.7  | List of an Example Data Structure using Queue Pointers                          | 51 |

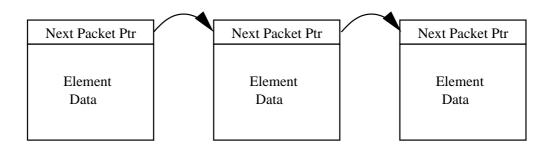

| 5.8  | Microblocks Required for Packet Processing in a General Router                  | 54 |

| 5.9  | Microblocks for the Implementation of the FVC Scheduler                         | 55 |

| 5.10 | $\mu$ Engine Layout of Packet Processor in Dual IXP Configuration               | 56 |

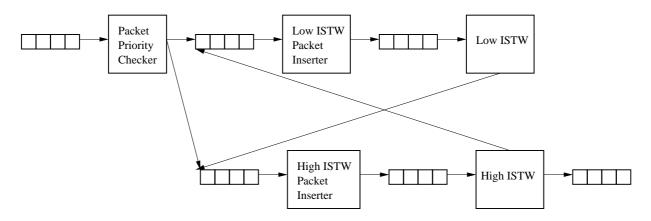

| 6.1  | General Packet Flow Through the Scheduler                                       |    |

| 6.2  | Packet Insertion Pseudocode                                                     |    |

| 6.3  | Low ISTW Pseudocode                                                             |    |

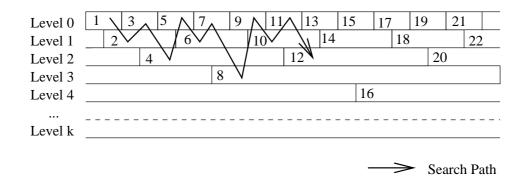

| 6.4  | An Example Search Path for the find_next_flow Operation                         |    |

| 6.5  | Arbitration and Synchronization between Threads                                 | 67 |

# Chapter 1 Introduction

There are two main solutions for processing packets in a networked environment. First, using a general-purpose processor, like the processor that powers a desktop computer. This solution has the advantage that it is cheap, has a large software base, can deal with virtually any network protocols and can be easily upgraded with new protocols. These advantages mean that software-based packet processing products can be put out on the market quickly, and easily upgraded with additional functionality.

However, the general processor solution is unable to keep up with improvements in network speeds due to the comparatively slow improvements in the processor and the data bus that connects it to memory. This problem is due to what is termed the *memory wall* [51], alluding to the fact that data-bus speeds and corresponding memory speeds do not increase at the same rate as processor speeds. With each upgrade in processor speed, this means that more processor cycles are spent waiting for the results of memory accesses to complete and return to the processor via the memory bus. Since all network data must flow through the bus to the CPU, the bus becomes the limiting factor in performance, without some direct connection between the network controller and CPU.

Packet processing tasks have also become more complex. Initially, routers just had to decrement the Time-To-Live field, perform a route lookup and recompute a checksum. These simplistic tasks could be easily handled, albeit slowly, using a general-purpose processor solution. With new protocols and methods of communication, some routers now have to handle encrypted packets, Quality of Service (QoS), as well as evaluate congestion and perform other computationally intensive operations. While general processors are designed to be more multi-purpose, they cannot handle the speed required by fast data networks.

The inability of general processors to handle packets at high rates leads to the second, and now preferred, solution for high-speed packet processing: Application Specific Integrated Circuits (ASICs). These customized ASICs are able to handle packets at wire-speed, which is the most important requirement of packet processing solutions. Unfortunately, the high-speed data buses necessary to achieve line speed make the ASIC a very expensive solution, even when produced in high volume. Also, ASICs are slow to design and develop, and thus have a longer time-to-market, making them cost-inefficient with respect to production and manufacturing. Given the rate of speed increases in a network, each ASIC platform has a short lifetime in the market. Finally, since these are hardwired platforms, they are inflexible, making them unable to handle changes to protocols or have additional functionality attached after manufacturing. Nevertheless, ASICs represent the only solution that is able to handle packets at high speed and so the Internet has come to rely on these devices.

Following the increase in network speeds, new applications and services have been developed to utilize the newly available bandwidth. Voice packets travel over IP networks, packets can be tagged with additional data to help classify them for different services and proxies monitor web site requests to reduce the amount of traffic at the site. These real-time applications have minimum requirements that the original best-effort nature of the Internet was not designed for, and so this functionality must now become part of the functionality in Internet routers. Developing hardwired solutions for all these tasks is possible, but with each new service or extension of existing service, a new piece of hardware needs to be designed, tested and manufactured. In contrast, software based solutions on a typical PC machine can be programmed to execute any of these tasks, but again, not at the high transmission speed required by today's networks.

The introduction of Network Processor Units (NPUs) in the late 1990s creates a third solution for packet processing products. Network processors are a hybrid between the two previous solutions, making it possible to develop software based solutions as on a PC-based packet processor, while still using specialized hardware capable of handling packet processing tasks at the current wire-speed of networks. Additionally, because all processing is software based, there is no need to develop new expensive hardware (except for significant changes in network design), which keeps the cost and time-to-market small. Finally, since the same hardware can be used for many diverse applications, these network products will hopefully become standard commodities, produced in high volume, which should drive costs even lower.

However, the biggest challenge in using NPUs is programming them. Development environments are still in their infancy, as are the programming languages for these devices. Designing processing applications is difficult because the application must be divided into discrete tasks executed in limited bursts. Moreover, managing the multiple forms of parallelism is very difficult for all but the most basic processing tasks, but this parallelism is necessary to achieve high levels of performance. For example, there is often a complex interaction of tasks and memory accesses that must be balanced to be able to reach the maximum processing speed without overloading any of the components. In these cases, even a very simple and straightforward task can become extremely complex when attempting to achieve maximum performance.

# 1.1 Motivation

This thesis examines the complexity of programming NPUs through the development of a novel scheduling algorithm [28] on the Intel IXP2400 Network Processor [7], and the adjustments and optimizations necessary to fully utilize the hardware. The algorithm uses sets of timer wheels in a pipeline to schedule packets in constant time, which is shown to translate quite well to the IXP2400 architecture. The two main steps of this thesis are translating the sequential packet scheduling algorithm to a parallel algorithm that uses the multiple threads in the IXP2400, and the implementation of the multi-threaded algorithm in Intel's network processor assembly programming language. In particular, this thesis details the concurrency and synchronization requirements of porting the scheduler to a multi-threaded algorithm. Caching and other optimizations are also examined in order to develop an understanding of the tradeoffs involved with managing shared data and processing tasks.

# 1.2 Outline

This thesis is structured as follows: Chapter 2 give a brief background on network processors, especially the IXP2400. Chapter 3 provides a brief overview of related technology and the work being done with network processors. Chapter 4 presents an overview of the concurrency mechanisms available on the IXP2xxx series of network processors and Chapter 5 discusses possible adaptations of the original scheduler design and details the process of transforming the algorithm to a multi-threaded one and implementing it. Chapter 6 details the specific implementation of one adaptation, as well as some bottlenecks of the scheduler and what optimizations are possible to improve the packet processing rates. Finally, Chapter 7 looks at the conclusions of this work and details future plans and further improvements that could be made to the system.

# Chapter 2

# **Network Processors**

# 2.1 General Architecture

A Network Processing Unit (NPU) is a hybrid between a general purpose processor and a hardwired architecture. Their goal is to achieve some level of general programmability while simultaneously achieving similar performance to ASIC-based packet processors. To reach this goal, compromises are made between the two objectives. For example, NPUs have a special instruction set to assist with common packet processing tasks, such as striping a packet of its headers, classifying them or performing route lookups. In addition to a special instruction set, NPUs also have specialized hardware blocks to aid in packet processing, but that are kept separate from the processors in order to maintain generality. Finally, rather than the customized memory and data buses in a hardware router, network processors use a combination of commodity and specialized memory to speed up memory accesses.

#### 2.1.1 General NPU Architectures

As of yet, no general consensus has been reached on what hardware is necessary to achieve optimal packet processing, but there are some trends. Currently, network processor manufacturers attempt to distinguish themselves within the market by the feature set of their network processors, which unfortunately results in only a few commonalities in their architectures. All NPUs have special hardware blocks to speed up common network processing tasks, but the tasks are usually different. These hardware blocks can be used to perform complex cryptographical calculations, calculate checksums or generate timestamps. Since handling traffic regularly involves looking up the final destination of a packet and determining what the next hop is, some network processors have special hardware tables to aid in the lookup process. Also, to schedule and shape the traffic, there are often hardware assisted memory queues for storing packets. With so many choices and the tradeoffs among different NPUs, the needs of the user largely define the best network processor to use in any given solution. However, the choice of hardware can also correspondingly reduce

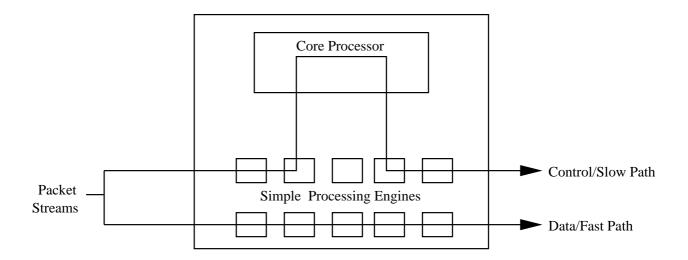

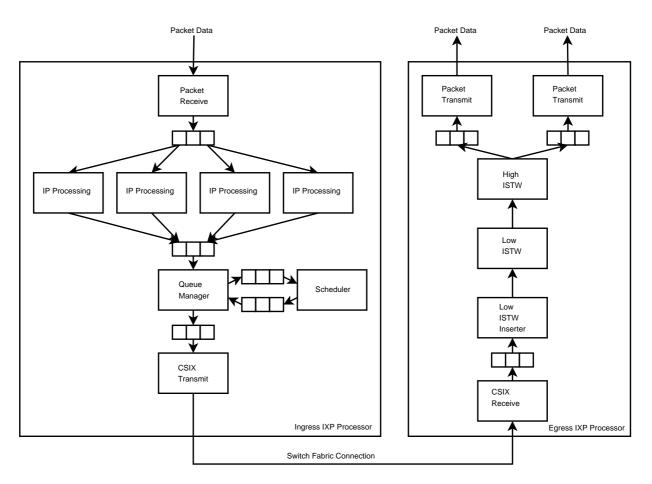

Figure 2.1: A General NPU Architecture with Data and Control Paths

the flexibility available to the user, since the lack of general consensus regarding architectures can lock the user into a specific brand of network processor.

The common trends in network processor architectures are all due to the similar obstacles that must be overcome. First of all, the constant increase in network speeds, faster than increases in processor speeds, forces designers to use any inherent concurrency available when processing packets. During packet processing, each packet generally gets the same treatment as it travels through a processor. In addition, this treatment, while complicated, is still relatively straightforward. This straight-forward packet processing is generally called the fast or data path and is the path that the vast majority of packets travel on the way to their final destination. To handle the high volume of traffic and the relatively simple requirements of processing it, NPU designers often use multiple simple processing engines to handle this traffic. Possessing a small storage space for instructions, these engines can perform the basic processing for the fast path, and perform it on multiple packets simultaneously. Besides the data path, there is also the control path. The control path handles packets that are destined for the packet processor itself, such as Border Gateway Protocol (BGP) routing updates. These packets are handled using more complex algorithms than the minimal fast-path processors can provide. These control packets are often routed to a more general processor, which is either part of the NPU or on a separate card. Figure 2.1 illustrates how the data and control paths are handled within an NPU.

Another common obstacle is that any memory access takes a certain number of cycles to look up and return a result via a separate bus, time during which the processor is effectively idle. It is the need to minimize the number of cycles taken up by memory accesses that necessitates the specialized, expensive hardware in hard-wired routers. Many network processors attempt to

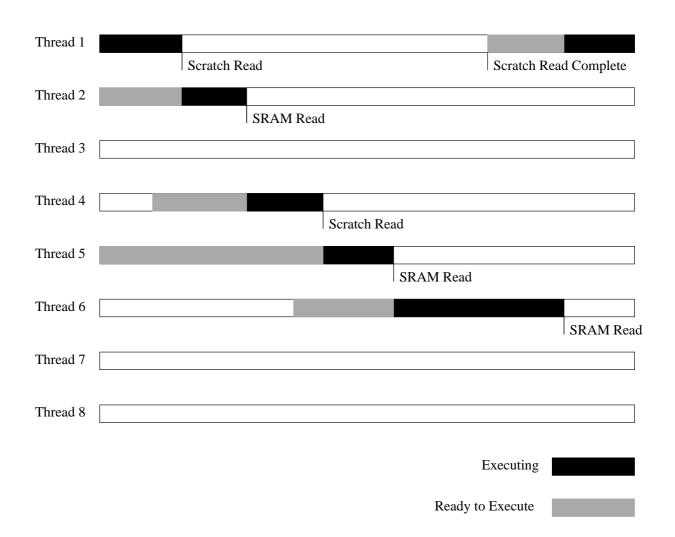

Figure 2.2: Concurrent Execution Between 8 Threads

ameliorate this cost by using multi-threaded processing engines. Any time a memory access is performed, the currently executing thread can perform a low-cost context switch to a thread that can perform useful work (as shown in Figure 2.2). These threads are hardware assisted, meaning that each thread has dedicated registers for storing its context information, so a context switch takes only a couple of processing cycles. By performing a context switch whenever the processing engine needs to wait for data, developers are able to take advantage of memory access latency to concurrently process other packets.

A network processor with multiple fast-path processing engines can simultaneously work on several packets, one in each engine. When each engine has multiple threads, even more packets can be processed concurrently. It is this parallel packet processing that allows a network processor to achieve the line speed processing required to handle today's network traffic. Hardware routers also distribute the workload using multiple processing engines, but on a different scale. For example, a CISCO 7000 series router [47], uses a Route/Switch Processor (RSP) for handling routing protocol tasks. The RSP manages the routing table and distributes it among the line cards that make up the router. The line cards handle data-packet routing based on the tables provided by the RSP and pass packets among themselves using a very high-speed switching backplane. This distributed switching is how hardware routers achieve their packet processing rates.

#### 2.1.2 Trade-Offs

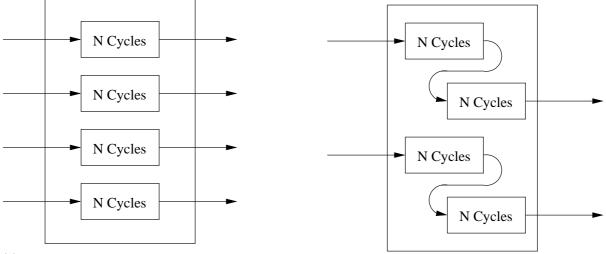

There are some trade-offs that occur when using multiple processing engines. For very simple processing, all of the processors can perform the same set of instructions on each packet. However, if the processing is more complicated, the processors can be put into a pipelined formation, with a processing engine performing a subset of the instructions on a packet before passing it to the next engine in line to execute a different set of instructions on the packet. The pipeline formation has the disadvantage of greatly increasing the latency that a packet experiences due to the number of instructions that are executed. For example, if each of the I processors performs the same N instructions on a packet (a parallel processing setup shown in Figure 2.3(a)), then the total processing latency that any packet experiences is N. However, in a pipelined setup of I processors (see Figure 2.3(b)), the latency becomes I \* N. The more hops a packet makes, the more latency may occur. Packets also experience other types of latency during processing, for example, the latency experienced during memory accesses. A network processor may switch out a thread when a memory access is performed so the processing time is unchanged, but the packet processing is delayed while other threads on the processing engine continue executing. Also, in a pipelined configuration, packets are generally queued up waiting to be processed at the next microprocessor in the pipeline, which adds to the latency a packet experiences. This latency is not a significant problem in file transfers and similar traffic, or even in media streaming where the latency is only experienced at the very start. However, in real-time applications, such as VoIP, the total latency must be kept below a certain level to provide acceptable results. It is important to remember that

(a) Parallel Configuration with N Cycle Latency tency (b) Pipelined Configuration with 2N Cycle Latency

Figure 2.3: Processor Configurations and Processing Latency

the actual packet processing rate is not affected by the processor configuration, as each processor is handling a different packet simultaneously, but the total latency a packet experiences does depend on the microprocessor configuration.

Even when the processors are configured in a parallel processing configuration, latency can be introduced by the need to synchronize memory accesses, since performing the same task may require accessing the same parts of memory. The need to synchronize memory accesses requires extra code, which reduces the packet processing rate. Also, scheduling must be implemented so that packets leave the router in the same order that they were received, which can require signals passed among the microprocessors. In this case, the packets experience more latency while waiting for the signals to arrive. In [52], it was found that the core processor alone, running at the same speed as a fast-path processor in the NPU, processed packets at nearly twice the rate compared to using the core processor and one fast-path processor in parallel, simply due to the synchronization required.

# 2.2 Network Processors

Each network processor differs in the number of fast path processors and the coprocessors available on each. These architectures show the differing views on what the key parts of packet processing are and how they can best be optimized.

## 2.2.1 Agere Payload Plus

The Agere PayloadPlus [46] series of network processors uses two hardware blocks to manage data path processing, the Fast Pattern Processor (FPP) and the Routing Switch Processor (RSP). The FPP contains a pattern processing engine to classify the packets and the RSP modifies packets and performs traffic management based on the results of the classification step. The PayloadPlus series appears to be the only network processor that is programmed using a functional programming language for classification tasks, which Agere claims is more efficient than the standard C-style languages used to program most NPUs [45].

## 2.2.2 IBM PowerNP Series

The IBM PowerNP [16] uses 16 microprocessors for handling fast-path packet processing tasks and a PowerPC processor for handling control-path processing. (The PowerNP and the Intel NPU are the only NPUs to include a core processor; the others use a processor located off-chip.) The 16 microprocessors are paired to create 8 Dyadic Protocol Processing Units (DPPU) and each DPPU manages 4 threads. The PowerNP Series uses several co-processors, including a coprocessor to perform table lookups, one to calculate checksums and a co-processor for enqueuing data on the data port or switch fabric. The PowerNP also has a co-processor for performing policy management of flows and a classification co-processor, which can parse packet data before it is dispatched to a DPPU thread.

# 2.2.3 Motorola C-5 Series

Like the Intel IXP NPUs, the Motorola C-5 network processor [17] uses multiple microprocessors to handle the data streams. The unique architecture behind the C-5 is that the microprocessors are physically linked to a single data port, which means high congestion at one port does not affect the entire NPU. However, no matter how many microprocessors on the C-5, packets only travel through two, one at the ingress port and one at the egress port, which severely limits the amount of processing available to each packet. The Motorola C-5 also uses several co-processors that are available to all of the microprocessors. These co-processors include a processor for managing the switch fabric connection and off-loading the processing tasks required to send and receive data on the switch fabric. The C-5 also has a co-processor and special memory to assist with table lookups.

## 2.2.4 Intel IXP

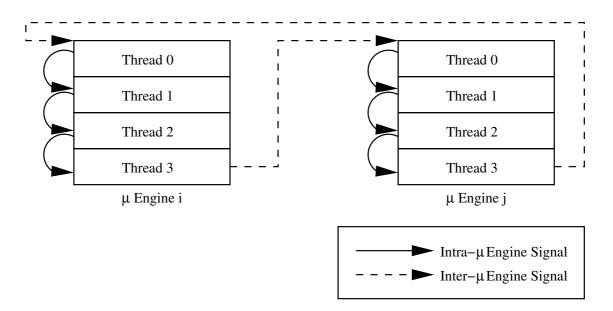

The IXP NPU uses multiple RISC processors, called microengines ( $\mu$ Engines), to handle packets on the data path. These  $\mu$ Engines are also multi-threaded, as explained previously, and context switching is performed in a non-preemptive manner to facilitate programming. In addition, Intel uses a general purpose ARM processor to handle control-path packets. All of these processors are contained on a single chip to speed packet processing. Similar to Figure 2.3, within the IXP chip,  $\mu$ Engines can be configured either in pipeline formation for larger processing tasks, in parallel to improve performance, or in a combination of the two configurations.

The Intel IXP also has several hardware blocks that act as coprocessors to aid in common computing tasks. Cyclic Redundancy Checks can be calculated without using the  $\mu$ Engines, hashes can be generated for various bit sizes, and there are hardware implemented clocks for generating timestamps. Additionally, second generation Intel IXP processors include a separate on-chip memory for fast accesses. This memory also includes hardware assisted queues to aid in passing packets among the  $\mu$ Engines.

The  $\mu$ Engines are quite complex as well. First of all, each  $\mu$ Engine has a local memory. This memory can be shared among the threads in the  $\mu$ Engine, or divided to give each thread a small number of private registers. In addition, there are sets of registers to store data written to or from the off-chip memory, which are used as buffers since reading and writing to the off-chip memory is significantly slower than the  $\mu$ Engine local registers.

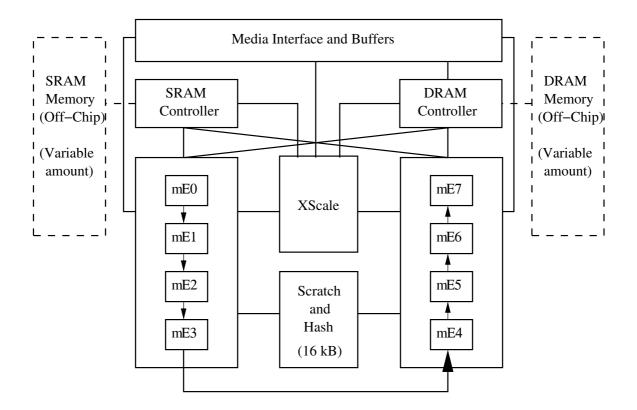

# 2.3 Intel IXP2400

This thesis uses one of Intel's current generation of network processors, the IXP2400, which can support up to 4 Gbps of network traffic. The IXP2400 uses a 600 MHz Intel XScale (ARM V5STE compliant) core for slow-path processing. In addition, there are eight 600 MHz  $\mu$ Engines, each of which has 8 hardware-assisted threads. These 8  $\mu$ Engines are arranged in 2 clusters of 4, each group having its own set of buses and memory controllers. Figure 2.4 shows the major hardware blocks of the IXP2400 and the connections among them. Intel also manufactures the IXP2800, which is essentially the IXP2400 with 16  $\mu$ Engines and additional hardware coprocessors to facilitate cryptographic computations.

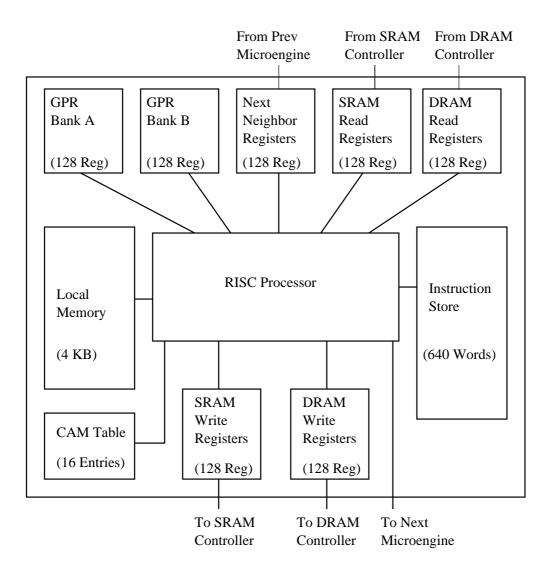

Each  $\mu$ Engine shown in Figure 2.5 has a 4KB instruction space, 640 words of local memory, 256 32-bit general purpose registers, and 256 registers for memory transfers to SRAM and DRAM, all of which are accessible by every thread on the  $\mu$ Engine. In addition, each  $\mu$ Engine has 128 Next-Neighbor (NN) registers. These NN registers are only accessible by the  $\mu$ Engine and its previous neighbor (by  $\mu$ Engine ID). These registers allow pipelined  $\mu$ Engines to synchronize or pass data without needing to use shared memory and the associated buses. Finally, every  $\mu$ Engine has a small 16 entry Content Addressable Memory (CAM) table. The CAM table can be accessed at the same speed as local memory, and is generally used to implement a cache.

Table 2.1 shows the different kinds of memory available on the IXP2400 and the number of cycles required to read or write to each type of memory. As usual, faster memory is more expensive, so there is less of the lower latency memory. The IXP2400 has 16KB of on-chip memory, called scratchpad memory. This memory is the lowest latency memory that can be accessed by all of the  $\mu$ Engines. In addition, this memory has special atomic bit operations, and 16 hardware assisted buffer rings with atomic put and get operations. Unfortunately, the

Figure 2.4: Block diagram of the Intel IXP2400 Network Processor

Figure 2.5: Block diagram of an IXP2400  $\mu \rm Engine$

Table 2.1: Intel IXP2400 Memory Access Times

| Memory Type     | Access Time (Cycles) |

|-----------------|----------------------|

| Local Registers | 3                    |

| Scratchpad      | 60                   |

| SRAM            | 90                   |

| DRAM            | 120                  |

scratchpad memory resides on the hardware block that also contains the hash unit, which means that hash generation and scratch memory accesses can interfere with each other.

The fastest off-chip memory is the SRAM memory. The SRAM provides the same atomic operations as the scratchpad, but instead of a set of rings, each SRAM controller supports 64 queues with atomic enqueue and dequeue operations.

The slowest, but largest memory available to the IXP2400 is the DRAM. Access to DRAM is via a 64-bit bus, rather than the 32-bit bus of the other memory. Also, DRAM has a direct connection to the media interfaces, meaning that transfers can occur between the two units without going through a processor. This capability makes DRAM the obvious choice for storing the actual packets that the NPU handles.

Programmers of this system must choose where to store any particular piece of data, based on the frequency of accesses, amount of data being stored, and which of the two clusters the  $\mu$ Engine is in. For example, packets would likely be stored in DRAM because that data is infrequently accessed and very large, and because of the direct connection between the DRAM controller and the media interface. However, it would be unwise to put packet receiving and packet transmission functionality in the same  $\mu$ Engine cluster, because the frequency of calls would saturate the cluster's DRAM bus. By putting the receive functionality in one group, and transmission in the other, the load can be distributed more efficiently, since each cluster has its own DRAM bus. Similarly, it would be inefficient to put an IP lookup table in DRAM because of the high frequency of accesses. Such a table would best be stored in SRAM, or even in the scratch memory if the table is small enough.

# Chapter 3

# **Related Work**

This chapter explores a wide variety of topics related to network processors. It examines other coprocessors that perform tasks on behalf of the main processor, thereby offloading work from the processor and allowing hardware optimizations because of the more specific functionality of the coprocessor. Also, other processors are examined that encounter similar obstacles and solutions to network processors. Finally, a brief summary of existing applications using network processors is given as well as the highlights of current research being performed using network processors.

# 3.1 Related Hardware

#### 3.1.1 Coprocessors

Coprocessors are used to reduce the load placed on a general processor. Historically, a math coprocessor is often used in computers to perform floating-point calculations on behalf of the main processor. The addition of this coprocessor greatly increased the speed of programs that performed many floating-point operations.

While floating-point operations have been incorporated into general processors for years, there is still a wide variety of coprocessors available, performing tasks from digital signal processing to cryptographical functions; several coprocessors exist for network related tasks. A network coprocessor can be included on ethernet cards for implementing the functions related to sending and receiving network packets, such as validating checksums, while more complex coprocessors can be used to take over all network-related tasks from a general processor [26]. A network processor is an evolutionary step above these coprocessors, designed to handle more complex communication-orientated tasks for an end host or router. With line speeds still increasing, researchers are now looking into using special coprocessors to aid NPUs. Using large CAM tables, these coprocessors could handle tasks such as classifying packets in a very small number of cycles [38] [36], saving the network processor cycles for modifying packets and performing complex scheduling computations.

Figure 3.1: Block Diagram of the Multiple Processors in a GPU

In time, these coprocessors may be absorbed into an NPU, as floating-point coprocessors were absorbed into general-purpose processors.

#### 3.1.2 Graphics Processors

Graphics Processing Units (GPUs), present on video cards for personal computers, are the most commonly used application-specific processor available. Specialized for performing the 2 and 3 dimensional calculations required for displaying data, these GPUs are often just as complex and difficult to program as network processors, and significant research efforts have been devoted to these challenges. Using the NVIDIA GeForce 6 series as an example, this section examines the typical architecture of these application-specific processors.

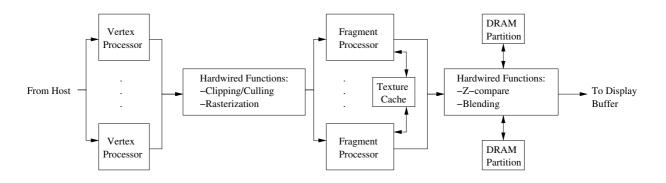

Graphics processors take data regarding object textures, movements, and vertices and apply a series of transformations to the data before displaying it on the screen (see Figure 3.1). First, the vertex processors take the objects' data and rotate, shift or scale the object according to commands from the main processor. The transformed data is sized to fit the screen and pixels that are within the viewing dimensions are grouped together based on where they are in the display. Fragment processors test these groups of pixel data to determine their location relative to other objects in the scene, then shading and textures are applied to the pixels based on those results. The final processing stage compares the depth of the objects being displayed and applies transparencies and color-blending. This procedure is a very computationally intense operation, and while not shown in Figure 3.1, multiple ASICs handling the blending operations. The pixel data is then sent to a buffer for display on the screen. A graphics card must be able to perform this sequence of operations fast enough to fill the buffer (which is the size of the screen) at least 24 times a second or the picture flickers at a rate that is noticeable to the human eye. As shown in Figure 3.1, this speed is achieved using multiple processors at each step that handle the pixel streams in parallel.

Each piece of data streamed though a GPU follows the same path and has the same operations

applied to it, similar to how each network packet follows the same path through an NPU. Also, both graphics and network processors handle the data streams in a pipeline fashion. Though GPU manufacturers are extremely secretive about their technology, some basic details are well-known and can be used to compare against other specialized processors. In general, the architectural details of a GPU are similar to an NPU.

First, graphics processors have a set of vertex processors, which take object-vertex data and transformation commands from the main processor and apply the transformations on the data as per user specifications. These vertex processors are essentially programmable floating-point processors and are quite analogous to the  $\mu$ Engines in the Intel IXP network processor, except the  $\mu$ Engines are also multi-threaded. The vertex processors are also designed to process massive amounts of data in parallel, like network processors handling packets.

Like network processors, GPUs must also handle latencies due to memory accesses. The fragment processors of the GeForce 6 series processor handle multiple sets of data simultaneously by performing the same instruction on multiple sets of data, a process known as SIMD (Single Instruction, Multiple Data). This helps to hide the latency of fetching data from the texture cache.

Also, like network processors, many graphics cards use consumer level memory to reduce costs. However, due to the speed requirements, the data bus on graphics cards is much faster than on network processor line cards. For example, the DRAM memory bus on an NVIDIA GeForce 6 series graphics card can transfer up to 35 gigabytes of data every second, while the memory bus on a Intel IXDP2400 development board is limited to 6 GB/sec [7] [8]. Graphics cards generally have fewer levels in their memory hierarchy, usually only local memory and DRAM, though the DRAM is partitioned into several independent sets to speed access. Unlike most network processors, the GeForce 6 series includes various types of caching memory for frequently accessed data, such as textures.

#### **Programming Graphics Processors**

Due to the rate of increase in processor capability, recent generations of graphics processors use programmable fragment and vertex processors. Initially, these processors were programmed using assembly languages, but recently higher-level languages have been developed for programming graphics processors. These new languages increase the portability of programs and facilitate incremental development, which is essential in graphical programs because of the real-time performance requirements.

The idea of programming graphics processors is attractive because of the amount of parallel processing available (see Figure 3.1) and the commodity price of GPUs. Indeed, graphics processors can be useful for many applications outside of displaying graphics. GPGPU (General-Purpose computation on GPUs) is an active research topic with numerous successes, particularly with database operations [24]. As GPUs are used to perform a larger variety of tasks and as the GPU architectures become more complicated, higher-level languages become extremely useful in abstracting the specific details and idiosyncracies of the hardware and allowing programmers to be more productive in their efforts.

OpenGL [41] is a domain-specific language specification. The OpenGL compiler is tightly integrated with the graphics processor pipeline, creating an interface that is more intuitive for developers. Since OpenGL is a domain-specific language, it includes a larger set of domainspecific modules, such as lighting models, and can be more aggressive in optimizations involving the modules. OpenGL can also expose more graphics-orientated data to a developer, such as the Model view and World view matrices used in a GPU to describe the position of the viewing camera with respect to the world. DirectX [1], created by Microsoft, is a similar set of APIs as OpenGL.

Cg, or "C for graphics," is a high-level shading language developed by the graphics processor manufacturer NVIDIA [33]. A shading language instructs a graphics processor on how to shade pixels, so Cg primitives include data types that are commonly used in graphical calculations, such as 3 or 4 element vectors. Cg is designed to look and function similar to the C language, which is already familiar to most developers, while still being very similar to the actual assembly instructions on a graphics processor but abstracting enough of the architecture so graphics programming is easier. However, by making Cg sufficiently high-level and general, it is possible to program graphics processors for more general purposes, and easier to port programs written in the language between different GPUs.

To allow for portability between GPUs, Cg uses *profiles* to specify the capabilities of a graphics processor, and, hence which Cg operations it can perform. Profiles are a compromise between portability and abstracting away full hardware functionality. Profiles also allow for function overloading so that any special mechanisms on a particular processor can be used to optimize common operations. To port a program between processors requires applying a different profile, and only parts of the program that use specialized features of a processor are compromised. Moreover, to keep the Cg language more general, any extra capabilities of a GPU are exposed via libraries rather than through standard language operators.

Sh [34] is a C++ library that can be used to transform a set of Sh operations into code that runs on a GPU. The C++ code from outside the library is used as a framework for the structure of the shader code in order to allow developers to access the mechanisms (classes, operator overloading, etc) that are available in C++. Using this mechanism, it is also possible to exchange variables between the host application and the GPU code. This tight integration between the shader language and the host CPU language also facilitates optimization, since it is easier for a compiler to view the program as a whole.

Figure 3.2 shows the graphical languages detailed above and how they build on each other. There are also higher-level languages beyond those explained above. For example, Brook [4] is a language designed specifically for processing streams of data and can be compiled into a Cg program. In this figure, Brook would be at a level above Cg at the top of the hierarchy.

|                         | Brook              |        |  |

|-------------------------|--------------------|--------|--|

|                         | Cg                 | Sh     |  |

| Open                    |                    | GL api |  |

|                         | Hardware Interface |        |  |

| Graphics Hardware (GPU) |                    |        |  |

Figure 3.2: Interaction Layers of Graphics Programming Languages

### 3.1.3 Cell Broadband Engine (BE)

The Cell BE multiprocessor is being created as a joint venture between IBM, Sony and Toshiba, and will be powering Sony's third-generation PlayStation video game console and used in HDTVs to decode the data streams for display. The primary goals for the Cell are quite far-reaching, as it is designed to provide:

- outstanding performance on game consoles and multimedia devices

- quick responses to user actions and network behavior

- applicability to a wide range of platforms [15]

The design of the Cell is particularly interesting as the design challenges are very similar to that of a network processor. First of all, the responsiveness of the chip is a primary requirement for handling real-time multimedia data, just as it is in handling flows of packets at line speeds. Since it is intended for the next-generation of game consoles, the Cell must also handle Internet connections. More specifically, due to its use in multiplayer online game environments, the Cell is optimized to handle workloads related to communicating with multiple peers, very similar to an NPU. Finally, the Cell BE encounters the same latencies with regards to memory accesses and processor speed.

Because of similar obstacles, it is not surprising that this multiprocessor and network processors share many design points. First of all, the Cell processor contains multiple processing engines, similar to network processors. In the case of the Cell, these Synergistic Processor Elements (SPEs) [14] use the SIMD architecture that graphics processors also use. Each of these SPEs contain local memory, similarly to the  $\mu$ Engines on the Intel IXP. It is these SPEs that allows the Cell to decode streams of data quickly enough for users to watch streaming video. With Cell's multiple processor architecture, it would even be possible to include the chip in a server that can stream different HDTV streams to separate televisions. The design goals of the compiler for the Cell multiprocessor, known as the Octopiler [13], are just as far-reaching as the goals for the hardware. In particular, the compiler must allow a developer to take full advantage of the SIMD architecture and multiple processors that are available on the Cell without requiring a developer to write completely specialized code for the hardware. The octopiler can generate code for both the SPEs and the core processor. Understanding the different processor architectures allows the compiler to better optimize the code by distributing the tasks among the processors.

One way that the octopiler is able to optimize applications is by taking scalar loops and combining the loops so that several iterations can be performed in parallel using a SIMD operation, a process called *auto-SIMDization* [50]. For example, the loop

with 32 bit integer arrays **a**, **b** and **c** can be parallelized to perform 4 iterations at a time using the 128 bit registers in the SPEs and the contiguous data in the arrays. Auto-SIMDization also occurs when setting contiguous data in an object; the data is packed together into a single assignment operation.

In addition to SIMD operations, which affects a single SPE, the parallelism of multiple SPEs is also exploited. To execute tasks in parallel, regions of code are marked by programmers, and the octopiler manages the partitioning of this code among the SPEs and coordinating the execution.

#### 3.1.4 The Success of Compilers and Higher Level Languages

There has always been a high demand for languages that help graphics developers be more productive, and hence release products, especially games, at a higher rate. Development companies often create customized rendering engines on top of the existing higher-level graphical languages to increase productivity for their type of applications. High-level graphics languages have succeeded for three reasons: the existence of standardized lower-level APIs (like OpenGL), their high demand and industry support, and because of the similarity in GPU architectures among different vendors.

The creation of the octopiler demonstrates that it is possible to create an efficient higher-level language for heterogenous multiprocessor systems. However, as with any compiler meant for a specialized hardware architecture, extending such a compiler to other architectures is much more difficult.

## **3.2** Network Processor Applications

Due to the programmability of a network processor, there is a wide variety of applications that can use network processors to handle packets, from simple firewalls and routers to streaming media

20

servers. Many of these applications use the previous generation of Intel network processors, the IXP1200. The IXP1200 uses a StrongARM core processor rather than the XScale streaming media servers. Many of these applications use this processor, which only has 6 (slower)  $\mu$ Engines compared to the 8  $\mu$ Engines on the current generation Intel IXP2400.

#### 3.2.1 Video Streaming

One rather unique application using the IXP1200 network processor is from the Osaka University in Japan. This application adjusts the quality of a video being streamed to handle connections of different speeds [52]. Video quality is adjusted by using a low-pass filter to remove high frequency data coefficients from the data blocks.

The most interesting aspect about this application is how the  $\mu$ Engines are used. First of all, this is one of the few applications where the  $\mu$ Engines all work on the same data packet. In addition, they are all slaved to the StrongARM core processor, which also does a large part of the packet processing (rather than just exception packet handling). For the video-quality adjustment application, the core processor receives a video packet and breaks it into a set of *video blocks*, storing the video blocks in shared memory for the  $\mu$ Engines. The  $\mu$ Engines then read out the individual video blocks and apply the low-pass filtering to them before copying them back to shared memory. Once all the video blocks in the packet have been filtered, the StrongARM processor repackages the video blocks and transmits the packet.

This application is an excellent example of what  $\mu$ Engines can be used for, as the low-pass filter is a relatively simple mathematical algorithm and well suited to the reduced instruction set. It also is a good example of what synchronization problems can occur when handling packets and using shared memory. In this case, all the  $\mu$ Engines are accessing the same packet simultaneously but each  $\mu$ Engine is accessing a different video block from the packet. The simultaneous access makes it important to manage memory accesses to eliminate duplicate work and to keep from overloading the data bus between memory and the  $\mu$ Engines. In fact, the developers found only a twofold increase in throughput when using all six  $\mu$ Engines and the StrongARM processors compared to just using the core processor to apply the filter. Using the StrongARM and a single  $\mu$ Engine actually resulted in slower throughput due to the added synchronization.

#### 3.2.2 Firewalls

Firewalls sit at the edge of a network and filter packets. They fill an important role in network security, protecting networks from attacks and keeping the network bandwidth and computing resources available for processing useful packets. A firewall examines each packet and makes a forward/drop decision, after examining the packet header and performing some computation. The amount of computation performed for each packet determines the type of firewall. A basic *packet filter firewall* examines packet headers and makes a decision based on a set of simple rules (e.g., dropping all packets being sent to TCP port 21). A simple firewall can be implemented

on ASIC-based hardware to quickly process packets. However, a more complex firewall requires storing data and/or performing more complex computations, which cannot be easily implemented in hardware nor perform well on a slower general-purpose processor. Because of the increasing complexity of network attacks, most commercial firewalls are more complex than a basic packet-filter firewall. Most of these firewalls are *stateful firewalls*, meaning some state on previously received packets is stored and that state is used to make a forward/drop decision. The firewall in [29] performs a stateful packet inspection by storing the TCP state information in a hash table. The hash table is indexed on the 5-tuple packet header information with the hash being performed by the hash hardware block on the IXP2400 chip.

Recently, there has been a push towards the integration of network functionality into single devices. This integration can lower the cost of such devices and can also improve performance, as such devices can perform faster, since one function can leverage the work done by another function (e.g. sharing packet meta-data). In [49], the authors combine packet-filter firewall and Network Address Translation (NAT) functionalities into a single device. It was found that the primary bottleneck in the system is rule-lookup, as a fully configurable firewall must accept new rules and rule changes, looking up every rule for each packet. With only one  $\mu$ Engine handling firewall functionality, the estimated performance of the firewall is able to meet 1 Gigabit/sec line speeds when 1 rule lookup is necessary before a rule match is found. Allocating 3  $\mu$ Engines of an IXP2400 to firewall functionality allowed an average of 10 rule lookups per packet for a firewall able to forward packets at a 1 Gigabit/sec line speed.

#### 3.2.3 Software-Based Routers

Click [30] is a software architecture project developed at MIT for creating easily configurable routers. The primary idea is to divide a router into as many individual components as possible (e.g., packet classification, header verification, route lookup, etc). Each of these components is made into a separate Click *element* class. Elements communicate with each other via published interfaces, which can be used to call methods or access data. Click is a single-threaded program where the elements are scheduled on the router's CPU. Moving packets between elements causes these elements to be scheduled for execution on the CPU. The NP-Click project [42] works to address many of the problems that occur when applying Click to a network processor. The authors refer to these problems as the *implementation gap*, the difference between the high-level Click language and the lower-level implementation languages of network processors that must be used in order to properly use a network processor's specialized hardware and memory. To this end, NP-Click uses Click's idea of elements but gives the programmer a degree of control in specifying objects within an element and how elements communicate. A programmer allocates objects to different memory types based on the scope of the data, and controls how the processing elements map to the processing threads. Finally, an abstraction library is created to hide some of the hardware specifics of the different network processors. The end result of this project is an architecture that is able to abstract away much of the resource contention and specific hardware concerns from a programmer. However, the programmer is still required to understand the network processor hardware to effectively use its available memory hierarchy and multi-threaded capabilities.

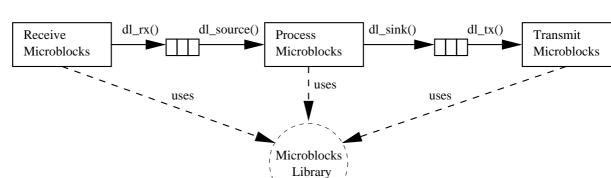

The NETKIT [9] project also uses the idea of software components with network processors. Here, components are stored in binary code compiled for the network processor's  $\mu$ Engines. These components are tightly-contained classes providing a complete piece of functionality. NETKIT components are very similar to JavaBeans [35], since both work towards the same goal: reusable code. With both JavaBeans and NETKIT, components all have well-defined interfaces for easy interchangeability, which keeps the modules separate and portable. Each NETKIT software component defines a set of *receptacles*, which must be linked to other existing components. In this way, NETKIT is able to provide some safety from improperly used components. As a further safety mechanism, NETKIT uses component frameworks to define rules and interfaces for a particular domain of components. These component frameworks even provide the property of nesting and inheritance. The NETKIT project looks at the idea of NPUs at a much more global scale than most other projects to create a structure that is easily managed and reconfigured during run-time and encompasses all the protocol layers.

#### 3.2.4 Overlay Networks

Overlay networks are connections between end hosts that operate on top of an existing IP network. However, as these networks are implemented at the application rather than network level, packets experience longer processing delays because the routing operations are performed through user-level code. In [20], network processors are used between the end host and the network. The NPUs assist with managing the streams of data that are sent across the overlay network, while the end host does more computationally intense work on the data that requires more time and state. This work showcases network processors working at a higher protocol layer than previous examples. Here, in addition to handling IP level headers, the  $\mu$ Engines in the NPU must reassemble the data packets into application-level data units, which is much different than simply checking IP headers. Essentially, the attached network processor becomes the middleware for the networked application. Also, this research is one of the few examples where the  $\mu$ Engine code is changed while the NPU is running. With this network, the attached network processors store several different  $\mu$ Engine implementations. Should the load or the user's preferences change, the end host can send a message to the core processor of the NPU to switch to one of the other pre-existing stream handling implementations.

#### 3.2.5 Grid Computing

Grid computing involves a large network of computers, each buying and selling spare processing cycles. Hosts looking to have remote computation performed on their behalf send the data and execution code to another computer, which executes the code on the data and returns the result.

To achieve this, a method is required for locating a remote host that is willing to execute the code. In [32], the authors use network processors to distribute computing requests. Computers willing to accept work register with a network processor, which stores their IP address and processing power in a special routing table. Hosts requiring remote computation send special *Task Message (TM)* packets with no IP destination, only the source address. The network processor recognizes these packets and forwards them to a registered computer with sufficient processing power to execute the code in the TM quickly. The result is sent back to the client using the IP source address in the TM packet. If the current network processor does not have any suitable computers registered, it passes the TM to another NPU deeper in the grid. In this manner, the grid is scalable in both the number of computers and the number of network processors running it.

#### 3.2.6 Porting Existing Applications

There is also work being done to convert other existing network domain applications onto network processors. In [5], the authors have created a compiler that generates C-style (rather than assembler) code for the IXP1200 network processor from a **snort** [40] configuration file. The compiler creates a condition tree of packet header fields and values based on the configuration file and generates the NPU code to check for these values. While this may seem like a minor piece of research, porting an existing application to NPUs helps to show the performance improvements that can be made as well as provide NPU users with programs they are already familiar with.

# 3.3 Network Processor Research

The ForCES (Forwarding and Control Element Separation) IETF working group [25] is currently trying to develop a protocol that separates the control and forwarding planes of a network device. This protocol is a framework and set of mechanisms for combining the components of an IP device and standardizing the way data is passed between the control and data paths. By utilizing this protocol, improvements and innovations can be made to either processing plane without affecting the other.

The goals of the working group directly affect research efforts on network processors, as there is currently a tight integration between the two processing planes. Separating the planes would allow for easier changes to the hardware or software that implements the planes.

#### 3.3.1 Programming Language Research

Language research is one of the most active areas involving network processors, primarily due to the difficulty in efficiently and effectively programming such a processor. This research involves not just creating libraries and components to develop a router, but also different applicationspecific languages to use when programming the packet processors. In [21], the authors have designed a reconfigurable rule engine that executes on an NPU. The engine contains a table of domain-specific rules that are checked for each data event that the NPU receives. These rules determine the actions that the NPU receives, such as forwarding the event, updating some state, modifying the data, or creating a new event. Rules can be chained to perform more complex operations such as application-level routing. The rule engine is based on the SPLITS (*Software architecture for Programmable LIghtweighT Stream handling*) [19] architecture, which is a pipelined set of nodes that data events flow through.  $\mu$ Engines in an IXP2400 are implemented as *rule handlers*, which read the rule engine's decision table from either SRAM or DRAM. Each  $\mu$ Engine is implemented to handle a specific set of rules, with early classification determining which branch of rule handlers the event is sent to for processing.

Network Speed Technologies, Inc. has developed the Nova language [23] for network processors. The language exposes the specificities of the actual hardware (such as the communication facilities and hardware assisted queues), while hiding some of the more difficult aspects of the hardware. For example, Nova makes it much easier to extract or create protocol headers for packets using the *layout* data type. This meta-data type is an object containing a list of data fields in the layout and their sizes. The most useful aspect of this data type is that it can be populated with packet data using a single command, which means that if the protocol changes and new fields are added, it does not change the code except in the layout definition. This capability is particularly important as the insertion of a new data field can often require rewriting the extraction methods to ensure that the data is properly shifted and masked. This language primarily focuses on allocating registers, which is difficult as there are several different register banks of limited size, and spilling data over into different banks can be expensive (e.g., moving GPR data into local memory). Allocating registers is also made difficult as performing memory accesses, either read or write, usually require contiguous blocks of registers. Nova handles these problems using static analysis to identify unused data, ILP (Integer Linear Programming)-based optimization to allocate the variables, and coloring algorithms to handle register bank conflicts. In [22], a sample IPv4 forwarding application is developed using the  $\mu L$  language (a descendant of the Nova language) that allocates registers more efficiently than hand-coded assembly code (from the IXP2400 sample code provided by Intel) and arranges the code for optimal execution. As such, the  $\mu L$  forwarder performs more efficiently than the sample application.