# Incorporating Physical Information into Clustering for FPGAs

by

## Doris Tzu Lang Chen

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2007

© Doris Tzu Lang Chen 2007

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

## **Abstract**

The traditional approach to FPGA clustering and CLB-level placement has been shown to yield significantly worse overall placement quality than approaches which allow BLEs to move during placement. In practice, however, modern FPGA architectures require computationally-expensive Design Rule Checks (DRC) which render BLE-level placement impractical.

This thesis research addresses this problem by proposing a novel clustering framework that produces *better initial clusters* that help to reduce the dependence on BLE-level placement. The work described in this dissertation includes: (1) a comparison of various clustering algorithms used for FPGAs, (2) the introduction of a novel hybridized clustering framework for timing-driven FPGA clustering, (3) the addition of physical information to make better clusters, (4) a comparison of the implemented approaches to known clustering tools, and (5) the implementation and evaluation of cluster improvement heuristics. The proposed techniques are quantified across accepted benchmarks and show that the implemented DPack produces results with 16% less wire length, 19% smaller minimum channel widths, and 8% less critical delay, on average, than known academic tools. The hybridized approach, HDPack, is found to achieve 21% less wire length, 24% smaller minimum channel widths, and 6% less critical delay, on average.

## Acknowledgements

I would like to thank Andrew Kennings for the help, advice, and guidance he has given me over the course of my degree. Much thanks should be directed to Kristofer Vorwerk, who has been extremely helpful and generous with his time in helping me out with any difficulties I encountered during the research process. Without the help of both of you, this thesis would not have come into existence.

# **Table of Contents**

| 1 | Introduction |                                                 |    |

|---|--------------|-------------------------------------------------|----|

|   | 1.1          | Overview of FPGAs                               | 1  |

|   | 1.2          | The FPGA CAD Flow                               | 6  |

|   | 1.3          | Definitions of Key Terms                        | 9  |

|   | 1.4          | Statement of Thesis                             | 9  |

| 2 | Bac          | kground                                         | 11 |

|   | 2.1          | Register Packing                                | 12 |

|   | 2.2          | Seed-Based Approaches                           | 13 |

|   | 2.3          | Depth-Optimal Methods                           | 17 |

|   | 2.4          | ASIC Clustering Algorithms                      | 19 |

|   | 2.5          | Simultaneous Clustering and Placement           | 21 |

|   | 2.6          | Relation of Past Literature to Current Research | 22 |

| 3 | Clus         | stering Algorithms                              | 24 |

|   | 3.1          | Greedy Packing (DPack)                          | 25 |

|   | 3.2          | Hybridized Packing (HDPack)                     | 26 |

|   |              | 3.2.1 Affinity-Based Packing (HFCC)             | 26 |

|   |              | 3.2.2 Formulation of HDPack                     | 28 |

|   | 3.3          | Incorporating Physical Information              | 31 |

| 4  | Clus                | ster Imp  | provement Algorithms                 | 35 |  |  |

|----|---------------------|-----------|--------------------------------------|----|--|--|

|    | 4.1                 | Overal    | l Flow                               | 36 |  |  |

|    | 4.2                 | Swaps     | and Moves                            | 36 |  |  |

|    | 4.3                 | Branch    | and Bound                            | 38 |  |  |

| 5  | Nun                 | nerical l | Results                              | 41 |  |  |

|    | 5.1                 | Experi    | mental Setup                         | 41 |  |  |

|    |                     | 5.1.1     | General Experimental Flow            | 42 |  |  |

|    |                     | 5.1.2     | Low-Stress Routing Setup             | 43 |  |  |

|    |                     | 5.1.3     | High-Stress Routing Setup            | 44 |  |  |

|    | 5.2                 | Results   | s for Implemented Algorithms         | 44 |  |  |

|    |                     | 5.2.1     | Low-Stress Routing                   | 44 |  |  |

|    |                     | 5.2.2     | High-Stress Routing                  | 47 |  |  |

|    | 5.3                 | How M     | Much Physical Information is Enough? | 47 |  |  |

|    | 5.4                 | Compa     | arison to Other Methods              | 48 |  |  |

|    |                     | 5.4.1     | Low-Stress Routing Tests             | 49 |  |  |

|    |                     | 5.4.2     | High-Stress Routing Tests            | 51 |  |  |

|    | 5.5                 | Integra   | tion of RPack and iRAC               | 53 |  |  |

|    | 5.6                 | Effecti   | veness of Improvement Algorithms     | 54 |  |  |

| 6  | Con                 | clusions  |                                      | 59 |  |  |

| 7  | Futu                | ıre Wor   | k                                    | 62 |  |  |

| Bi | bliogr              | aphy      |                                      | 63 |  |  |

| Gl | Glossary of Terms 7 |           |                                      |    |  |  |

## **List of Tables**

| 5.1 | Packing without physical information               | 45 |

|-----|----------------------------------------------------|----|

| 5.2 | Packing with physical information                  | 46 |

| 5.3 | Run-time comparison vs. baseline                   | 47 |

| 5.4 | Improvement in minimum channel widths              | 48 |

| 5.5 | Comparison between known tools, $N = 8$ , $I = 18$ | 51 |

| 5.6 | Effect of Improvement Algorithms on T-VPack        | 56 |

| 5.7 | Effect of Improvement Algorithms on DPack          | 58 |

| 5.8 | Effect of Improvement Algorithms on HDPack         | 58 |

# **List of Illustrations**

| 1.1 | Sample Island-Style FPGA Architecture                                         | 3  |

|-----|-------------------------------------------------------------------------------|----|

| 1.2 | Detailed Placed-and-Routed FPGA Design                                        | 4  |

| 1.3 | FPGA Routing Switch Block                                                     | 5  |

| 1.4 | A Basic Logic Element (BLE)                                                   | 6  |

| 1.5 | A Configurable Logic Block (CLB)                                              | 7  |

| 1.6 | FPGA CAD Flow                                                                 | 8  |

| 2.1 | Possible BLE Configurations                                                   | 13 |

| 2.2 | Pseudocode for Register Packing                                               | 14 |

| 2.3 | Hill Climbing Example from [16]                                               | 16 |

| 2.4 | Depth-Optimal Example: The Labelling Phase [32]. (a) Circuit graph (b) Labels |    |

|     | of nodes $b$ , $c$ , and $f$ (c) Computing the label of $b$                   | 19 |

| 2.5 | Depth-Optimal Example: Optimal Clustering of Figure 2.4a from [32]            | 20 |

| 2.6 | Logic Duplication Example [46]                                                | 23 |

| 3.1 | Pseudocode for DPack                                                          | 27 |

| 3.2 | Pseudocode for HFCC                                                           | 29 |

| 3.3 | Pseudocode for HDPack                                                         | 32 |

| 3.4 | Min-Cut Partitioning Algorithm                                                | 33 |

| 4.1 | Outer Loop of Improvement Heuristics                                          | 37 |

| 4.2 | Pseudocode for Branch and Bound                                               | 40 |

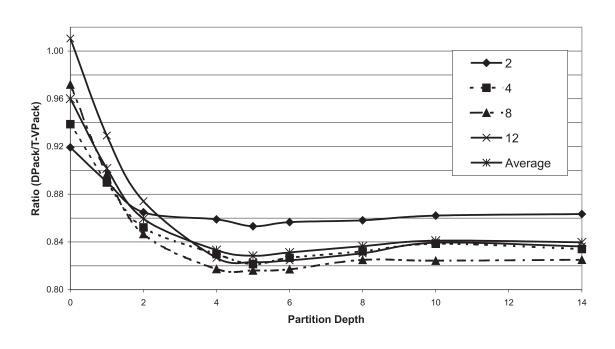

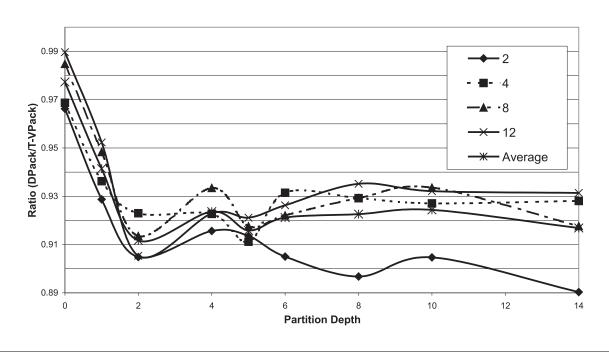

| 5.1 | Wire Length Reduction vs. Partition Depth    | 49 |

|-----|----------------------------------------------|----|

| 5.2 | Critical Delay Reduction vs. Partition Depth | 50 |

| 5.3 | Effect of Depopulation: N=8                  | 52 |

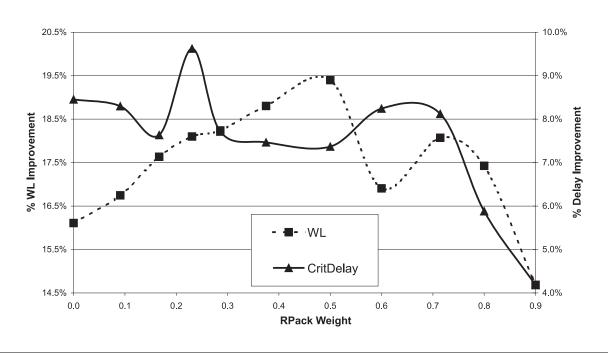

| 5.4 | Incorporation of RPack Sweep: N=8            | 54 |

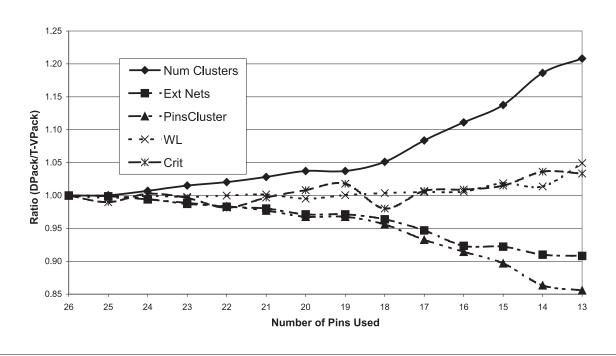

| 5.5 | Effect of Reducing Pin Count: N=8            | 55 |

## **Chapter 1**

## Introduction

The Field Programmable Gate Array (FPGA) has become very popular in the last 25 years, and can be found in a variety of applications. However, the performance of the FPGA is highly dependent on the quality of the Computer-Aided Design (CAD) tool used. As the FPGA becomes more and more powerful due to advances in process technology and architecture research, better tools are needed to take full advantage of its capabilities. Therefore, it is of utmost importance to improve the quality of the design tools used.

#### 1.1 Overview of FPGAs

There are two primary platforms that hardware designs can be implemented upon: ASICs, and FPGAs. The Application-Specific Integrated Circuit (ASIC) is a specially designed, custom manufactured chip. In comparison, the Field Programmable Gate Array (FPGA) has a regular structure, with a standard set of elements that can be programmed to function as any digital circuit. There are several advantages of using FPGAs over ASICs. First and foremost, the FPGA is programmable, whereas the ASIC is not. The programmability of the FPGA allows easy modification of its programmed application. In contrast, the ASIC cannot be modified once manufactured. If a different function is required of the chip, then a new ASIC must be made. This can pose as a significant problem during the developmental stage of hardware designs. If

a bug is found in the design, new chips must be remanufactured with the old ones discarded. However, if the hardware design was based on FPGAs, then the design can be altered easily by simply reconfiguring the FPGA. For this reason, FPGAs are very popular for prototyping designs. FPGAs also have an advantage over traditional ASICs in terms of time-to-market, as the chip manufacturing process can take months, whereas FPGAs are available off the shelf. However, even though there are many advantages to adopting the FPGA for development, FPGAs are not without drawbacks. Because of their programmability, FPGAs are usually much larger in area than an equivalent ASIC, leading to higher silicon costs and power consumption. They also tend to be slower than their ASIC counterpart. Therefore, for applications that require high performance and have stringent power requirements, such as cell phone applications, ASICs are still the preferred choice.

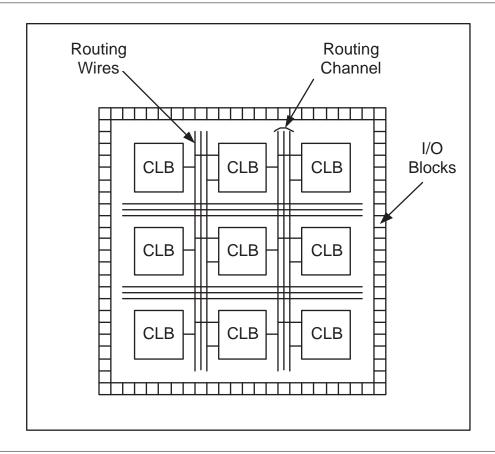

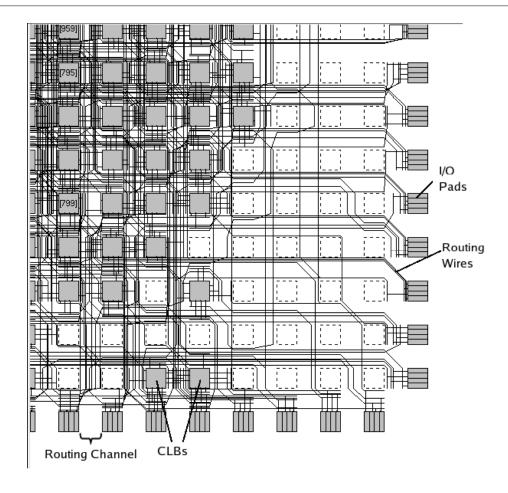

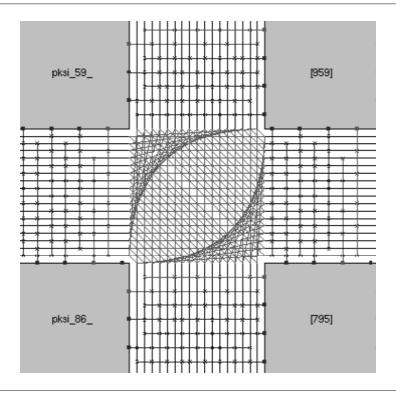

A popular FPGA architecture that is manufactured today is the island-style cluster-based FPGA. An example of this type of architecture is shown in Figure 1.1. The key characteristic of this architecture is the organization of logic blocks and wires. In this architecture, groups of logic, called Configurable Logic Blocks (CLBs) are arranged in a grid-like pattern, separated by routing channels. These channels contain many parallel segments of wires that can be programmed to form connections between CLBs. A more detailed view of the FPGA architecture is shown in Figure 1.2, where the building blocks of the FPGA is labelled. FPGAs interact with off-chip devices through the use of Input/Output (I/O) blocks, located along the periphery of the chip. The square blocks in the interior of the chip are CLBs with routing channels separating them. At the intersection of horizontal and vertical channels, routing switch blocks, such as the one shown in Figure 1.3, control which horizontal and vertical wires are connected. In Figure 1.3, 17 wires can be seen in every horizontal and vertical channel. The routing switch block performs the actual connection of wires, thus allowing horizontal wires to be connected to vertical wires as necessary. The switch shown allows a wire to be connected to one specific wire in every channel to which it is adjacent.

It should be noted that the architecture shown in Figure 1.1 is a very simplified layout of a

Figure 1.1: Sample Island-Style FPGA Architecture

FPGA. Modern FPGAs, such as the Cyclone II [1] and Stratix III [2] families manufactured by Altera, have many other types of blocks other than logic on the FPGA. These additional hard components further extend the capabilities of the FPGA, by incorporating memory components such as Random Access Memory (RAM) blocks, multiplier blocks such as Digital Signal Processing (DSP) units, and Phase-Locked Loops (PLLs) in the FPGA fabric.

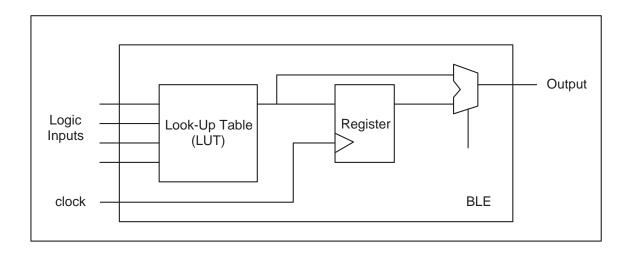

The basic building block of logic in a FPGA is the Basic Logic Element (BLE). A simplified architecture for a BLE is shown in Figure 1.4. The BLE is made up of a Look-Up Table (LUT) for combinational logic, and a register, also referred to as a flip-flop, to store state. A k-LUT is essentially a memory component with k input pins, and one output pin. Depending on the combination of the input pin values, the row in the k-LUT will be addressed and the output set accordingly. There are a few different configurations that the BLE can take. As seen from

Figure 1.2: Detailed Placed-and-Routed FPGA Design

Figure 1.4, the output of the BLE may either be the output of the LUT, or the output of the register. Again, this diagram is very simplistic, and does not show several control signals (e.g., sets/presets), or other enhancements such as high-speed arithmetic logic (e.g., carry-chains).

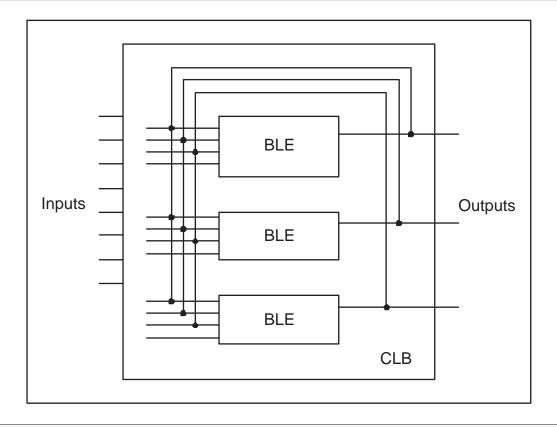

The second hierarchical logic structure of the FPGA is the Configurable Logic Block (CLB). A CLB is a collection of BLEs. Several salient features of a CLB are shown in Figure 1.5. It can be seen that the outputs of the BLEs contained in the CLB can be connected to the input of all BLEs within the CLB. These are also referred to as local, or intra-cluster, connections of a CLB. It should be noted that the number of input pins of the CLB is typically less than the sum of the number of input pins of the contained BLEs. Therefore, if the BLEs within the CLB are to be fully utilized, some of the BLEs will need to share inputs. Also, if one of the inputs of a BLE is driven by another

Figure 1.3: FPGA Routing Switch Block

BLE located within the CLB, the output signal can directly feed this BLE without having to be routed outside the CLB. To take advantage of this unique characteristic of the CLB, it is preferable to group together BLEs that have many interconnections. In this FPGA architecture, the wires within the CLB are much shorter than wires between CLBs. Therefore, the delay of intra-cluster connections are much less than inter-cluster connections since it is unnecessary to use routing resources. In Figure 1.5, the number of BLEs contained in the CLB is 3. Although the inputs are depicted to come from the left side of the CLB in this figure, in practice, inputs are generally distributed along the top, left, and bottom sides of the CLB, with the outputs leaving the right side.

There are many parameters and constraints present in the FPGA architecture. Many of these parameters cannot be controlled by the user. For example, parameters such as the number of BLEs per CLB, the number of inputs per CLB, and the number of wires in the routing channel are predetermined by the manufacturer, and consistent throughout the chip. Therefore, it is up to the user of the FPGA to take advantage of the architecture to achieve the best possible performance.

Figure 1.4: A Basic Logic Element (BLE)

However, it is unreasonable to expect all users of the FPGA to fully understand the complete inner workings of the FPGA. This would create a very steep learning curve, and discourage designers from using the FPGA as their primary method of development. Fortunately, tools have been developed to make FPGAs much easier to use, and to help the user maximize the performance of their designs on the FPGA.

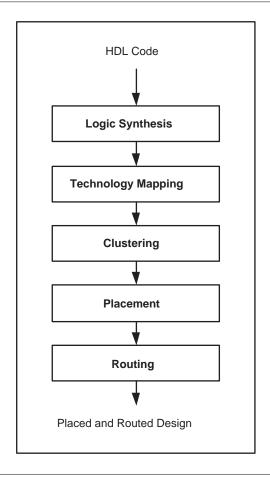

#### 1.2 The FPGA CAD Flow

The purpose of the Computer-Aided Design (CAD) flow is to bridge the gap between the hardware designer and the hardware implementation of their design on the FPGA. The CAD tool takes the circuit design, written in Hardware Description Languages (HDL) such as VHDL and Verilog or as schematics, as input. It then executes a number of steps to output a format that can be used directly to configure the circuit onto the FPGA. The overall FPGA CAD flow is shown in Figure 1.6. The main steps of the FPGA CAD flow include *Logic Synthesis*, *Technology Mapping*, *Clustering*, *Placement*, and *Routing*.

The first step is *Logic Synthesis* which, in itself, consists of high-level synthesis and technology-independent logic optimization. High-level synthesis works to convert the HDL of a design into Register Transfer Level (RTL) logic (i.e., registers, logic equations and macro blocks such as

**Figure 1.5:** A Configurable Logic Block (CLB)

RAM, DSP and arithmetric). Technology independent logic optimization subsequently performs additional optimizations such as the removal of redundant logic, register retiming, and so forth. The most well-known academic synthesis tools include SIS [3], MVSIS [4] and ABC [5]. Then, during *Technology Mapping*, the design is converted into a set of primitive blocks that exist in the FPGA, connected by nets. For the cluster-based FPGA, these primitive blocks are LUTs and registers. Some popular technology mappers include Chortle [6], FlowMap [7], CutMap [8], DART [9], FAST [10], IMap [11] and DAOmap [12]. Then, in the *Clustering* stage, these primitive blocks are grouped into larger blocks that exist on the FPGA. In the case of the island-style FPGA described previously, the LUTs and registers are first grouped into BLEs in an intermediate step called register packing. Then, from the resulting set of BLEs, a set of CLBs are made using various clustering algorithms. VPack[13], T-VPack [13], iRAC [14] and RPack [15] are examples of academic clustering tools.

**Figure 1.6:** FPGA CAD Flow

At this point, a clustered netlist consisting of CLBs and nets that connect the CLBs together is generated. This netlist is then fed into the *Placement* step, where CLBs are moved around on a grid representing the FPGA chip to determine the best location for each CLB in the clustered netlist. Academic placers vary widely in the algorithm used, ranging from algorithms such as simulated annealing in VPR [13, 16], to partitioning algorithms [17–20]. After the placement step has been completed, every CLB is assigned to an x and y coordinate representing its final placement location. This is also referred to as the physical location of a CLB.

Finally, after the physical locations of all CLBs are found and set, the nets that connect CLBs are assigned to specific wires in the routing channels during the *Routing* stage. Routing can be split up into two stages: global, and detailed routing. During global routing, the channel is selected for every net, but the specific wire in the channel is not chosen. Then, during detailed routing,

each net is assigned to a specific wire in the channel. Routers typically perform the two step either sequentially, known as 2-step routing, or simultaneously, where both the channel and wire are chosen at the same time. One notable detailed routing algorithms is SEGA [21,22]. The most widely used routing algorithm is the Pathfinder [23] algorithm, which is based on the A\* search algorithm. There have been extensive studies on routing [24,25]. VPR [13,16] also functions as a router in addition to serving as a placement tool.

As the design progresses through each step of the CAD flow, it becomes more and more fixed. Decisions made early in the flow have a dramatically greater impact on subsequent steps of the flow. For example, at the *Placement* stage, the contents of CLBs have been determined, and usually cannot be changed. Therefore, if clustering was performed poorly, the placement problem also becomes more difficult. For example, if a large number of CLBs was made during clustering, the number of blocks that the placer needs to deal with also increases. This can affect the quality of the final placement, as well as increase the runtime of subsequent stages of the flow. Thus, it is important to optimize each step of the CAD flow, and more importantly, steps that occur early on in the flow.

## 1.3 Definitions of Key Terms

Throughout this thesis, a *cluster* refers to a CLB. *Clustering* is the process of grouping BLEs into CLBs such that they are design rule correct. The *architecture* of an FPGA refers to the maximum number of BLEs that can be put into one CLB. A *netlist* is the description of a hardware circuit, denoted by blocks of logic, or nodes, connected by *edges* or *nets*.

### 1.4 Statement of Thesis

There are three main objectives in the research documented in this dissertation. The primary objective is to provide a thorough analysis of the *Clustering* step of the FPGA CAD flow, and how it can be enhanced. To achieve this, several clustering algorithms have been implemented within

the same framework to evaluate and compare the performance of each algorithm. The second objective is to further improve upon the performance of the implemented algorithms through the addition of some preliminary physical information. The augmented algorithms have been evaluated to determine whether an improvement can be achieved. These results have been compared to data from other known clustering tools. Then, it is the goal of the thesis to determine how accurate physical information needs to be before a positive impact on clustering can be witnessed. Finally, several cluster improvement strategies have been implemented to study whether post-clustering optimizations can lead to improvements in the final placement.

This dissertation is organized as follows. Chapter 2 provides an overview of clustering algorithms found in the literature, and discusses relevant papers. Chapter 3 describes the implemented clustering algorithms in detail, as well as the enhancements made to these algorithms via the addition of physical information. Two cluster improvement heuristics are described in Chapter 4, which seeks to improve upon any initial set of clusters made by other tools. In Chapter 5, results from the implemented algorithms and heuristics are collected and compared. Finally, the findings are summarized in Chapter 6 with future directions outlined in Chapter 7.

## Chapter 2

## **Background**

Clustering serves many crucial functions in the FPGA CAD flow. First, it makes the placement problem smaller. By clustering BLEs into CLBs, the number of blocks that the placement tool needs to deal with decreases substantially. This tends to translate into reduced CPU requirements. The second advantage of performing clustering is that it eliminates Design Rule Checks (DRC) during placement. While making CLBs for a given FPGA architecture, the constraints of CLBs are strictly observed. Therefore, during placement, CLBs can be moved around without the need to worry that the move will result in an infeasible placement. For placement algorithms such as simulated annealing, where thousands of CLB moves are made while placing the circuit, the elimination of DRC checks can significantly speed up the placement process. Lastly, but most importantly, the main objective of clustering is to absorb signals and/or critical connections into CLBs. Critical connections are those connections that are important to the performance of the circuit. The absorption of critical signals into CLBs tends to improve the overall timing performance of the circuit since critical connections do not need to be routed between CLBs. The absorption of signals in general, whether critical or not, tends to reduce the number of signals that require routing between CLBs. This also has a great impact on the overall routability of the circuit.

Clustering can be broken up into two stages: register packing, and clustering. During register packing, the LUTs and registers of the primary netlist are packed into BLEs. In the second step,

the BLEs are clustered to form CLBs. The focus of clustering optimizations is on the second stage, since register packing is fairly straightforward.

The clustering problem is inherently different between FPGAs and ASICs. In ASICs, the main purpose of clustering is to group together standard cells so that the placer will have fewer aggregates to deal with. However, in FPGAs, because of their many architectural features and constraints, the primary objective is to create architecturally legal blocks of logic, rather than to reduce the size of the placement problem. Clustering algorithms can generally be grouped into two categories: seed-based, and depth-optimal methods. Seed-based algorithms work by forming one CLB at a time using an objective function. Depth-optimal methods tend to focus on improving the timing aspect of the circuit, and seek to optimize its performance by duplicating timing-critical logic during clustering.

This chapter seeks to provide an overview of the basic clustering algorithms, and a survey of existing literature. There have been substantial investigations conducted on the optimization of the clustering step. In Section 2.1, the algorithm used during register packing is briefly described. Section 2.2 discusses seed-based clustering algorithms. Depth-optimal techniques, such as logic duplication, are shown in Section 2.3. A brief survey of ASIC clustering algorithms can be found in Section 2.4. There has been some recent work that involves combining the clustering step with the placement step, and these are discussed in Section 2.5. Finally, the connection of the literature discussed to the work presented in this dissertation is shown in Section 2.6.

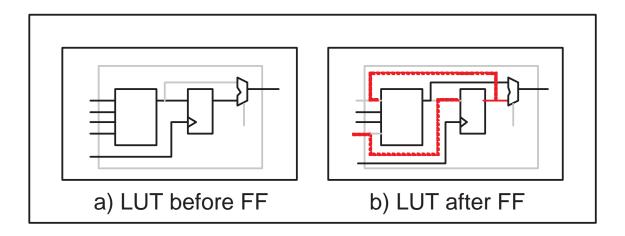

## 2.1 Register Packing

The first stage in clustering is the formulation of BLEs from the LUTs and registers in the netlist. A BLE can contain at most a LUT node and a register node, and will have only one output. Therefore, a register can only be packed with a LUT node if one of the outputs is not needed outside the BLE. This can occur in two situations, as illustrated in Figure 2.1. The first situation occurs when the output of the LUT goes only to the input of a register, and is not required by any other node in the netlist. The second situation occurs when the output of a register is only used as an

Figure 2.1: Possible BLE Configurations

input to a single LUT node. In this case, the LUT and register can be packed together as long as it does not violate the input constraints of the BLE. In Figure 2.1a, the absorbed net exists between the output of the LUT and the input of the register. However, in Figure 2.1b, the absorbed net is between the output of the register, and the input of the LUT.

The basic register packing algorithm is shown in Figure 2.2. For every register, its input and output nets are examined. If the net only has two terminals, and the terminal is a LUT, then this register is grouped with the LUT to form a BLE. At the end of register packing, all unclustered nodes are placed into separate BLEs.

## 2.2 Seed-Based Approaches

Seed-based methods are among the most established techniques for clustering BLEs in FPGAs. In such methods, CLBs are made greedily one at a time until every BLE has been clustered into a CLB. Seed-based approaches typically aim to minimize the number of CLBs formed, but can also be modified to take into account other objectives such as timing and power constraints.

One of the most widely known academic seed-based clustering tools is VPack and its timing-driven version T-VPack [26, 27]. In addition to trying to pack CLBs to capacity, T-VPack also accounts for the timing performance of the circuit by attempting to absorb netlist connections that

```

Procedure: REGISTERPACKING

Inputs: A primary netlist to be packed, N

Returns: A packed BLE-level netlist, N'

for each register i \in N do

clus ← new Cluster;

2

clus.add(i);

3

for each edge e \in i and i is unclustered do

4

if e is an input edge to i and getNumTerminals(e) == 2 then

5

driverNode \leftarrow get the driver of edge e;

if driverNode is a LUT then

7

clus.add(driverNode);

continue;

fi

10

11

if e is an output edge of i and getNumTerminals(e) == 2 then

12

sinkNode \leftarrow get the sink of edge e;

13

if sinkNode is a LUT and sinkNode and i can be added in the same cluster then

14

clus.add(sinkNode);

continue;

16

fi

17

fi

18

od

19

20

// At this point, all unclustered blocks go into their own BLE

for each unclustered block i \in N do

clus ← new Cluster;

23

clus.add(i);

24

25

od

return N';

```

**Figure 2.2:** Pseudocode for Register Packing.

are deemed to be timing critical. The packing algorithm of VPack and T-VPack starts with the selection of a seed BLE. The BLE with the most fully utilized inputs is usually selected as the seed BLE for a CLB. When timing is of importance, the most timing critical BLE is used as the seed of a CLB. Additional BLEs are added to the CLB until no more BLEs can be added without exceeding CLB constraints, such as number of BLEs per CLB or the number of pins available on the CLB. To choose which BLEs to add to the CLB, a gain value is calculated for every BLE that shares an edge with the current CLB, using a cost function. The gain is a function of the number of shared edges between the BLE and the CLB, and the criticalities of shared edges. T-VPack has been used extensively in academic research as the clustering tool to which all other clustering algorithms are compared against.

Two algorithms of note are present in T-VPack: hill climbing, and unrelated logic clustering. Hill climbing is an addition to the basic flow where BLEs are continually added to the CLB even after the number of inputs has been exceeded. This is done in the hope that an additional BLE will actually reduce the number of inputs needed for the CLB. This can occur when the output of a BLE is needed within the CLB as shown in Figure 2.3 [16]. The third BLE in the diagram generates the signal that is needed as an input in the first group of BLEs. By adding this BLE to the CLB, the input count can actually be reduced by 1, since the signal c can be generated locally without needing to route it from external sources. However, in general, this is shown to have limited benefits, with at most 1-2% improvement in logic utilization [16]. The second algorithm allows unrelated logic to be packed together if some CLBs are not full. In this case, BLEs that do not share any inputs or outputs with the current CLB is still added, as long as no CLB constraints are exceeded. This allows T-VPack to pack as tightly as possible.

Although T-VPack can achieve very good results, it does not always give the most optimal answer. It is possible that the unrelated logic packed in this stage is best grouped elsewhere where a greater gain in edge reduction or critical delay is possible. Also, if a group of highly connected BLEs span more than one CLB, it is possible that by rearranging BLEs within the larger group, the edges connecting the CLBs can be reduced.

**Figure 2.3:** Hill Climbing Example from [16]

RPack is proposed in [15]. Like VPack and T-VPack, RPack also packs BLEs one at a time starting with a seed BLE. However, RPack extends VPack by integrating routability into the clustering step to reduce the number of wires required in the routing channel [15]. This is performed by adding a term to the cost function. This extra term accounts for routability by calculating the number of shared input and output pins between an unclustered BLE and the current CLB. This routability term also penalizes BLEs that do not share anything with the current CLB, to deter this algorithm from putting them together. Compared to VPack (non-timing-driven T-VPack), previous research [15] show that RPack can significantly improve circuit routability. However, this research [15] focused only on routability—no performance numbers were presented to indicate the impact of packing for routability on the final quality of the result in terms of timing. Additional research [14] provides numerical results that show that while RPack outperforms VPack, it only produces results that are comparable to T-VPack.

In iRAC [14], another routability-driven packing algorithm is described. This algorithm is also seed-based and packs CLBs one at a time. However, the selection of a seed BLE is different from the method employed by T-VPack. iRAC selects seed BLEs based on its connectivity factor c. This is calculated via Equation 2.1, where the separation of a BLE is the sum of the number of terminals on nets connected to the BLE, and the degree is the number of nets directly connected to the BLE.

$$c = \frac{separation}{degree^2} \tag{2.1}$$

This connectivity factor increases the importance of BLEs that have more low-fanout nets. By starting with BLEs that have low-fanout nets, it increases the likelihood that additions to the CLB will result in nets being absorbed in their entirety. Thus, these nets can be removed from the resulting clustered netlist. Since the router will have fewer edges to route, this makes the routing step easier. Another key idea presented in iRAC is the use of Rent's Rule during clustering. iRAC limits the the number of pins that are usable on any CLB to match the Rent parameter of the architecture. By reducing the number of usable pins on CLBs, the demand on the routing channel is also reduced. Numerical results [14] indicate that the improved selection of the seed BLE coupled with the use of the Rent parameter can reduce the number of inter-CLB edges by roughly 30% compared to RPack and T-VPack for the case of 8 BLEs per CLB architecture. However, the number of used CLBs increased substantially by 5% to 6%. This may become a problem in a highly utilized device. Although edge reduction results are encouraging, the effect on performance is unknown since no performance numbers were presented in this paper.

#### 2.3 Depth-Optimal Methods

While capable of achieving very tight packings, seed-based approaches are localized, greedy algorithms that may become trapped in local minima. Another set of methods, called depth-optimal or depth-relaxed methods, seeks to optimize the performance of the circuit by duplicating timing-critical logic during clustering. Through the process of node duplication, a set of CLBs with optimal depth can be obtained through the use of a variety of post-processing, bin-packing methods. TLC [28], MLC [29] and RCP [30] are all examples of depth-optimal clustering tools. These three methods are all multi-level clustering algorithms, with an emphasis on producing timing-optimal designs. The advantage of these methods is that they enable a more global view of

the circuit to be taken. Although most often used for hierarchical FPGAs in which CLBs are futher grouped together (e.g., the Altera APEX20K [31]), they work just as well in architectures with only 1 level of hierarchy. Therefore, these methods still apply to the island-style FPGAs considered in this thesis, where the only hierarchy is that in which BLEs are grouped into CLBs.

In depth-optimal algorithms, three phases are performed: a labeling phase, a clustering phase and a packing phase. In the labeling phase, each node in the circuit is labeled with its depth-optimal delay from the primary inputs of the network. This is performed by traversing the netlist from primary inputs to primary outputs. This generally results in a large number of highly underutilized CLBs. Then, in the clustering phase, the network is traversed from primary outputs backwards to the primary inputs, and a subset of CLBs are selected such that the entire network can be covered. However, there is usually still a large number of CLBs. Therefore, a third phase is needed to pack the CLBs tighter to reduce the number of CLBs needed.

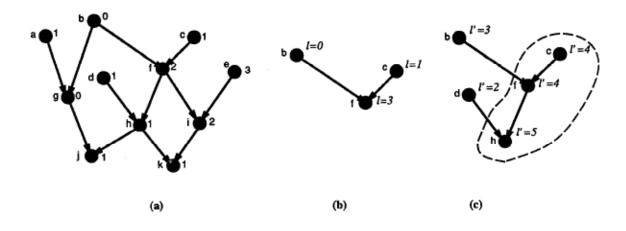

An example of how typical depth optimal methods work is shown in Figure 2.4 and Figure 2.5. These figures, found in [32], describe the process of logic duplication used in conjuction with a depth-optimal algorithm to reduce timing delays. The labelling phase is shown in Figure 2.4. Figure 2.4a depicts a graph that represents a circuit with a, b, c, d, and e as primary input nodes, and f and f as primary output nodes. The delay of each node is shown in the graph by a number next to the node, with all inter-cluster delays set to be 3. The architecture of this example is 3 BLEs per CLB. The labels are computed by traversing the graph from primary inputs, to assign the maximum delay encountered at each node. Thus, it can be seen in Figure 2.4b that f has a delay of 3. Then, as we propagate the delays forward from f to f, we consider the entire subgraph based at f, shown in Figure 2.4c, and calculate accordingly. If the cluster is performed as circled in Figure 2.4c, then there will not be any inter-cluster delay between f and f, and its label is only increased by its internal delay.

After labels have been computed for the entire circuit, the clustering phase of the algorithm is executed, propagating backwards from the primary outputs, to form the optimal set of clusters shown in Figure 2.5. As evident from the clusters shown, nodes b and f have been duplicated.

**Figure 2.4:** Depth-Optimal Example: The Labelling Phase [32]. (a) Circuit graph (b) Labels of nodes b, c, and f (c) Computing the label of h

The strength of depth-optimal algorithms is in that they can dramatically shorten timing-critical paths by absorbing them within the CLB. However, in the process of such reductions, logic must be duplicated to provide maximum benefits. Logic duplication can therefore get out of hand very quickly. Although effective at reducing critical path delay, previous experimental results indicate that the process of logic duplication can be hard to control, leading to large increases in area. Also, minimizing logic depth does not mean a reduction in wire length in modern designs. Although the use of timing information during clustering can lead to a better set of clusters, recent research indicates that timing estimates made during clustering may not be accurate when compared to the final placement [33].

## 2.4 ASIC Clustering Algorithms

It is worth mentioning that a substantial set of literature exists on ASIC clustering techniques [34–37]. The main difference between the ASIC and the FPGA clustering problem is that there are no CLBs in ASICs. Therefore, there are no CLB constraints that need to be taken into account. The main objective of ASIC clustering algorithms is to create larger aggregates of highly connected nodes so as to speed up placement. In contrast to the BLEs and CLBs for FPGAs, the netlist for

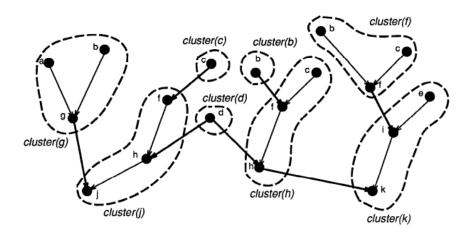

**Figure 2.5:** Depth-Optimal Example: Optimal Clustering of Figure 2.4a from [32]

ASICs includes macro blocks, and standard cells or nodes.

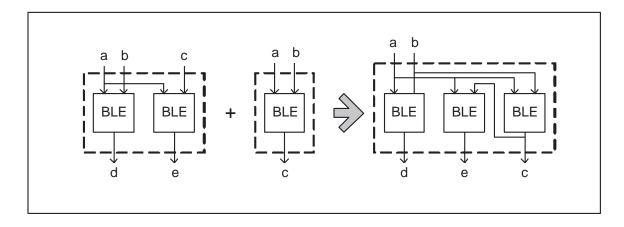

ASIC clustering methods are usually affinity-based, and work on many clusters simultaneously. Examples of affinity-based algorithms used in the ASIC CAD flow include Best Choice [38], First Choice [39], and Hybrid First Choice (HFCC) [40, 41]. At the beginning of clustering, HFCC [41, 42] computes the affinity of every possible pair of nodes. After sorting the calculated affinities, it starts to make pairings between nodes to form clusters by pairing nodes with the highest affinities to each other. If the nodes in question are already clustered, then the possibility of merging this additional node into the existing cluster is investigated. This process of pairing is continued until no more merging of blocks can be made without violating cluster constraints.

One of the advantages of affinity-based methods is that, unlike seed-based methods, affinity-based methods work on multiple clusters at the same time. Therefore, it is not concerned with the minimization of cluster count. Because of the greedy nature of seed-based algorithms, clusters are packed as tightly as possible. Although this is benefical in terms of area reduction, it is possible that blocks may be added early on that are better off clustered with other, still unclustered, blocks. This problem does not exist in ASIC clustering, since there aree no CLB constraints to take into consideration. This means that the algorithm is always making the best possible decision. Since it is not limited by dense packing, affinity-based methods ensure that good decisions are always

made. However, the side effect of this method is that affinity-based methods produce a much higher number of clusters than seed-based algorithms, which may be problematic if applied to FPGAs. As described later in Chapter 3, an attempt was made to adapt these methods mentioned here to FPGAs with mixed results.

## 2.5 Simultaneous Clustering and Placement

In the traditional FPGA CAD flow, the clustering step is completed before placement is performed. Normally, placement tools such as VPR perform placement on the netlist of CLBs, and make moves by swapping CLBs between locations on the FPGA grid. However, in recent years, an alternative has been investigated such that BLEs are allowed to move between CLBs during the placement step. This in turn restructures CLBs that were previously formed in the clustering stage. The advantage of performing BLE-level moves during placement is that physical information, as well as more accurate timing information, can be used to make better CLBs. An example of this can be found in SCPlace [43]. SCPlace implements a simulated annealing-based placement method that is capable of moving both CLBs and BLEs. SCPlace uses T-VPack to generate an initial set of CLBs which are feasible for the architecture (i.e., an initial packing must still be performed). Then, during placement, both CLB-level and BLE-level moves are performed. It is fairly easy to make a CLB-level move. However, when BLEs are moved between CLBs, CLB constraints must be observed before the benefit of the move can be evaluated.

SCPlace also implements the net weighting algorithm proposed by Kong [44] to improve its performance. Through experimentation, substantial reductions in wire length of up to 36% and critical path improvement of up to 31% can be found, when compared to VPR (which performs no reclustering and only moves CLBs). It was found that the combination of CLB- and BLE- level moves produce the best results. By performing only 10% of the number of CLB moves that VPR performs, SCPlace was able to compensate for the time it uses to do BLE moves. The significance of SCPlace is that it demonstrates the importance of physical information in correctly predicting wire length and delay information.

However, BLE moves are expensive to make. In modern FPGA architectures, there are many more constraints, such as carry chains, to consider in a CLB. Therefore, each time a BLE move is considered, the legality of the proposed move must be verified. Since there are many such constraints in commercial FPGAs, this DRC check can take a much larger proportion of runtime execution if used in a commercial setting. Hence, if similar results can be achieved by altering the clustering stage with physical information, the need for BLE moves during placement can be eliminated. This should also improve overall runtime of the FPGA CAD flow.

Finally, reclustering can also occur at the end of placement. It is here that physical optimizations can be made, often by exploiting physical information obtainable at this point [45]. Logic replication can also be found at the placement level for FPGAs [46]. Critical paths can be *straightened* whenever possible by means of duplicating logic. An example is shown in Figure 2.6 [46].

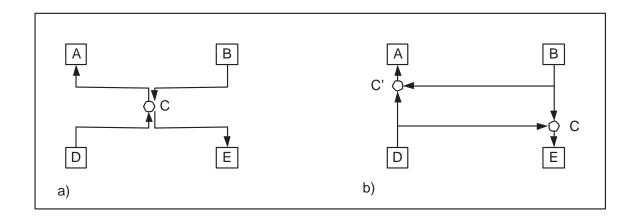

In Figure 2.6a, there are 4 paths going through node c, between fixed output nodes of a and e, and input nodes of b, and d. If no logic duplication is allowed, then node c would have to be placed in the center to minimize the maximum path delay of all paths. However, if node c can be duplicated to create a copy c', then it may be possible to place nodes c and c' in the arrangement shown in Figure 2.6b. In this case, the paths have been straightened, and it can be seen that the length of all paths have effectively been cut in half. By straightening the path, the impact of routing delays on the critical paths can be minimized. However, these physical optimizations do require reclustering and relegalization of the design, and are beyond the scope of this thesis.

#### 2.6 Relation of Past Literature to Current Research

The goal of this work is to develop a new clustering algorithm that can outperform the clustering algorithms mentioned. By extracting the positive characteristics from the existing approaches, it is hoped that a better clustering approach can be found. The investigation carried out in this thesis research is essentially a hybridization of ASIC techniques and seed-based approaches. The key idea is to perform partitioning, such as algorithms normally occurring during placement, to

Figure 2.6: Logic Duplication Example [46]

obtain the approximate physical location of BLEs. Then, a seed-based clustering algorithm can be performed while utilizing the additional information. It is hoped that through the use of physical information, the advantages of both approaches can be realized. Therefore, physical information is incorporated into the seed-based clustering algorithm from T-VPack. By clustering with some physical information, potentially better clusters can be made, which may lead to better performance of the final placement.

In this thesis research, two packing algorithms—called DPack and HDPack—are introduced. These three algorithms produce *better initial packings*, which in turn reduce the dependence on computationally-expensive BLE-level placement. DPack and HDPack incorporate the concept of "physical clustering" [41] within a novel hybrid framework for timing-driven FPGA packing. These techniques employ a quick min-cut, partitioning-based global placer to determine *approximate* BLE locations. By using this information, these tools are capable of making more informed decisions which, in turn, can lead to reduced wire lengths and critical path delays.

## **Chapter 3**

## **Clustering Algorithms**

From Chapter 2, it can be seen that seed-based and depth-optimal algorithms have been widely used and adapted for FPGAs. Both types of clustering algorithms generally have very fast runtimes and provide good solutions. However, the depth-optimal methods generally provide better performance than seed-based algorithms. Since depth-optimal methods are allowed to duplicate timing-critical nodes, the critical path delay of circuits can generally be shortened. Although these methods give good performance gains, an area increase is inevitable and can sometimes be quite substantial. Simultaneous clustering and placement methods also show promise by allowing the contents of clusters to change during placement. However, since each change in cluster content must be preceded by a DRC check, the runtime of such algorithms is greater than clustering algorithms Therefore, the focus of the research here is to improve upon the most widely used seed-based clustering algorithms, and attempt to achieve equivalent, or better, results found in the existing literature without the use of node duplication or BLE-level moves in placement. Although BLE-level placement algorithms will likely remain a necessity in commercial FPGA placement, it is the premise of this work to reduce the reliance on this step by producing better CLBs in the first place. The idea is to create a better set of clusters, and a better final placement, without incurring area or runtime penalties. To this end, several known algorithms have been implemented and modified to see whether the results can be improved in ways other than node duplication and

BLE-level placement algorithms.

Two clustering algorithms are implemented as part of this thesis research. First, the primary algorithm, called DPack, is discussed in Section 3.1. Section 3.2 describes a second algorithm, called HDPack, which is an extension to DPack by hybridizing it with an affinity-based algorithm. The process of augmenting both algorithms with physical information is presented in Section 3.3.

## 3.1 Greedy Packing (DPack)

In pursuit of better clusters, a seed-based packing algorithm, similar to T-VPack, was developed. The pseudocode for this clusterer, DPack, is shown in Figure 3.1. Like T-VPack, a seed BLE is selected as the most critical, unpacked block. Kong's path counting algorithm [44] was implemented as a tie-breaking mechanism during seed selection, with the block that has the highest path count selected as the seed. It should be noted that logic depth is also used as a secondary mechanism to break ties [16]. After the seed BLE has been chosen, a cost function is computed for all blocks that are connected to this BLE. This cost function is given by

$$Cost_{ij} = \lambda \times E_{ij} + (1 - \lambda) \times Crit_{ij}$$

(3.1)

where

$$E_{ij} = \sum_{e \in E_h \mid i,j \in e} \frac{1}{|e| - 1}$$

and  $Crit_{ij} = \sum_{e \in E_h \mid i,j \in e} Criticality(e)$ .

Here,  $E_h$  represents all nets in the netlist,  $E_{ij}$  models connectivity, and Criticality(e) is the estimated timing criticality of net e. From this equation, it can be seen that each net is weighted by the number of terminals on it, similar to [47]. This increases the importance of nets that have fewer fanouts, and increases the likelihood that they will be absorbed. In Equation 3.1,  $\lambda$  varies between 0 and 1 and controls the preference between edge absorption and timing criticality. The BLE with the highest computed cost is added to the CLB. This is continued until either the CLB is

full, or other constraints, such as the number of pins available on the CLB, are exceeded. Then, a new seed BLE is chosen to start a new CLB, and the process is repeated until the circuit has been packed.

DPack also incorporates the hill-climbing and unrelated logic packing algorithms from [16]. When the pin constraints of a CLB have been reached, but the CLB is not full, the clusterer enters a hill-climbing phase; BLEs are continuously added to the CLB even if the number of pins on the resulting CLB exceed what is feasible. This is done in the hopes that, by adding more BLEs to the CLB, the number of pins can be reduced as more edges are absorbed. If, after reaching the maximum number of BLEs per CLB, the pin constraints are still violated, the last feasible arrangement is restored. If a CLB is not full, then additional BLEs that have no direct connection (i.e., unrelated logic) with the BLEs in the CLB may be added provided that the CLB constraints are not violated.

## 3.2 Hybridized Packing (HDPack)

The second clustering algorithm is built on DPack. For this approach, an affinity-based algorithm was incorporated into the clustering flow. This affinity-based algorithm, called Hybrid First Choice clustering (HFCC), has been successfully used in ASIC clustering. Since HFCC has been applied successfully to large-scale placement, it seems worthwhile to explore the usefulness of this algorithm in the context of FPGA placement. First, Section 3.2.1 describes the HFCC algorithm, and Section 3.2.2 provides the details of the hybridization of HFCC and DPack.

#### 3.2.1 Affinity-Based Packing (HFCC)

In HFCC, objects are initially placed onto a "free" list which contains the set of objects which have not been paired. The *affinity* for pairing any two objects is calculated using Equation 3.1 [41]. Then, starting with the highest affinity value, pairings are made between the specified blocks, which may be unclustered BLEs or clusters, as long as no CLB constraints are violated. The

```

Procedure: DPACK

Inputs: A netlist to be packed, N

Returns: A packed netlist, N'

Perform timing analysis on the circuit;

Compute block criticalities via Kong path counting;

2

Sort block criticality from highest to lowest;

seedBLE \leftarrow most critical unclustered node;

while seedBLE > 0 do

clus ← new Cluster;

clus.add(seedBLE);

while clus.getNumBLEs() < maxNumBLEsPerCLB do

for each BLE that shares an edge with clus do

9

Calculate the cost according the equation;

10

if BLE can be added (passes DRC) then

11

costVector.add(BLE, cost);

12

fi

13

od

14

BLEtoAdd \leftarrow getHighestCostBLE(costVector);

15

if BLEtoAdd is not valid then

16

BLEtoAdd ← get best unrelated BLE to add;

17

18

if BLEtoAdd is valid then

19

clus.add(BLEtoAdd);

20

else

21

break:

22

fi

23

24

Add clus into N';

25

26

seedBLE ← most critical unclustered node;

27

od

return N';

28

```

**Figure 3.1:** Pseudocode for DPack.

algorithm repeatedly removes the object with the highest affinity from the free list, and pairs it with the object that (originally) yielded this high affinity, even if that object had already been paired. Once an object has been paired, it is said to have formed a "cluster". Pairings are made continuously, until no more pairings can be made without exceeding CLB constraints. The basic pseudocode for the affinity clustering algorithm is found in Figure 3.2.

HFCC has the advantage of making CLBs simultaneously, without the worry of packing clusters to the fullest. However, the algorithm can terminate with a large number of CLBs. This is due to the fact that ASIC clusters do not have constraints such as in FPGAs. ASIC clusters are not required to pack for a minimum number of clusters, and hence there is no need to pack unrelated logic. This is not a deficiency in ASIC clustering algorithms; rather, this is only seen as a deficiency when these algorithms are applied to FPGAs. However, this makes it difficult to compare results fairly to other clusterers that pack for minimum area. Also, this artificial bloat in the number of clusters wastes FPGA area, and affects the performance of the circuit design. This large set of clusters can be difficult to pack together in later stages of the algorithm due to pin constraints and a lack of a hill-climbing phase. Consequently, HFCC packings typically contain several percent *more* CLBs than DPack or T-VPack; for highly-utilized devices, this can be a significant drawback.

In practice, this algorithm is followed by several post-processing steps to reduce the number of clusters. These steps include the merging of single BLEs into CLBs when possible, and the merging of half-filled blocks. However, these post-processing routines are inherently greedy, and the only optimization goal during this phase is to minimize the number of clusters. This is similar to depth-optimal methods (without duplication) in which the bin-packing applied after the initial clustering cannot effectively group clusters together to reduce the CLB count. This may have a detrimental effect on the quality of clusters, both in terms of wire length and critical path delay.

#### 3.2.2 Formulation of HDPack

Both DPack and HFCC have numerous associated advantages. HFCC is noted to be very effective at making good pairwise packings and in minimizing the number of external nets in the clustered

```

Procedure: HFCC

Inputs: A netlist to be packed, N, StoppingCost

Returns: A packed netlist, N'

//Do affinity clustering ...

for each edge e \in N do

for each cell i, j \in e do

Cost_{ij} \leftarrow compute affinity cost for pairing i, j;

4

od

5

od

6

Sort all affinity Cost_{ij} from largest cost to lowest;

StoppingCost \leftarrow predetermined Cost_{ij} value at which to stop;

for each Cost<sub>ij</sub> do

Attempt to pack cell i and j together;

10

if DRC was not successful then

11

continue;

12

13

if Cost_{ij} < StoppingCost then

14

break;

15

fi

16

od

17

18

return N';

```

**Figure 3.2:** Pseudocode for HFCC.

netlist. However, it often creates a large number of CLBs, and the employed post-processing routines have a negative impact on the quality of clusters made. In contrast, DPack is known to achieve good critical delay reduction while being able to pack for a minimum number of CLBs. Thus, it is proposed to combine the two approaches in order to take advantage of the benefits of both DPack and HFCC. It is hoped that this hybridized flow, HDPack, can yield the same high net absorption offered by HFCC, while still preserving the critical delay reduction from DPack. The pseudocode for HDPack is shown in Figure 3.3.

In this combined approach, HFCC is used as a *pre-packing* step before DPack is called to perform clustering. First, HFCC is used to make initial pairings; when the affinity values of the pairings in the HFCC packer fall below a certain threshold, HFCC packing is stopped. At this point, a large number of CLBs is generally required. However, unlike HFCC, none of the original post-processing routines are used. Instead, this list of "intermediate" clusters is fed to DPack to complete the clustering process. In this stage, DPack looks at this set of clusters, and computes costs using Equation 3.1. Then, it starts to fill CLBs, starting with the CLB that has the highest number of contained BLEs, highest number of used pins, and highest criticality. The BLE with the highest computed cost is then added to the CLB until the CLB becomes full. However, unlike DPack, it is possible that the BLE has already been packed into another CLB by HFCC. In this case, the BLE will be removed from its current cluster and added to this CLB only if its original CLB was *not* full.

The effectiveness of HDPack has a strong dependency on the handoff point between HFCC and DPack. If HFCC performs too few affinity-based matches, the true benefit of the hybridization may not be visible. On the other hand, if HFCC almost finishes off all the possible pairings, DPack may not have enough room to achieve a minimum set of clusters without significantly messing up the decisions HFCC made. Therefore, this handoff point, or threshold, must be clearly analyzed, parameterized, and the possible values swept to determine the best configuration. This point is calculated according to Equation 3.2, where  $Aff_{max}$  and  $Aff_{min}$  are the maximum and minimum affinities found, respectively. The hybrid cutoff value,  $\beta$ , is a parameter that is then swept from 0 to 1 to see which value provides the best wire length and critical delay improvement. If the affinity

values fall below the calculated threshold, HFCC terminates, letting DPack finish packing the rest of the blocks. In practice, it was found that this hybrid flow produces very good improvements in wire length and critical path delays over traditional methods.

$$Aff_{thres} = (Aff_{max} - Aff_{min}) \times \beta + Aff_{min}$$

(3.2)

## 3.3 Incorporating Physical Information

The concept of "physical clustering" has been employed successfully in ASIC placement for some time [41]. In these approaches, an initial placement for cells in the unclustered netlist is determined via a quick global placement operation. During this global placement, cells are allowed to overlap, since circuit legality is not a concern. The clustering method leverages the inter-cell distances from this approximate placement to make more informed "tie-breaking" decisions, and to make better clustering decisions when packing unrelated logic. The core of this research is to determine whether the same approach can be used in FPGAs with positive outcomes by incorporating physical information into the clustering algorithms described previously.

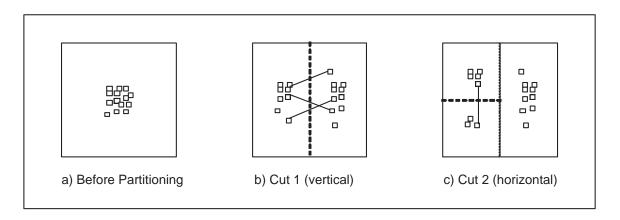

Before physical information was incorporated into DPack and HDPack, a simplistic, top-down, min-cut partitioning-based global placer was first developed. This placer uses hMetis [40, 48] to recursively bi-partition and place the primitive netlist. A sample figure illustrating how min-cut partitioning is typically performed is shown in Figure 3.4. First, all the nodes are placed onto the chip, with positions set in the centre as shown in Figure 3.4a. Then, these nodes are divided into two groups, or partitions, as shown in Figure 3.4b. This division between the nodes is called a cut. The objective of this cut selection is to minimize the number of nets that connect between the two sections. Thus, the algorithm encourages highly-connected nodes to remain within a common partition. After the nodes have been divided, each resulting region is then partitioned further, independently of the other partition. The nodes are then further distributed as shown in Figure 3.4c.

```

Procedure: HDPACK

Inputs: A netlist to be packed, N

Returns: A packed netlist, N'

Call HFCC to perform affinity-based clustering(N, StoppingCost);

2 // Finish off using greedy ...

Put each unclustered BLE into its own cluster;

Collect statistics (num pins, etc.) for each cluster;

Sort the list of clusters first (num BLEs contained, num pins, criticality);

seedClus ← cluster with highest # BLEs, highest # pins, highest criticality;

while seedClus is valid do

for each BLE B that shares an edge with clus (not in full cluster) do

8

Calculate the cost of putting B in seedClus;

9

if B can be added to seedClus without violating DRC then

10

costVector.add(B, cost);

11

fi

12

od

13

\texttt{BLEtoAdd} \leftarrow \ getHighestCostBLE(\texttt{costVector});

14

if BLEtoAdd is not valid then

15

BLEtoAdd \leftarrow get best unrelated BLE to add;

16

fi

17

if BLEtoAdd is in another cluster already then

18

Remove BLEtoAdd from its original cluster;

19

20

fi

if BLEtoAdd is valid then

21

22

seedClus.add(BLEtoAdd);

else

23

break;

24

25

if seedClus.getNumBLEs() = numBLEsPerCLB then

26

Mark seedClus as full, and therefore cannot be modified anymore;

27

28

fi

seedClus \leftarrow most fully used, yet still incomplete cluster;

29

od

30

return N';

31

```

**Figure 3.3:** Pseudocode for HDPack.

Figure 3.4: Min-Cut Partitioning Algorithm

This is performed recursively until some stopping criterion has been reached. During placement, this may occur when all nodes are suitably spread throughout the chip area, and physical locations can be assigned.

It should be noted that the technique used in this research does not employ placement feedback, or branch-and-bound partitioning, as in [49]. These methods are used to fine-tune the accuracy of a partitioner, and are not used since only a basic partitioner is required for our purposes. Placement feedback [50] is a method to make accurate terminal propagation during partitioning by using the concept of feedback from control system applications. Branch-and-bound partitioning [51] essentially enumerates partitioning solutions, and uses bounds to discourage unnecessary exploration.

Since accurate information is not necessary, the partitioning algorithm does not need to run to the point where every block has a unique location. Instead, this min-cut partitioning placer is augmented with a stopping criterion that depends on the number of nodes in the current partition. hMetis will then be recursively called until one of two conditions is reached. Once the number of nodes in a partition is either (a) less than a predetermined amount or (b) the depth of the partitioning tree has exceeded a threshold, the partitioning algorithm stops. The BLEs within the partition are then assigned the same x and y grid locations. It should be noted that this is perfectly acceptable since it is not the intention of this fast partitioning to generate legal placements, but rather, to

provide a rough idea of which BLEs may end up close together. Then, a clustering algorithm such as DPack or HDPack is executed.

To account for physical information, the cost function in Equation 3.1 is augmented with an additional cost term; the new cost function is given by Equation 3.3

$$Cost_{ij} = \lambda \times E_{ij} + \gamma \times Crit_{ij} - (1 - \lambda - \gamma) \times Dist_{ij}$$

(3.3)

where

$$Dist_{ij} = \frac{|x_i - x_j|}{GridSize_x} + \frac{|y_i - y_j|}{GridSize_y}$$

where  $E_{ij}$  and  $Crit_{ij}$  are the same as in Equation 3.1. In this formulation,  $\lambda$  and  $\gamma$  control the preference between edge absorption and timing, respectively. The  $Dist_{ij}$  term is a calculation of the Manhattan distance between the current CLB and the potential BLE, normalized by the grid size. As a consequence of this formulation, this cost *penalizes* objects that are far apart. Although several other formulations of the cost function were also considered and tested, this formulation was found to yield the best performance.

Another modification to DPack and HDPack was made in the way unrelated logic clustering is performed. In the original algorithm, any BLE that could fully utilize the remaining available inputs of a CLB was added. In practice, there can be many blocks with the same number of inputs. To break ties, we use the physical distance between the potential BLEs and the current CLB. Consequently, the BLE that is closest to the current CLB is added to the CLB.

# **Chapter 4**

# **Cluster Improvement Algorithms**

Since clustering is an important algorithm in the overall FPGA CAD flow, additional time spent on improving the quality of the resulting CLBs should be reflected in the final overall quality of placements. In addition to the clustering algorithms proposed in Chapter 3, two cluster improvement algorithms were implemented and investigated. These improvement algorithms are complementary to any of the aforementioned clustering algorithms. That is, the algorithms introduced in this chapter are not intended to produce an initial set of CLBs, but rather, to *further improve* on an existing set of CLBs. When used with a placement method such as SCPlace, these algorithms are still valid. If these cluster improvement techniques can be performed quickly, a better initial packing may be made. This better initial set of clusters would likely translate into both a better initial placement and a potential reduction in runtime due to the need to perform fewer placement perturbations to obtain a high quality final result.

Given an initial clustering of BLEs into CLBs, two heuristics are implemented to further improve upon the clusters. Both of the described heuristics work as follows. A number of improvement attempts are performed. In each attempt, a pair of CLBs is selected. This selection can be random or require that the selected pair of CLBs share some common connections. This requirement that CLBs share common connections makes sense; it is likely that to improve the absorption of edges — either for routability or for timing — a selected pair of CLBs must have some common edges

which can potentially be absorbed.

This chapter starts with the general outline of the improvement algorithms in Section 4.1. Then, in Section 4.2, a greedy improvement scheme is described that performs swaps and moves to improve the quality of clusters. Section 4.3 shows a branch-and-bound scheme that takes a different approach to improve clusters.

### 4.1 Overall Flow

Both cluster improvement algorithms take place *after* an initial set of CLBs has been created and works as follows; for a given set of CLBs, the algorithm selects pairs of CLBs — either random pairs of CLBs or pairs of CLBs that share common edges — and attempt to rearrange these two BLEs through either of the improvement heuristics described below. This rearrangement is then evaluated to see if an "improved" pair of CLBs can be obtained. The pseudocode for this overall flow is presented in Figure 4.1.

The two proposed heuristics differ in how they select BLEs to move. In Swaps and Moves, random BLEs are selected from each CLB and are either swapped (when two BLEs are selected to be switched) or moved (when one BLE is selected to move to an empty spot in the other CLB). The two CLBs are then evaluated to see if the quality, in terms of timing or wire length, has improved. The second heuristic is based on branch-and-bound, and enumerates all possible packings of BLEs into the pair of selected CLBs to find an improved packing of BLEs into CLBs.

## 4.2 Swaps and Moves

The first proposed heuristic involves the simple greedy swapping of BLEs between CLBs. This heuristic is similar to that originally proposed for ASIC clustering [47] in which the objective was to absorb as many edges as possible into clusters. Pairs of connected clusters were randomly selected and a cell (pair of cells) was moved (swapped) between the two chosen clusters. In

```

Procedure: IMPROVECLUSTERPAIRS

Inputs: A packed netlist, N

Returns: An improved packed netlist, N'

pass \leftarrow 1;

while pass < max_pass do

Select two connected CLBs i and j;

ImproveCLBs(i,j);

od

return N';

```

**Figure 4.1:** Outer Loop of Improvement Heuristics.

performing the swap, edges were weighted according to Equation 4.1

$$w_i = \frac{1}{p_i - 1} \tag{4.1}$$

where  $w_i$  and  $p_i$  represent the weight and number of pins on edge i, respectively. This weighting scheme tends to give priority to low fan-out edges which are easier to absorb completely into a cluster. Upon performing either a move or swap of cells between clusters, the total absorption of edges into the pair of clusters is computed. If the absorption of edges is improved, then the move (swap) is retained, otherwise it is discarded. In [47], the moves and swaps are performed using annealing such that it is likely some worsening swaps are chosen during the improvement heuristic. However, since only improving moves are allowed here, this implementation is greedy.

Several additions to the algorithm in [47] were necessary to adapt it for the FPGA. The above algorithm is purely driven by edge absorption. This usually has the effect of reducing wire length in the final routed circuit. However, for FPGAs, the critical path delay is also an important parameter to optimize for. To account for timing, a "unit-delay" timing analysis is performed and a slack for each connection i in the circuit is computed. The slack is used to compute a criticality for each connection given by Equation 4.2

$$Criticality(i) = 1 - \frac{slack(i)}{MaxSlack} \tag{4.2}$$

where *MaxSlack* is equal to the largest slack found in all the connections in the circuit. This criticality is then squared so that critical connections appear more critical, while relatively non-critical connections are ignored. The cost of a CLB is calculated by summing up the number of edges absorbed (as in [47]) *and* by summing up the absorption of critical circuit connections. If both edge absorption and criticality absorption are improved after either a move or swap, then the new arrangement of BLEs to CLBs is accepted. Otherwise, the original assignment of BLEs to CLBs is restored.

## 4.3 Branch and Bound

Although random greedy moves and swaps do improve clusters, this scheme may be somewhat limited in its ability to improve CLBs. For instance, it might be the situation that many attempts are made that do not meet the architectural constraints of the CLB. Furthermore, it might be necessary that *more than two* BLEs should change CLBs in order to obtain an improvement. To overcome the potential limitations of simple moves and swaps, an *enumerative* heuristic, which is based on branch-and-bound, is proposed to improve pairs of CLBs. Since the number of BLEs per CLB is limited to a fairly small number in modern architectures, branch-and-bound is practical. Furthermore, because of the enumerated nature of branch-and-bound, if a better packing of BLEs into CLBs exists, it will be found. Complex packing constraints such as limited inputs, outputs and control signal constraints are handled seamlessly by branch-and-bound.

This technique essentially performs a constraint-aware bin packing between two CLBs. The algorithm initially begins with no assignment of BLEs to either CLB. It then attempts to assign each BLE to the first CLB and then to the second CLB in a subsequent pass. When assigning a BLE to a particular CLB, the architectural constraints need to be obeyed. It should be noted that some computations must be performed carefully. For instance, to ensure that the input limits on a CLB are not violated, input counts cannot be simply be "incremented" when a BLE is assigned to a CLB. This assignment needs to be *deferred* until the location of the source BLE of an edge is known. If the source BLE of an edge is in the same CLB as this BLE, the edge is absorbed, and thus will not

add to the input count of the CLB.

The general outline of the algorithm is very similar to the end-case partitioner introduced in [51], and is provided in Figure 4.2. The method begins by assigning every BLE in the 2 CLBs to either one or the other, and checks for feasibility. If it is a feasible solution, then its cost is found and the method checks to see if the solution can be bound. Appropriate information is kept during the enumeration to improve both the absorption of edges as well as the absorption of connections deemed to be timing critical; various stacks are kept in order to be able to track the current edge absorption and criticality absorption.

```

Procedure: BRANCHANDBOUND

Inputs: Two CLBs clus<sub>i</sub> and clus<sub>i</sub>

Returns: Two potentially better CLBs clus' and clus',

Compute the current cost of clusters i and j

bestSoln = empty;

assignmentStack.add(clus<sub>i</sub>.nodes() and clus<sub>i</sub>.nodes());

for each k of 0 and 1 do

\texttt{currentNode} \leftarrow last \ node \ in \ \texttt{assignmentStack};

if k = 0 then

assign currentNode to clus;

else

8

assign currentNode to clus_i'

9

10

if arrangement is feasible then

11

check if it is boundable

12

if boundable then

13

pop currentNode from assignmentStack

14

if assignmentStack.empty() and k = 0 then

15

break

16

fi

17

else if all nodes have been assigned then

18

a complete solution that is the best one found so far

19

bestSoln \leftarrow current \ assignment

20

fi

21

else

22

the arrangement is infeasible, and is bound

23

24

25

od

return clb'_i and clb'_j;

26

```

Figure 4.2: Pseudocode for Branch and Bound.

# Chapter 5

# **Numerical Results**

To measure the effectiveness of the algorithms implemented as per Chapter 3 and 4, several experiments were conducted. This chapter documents the many investigations carried out using the implemented clusterers, and is organized as follows. In Section 5.1, the method through which the algorithms are evaluated is described. This section also defines several key metrics that are used during comparison. Section 5.2 compares DPack and HDPack both with and without the use of physical information. In Section 5.3, the impact of the accuracy of physical information has on the quality of the routed designs is investigated. Then, DPack and HDPack are compared with other existing tools in Section 5.4. In Section 5.5, several concepts from other tools were integrated into these algorithms to see if any additional improvement can be achieved. Section 5.6 presents the results from the use of cluster improvement heuristics from Chapter 4.

### 5.1 Experimental Setup

To make a fair comparison between the implemented tools and other existing clustering algorithms, the twenty largest designs from the MCNC benchmark set were used [52]. The circuits in this set vary in size and circuit structure. The benchmark set has been used widely in academic research for FPGAs, and facilitates direct comparisons to be made to other known clustering tools.

#### **5.1.1** General Experimental Flow

Before any comparisons can be made, a baseline must first be established. In the comparisons that follow, the baseline flow uses T-VPack, followed by VPR for placement and routing. Then, to compare the clustering algorithms outlined in Chapter 3, DPack and HDPack were employed to perform packing. The resultant netlists are then placed and routed by VPR. The three constructed flows can be summarized as follows: (1) the baseline flow of T-VPack+ VPR, (2) DPack + VPR, and (3) HDPack + VPR.

A good clustering algorithm should be able to perform well under a variety of situations and constraints. Therefore, the implemented clustering algorithms were tested on a set of FPGA architectures. The range of architectural sizes used corresponds to  $N = \{2,4,8,12\}$  BLEs per CLB. By using both large and small CLB sizes, it becomes possible to determine whether a particular clustering algorithm can perform well in all cases. For each architecture, the number of CLB inputs is calculated as I = 2N + 2. This was shown to yield good area efficiency by achieving an average of 98% logic utilization [26]. The grid size is set to the smallest square grid that can accommodate a particular design.