## Design, Optimization and Fabrication of Amorphous Silicon Tunable RF MEMS Inductors and Transformers

by

### Stella Chang

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2006

©Stella Chang 2006

I hereby declare that I am the sole author of this thesis.

I understand that this thesis may be made available to other institutions or individuals for the purpose of scholarly research.

Stella Chang

### Abstract

High performance inductors are playing an increasing role in modern communication systems. Despite the superior performance offered by discrete components, parasitic capacitances from bond pads, board traces and packaging leads reduce the high frequency performance and contribute to the urgency of an integrated solution. Embedded inductors have the potential for significant increase in reliability and performance of the IC. Due to the driving force of CMOS integration and low costs of silicon-based IC fabrication, these inductors lie on a low resistivity silicon substrate, which is a major source of energy loss and limits the frequency response. Therefore, the quality factor of inductors fabricated on silicon continues to be low. The research presented in this thesis investigates amorphous Si and porous Si to improve the resistivity of Si substrates and explores amorphous Si as a structural material for low temperature MEMS fabrication.

The process development for depositing thick amorphous Si films at low temperature with good uniformity and surface roughness is presented. The film is optimized for our proposed application with acceptable optoelectronic properties and mechanical stress. Porous Si is also studied as another candidate to improve the resistivity of Si substrates. A Teflon etch cell was machined to electrochemically form porous Si at room temperature and the process conditions are optimized to achieve thick films with suitable porosity for multi-layer applications.

Planar inductors are built-on undoped amorphous Si in a novel attempt to improve the isolation of RF passive devices from the low resistivity Si substrate. A 56% increase in Q was measured by incorporating a thick amorphous Si film before depositing the underpass of the inductor. Planar inductors are also built-on a porous Si and amorphous Si bilayer and showed 47% improvement in Q compared to the same structure without a porous Si layer.

Amorphous Si is proposed as a low temperature alternative to polysilicon for MEMS devices. Tunable RF MEMS inductors and transformers are fabricated on low resistivity Si in a six mask process. The design concept is based on an amorphous Si and Al bimorph coil that is suspended and warps in a controllable manner that is accurately predicted by thermomechanical simulations. The tuning of the devices is achieved by applying a DC voltage and due to joule heating the air gap can be adjusted. A tunable inductor with a

32% tuning range from 5.6 to 8.2 nH and a peak Q of 15 was measured. A transformer with a suspended coil demonstrated a 24% tuning range of the mutual coupling between two stacked windings.

The main limitation posed by post-CMOS integration is a strict thermal budget which cannot exceed a critical temperature where impurities can diffuse and materials properties can change. The research carried out in this work accommodates this temperature restriction by limiting the RF fabrication processes to 150°C to facilitate system integration on silicon.

### Acknowledgments

At the start of my life as a grad student, completing a thesis seemed like an impossible task. Now as I look back, I know I would not have gotten to this point if it weren't for the support of a number of people. I would like to thank my advisor, Prof. Siva Sivoththaman, for sharing his tremendous amount of processing knowledge and always making time in his busy schedule to discuss my research. If it wasn't for his perceptiveness, motivation, and persistence, I would never have finished. I would also like to thank Prof. Nazir Kherani, Prof. Andrei Sazonov, Prof. Rafaat Mansour, and Prof. Vassili Karanassios for participating in my examination committee and for reviewing my thesis and providing valuable comments and suggestions. I am also grateful to Prof. Rafaat Mansour for sharing his expertise and his continued support of this work.

It was both an honor and privilege to be part of the Centre for Integrated RF Engineering (CIRFE) group. I would like to thank Bill Jolley who made sure we kept things in perspective and ran the lab in a calm and collected fashion. I am also indebted to the genuine advice from Roger Grant who could come up with a dozen suggestions for processing issues I encountered. Thank you to Winter Yan and Tania Oogarah for the extended coffee breaks and lively discussions; and Dr. Mojgan and Daria Daneshmand, and Reena Al-Dahleh for their collaboration in and out of the lab. I would also like to thank my colleagues in the cleanroom who made me laugh when my devices shriveled at the last step after a week's of processing efforts. I'm also grateful to my officemate, Dr. Mahdi Farrokh Baroughi, for sharing his knowledgeable advice over the years.

Last but not least, I have the utmost gratitude and appreciation for my parents who are a continued source of encouragement and never let me look back when I set forth on this path. I am truly blessed to have a brother and sister who are the best role models and my best friends; they test out the waters and look out for me, but never let anything get to my head. I am forever grateful to my fiancé who taught me more than he'll ever know. I'm also thankful to my future in-laws for keeping my tummy satisfied and providing a home away from home. I dedicate this thesis to my grandparents who first proposed I pursue my PhD, but passed away during the course of my research.

Thanks to phdcomics.com for understanding everything I've gone through these last few years.

## Contents

| 1 | Intr | roduction 1 |                                            |    |  |  |  |  |  |

|---|------|-------------|--------------------------------------------|----|--|--|--|--|--|

|   | 1.1  | Research    | ch Motivation                              | 1  |  |  |  |  |  |

|   |      | 1.1.1       | Inductors and Transformers on Silicon      | 2  |  |  |  |  |  |

|   |      | 1.1.2       | Low Temperature and Low Loss Films         | 3  |  |  |  |  |  |

|   |      | 1.1.3       | Low Temperature MEMS Fabrication           | 3  |  |  |  |  |  |

|   |      | 1.1.4       | Tunable RF MEMS Devices                    | 4  |  |  |  |  |  |

|   | 1.2  | Research    | ch Objectives                              | 6  |  |  |  |  |  |

|   | 1.3  | Structu     | are of Thesis                              | 7  |  |  |  |  |  |

| 2 | Bac  | kgroun      | $\mathbf{d}$                               | 8  |  |  |  |  |  |

|   | 2.1  | Brief H     | listory                                    | 8  |  |  |  |  |  |

|   |      | 2.1.1       | Amorphous Silicon                          | 8  |  |  |  |  |  |

|   |      | 2.1.2       | Porous Silicon                             | 11 |  |  |  |  |  |

|   | 2.2  | Mechan      | nical Properties of Silicon                | 13 |  |  |  |  |  |

|   |      | 2.2.1       | Structural Materials for MEMS Integration  | 14 |  |  |  |  |  |

|   |      | 2.2.2       | Amorphous Silicon as a Structural Material | 15 |  |  |  |  |  |

|   | 2.3  | Integra     | ted Inductors on Silicon                   | 16 |  |  |  |  |  |

|   |      | 2.3.1       | Modeling Parameters                        | 17 |  |  |  |  |  |

|   |      | 2.3.2       | Inductor Performance Metrics               | 24 |  |  |  |  |  |

|   |      | 2.3.3       | Previous Work                              | 26 |  |  |  |  |  |

|   | 2.4  | Integra     | ted Transformers on Silicon                | 31 |  |  |  |  |  |

|   |      | 2.4.1       | Modeling Parameters                        | 32 |  |  |  |  |  |

|   |      | 2.4.2       | Transformer Performance Metrics            | 33 |  |  |  |  |  |

|   |     | 2.4.3 Previous Work                                               | . 36  |

|---|-----|-------------------------------------------------------------------|-------|

|   | 2.5 | Summary                                                           | . 38  |

| 3 | Dev | velopment of Low Temperature Formation of Low Loss Films on S     | i 40  |

|   | 3.1 | Development of Undoped Amorphous Silicon Thick Films              | . 41  |

|   |     | 3.1.1 Film Formation                                              | . 41  |

|   |     | 3.1.2 Film Characterization and Results                           | . 46  |

|   |     | 3.1.3 Summary                                                     | . 58  |

|   | 3.2 | Formation of Porous Silicon Thick Films                           | . 59  |

|   |     | 3.2.1 Film Formation                                              | . 59  |

|   |     | 3.2.2 Film Characterization and Results                           | . 64  |

|   |     | 3.2.3 Summary                                                     | . 70  |

| 4 | Pla | nar Inductors built on Low Temperature and Low Loss Films on S    | Si 71 |

|   | 4.1 | Design of Planar Inductors on Silicon                             | . 72  |

|   |     | 4.1.1 Basic Structure                                             | . 72  |

|   |     | 4.1.2 Design Parameters                                           | . 73  |

|   |     | 4.1.3 Film Thicknesses                                            | . 75  |

|   |     | 4.1.4 Design Rules                                                | . 79  |

|   | 4.2 | Planar Inductors on Amorphous Silicon                             | . 79  |

|   |     | 4.2.1 Device Fabrication                                          | . 79  |

|   |     | 4.2.2 Results and Discussion                                      | . 81  |

|   | 4.3 | Planar Inductors on Porous Silicon                                | . 85  |

|   |     | 4.3.1 Device Fabrication                                          | . 86  |

|   |     | 4.3.2 Results and Discussion                                      | . 89  |

|   | 4.4 | Summary                                                           | . 92  |

| 5 | Am  | orphous Si Thick Films for sub 150°C MEMS Fabrication             | 94    |

|   | 5.1 | Lowering a-Si:H Thick Film Deposition to 150°C                    | . 95  |

|   | 5.2 | Film Stress Issues of a-Si:H Thick Films as a Mechanical Material | . 97  |

|   | 5.3 | Integration Issues of a-Si:H Thick Films as a Mechanical Material | . 100 |

|   |     | 5.3.1 Critical Role of Step Coverage of an Anchor                 | 101   |

|                           |       | 5.3.2 Optimizing the Step Coverage of a-Si:H Thick Films               | 102 |

|---------------------------|-------|------------------------------------------------------------------------|-----|

|                           | 5.4   | Fabrication and Testing of a Simple MEMS Device with a-Si:H Thick Film | 104 |

|                           |       | 5.4.1 Simple Vertical Bimorph Thermal Actuator                         | 104 |

|                           | 5.5   | Summary                                                                | 109 |

| 6                         | Tun   | able RF MEMS Inductors and Transformers using Amorphous S              | i   |

|                           | Thi   | ck Films as a Mechanical Material                                      | 111 |

|                           | 6.1   | Tunable RF MEMS Inductors                                              | 111 |

|                           |       | 6.1.1 Device Design                                                    | 112 |

|                           |       | 6.1.2 Device Fabrication                                               | 112 |

|                           |       | 6.1.3 Results and Discussion                                           | 117 |

|                           | 6.2   | Tunable RF MEMS Transformers                                           | 119 |

|                           |       | 6.2.1 Device Design                                                    | 120 |

|                           |       | 6.2.2 Device Fabrication                                               | 121 |

|                           |       | 6.2.3 Results and Discussion                                           | 121 |

|                           | 6.3   | Simulations Involving Traditional RF Materials                         | 134 |

|                           | 6.4   | Future Outlook of post-CMOS and MEMS                                   | 136 |

|                           | 6.5   | Summary                                                                | 137 |

| 7                         | Con   | aclusions                                                              | 138 |

|                           | 7.1   | Contributions                                                          | 138 |

|                           | 7.2   | Future Work                                                            | 140 |

| $\mathbf{A}_{\mathbf{J}}$ | ppen  | dix A Recipes Developed in this research for MEMS Processing           | 142 |

| $\mathbf{A}_{\mathbf{I}}$ | ppen  | dix B Calculating the Hydrogen Content in a-Si:H                       | 147 |

| $\mathbf{A}_{\mathbf{l}}$ | ppen  | dix C Extracting the Optical Bandgap of a-Si:H                         | 149 |

| Li                        | st of | Thesis Publications                                                    | 151 |

| Li                        | st of | Acronyms                                                               | 153 |

| Re                        | efere | nces                                                                   | 155 |

# List of Figures

| 1.1  | Integrated transformer-based front-end wireless transceiver on CMOS       | 3  |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------|----|--|--|--|--|--|--|

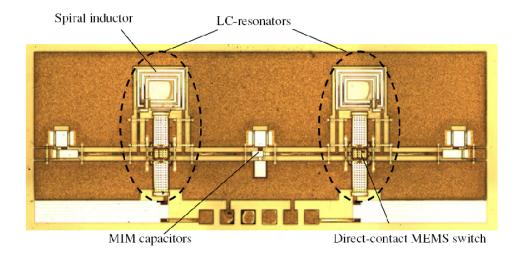

| 1.2  | MEMS dual-band filter with contact switched inductors                     |    |  |  |  |  |  |  |

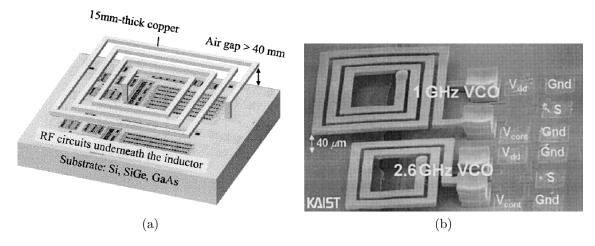

| 1.3  | Integrated VCO with on-chip MEMS inductors                                | 5  |  |  |  |  |  |  |

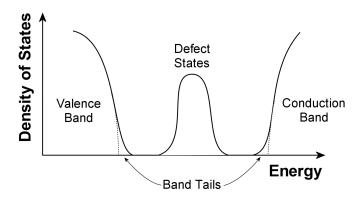

| 2.1  | Density of states distribution in a-Si:H                                  | 11 |  |  |  |  |  |  |

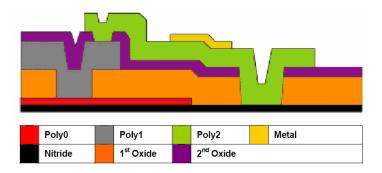

| 2.2  | Cross-section of MEMSCAP's PolyMUMPs commercial MEMS process              | 15 |  |  |  |  |  |  |

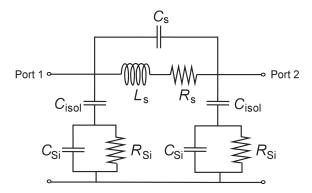

| 2.3  | Conventional compact model of a planar inductor on Si                     | 17 |  |  |  |  |  |  |

| 2.4  | Schematic of self and mutual inductances in a coil                        | 18 |  |  |  |  |  |  |

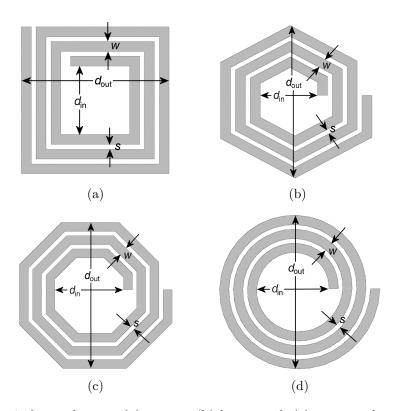

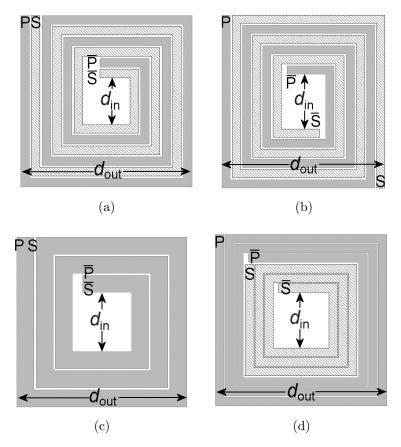

| 2.5  | Planar inductor layouts                                                   | 20 |  |  |  |  |  |  |

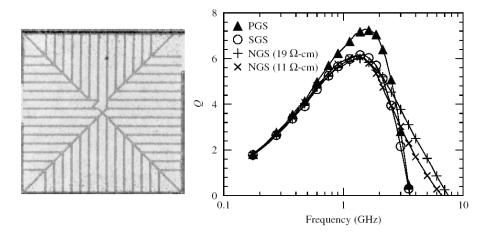

| 2.6  | Effect of ground shield on $Q$                                            | 27 |  |  |  |  |  |  |

| 2.7  | Cross-section of a multi-metal layer inductor                             | 27 |  |  |  |  |  |  |

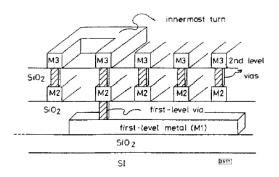

| 2.8  | Effect of layout optimization on $Q$                                      | 28 |  |  |  |  |  |  |

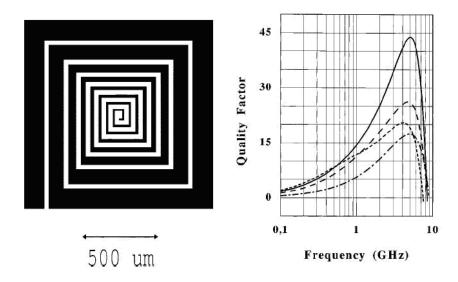

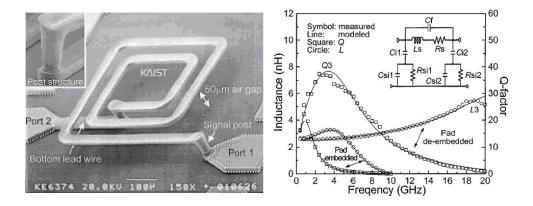

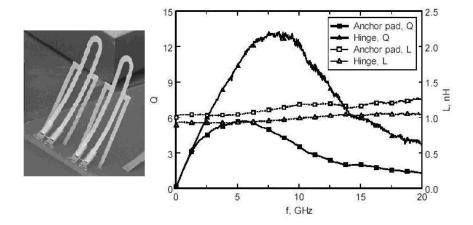

| 2.9  | Bulk micromachined inductor                                               | 29 |  |  |  |  |  |  |

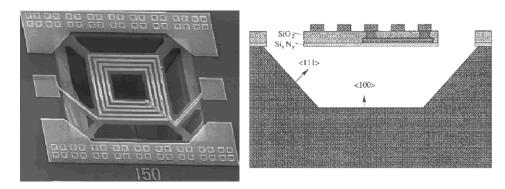

| 2.10 | Surface micromachined inductor                                            | 30 |  |  |  |  |  |  |

| 2.11 | Self-assembling tunable inductor                                          | 31 |  |  |  |  |  |  |

| 2.12 | 3-D Inductors by plastic deformation magnetic assembly                    | 31 |  |  |  |  |  |  |

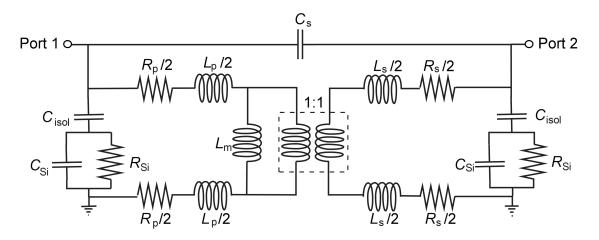

| 2.13 | Conventional compact model of a transformer on Si                         | 32 |  |  |  |  |  |  |

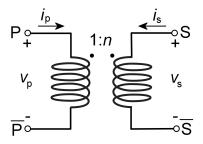

| 2.14 | Schematic symbol of a monolithic transformer                              | 33 |  |  |  |  |  |  |

| 2.15 | Planar transformer layouts                                                | 36 |  |  |  |  |  |  |

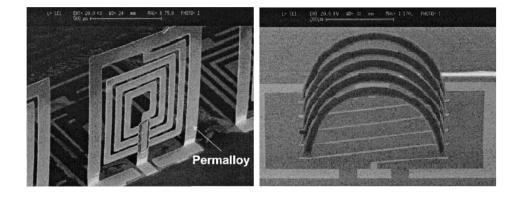

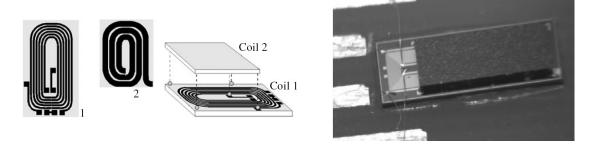

| 2.16 | Magnetic transformers fabricated in a flip-chip process                   | 37 |  |  |  |  |  |  |

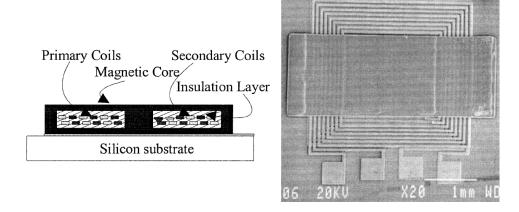

| 2.17 | Transformers fabricated with a permalloy magnetic core                    | 37 |  |  |  |  |  |  |

| 2.18 | Millimeter-wave inductors and transformers operating in the 30-100 GHz $$ | 38 |  |  |  |  |  |  |

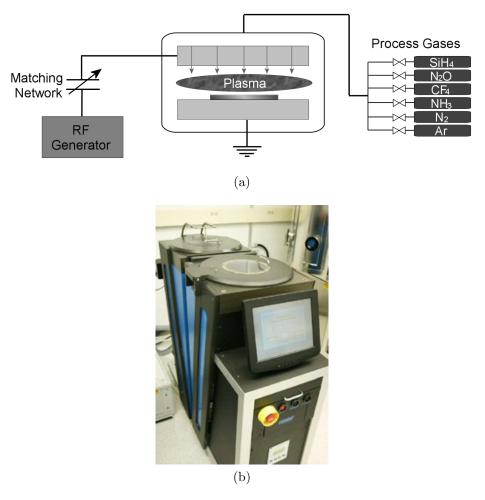

| 3.1  | Trion PECVD System in the CIRFE Lab.                                      | 42 |  |  |  |  |  |  |

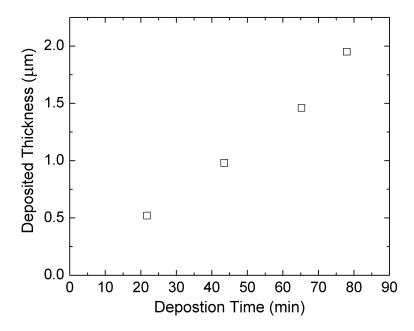

| 3.2  | Variation in deposition thickness with time of PECVD a-Si:H thick films            | 44         |

|------|------------------------------------------------------------------------------------|------------|

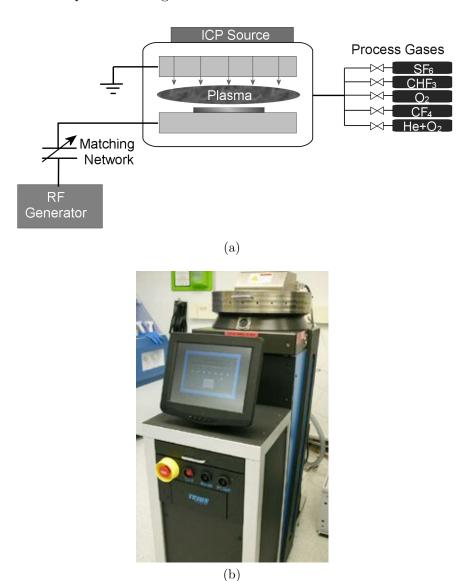

| 3.3  | Trion RIE System in the CIRFE Lab                                                  | 45         |

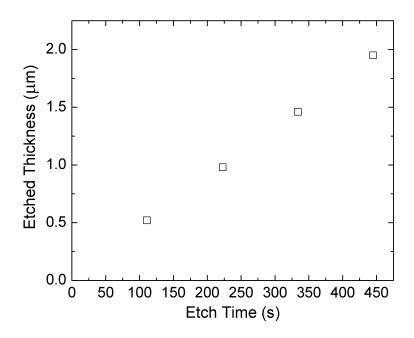

| 3.4  | Variation in etched thickness with time of RIE a-Si:H thick films                  | 46         |

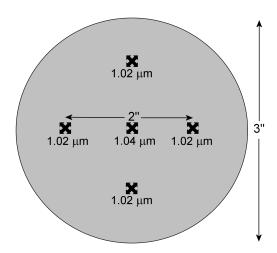

| 3.5  | Film uniformity of PECVD a-Si:H thick film                                         | 47         |

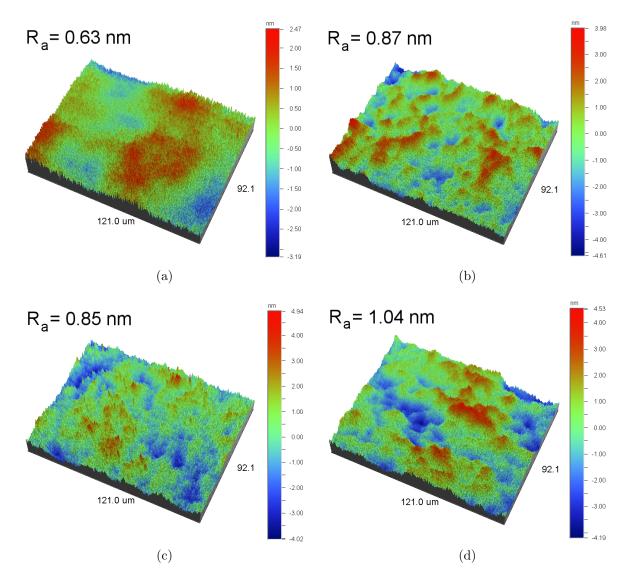

| 3.6  | Surface roughness of PECVD a-Si:H thick films                                      | 48         |

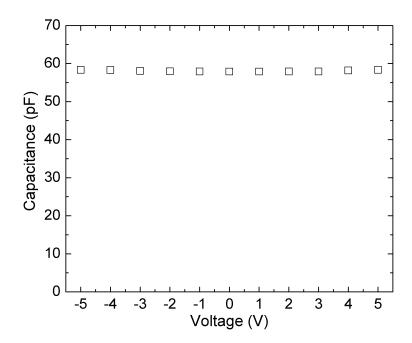

| 3.7  | Capacitance-voltage measurements of a-Si:H thick film                              | 50         |

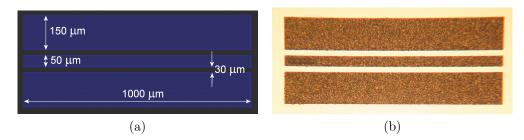

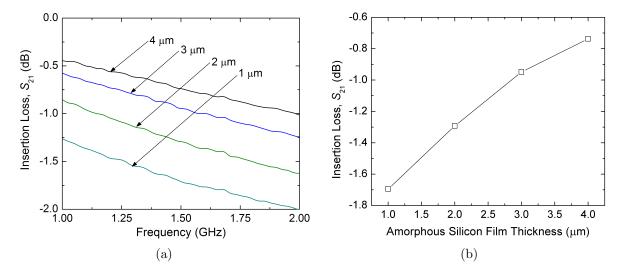

| 3.8  | CPW transmission line used to extract loss tangent of a-Si:H thick films           | 52         |

| 3.9  | Insertion loss of CPW line on a-Si:H thick films with different thicknesses.       | 53         |

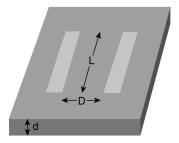

| 3.10 | Structure used to measure conductivity of a dielectric film                        | 54         |

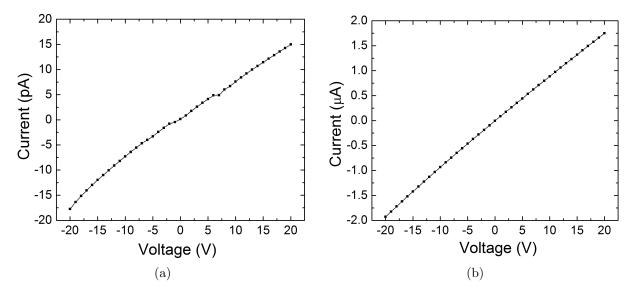

| 3.11 | Measured dark and photoconductivity of a-Si:H thick film                           | 55         |

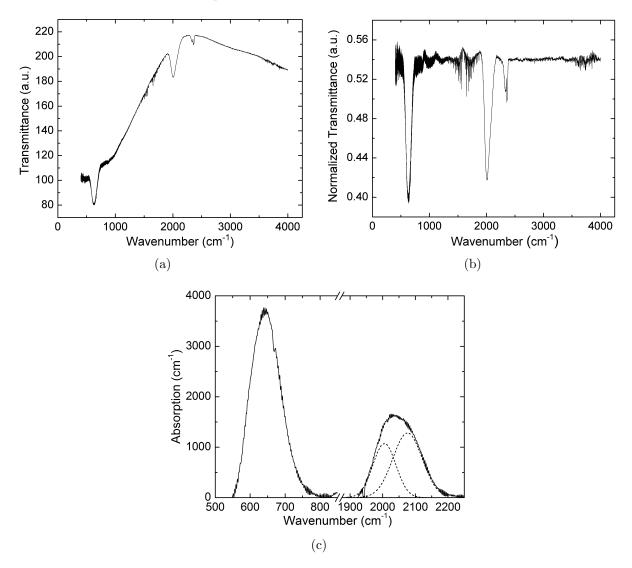

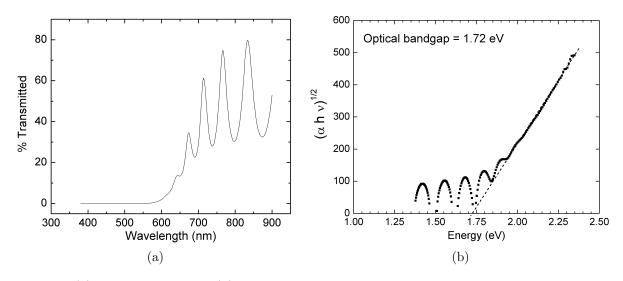

| 3.12 | Infrared transmission spectrum of a-Si:H thick film                                | 56         |

| 3.13 | UV spectrum and Tauc plot of a-Si:H thick film                                     | 58         |

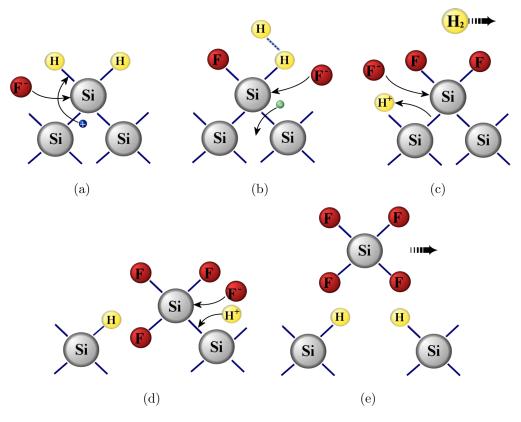

| 3.14 | Porous Si formation steps                                                          | 61         |

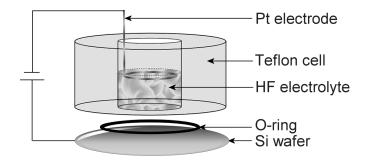

| 3.15 | Schematic of a single wafer etch cell                                              | 65         |

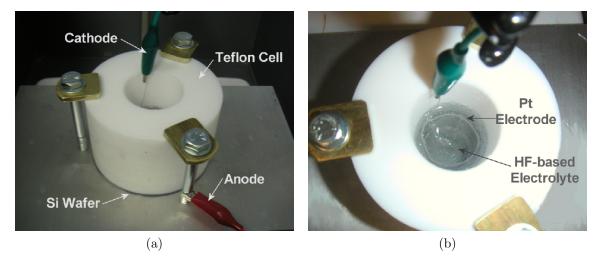

| 3.16 | Photograph of Teflon etch cell machined for this study                             | 65         |

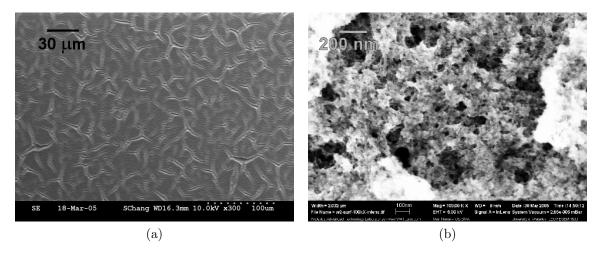

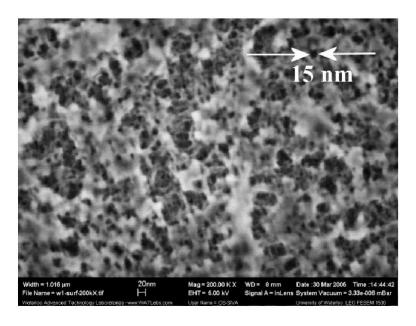

| 3.17 | SEM of PS formed with 25% HF concentration and 1 $\rm mA/cm^2$ current             |            |

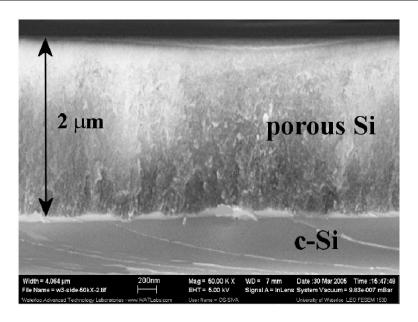

|      | density for 45 min                                                                 | 66         |

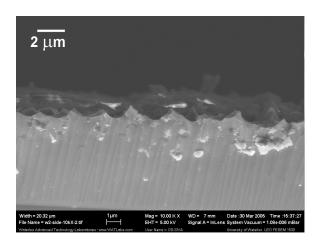

|      | PS formed with $12.5\%$ HF concentration and $20~\text{mA/cm}^2$ currenty density. | 67         |

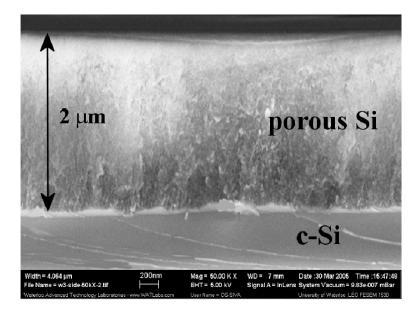

| 3.19 | Border between PS formation and c-Si substrate                                     | 67         |

| 3.20 | PS formed with 12.5% HF concentration and 40 $\mathrm{mA/cm^2}$ current density    | 68         |

| 3.21 | PS formed from with 5 $\rm mA/cm^2$ current density and varying HF concentration.  | 69         |

| 3.22 | Photograph of electrochemical etching of c-Si with a particle defect               | 70         |

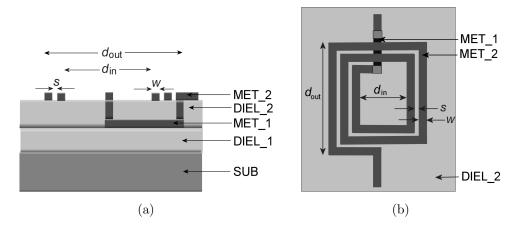

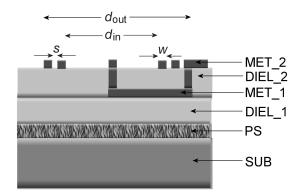

| 4.1  | Schematic of a planar inductor                                                     | 72         |

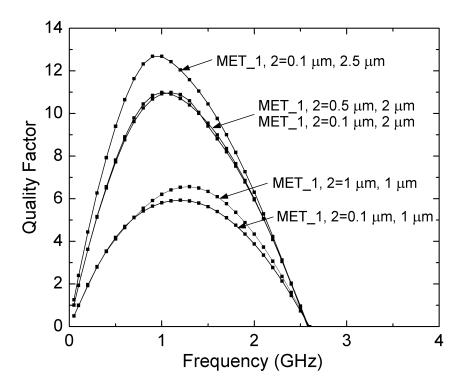

| 4.2  | Q versus metal layer thickness.                                                    | 76         |

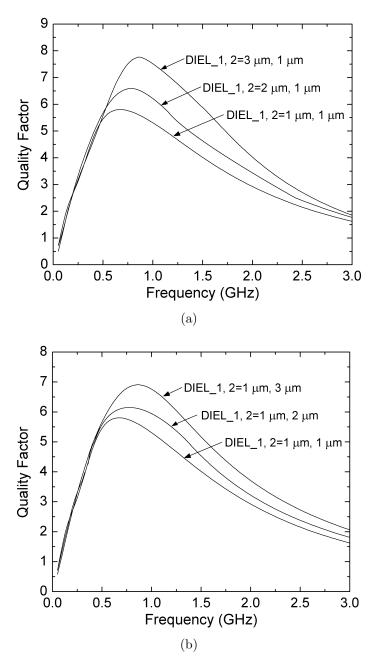

| 4.3  | Q versus dielectric layer thickness.                                               | 77         |

| 4.4  | Q versus conductivity of DIEL_1 and DIEL_2 layers                                  | 78         |

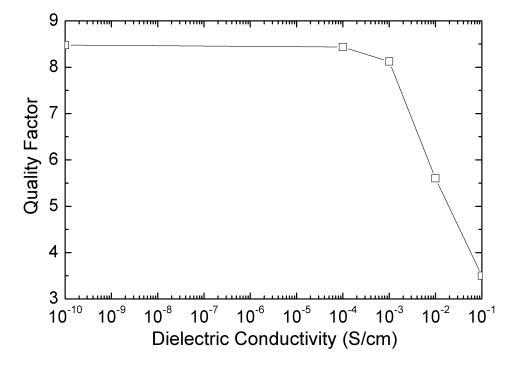

| 4.5  | Process flow of planar inductors                                                   | 80         |

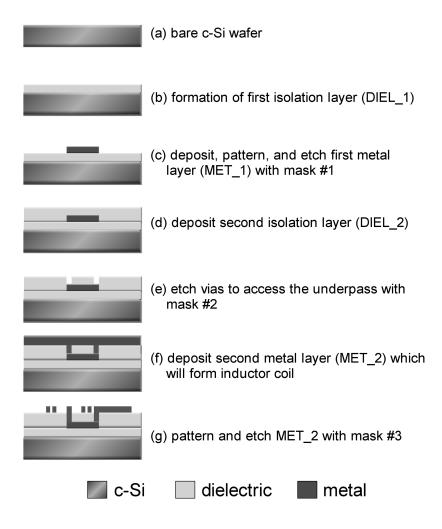

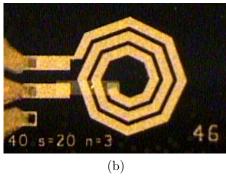

| 4.6  | Fabricated planar inductors incorporating a-Si:H on c-Si                           | 82         |

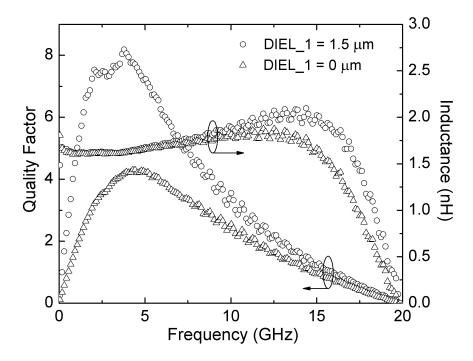

| 4.7  | Influence of thickness of a-Si:H layer on performance of fabricated planar         | J <b>-</b> |

|      | inductor                                                                           | 83         |

|      |                                                                                    |            |

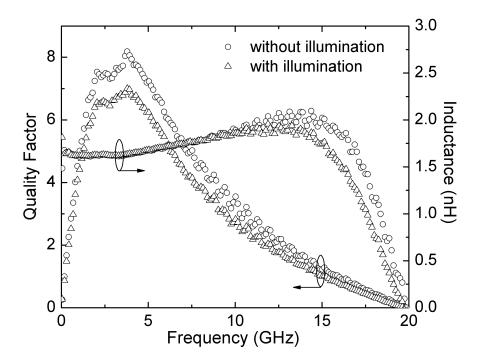

| 4.8  | Influence of light-induced conductivity of a-Si:H on performance of fabri-                               |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | cated planar inductor                                                                                    | 84  |

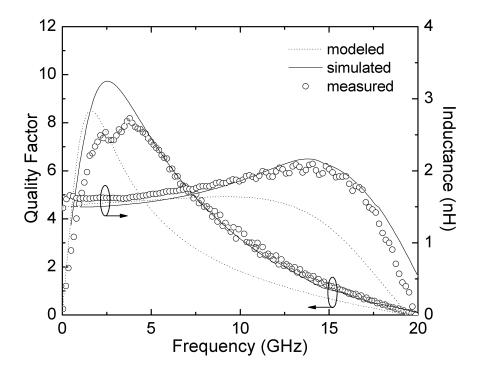

| 4.9  | Comparison between modeled, simulated and measured results of a fabri-                                   |     |

|      | cated planar inductor                                                                                    | 85  |

| 4.10 | Schematic cross-section of planar inductor incorporating PS                                              | 86  |

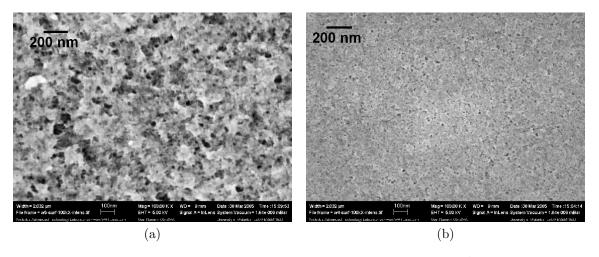

| 4.11 | SEM of PS pore size formed with 25% HF concentration and 1 mA/cm <sup>2</sup> current density for 45 min | 87  |

| 4.12 | SEM of PS thickness formed with 25% HF concentration and 1 $\rm mA/cm^2$                                 |     |

|      | current density for 45 min                                                                               | 88  |

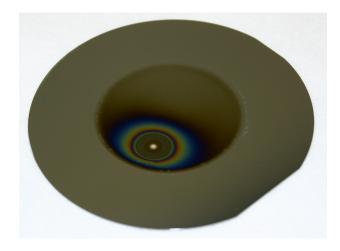

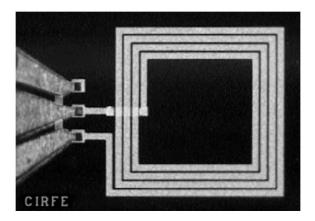

| 4.13 | Micrograph of fabricated inductor on PS and a-Si:H                                                       | 88  |

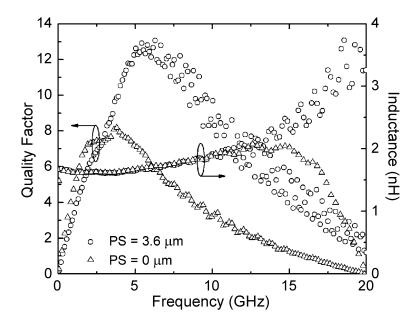

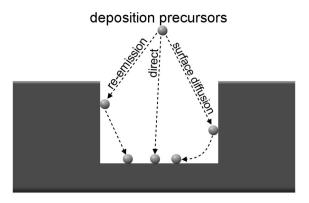

| 4.14 | Measured RF performance of a fabricated inductor with PS and a-Si:H                                      | 90  |

| 4.15 | Measured RF performance of a fabricated inductor on PS showing the                                       |     |

|      | influence of applied current density                                                                     | 91  |

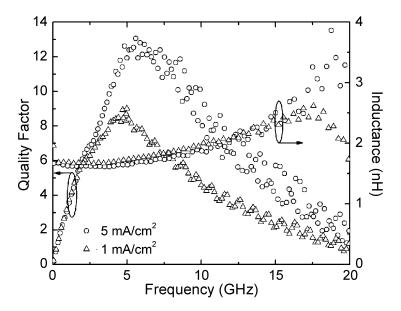

| 4.16 | Effective substrate resistivity of Si incorporating PS and a-Si:H                                        | 9   |

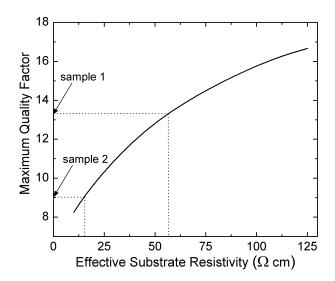

| 5.1  | PECVD surface deposition kinetics in a trench                                                            | 9   |

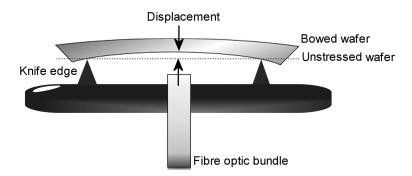

| 5.2  | Schematic of an optical stress gauge                                                                     | 98  |

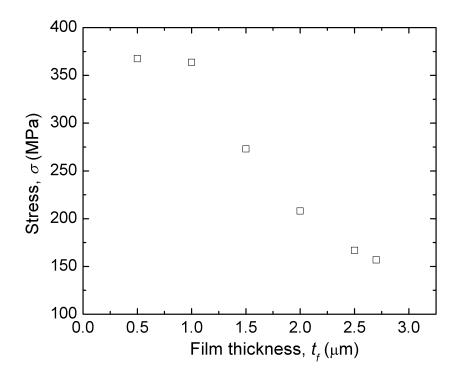

| 5.3  | Measured stress of PECVD a-Si:H thick films with varying thicknesses. $$                                 | 100 |

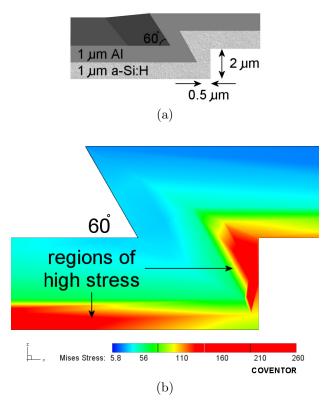

| 5.4  | Simulated stress distribution in the anchor                                                              | 101 |

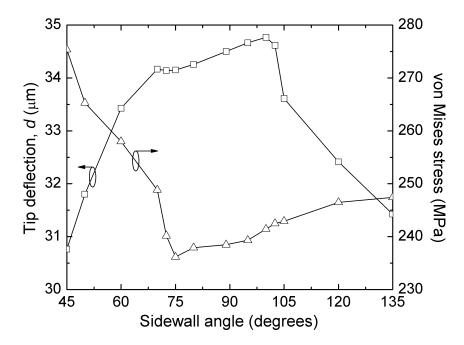

| 5.5  | Simulated displacement and stress in a bimorph cantilever beam                                           | 102 |

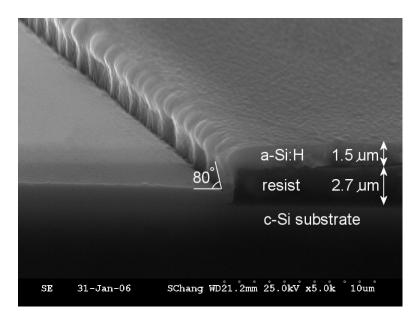

| 5.6  | SEM cross-section of a-Si:H thick film coverage over a step of resist                                    | 103 |

| 5.7  | SEM cross-section of a-Si:H thick film coverage over extreme sidewall                                    | 104 |

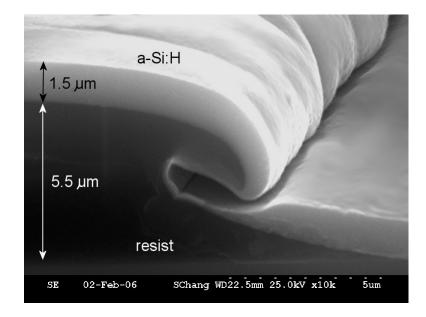

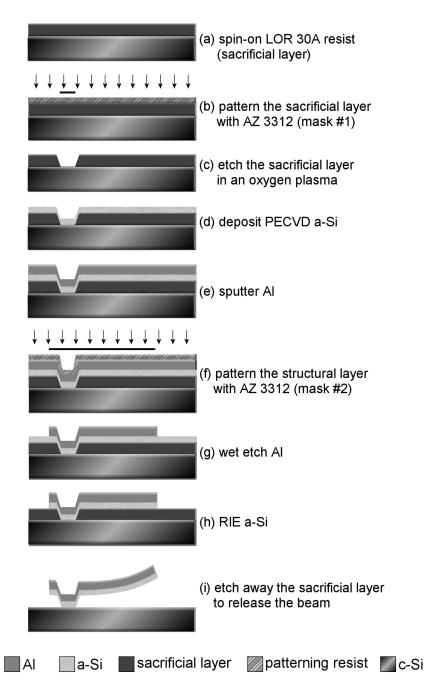

| 5.8  | Fabrication steps of simple bimorph cantilever beams                                                     | 107 |

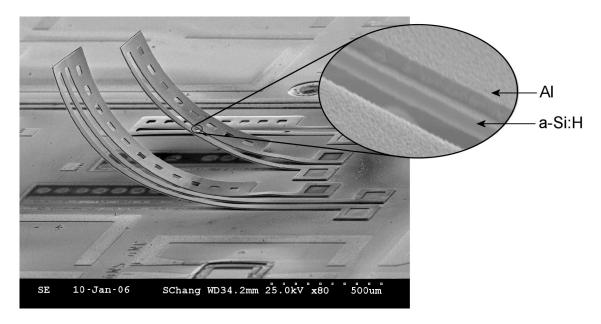

| 5.9  | SEM of fabricated bimorph thermal actuators incorporating a-Si:H. $$                                     | 108 |

| 5.10 | Overlay of microscope images showing the actuated tip of a fabricated                                    |     |

|      | bimorph thermal actuator                                                                                 | 108 |

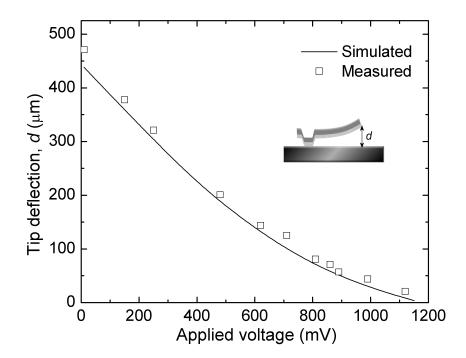

| 5.11 | Measured and simulated tip deflection of a fabricated bimorph thermal                                    |     |

|      | actuator incorporating a-Si:H as a mechanical material                                                   | 109 |

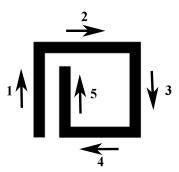

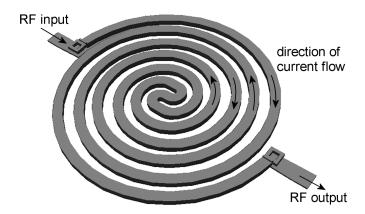

| 6.1  | Schematic indicating the direction of current flow for a single metal layer                              |     |

|      | MEMS inductor                                                                                            | 11: |

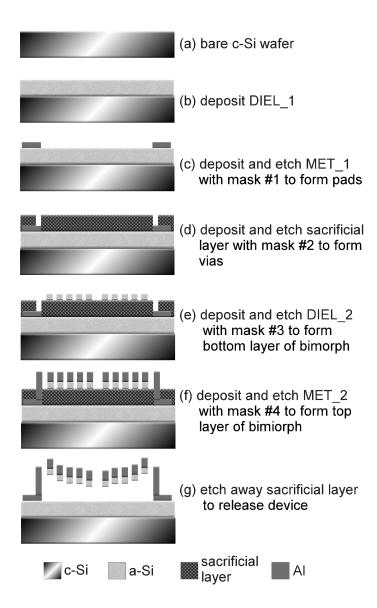

| 6.2  | Fabrication process of a RF MEMS inductor                                                                | 114 |

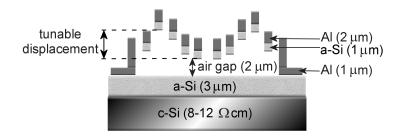

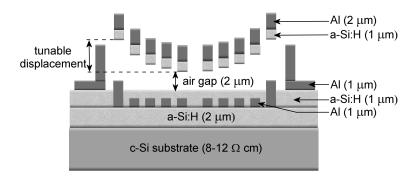

| Cross-sectional schematic of tunable RF MEMS inductor                                                                            | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

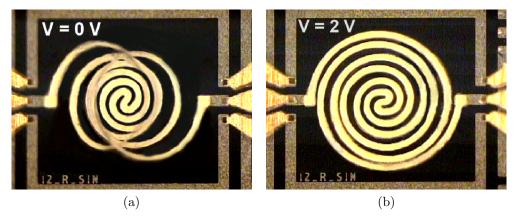

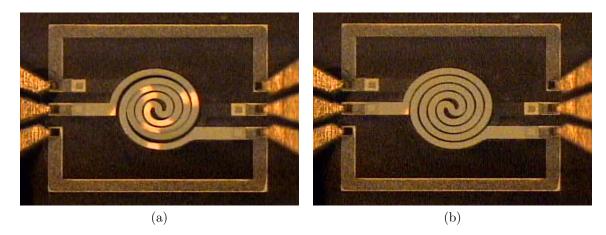

| Micrograph image of a fabricated RF MEMS tunable inductor                                                                        | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

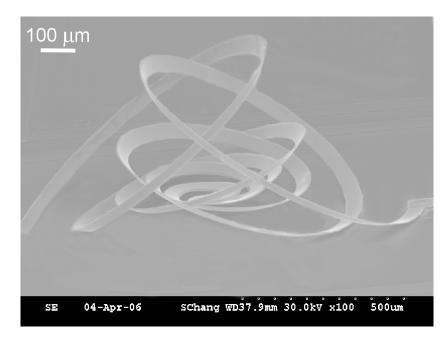

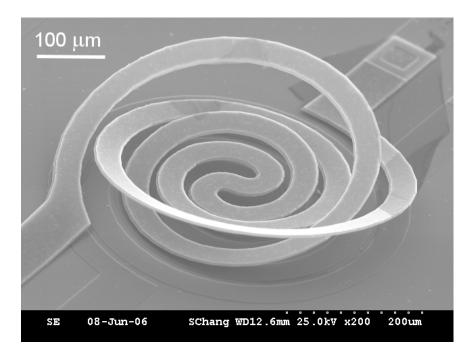

| SEM of a fabricated tunable RF MEMS inductor                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

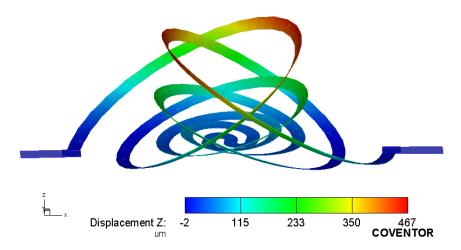

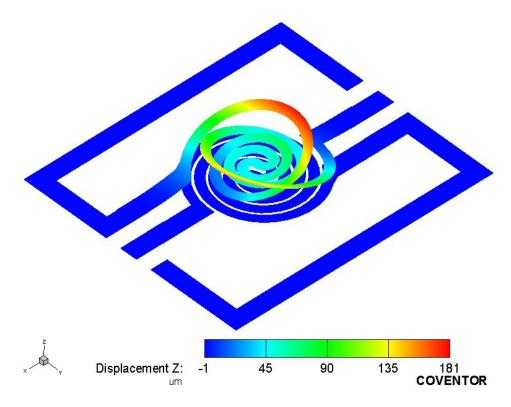

| Thermomechanical simulation of a tunable RF MEMS inductor 116                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

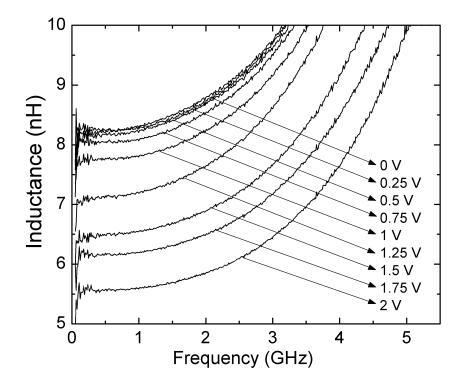

| Measured inductance of a fabricated RF MEMS tunable inductor                                                                     | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

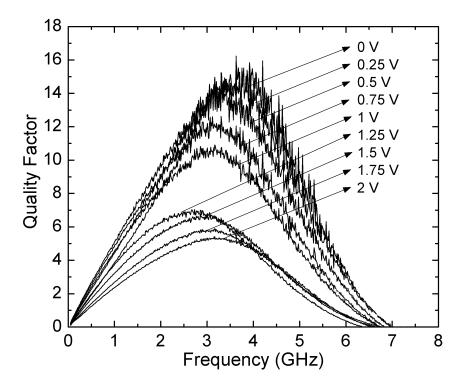

| Measured $Q$ of a fabricated RF MEMS tunable inductor                                                                            | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

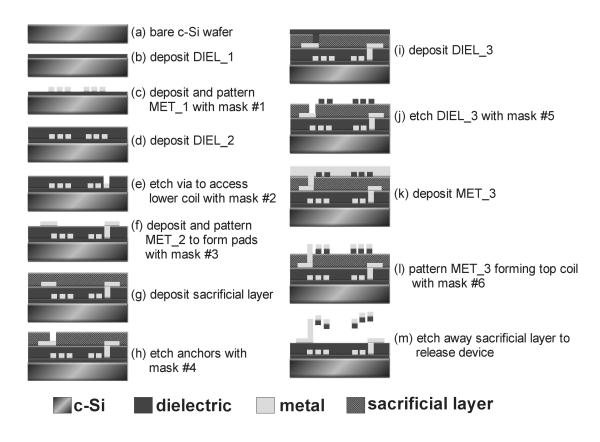

| Fabrication process of a tunable RF MEMS transformer                                                                             | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Cross-section schematic of a tunable RF MEMS transformer                                                                         | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

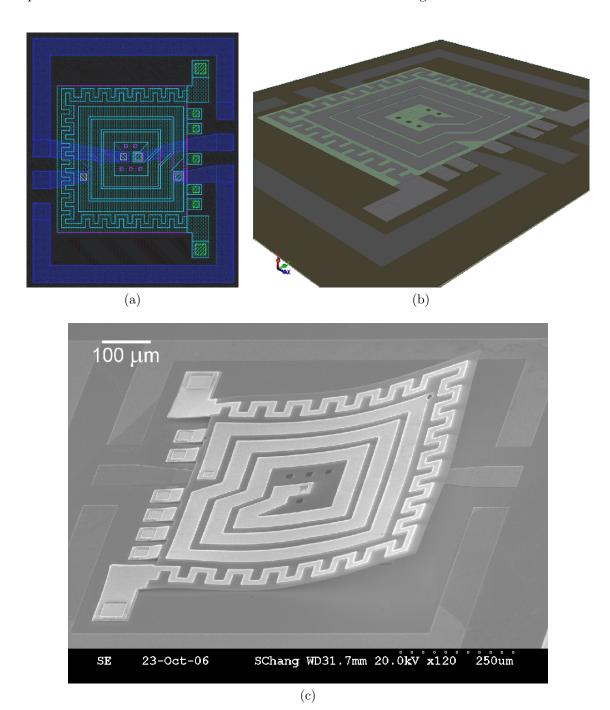

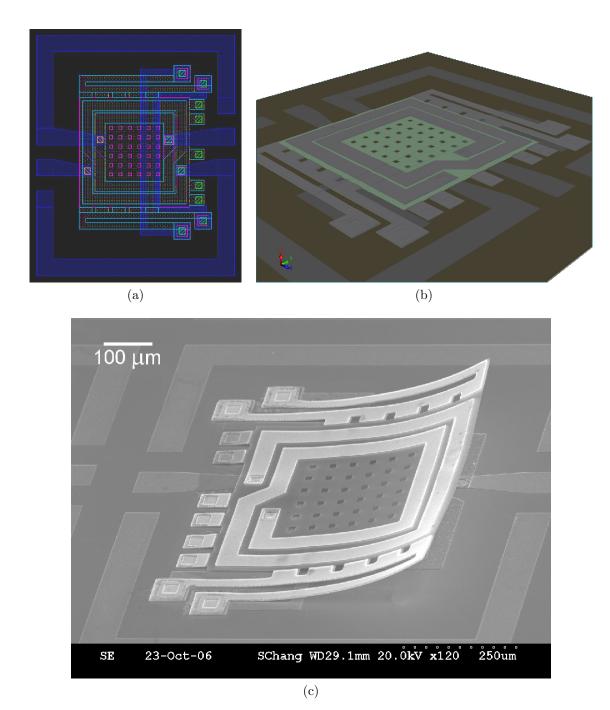

| Micrograph of a fabricated tunable RF MEMS transformer                                                                           | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| SEM of a fabricated tunable RF MEMS transformer                                                                                  | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

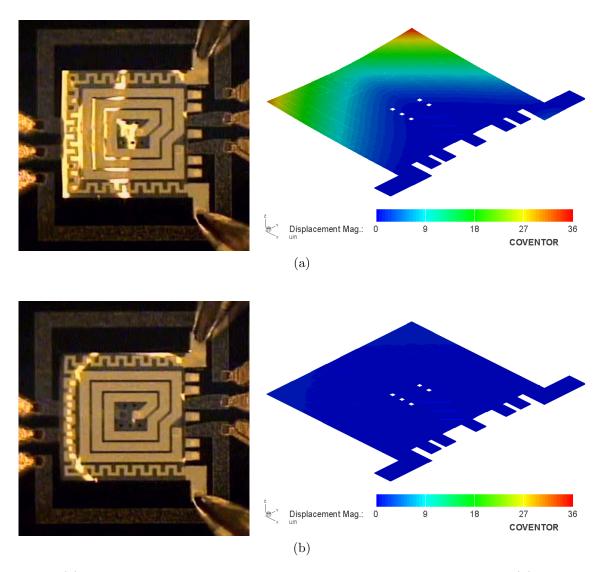

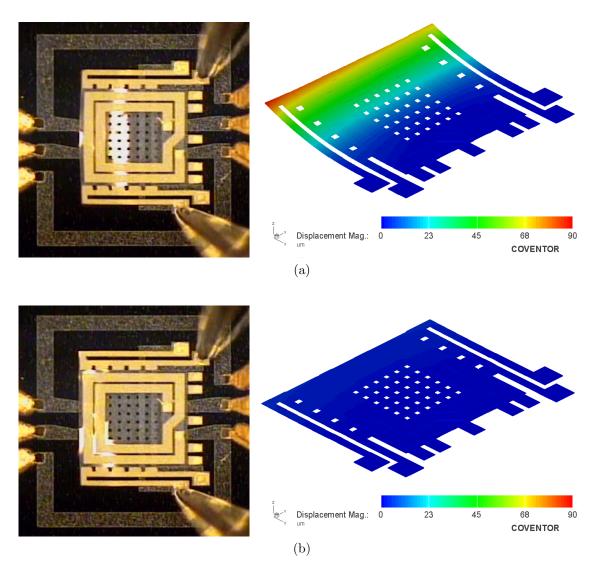

| Thermomechanical simulation of a tunable RF MEMS transformer                                                                     | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

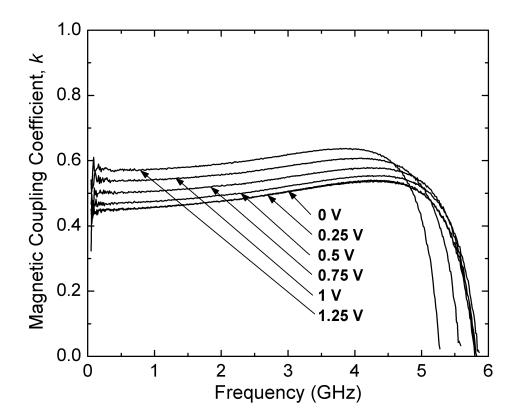

| Measured magnetic coupling of a fabricated tunable RF MEMS transformer.                                                          | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

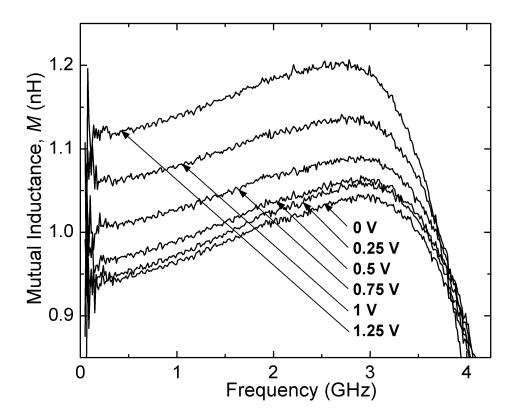

| Measured mutual inductance of a fabricated tunable RF MEMS transformer.                                                          | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

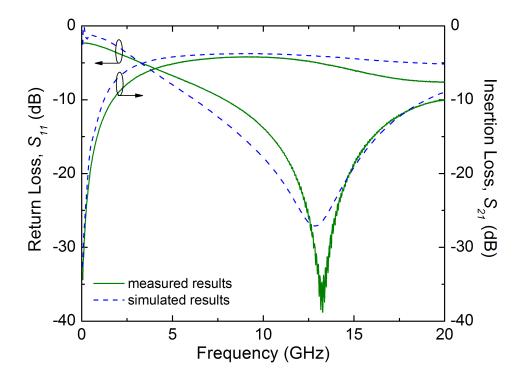

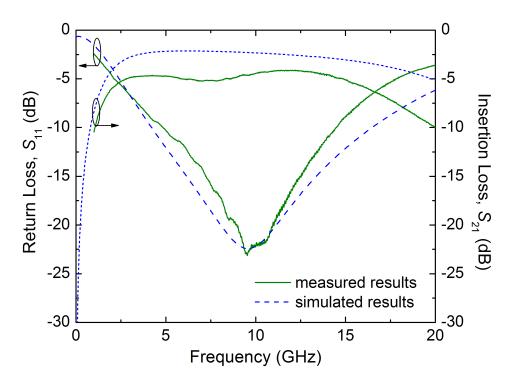

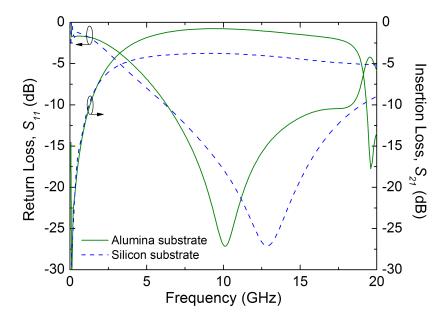

| Measured and simulated $S$ -parameters of a fabricated tunable RF MEMS                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| $transformer. \dots \dots$ | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

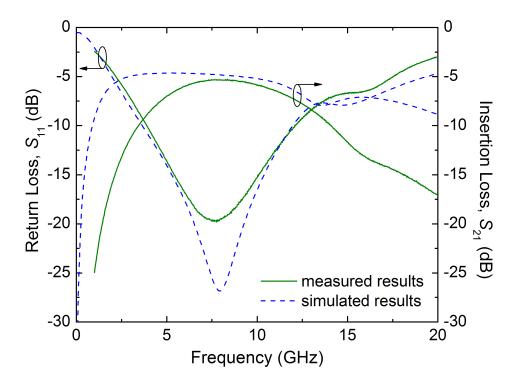

| Comparison of measured and simulated results of a resistively heated plate                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| $transformer. \dots \dots$ | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Schematic of resistively heated plate transformer design                                                                         | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Fabricated resistively heated plate transformer design                                                                           | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Comparison of measured and simulated results of a thermally actuated plate                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| $transformer. \dots \dots$ | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Schematic of thermally actuated plate transformer design                                                                         | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Fabricated thermally actuated plate transformer design                                                                           | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

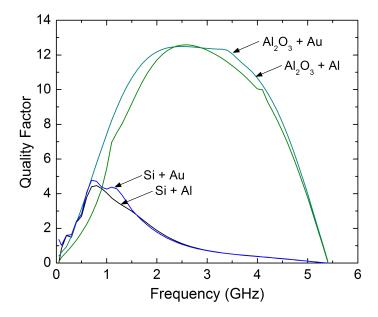

| Comparison of simulations using alumina and gold of a fabricated RF MEMS                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| $inductor. \dots \dots$    | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Comparison of simulations using alumina for a fabricated RF MEMS                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| $transformer. \dots \dots$ | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

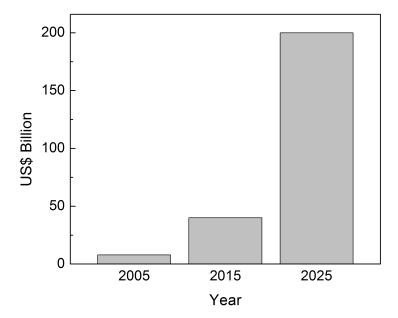

| MEMS-based IC product market                                                                                                     | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

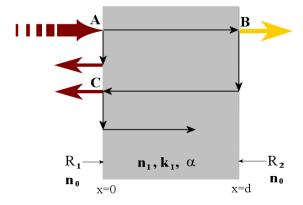

| Absorbed, transmitted and reflected light in a thin film                                                                         | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                  | Micrograph image of a fabricated RF MEMS tunable inductor.  SEM of a fabricated tunable RF MEMS inductor.  Thermomechanical simulation of a tunable RF MEMS inductor.  Measured inductance of a fabricated RF MEMS tunable inductor.  Measured Q of a fabricated RF MEMS tunable inductor.  Fabrication process of a tunable RF MEMS transformer.  Cross-section schematic of a tunable RF MEMS transformer.  Micrograph of a fabricated tunable RF MEMS transformer.  SEM of a fabricated tunable RF MEMS transformer.  Thermomechanical simulation of a tunable RF MEMS transformer.  Measured magnetic coupling of a fabricated tunable RF MEMS transformer.  Measured mutual inductance of a fabricated tunable RF MEMS transformer.  Measured and simulated S-parameters of a fabricated tunable RF MEMS transformer.  Comparison of measured and simulated results of a resistively heated plate transformer.  Schematic of resistively heated plate transformer design.  Fabricated resistively heated plate transformer design.  Comparison of measured and simulated results of a thermally actuated plate transformer.  Schematic of thermally actuated plate transformer design.  Comparison of simulations using alumina and gold of a fabricated RF MEMS inductor.  Comparison of simulations using alumina for a fabricated RF MEMS transformer. |  |  |  |  |

## List of Tables

| 2.1 | Comparison of mechanical properties of common materials compared to Si.     | 14 |

|-----|-----------------------------------------------------------------------------|----|

| 2.2 | High temperature steps in MEMSCAP's PolyMUMPs process                       | 15 |

| 2.3 | Comparison of thermomechanical properties of poly-Si and a-Si:H             | 16 |

| 2.4 | Fitting parameters for modified Wheeler formula                             | 20 |

| 2.5 | Conductivity and skin depth of metal layers commonly used in IC processes.  | 21 |

| 2.6 | Summary of equations and description of parameters in the compact model     |    |

|     | of a planar inductor                                                        | 24 |

| 3.1 | PECVD process conditions for deposition of a-Si:H thick films at 250°C      | 43 |

| 3.2 | RIE process conditions for etching a-Si:H thick films                       | 46 |

| 3.3 | Experimental results of stain etching of c-Si                               | 64 |

| 3.4 | Experimental results of electrochemical etching of c-Si                     | 66 |

| 4.1 | General trends of inductor design parameters                                | 74 |

| 4.2 | Design rules for the fabrication of planar inductors                        | 79 |

| 4.3 | Dimensions and measured performance of fabricated planar inductors          | 81 |

| 4.4 | Experimental parameters for forming PS for 45 min                           | 87 |

| 4.5 | Comparison of some planar inductors reported in literature compared to this |    |

|     | work                                                                        | 92 |

| 4.6 | Comparison of some planar inductors on PS reported in literature compared   |    |

|     | to this work                                                                | 92 |

| 5.1 | Variation in deposition rates for PECVD a-Si:H films                        | 96 |

| 5.2 | PECVD process conditions for depositing a-Si:H thick films                  | 97 |

| 6.1 | Inductor compact model parameters fitted to measured results for different  |      |  |  |  |  |

|-----|-----------------------------------------------------------------------------|------|--|--|--|--|

|     | applied voltages of a fabricated tunable RF MEMS inductor in this work      | 118  |  |  |  |  |

| 6.2 | Design rules for the fabrication of MEMS inductors and transformers in this |      |  |  |  |  |

|     | work                                                                        | 120  |  |  |  |  |

| 6.3 | Transformer compact model parameters fitted to measured results for         |      |  |  |  |  |

|     | different applied voltages                                                  | 126  |  |  |  |  |

| Δ 1 | Amorphous Si PECVD recipe                                                   | 1/19 |  |  |  |  |

|     |                                                                             |      |  |  |  |  |

| A.2 | Amorphous Si RIE recipe                                                     | 143  |  |  |  |  |

| A.3 | Photolithography steps                                                      | 144  |  |  |  |  |

| A.4 | Spin-on sacrificial layer recipe                                            | 145  |  |  |  |  |

| A.5 | Sacrificial layer RIE recipe                                                | 146  |  |  |  |  |

| A 6 | Release process                                                             | 146  |  |  |  |  |

## Chapter 1

## Introduction

### 1.1 Research Motivation

A wireless radio frequency (RF) receiver must select the desired signal out of many unwanted and potentially interfering signals and then amplify it with near perfect quality. In addition to these challenges of modern day engineering, the consumer market places strict constraints on low cost, low power, and high volume production. In order to meet these requirements, an integrated system is the most promising solution.

Many technology tradeoffs exist in RF integrated circuits (ICs) for wireless communication systems. The optimum technology for RFICs may follow the same path as digital ICs - toward complementary metal-oxide-semiconductor (CMOS) integration where cost decreases as the level of integration increases [1]. However, the technical requirements for an RF transceiver are far more complex than digital ICs where, in the later case, parameters such as power dissipation, operating speed, and manufacturing yield are the main performance concerns. In the case of RFICs, in conjunction with the requirements of digital ICs, issues such as noise, linearity, gain, and efficiency must also be addressed.

Today, commercial implementations of high performance wireless transceivers use a mixture of processing technologies to implement an integrated solution. These on- and off-chip components are often mixed together to reach design specifications which can complicate packaging, increase costs, and decrease performance reliability. Due to recent research efforts, high frequency performance of devices on silicon (Si) are approaching those

achieved on gallium arsenide (GaAs), but at higher power dissipation [1]. Nonetheless, higher integration with Si technology will reduce the need for routing high frequency signals which can potentially reduce the overall power dissipation of the system as a whole.

#### 1.1.1 Inductors and Transformers on Silicon

An inductor is a device capable of producing a voltage in response to a changing current. The changing current produces a time-varying magnetic field which induces an electromotive force (emf). A low loss inductor is the last passive element to be successfully integrated onto Si ICs. High performance on-chip inductors are in increasing demand in today's communication systems with an emphasis on RF and mixed-signal ICs, and system on chip (SoC) applications. Inductors are widely used in RF circuits, such as filters, voltage controlled-oscillators (VCO), low-noise amplifiers (LNA), and impedance matching circuitry. The key parameters used to characterize the performance of inductors are the inductance (L), the quality factor (Q) and the self-resonance frequency  $(f_{res})$ . A constant L over a broad frequency range is necessary for a reliable circuit design. A high Q improves the insertion loss of a filter and enhances the phase noise performance of a VCO, for instance. An increase in  $f_{res}$  allows the device to be operated at higher frequency. In general, the trace capacitance to ground lowers  $f_{res}$ , and the substrate conductivity lowers the Q at RF frequencies.

The conventional monolithic inductor is implemented as a metal trace on oxide over a conductive Si substrate. The Q is limited by the series resistance of the thin film metalization at low frequency and the low substrate resistivity at high frequency. Due to the driving force of CMOS integration and low costs of Si-based ICs, these inductors must lie on a conductive Si substrate which is a major source of energy loss and limits the RF performance. As a result, the Q factor of inductors fabricated on low resistivity Si is low (Q < 10). In matching circuits for example, the Q of the inductor is much lower than that of the capacitor and hence, dominates the overall Q of the circuit. The wide range of applications of inductors emphasizes this need for improving the performance of an inductor fabricated on low resistivity Si.

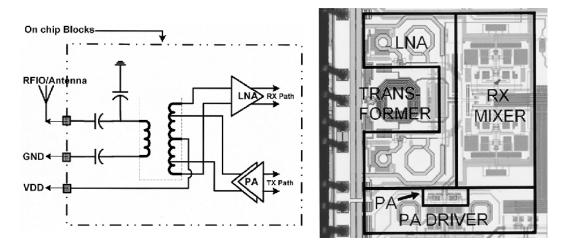

A transformer is simply two inductive coils coupled together and are also integrated into RF systems. Figure 1.1 is a wireless transceiver with an on-chip transformer integrated

on CMOS to perform matching and single-ended to differential conversion (one set of ports on the primary side and two sets on the secondary side). This front-end architecture has been used in Bluetooth products [2].

Fig. 1.1: Integrated transformer-based front-end wireless transceiver on CMOS, from [2].

### 1.1.2 Low Temperature and Low Loss Films

To improve the performance of inductors on Si, thick low loss films on Si with minimum stress are required. In addition, with the continued search for low-k dielectrics and metal alloys, a low thermal budget is always preferred. Plasma enhanced chemical vapor deposition (PECVD) of hydrogenated amorphous Si (a-Si:H) is an attractive choice because the substrate can remain at a low temperature. Porous Si (PS) is another low temperature material that is formed by electrochemically etching pores in the Si substrate improving the resistivity. It is a wet etching process that can take place at room temperature.

### 1.1.3 Low Temperature MEMS Fabrication

In the last few decades, CMOS technology has dominated microelectronics fabrication for ICs. The minimum feature size has continued to decrease with increasing integration density as predicted by semiconductor roadmaps. Microsensors and microactuators are being integrated with on-chip CMOS circuitry exploring the opportunities of CMOS-based microelectromechanical systems (MEMS).

In pre-CMOS MEMS integration, the MEMS structures are first micromachined and must meet strict criteria in terms of issues such as contamination and planarization before being able to continue with commercially available CMOS microelectronics processing. In intermediate-CMOS MEMS integration, the CMOS process is interrupted for additional micromachining steps. This approach requires custom fabrication facilities. In post-CMOS MEMS integration, the MEMS devices are built on top of a CMOS substrate. This approach is advantageous because the CMOS wafers are fabricated at any industrial CMOS foundry where advanced technologies can be exploited for MEMS. The main limitation of post-CMOS is the stringent thermal budget for the additional micromachining steps, limiting process temperatures to 400°C [3]. Amorphous Si is a promising candidate as a structural material for MEMS because it has similar mechanical properties similar to polysilicon but offers much lower temperature deposition suitable for post-CMOS integration.

#### 1.1.4 Tunable RF MEMS Devices