# Energy Efficient Design for Deep Sub-micron CMOS VLSIs

by

Mohamed Elgebaly

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2005 ©Mohamed Elgebaly 2005 I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Over the past decade, low power, energy efficient VLSI design has been the focal point of active research and development. The rapid technology scaling, the growing integration capacity, and the mounting active and leakage power dissipation are contributing to the growing complexity of modern VLSI design. Careful power planning on all design levels is required. This dissertation tackles the low-power, low-energy challenges in deep sub-micron technologies on the architecture and circuit levels.

Voltage scaling is one of the most efficient ways for reducing power and energy. For ultra-low voltage operation, a new circuit technique which allows bulk CMOS circuits to work in the sub-0.5V supply territory is presented. The threshold voltage of the slow PMOS transistor is controlled dynamically to get a lower threshold voltage during the active mode. Due to the reduced threshold voltage, switching speed becomes faster while active leakage current is increased. A technique to dynamically manage active leakage current is presented. Energy reduction resulting from using the proposed structure is demonstrated through simulations of different circuits with different levels of complexity.

As technology scales, the mounting leakage current and degraded noise immunity impact performance especially that of high performance dynamic circuits. Dual threshold technology shows a good potential for leakage reduction while meeting performance goals. A model for optimally selecting threshold voltages and transistor sizes in wide fan-in dynamic circuits is presented. On the circuit level, a novel circuit level technique which handles the trade-off between noise immunity and energy dissipation for wide fan-in dynamic circuits is presented. Energy efficiency of the proposed wide fan-in dynamic circuit is further enhanced through efficient low voltage operation.

Another direct consequence of technology scaling is the growing impact of interconnect parasitics and process variations on performance. Traditionally, worst case process, parasitics, and environmental conditions are considered. Designing for worst case guarantees a fail-safe operation but requires a large delay and voltage margins. This large margin can be recovered if the design can adapt to the actual silicon conditions. Dynamic voltage scaling is considered a key enabler in reducing such margin. An on-chip process identifier to recover the margin required due to process variations is described. The proposed architecture adjusts supply voltage using a hybrid between the one-time voltage setting and the continuous monitoring modes of operation. The interconnect impact on delay is minimized through a novel adaptive voltage scaling architecture. The proposed system recovers the large delay and voltage margins required by conventional systems by closely tracking the actual critical path at anytime. By tracking the actual critical path, the proposed system is robust and more energy efficient compared to both the conventional open-loop and closed-loop systems.

#### Acknowledgements

This dissertation is dedicated to the memory of my father, Maher Elgebaly.

Looking back on my days at Waterloo, I realize that I am tremendously blessed by God Almighty to have the ability to withstand the pressure of graduate studies and to be able to complete this dissertation. I have been also blessed to have had teachers, friends, colleagues, and a family who have been providing me with guidance and support.

I am fortunate to have had Prof. Manoj Sachdev as my research advisor. This thesis would have been difficult without his encouragement, support, and listening to my ideas even when they did not make sense. In Waterloo, Manoj and many other professors inspired me on both the academic and the personal levels. In particular, I would like to acknowledge Mark Aagaard, Anwar Hassan, and Gord Agnew.

It would have been difficult for me to continue the course of graduate school without an exceptional group of friends. I still remember when Amr Wassal and Ayman Alsayed picked me up from Pearson Airport when my feet first touched the Canadian land. Nayer Wanas and Mohamed Mohsen were my housemates for a year. We had a wonderful time together, from painting our rooms in the house, the submarine, to the amount of food that we used to cook. I will always remember that whatever the amount of food left after dinner would not see the morning light. Has Khalid Hammouda joined the club, I have had a good time listening to an enormous number of funny jokes. We enjoyed our dinners together, the movie nights, and the road trips to Montreal and Toronto. My memories of Algonquin park camping trips will never fade away. With Muhammed Nummer, I drafted the second idea on dynamic voltage scaling. I learned from Mohamed Kamal how objectivity is an essential part of success. Ehab Elsaadaany and Yasser Ibrahim are like big brothers to me with their soft and open hearts. With the support of these friends and many others I managed my way through the years I spent in Waterloo. Having an internship at Qualcomm in San Diego has had a profound impact on my research track. Amr Fahim, Tauseef Kazi, and Inyap Kang have introduced me to the second part of this dissertation, dynamic voltage scaling, and guided me through. Amr was of tremendous help during my stay at Qualcomm and in San Diego in general. I also would like to acknowledge Lew Chua and Devin Kelley who helped me testing my second test chip.

In the department of Electrical and Computer Engineering, Wendy Boles and Phil Regier have been very helpful on the administrative and the computing related issues. The Natural Science and Engineering Research in Canada (NSERC) provided the financial support for my research.

I am at a loss of words to express my gratitude to my mother and my brother for their continuous love and support. Spending years away from home was hard for me and even harder for my mother who patiently has encouraged and supported me. Mahmoud, my wonderful brother, has been there for me whenever I needed him. I feel fortunate to have them always standing by my side.

I am grateful to God who blessed me with my wife, Amira. Her love, support, and encouragement throughout the last and most important period of my Ph.D. has made it possible for me to reach the stage of writing these lines. She put my dreams ahead of hers. For this I am very grateful, my princess.

## Contents

| 1 | Intr | Introduction |                                                 |    |

|---|------|--------------|-------------------------------------------------|----|

|   | 1.1  | Motiva       | ation for Low Voltage and Low Energy Design     | 2  |

|   | 1.2  | Thesis       | Organization                                    | 5  |

| 2 | Low  | -Powe        | er, Low-Energy CMOS Design                      | 9  |

|   | 2.1  | Introd       | luction                                         | 9  |

|   | 2.2  | Power        | Dissipation Components in Digital CMOS Circuits | 11 |

|   |      | 2.2.1        | Switching power                                 | 13 |

|   |      | 2.2.2        | Leakage Power                                   | 15 |

|   | 2.3  | Power        | and Energy Reduction Techniques                 | 18 |

|   |      | 2.3.1        | Supply Voltage Reduction                        | 18 |

|   |      | 2.3.2        | Circuit Level Techniques                        | 21 |

|   |      | 2.3.3        | Device Level Optimizations                      | 25 |

|   | 2.4  | Leaka        | ge Reduction Techniques                         | 26 |

|   |      | 2.4.1        | Multi-Threshold CMOS (MTCMOS)                   | 27 |

|   |      | 2.4.2        | Variable-Threshold CMOS (VTCMOS)                | 29 |

|   |      | 2.4.3        | Transistor Stacking                             | 30 |

|   |      | 2.4.4        | Gate level leakage reduction                    | 31 |

|          | 2.5 Ultra-Low Voltage Circuit Techniques |                                                                       | 32 |

|----------|------------------------------------------|-----------------------------------------------------------------------|----|

|          |                                          | 2.5.1 Dynamic Threshold PMOS (DTPMOS) Scheme                          | 33 |

|          |                                          | 2.5.2 DTPMOS Implementation of Parallel MultiplicationBuilding Blocks | 34 |

|          |                                          | 2.5.3 Active Leakage Power Management Techniques                      | 38 |

|          |                                          | 2.5.4 Simulation Results and Comparison                               | 40 |

|          | 2.6                                      | Summary                                                               | 43 |

| 3        | Ene                                      | ergy Efficient Dynamic Circuits                                       | 45 |

|          | 3.1                                      | Introduction                                                          | 45 |

|          | 3.2                                      | Leakage Tolerant Wide Domino Logic                                    | 47 |

|          | 3.3                                      | Split Domino (SD) Circuit Technique                                   | 51 |

|          | 3.4                                      | Simulation Results and Comparison of the SD Circuit Technique         | 54 |

|          | 3.5                                      | Low Voltage Operation of Wide Fan-In Domino Circuits                  | 58 |

|          | 3.6                                      | MOSFET Device Model for Circuit Analysis                              | 64 |

|          | 3.7                                      | Modeling of Conventional Wide Fan-In Domino Circuits                  | 70 |

|          |                                          | 3.7.1 Optimum Keeper Sizing                                           | 70 |

|          |                                          | 3.7.2 Dynamic Node Capacitance Estimation                             | 72 |

|          |                                          | 3.7.3 Delay Estimation                                                | 74 |

|          | 3.8                                      | Model Extension to Complex Designs                                    | 77 |

|          | 3.9                                      | Optimization of Wide Fan-In Domino Gates                              | 80 |

|          | 3.10                                     | Summary                                                               | 87 |

| <b>4</b> | Rob                                      | oust and Efficient DVS                                                | 89 |

|          | 4.1                                      | Introduction                                                          | 89 |

|          | 4.2                                      | Dynamic Voltage Scaling Systems for Deep-Submicron Technologies       | 94 |

|          |                                          | 4.2.1 Open-loop DVS                                                   | 97 |

| 6                                 | Con | clusior | ns                                             | 149 |

|-----------------------------------|-----|---------|------------------------------------------------|-----|

|                                   | 5.2 | Critica | l Path Emulator Test Chip                      | 137 |

|                                   | 5.1 | Open-l  | loop DVS Test Chip                             | 133 |

| 5 DVS System Experimental Results |     | 133     |                                                |     |

|                                   | 4.7 | Summa   | ary                                            | 130 |

|                                   | 4.6 | Analys  | sis of the Critical Path Emulator Architecture | 125 |

|                                   |     | 4.5.3   | Algorithm                                      | 123 |

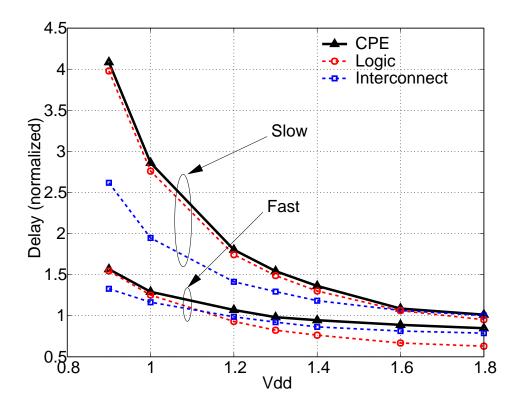

|                                   |     | 4.5.2   | Delay Modeling of Logic and Interconnects      | 120 |

|                                   |     | 4.5.1   | Proposed Architecture                          | 116 |

|                                   | 4.5 | Critica | l Path Emulator Architecture                   | 112 |

|                                   | 4.4 | Analys  | sis of the Hybrid DVS system                   | 109 |

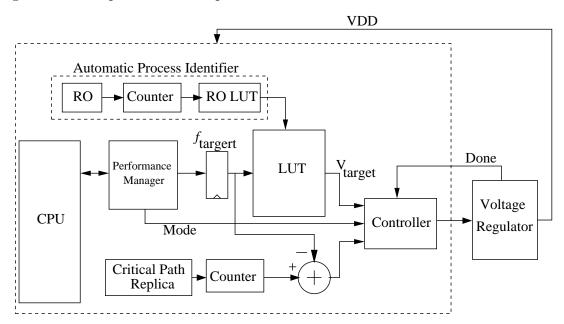

|                                   | 4.3 | Hybrid  | l Dynamic Voltage Scaling Architecture         | 104 |

|                                   |     | 4.2.2   | Closed-loop DVS                                | 99  |

## List of Tables

| 2.1 | Strategies for converting a high-performance chip to a low-power chip $[1]$ . | 11  |

|-----|-------------------------------------------------------------------------------|-----|

| 2.2 | VTCMOS vs. MTCMOS techniques                                                  | 30  |

| 2.3 | Simulation results for the 16x16-bit multiplier architectures                 | 42  |

| 2.4 | 16x16-bit Multiplier Architectures Comparison                                 | 42  |

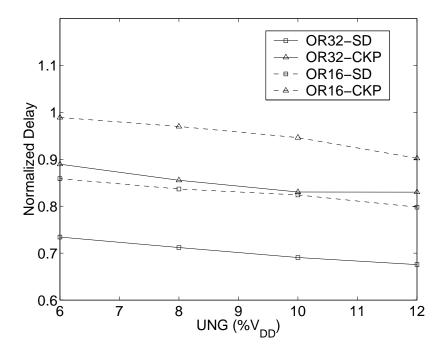

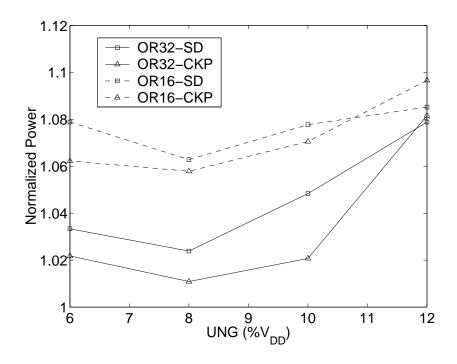

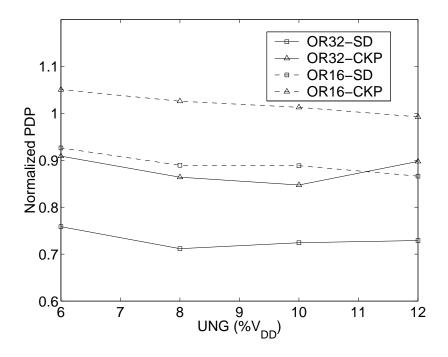

| 3.1 | Simulation results at 12% UGDN                                                | 58  |

| 3.2 | Leakage Current Model Parameters                                              | 81  |

| 3.3 | Model Parameters for Worst Case Delay                                         | 82  |

| 4.1 | RO LUT for Process Split Identification                                       | 107 |

| 4.2 | LUT for Split Compensation                                                    | 108 |

# List of Figures

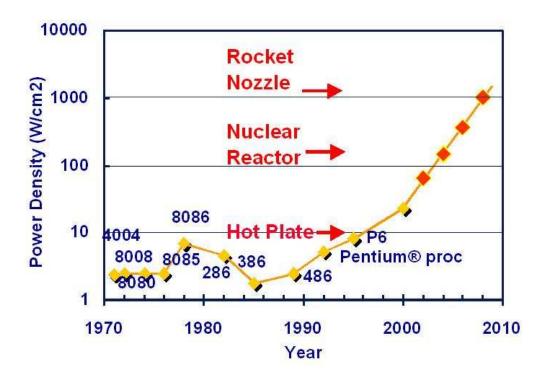

| 1.1  | Power Density of modern microprocessors approaches that of the Hot plate. | 3  |

|------|---------------------------------------------------------------------------|----|

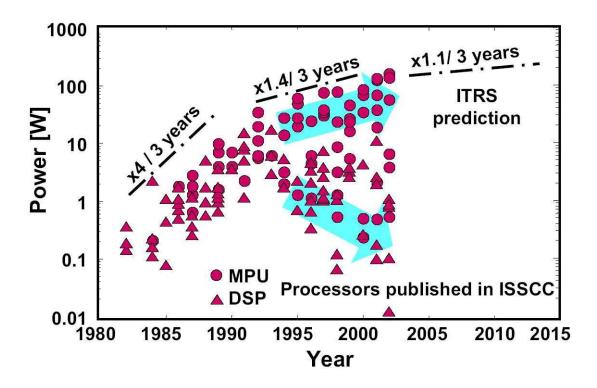

| 1.2  | Power Dissipation increase is bounded with scaling                        | 4  |

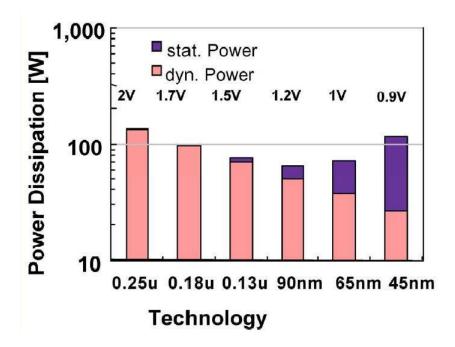

| 2.1  | Static and Dynamic Power for different technology generations             | 12 |

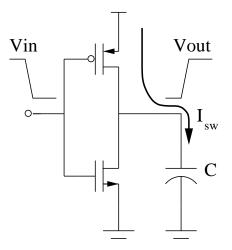

| 2.2  | Switching Power in a CMOS Inverter                                        | 13 |

| 2.3  | Leakage Current Components                                                | 16 |

| 2.4  | Parallelism vs. Pipelining.                                               | 20 |

| 2.5  | Logic Styles                                                              | 22 |

| 2.6  | Silicon On Insulator (SOI) devices.                                       | 26 |

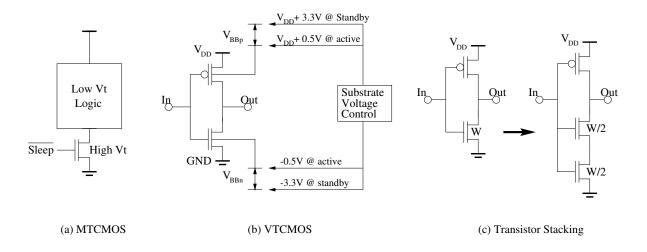

| 2.7  | Leakage Reduction Techniques                                              | 28 |

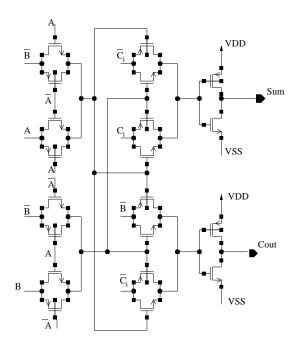

| 2.8  | DTPMOS Full Adder circuit.                                                | 35 |

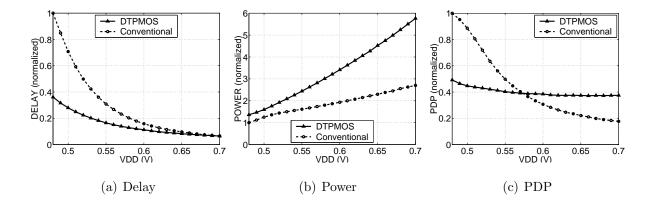

| 2.9  | DTPMOS and Conventional CMOS FA simulations results                       | 36 |

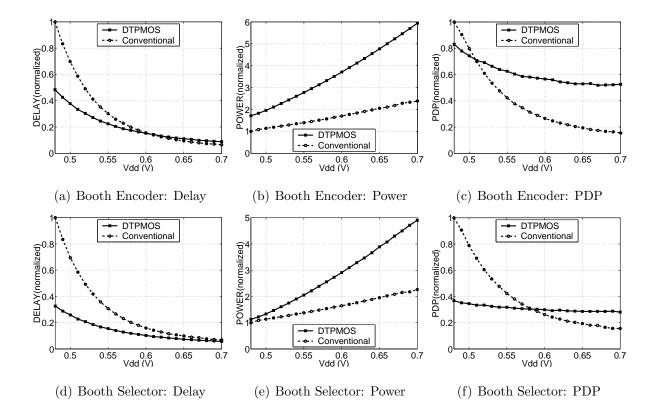

| 2.10 | Results for DTPMOS vs. Conventional for the Booth Encoder and Selector.   | 37 |

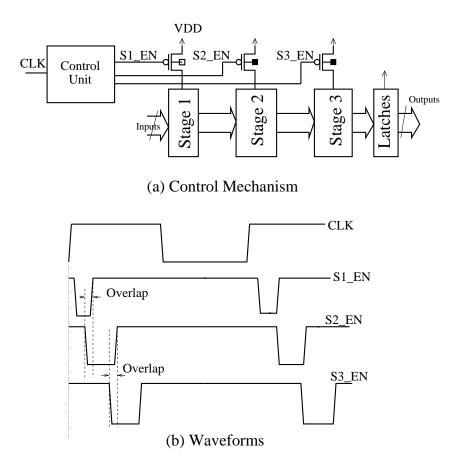

| 2.11 | Static active leakage power management scheme                             | 39 |

| 2.12 | Simulation results for the static active leakage reduction                | 40 |

| 2.13 | Dynamic active leakage power management scheme                            | 41 |

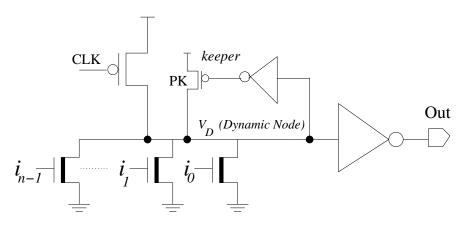

| 3.1  | Conventional DVT Wide Fan-In Domino <i>n</i> -input OR gate               | 47 |

| 3.2  | Conditional Keeper technique                                              | 48 |

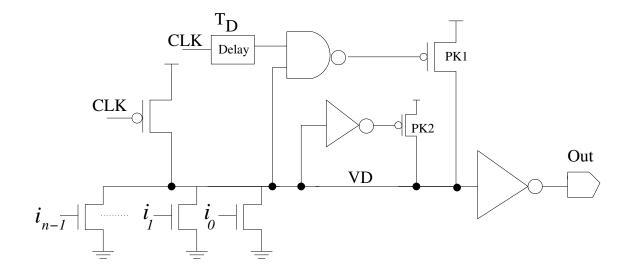

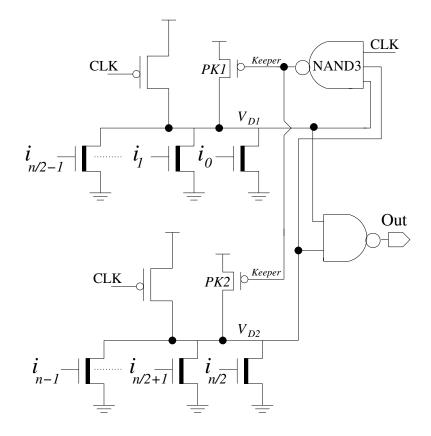

| 3.3  | n-input split domino (SD) OR gate                                               | 51 |

|------|---------------------------------------------------------------------------------|----|

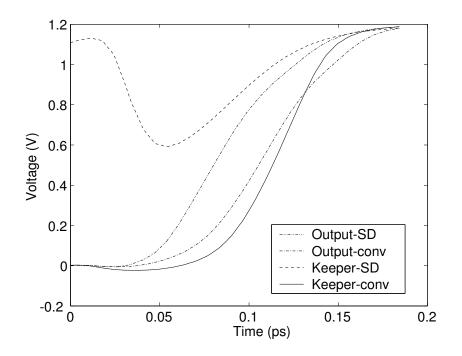

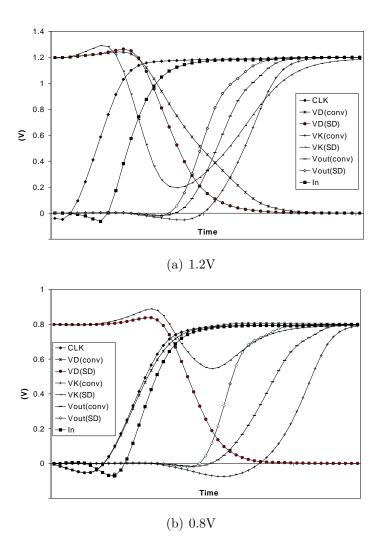

| 3.4  | Keeper and output waveforms for SD and conventional 32-input OR gate .          | 52 |

| 3.5  | Delay of SD, CKP and conventional Domino                                        | 55 |

| 3.6  | Power Dissipation of SD, CKP and conventional Domino                            | 56 |

| 3.7  | Energy of SD, CKP and conventional Domino                                       | 57 |

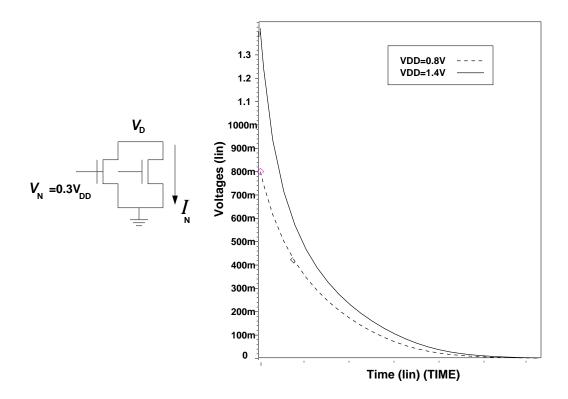

| 3.8  | Discharge time for two different noise levels at two different supply voltages. | 60 |

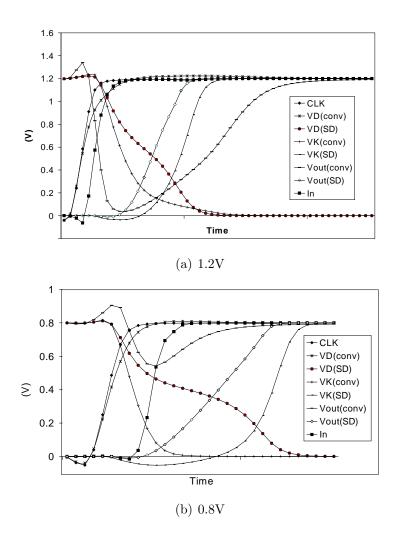

| 3.9  | Simulations for 8-bit SD and conventional Domino.                               | 62 |

| 3.10 | Simulations for 16-bit SD and conventional Domino                               | 63 |

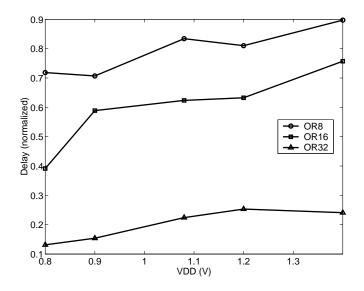

| 3.11 | Delay of SD vs. conventional Domino.                                            | 64 |

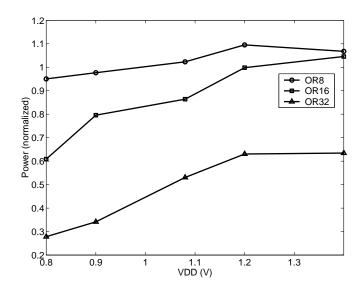

| 3.12 | Power of SD vs. conventional Domino.                                            | 65 |

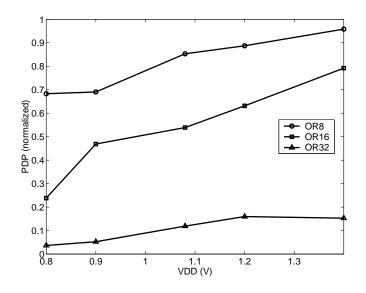

| 3.13 | Energy of SD vs. conventional Domino                                            | 66 |

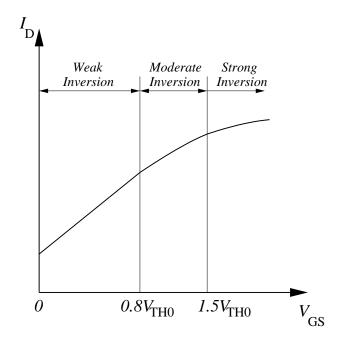

| 3.14 | Different Inversion Modes for the MOSFET Device                                 | 68 |

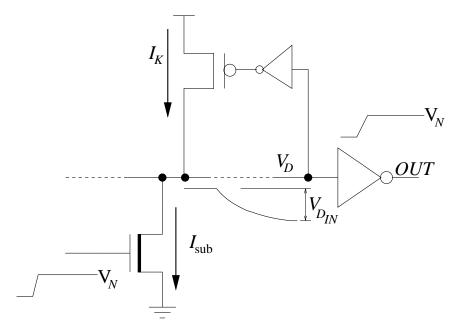

| 3.15 | Keeper transistor sizing                                                        | 71 |

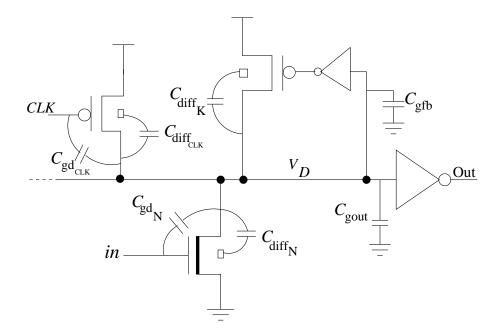

| 3.16 | Dynamic node capacitive components                                              | 73 |

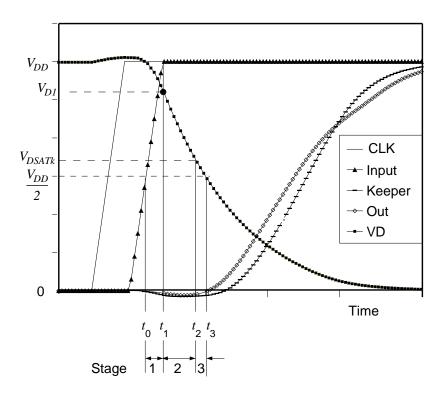

| 3.17 | Transient Response of a Conventional 16-input Domino Gate                       | 76 |

| 3.18 | Simulation Waveforms for Split Domino                                           | 78 |

| 3.19 | Keeper Device Size for 4, 8, 16, and 32 -input Conventional Domino. $\ldots$    | 83 |

| 3.20 | Model vs. Simulation for 4, 8, 16, and 32-bit Conventional Domino               | 84 |

| 3.21 | Model vs. Simulation for 4, 8, 16, and 32-bit SD Domino                         | 85 |

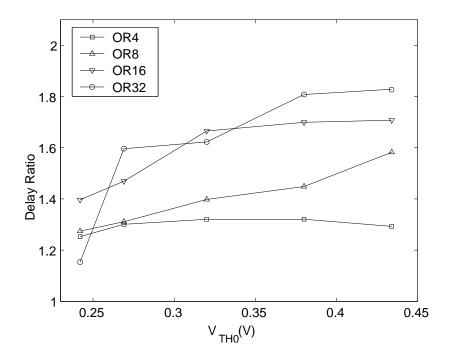

| 3.22 | Ratio of Conventional Delay to SD delay                                         | 86 |

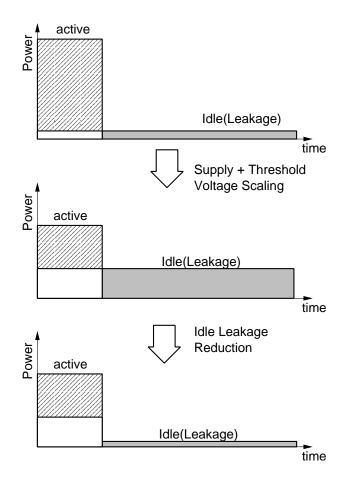

| 4.1  | Power reduction through reducing supply voltage                                 | 92 |

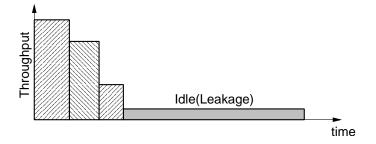

| 4.2  | Throughput required for a certain application                                   | 93 |

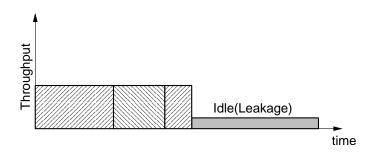

| 4.3  | Task Scheduling with Dynamic Voltage Scaling.                                   | 93 |

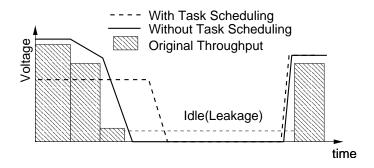

| 4.4  | Dynamic Voltage Scaling with and without Task Scheduling                        | 94 |

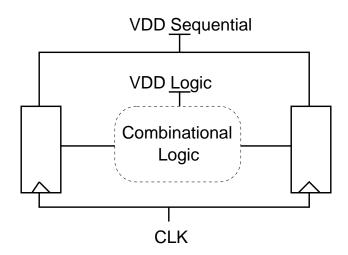

| 4.5  | Two power supplies scheme for low standby power applications                    | 95 |

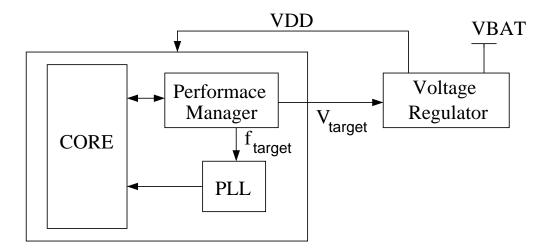

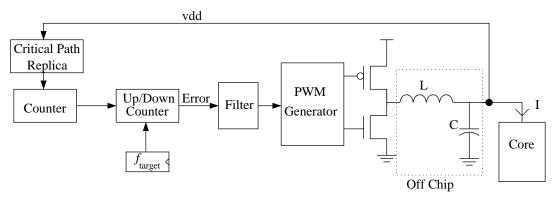

| 4.6  | Architecture of a Dynamic Voltage Scaling System.                            | 96  |

|------|------------------------------------------------------------------------------|-----|

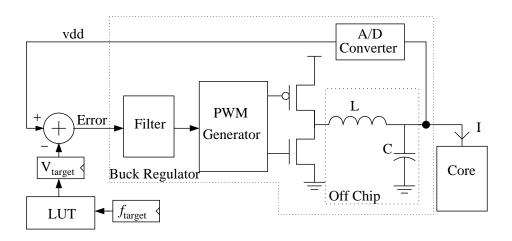

| 4.7  | Open-loop DVS                                                                | 98  |

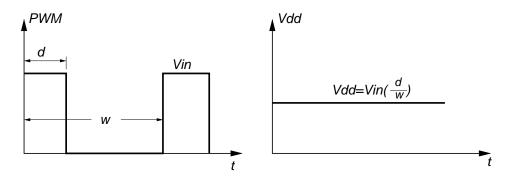

| 4.8  | Converting the PWM signal to a DC voltage.                                   | 98  |

| 4.9  | Closed-loop DVS.                                                             | 100 |

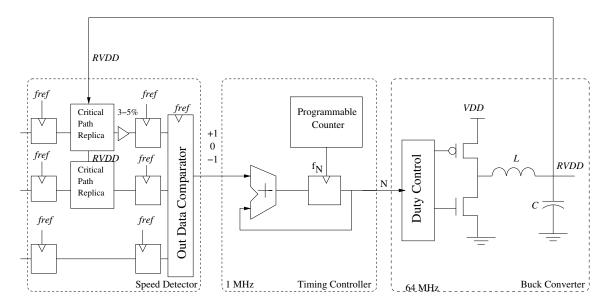

| 4.10 | Closed-loop DVS system using a critical path replica                         | 101 |

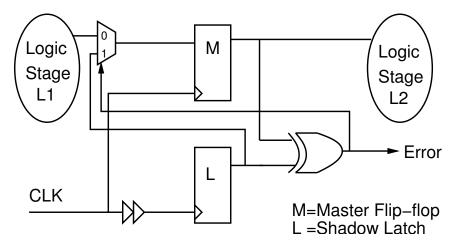

| 4.11 | Razor approach                                                               | 102 |

| 4.12 | Architecture of the proposed hybrid DVS system                               | 104 |

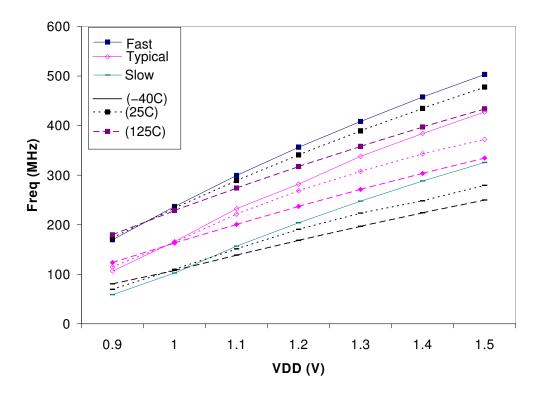

| 4.13 | Critical path frequency scaling across process and temperature. $\ldots$ .   | 106 |

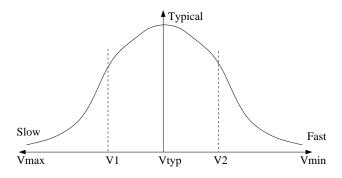

| 4.14 | Voltage Distribution due to Process Variation at a fixed frequency           | 109 |

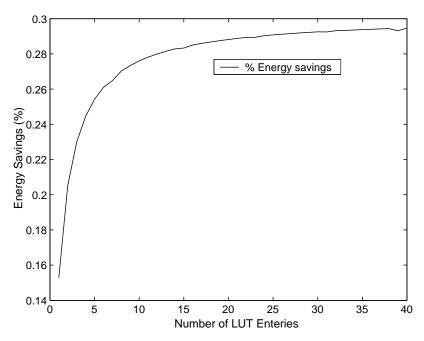

| 4.15 | Energy Savings vs. number of entries in the LUT                              | 110 |

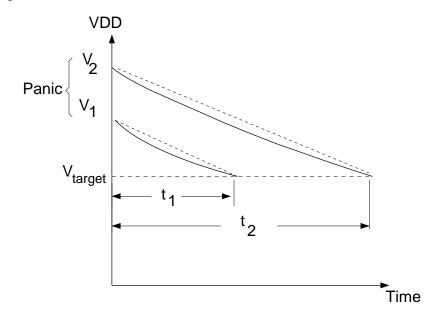

| 4.16 | Voltage Waveform when going to panic mode                                    | 111 |

| 4.17 | Critical path changing due to process and interconnect variations            | 113 |

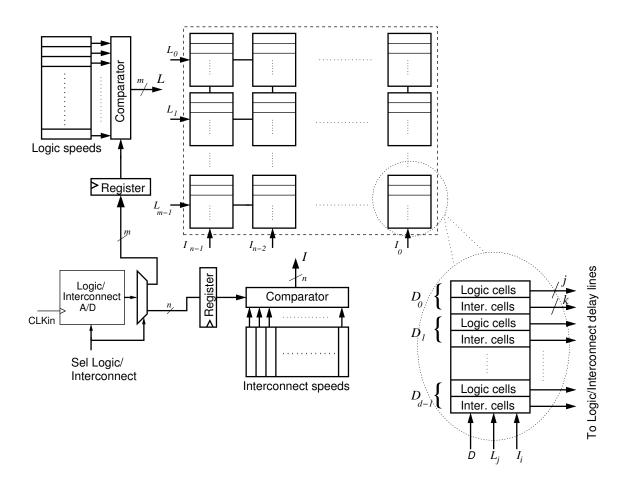

| 4.18 | Critical Path Emulator Architecture.                                         | 115 |

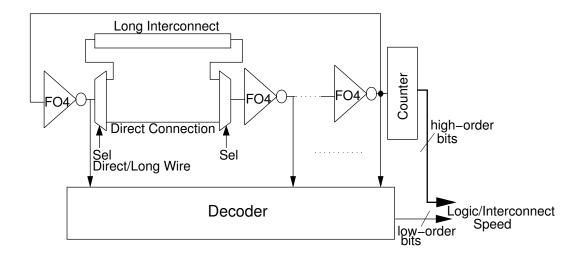

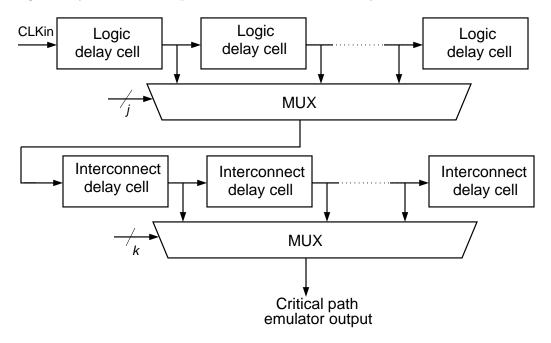

| 4.19 | Logic and Interconnect low-power high-resolution A/D                         | 118 |

| 4.20 | Implementation of logic and interconnect delay lines                         | 119 |

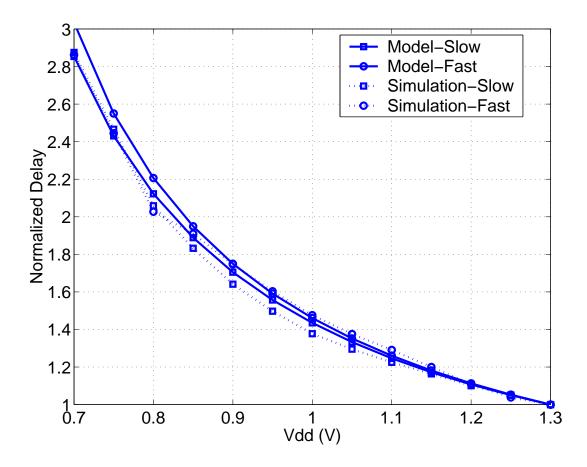

| 4.21 | Logic delay vs. HSPICE simulations                                           | 122 |

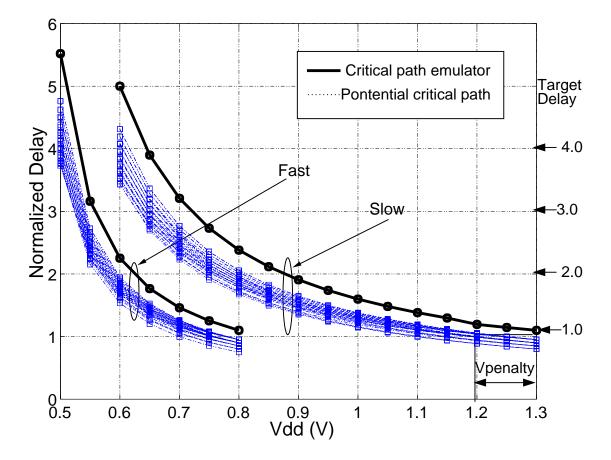

| 4.22 | The CPE tracks well with the actual critical path                            | 126 |

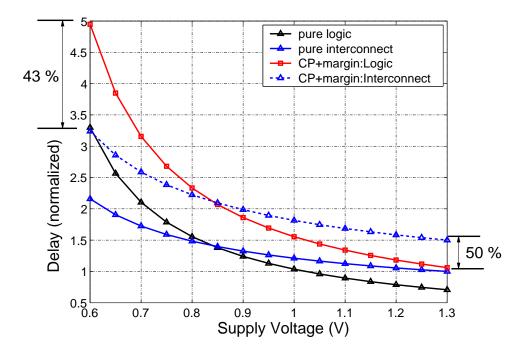

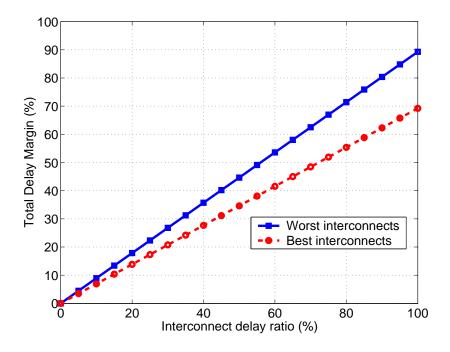

| 4.23 | Delay margin required to compensate for process and interconnect variations. | 129 |

| 4.24 | Delay margin required by conventional AVS                                    | 130 |

| 4.25 | Energy Efficiency of the proposed vs. the conventional architectures         | 131 |

| 5.1  | Architecture of the Open-loop DVS System Test Chip                           | 134 |

| 5.2  | Post-layout and measured results for the Ring oscillator                     | 136 |

| 5.3  | Die photo for the Open-loop DVS system                                       | 137 |

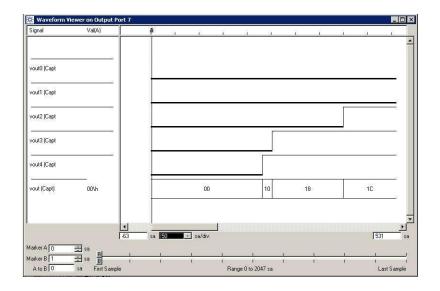

| 5.4  | Captured output voltage codeword for different target frequencies            | 138 |

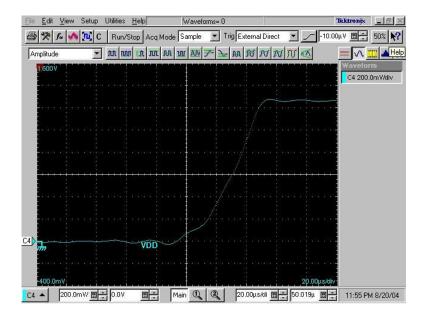

| 5.5  | Measured output of the programmable DC-DC converter                          | 139 |

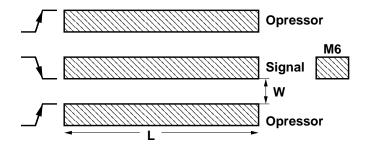

| 5.6  | Worst Case coupling for interconnect capacitance.    | 140 |

|------|------------------------------------------------------|-----|

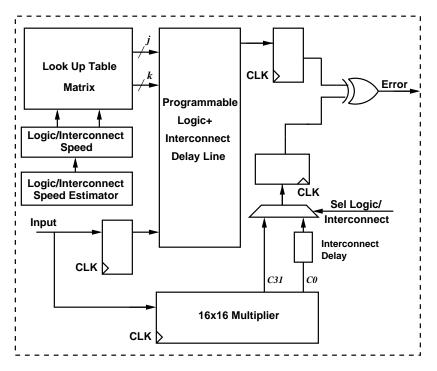

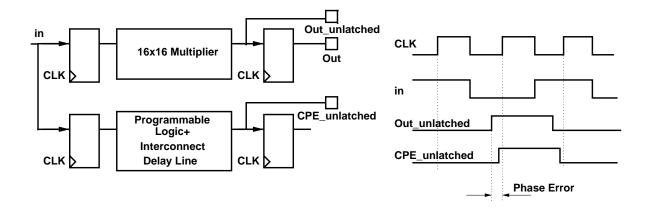

| 5.7  | Test chip schematic for the CPE system               | 141 |

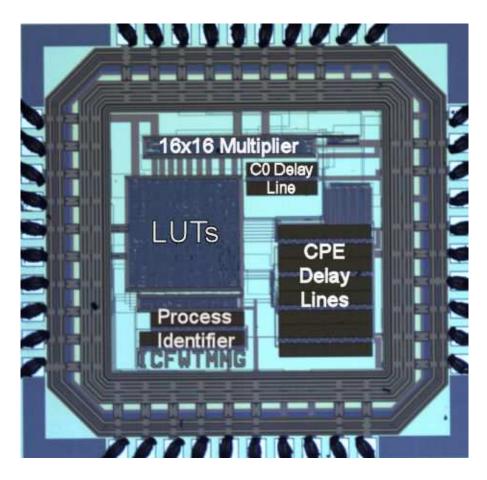

| 5.8  | Die photo for the Critical Path Emulator system.     | 143 |

| 5.9  | Post-layout simulation results for the CPE test chip | 145 |

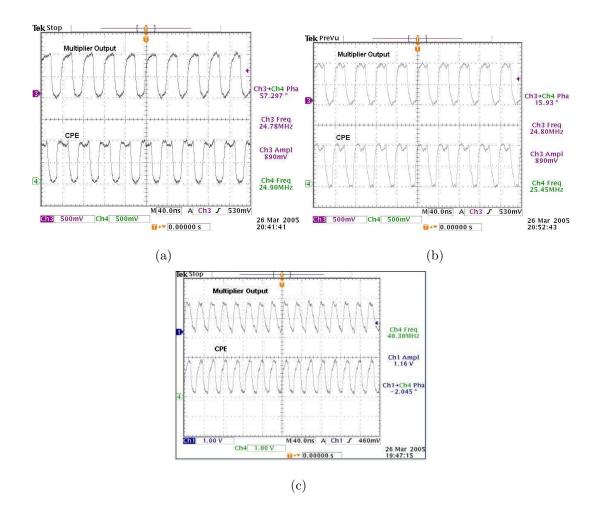

| 5.10 | Delay measurement arrangement for the CPE chip       | 146 |

| 5.11 | Measured results of the CPE test chip                | 147 |

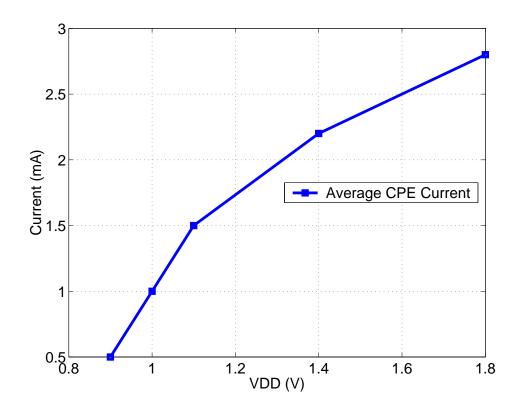

| 5.12 | Measured current dissipation of the CPE architecture | 148 |

# Nomenclature

| $V_{DD}$          | Supply voltage.                               |  |

|-------------------|-----------------------------------------------|--|

| $V_{TH}$          | Transistor threshold voltage.                 |  |

| $v_{TH}$          | Normalized Transistor threshold voltage.      |  |

| $V_{TH0}$         | Transistor threshold voltage at zero bias.    |  |

| $\gamma$          | Body effect coefficient.                      |  |

| $\eta$            | Drain-induced barrier lowering effect.        |  |

| $V_T$             | Thermal Voltage (26mV at $25^{\circ}$ C).     |  |

| $2\Phi_F$         | Surface potential at strong inversion.        |  |

| $\lambda$         | Channel length modulation coefficient.        |  |

| $\alpha$          | Alpha-law power model coefficient.            |  |

| $I_{DSAT}$        | Transistor saturation Current.                |  |

| $V_{DSAT}$        | Transistor saturation voltage.                |  |

| $I_{ m sub}$      | Subthreshold leakage current.                 |  |

| $I_{\rm w}$       | Weak inversion leakage current.               |  |

| n                 | Subthreshold swing coefficient.               |  |

| $V_{\rm off}$     | BSIM3 subthreshold current fitting parameter. |  |

| $N_{CH}$          | Channel carrier concentration.                |  |

| $\mu_{	ext{eff}}$ | Effective mobility.                           |  |

| tox               | Oxide thickness.                              |  |

| $C_{gd}$          | Gate-Drain capacitance.                       |  |

| $C_{diff}$        | Diffusion capacitance.                        |  |

| $C_D$             | Dynamic node capacitance.                     |  |

| $C_L$           | Load capacitance.                                  |

|-----------------|----------------------------------------------------|

| $	au_r$         | Signal rising time.                                |

| $t_{HL}$        | Output delay time during a high to low transition. |

| $t_{LH}$        | Output delay time during a low to high transition. |

| $I_{\rm ratio}$ | Interconnect to logic delay ratio of a path delay. |

| $t_{dl}$        | Logic delay potion of a path delay.                |

| $t_{di}$        | Interconnect delay potion of a path delay.         |

## List of Abbreviations

| DTPMOS | Dynamic threshold PMOS.          |  |  |

|--------|----------------------------------|--|--|

| MTCMOS | Multi-threshold MOS.             |  |  |

| VTCMOS | Variable-threshold MOS.          |  |  |

| DVT    | Dual-threshold logic.            |  |  |

| SOI    | Silicon On Insulator (SOI).      |  |  |

| FA     | Full adder.                      |  |  |

| SD     | Split-domino logic.              |  |  |

| CKP    | Conditional-keeper domino logic. |  |  |

| UGDN   | Unity-gain dynamic noise.        |  |  |

| DVS    | Dynamic voltage scaling.         |  |  |

| AVS    | Adaptive voltage scaling.        |  |  |

| PWM    | Pulse-width modulated signal.    |  |  |

| CPE    | Critical Path Emulator           |  |  |

| LUT    | Look-up table.                   |  |  |

### Chapter 1

## Introduction

The tremendous success of the semiconductor industry over the last 50 years has simply caused a significant change in our lifestyle. Integrated circuits are everywhere from computers to automobiles, from cell phones to home appliances. The growth of the semiconductor industry is predicted to continue even at a faster pace. Since the first integrated circuit was invented in the labs of Texas Instruments in 1958, the integration capacity of the transistors on a single chip is doubling every two to three years. In 1965, Gordon Moore showed that for any MOS transistor technology there exists a minimum cost that maximizes the number of components per integrated circuit. He also predicted that as transistor dimensions are shrunk from one technology generation to the next, the minimal cost point allows doubling the number of transistors every two to three years. This trend has been sustained and is expected to be maintained well into the first 20 years of this century [2].

Historically, technology scaling resulted in scaling of the transistor's dimensions by 0.7X each generation. Gate oxide also has been scaled to gain a better control over transistor characteristics. Supply voltage was kept constant is the so called "constant voltage scaling".

Not until reliability emerged to become an issue due to the continuous scaling of gate oxide, that the industry shifted into a different law of scaling. Constant field scaling has emerged in the early years of the last decade in order to keep a constant electric field inside the device. By then, electronics designers have started to face new challenges to keep scaling transistor dimensions as Moore predicted in his historic law.

## 1.1 Motivation for Low Voltage and Low Energy Design

As number of transistor is doubled every technology generation, chips grow in functionality and switching frequencies. The millions of parasitic capacitances charging and discharging at an ever increasing rate has led to a soaring amount of power dissipation. It has been shown that the usual scaling trend of transistors is facing three main challenges going forward [2]. The first and the most challenging is power dissipation. With clock speeds exceeding 4 GHz and switching millions of transistors, chip temperature has reached unprecedented levels requiring expensive packaging and heat dissipation techniques. Figure 1.1 shows that heat dissipation of modern processors is reaching the level of a hot plate. Serious reliability issues arise when working at such high temperatures [2].

Not until the last decade that power has started to become an issue that low power design has emerged to play an important role in modern VLSI design. Sakurai [3] showed that the trend of power dissipation of recent published microprocessors and digital signal processors (DSPs) is tapering off due to the limitation on power dissipation imposed by physical limits. Figure 1.2 shows that the early scaling trend for power dissipation was  $4 \times$  every 3 years. The rate of power dissipation has changed to  $1.4 \times$  every 3 years since heat is approaching the limit that current packaging technology is able to handle. The

Figure 1.1: Power Density of modern microprocessors approaches that of the Hot plate.

International Technology Roadmap for Semiconductors (ITRS) predicts an even slower rate of power dissipation increase moving forward.

Over the last few years, there has been a growing interest in low power processors and DSPs as shown in Figure 1.2. Since the early 1990s, the increasing demand for portable devices such as cellular phones has driven the semiconductor industry into a new low power and low energy frontier. A limited amount of energy stored in a small battery requires extensive power management techniques to lengthen battery lifetime for as long as possible. On the other hand, battery capacity have grown at the very modest rate (2 to 3 times over the last 30 years) [4]. Keeping performance enhancements with a limited energy source is

Figure 1.2: Power Dissipation increase is bounded with scaling.

a great challenge that faces low power designers.

Beside the above elements, another motive for energy efficient design is related to the environment. The information technology industry council estimated that electricity consumption of computers in the U.S. was about 13% of the total power in 1998 with an annual growth of 2 - 3% [5]. That means in about a decade, power consumed by the IT industry would be 25% of the total power consumed in the U.S. As more microelectronics are being used in everyday's life, the demand on energy will sharply increase. Therefore, the lower the power consumption, the lesser the heat generated and so the lower the cost required for extra cooling systems in offices and homes. In this respect, energy efficient design facilitates competitive cost-to-performance ratio of the electronic equipment.

#### **1.2** Thesis Organization

Energy efficient design often requires optimizations on all fronts and design levels. In this dissertation, new techniques to achieve energy efficient design on the architecture and on the circuit levels are presented. Chapter 2 presents an overview for the low power and low energy design aspects. The main power and energy reduction techniques are described. The concepts presented in Chapter 2 serve as a background and motivate the need for the work presented in later chapters. Moreover, low voltage, low energy circuit design is demonstrated through the DTPMOS technique. Low voltage is achieved by reducing the threshold voltage of the device dynamically during the active mode in order to increase current drive and speed. During the inactive mode, the threshold voltage is restored back to normal. Supply voltage applied to DTPMOS circuits is limited to 0.5V in order to limit the current resulting from the forward-biased drian/source to well junctions. The DTPMOS technique extends the concept of connecting the gate to the well usually used in Silicon On Insulator (SOI) technologies and applies it to bulk CMOS. Such a connection is possible in PMOS devices in the bulk technology. Shorting the well to the gate of the PMOS transistor helps improving its driving capability. However, since NMOS devices are connected to a common substrate, connecting the gate to the well is not possible.

Energy optimization of high speed circuits is addressed in Chapter 3. A new circuit technique suitable for scaled supply voltages in high-speed applications is presented. The Split Domino (SD) technique is a dynamic logic circuit technique. The high-speed advantage of dynamic logic is preserved by the SD technique while energy dissipation is reduced. The SD circuit technique offers reduced dynamic node capacitance and reduced contention at the start of the evaluation phase yielding better energy efficiency. In addition, a delay model for wide domino gates is presented. Model accuracy is close to HSPICE simulation. The model is used to examine different design tradeoffs early in the design stage to further improve energy efficiency.

Chapter 4 focuses on supply scaling reduction as a mean for power and energy reduction. Two different architectures to control supply voltage dynamically based on performance requirements are presented. Dynamic Voltage Scaling (DVS) systems are often categorized into an open-loop and a closed-loop system. The open-loop system is based on a one-time voltage setting that accommodates worst case delay scenario. The closed-loop system relies on continuous monitoring of the actual system performance through on-chip structures. A hybrid between the one time voltage setting (open-loop) and the closed-loop system is presented. The hybrid system saves energy by detecting the actual silicon conditions and adjusting supply voltage at the closest point required to achieve the required performance.

The impact of interconnect delay is increasing as the feature size is continuously being shrunk. Selecting a single critical path for a system and monitoring its actual performance is growing in complexity. It is becoming common in modern VLSIs to see several paths that have close delays with different mixtures of logic and interconnect delay. These paths have different voltage scaling characteristics due to the difference between voltage scaling behavior of logic and interconnect delay. The traditional DVS approach is to select a certain path and add enough margin to it to guarantee that it remains the most critical at all times. Otherwise, the dynamic voltage scaling system would fail. Such a margin is growing as technology is scaled down due to the increasing impact of the interconnect delay. Chapter 4 presents a technique to mitigate the impact of interconnect delay on deep sub-micron dynamic voltage scaling systems. The proposed critical path emulator (CPE) system closely tracks the actual critical path of the system whose supply voltage is dynamically scaled. The CPE system reduces the margin required by conventional systems and therefore, is more energy efficient. Experimental results for the open-loop and the closed-loop DVS systems described in Chapter 4 are presented in Chapter 5. Chapter 6 summaries the conclusions and thesis contributions.

### Chapter 2

# Low-Power, Low-Energy CMOS Design

#### 2.1 Introduction

Low power and low energy have captivated circuit designers for the past few years in the quest for enhancing performance and extending battery lifetime. The increasing demand for integrating more functions with faster speeds is met by a slow increase in the capacity of batteries. For example, the third generation (3G) wireless protocol provides real-time streaming video at a high data rate on a 3G-enabled cellular phone. Such a computation intensive application can impact the battery life of the portable device. Therefore, the demand for increased battery life will require designers to seek out new technologies and circuit techniques to maintain high performance with longer battery lifetime.

Portable devices, however, are not the sole motive behind the low power and low energy design efforts. The increasing power dissipation for fixed supply devices is almost equally challenging as for portable devices. As technology feature size is reduced, the number of transistors on the chip is increased and more power is dissipated. According to Moore's law, the number of transistors quadruples every two to three years. One hundred billion transistors on a single chip are projected before 2020 [6]. Expensive packing techniques are essential for dissipating such extensive power generated from that large number of transistors. Also, increased power dissipation has a negative impact on device's reliability.

Several methods for power and energy reduction have been proposed. Voltage supply,  $V_{DD}$ , scaling is considered one of the most effective elements in the process of reducing power dissipation in CMOS circuits. Threshold voltage,  $V_{TH}$ , has also to be reduced to maintain the required current drive. Reducing  $V_{TH}$  results in an exponential increase in leakage power. In order to keep leakage power under control, the ratio  $V_{DD}/V_{TH}$  tend to decrease with technology scaling.

The terms *low power* and *low energy*, although have different definitions, both serve to achieve the same objective. *Power* is defined as the average power supplied to a chip from the power supply and is measured in watts. Meanwhile, the term *energy* refers to the energy dissipated per operation and is measured in joules. In fact, energy can be expressed in terms of the *Power-Delay Product* (PDP), which is the product of power consumption and delay [7].

Table 2.1 shows the different strategies in converting a high-performance chip to a low-power chip using various power reduction methods [1]. The DEC Alpha 21064 chip operating at a supply voltage of 3.45V and consumes 26W of power at 200 MHz has been used as the starting point. As shown in the table, voltage supply reduction is the most effective among all other power reduction. When the supply voltage is scaled from 3.45V to 1.5V, power dissipation is reduced by a  $5.3 \times$ . Function reduction comes in second with  $3 \times$  reduction.

Shrinking device geometries introduces non-ideal device behavior in the form of short

|                           |                    | c 1•              | 1 1            | 1 • 「-  | 11          |

|---------------------------|--------------------|-------------------|----------------|---------|-------------|

| Table 2.1: Strategies for | converting a high- | performance chin  | to a low-nower | chin 11 |             |

|                           | converting a mon   | per for manee emp | to a lon ponor |         | <b>-</b>  • |

| Strategy                                                              | Power Reduction |

|-----------------------------------------------------------------------|-----------------|

| $V_{DD}$ reduction (3.45V $\rightarrow$ 1.5V)                         | $5.3 \times$    |

| Function reduction (Architectural level)                              | $3 \times$      |

| Scale process $(0.75\mu m \rightarrow 0.35\mu m)$                     | $2\times$       |

| Clock Load reduction (Latches $\rightarrow$ Single edge-triggered FF) | $1.3 \times$    |

| Clock frequency reduction (200MHz $\rightarrow$ 160MHz)               | $1.25 \times$   |

and narrow channel effects, drain-induced barrier lowering (DIBL), threshold voltage roll off. Producing low power, high performance, manufacturable transistors at low cost in deep-submicron (DSM) technology generations is growing in complexity. Further technology scaling problems arise due to inter and intra-die process variations.

### 2.2 Power Dissipation Components in Digital CMOS Circuits

Power consumption in CMOS circuits can be divided into three main components: shortcircuit power, switching power, and leakage power. Short-circuit power arises when a conducting path between supply and ground is formed. The pull-up and pull-down devices should to be sized properly to achieve approximately equal rise and fall time. This component of power consumption can be significant in precharge and evaluate circuits, e.g. dynamic circuits. Careful design is required to keep this component of power dissipation small enough to be ignored [8].

Switching power is a result of the power consumed in charging and discharging internal capacitances in the circuit. Leakage power is the power dissipated while the device is turned off. Leakage power has started to form a significant portion of the total power consumption as a result of the low threshold devices normally used in advanced DSM technologies. Figure 2.1 shows the increase in static (leakage) power for different technology generations [9]. It is apparent that static power is dramatically increasing with technology scaling. The ratio of leakage to total power is expected to exceed 50% in 45nm designs from about 10% in 90nm designs. Since switching and leakage power are the dominant components of power consumption, they are discussed in detail below.

Figure 2.1: Static (Leakage) and Dynamic (Switching) Power for different technology generations.

#### 2.2.1 Switching power

Switching power is the largest contributor to the total power dissipation in conventional CMOS technologies. It is a result of switching the junction, diffusion, and interconnect capacitances. Consider the CMOS inverter circuit in Figure 2.2. The parasitic capacitances are lumped into the output capacitor C. Consider the behavior of the circuit over one full clock cycle with the input going from  $V_{DD}$  to zero and back to  $V_{DD}$ . As the input switches from high to low, the NMOS pull-down transistor is turned OFF while the PMOS pull-up transistor is ON and capacitor C is charged. This charging process draws an energy equal to  $CV_{DD}^2$  from the power supply. Half of this energy is dissipated immediately in the PMOS transistor, while the other half is stored on C. When the input switches from zero back to  $V_{DD}$ , the NMOS pull-down turns ON and the capacitance C discharges through it. If the rise time of the input signal is slow, both PMOS and NMOS are simultaneously ON causing a short circuit current to flow. This slow rise/fall time should be avoided through proper transistors sizing.

Figure 2.2: Switching Power in a CMOS Inverter.

For any logic gate, if inputs to the gate are assumed to switch at a rate of f times per second, then the average switching power for that gate is given by

$$P_{sw} = \alpha. C. \Delta V^2. f_{clk} \tag{2.1}$$

where  $\alpha$  is the switching activity factor which represents the probability of the output switching from 0 to 1, C is the switching capacitance,  $\Delta V$  is the voltage swing, and  $f_{clk}$  is the switching frequency.

Generally,  $\alpha$  is less than one. As an example for activity factor computation, consider a 2-input NOR gate with equal probability of 0 and 1 at its inputs. The probability that the output becomes 0, is (3/4). While the probability the output is 1 would be (1/4). Therefore, the activity factor of the CMOS gate is given by the probability that the output is at 0 state (=3/4) multiplied by the probability the next state is 1 (=1/4). For the NOR gate, this translates to

$$\alpha = p(0)p(1) = p(0)(1 - p(0)) = \frac{3}{4}(1 - \frac{3}{4}) = \frac{3}{16}$$

(2.2)

Similar probabilities can be derived for other CMOS gates. In case of a logic network of several levels of gates, the activity factor of the gate becomes a function of its inputs probabilities.

For certain logic styles, however, glitching can form a non trivial part of the overall consumption. Glitching often arises when paths with unbalanced proportional delays converge at the same node in the circuit. If glitching due to signal races is to be accounted for,  $\alpha$  might be greater than one [10]. Calculations of this activity in a circuit is very difficult and requires careful logic and/or circuit level characterization of the gates in a library as well as detailed knowledge of the circuit structure [4].

Obviously, reducing any term in (2.1) will result in a reduction in switching power.

However, low power techniques needs to address power reduction without affecting performance or device functionality. For example, frequency reduction is beneficial in terms of power consumption but it affects the overall system speed. Therefore, it is often a challenge to reduce power dissipation while maintaining the system performance.

#### 2.2.2 Leakage Power

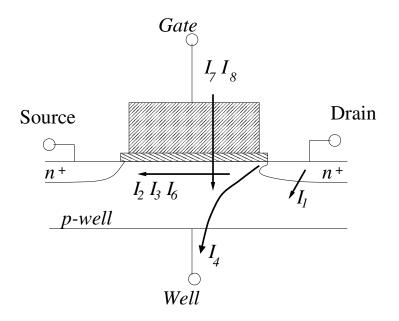

Leakage power forms a significant potion of the total power dissipation in DSM technologies. The different leakage current components are shown in Figure 2.3 [11].  $I_1$  is the reverse-bias p-n junction leakage caused by barrier emission and minority carrier diffusion and band-to-band tunneling.  $I_2$  is subthreshold conduction current.  $I_3$  results from the drain-induced barrier lowering (DIBL) effect.  $I_4$  is gate-induced drain leakage (GIDL).  $I_5$ is channel punchthrough.  $I_6$  is hot carrier injection current.  $I_7$  is oxide leakage.  $I_8$  is gate current due to hot carrier injection.  $I_1$  through  $I_6$  are OFF currents while  $I_7$  and  $I_8$  are ON and switching currents. Here, the main concern is the OFF leakage current and therefore, the focus is on the current components  $I_1$  through  $I_6$  which are explained below [12].

- Junction Reverse Bias Current  $(I_1)$ :  $I_1$  has two components: One is minority carrier diffusion/drift near the edge of the depletion region, and the other is due to electronhole pair generation in the depletion region of the reverse biased junction [13]. Heavily doped junctions are also prone to Zener and band-to-band tunneling. The p-n reverse bias leakage is a function of junction area and doping concentration.  $I_1$  is normally a minimal contributor to total OFF current.

- Subthreshold Conduction Current  $(I_2)$ : Subthreshold conduction or weak inversion current between source and drain when supply voltage is below  $V_{TH}$ . The subthreshold current occurs due to carrier diffusion when the gate-source voltage,  $V_{GS}$ , has

Figure 2.3: Leakage Current Components.

exceeded the weak inversion point, but still below the threshold voltage, where carrier drift is dominant. Subthreshold conduction typically dominates modern device off-state leakage due to the low threshold devices.

- Drain-Induced Barrier Lowering, DIBL  $(I_3)$ : DIBL is the effect of lowering the source potential barrier near the channel surface as a result of the applied drain voltage. Ideally, DIBL does not change the subthreshold slope but does lower  $V_{TH}$ . Higher surface and channel doping, and shallow source/drain junction depths work to reduce the DIBL mechanism.

- Gate-Induced Drain Leakage, GIDL  $(I_4)$ : GIDL current arises in the high electric field under gate/drain overlap region causing a thinner depletion region of drain to well junction. GIDL results in an increase in leakage current when applying a negative

voltage to the gate (NMOS case). GIDL is small for normal supply voltage but its effect rises at higher supply voltages (near burn-in).

- Punchthrough  $(I_5)$ : Punchthrough occurs when source and drain depletion regions approach each other and the gate voltage loses control over the channel current in the subgate region. Punchthrough current varies quadratically with drain voltage. Punchthrough is often regarded as a subsurface version of DIBL.

- Narrow width effect (I<sub>6</sub>): Threshold voltage tends to decrease in trench-isolated small effective channel width devices. The narrow width effect causes the threshold voltage to decrease in trench isolated technologies for channel widths on the order of W ≤ 0.5µm. It can be ignored for device sizes >> 0.5µm.

Subthreshold leakage current is the largest leakage current component. It increases exponentially as a result of threshold voltage reduction. In a simple form, subthreshold leakage current,  $I_{sub}$ , is given by

$$I_{sub} = I_0 e^{\frac{V_G - V_S - V_{TH0} - \gamma V_s + \eta V_{DS}}{n V_T}} \left(1 - e^{\frac{V_{DS}}{V_T}}\right)$$

(2.3)

where  $V_{TH0}$  is the zero-bias threshold voltage,  $\gamma$  is the linearized body effect coefficient,  $\eta$  is the DIBL coefficient,  $V_T$  is the thermal voltage (26 mV at room temperature), and  $I_0$  is a constant proportional to  $V_T$  and transistor dimensions.

Various techniques have been developed to keep both active and leakage power under control. In the next section, some of the effective power and energy reduction methodologies are described. The intent is to focus on these particular methodologies since the work presented in this thesis builds on these methodologies.

### 2.3 Power and Energy Reduction Techniques

Since switching power is the major source of power dissipation in CMOS technologies, various techniques have been proposed on a variety of design levels to achieve switching power reduction. Considering a top-down design paradigm, power and energy reduction can be achieved on the architecture, circuit, and device levels. Starting at the top level, the architecture is modified to lower power dissipation by introducing or adding parallelism or pipelining. When such modifications are implemented, power can be reduced via supply or frequency scaling. Moving down the design paradigm, both circuit and device level optimizations are required to enable energy efficient operation.

#### 2.3.1 Supply Voltage Reduction

Many designers have focused on power supply reduction as a mean for low power operation. By noting the three parameters that appear in (2.1), it is obvious that reducing frequency or switching capacitance provides a linear reduction in switching power. However, supply voltage reduction leads to quadrable savings. Moreover, subthreshold leakage current can be reduced exponentially with supply voltage reduction. As can be seen from (2.3), both  $V_G$ and  $V_{DS}$  are reduced when supply is scaled yielding an exponential scaling of subthreshold leakage. In [3], it was shown that both dynamic and leakage power can be effectively reduced through supply scaling.

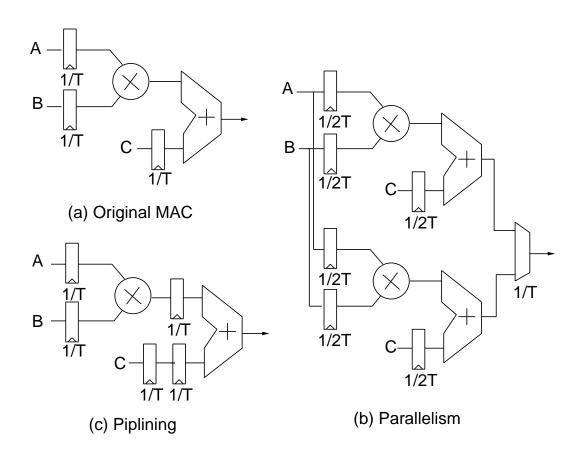

Voltage reduction enables architectural level power optimizations. Parallelism or pipelining can be employed to reduce power dissipation [10] [14]. Consider the *multiply and accumulate* (MAC) structure shown in Figure 2.4 (a). Assume that the clock period for maximum throughput at normal supply voltage is T. Using a duplicated MAC unit in parallel with the original one, the clock frequency can reduced by half (doing the computations in parallel) as shown in Figure 2.4 (b). Slashing the operating frequency by half can allow for a 40% reduction in the supply voltage (this reduction might vary from design to design and from one technology to another). Due to the parallelism used, the capacitance increases by a factor of 2 as a result of using a duplicated MAC. In addition, capacitance increases by another 20% due to the extra routing required. Therefore, the resulting reduction in power consumption of the parallel architecture compared to the original one is given by

$$P_{\text{parallel}} = CfV^2 = (2.2C_{\text{org}})(0.6V_{\text{org}})^2(0.5f_{\text{org}})$$

= 0.4P<sub>org</sub> (2.4)

where  $C_{\text{org}}$  is the original effective capacitance being switched per clock cycle. Apparently, the main restriction on using parallelism to reduce overall power is the area. A considerable part of the extra area required for parallelism is the extra routing area. Wiring capacitance represents a significant part of the total capacitance of a chip. In addition, wiring capacitance does not scale as much as the feature size. Therefore, careful optimization and sophisticated routing techniques have to be utilized to fully exploit the advantage of parallelism and minimize its side effects.

For area-constrained designs, pipelining is a viable option with much less area overhead compared to parallelism but yet a comparable throughput. By adding two extra latches at the adder inputs as shown in Figure 2.4 (c), the minimum clock period is reduced to that of the multiplier (assuming that the adder delay is less than that of the multiplier). Assuming that the clock frequency can be reduced by only 20% instead of 40% in case of parallelism for the static CMOS MAC architecture, this reduction in the clock frequency would leave a room for supply voltage reduction to get the same throughput of the original structure. Supply voltage can then be reduced by approximately 15%. The area overhead represented by the extra latches results in a switching capacitance increase of 15% instead of 220% in

Figure 2.4: Parallelism vs. Pipelining.

the case of using parallelism. Therefore, the power reduction in case of pipelining would be

$$P_{\text{pipeline}} = CfV^2 = (1.15C_{\text{org}})(0.85V_{\text{org}})^2(0.8f_{\text{org}})$$

$$= 0.65P_{\text{org}}$$

(2.5)

The power reduction is less than that of the parallel structure. Balancing the delay of all the pipelined stages is extremely important to achieve further reduction in power. That would allow for more supply voltage reduction and hence more power savings. In addition, increasing the level of pipelining also reduces the logic depth and hence the power contributed by hazards and critical races.

Furthermore, exploiting both pipelining and parallelism is more attractive. This architectural choice results in further speedup and more room for supply voltage reduction. This combination, given no restriction on area, would allow for more power savings.

#### 2.3.2 Circuit Level Techniques

Different static and dynamic logic styles have been introduced for the sole aim of reducing power. It is also a common design practice to combine both static and dynamic logic styles to optimize for delay and power at the same time. The merits of each logic style are explained below.

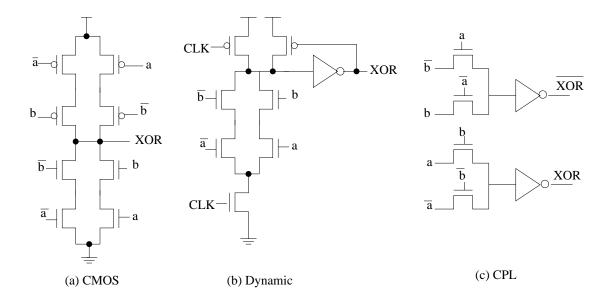

• Conventional CMOS logic style: Static CMOS logic refers to conventional CMOS circuits which are constructed using an NMOS pull-down network and a complementary PMOS pull-up network as shown in Figure 2.5 (a). Due to the complementary nature of the circuit, conventional CMOS logic style is inherently able to reject noise. Therefore, static CMOS is robust against voltage scaling and transistor sizing. Input signals are connected to the gate terminals, which facilitates the usage and characterization of logic cells. The layout of CMOS gates is simple and regular due to the similar, yet complementary, pull-up and pull-down network structure.

On the other hand, conventional CMOS suffers from inherent disadvantages due to the pull-up PMOS network. One of the main disadvantages is the increased gate capacitance resulting from the large size PMOS transistors. Furthermore, the PMOS transistor is usually made larger to compensate for the speed difference with respect to the NMOS due to the lower hole mobility compared to electron mobility. However, this disadvantage is diminishing as technology feature size is shrunk. The carrier drift

Figure 2.5: Logic Styles

velocities of both PMOS and NMOS approach the saturation velocity and therefore the size ratio between PMOS and NMOS devices is quickly approaching one [15]. Another drawback of static CMOS logic is the relatively weak driving current. By adding output buffers, the driving current can be enhanced.

• Dynamic Logic Style: Dynamic logic operates in two phases: precharge and evaluation. During the precharge phase, the *CLK* signal charges up the dynamic node (shown in Figure 2.5 (b)). During the evaluation phase, the *CLK* signal switches High. Depending upon input values, the dynamic node is discharged or remains charged. Dynamic logic is usually faster than static CMOS due to less capacitance (PMOS network is eliminated). However, dynamic logic consumes more power. Many dynamic logic styles with improved delay and power compared to the conventional dynamic style shown in Figure 2.5 (b) have been reported. Some of these design styles will be discussed in more details in Chapter 3.

• Pass-Transistor Logic Style: Unlike static and dynamic logic, pass-transistor logic provides complementary output. Moreover, inputs are connected to both the gates and the sources of transistors. Pass-transistor gates have two input categories: pass inputs and control inputs. Pass inputs are connected to the sources of the devices while control inputs are connected to the gates. The strongest advantage of passtransistor implementation is that it can use just one network, usually NMOS, to build the logic. Also, the dual rail nature of the logic style can be used efficiently to implement multiplexing functions. However, connecting some inputs to the source causes a  $V_{TH}$  drop. As a result, the voltage swing is reduced and it requires restoration at the output stage to increase noise margin and to minimize short circuit currents. As a consequence, two NMOS networks would be used in addition to the output buffering circuitry. This overhead annihilates the advantage of the low transistor count and small input capacitance. Moreover, pass-transistor logic is sensitive to voltage scaling and transistor sizing. Finally, the layout of pass-transistor logic is complicated due to the extra wiring normally required. One example of pass-transistor logic is the complementary pass-transistor logic (CPL) shown in Figure 2.5 (c). CPL has two NMOS networks, one for each rail, and two inverters for level restoration [16]. CPL has small input capacitance, a fast differential output stage, and a high driving current. However, CPL, as a member of the pass-transistor logic family, suffers from short circuit currents at the output and wiring complexity due to the dual rail. Other pass-transistor logic styles have been proposed. A good comparison between the different styles can be found in [17]. In [17], static CMOS has been shown to have superior performance over pass-transistor logic. Therefore, static and dynamic logic usually occupy a larger share of the circuit design space.

From a low power perspective, static logic dissipates less power compared to dynamic logic due to the following reasons:

- 1. Spurious Transitions: Static designs are prone to spurious transitions more than dynamic circuits due to critical races and dynamic hazards in static logic. The magnitude and the number of those undesirable transitions in a logic structure is a function of the logic design, delay skew, and logic depth. For example, an 8-bit ripple carry adder consumes an extra 30% of power due to spurious transitions [10]. Dynamic logic, however, intrinsically does not suffer from spurious transitions, since any node can undergo at most one power-consuming transition per clock cycle.

- 2. Switching Capacitance: Dynamic logic has fewer devices, typically N+2 for N-input gate compared to 2N in case of CMOS. This is reflected directly on the switching capacitance and thus has a direct impact on delay and power dissipation.

- 3. Switching Activity: Dynamic logic is notorious for its high switching activity. The dynamic node has to be precharged every clock cycle even if it going to be discharged immediately after evaluation starts. For example, for a 2-input dynamic NOR gate, the switching activity is (3/4) compared to just (3/16) in case of static logic implementation. If spurious transitions are neglected, then using dynamic logic would result in a 4 times increase in power. But if reduction in capacitance and spurious transitions are taken into account, the resulting power increase would not be that dramatic.

With fewer transistors required to implement a certain dynamic logic function compared to static logic, standby leakage current of dynamic logic can be less than its static logic counterpart. In some applications where fast evaluation time is followed by a long idle period, dynamic logic can be more attractive than static logic for its low standby leakage.

#### 2.3.3 Device Level Optimizations

As mentioned before, CMOS is regarded as the technology of choice for low power and low energy applications. It offers a good performance and a considerable stability. However, as supply voltage is reduced, threshold voltage has to be reduced to maintain the required performance. A reduced threshold voltage directly results in an exponential increase in subthreshold current.

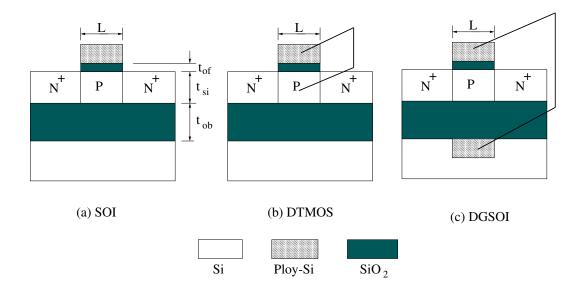

Some technologies have been offering a solution for the increase in subthreshold current resulting from the reduced threshold voltage. Silicon on insulator (SOI) technology has emerged with a good potential in low power and low voltage applications. A simple SOI device structure is shown in Figure 2.6 (a). In SOI technology, the thin film is totally isolated from the body by a thick film oxide. The thick oxide serves to suppress the radiation induced current. Also, due to the thick oxide layer, the gate to source/drain capacitance is greatly reduced. As a consequence, SOI devices are faster and consume less dynamic power compared to CMOS. In terms of integration and technology down scaling, the depletion regions in bulk CMOS which are used for isolation put a lower limit on feature size in bulk CMOS. The buried thick oxide in SOI makes it easier to down scale device dimensions.

Figure 2.6 shows two additional SOI structures. DTMOS SOI and DGSOI are shown in Figure 2.6 (b) and (c) respectively. DTMOS refers to the Dynamic Threshold MOS structure proposed in [18]. In the DTMOS structure, the gate is tied to the body of the SOI device. This type of connection allows for low threshold during the ON state and high threshold during the OFF state. The DGSOI is a Double-Gate SOI device in which there is a back gate separated from the body of the device by the back oxide [19]. The DGSOI has a higher current drive for high output load in addition to an excellent ability of leakage control [20].

Figure 2.6: Silicon On Insulator (SOI) devices.

However, the history-effect of SOI devices, and low thermal conductivity of the buried oxide which results in an increase in temperature are among the drawbacks of using SOI technology. Further development and innovations are required to enable a cost-effective and efficient SOI solution.

In addition to switching power, leakage power is forming an increasing portion of the total power dissipated in modern technologies, several techniques have been developed to reduce its impact. Some of these techniques are summarized in the next section.

# 2.4 Leakage Reduction Techniques

Modern DSM technologies are suffering from a dramatic increase in leakage current. Constant field scaling dictates that the supply voltage has to be reduced when downsizing the technology feature size. Low threshold voltage devices are used to maintain the required current drive and to satisfy performance specifications. Low threshold devices have caused a dramatic increase in leakage current. A direct and effective solution for that is to utilize low threshold devices in the critical path and high threshold devices elsewhere. The threshold voltage can be controlled utilizing the well bias of the device in the so called *Variable Threshold CMOS* (VTCMOS) [21].

Dual threshold technology is another way to address the increasing active and leakage power problem. The technology is a CMOS process with two types of devices, low threshold and high threshold device. Performance is enhanced by placing the low threshold devices on the critical path to increase performance and place the high threshold devices on the non-critical paths to decrease leakage. Several mechanisms have been developed to optimize the process of placing the low/high threshold devices on the gate level such as in [22] or on the transistor level such as in [23] and [24]. This method was presented in [25] and referred to as *Multi-Threshold CMOS* (MTCMOS). These two methodology are discussed in detail below. Some recent enhancements and design considerations are also summarized.

#### 2.4.1 Multi-Threshold CMOS (MTCMOS)

The leakage current can be dynamically controlled using multi-threshold devices as was proposed in [25] and is shown in Figure 2.7 (a). In this scheme, low  $V_{TH}$  logic is used for faster evaluation while a high  $V_{TH}$  NMOS device, *Sleep* device, is used to disconnect the logic from the supply during standby. A *Sleep* control signal is used to turn the high  $V_{TH}$ NMOS device ON and OFF depending upon the mode of operation. A clear drawback of this technique is the impact of the *Sleep* device sizing on performance. Increasing the *Sleep* transistor size more than necessary would add to the circuit capacitance and power dissipation while sizing it too small would result in a supply current limitation and speed degradation. Another potential problem in the MTCMOS scheme is the bounce of virtual ground line bouncing. In fact, the capacitance of the virtual ground line is much larger than that of the real ground resulting in a ground bounce. This bounce adversely affects both noise margin and delay. A methodology for properly sizing the *Sleep* device to minimize the delay based on mutual exclusive discharge patterns was proposed in [24].

Figure 2.7: Leakage Reduction Techniques

The advantage of low leakage during standby mode is stressed by back biasing the sleep transistors to more than  $V_{DD}$  [26] [27]. By reverse biasing the body of the sleep transistor, threshold voltage is increased and leakage current is decreased. Therefore, a low threshold voltage device can be used without an increase in leakage current during standby. The low threshold sleep device limits voltage drop during the active mode and provides more current drive. Improving the current drive during the active mode is highly desirable in order to achieve more speed. By increasing the voltage swing of the gate of the sleep transistor, the gate-to-source voltage becomes greater than zero and boosts the current drive [28].

#### 2.4.2 Variable-Threshold CMOS (VTCMOS)

VTCMOS technique uses all low threshold devices [21]. However, the threshold voltage is controlled using the well bias of the devices in a triple-well CMOS process. During the ON state, the well bias is  $V_{DD} + 0.5V$  for the p-well and -0.5V for the n-well allowing for low threshold voltage realization as shown in Figure 2.7 (b). During standby, the sourcebody junction is strongly reverse biased to increase the threshold voltage and to reduce leakage current. The p-well bias is set to  $V_{DD} + 3.3V$  while the n-well bias is set to -3.3V. Consequently,  $V_{TH}$  is adjusted to be 0.77V during the active mode and greater than 0.5V during the standby mode. One potential problem with this approach is that the threshold voltage varies as the square root of the body-source voltages. Therefore, the body-source voltage has to significantly increase to change the threshold voltage to a relatively higher value. VTCMOS is even more efficient in leakage current suppression for series connected transistors due to the increased body-effect [29].

VTCMOS scheme depends on a high body-effect to control the threshold voltage. With technology scaling, the body-effect is reduced from one technology generation to the next. The body effect is primarily reduced due to the short channel effects. Techniques such as well doping can be applied to enhance the short channel effects. However, well doping causes the doping levels in the vicinity of source-body and drain-body junctions to increase significantly. As the doping limit approaches the tunneling limit, the junction current increases exponentially, and becomes the dominant leakage component. Therefore, bodyeffect is reduced and limits the effectiveness of the VTCMOS scheme [30].

SOI technology can also be used in the implementation of VTCMOS. In [31], a siliconon-insulator-with-active-substrate (SOIAS) was used to dynamically control the threshold voltage. The dynamic threshold MOS (DTMOS) scheme is another mean to provide low threshold during the ON state and high threshold during the OFF state [18]. A summary of the different features of the MTCMOS and VTCMOS techniques is presented in Table 2.2 [32]. Moving towards smaller feature size, the MTCMOS technique seems to be a better choice. However, VTCMOS is more effective in reducing process variations which are increasing with technology scaling. Therefore, the choice between MTCMOS and VTCMOS is application dependent.

|                                    | MTCMOS             | VTCMOS                      |  |  |  |  |  |

|------------------------------------|--------------------|-----------------------------|--|--|--|--|--|

| Principle                          | Sleep-mode switch  | Well-bias threshold control |  |  |  |  |  |

| Low leakage in standby             |                    |                             |  |  |  |  |  |

| Products are already rolled out    | $\checkmark$       | $\checkmark$                |  |  |  |  |  |

| Scalability                        | $\checkmark$       | ×                           |  |  |  |  |  |

| $V_{TH}$ fluctuations compensation | ×                  | $\checkmark$                |  |  |  |  |  |

| $I_{DDQ}$ testing                  | ×                  | $\checkmark$                |  |  |  |  |  |

| Serial Sleep Device                | $\checkmark$       | ×                           |  |  |  |  |  |

| slower, lower yield                |                    |                             |  |  |  |  |  |

| Sleep-mode storage                 | Dual $V_{TH}$ FF's | Conventional FF's           |  |  |  |  |  |

| Process                            | Dual threshold     | d Triple Well or SOI        |  |  |  |  |  |

Table 2.2: VTCMOS vs. MTCMOS techniques

#### 2.4.3 Transistor Stacking

Narendra *et.al.* [33] examined the effect of transistor stacking on subthreshold leakage current reduction. It has been shown that the stacking effect increases as the technology

scales. Therefore, by forcing transistor stacking as shown in Figure 2.7 (c), speed can be traded for leakage reduction. The stack effect can reduce leakage current by 2 orders of magnitude for low  $V_{TH}$  devices and 3 orders of magnitude for high  $V_{TH}$  devices [33]. Stacking of transistors during the standby mode can be accomplished by controlling the sleep mode input vector to maximize the number of transistors is the stack during sleep. Such a technique has a negligible speed penalty. However, the minimum leakage state is difficult to achieve by using a specific vector that maximizes the use of stacking since it is not a default feature in all logic gates (e.g. Inverter, Nor, etc.). By combining the use of sleep vector control and forcing stacks in stackless structures, a 30-90% reduction is leakage can be achieved [34]. In addition, transistor stacking has been shown to effectively reduce gate leakage [35].

#### 2.4.4 Gate level leakage reduction

Wei *et.al.* [22] proposed a gate level optimization method for leakage reduction. In their work, gates are divided into groups, one is low threshold and the other is high threshold. Gates in the critical path are low  $V_{TH}$  for faster evaluation while non-critical path gates are high  $V_{TH}$  to reduce leakage. The optimization method is run iteratively to find the optimum gate assignment for the a given  $V_{TH}$  value. Leakage reduction through the use of multiple supply voltages can be also achieved. The normal supply voltage is assigned to the gates on the critical path while reduced voltages are applied to gates not on the critical path [36]. An earlier work was proposed in [37] where optimization of supply and threshold voltages are performed to achieve low power implementations.

## 2.5 Ultra-Low Voltage Circuit Techniques

Voltage supply,  $V_{DD}$ , reduction has been utilized to achieve low power, energy efficient operation due to the quadratic relationship between power and  $V_{DD}$ . The transistor's threshold voltage,  $V_{TH}$ , is often reduced to maintain a decent performance. In a limiting case, fully static CMOS logic works when  $V_{DD}$  is slightly greater than max {|  $V_{TH_p}$  |,  $V_{TH_n}$ } where  $V_{TH_p}$  and  $V_{TH_n}$  are the threshold voltages of the PMOS and NMOS transistors respectively. However, when  $V_{DD}$  is reduced below that value, the switching delay increases appreciably.

Reducing supply voltage is often accompanied by threshold voltage reduction in order to prevent current drive degradation and the resulting delay increase. Assaderaghi *et.al.* [18] introduced the concept of dynamically controlling the threshold voltage (DTMOS) by connecting the gate of the MOS transistor to its substrate in silicon on insulator (SOI) technology. Threshold voltage is reduced during the active mode and is restored back to normal during the standby mode. This results in a significant speedup during the active mode and normal standby leakage current. However, an exponential increase in active mode leakage current is observed due to threshold voltage reduction. A potential remedy to this increase in leakage current is to use one of the leakage reduction techniques described earlier.

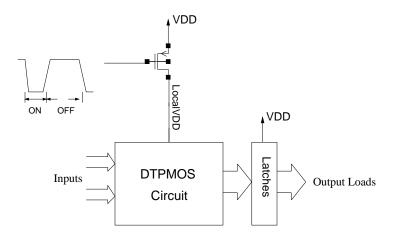

The DTPMOS technique extends the concept of dynamic threshold to bulk CMOS technologies. However, only the gate of the PMOS transistor is connected to the well. This type of connection can be implemented in bulk CMOS since each PMOS transistor is implemented in a separate well isolated from other PMOS transistors. This technique allows for energy efficient realizations of digital blocks working at sub-0.5V. The DTPMOS technique is described below. A technique to mitigate the active mode leakage current is also introduced.

#### 2.5.1 Dynamic Threshold PMOS (DTPMOS) Scheme

The proposed concept relies on the connection between the gate and the well of PMOS transistors to reduce  $V_{TH_p}$  during the on-state and maintain a high  $V_{TH_p}$  during the offstate. For simplicity, the threshold voltage of the DTPMOS transistor will be denoted  $V_{TH}$ . The dynamic nature of the DTPMOS threshold voltage can be explained using the expression

$$V_{TH} = V_{TH_0} - \gamma(\sqrt{|-2\Phi_F|} - \sqrt{|-2\Phi_F + V_{BS}|})$$

(2.6)

Here  $V_{TH_0}$  is the threshold voltage at zero body bias,  $\gamma$  is the body effect coefficient,  $2\Phi_F$  is the surface potential at strong inversion, and  $V_{BS}$  is the body-source voltage. The minus sign of the body effect coefficient in (2.6) is due to the forward biased body-source junction [18]. During the on-state and assuming that  $V_{DD}$  is 0.5 V,  $V_{BS}$  for conventional CMOS is zero while it is -0.5 V for DTPMOS. Assuming that  $V_{TH_0}$  is -0.435 V,  $\gamma$  is 0.5667 and  $2\Phi_F$  is 0.6 V,  $V_{TH}$  is reduced to -0.28 V (36% reduction) compared to its value at zero body bias. During the off-state, however,  $V_{BS}$  is set back to zero and  $V_{TH}$  returns to its original value at zero body bias,  $V_{TH_0}$ . The low threshold voltage in the on-state leads to a significant reduction in delay at a low voltage supply.

Compared to conventional CMOS, DTPMOS results in a higher PMOS current drive and consequently a higher operating speed at a very low voltage. This is mainly due to a larger inversion charge and a lower effective normal field in the channel. The lower effective normal field leads to higher mobility and consequently higher current drive [18]. The main features of the DTPMOS scheme are discussed below by applying the scheme to the different building blocks of a parallel multiplier. Performance, standby power, and energy comparisons of DTPMOS and conventional CMOS are also discussed.

# 2.5.2 DTPMOS Implementation of Parallel Multiplication Building Blocks

The parallel multiplier is one of the most analyzed structures in digital VLSIs. Several multiplier architectures and implementations have been proposed for low power applications [38, 39, 40, 41]. In general, the parallel multiplier architecture can be divided into three blocks: the partial product (PP) generator, the summation network, and the final adder. Modified Booth algorithm (MBA) is used for PP generation. MBA is implemented using Booth encoders and Booth selectors. Full adders (FAs) are used to implement a carry save addition tree in the summation network. Finally, a carry skip adder is used to produce the final product. The multiplier circuit is designed using minimum size transistors in most of the instances to minimize the power consumed. Non-minimum size transistors are used where the load and/or the fanout is high. Furthermore, the pass-transistor logic has been extensively used to further achieve lower power operation.

In order to explore the characteristics of operation of the DTPMOS scheme, a passtransistor full adder (FA) circuit is implemented in both DTPMOS and conventional CMOS. Figure 2.8 shows the DTPMOS implementation of the FA circuit.

HSPICE simulations for the FA circuit for both the DTPMOS and conventional CMOS schemes are carried out in the 0.18  $\mu$ m CMOS technology. The input frequency is 10 MHz. This speed is adequate for certain applications specially hearing aids where energy is a very critical design constraint and the typical operating speed is 1-2 MHz [42][43]. Another area of application is sensor networks where battery life is expected to last for years [44] [45]. The simulation setup is to connect all the outputs of the FA circuit (*simulated* circuit) to inputs of a similar FA circuit (load circuit). The outputs of the load circuit are connected to 10 fF loads.

A comparison between the DTPMOS FA and the conventional CMOS FA is illustrated

Figure 2.8: DTPMOS Full Adder circuit.

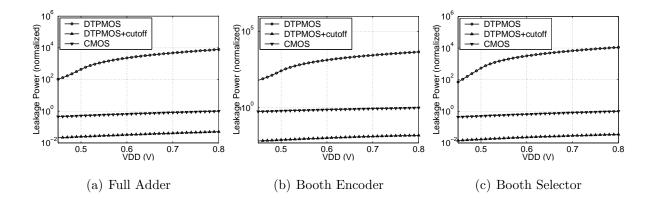

in Figure 2.9. Figure 2.9 (a) shows that using DTPMOS is beneficial below the 0.5V supply voltage. Delay of DTPMOS is 60% less than that of conventional CMOS at a supply voltage of 0.48 V. The DTPMOS delay advantage decreases as supply voltage goes higher than 0.6 V. This is a result of a significant increase in the active leakage current due to the forward biased source and drain junctions. As supply voltage exceeds the built-in junction potential, the excessive current flowing through the forward biased junctions has a small positive impact on delay while causing a large dissipation of power. Consequently an increase in power and power-delay product (PDP) is expected. This trend is shown in Figure 2.9 (b) and (c). Power dissipation of DTPMOS is almost double that of the conventional CMOS at 0.7 V. With a small delay enhancement of the DTPMOS scheme a 0.7 V, PDP of conventional CMOS is approximately half that of DTPMOS. This trend

is reversed when supply voltage is lowered to sub-0.5 V. At 0.48 V, the small difference in power dissipation of both schemes in addition to a large delay reduction of DTPMOS leads to reducing PDP of DTPMOS to approximately half that of the conventional CMOS implementation. Therefore, the DTPMOS scheme is attractive for sub-0.5 V operation.

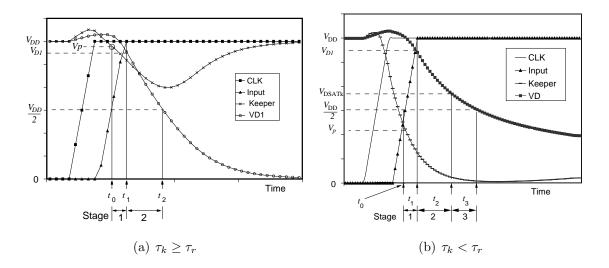

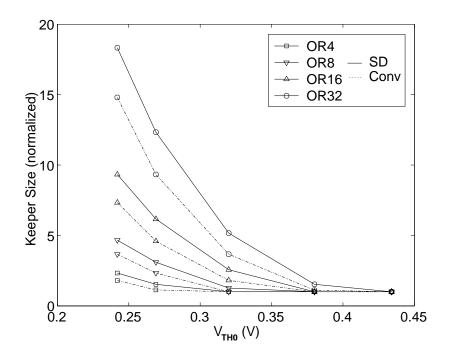

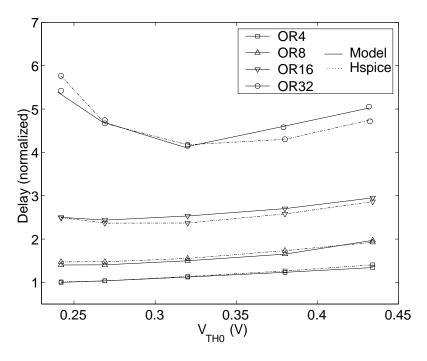

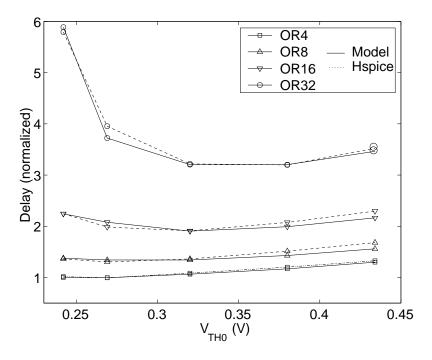

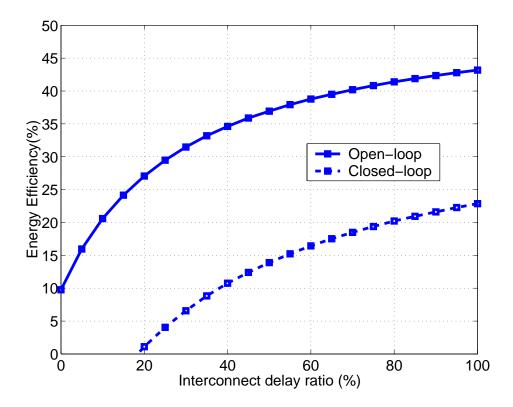

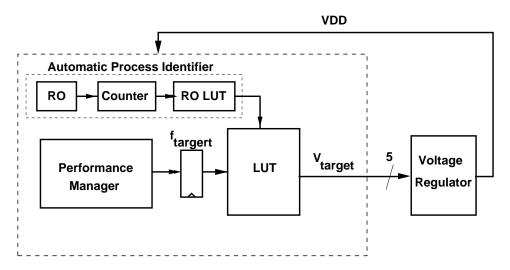

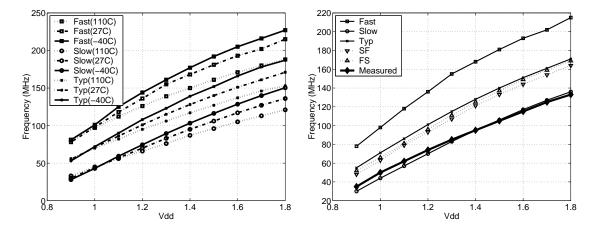

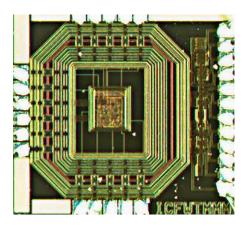

Figure 2.9: Simulation results for the DTPMOS and Conventional CMOS implementations of the FA circuit at different supply voltages.