## Leakage Power Modeling and Reduction Techniques for Field Programmable Gate Arrays

by

#### Akhilesh Kumar

A thesis presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2006 © Akhilesh Kumar, 2006

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF THESIS

I hereby declare that I am the sole author of this thesis. This is a true copy the thesis including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

FPGAs have become quite popular for implementing digital circuits and systems because of reduced costs and fast design cycles. This has led to increased complexity of FPGAs, and with technology scaling, many new challenges have come up for the FPGA industry, leakage power being one of the key challenges. The current generation FPGAs are being implemented in 90nm technology, therefore, managing leakage power in deepsubmicron FPGAs has become critical for the FPGA industry to remain competitive in the semiconductor market and to enter the mobile applications domain.

In this work an analytical state dependent leakage power model for FPGAs is developed, followed by dual-Vt based designs of the FPGA architecture for reducing leakage power.

The leakage power model computes subthreshold and gate leakage in FPGAs, since these are the two dominant components of total leakage power in the scaled nanometer technologies. The leakage power model takes into account the dependency of gate and subthreshold leakage on the state of the circuit inputs. The leakage power model has two main components, one which computes the probability of a state for a particular FPGA circuit element, and the other which computes the leakage of the FPGA circuit element for a given input using analytical equations. This FPGA power model is particularly important for rapidly analyzing various FPGA architectures across different technology nodes.

Dual-Vt based designs of the FPGA architecture are proposed, developed, and evaluated, for reducing the leakage power using a CAD framework. The logic and the routing resources of the FPGA are considered for dual-Vt assignment . The number of the logic elements that can be assigned high-Vt in the *ideal* case by using a dual-Vt assignment algorithm in the CAD framework is estimated. Based upon this estimate two kinds of architectures are developed and evaluated, homogeneous and heterogeneous architectures. Results indicate that leakage power savings of up to 50% can be obtained from these architectures. The analytical state dependent leakage power model developed has been used for estimating the leakage power savings from the dual-Vt FPGA architectures. The CAD framework that has been developed can also be used for developing and evaluating different dual-Vt FPGA architectures, other than the ones proposed in this work.

### Acknowledgments

I would like to acknowledge the invaluable guidance and encouragement received from my research advisor Professor Mohab Anis for the work done in this thesis. I would also like to thank my group members for their suggestions and help.

I am greatly thankful to the readers of my thesis, Professor Mark Aagaard and Professor Shawki Areibi.

Thanks are also due to the technical and administrative staff of the Department of Electrical and Computer Engineering, University of Waterloo.

To my mother, father, sisters, cousins, uncles and aunts.

# Contents

| 1 | Introduction                                        |                                                         | 1  |

|---|-----------------------------------------------------|---------------------------------------------------------|----|

|   | 1.1                                                 | Field Programmable Gate Arrays: Leakage Power Challenge | 1  |

|   | 1.2                                                 | Contributions of this Work                              | 2  |

|   | 1.3                                                 | Organization of the Thesis                              | 3  |

| 2 | Ove                                                 | rview of FPGA Architecture and CAD Tools                | 4  |

|   | 2.1                                                 | FPGA Architecture                                       | 4  |

|   |                                                     | 2.1.1 Logic Block                                       | 4  |

|   |                                                     | 2.1.2 Routing Resources                                 | 8  |

|   |                                                     | 2.1.3 I/O Blocks                                        | 8  |

|   | 2.2                                                 | CAD Tools                                               | 8  |

|   |                                                     | 2.2.1 Synthesis                                         | 8  |

|   |                                                     | 2.2.2 Placement                                         | 11 |

|   |                                                     | 2.2.3 Routing                                           | 12 |

|   | 2.3                                                 | VPR and T-VPack                                         | 13 |

|   | 2.4                                                 | Summary                                                 | 14 |

| 3 | Leakage Power in FPGAs: Background and Related Work |                                                         |    |

|   | 3.1                                                 | Introduction                                            | 16 |

|   | 3.2                                                 | Leakage Power                                           | 17 |

|   |                                                     | 3.2.1 Technology Scaling and Leakage Power              | 17 |

|   |     | 3.2.2 Leakage Power in FPGAs                          | 20 |

|---|-----|-------------------------------------------------------|----|

|   |     | 3.2.3 Estimating Power Savings                        | 21 |

|   | 3.3 | Leakage Power Modeling for FPGAs                      | 21 |

|   | 3.4 | Leakage Power Reduction in FPGAs                      | 23 |

|   | 3.5 | Summary                                               | 27 |

| 4 | Ana | lytical State Dependent Leakage Power Model for FPGAs | 29 |

|   | 4.1 | Introduction                                          | 29 |

|   | 4.2 | Analytical Models for Leakage Currents                | 29 |

|   | 4.3 | Leakage in FPGA Circuit Elements                      | 32 |

|   | 4.4 | Leakage Power Model                                   | 38 |

|   | 4.5 | Results and Discussion                                | 40 |

|   | 4.6 | Summary                                               | 44 |

| 5 | Dua | I-Vt FPGA Design for Leakage Reduction                | 45 |

|   | 5.1 | Introduction                                          | 45 |

|   | 5.2 | Technology Used                                       | 45 |

|   | 5.3 | Proposed Dual Threshold FPGA Architecture             | 46 |

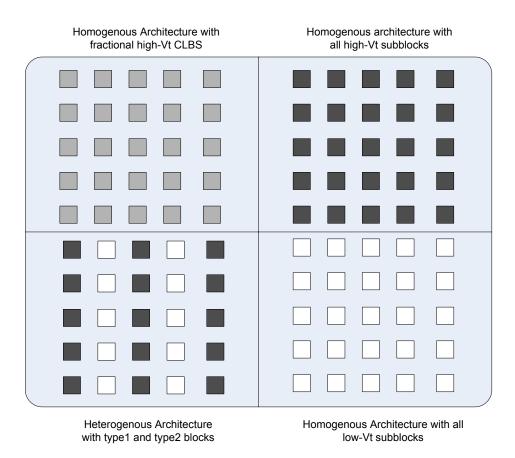

|   |     | 5.3.1 Homogeneous dual-Vt FPGA architecture           | 46 |

|   |     | 5.3.2 Heterogeneous dual-Vt FPGA architecture         | 47 |

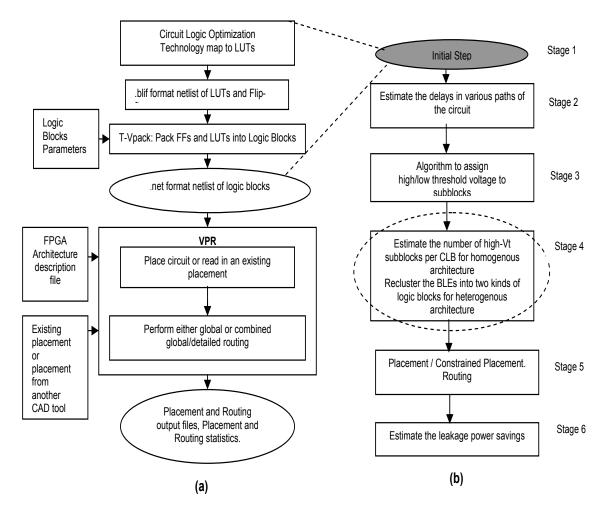

|   |     | 5.3.3 Proposed Dual-Vt FPGA CAD Framework             | 49 |

|   | 5.4 | CAD framework implementation                          | 49 |

|   |     | 5.4.1 Stage 1                                         | 49 |

|   |     | 5.4.2 Stage 2                                         | 51 |

|   |     | 5.4.3 Stage 3                                         | 51 |

|   |     | 5.4.4 Stage 4                                         | 52 |

|   |     | 5.4.5 Stage 5                                         | 55 |

|   |     | 5.4.6 Stage 6                                         | 56 |

|   | 5.5 | Evaluation, Results and Discussions                   | 56 |

| A | List                        | of publ | lications from this work                                                                            | 76 |  |

|---|-----------------------------|---------|-----------------------------------------------------------------------------------------------------|----|--|

| 6 | Conclusions and Future Work |         |                                                                                                     |    |  |

|   | 5.7                         | Summ    | ary                                                                                                 | 68 |  |

|   | 5.6                         | Desigr  | ning a Dual-Vt FPGA                                                                                 | 66 |  |

|   |                             | 5.5.4   | Distribution of Leakage Savings                                                                     | 64 |  |

|   |                             | 5.5.3   | Design tradeoffs                                                                                    | 62 |  |

|   |                             | 5.5.2   | Realizing and evaluating different FPGA architectures for leak-<br>age savings and design tradeoffs | 58 |  |

|   |                             | 5.5.1   | Evaluation Methodology                                                                              | 57 |  |

# **List of Figures**

| 2.1 | A basic FPGA                                                                                                        | 5  |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Programmable switches used in SRAM-based FPGAs                                                                      | 5  |

| 2.3 | A 2-input LUT                                                                                                       | 5  |

| 2.4 | Basic Logic Element [9]                                                                                             | 6  |

| 2.5 | Cluster based logic block [9]                                                                                       | 6  |

| 2.6 | Island style routing architecture [9]                                                                               | 7  |

| 2.7 | Basic CAD flow for FPGAs                                                                                            | 9  |

| 2.8 | Synthesis procedure for FPGAs                                                                                       | 10 |

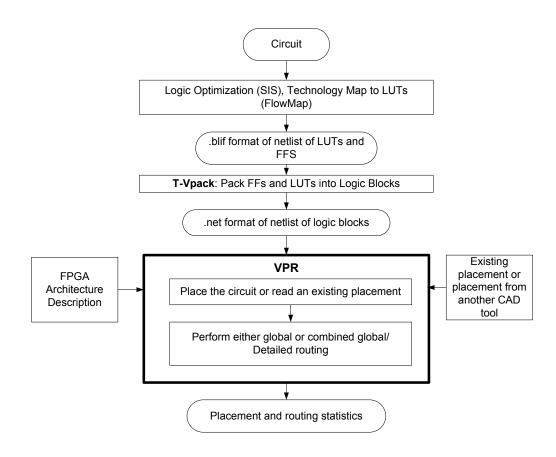

| 2.9 | VPR CAD flow                                                                                                        | 15 |

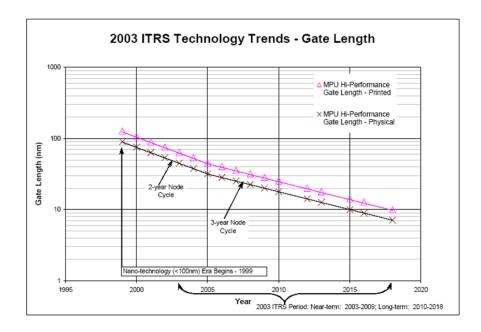

| 3.1 | Technology Scaling                                                                                                  | 18 |

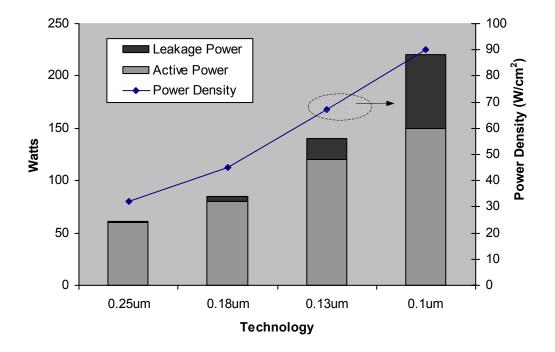

| 3.2 | Leakage power contribution to total power with technology scaling                                                   | 18 |

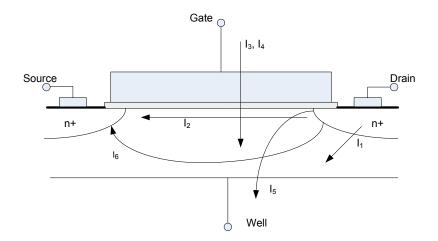

| 3.3 | Leakage currents in a short channel transistor                                                                      | 19 |

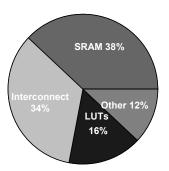

| 3.4 | Leakage breakdown among different FPGA elements [4]                                                                 | 20 |

| 3.5 | Power model framework developed in [11]                                                                             | 22 |

| 3.6 | Dual-Vt design implementation                                                                                       | 25 |

| 4.1 | Dependence of $V_{th}$ on the width of NMOS for CMOS 130nm                                                          | 32 |

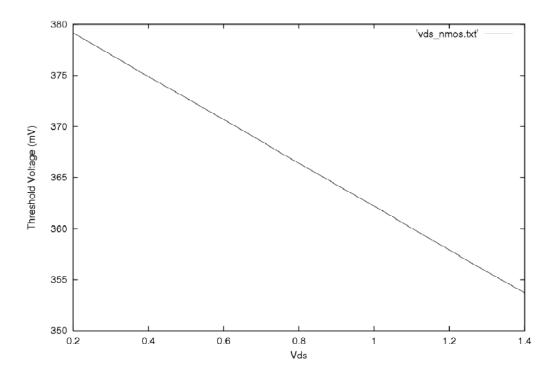

| 4.2 | Dependence of $V_{th}$ on drain to source voltage for NMOS in CMOS 130nm                                            | 33 |

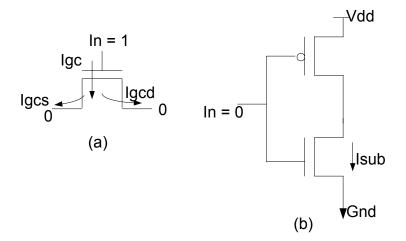

| 4.3 | (a) Gate leakage in NMOS (b) Subthreshold leakage in Inverter                                                       | 34 |

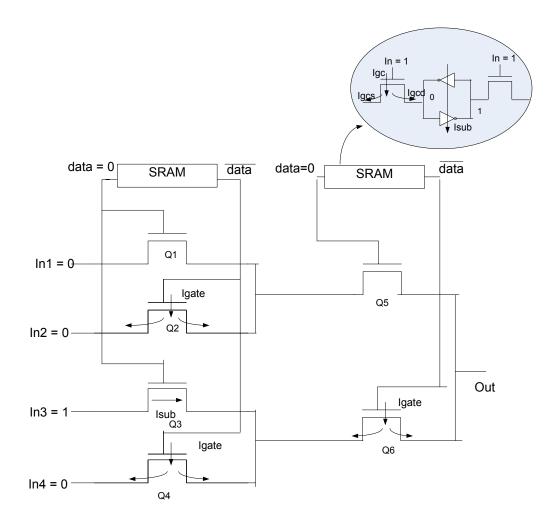

| 4.4 | Multiplexer structure and the corresponding state dependent leakage for a particular select signal and input vector | 35 |

| 4.5  | Leakage in multiplexers is affected by the voltage drop during signal propagation                                                                                                                    | 36 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6  | (a) Buffered routing switch. Subthreshold and gate leakage currents under certain input conditions. (b) Pass transistor routing switch. Only gate leakage is present when the switch is turned on    | 37 |

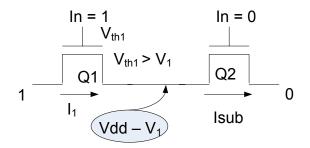

| 4.7  | (a) Static current without gate boosting. (b) Reduced static current with gate boosting                                                                                                              | 38 |

| 4.8  | Overall architecture of the leakage power model                                                                                                                                                      | 39 |

| 4.9  | Average Leakage distribution for different parts the FPGA for CMOS 130nm and 90nm                                                                                                                    | 42 |

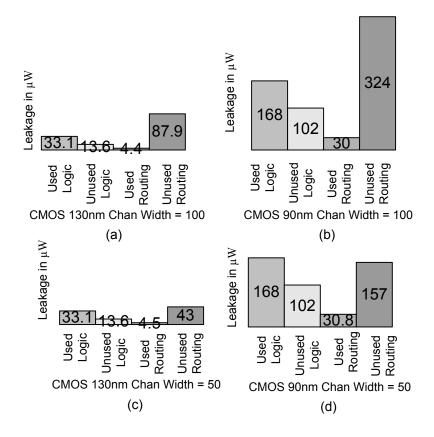

| 4.10 | (a),(b)Used and unused leakage for different components of FPGA for the benchmark alu4 for the FPGA architecture with routing channel width of 100 (c),(d) With routing channel width of 50 $\ldots$ | 43 |

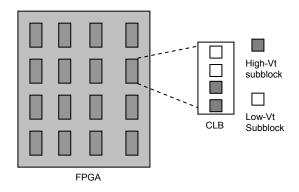

| 5.1  | Proposed homogeneous FPGA architecture. Each CLB has a fixed ratio of high-Vt and low-Vt subblocks.                                                                                                  | 47 |

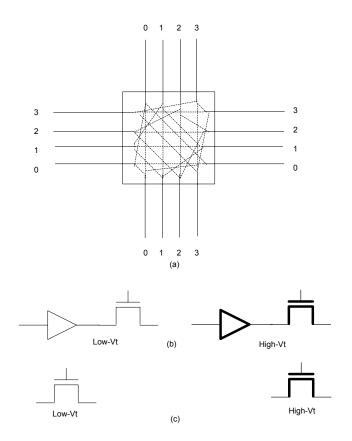

| 5.2  | Switch block. (a) The overall architecture of a switch block (b) Buffered pass transistor switch (c) Pass transistor based switch                                                                    | 48 |

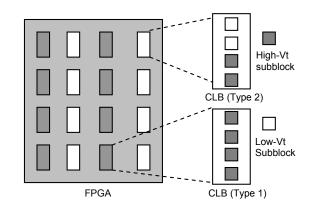

| 5.3  | Proposed heterogeneous FPGA architecture. Two kinds of CLBs; one having all high-Vt subblocks, the other having a fixed ratio of high-Vt and low-Vt subblocks.                                       | 48 |

| 5.4  | (a) Typical FPGA CAD flow within VPR and T-Vpack framework. (b) Proposed generic dual-Vt FPGA CAD flow                                                                                               | 50 |

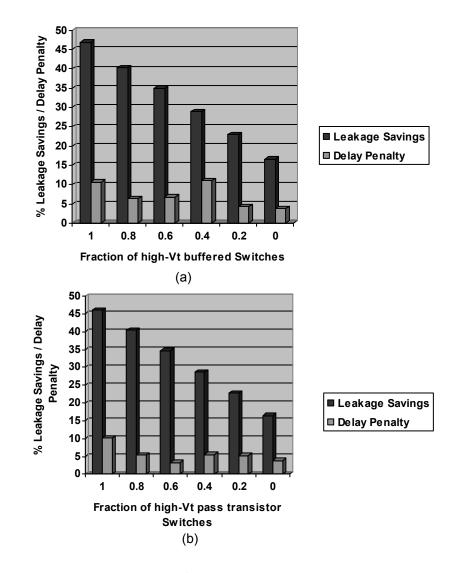

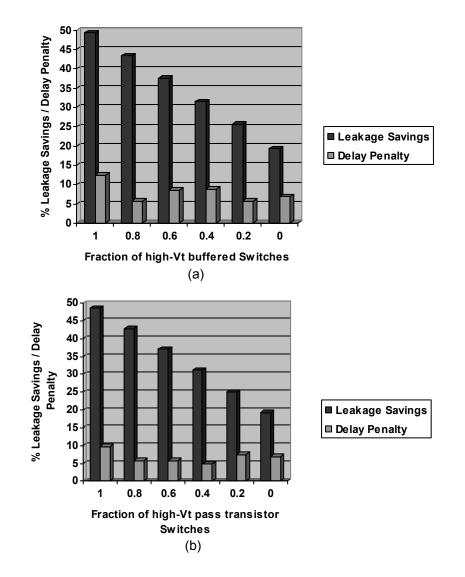

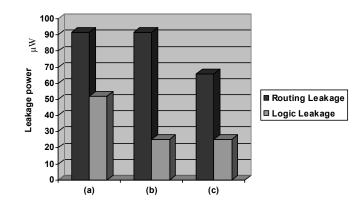

| 5.5  | Leakage savings for <i>arch</i> 2 with 6 high-Vt subblocks per CLB (a) Buffered switches assigned high-Vt (b) Pass transistor switches assigned high-Vt                                              | 61 |

| 5.6  | Leakage savings for <i>arch</i> 4 (a) Buffered switches assigned high-Vt (b)<br>Pass transistor switches assigned high-Vt                                                                            | 63 |

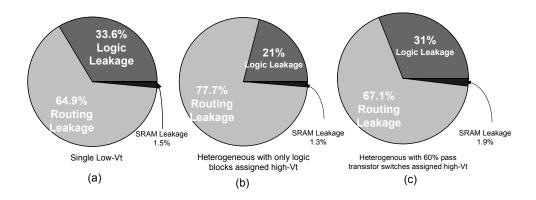

| 5.7  | (a) Leakage contributions of routing resources, logic resources and SRAM cells for single low-Vt implementation, (b) and (c) after dual-Vt implementation for alu4.                                  | 66 |

| 5.8  | Leakage power for alu4. (a) Single low-Vt implementation (b) dual-Vt $arch3$ (c) dual-Vt $arch4$ with 60% high-Vt pass transistor switches                                                           | 67 |

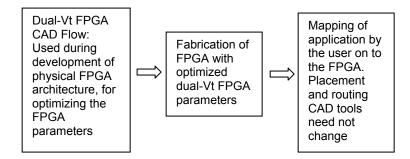

| 5.9  | Realizing a dual-Vt FPGA design                                                                                                                                                                      | 67 |

| 5.10 | A low-leakage Field Programmable SoC                                                                                                                                                                 | 69 |

# **List of Tables**

| 4.1 | Comparison of Power Model with the SPICE simulations for CMOS 130nm                                                                                                                                                                              | 33 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Subthreshold and gate leakage for different benchmarks                                                                                                                                                                                           | 41 |

| 5.1 | Leakage savings with logic blocks assigned dual-Vt for a cluster size of 12 for homogeneous and heterogeneous architectures                                                                                                                      | 59 |

| 5.2 | Design tradeoffs for homogeneous architecture $arch^2$ with 6 high-Vt subblocks and 80% high-Vt pass transistor switches, heterogeneous architecture $arch^4$ with 80% high-Vt pass transistor switches, and all high-Vt subblocks architecture. | 65 |

# Chapter 1

# Introduction

# **1.1 Field Programmable Gate Arrays: Leakage Power Challenge**

Digital systems have grown immensely complex with the scaling of technology. The custom VLSI designs have led the growth of high performance digital systems. However, with increasing complexity of designs, the cost and design cycles of custom VLSI designs have increased significantly. FPGAs offer an efficient and cost effective option for implementing digital systems for medium to low volume production. Earlier, FPGAs were being used only for ASIC prototyping, however with increasing logic density and performance the FPGAs are getting embedded in the end user products. Digital system designers can now get the advantages of low time-to-market of the programmable logic in addition to almost ASIC-like logic density. Commercial FPGAs, such as *Stratix* from Altera, and *Virtex* from Xilinx have on-chip memory blocks and DSP resources, apart from the programmable logic, making it even more attractive for implementing complete systems on chip.

Leakage power has been recently recognized as a major challenge in the FPGA industry. This was primarily because other design challenges, such as performance and area, were given more attention in the past. With technology scaling, leakage power has emerged as a key design challenge. The current generation of FPGAs are being implemented in the 90nm CMOS technology, which necessitates devising techniques for leakage power reduction, because leakage power increases with small geometries. For the FPGAs to continue to retain its semiconductor market and competitive advantages over the high performance custom VLSI designs, the FPGA industry must adopt new techniques for leakage power reduction. The work in [4] showed that a 90nm FPGA consumes too much leakage power to be successfully used in mobile applications. Therefore, for FPGAs to gain popularity in the domains such as wireless personal communication system, or in the biomedical applications, the FPGAs need to implement techniques for reducing leakage power.

The increase in complexity of the current generation FPGAs has resulted in more number of transistors in the FPGAs which directly translate into increased leakage power. The resource utilization of FPGAs is just over 60%, and the unutilized parts also consume leakage power, which means that reducing leakage power is important both in the used and the unused parts of the FPGA. The problem of leakage power in FPGAs is more difficult to handle than in ASICs because of the very nature of programmability of FP-GAs, which means that the final application which would run on the FPGA is unknown. Motivated by the above challenges, this work contributes to leakage power management in FPGAs as outlined in the next section.

#### **1.2** Contributions of this Work

- 1. Analytical Models for Total Leakage Power for FPGAs: In this work analytical models for leakage power calculation for FPGAs have been developed. The leakage power models incorporate BSIM4 models to compute the subthreshold leakage and gate leakage. These leakage power models have been used for computing leakage currents through the various FPGA circuit elements.

- 2. State Dependency for Leakage Power Calculation in FPGAs: The leakage power model takes state dependency of subthreshold and gate leakage during the computation of these leakage currents.

- 3. CAD framework for dual-Vt FPGA designs: A dual-Vt FPGA CAD framework for designing, developing, and evaluating dual-Vt FPGAs has been proposed. VPR and T-Vpack [9], the widely used academic research tools for FPGA, have been used for developing the dual-Vt FPGA CAD framework.

- **4. Dual-Vt FPGA Architectures:** Based on the dual-Vt FPGA CAD framework, dual-Vt FPGA architectures are proposed, developed and evaluated using the dual-Vt FPGA CAD framework. These architectures are intended for reducing leakage power consumption without severe delay penalties.

#### **1.3** Organization of the Thesis

This thesis has been organized as follows.

**Chapter 2** gives an overview of the FPGA architecture. It discusses the logic block structure and the routing resources and outlines a general SRAM based FPGA architecture that has been used in this work. It also gives a brief description of the CAD tools used for implementing digital circuits on FPGAs.

*Chapter 3* discusses the leakage power in FPGAs. It gives an overview of power dissipation in FPGAs and discusses previous work on leakage power reduction in FPGAs.

*Chapter 4* discusses the work on the analytical, state dependent leakage power model for FPGAs. It describes the BSIM4 subthreshold and gate leakage equations and explains the state dependency of the subthreshold and gate leakage in the FPGA circuit elements. It describes the overall framework used for computing the total leakage power in FPGAs, using a Leakage Computation Engine (LCE). Finally results are presented for various MCNC benchmarks.

*Chapter 5* explains the dual-Vt FPGA CAD framework that has been developed, followed by a description of the proposed dual-Vt FPGA architectures. It explains various algorithms modified, developed and used in the CAD framework. The different stages of the CAD framework have been discussed in detail and compared with the traditional CAD framework for implementing a digital circuit on FPGA. It presents the results of leakage power savings and design tradeoffs for various dual-Vt FPGA architectures using the dual-Vt FPGA CAD framework. Guidelines for designing dual-Vt FPGA architectures are also presented.

*Chapter 6* concludes the thesis and outlines the future work for leakage power management in FPGAs.

# Chapter 2

# **Overview of FPGA Architecture and CAD Tools**

#### 2.1 FPGA Architecture

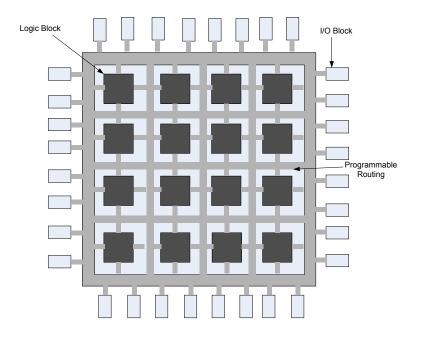

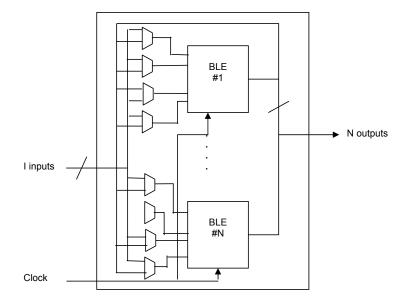

A basic FPGA is shown in Fig. 2.1. The FPGA architecture is very regular in structure. It is made up of two main components - logic blocks (CLBs) and routing resources. The logic blocks implement the functionality of the given circuit while the routing resources provide the connectivity for implementing the logic. The logic blocks have the flexibility to connect to the routing resources surrounding them. The logic blocks and the routing resources are configurable, so that they can be programmed to implement any logic. Though many types of architectures have been experimented with, the most popular one is the SRAM based architecture which is described below and has been used in this work [9].

#### 2.1.1 Logic Block

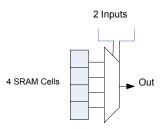

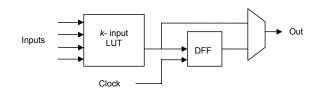

The logic block of the SRAM based FPGA is LUT (look-up-table) based and are composed of basic logic elements (BLE). LUT is an array of SRAM cells to implement a truth table. Fig. 2.3 shows a two input LUT. It has 4 SRAM cells and a multiplexer to select one of the SRAM cells. The selection is done by the two select signals to the multiplexer, which serve as inputs to the truth-table. Each BLE consists of a k-input LUT, flip-flop and a multiplexer for selecting the output either directly from the output of LUT or the registered output value of the LUT stored in the flip-flop. Fig. 2.4 shows the basic logic element. Previous works have shown that the 4-input LUT is the most

Figure 2.1: A basic FPGA

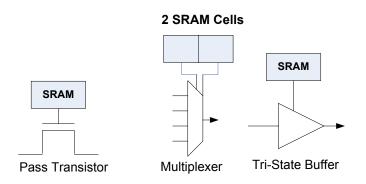

Figure 2.2: Programmable switches used in SRAM-based FPGAs

Figure 2.3: A 2-input LUT

Figure 2.4: Basic Logic Element [9]

Figure 2.5: Cluster based logic block [9]

optimum size as far as logic density, and utilization of resources are concerned, and this has been widely used. Cluster based logic blocks were investigated in [9] and it was shown that the cluster based logic blocks are better in speed and area. The structure of a cluster based logic block is shown in Fig. 2.5. In the cluster based logic block, the logic block is made up of N BLEs. There are I inputs to the logic block such that each input can connect to all the BLEs. Also the output of each BLE can drive one of the inputs of each of the BLEs. The clock feeds all the BLEs. The work in [9] showed that the logic clusters containing 4 to 10 BLEs achieve good performance. Each subblock is made up of a BLE and the corresponding LUT input multiplexers.

Figure 2.6: Island style routing architecture [9]

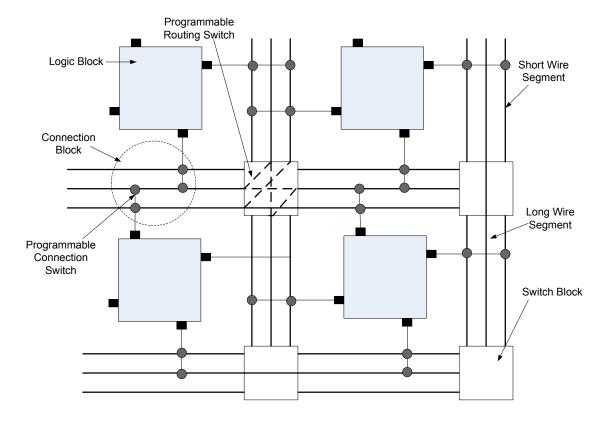

#### 2.1.2 Routing Resources

The routing resources are of various types, but the one used in this work is the islandbased architecture. In the island based architecture, the routing resources form a mesh like structure with the horizontal and vertical routing channels. The horizontal and vertical routing channels are connected by switch boxes which are programmable and thus provide the flexibility in making the connections. The logic blocks are connected to the routing channels through the connection boxes which are also programmable. Fig. 2.6 shows the island style routing architecture [9]. The programmable switches used for implementing the interconnections are shown in Fig. 2.2. These programmable switches have SRAM cells which can be programmed to either turn on or turn off the switch. Apart from the logic blocks and the routing resources, the clock distribution is assumed to have a dedicated network. Most of the commercial FPGAs have a structure similar to the one described above or some variant of the above architecture.

#### 2.1.3 I/O Blocks

The I/O blocks are also programmable so that they can be configured either as input or as output, or can be tri-stated.

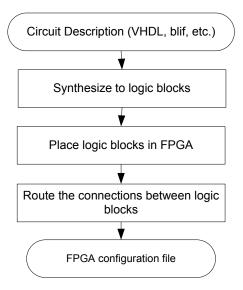

#### 2.2 CAD Tools

To implement a circuit on the current generation FPGAs, CAD tools are needed which can generate the configuration bits for the SRAM cells of the FPGAs. Usually the circuit description is provided using Verilog, VHDL, SystemC, or other higher level descriptions. The CAD tools for the FPGAs read this input and output a configuration file for programming the FPGA. Fig. 2.7 shows the basic CAD flow for implementing a digital circuit/system on FPGAs [9]. The CAD flow has three main tasks: Synthesis, placement and routing. In the following sections synthesis, placement and routing for FPGAs are explained. Since VPR and T-Vpack have been used in this work, the discussion will be kept in context of these CAD tools. Almost all of the commercial FPGA CAD flows perform the same basic functions of synthesis, placement and routing.

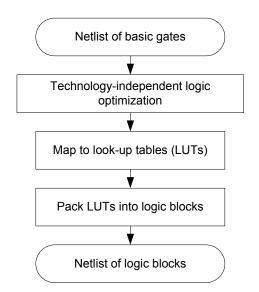

#### 2.2.1 Synthesis

The synthesis of a netlist involves conversion of a circuit description, usually in hardware description language (HDL), into a netlist of basic gates. This netlist of basic gates is

Figure 2.7: Basic CAD flow for FPGAs

then converted into a netlist of FPGA logic blocks. Fig. 2.8 shows the steps involved in the synthesis of a circuit description into a netlist of logic blocks.

Technology independent logic optimization involves the removal of redundant logic and simplification of the logic [27] [28]. The optimized netlist is then mapped to look-up tables, which is a process of identifying the logic gates that would go into a LUT [21]. The final step of the synthesis procedure is the clustering of the LUTs and flip-flops (for sequential logic) into logic blocks. The goal here is usually to minimize the number of logic blocks and/or minimize the delay. The work in [29] used a measure of closeness of LUTs to pack them into a cluster to form a logic block.

The work in [9] uses a timing driven logic block packing tool, called T-VPack. The tool targets packing the BLEs into a cluster shown in Fig. 2.5. It needs the parameters such as number of BLEs per cluster, number of inputs per cluster, size of the LUTs, and number of clocks per cluster. The first stage of the packing procedure simply forms the BLEs by packing a register and a LUT together. Initially the packing procedure packs the BLEs greedily into a cluster, followed by a hill climbing phase if the greedy phase is not able to fill the cluster completely.

To enable a timing driven packing, it is necessary to get an estimate of delays through various paths of the netlist. To enable this computation three types of delays are modeled: delay through a BLE, *LogicDelay*, delay between blocks in the same cluster, *Intr-aClusterConnectionDelay*, and the delay between blocks in different clusters, *InterClusterConnectionDelay*. The values for these are set as 0.1, 0.1 and 1.0 for *LogicDelay*,

Figure 2.8: Synthesis procedure for FPGAs

*IntraClusterConnectionDelay* and *InterClusterConnectionDelay*, respectively. The *InterClusterConnectionDelay* cannot be determined until the circuit has been implemented on the FPGA. However, these values represent the correct trend of values, and the performance of T-Vpack is not very sensitive to the exact values. The criticality of a connection is defined as

$$ConnectionCriticality(i) = 1 - \frac{slack(i)}{MaxSlack}$$

(2.1)

where MaxSlack is the largest slack amongst all the connections in the circuit. A new cluster is created by selecting a seed BLE having the highest criticality amongst the un-clustered BLEs. After the seed BLE has been selected, an attraction function is used to determine the next un-clustered BLE, B, to be added to the current cluster C. The attraction function is given by:

$$Attraction(B) = \alpha.Criticality(B) + (1 - \alpha) \left[ \frac{Nets(B) \cap Nets(C)}{MaxNets} \right]$$

(2.2)

where the first term represents the timing part, and the second term represents the cost of nets shared between the current cluster and the BLE under consideration. Any value of  $\alpha$  between 0.4 and 0.8 gives good results. The computation of *Criticality* of a

BLE is explained in [9] and also the tie-breaker mechanism used for the case when two or more BLEs have the same criticality. Essentially, the tie-breaker mechanism selects that BLE which reduces the length of the largest number of critical paths.

The hill-climbing phase tries to add more BLEs to the cluster in case it is not full. In this phase adding a BLE to a cluster is allowed even if it leads to more inputs required for the cluster than the maximum allowable. This is done because in some cases the BLE being added might have all its inputs from the BLEs in the current cluster and also might drive the inputs of some of the BLEs in the current cluster. In this case the number of inputs required for the cluster decreases by one. However, this hill climbing phase increases the logic utilization only by 1 - 2% in some of the circuits.

#### 2.2.2 Placement

The work in [9] developed the tool VPR for placement and routing. For placement the FPGA is considered as a set of legal discrete positions at which the logic blocks of the synthesized netlist can be placed. For placement, the architecture descriptions needed by VPR are:

- 1. The number of logic block input and output pins.

- 2. The number of I/O pads that fit into one row or column of the FPGA.

- 3. The routing channel width (number of tracks in a routing channel).

The placement technique used in VPR is based on simulated annealing [30], which imitates the annealing process used to gradually cool a molten metal to produce high quality metal objects. The simulated annealing works by first starting with an initial random placement by placing the logic blocks randomly on the available locations in the FPGA. The placement then proceeds by making a large number of moves to improve the placement. This is done by selecting a logic block randomly and its new location also randomly. This would produce a change in the cost function, and if the cost function improves, the move is always accepted. However, if the cost function worsens, there is still some probability of acceptance of the move. The probability of acceptance is given by  $e^{-\Delta C/T}$ , where  $\Delta C$  is the change in the cost function and the goal is to decrease the cost function. The T is the temperature parameter and controls the probability of acceptance of the moves much worsen the placement. The temperature is initially set to a high value so that at the beginning of the annealing, virtually all the moves are accepted. The temperature is gradually decreased as the placement improves, such that finally the probability of accepting a bad move is almost negligible. The flexibility of accepting bad moves allows the simulated annealing schedule to overcome the local minima in the cost function.

The VPR sets the initial temperature in the same way as in [31]. The number of moves attempted at each temperature is done as in [32]. It is set to

$$MovesPerTemperature = InnerNum.(N_{blocks})^{4/3}$$

(2.3)

where the default value of InnerNum is 10, and  $N_{blocks}$  is the number of logic blocks in the netlist. The fraction of moves accepted is kept close to 0.44 for as long as possible, as it yields better results [32]. However, VPR uses a new method of updating the temperature. The VPR computes the new temperature as  $T_{new} = \gamma . T_{old}$ , where the value of  $\gamma$  depends on the fraction of moves accepted at  $T_{old}$ . The idea is to spend maximum time near the temperatures at which large improvements in placement occur. The annealing procedure is not very sensitive to the exact value of  $\gamma$ , if it has the right form,  $\gamma$  is close to 1 if the fraction of moves accepted is close to 0.44, whereas  $\gamma$  is small if the fraction of moves accepted is near 1 or 0. VPR has a timing driven placement and uses a cost function to optimize both the timing and the delay. The complete timing driven placement algorithm is explained in detail in [33]. The cost function for the timing driven placement developed in [33] is given by

$$\Delta C = \lambda \cdot \frac{\Delta TimingCost}{PreviousTimingCost} + (1 - \lambda) \cdot \frac{\Delta WiringCost}{PreviousWiringCost}$$

(2.4)

where  $\triangle TimingCost$  and  $\triangle WiringCost$  represent the change in the timing cost and the change in the wiring cost, respectively, due to a move. The simulated annealing procedure is terminated when

$$T < \epsilon. \frac{Cost}{N_{nets}} \tag{2.5}$$

where  $N_{nets}$  is the total number of nets in the circuit and the value of  $\epsilon$  is set as 0.005.

#### 2.2.3 Routing

The routing of the placed netlist, essentially, determines the switches that need to be turned on in the routing resources of the FPGA. The routing algorithm in VPR is based on the Pathfinder algorithm proposed in [34]. The Pathfinder repeatedly rips-up and re-routes every net in the circuit until all congestion is resolved. One routing iteration involves ripping-up and re-routing every net in the circuit. The first routing iteration routes for minimum delay, even if it leads to congestion, or overuse of routing resources.

To remove this overuse another routing iteration is performed. The cost of overusing a routing resource is increased after every iteration. This improves the chance of resolving the congestion. At the end of each routing iteration all the nets are completely routed, although with some congestion. Based on this routing, timing analysis can be done to compute the critical path and also the slack of each source sink connection. The timing driven router uses an Elmore delay model to compute the delays of all the connections. The criticality of a connection beteen source of net i and one of its sink j is computed as follows:

$$Crit(i,j) = max\left(\left[MaxCrit - \frac{slack(i,j)}{D_{max}}\right]^{\eta}, 0\right)$$

(2.6)

where slack(i, j) is the the slack available to the connection and  $D_{max}$  is the delay of the critical path. MaxCrit and  $\eta$  are the parameters which determine how the slack impacts the congestion delay tradeoff in the cost function. In VPR  $\eta$  is set to 1 and MaxCrit is set to 0.99.

The VPR creates a routing resource graph to describe the FPGA architecture and connectivity information. The wire and the logic block pins of the FPGA are represented as nodes in the routing resource graph, and the switches are represented as directed edges in the graph. This routing resource graph is used to perform the routing.

The routing of a net is done by starting with a single node in the routing resource graph, corresponding to the source of the net. A wave expansion algorithm is invoked (k-1) times to connect the source to each of the net's (k-1) sinks, in order of the criticality of the sinks, the most critical sink being the first. The cost for using a node n during this expansion is given by:

$$Cost(n) = Crit(i, j).delay(n, topology) + [1 - Crit(i, j)].b(n).h(n).p(n)$$

(2.7)

where b(n), h(n) and p(n) are the base cost, historical congestion, and present congestion as explained in [9]. This procedure is repeated for each of the nets to get the complete routing.

#### **2.3 VPR and T-VPack**

This section describes the FPGA CAD tools used in this work. The CAD tools used in this work are VPR, for placement and routing, and T-VPack for clustering of the BLEs [9]. VPR is invoked on the command line as follows [40]

vpr netlist.net architecture.arch placement.p routing.r [-options] (2.8)

where *netlist.net* is the circuit description providing the information about the connectivity of the logic blocks, *architecture.arch* is the architecture file which describes the architectural parameters of the FPGA. The output of the final placement is written in *placement.p*, or, if the circuit is only being routed, the placement information is read from the file *placement.p*. The final routing information is written in *routing.p*. VPR has two basic modes of operation. In the first mode, VPR places a circuit on the FPGA and routes it for minimum routing channel width. In the other mode, when the user specifies the routing channel width, VPR attempts to route the circuit only once and if it is un-routable it simply aborts, reporting that the circuit is un-routable. The VPR also provides graphics which shows the actual placement and routing of the logic blocks, along with the routing switches.

T-VPack reads a netlist in the *blif* (Berkeley Logic Interchange Format) format having look-up tables (LUTs) and flip-flops (FFs) and packs these into logic blocks. The output of the T-Vpack is in the *.net* format, which is a netlist of logic blocks. T-VPack is invoked on the command line by

$$t - vpack input.blif output.net [-options]$$

(2.9)

where options are used to specify the size of the LUTs, cluster size, inputs per cluster and various optimization options.

The complete VPR CAD flow is shown in Fig. 2.9. SIS [20] is used for logic optimization of the circuit. FlowMap [21] is used for technology-mapping to 4-LUTs and flip-flops. FlowMap produces an output in the *.blif* format. T-VPack packs the netlist into logic blocks and produces an output in the *.net* format. VPR is then used for the placement and routing of the netlist. Other logic optimizers and technology mappers, instead of SIS and FlowMap can also be used in this CAD flow.

#### 2.4 Summary

This chapter discussed the island based FPGA architecture used in this work. The logic blocks, programmable switches and routing resources were described. An overview of the CAD tool based on VPR was given. This CAD tool is used for implementing a circuit on the FPGA. Synthesis, placement and routing techniques were discussed.

The next chapter discusses the leakage power mechanisms and the related work in leakage power modeling and reduction techniques for FPGAs.

Figure 2.9: VPR CAD flow

## Chapter 3

# Leakage Power in FPGAs: Background and Related Work

#### 3.1 Introduction

There are two sources of power dissipation in a CMOS circuit: dynamic power and static power. The dynamic power dissipation has three components: Switching power, short circuit power and glitching power. The switching power is due to the charging and discharging of the node capacitances in the circuit. The average switching power dissipation is given by

$$P_{dyn} = \frac{1}{2} \cdot V_{dd}^2 \cdot \sum_i C_i \cdot A_i$$

(3.1)

where  $V_{dd}$  is the supply voltage,  $A_i$  is the activity of the node *i*,  $C_i$  is the capacitance of the node *i*. The short circuit power is due to the transient current between  $V_{dd}$  and ground during logic transition. It is around 10% of the switching power. The glitching power is due to spurious transitions during the logic evaluation in the circuit and is caused primarily because of unbalanced path delays.

The static power dissipation in a CMOS circuit is due to leakage current. The static power dissipation is given by

$$P_{leak} = V_{dd}.I_{leak} \tag{3.2}$$

where  $I_{leak}$  is the leakage current in the circuit. The leakage power is discussed in detail in the next section.

Dynamic power management in FPGAs was given more importance earlier, because the dominant component of total power was dynamic power. The work in [8] evaluated different architectural parameters for designing a power efficient FPGA for reducing both the dynamic and leakage power. The work in [38] used a clustering technique for reducing the dynamic power. The work in [36] reduced dynamic power by optimizing the interconnect architecture and circuit design, and by reducing the voltage swing for the interconnects. The work in [37], used a dual-voltage scheme for operating pass transistor networks at low voltage for reducing the dynamic power. The work in [39] used a programmable dual-Vdd technique for reducing the dynamic and leakage power. The work in [43] develops a power-aware technology mapping for LUT based FPGAs to keep the high switching activity nets out of the FPGA routing network, because the routing network has a high capacitance and leads to increased switching power. The work in [42] reduces switching power by optimizing the technology-mapping, clustering, placement and routing stages of the VPR CAD flow, by taking into account the activity of the nets in each stage of the CAD flow.

#### 3.2 Leakage Power

In this section, leakage mechanisms and the impact of technology scaling on leakage power is discussed. The leakage power of a state of the art 90nm FPGA is also discussed.

#### 3.2.1 Technology Scaling and Leakage Power

Rapid scaling of technology was targeted to increase the performance and logic density. Fig. 3.1 shows the technology scaling trend projected by ITRS [46]. There has been an improvement of more than 30% in the delays of the transistors per technology generation. With this, the supply voltage has been scaling and also the threshold voltage ( $V_{th}$ ) of the transistor, so that sufficient gate overdrive is maintained. This has resulted in significant increase in subthreshold leakage as shown by the following equation

$$I_{sub} = I_0 \left[ 1 - exp \left[ \frac{-V_{ds}}{V_T} \right] \right] . exp \left[ \frac{V_{gs} - V_{th} - V_{off}}{nV_T} \right]$$

(3.3)

where  $V_T$  is the thermal voltage,  $V_{off}$  is the offset voltage which determines the channel current at  $V_{gs} = 0$ , *n* is the subthreshold swing coefficient,  $W, L, \mu, q, \phi_s, \epsilon_{si}$ , are the width, length, mobility of charge carriers, electron charge, surface potential and permittivity of silicon, respectively, for the transistor. It can be seen that the subthreshold leakage is exponentially dependent on the threshold voltage,  $V_{th}$ , of the transistor.

Fig. 3.2 shows the active and leakage power trends for the Intel's process technologies [41]. The leakage power for the  $0.25\mu$ m technology is 0.1% of the total power,

Figure 3.1: Technology Scaling

Figure 3.2: Leakage power contribution to total power with technology scaling

Figure 3.3: Leakage currents in a short channel transistor

whereas for the  $0.1\mu$ m technology, it is almost 25% of the total power. It is projected that for 65nm technology, the leakage power would be as high as 50% of the total power. Therefore leakage power management is very important in scaled technologies.

The shrinking geometries has led to other sources of leakage current. Fig. 3.3 shows the leakage currents through a short channel transistor [13].

$I_1$  is the reverse-bias pn junction leakage current. This current is caused because of the minority carrier diffusion/drift near the edge of the depletion region, and due to electron-hole pair generation in the depletion region of the reverse biased junction [13]. In case the n and p regions are heavily doped then band-to-band tunneling (BTBT) starts to dominate the leakage current in the pn junction. The BTBT leakage current flows under high electric field conditions, when the electrons from the valence band of p tunnel into the conduction band of n.

$I_2$  is the subthreshold leakage current. This current occurs between the source and drain of the transistor due to weak inversion in the subthreshold region, when the gate voltage is below the threshold voltage  $V_{th}$  [13].

$I_3$  is the gate tunneling current through the gate oxide of the transistor. With the reduction of gate oxide thickness the electric field across the gate oxide increases. These lead to tunneling of electrons from the substrate to gate and from gate to substrate resulting in the gate oxide tunneling current [13].

$I_4$  is the current due to injection of hot carriers from substrate to gate oxide. The short-channel transistors have high electric field near the silicon and gate oxide interface. This results in holes and electrons gaining sufficient energy to cross interface barrier to enter the oxide layer, resulting in hot-carrier injection [13].

Figure 3.4: Leakage breakdown among different FPGA elements [4]

$I_5$  is the gate induced drain leakage current (GIDL). This phenomenon occurs because of high electric field effect in the drain junction of the transistor [13].

$I_6$  is the punch-through current. This occurs in short channel devices because the source-substrate and drain-substrate depletion regions tend to come closer. When these depletion regions merge, punch-through occurs [13].

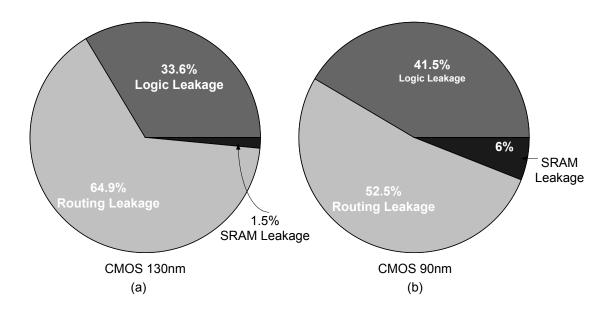

#### 3.2.2 Leakage Power in FPGAs

The work in [4] analyzed leakage power in a state of the art 90nm FPGA using SPICE simulations with BSIM4 models. The leakage power was reported to be  $4.2\mu$ W per CLB at 25 °C. With a GSM cell phone's standby current budget of  $300\mu$ A, the upper bound on leakage power would imply only 86 CLBs [4], which is too small for any significant processing. Hence leakage power is a very big obstacle for FPGAs to enter into mobile applications domain. The leakage power breakdown among different elements of the FPGA reported in [4] is shown in Fig. 3.4. It shows that leakage power from the configuration SRAM cells and the routing interconnects form a major part of the total leakage. Further, it shows that leakage from the unused parts of the FPGA can be as high as 56% for a small design using 50% of the available CLBs, whereas for a design which uses all the CLBs, the unused leakage is 35%, still a significant portion of total leakage. Therefore reducing leakage power in the unused parts of FPGAs is also very important.

#### **3.2.3** Estimating Power Savings

The total power consumption can be divided into 2 parts, active power and standby power. The total average power can be written as

$$P_{avg} = \frac{t_{act} \times P_{act} + t_{off} \times P_{off}}{t_{act} + t_{off}}$$

(3.4)

$$T = t_{act} + t_{off} \tag{3.5}$$

where  $P_{avg}$ ,  $P_{act}$ , and  $P_{off}$  are the average, active and standby (off) power. For personal wireless communication systems, typically the standby time or off time  $(t_{off})$  is 90% of the total time (T) and active time  $(t_{act})$  is 10% of the total time. During the active time the components of power dissipation can be written as

$$P_{act} = [P_{dyn} + P_{sckt} + P_{actleak}]_{used} + [P_{actleak}]_{unused}$$

(3.6)

where  $P_{dyn}$ ,  $P_{sckt}$ , and  $P_{actleak}$  are the dynamic, short circuit and active leakage power consumptions respectively.  $P_{off}$  is the standby leakage power consumption of the FPGA, because during the standby mode, only leakage power is dissipated. Hence, reducing leakage power during the standby mode for mobile applications would increase the battery life significantly.

#### **3.3 Leakage Power Modeling for FPGAs**

Analytical equations for leakage computation have been studied and developed in detail, which can model the complex behavior of various components of leakage current in a MOS transistor. These models are based on physical and empirical parameters [25]. Typically, the leakage power consumption of any circuit is not only dependent on the physical parameters of the circuit, but is also heavily dependent on the inputs to the circuit. The work in [5] showed that the leakage current can vary by an order of magnitude depending on the input to the circuit and demonstrated that certain input vectors are the dominant leakage states for a logic gate.

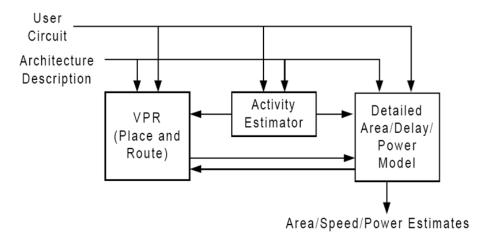

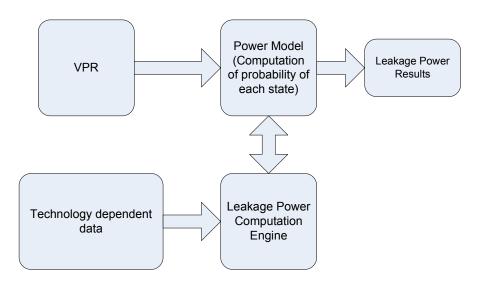

There have been very few works targeted at modeling leakage power for the FPGAs. The work in [11] modeled the dynamic and the leakage power in FPGAs. The power model was integrated into the VPR framework. The power model framework is shown in Fig. 3.5. It developed an activity estimation tool, using a transition density model to estimate the activities of the internal nodes of the FPGA for dynamic power computation.

Figure 3.5: Power model framework developed in [11]

It used the concept of boolean difference to propagate the signal probabilities which is given by the following equation for a given boolean function f(x).

$$\frac{df(x)}{dx_i} = f(x_i) \oplus f(\overline{x_i})$$

(3.7)

The probability of boolean difference,  $P(\frac{df(x)}{dx_i})$  represents the static probability that a change in  $x_i$  would produce a change at the output. With an input transition density (number of transitions per second) of  $D(x_i)$ , the total transition density at the output is given by [11]:

$$D(y) = \sum_{i} \frac{df(x)}{dx_i} D(x_i)$$

(3.8)

The primary inputs were considered to be uncorrelated having a static probability of 0.5 and transition density of 0.5. The dynamic power is then given by

$$P_{dyn} = \sum_{all \ nodes} \frac{1}{2} \cdot V_{dd}^{2} \cdot C_{y} \cdot D(y) \cdot f_{clk}$$

(3.9)

where  $C_y$ , and  $f_{clk}$  are the capacitance of the node y, and clock frequency, respectively. The short circuit power was assumed to be 10% of the dynamic power. This work modeled only subthreshold leakage. The subthreshold leakage was modeled using the following equation for a transistor,

$$I_{sub} = I_{on}.exp\left[\frac{(V_{gs} - V_{on}).q}{n.k.T}\right]$$

(3.10)

where  $V_{on} = V_{th} + n.K.T/q$ , *n* is the subthreshold swing coefficient, *k* is the Boltzman's constant, *q* is the electron charge and  $V_{gs}$  is the gate to source voltage of the transistor,  $I_{on}$  is the drain current when  $V_{gs} = V_{on}$ . For the inactive transistors,  $V_{gs}$  was considered as half of the threshold voltage.

However, this work has some major drawbacks in leakage power modeling. This work considered only subthreshold leakage and did not consider the dependency of subthreshold leakage on the state of the circuit, rather it calculated an average leakage considering that all the transistors were leaking and the  $V_{gs}$  was considered as half of  $V_{th}$ for leakage computation, which is not accurate. The short channel effects have not been taken into account in this work. These produce inaccurate estimation of leakage current. Further, for scaled technologies it is important to model the gate leakage.

The work in [8] and [4] calculated total power using look-up table based approach based on SPICE simulations to characterize the power of the FPGA circuit elements. The look-up table stores the leakage power of the circuit elements for different inputs or an average leakage for each circuit element. The total leakage is computed by adding the leakage of all the circuit elements. However, this methodology is not accurate as the leakage power is strongly dependent on the state of the inputs and considering an average leakage for the circuit elements of the FPGA leads to inaccurate leakage estimation.

Motivated by the above mentioned limitations of the previous works, this work develops an analytical model for leakage power calculation for FPGAs, that takes into account the dependency of the leakage power on the state of the circuit. The contribution of this work on leakage power modeling for FPGAs can be summarized as:

- 1. Developing analytical models and methodology to compute subthreshold and gate leakage power for FPGAs, independent of the technology node.

- 2. Computation of state dependent subthreshold and gate leakage.

- 3. Analysis of sources of leakage in FPGAs.

#### **3.4 Leakage Power Reduction in FPGAs**

In this work reduction of subthreshold leakage reduction is targeted, because the gate leakage is still orders of magnitude smaller than subthreshold leakage for current generation technologies. The subthreshold leakage current through a MOSFET can be modeled as shown in equation 4.1. Since the subthreshold leakage current is exponentially dependent on the threshold voltage, increasing the threshold voltage would decrease the leakage current substantially. However, the high threshold voltage devices have larger switching delays.

The various leakage current mechanisms and some leakage reduction techniques for CMOS circuits were discussed in [13][2]. The techniques for reducing leakage power involve static and dynamic approaches. The dynamic approach involves run time decision making for leakage reduction. One such popular technique is the use of sleep transistors in MTCMOS circuits for controlling the leakage power [16]. Several optimizations for MTCMOS circuits involving the use of sleep transistors have been proposed, such as in [14][15]. However, this technique can reduce only standby leakage power and leads to performance degradation. The static technique does not involve run time decision making for leakage control. The dual threshold voltage design technique, which is a static approach, has been widely used in the custom VLSI designs for reducing leakage power. The dual-Vt implementation reduces both, the active leakage and the standby leakage. Further, there is no performance degradation in a dual-Vt implementation for custom VLSI designs.

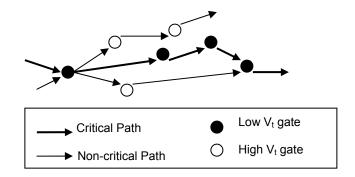

The dual threshold voltage design technique uses two kinds of transistors in the same circuit. Some transistors have a high threshold voltage, while other transistors have a low threshold voltage. The high threshold voltage transistors have less subthreshold leakage power dissipation but also have a larger delay as compared to the low threshold voltage transistors. Fig. 3.6 shows the concept of dual threshold voltage implementation in custom VLSI designs. Here, gates on non-critical paths are assigned high-Vt and the gates on the critical path are assigned low-Vt. The objective is to maximize the number of transistors having high threshold voltage without sacrificing the performance of the circuit. Several prior works have proposed algorithms which assign high-Vt and low-Vt to the logic gates of the given circuit [1][5][17][18]. However the dual threshold voltage design technique proposed in the literature for custom VLSI designs cannot be used for FPGAs. This is because the FPGAs are programmable and the circuit that would be eventually implemented on it is unknown and hence the delays through various paths of the circuit are not known. In this work a dual-Vt FPGA CAD flow for designing and evaluating different dual-Vt FPGA architectures is proposed and developed. No published work has proposed such a CAD flow.

There have been very few works targeted at reducing the leakage power in FPGAs. The leakage reduction techniques can be broadly divided into techniques that target reduction of leakage in logic, routing or both.

The work in [3] used a technique based on the property that the leakage power consumed by a CMOS circuit is dependent on the state of its inputs and used the signal statistics to alter the state of the inputs in order to reduce the leakage power in such a way that the functionality of the circuit does not change. It explains that FPGA circuit

Figure 3.6: Dual-Vt design implementation

elements such as multiplexers and pass transistors should have their inputs and outputs at logic level 1 to reduce active leakage. For example, the gate leakage of a turned on pass transistor is more when a logic 0 is being driven as compared to the case when logic 1 is passed through it. The methodology tries to maximize the time that a signal spends in logic level 1. It uses the concept of static probability of signals to alter the state of the signal. If the static probability of the signal is less than 0.5, then it is a candidate for signal inversion. The signal is inverted if it is possible to do so without changing the functionality of the circuit. It reports an average active leakage savings of 25%. However this work addressed only active leakage. Standby leakage reduction is very important for mobile application because mobile devices typically spend almost 90% of the time in standby mode. Further, this work addressed leakage reduction only in the used parts of the FPGA, and it was shown in [4] that leakage from the unused parts of FPGA can be as high as 56% of the total leakage.

The work in [6] approached the problem of reducing leakage power by dividing the FPGA fabric into small regions with each of the regions being controlled by a sleep transistor which would be turned on/off depending upon whether that region is being used or not, thus reducing the leakage power. It uses a region constrained placement technique to maximize the sleep time. It reports leakage savings of around 20%-30%, with performance loss of 8%. However, this technique requires extra sleep transistors and control circuitry for configuration of the control bits, leading to area overhead. Further, it uses dynamic reconfiguration of SRAM cells, i.e. during the actual run time of the application, which leads to problems associated with the wake up time for the system, and an extra overhead. With the extra overhead the leakage energy savings is reported as 19%. Finally, this technique leads to reduction of only standby leakage power.

The work in [7] explored the dual-Vt, body biasing and gate biasing of nMOS pass transistors for reducing leakage power. The dual-Vt technique used in [7] was based on

varying the percentage of high threshold voltage elements in the routing resources of the FPGA and studying its effect for a number of benchmarks. It did not specify the leakage savings obtained, and no detailed evaluation of several possible routing architectures was presented. Body-biasing technique requires control circuitry and generation of voltages for body biasing. Further, this technique leads to reduction in leakage savings with technology scaling [19]. The negative gate biasing of nMOS pass transistors has implementation issues and also leads to additional leakage current component, called gate induced drain leakage.

The work in [22] used a dual-Vdd/Vt architecture to reduce leakage power and dynamic power. Only the configuration SRAM cells were assigned high-Vt to reduce leakage power. Two types of logic blocks are used, logic blocks with high-Vdd and logic blocks with low-Vdd. The logic blocks have a fixed pattern on the FPGA. An algorithm is used to assign high-Vdd/low-Vdd to the logic blocks based on slack available and power sensitivity. It uses a level converter to transfer the logic between high-Vdd and low-Vdd regions. An overall power savings of around 14% is reported for the dual-Vdd architectures with non-negligible delay penalties. However, the dual-Vdd approach requires design of power supply network with two voltage levels and level converters which lead to area overhead and increased complexity. Further it is difficult to increase the granularity of the approach because that would imply increasing the complexity of the power supply network.

The work in [44] uses logic blocks with dual-Vdd supplies which can be configured so that the logic blocks can be assigned high-Vdd/low-Vdd during the configuration phase for power and performance tradeoffs and leakage power is reduced only in the logic blocks. This technique reduces both the dynamic and leakage power. It uses three kinds of logic blocks, H-block having a fixed high-Vdd, L-block having a low-Vdd and P-block having configurable  $V_{dd}$ . The P-logic blocks are allowed to have a 5% performance degradation and the power switch leads to area overhead of 24% for these blocks. An architecture, arch-DV, is used with H/L/P blocks having the ratio 1/1/3 with an overall area overhead of 14%. An overall power savings of 9.04% is reported for the arch-DV. For the architecture having all P-blocks with an area overhead of 24%, an overall power savings of 14.3% is reported. This work has problems with area overhead management, and design of supply network with dual-Vdd. No analysis of delay penalties was presented, rather the comparison with the baseline architecture was done for a number of fixed clock frequencies. A similar work was done in [39] using configurable dual-Vdd blocks with a different algorithm to assign high-Vdd/low-Vdd to logic blocks. An average overall power savings of 61% was reported with leakage savings of 71% with delay penalty of around 20%. This work has similar design issues as above.

The work in [45] proposes low power routing switch design for reducing the leakage

and switching power. The low power switch is designed by having sleep transistors for the buffer at the output of the multiplexer switch. Two sleep transistors are used in parallel, NMOS sleep transistor called MNX, and PMOS sleep transistor called MPX, providing virtual Vdd to the output buffer. In the high speed mode MPX is turned on and MNX is turned off. In the low power mode MNX is turned on and MPX is turned off. In the low power mode the virtual Vdd is equal to  $Vdd - V_{th}$ , leading to lower output swing and reduced subthreshold leakage. In an alternate design the body of the PMOS switches in the buffer is tied to virtual Vdd, leading to reduced threshold voltage and consequently increased drive strength. This leads to increased leakage, but the buffer can be smaller in size leading to area reduction. The switches were designed such that the performance loss is within 5%. It also took advantage of the fact that for most of the routing switches in FPGAs, significant slacks are available, so that a significant fraction of the routing switches can be of this type. A leakage power savings of 36% was reported for the switch in the low power mode versus the high speed mode. For the alternate switch design, a leakage power savings of 28% was reported. The switching energy was reduced by 29%. In the sleep mode, a leakage savings of 61% was observed. The proposed switch is 1.3 times larger in area as compared to the traditional switch, whereas the alternate switch is 1.2 times larger in area as compared to the traditional switch. The area overhead for the complete FPGA is estimated to be around 20%. The main drawback of this work is that it leads to non-negligible area overhead.

Motivated by the limitations of the leakage power reduction techniques for FPGAs, a dual-Vt technique and CAD flow that has the following advantages, is proposed in this work:

- 1. Reduces both active leakage power and standby leakage power.

- Provides a CAD framework for developing and evaluating a dual-Vt FPGA implementation.

- 3. The inherent area penalty in using sleep transistors is not present in this design technique.

- 4. The dual-Vt architecture does not require any modification in the existing placement and routing tools from the perspective of the users.

### 3.5 Summary

This chapter presented work that has been done on leakage power modeling and reduction for FPGAs. The methodologies were described and the results were discussed. The drawbacks of these techniques were discussed, which served as the motivation for this work.

In the next chapter, the leakage power model for FPGAs developed in this work is explained and results obtained from the leakage power model are discussed. Chapter 5 discusses the dual-Vt FPGA architecture and CAD flow for leakage power reduction.

## Chapter 4

# **Analytical State Dependent Leakage Power Model for FPGAs**

### 4.1 Introduction

In this chapter the leakage power model for FPGAs is explained and discussed. Analytical models are used for computing leakage current through each of the FPGA circuit elements. A library of functions is used for this purpose. This library of functions takes the input as the probability of state of the FPGA circuit element and the technology parameters and computes the leakage for the FPGA circuit element. This is repeated for all the elements in the FPGA and the total leakage current is computed as the sum of the individual leakage currents.

Analytical models for leakage currents in a transistor are explained in the next section and leakage models to account for short-channel effects are developed. The leakage currents in various FPGA circuit elements and their state dependency are discussed in section 4.3. Section 4.4 discusses the overall framework for computing the leakage power for FPGAs. Finally, in section 4.5 results obtained from the leakage power model are discussed.

### 4.2 Analytical Models for Leakage Currents

The leakage power model considers the subthreshold and the gate leakage. The following are the subthreshold and gate leakage equations used in the power model [25].

$$I_{sub} = I_0 \left[ 1 - exp \left[ \frac{-V_{ds}}{V_T} \right] \right] \cdot exp \left[ \frac{V_{gs} - V_{th} - V_{off}}{nV_T} \right]$$

(4.1)

$$I_0 = \mu \frac{W}{L} \sqrt{\frac{q\epsilon_{si}NDEP}{2\phi_s}V_T^2}$$

(4.2)

$$I_{gc0} = \frac{W.L.A.V_{gs}.V_{aux}}{T_{ox}^2}.exp\left[-B.T_{ox}\right].$$

$$(AIGC - BIGC.V_{oxdepinv}).(1 + CIGC.V_{oxdepinv})$$

$$(4.3)$$

$$V_{aux} = NIGC.V_T.log \left[1 + exp\left(\frac{Vgs - V_{th0}}{NIGC.V_T}\right)\right]$$

(4.4)

$$V_{oxdepinv} = K1.\sqrt{\phi_s} + V_{gs} - V_{th} \tag{4.5}$$

$$I_{gcs} = \frac{PIGCD.V_{ds} + exp(-PIGCD.V_{ds})}{PIGCD^2.V_{ds}^2 + 2e - 4} - \frac{1 + 1e - 4}{PIGCD^2.V_{ds}^2 + 2e - 4}$$

(4.6)

$$I_{gcd} = \frac{1 - (PIGCD.V_{ds} + 1).exp(-PIGCD.V_{ds})}{PIGCD^2.V_{ds}^2 + 2e - 4} + \frac{1e - 4}{PIGCD^2.V_{ds}^2 + 2e - 4}$$

(4.7)

The subthreshold leakage  $(I_{sub})$  equations [25] are given by equations (4.1) and (4.2), where  $V_T$  is the thermal voltage,  $V_{off}$  is the offset voltage which determines the channel current at  $V_{gs} = 0$ , n is the subthreshold swing coefficient,  $W, L, \mu, q, \phi_s, \epsilon_{si}$ , are the width, length, mobility of charge carriers, electron charge, surface potential and permittivity of silicon, respectively, for the transistor. Since only the gate to channel current  $(I_{gc0})$  is the dominant gate leakage current, and the gate current for the PMOS is significantly smaller than the gate current for the NMOS, only gate to channel current for the NMOS is modeled [26]. However, the proposed model can be easily extended to incorporate other gate leakage components and the gate leakage for the PMOS. The gate leakage equations are given by (4.3)- (4.7), where A, B are physical constants,  $T_{ox}$  is the gate oxide thickness, AIGC, BIGC, CIGC, and NIGC are the empirical parameters, K1 is the first order body bias coefficient. Equation (4.3) is used for computing  $I_{gc0}$  and equations (4.6), and (4.7) are used for partitioning  $I_{gc0}$  into the source current  $I_{gcs}$  and drain current  $I_{qcd}$ , where *PIGCD* is a parameter for the partitioning.

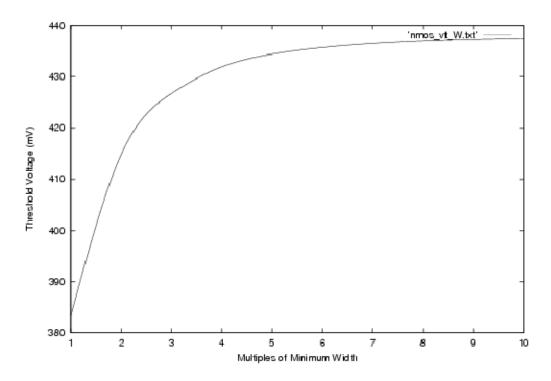

In this work, industrial CMOS 130nm and CMOS 90nm processes were used for the leakage analysis of the FPGA using the leakage power model. The deep-submicron MOSFETs have various short channel effects (SCE) which were not present in long channel devices. For the CMOS 130nm process that was used, it was observed that the threshold voltage ( $V_{th}$ ) of the NMOS was affected by the reverse narrow width effect (RNWE) [13], i.e., the threshold voltage of the transistor increased as the width of the transistor increased from the minimum width, which consequently reduced the leakage of the transistor. Further, the threshold voltage of the transistors are also affected by the drain to source voltage ( $V_{ds}$ ). The threshold voltage of the transistor decreases when the drain to source voltage is increased. To incorporate these effects into the models, the experimental data from the SPICE simulation was curve fitted to empirical equations as follows:

$$V_{th}|_{(V_{ds}=0)} = V_0 \left( 1 - a.exp(-b_1.W - b_2.W^2) \right)$$

(4.8)

$$V_{th} = V_{th}|_{(V_{ds}=0)} - m.V_{ds}$$

(4.9)

where W is the width of the transistor, equation 4.8 models the RNWE, and equation 4.9 models the impact of  $V_{ds}$  on  $V_{th}$ . For CMOS 130nm NMOS,  $V_0 = 0.412V$ , a = 0.345003,  $b_1 = 1.01194$ ,  $b_2 = -0.0568004$ , and m = 0.02125. For CMOS 130nm PMOS, the RNWE was not too significant, so only the dependence of  $V_{th}$  on  $V_{ds}$  was modeled, with m = 0.02388. These values were determined from curve fitting of the simulation data. For the CMOS 90nm process a similar RNWE for the NMOS was observed, and the dependence of  $V_{th}$  on  $V_{ds}$  was observed for both NMOS and PMOS. However, for the CMOS 90nm PMOS a narrow width effect (NWE)[13] was observed, which results in increasing  $V_{th}$  as the width of the transistor is decreased. The RNWE and  $V_{ds}$  dependence for CMOS 90nm NMOS were modeled using equations (4.8) and (4.9) with the constants as  $V_0 = 0.320812$ , a = 0.437178,  $b_1 = 1.2$ ,  $b_2 = -0.068$ , and m = 0.0668. For the PMOS, a model using curve fitting to account for the NWE was developed, as follows:

$$V_{th} = \frac{f_1 + f_2 \cdot W + f_3 \cdot W^2}{q_1 + q_2 \cdot W + q_3 \cdot W^2}$$

(4.10)

where  $f_1 = 0.49$ ,  $f_2 = 1.16679$ ,  $f_3 = -1.51$ ,  $g_1 = 0.318$ ,  $g_2 = 4.3$  and  $g_1 = -0.533$ . The impact  $V_{ds}$  was modeled using equation (4.9), with m = -0.0468. These equations have been used in our leakage power model to model the reverse narrow width effect and the dependence of  $V_{th}$  on  $V_{ds}$ . Although the constants used in these equations make it technology dependent, the data can be easily extracted by simulating only one device under few different widths and drain to source voltages.

Figure 4.1: Dependence of  $V_{th}$  on the width of NMOS for CMOS 130nm

For illustrative purposes the dependence of  $V_{th}$  on the width of the transistor and the drain to source voltage are shown in Fig. 4.1 and Fig. 4.2, respectively for NMOS in CMOS 130nm. Fig. 4.1 shows the dependence of  $V_{th}$  on the width of NMOS. It shows that as the width is increased the threshold voltage increases rapidly, and flattens out after the width of the transistor is 7 times the minimum width. Fig. 4.2 shows the dependence of  $V_{th}$  on the drain to source voltage. It can be seen that the threshold voltage of the NMOS decreases linearly with the drain to source voltage.

Table 4.1 shows that the inclusion of the RNWE in the power model greatly improves the overall accuracy of the power model. The base threshold voltages of the devices were determined from the SPICE simulation so that various effects can be accounted for in the model.

### 4.3 Leakage in FPGA Circuit Elements

This section describes the various leakage current components that have been modeled in different circuit elements. The inverters were sized for equal rise and fall times, and

Figure 4.2: Dependence of  $V_{th}$  on drain to source voltage for NMOS in CMOS 130nm

| Table 4.1. Comparison of Fower Model with the SFICE simulations for CMOS 150m |       |           |            |          |             |  |  |

|-------------------------------------------------------------------------------|-------|-----------|------------|----------|-------------|--|--|

| Circuit El-                                                                   | SPICE | Power     | Power      | Error    | Error (with |  |  |

| ement                                                                         | (pW)  | Model     | Model      | (without | SCE)        |  |  |

|                                                                               |       | (without  | (with SCE) | SCE)     |             |  |  |

|                                                                               |       | SCE) (pW) | (pW)       |          |             |  |  |

| Inverter                                                                      | 372.7 | 901.2     | 411.8      | 141%     | 10.5%       |  |  |

| (2x)                                                                          |       |           |            |          |             |  |  |

| 4-Binary                                                                      | 1156  | 1352      | 1212       | 16.9%    | 4.8%        |  |  |

| Tree                                                                          |       |           |            |          |             |  |  |

| Buffered                                                                      | 883.2 | 1403      | 873.4      | 58.8%    | 1.1%        |  |  |

| Switch                                                                        |       |           |            |          |             |  |  |

|                                                                               |       |           |            |          |             |  |  |

Table 4.1: Comparison of Power Model with the SPICE simulations for CMOS 130nm

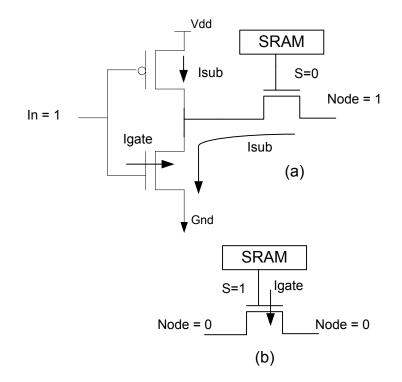

Figure 4.3: (a) Gate leakage in NMOS (b) Subthreshold leakage in Inverter

for minimizing the delay and area product [9]. All the multiplexers were implemented with minimum sized transistors, the SRAM cells are considered to have minimum sized transistors with high- $V_{th}$  to mitigate subthreshold leakage, and the routing switches were optimized for area and delay product. Both the PMOS and NMOS in various circuit elements are considered as the candidates for subthreshold leakage, but only the NMOS transistors are considered as candidates for gate leakage because the gate leakage in PMOS is considerably smaller than NMOS [26]. Furthermore, the back gate leakage of the NMOS transistors is ignored and only the gate current from the gate to channel is considered, which then gets partitioned, and flows into the source and the drain of the transistor as shown in Fig. 4.3(a). The methodology that was adopted for computing the leakage power for each of the circuit elements in the FPGA is described below.

*Inverter*: The subthreshold leakage of the inverters is modeled in both the states, i.e, when the input is 0 and when the input is 1 and the gate leakage of the inverter when the input is 1. With the input at 0, only subthreshold leakage flows through the NMOS of the inverter and the gate leakage through PMOS is ignored as shown in Fig. 4.3(b). When the input to the inverter is 1, there is subthreshold leakage through the PMOS and gate leakage through the NMOS.

*Multiplexer*: In FPGAs, the multiplexers are implemented with NMOS pass transistor structures. The multiplexer is binary tree implemented using pass transistors. The leakage currents in the multiplexer is again strongly dependent on the state of its inputs. The multiplexer leakage under two cases are as follows.

*Case1:* Fig. 4.4 shows the structure of the multiplexer and the subthreshold and gate leakages for the select signal (0,0) and the input vector (0010). Only one transis-

Figure 4.4: Multiplexer structure and the corresponding state dependent leakage for a particular select signal and input vector

tor (Q3) has subthreshold leakage, whereas three transistors have gate leakage currents (Q2,Q4,Q6). However, when the input vector changes to (0110), keeping the select signal same, there are three transistors which have subthreshold leakage (Q1,Q3,Q5) and two transistors have gate leakage (Q1,Q6). Therefore it is quite important to consider the state dependency of leakage currents in any circuit.

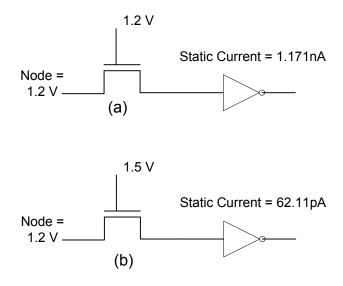

*Case2:* Another phenomenon that needs to be accounted for in the pass transistor structures is that of the impact of  $V_{ds}$  on the threshold voltage of the transistor. Consider the case of two cascaded pass transistors as shown in Fig. 4.5. Here, transistor Q2 has subthreshold leakage. However, the drain terminal of Q2 is not at  $V_{dd}$ , but at a smaller

Figure 4.5: Leakage in multiplexers is affected by the voltage drop during signal propagation