## Foveated Sampling Architectures for

## **CMOS** Image Sensors

by

Fayçal Saffih

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2005

© Fayçal Saffih 2005

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A THESIS

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Electronic imaging technologies are faced with the challenge of power consumption when transmitting large amounts of image data from the acquisition imager to the display or processing devices. This is especially a concern for portable applications, and becomes more prominent in increasingly high-resolution, high-frame rate imagers. Therefore, new sampling techniques are needed to minimize transmitted data, while maximizing the conveyed image information.

From this point of view, two approaches have been proposed and implemented in this thesis:

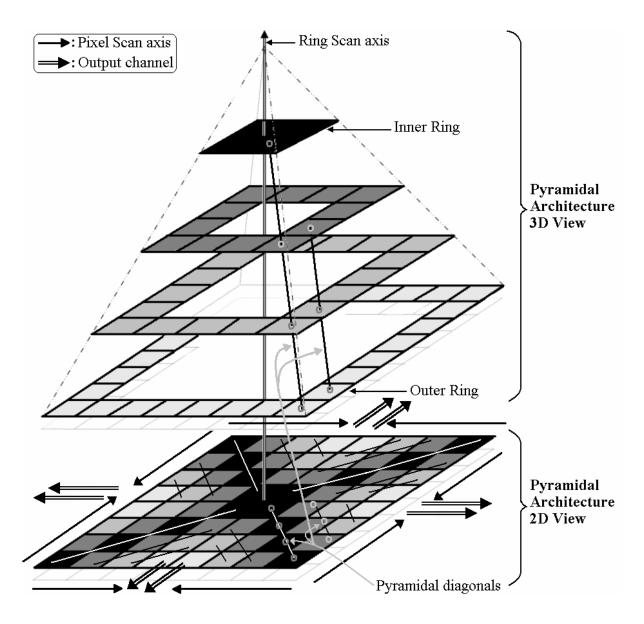

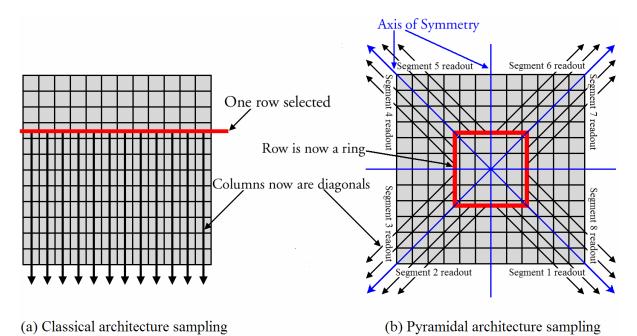

1) A system-level approach, in which the classical 1D row sampling CMOS imager is modified to a 2D ring sampling pyramidal architecture, using the same standard three transistor (3T) active pixel sensor (APS).

2) A device-level approach, in which the classical orthogonal architecture has been preserved while altering the APS device structure, to design an expandable multiresolution image sensor.

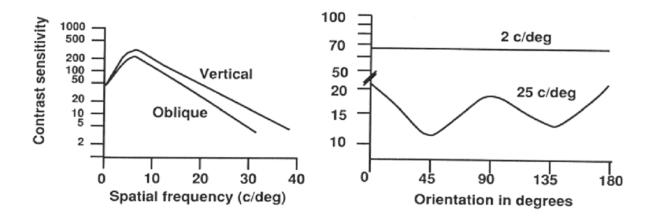

A new scanning scheme has been suggested for the pyramidal image sensor, resulting in an intrascene foveated dynamic range (FDR) similar in profile to that of the human eye. In this scheme, the inner rings of the imager have a higher dynamic range than the outer rings. The pyramidal imager transmits the sampled image through 8 parallel output channels, allowing higher frame rates. The human eye is known to have less sensitivity to oblique contrast. Using this fact on the typical oblique distribution of fixed pattern noise, we demonstrate

lower perception of this noise than the orthogonal FPN distribution of classical CMOS imagers.

The multiresolution image sensor principle is based on averaging regions of low interest from frame-sampled image kernels. One pixel is read from each kernel while keeping pixels in the region of interest at their high resolution. This significantly reduces the transferred data and increases the frame rate. Such architecture allows for programmability and expandability of multiresolution imaging applications.

*Index terms:* CMOS image sensor, Pyramidal image sensor, Multiresolution image sensor, 2D sampling, Foveated Dynamic Range (FDR), Videophone, Video communication, Remote imaging.

#### Acknowledgements

# (أب تَّ أوْز عْنِي أَنْ أَشْكُرَ نِعْمَتَكَ الَّتِي أَنْعَمْتَ عَلَيَّ وَعَلَى وَالِدَيَّ وَأَنْ أَعْمَلَ صَالِحًا تَرْضَاهُ وَأَدْخِلْنِي بِرَحْمَتِكَ فِي عِبَادِكَ الصَّالِحِينَ دو أَدْخِلْنِي بِرَحْمَتِكَ فِي عِبَادِكَ الصَّالِحِينَ

I would like to extend my sincere thanks to my supervisor Dr. Richard Hornsey for his support and patience all along my doctoral research program. His view of CMOS imaging has inspired me to endorse an interesting CMOS vision path I am very confident it will change the course of imaging technology in near and far future.

To my beloved wife Rima and my son Taha I dedicate my present thesis. Their support, encouragements and love were my driving force to write my thesis and carrying on my doctoral research.

I dedicate my thesis to my father Hocine, whom I am always missing ..., who taught me the courage of carrying on my endeavours ..., and to excel in science and encouraged me to follow up my studies. To my mother, I dedicate my present work for her tremendous effort in raising me since my early steps in this life.

To all my teachers and supervisors, I dedicate this thesis thanking them from the bottom of my heart.

## **Table of Contents**

| Abstract                                                | iii   |

|---------------------------------------------------------|-------|

| Acknowledgements                                        | v     |

| Fable of Contents                                       | vi    |

| List of Figures                                         | xi    |

| List of Tables                                          | . xvi |

| Chapter 1 Introduction to CMOS Image Sensors            | 1     |

| 1.1 Imaging Evolution                                   | 1     |

| 1.1.1 CCD and CMOS Image Sensors                        | 2     |

| 1.1.2 Future Prospects and Trends                       | 2     |

| 1.2 Thesis Objectives                                   | 3     |

| 1.2.1 Thesis Philosophical Statements                   | 3     |

| 1.2.2 Scanning Statement                                | 3     |

| 1.2.3 Image Sampling Statement                          | 4     |

| 1.3 Thesis Motivations and Goals                        | 4     |

| 1.4 Contributions                                       | 5     |

| 1.5 Thesis Organization                                 | 6     |

| Chapter 2 Background: CMOS imagers and Spatial Sampling | 8     |

| 2.1 Introduction to CMOS Image Sensors                  | 8     |

| 2.1.1 Passive Pixel Sensor (PPS)                        | 10    |

| 2.1.2 Photodiode Active Pixel Sensor                    | 10    |

| 2.1.3 Photogate Active Pixel Sensor                            | 11 |

|----------------------------------------------------------------|----|

| 2.1.4 Integration Time & Raster Scanning                       |    |

| 2.1.5 Correlated Double Sampling CDS                           | 14 |

| 2.1.6 Fixed Pattern Noise (FPN)                                | 14 |

| 2.2 Non Raster Scanning (Sampling) CMOS Imagers                | 16 |

| 2.3 Our Approach for Image Sampling                            |    |

| 2.4 Biological Vision                                          |    |

| 2.4.1 Spatial Sampling                                         |    |

| 2.5 Previous Foveated Vision CMOS imagers                      |    |

| 2.5.1 Foveated CMOS Image Sensor                               |    |

| 2.5.2 Multi-Resolution CMOS Image sensors                      |    |

| 2.6 Dynamic Range Enhancement Techniques                       |    |

| 2.6.1 Dynamic Range Enhancement by Photo-Response Compression  |    |

| 2.6.2 Dynamic Range Enhancement using Integration Time Control |    |

| 2.6.3 Dynamic Range Enhancement using Variable Light Exposures |    |

| 2.6.4 Dynamic Range Enhancement using Multiple Sampling        | 49 |

| 2.7 Why Foveated Dynamic Range?                                | 53 |

| Chapter 3 Foveated CMOS Image Sensors Design                   | 55 |

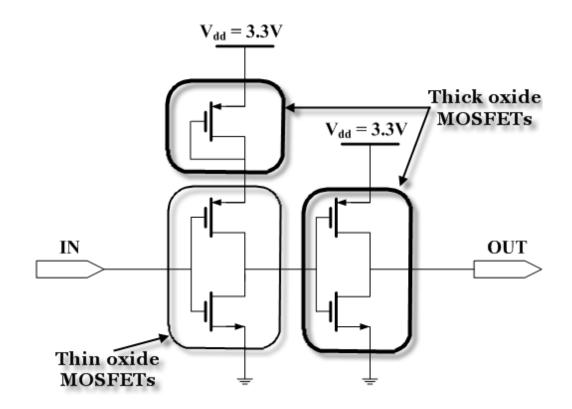

| 3.1 Brief description of CMOS 0.18µm technology                | 55 |

| 3.2 Foveated Architecture Motivations                          | 57 |

| 3.3 Design Motivation                                          | 58 |

| 3.4 Pyramidal CMOS Imager Design Tools                                      | 60  |

|-----------------------------------------------------------------------------|-----|

| 3.5 Pyramidal Architecture and Its Building Blocks                          | 62  |

| 3.5.1 Architecture Description                                              | 62  |

| 3.5.2 APS Pixel                                                             | 65  |

| 3.5.3 Voltage Conversion block                                              | 71  |

| 3.5.4 Sample and Hold block                                                 | 73  |

| 3.5.5 Output Buffer                                                         | 76  |

| 3.5.6 Decoders for Column (Diagonal) Select                                 | 79  |

| 3.5.7 Pyramidal Imager Chip design                                          | 80  |

| 3.5.8 Bouncing Scanning                                                     | 82  |

| 3.5.9 Pyramidal Ring Sampling and Blur Symmetrization                       | 84  |

| 3.5.10 Hardware Cost Scaling of the Pyramidal Imager Design                 | 91  |

| 3.6 Multiresolution Imager Design                                           | 94  |

| 3.7 Summary                                                                 | 94  |

| Chapter 4 Mathematical Basis of Foveated Dynamic Range & High Speed Imaging | 96  |

| 4.1 Mathematical Analysis of Foveated Dynamic Range                         | 96  |

| 4.1.1 Timing examination of bouncing scanning:                              | 96  |

| 4.1.2 Mathematical Analysis                                                 | 99  |

| 4.1.3 The Control of the Fovea Border                                       | 108 |

| 4.1.4 Inverse-Foveated Dynamic Range                                        | 115 |

| 4.1.5 Pyramid-bordered FDR Profile Control                                  | 118 |

| 4.2 Restrictions of the FDR Mathematical foundations          | 123 |

|---------------------------------------------------------------|-----|

| 4.3 High Speed Imaging of Pyramidal Imager                    |     |

| 4.4 Pyramidal Acquisition Speed with Serial readout.          |     |

| 4.5 FDR Pinning Cost on Frame Rate                            |     |

| 4.6 Benefit of Foveated Dynamic range                         |     |

| 4.7 Summary                                                   |     |

| Chapter 5 Testing and Characterization                        |     |

| 5.1 Testing Setup                                             |     |

| 5.2 Dynamic Range Calculation                                 |     |

| 5.3 Pyramidal Data Structure                                  |     |

| 5.4 Data Analysis                                             |     |

| 5.4.1 Non-Bouncing Scanning data analysis                     |     |

| 5.4.2 Sensitivity                                             |     |

| 5.4.3 Photon-response Modeling                                | 150 |

| 5.5 Bouncing Scanning and Dynamic Range calculation           |     |

| 5.5.1 Foveated Dynamic range and Video Communications         |     |

| 5.6 Summary                                                   |     |

| Chapter 6 Pyramidal Imager Fixed Pattern Noise Low Perception |     |

| by the Human Visual System                                    |     |

| 6.1 Fixed Pattern Noise                                       |     |

| 6.2 Fixed Pattern Noise Topology in Classical CMOS imagers    |     |

## List of Figures

| Fig 2.1 From photodiode to CMOS image sensor                               | 9  |

|----------------------------------------------------------------------------|----|

| Fig 2.2 The different types of CMOS imaging pixels                         | 9  |

| Fig 2.3 Pixel frame integration time in raster scanning                    | 13 |

| Fig 2.4 The scanning process framework                                     | 18 |

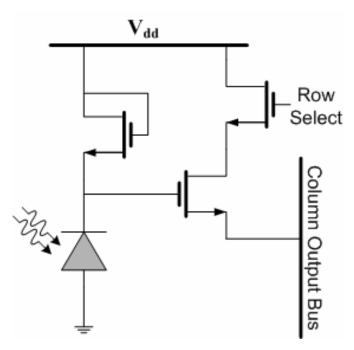

| Fig 2.5 Individual pixel reset APS                                         | 19 |

| Fig 2.6 Polar foveated CMOS image sensors [33]                             | 26 |

| Fig 2.7 All CMOS rectilinear foveal image sensor                           | 27 |

| Fig 2.8 Programmable multiresolution CMOS active pixel sensor architecture | 29 |

| Fig 2.9 Logarithmic active pixel sensor                                    | 32 |

| Fig 2.10 Light to pulses conversion forms                                  | 34 |

| Fig 2.11 Global shutter general schematic                                  | 36 |

| Fig 2.12 Pixel schematic of MIT photoreceptor                              | 37 |

| Fig 2.13 Spatially varying exposure time technique for DR enhancement      | 39 |

| Fig 2.14 The quantization in SVE imager                                    | 43 |

| Fig 2.15 Quantization level adjustment for the SVE exact Gamma correction  | 47 |

| Fig 2.16 SVE cluster aggregation photo-response of the local brightness    | 48 |

| Fig 2.17 Architecture schematic of the dual sampling technique             | 50 |

| Fig 3.1 Classical sampling architecture of CMOS image sensor               | 60 |

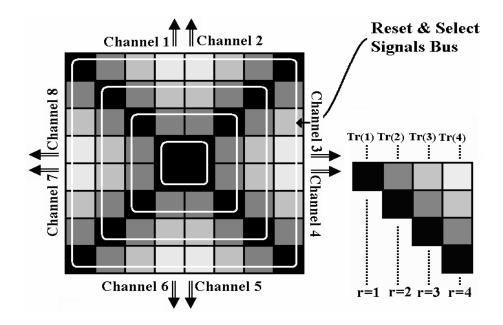

| Fig 3.2 Pyramidal architecture schematic views                             | 63 |

| Fig 3.3 Variations between the classical and pyramidal architectures of CMOS imagers   | 64  |

|----------------------------------------------------------------------------------------|-----|

| Fig 3.4 The classical structure of active pixel sensor with $N^+/P_{sub}$ photodiode   | 65  |

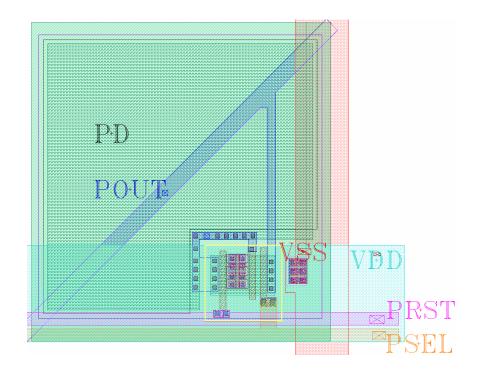

| Fig 3.5 Layout of the pyramidal CMOS imager pixel                                      | 66  |

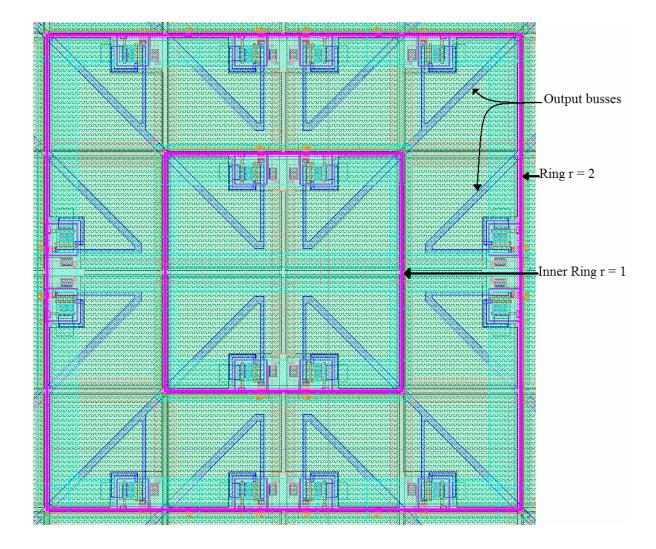

| Fig 3.6 Layout of the two first inner rings of pyramidal CMOS imager                   | 68  |

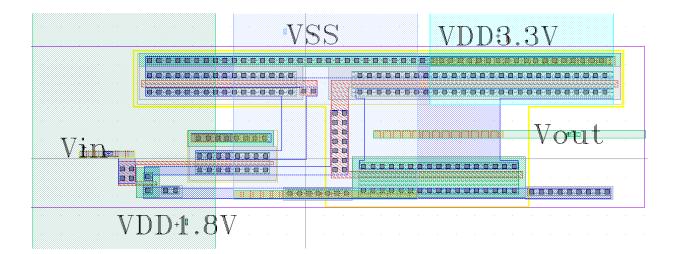

| Fig 3.7 Schematic of the 1.8V-to-3.3V voltage conversion block                         | 72  |

| Fig 3.8 Layout of the 1.8V-to-3.3V voltage conversion block                            | 72  |

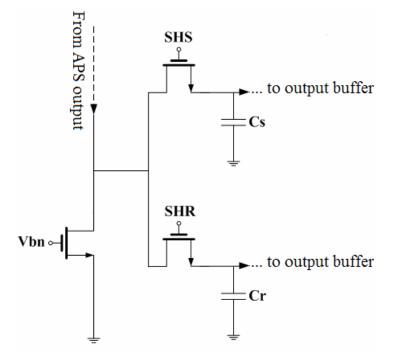

| Fig 3.9 Sample and hold circuit schematic                                              | 74  |

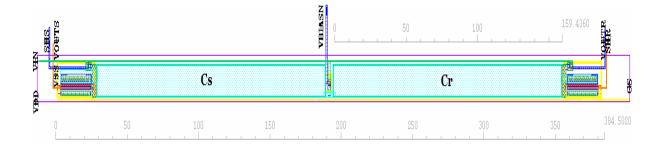

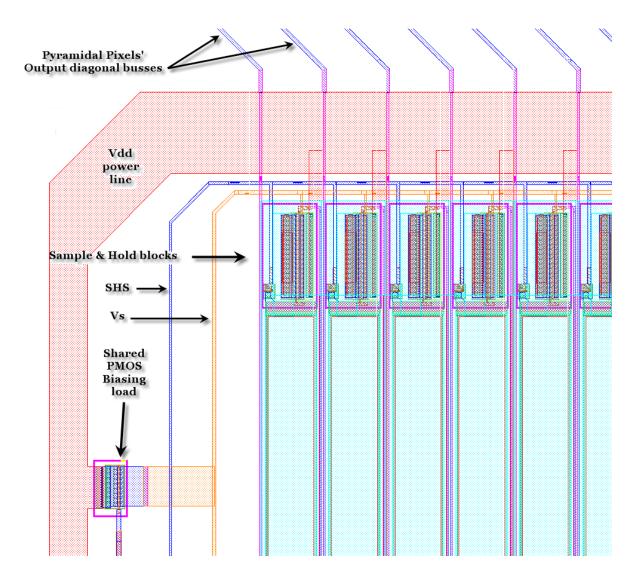

| Fig 3.10 Layout of the sample and hold block                                           | 75  |

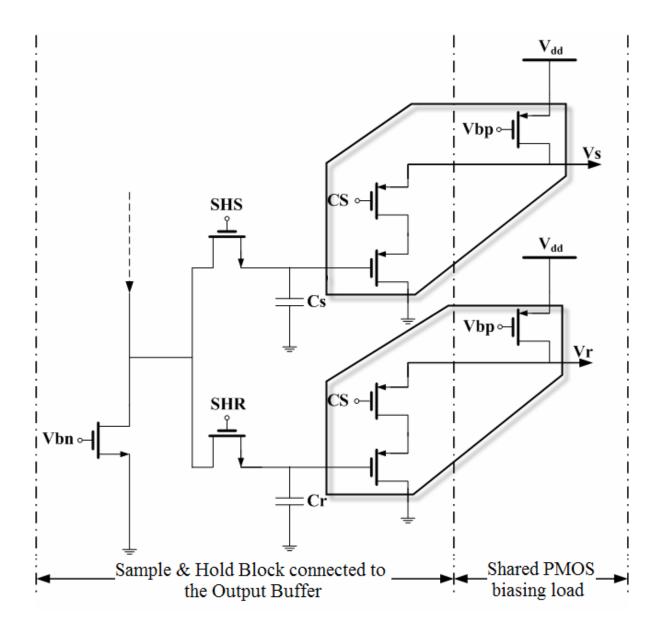

| Fig 3.11 The output buffer split between the S&H block and the shared PMOS bias        | 77  |

| Fig 3.12 Layout of the output buffer within the S&H blocks                             | 78  |

| Fig 3.13. Gate level block diagram of 3 to 8 decoder                                   | 79  |

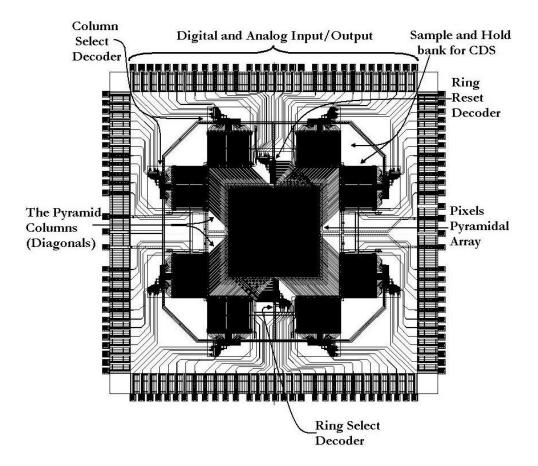

| Fig 3.14 Pyramidal CMOS image sensor structural layout                                 | 80  |

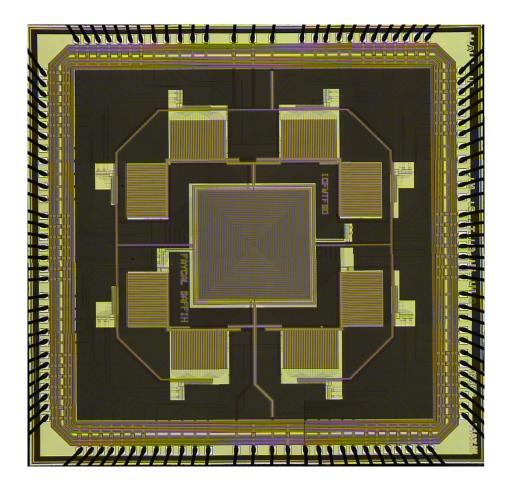

| Fig 3.15 Optical micrograph image of the pyramidal CMOS image sensor                   | 81  |

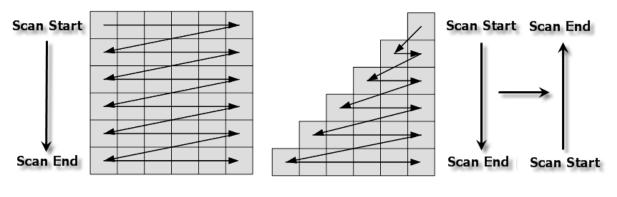

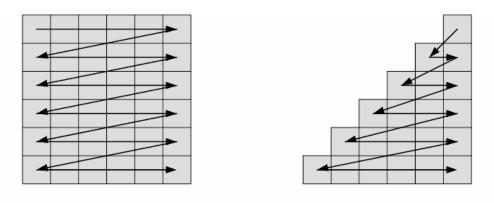

| Fig 3.16 Classical imager raster scan and bouncing scan in a pyramidal imager segment  | 83  |

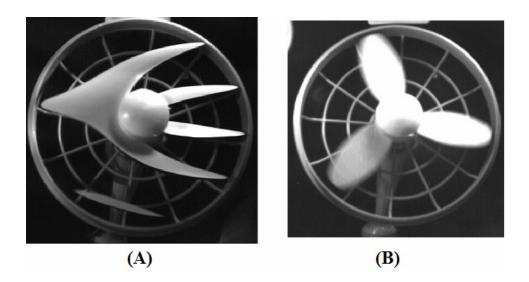

| Fig 3.17 Impact of rolling-shutter on CMOS sensor causing motion blur                  | 85  |

| Fig 3.18 Global shutter (B) versus rolling shutter (A) and motion blur distortion [84] | 86  |

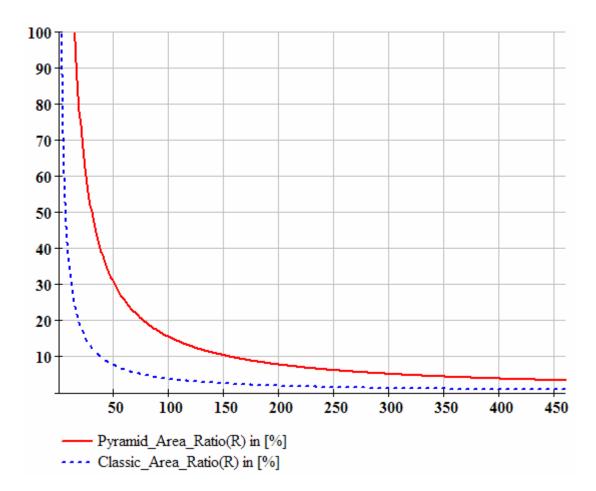

| Fig 3.19 S&H hardware cost ratios of the classical and pyramidal imagers               | 93  |

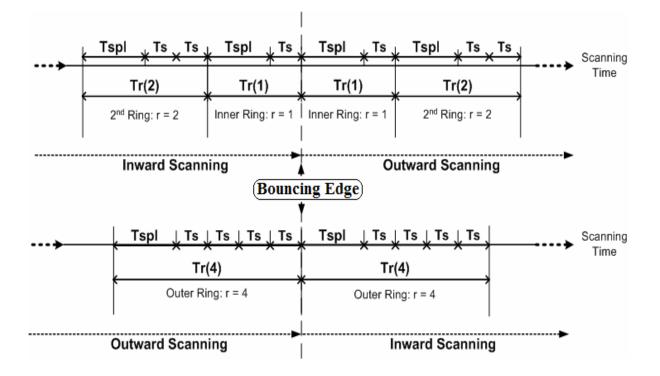

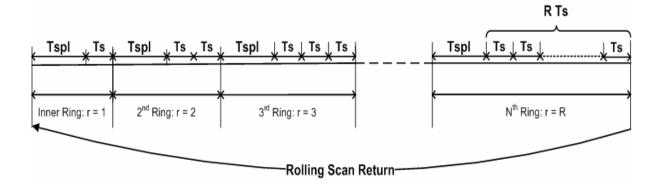

| Fig 4.1 Pyramidal imager readout scheme                                                | 98  |

| Fig 4.2 Timing diagram of inward and outward scanning                                  | 99  |

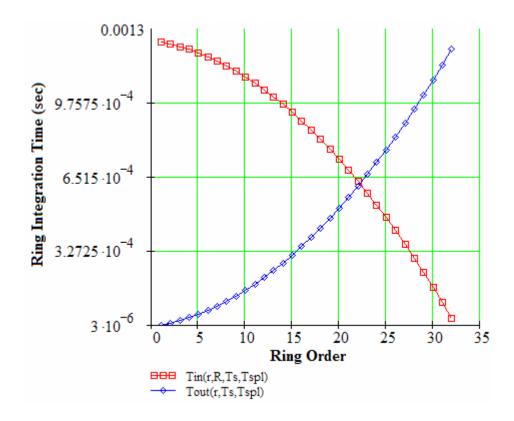

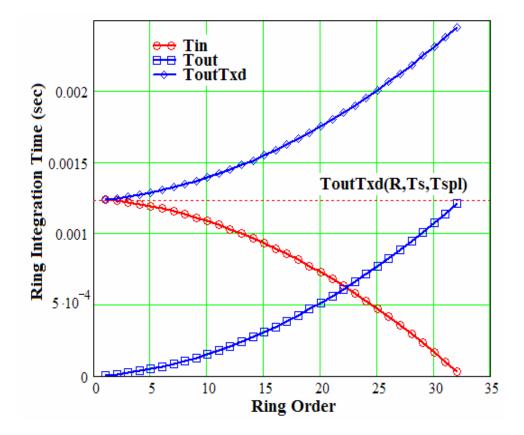

| Fig 4.3 Plot of the rings inward and outward scanning integration time                 | 101 |

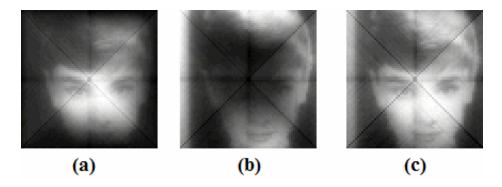

| Fig 4.4 Bouncing scanning in linear regime: (a) Inward, (b) Outward, (c) Fused images  | 102 |

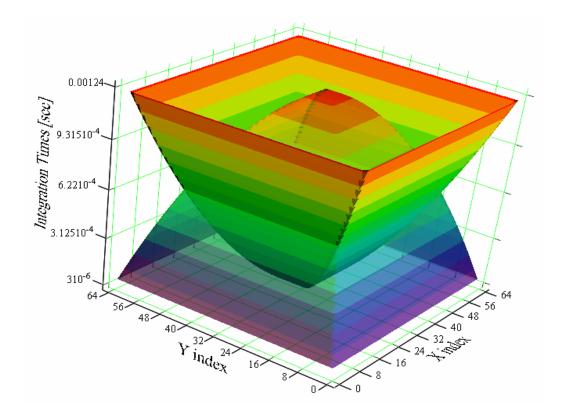

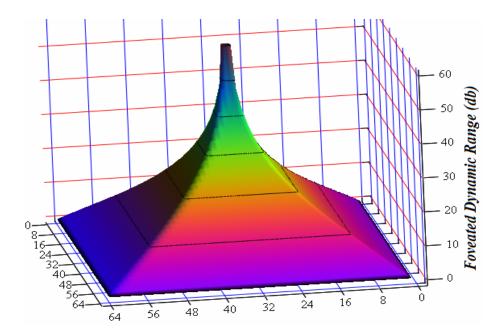

| Fig 4.5 3D view of the rings inward and outward scanning integration time profiles               | 103 |

|--------------------------------------------------------------------------------------------------|-----|

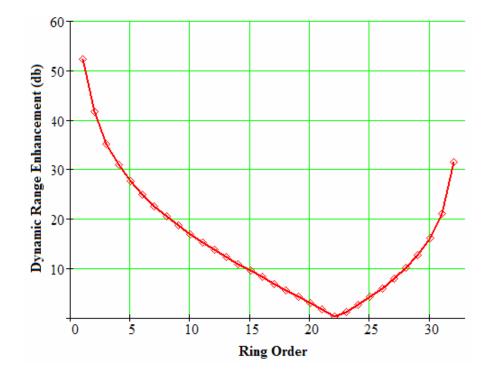

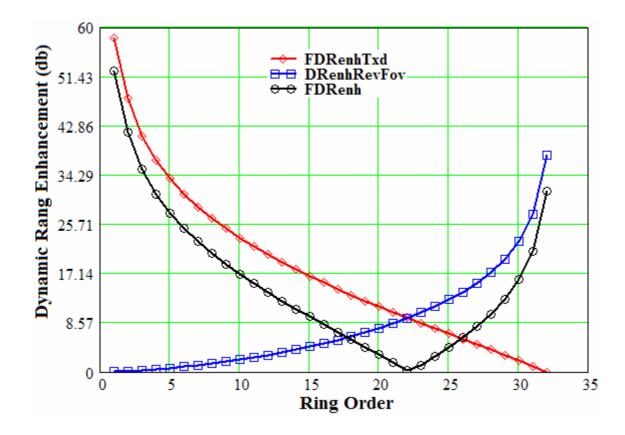

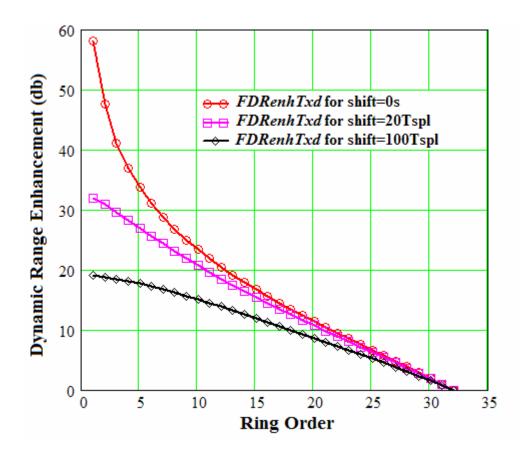

| Fig 4.6 Intrascene foveated dynamic range enhancement                                            | 104 |

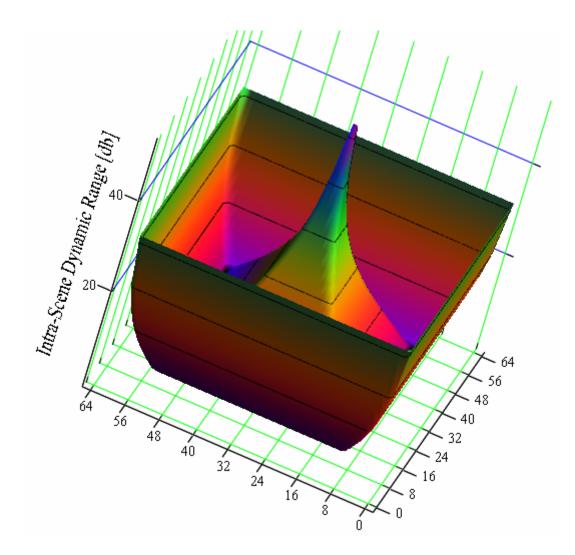

| Fig 4.7 Intrascene foveated dynamic range enhancement in 3D view                                 | 105 |

| Fig 4.8 Foveated dynamic range border limit for a 32 ring pyramidal imager                       | 107 |

| Fig 4.9 Foveated dynamic range border control technique                                          | 111 |

| Fig 4.10 Foveated dynamic range enhancement after border pinning                                 | 113 |

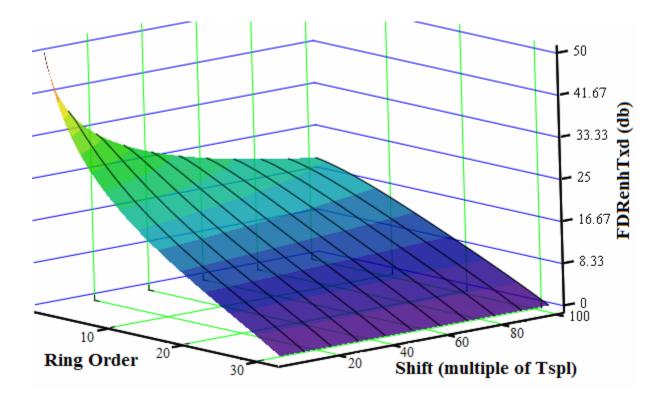

| Fig 4.11 Bouncing scanning integration times after FDR border pinning in 3D view                 | 114 |

| Fig 4.12 Foveated dynamic range enhancement after border pinning in 3D view                      | 114 |

| Fig 4.13 Inverse foveated dynamic range enhancement technique                                    | 116 |

| Fig 4.14 The different foveated dynamic range enhancement profiles                               | 117 |

| Fig 4.15 Control technique for pinned foveated dynamic range enhancement                         | 118 |

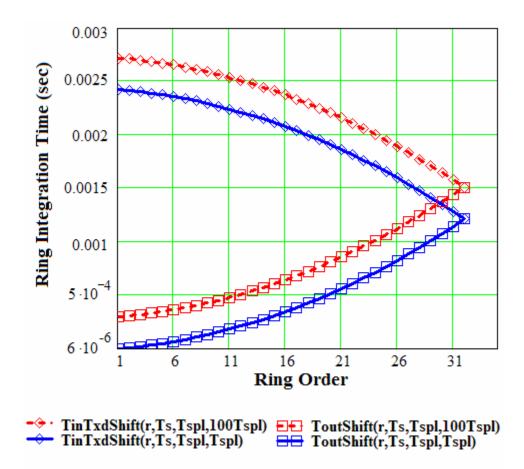

| Fig 4.16 Pinned foveated dynamic range enhancement versus shifting time                          | 120 |

| Fig 4.17 Pinned foveated dynamic range enhancement versus shifting time in 2D                    | 121 |

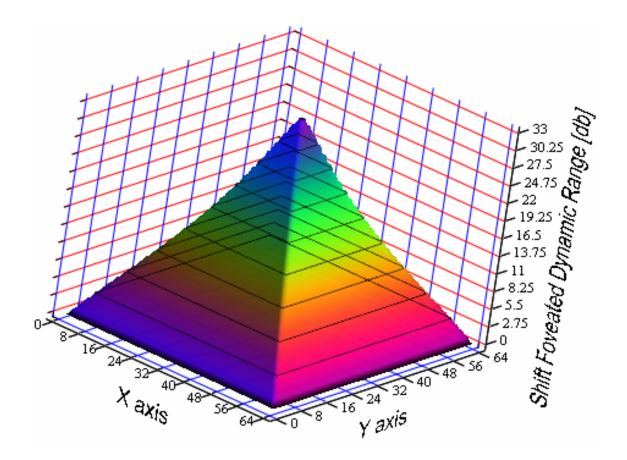

| Fig 4.18 Pyramidal dynamic range enhancement profile                                             | 122 |

| Fig 4.19 Rolling scanning timing diagram                                                         | 124 |

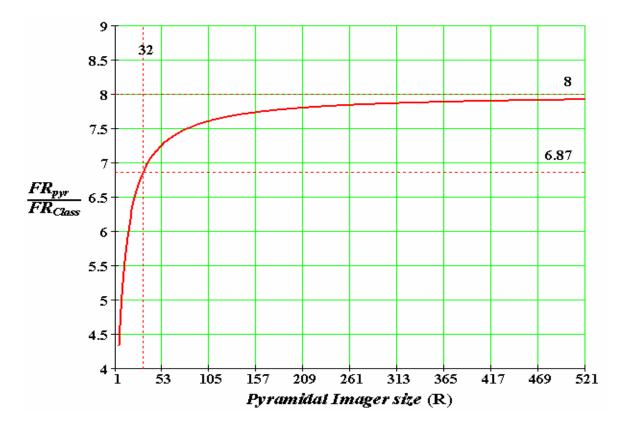

| Fig 4.20 Fame rate ratio between pyramidal and classical imager of size 2 <i>R</i> by 2 <i>R</i> | 126 |

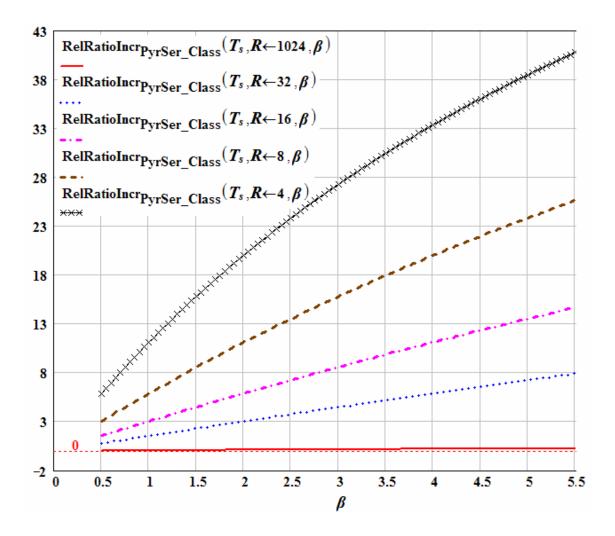

| Fig 4.21 Relative ratio of pyramidal imager rate (serial readout) over classical imager's        | 129 |

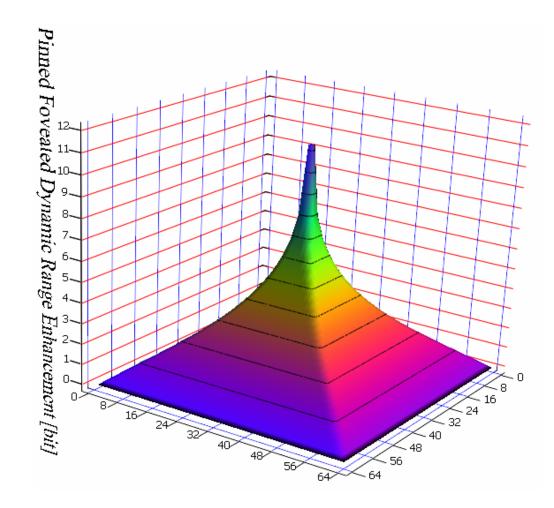

| Fig 4.22 3D view of the pinned FDR expressed in binary bits                                      | 135 |

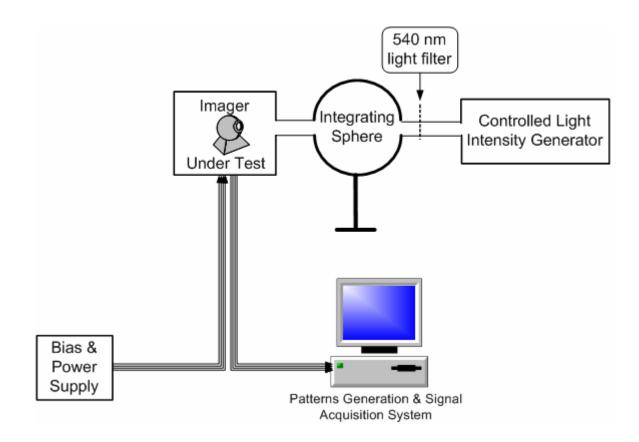

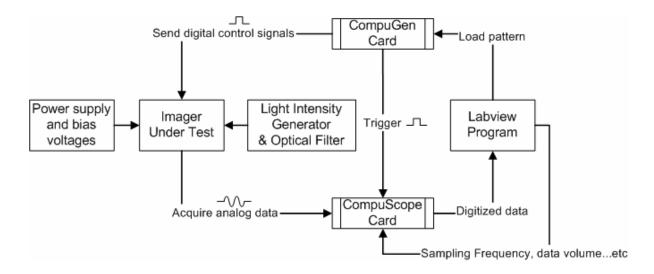

| Fig 5.1 Experimental setup for the characterization of Pyramidal CMOS imager                     | 138 |

| Fig 5.2 Software and hardware acquisition system                                                 | 140 |

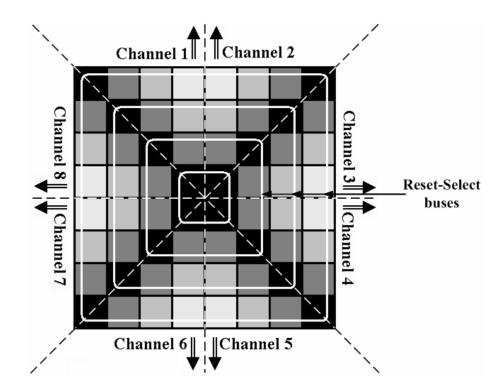

| Fig 5.3 Pyramidal imager segments and channels.                                                  | 141 |

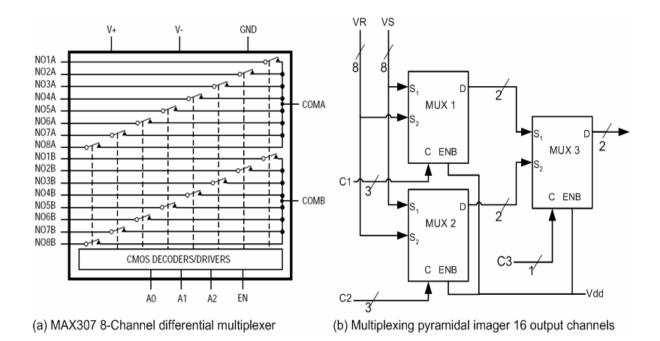

| Fig 5.4 Multiplexing pyramidal imager 16 output channels to 2 acquisition channels  | . 142 |

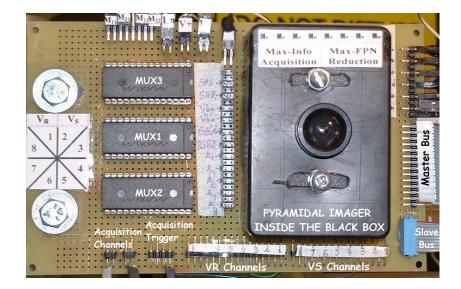

|-------------------------------------------------------------------------------------|-------|

| Fig 5.5 Board of the imager under test with the multiplexing implementation         | . 144 |

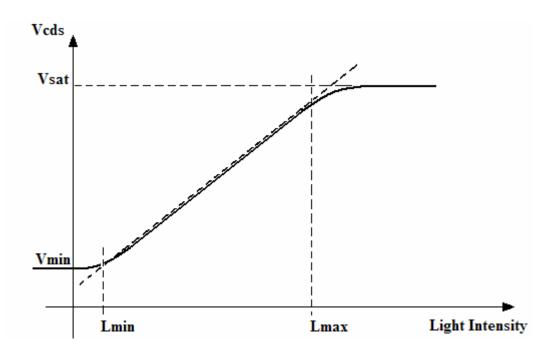

| Fig 5.6 Dynamic range extraction from light intensity transfer function             | . 145 |

| Fig 5.7 Sampled data structure in pyramidal and classical imagers                   | . 147 |

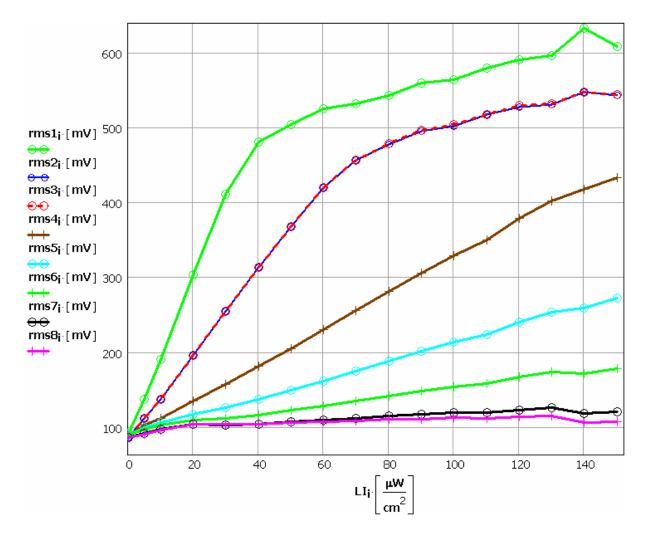

| Fig 5.8 Vcds in RMS voltage the whole pyramidal imager for 8 integration times      | . 148 |

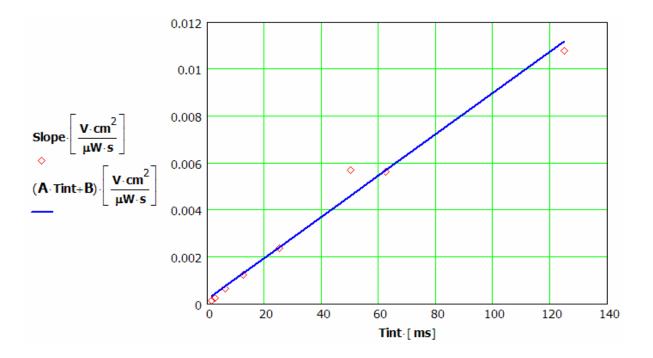

| Fig 5.9 Slopes of linear regions of photon transfer curve in Fig 5.8                | . 149 |

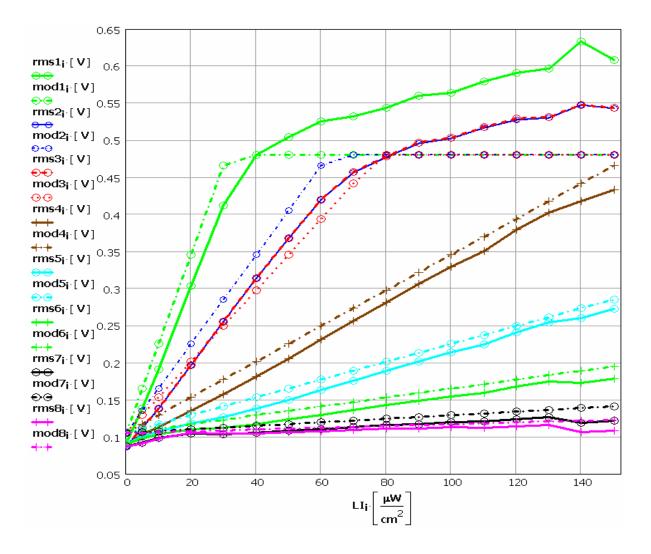

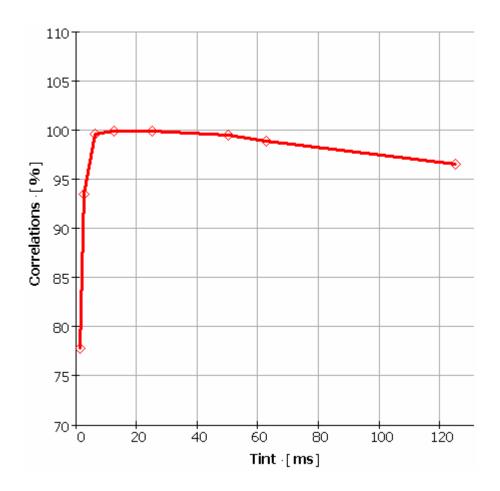

| Fig 5.10 Model plots and exact values of Vcds                                       | . 152 |

| Fig 5.11 Correlation between the model exact curves of Vcds versus integration time | . 153 |

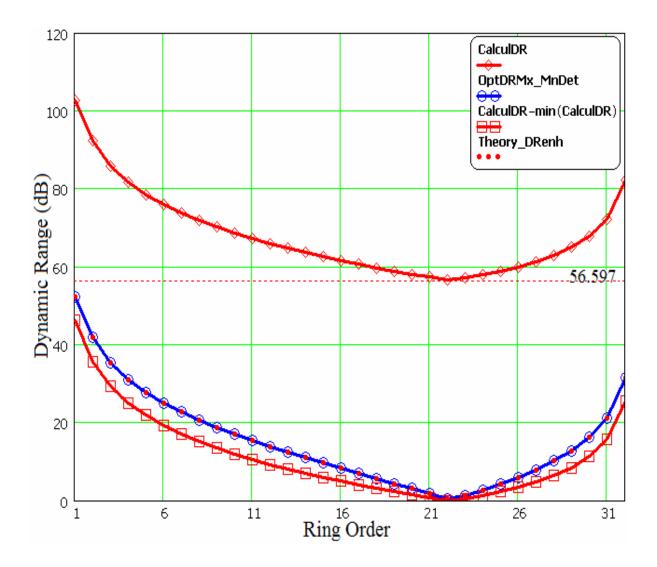

| Fig 5.12 The pyramidal imager system and enhancement dynamic ranges                 | . 155 |

| Fig 5.13 Demonstration of foveated dynamic range enhancement at the foveal rings    | . 157 |

| Fig 5.14. Manifestation of foveated dynamic range enhancement at the bouncing rings | . 158 |

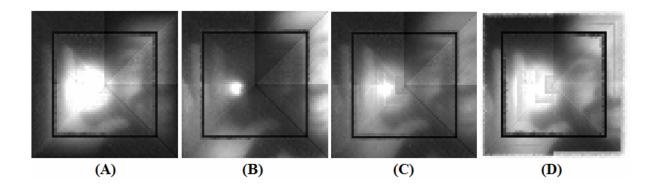

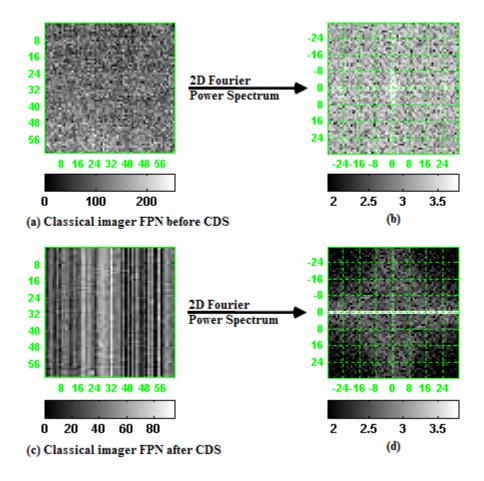

| Fig 6.1 FPN noise topology in classical CMOS imager sensor                          | . 163 |

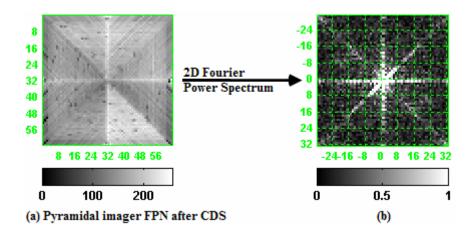

| Fig 6.2 FPN topology in a 64x64 pyramidal CMOS image sensor                         | . 165 |

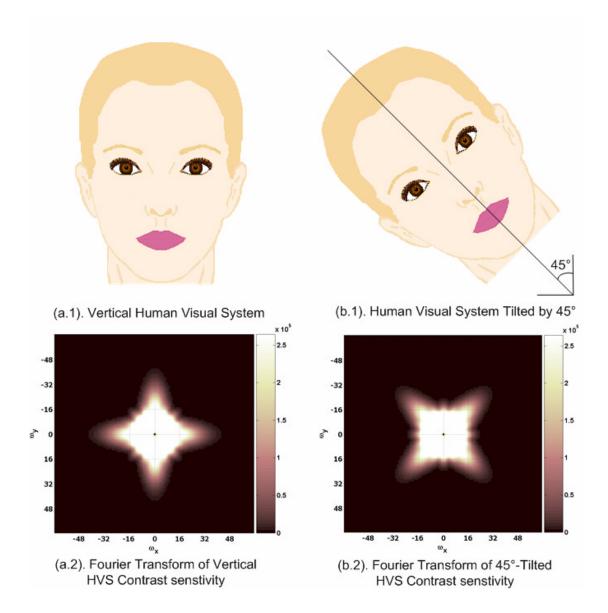

| Fig 6.3 Oblique effect in the human visual system                                   | . 166 |

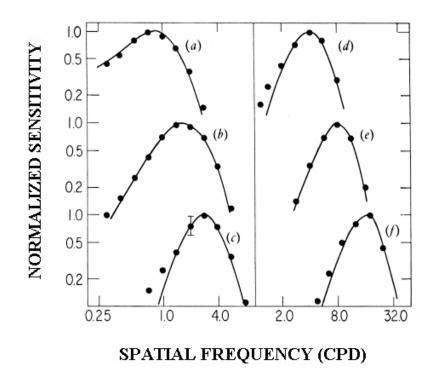

| Fig 6.4 The six human spatial pattern sensitivity filters [98]                      | . 167 |

| Fig 6.5. Average spatial power spectrum distribution of about 500 scenes [103]      | . 170 |

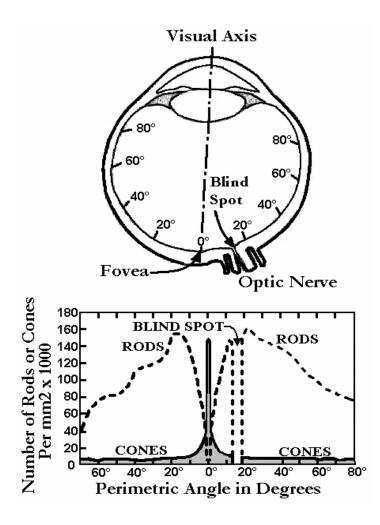

| Fig 6.6 The distribution of rods and cones photoreceptors in human eye [4]          | . 172 |

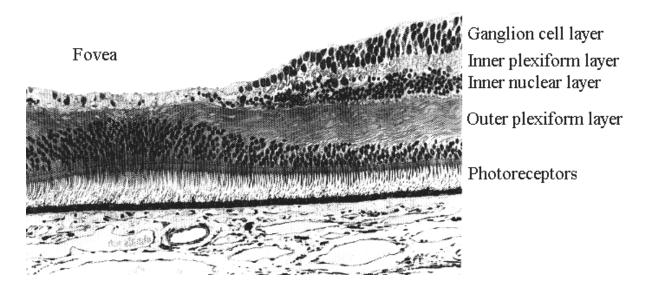

| Fig 6.7 Cross section of the human retina near the fovea region [4]                 | . 173 |

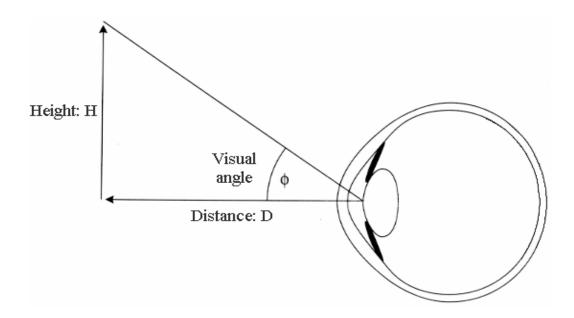

| Fig 6.8 Viewing angle calculation for image construction at the retina              | . 174 |

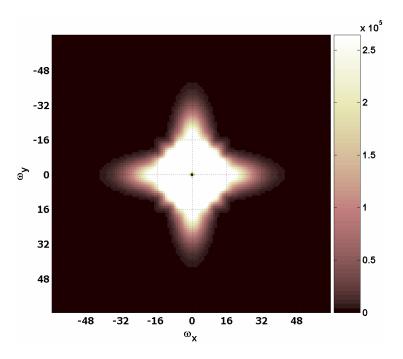

| Fig 6.9 Fourier spectrum of the constructed HVS spatial filter                      | . 175 |

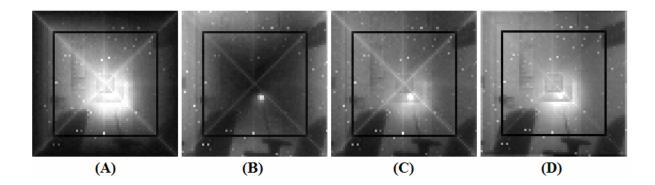

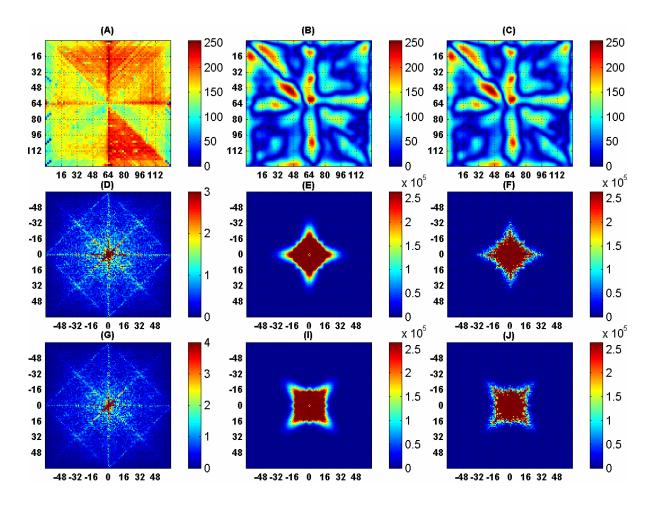

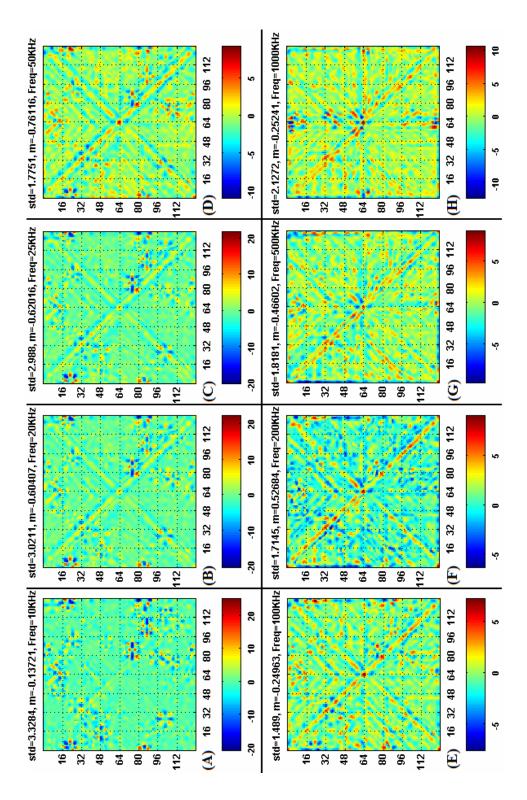

| Fig 6.10 Pyramidal FPN noise perception by HVS experiment                           | . 177 |

| Fig 6.11 HVS perception verification steps operations.             |  |

|--------------------------------------------------------------------|--|

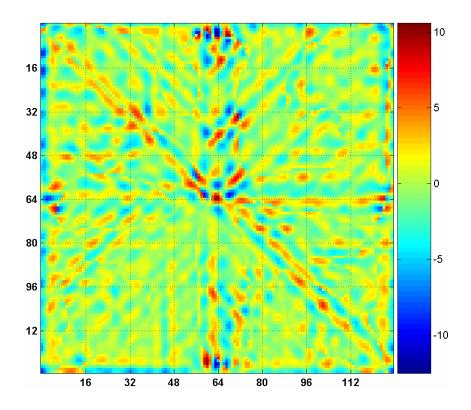

| Fig 6.12 The subtraction image of Fig 6.11.B from Fig 6.11.C.      |  |

| Fig 6.13 Frequency analysis of oblique FPN suppression by HVS      |  |

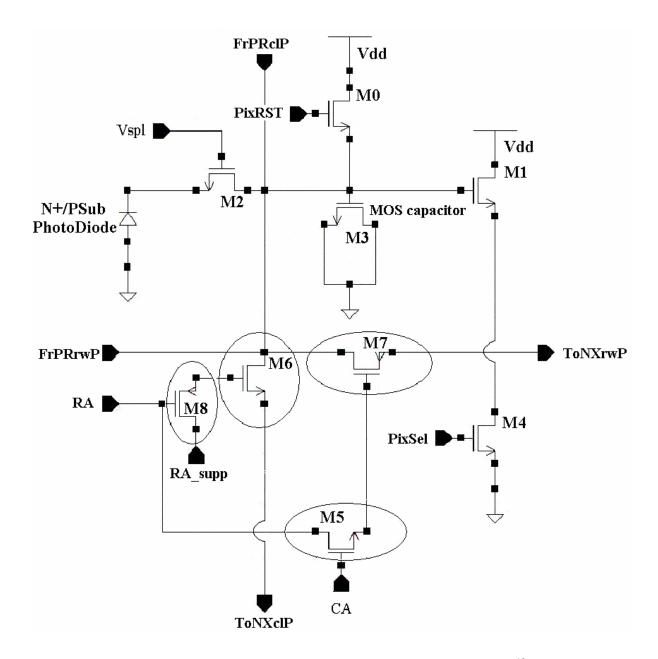

| Fig 7.1 Schematic of the proposed multiresolution pixel            |  |

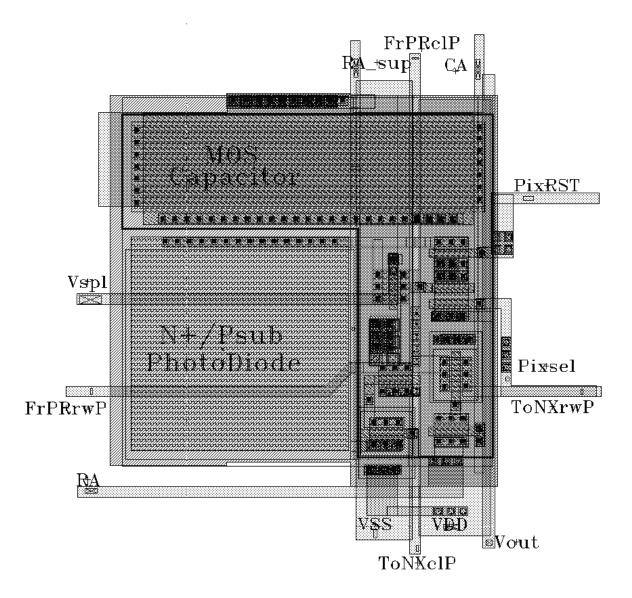

| Fig 7.2 Layout of the multiresolution pixel                        |  |

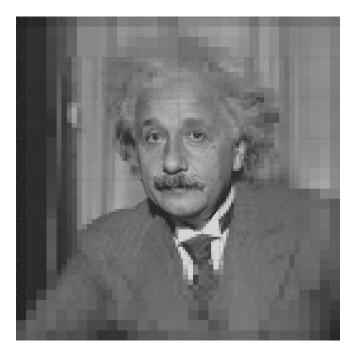

| Fig 7.3 A multiresolution image of centric foveation               |  |

| Fig 7.4 A multiresolution image of random foveation                |  |

| Fig 7.5 A multiresolution image with a horizontal kernel averaging |  |

| Fig 7.6 A multiresolution image with a vertical kernel averaging   |  |

## List of Tables

| Table 2-1 Graphical and functional slopes of SVE gamma correction aspect                 | 46  |

|------------------------------------------------------------------------------------------|-----|

| Table 3-1 Physical characteristics of the pyramidal pixel                                | 70  |

| Table 3-2 General characteristics of CMOS pyramidal imager                               | 82  |

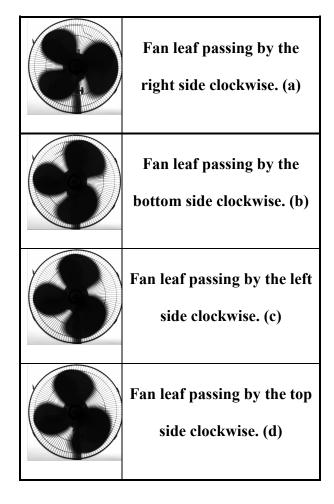

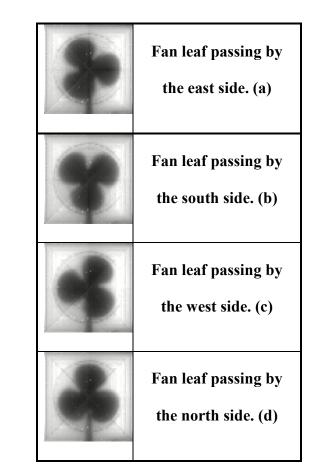

| Table 3-3 Standard CMOS image sensor raster scanning motion blur demonstration           | 88  |

| Table 3-4 Pyramidal CMOS image sensor ring scanning motion blur demonstration            | 91  |

| Table 6-1 Fitting parameters of the equation (6.1) for some fovea spatial filters [98] 1 | 68  |

| Table 7-1 Physical characteristics of the multiresolution pixel         1                | .89 |

#### **Chapter 1**

#### Introduction to CMOS Image Sensors

#### **1.1 Imaging Evolution**

It is interesting to follow the evolution of imaging technology from chemical imaging (using photographic film) to electronic imaging (using solid state sensors). Electronic imaging now encompasses two major imaging technologies: Charge-Coupled Device (CCD) imaging, which first appeared in the late 1960's [1], and Complementary Metal-Oxide-Semiconductor (CMOS) imaging, which has developed much attraction since the early 1990's [2]. CMOS imaging is an especially dynamic field of research and development, with advantages in development cost, ease of use and compatibility with surrounding technologies.

Historically, chemical, CCD and CMOS imaging technologies competed for dominance over imaging market share, without completely eliminating each other (as we can see still today film cameras on the market). This co-existence is mainly due to the different physical limitations (beside fabrication cost) of each imaging technology. CCDs, for example are well suited for low light imaging due to their superior low noise, whereas CMOS imagers perform better in high light imaging and integrated applications. These two major electronic imaging technologies will be further presented in the next section.

#### 1.1.1 CCD and CMOS Image Sensors

Both imaging technologies use silicon for light transduction into electrical voltage signals. However, their main difference lies in their sampling architectures. While CCD imaging is based on transporting the integrated photo charges from their pixel sites to the output amplifier (where they are converted into voltages), CMOS imagers (based mostly on Active Pixel Sensor APS) make the charge-to-voltage conversion at the pixel site. This difference is the source of all advantages and disadvantages that divide imaging applications between the two technologies. For example, this architectural difference has given CCD imagers better noise figure, both temporally and spatially (uniformity), making it the technology of choice for imaging applications sensitive to noise, such as astronomical imaging. On the other hand, the architecture of CMOS imagers provides them with sampling flexibility, random accessibility and high integration.

#### 1.1.2 Future Prospects and Trends

It is still unclear which of the two imaging technologies (if either) will dominate the market, although there are progressing signs that CMOS imagers are (and will in the near future) have the largest share due to their low power and architecture flexibility. However, CCD imaging will continue to find application due to its low noise, which makes it the best choice for high-quality imaging applications [3].

#### **1.2 Thesis Objectives**

The objectives of this thesis are presented by the following two statements, which comment on the unique performance or characteristic advantages that CMOS imaging technology has over CCDs, namely architectural flexibility and random accessibility. These features are used to address the two critical and related issues of sensor scanning and spatial sampling, as outlined in the philosophical statements below.

#### **1.2.1 Thesis Philosophical Statements**

#### 1.2.2 Scanning Statement

Image Scanning should be more adapted to image sampling/acquisition rather than image display compatibility.

Since the appearance of CCD (and later CMOS imaging), raster scanning has become the adopted scanning technique for sampling integrated images at the imager's focal plane. This is partly due to the lack of random accessibility in CCD imagers' architecture, and the compatibility with the widely used raster scanning technique of contemporary display monitors. The flexibility of CMOS imagers has not been fully utilized to optimize scanning, nor was exploited to enhance system capabilities.

The second philosophical statement we explored in the present thesis was more relevant to the future development of the CMOS image sensor. An important feature in any imaging technology is the achieved image resolution. As the image resolution becomes higher and higher, the amount of data transmitted from the imager to a display or an image processor becomes larger and larger. This will impact power consumption and limit the transmission of video signals. In this view we developed our second philosophical statement.

#### 1.2.3 Image Sampling Statement

As image resolutions increases and with it the amount of transmitted image data for display or processing, new architectures are needed for down-scaling the sampling resolution for regions of reduced interest. Innovative architectures are also needed to exploit the Human Visual System for transmitting only the most important regions in the acquired image.

In other words, as the amount of transmitted image data becomes higher, only selected data of interest, (regardless of resolution, dynamic range, or any other attribute), should be transmitted. This is similar to the strategy used in lossy compression algorithms, such as the Joint Photographic Experts Group (JPEG) format, that takes advantage of limitations in human vision to produce smaller image files [61].

#### **1.3 Thesis Motivations and Goals**

The main motivations behind the present thesis are to exploit the architectural flexibility of the CMOS imager, and to explore the possibilities it may offer. This intention is also influenced by the image processing needs of future imagers, as well as the possibility of embedding smart acquisition sampling architectures. Indeed, future imagers are likely to have higher resolutions and higher frame rates, so smart architectures that can minimize the amount of sampled data while maximizing the amount of information would be desirable. Such vision systems are found in biological vision systems, such as human vision, where the spatial sampling is not uniform and yet the system has sharp vision and adaptability to various light intensities and spatial frequency patterns [4]. Finally, we note that, in order to be adopted for future CMOS imaging development, such novel architectures should conform as much as possible to certain principal features and not to be just *ad hoc* designs. These key characteristics are:

Expandability: refers to the lack of increase in complexity when increasing imager size. This means that the suggested architecture is not limited by the size of the imager.

Programmability: refers to the fact that the imager's functionality during sampling of the integrated image should be programmable (controllable) and flexible.

#### **1.4 Contributions**

In the context of the motivations mentioned above, a number of contributions have been achieved in this work in two principal themes:

Two-dimensional scanning: We have developed a new and practical architecture based on a standard array of pixels, in which the rows of the classical CMOS image sensor are replaced by rings, and orthogonal output buses by diagonals. The asymmetric information acquisition inherent in raster scanning is thereby replaced by a two-dimensional symmetric image

sampling. It is shown that distortion of moving objects is significantly reduced using this scheme. A new scanning scheme, called bouncing scanning, has also been demonstrated to realize the two integration time profiles for each ring. Fusing the two frames results in a foveated dynamic range (FDR) enhancement. Lastly, it is shown that the dominant form of fixed pattern noise in CMOS image sensors (columnar variations) are perceived less by human observers in the new sensor owing to the diagonal arrangement of the output buses. Multiresolution CMOS imager: In this architecture the multiresolution approach is implemented on-pixel. Beside sampling and holding the integrated photo charge, each pixel can share charge with neighbouring pixels (given the proper control signals). This charge sharing allows a decrease in resolution on regions of less interest, while maintaining maximum resolution in regions of interest (ROI) where the charge sharing is disabled. Since the multiresolution mechanism (using the charge sharing concept) is implemented at the pixel level, the proposed scheme guarantees most of the requested characteristics discussed in the

motivation section. This architecture is presented and discussed in Chapter 7.

#### 1.5 Thesis Organization

CMOS imaging technology is reviewed in Chapter 2, with a focus on image acquisition processes beside our approach in implementing new imaging architectures and their fields of application. Subsequently, the system-level pyramidal architecture design is discussed in Chapter 3. The suggested scanning scheme, supported by the pyramidal architecture and known as the bouncing scanning, is also introduced in this chapter, together with its implications (particularly the foveated dynamic range). The theoretical framework of the

foveated dynamic range is analyzed mathematically in Chapter 4 before being experimentally verified in Chapter 5, which includes testing and characterization results. The discussion of the pyramidal CMOS imager concludes in Chapter 6 by verifying the reduced perception of the pyramidal imager's Fixed Pattern Noise (FPN) noise when viewed by human observer. The implementation and layout of the pixel-based Multiresolution CMOS imager are presented in Chapter 7 before the concluding remarks made in Chapter 8.

### **Chapter 2**

### **Background: CMOS imagers and Spatial Sampling**

In this chapter we will review some architectures used in CMOS imagers for spatial sampling and other objectives, such as dynamic range enhancement and high frame rate. This study will help us subsequently to locate where our suggested approach fits within the established framework, what it contributes to this research field and finally to be able to suggest the future trends for CMOS imager development. Before proceeding with the architectural aspect of APS CMOS image sensors, a short introduction of CMOS imaging technology along with some of its main characteristics is presented.

#### 2.1 Introduction to CMOS Image Sensors

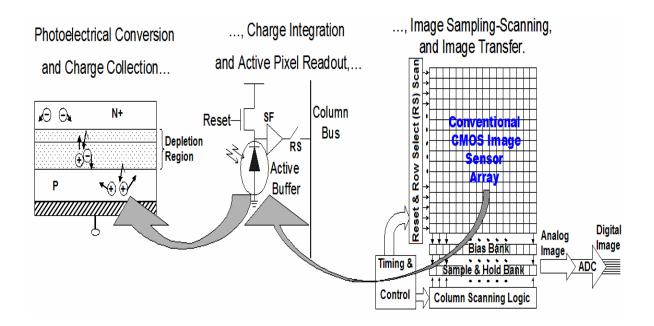

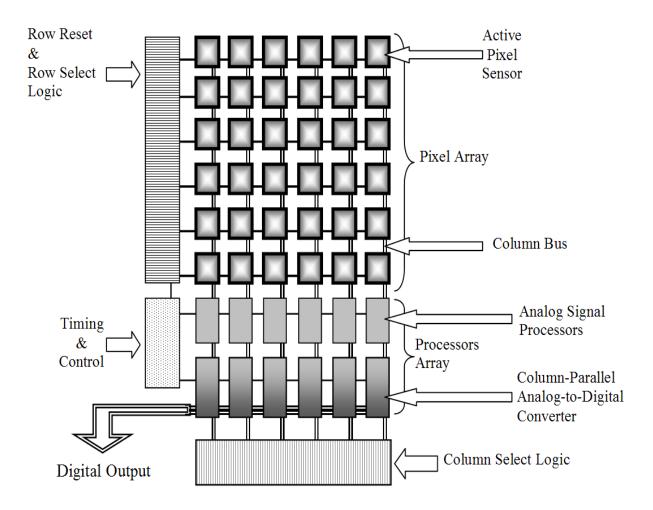

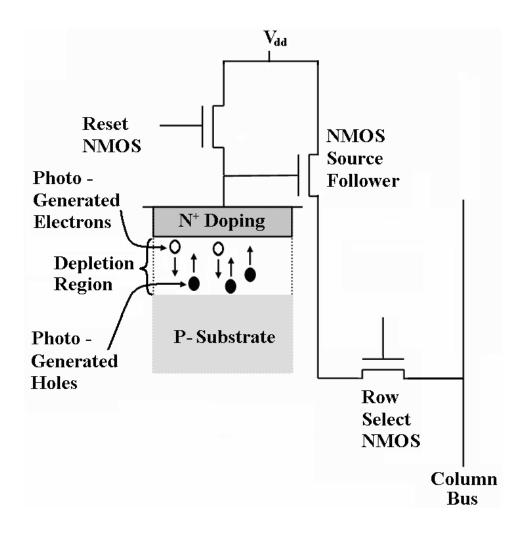

Fig 2.1 shows the construction of a typical CMOS image sensor, from the light sensing photodiode to the focal plane pixel active pixel sensor (APS) and finally the sampling architecture. Initially, the photodiode is reset to a relatively large reverse bias. Photo-electrons are generated both in the photodiode depletion region, from which they then drift towards the diffusion areas, and in the bulk, from which they diffuse towards the photodiode. The photo-generated electrons discharge the photodiode at a rate that is approximately proportional to the incident illumination. Pixels are later reset by row reset logic during the image sampling. Further details of this process are presented in Chapter 3.

Fig 2.1 From photodiode to CMOS image sensor

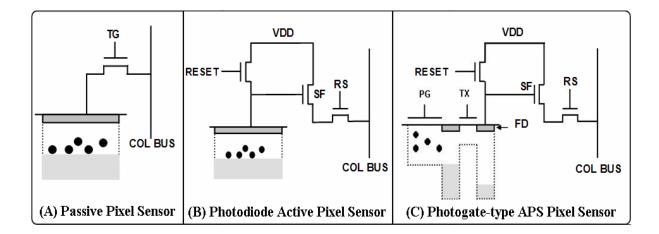

The main three types of photodiode pixels widely used in CMOS image sensors technology are shown in Fig 2.2 and are discussed below.

Fig 2.2 The different types of CMOS imaging pixels

#### 2.1.1 Passive Pixel Sensor (PPS)

Fig 2.2.A shows the simplest and earliest (1967) MOS pixel type [5], built simply of a photodiode and a charge-transfer transistor used as a switch. Functionally simple, the passive pixel sensor integrates the light at the active region; the photo-generated charge is then transferred to the column bus *passively* through a transfer gate, simply a MOS switch. The column bus (COL BUS) is connected to a charge amplifier that keeps it at a constant voltage level. When the Transfer Gate (TG) is activated the charge of the photo-diode is transferred through the bus to the column charge amplifier which itself transduces it to the subsequent processing elements such as Analog-to-Digital Converter ADC or Correlated Double Sampling CDS.

Two main problems are attributed to this type of pixels: readout noise due the charge sharing between TG transistor and column bus, and the scalability due to the increased bus capacitance. While the Quantum efficiency of the pixel (ratio of collected electrons to incident photons) of the passive pixel sensor is much higher than that of the CCDs due to its high fill factor and the absence of overlaying layers, it has the read noise of 250 electrons rms compared with typical value of less than 20 electrons rms found in CCDs [6].

#### 2.1.2 Photodiode Active Pixel Sensor

The Active pixel sensor as shown in Fig 2.2.B was firstly suggested by Noble [7] and later investigated further by Andoh at NHK, Japan [8]. The pixel is initially reset to VDD, then after some time, its output is read out through the source follower (SF) transistor in order to generate significant pixel output voltage with larger dynamic range. The readout is

performed through the row select (RS) transistor, which transfers the photo-generated voltage to the column bus. Although its fill factor (ratio of light sensitive to the pixel area) is less than that of the PPS sensor in the range of 20%-30%, it is the most used pixel in research as well as industry. This is due primarily to its low noise (less than 20 electrons rms), higher signal to noise ratio and scalability.

Finally, it is worthy to mention that the photodiode APS noise performance improves as the size of the pixel shrinks down since the reset noise scales as  $C^{1/2}$ , where *C* is the photodiode capacitance [9]. However, other counter effects emerge such as decreasing fill factor and sensitivity as the pixel sizes shrinks-down [10].

#### 2.1.3 Photogate Active Pixel Sensor

The photogate APS was introduced first time by JPL in 1993 [11] for high-performance scientific imaging and low light applications. The principal structure of the photogate-active pixel sensor is based on the integration of the photo-generated carriers in the potential well, which is created by applying a large positive voltage to that gate in similar manner with CCD technology. Fig 2.2.C shows the structure of this kind of CCD-like active pixel photosensor. For readout, the output floating diffusion (FD) is reset and its resultant voltage is measured by the source-follower. The photo-generated charge is transferred to the output diffusion by pulsing the photogate. The new voltage is then sensed. The difference between the reset level and the signal level is the output of the sensor. This correlated double sampling suppresses reset noise, 1/*f* noise, and Fixed Pattern Noise (FPN) due to threshold voltage variations. Although this pixel structure has the lowest noise compared to the previous ones (13

electrons rms [12]), it suffers from the reduction of quantum efficiency, particularly in the blue due to the overlaying polysilicon photogate, beside its higher operational complexity and reduced fill factor.

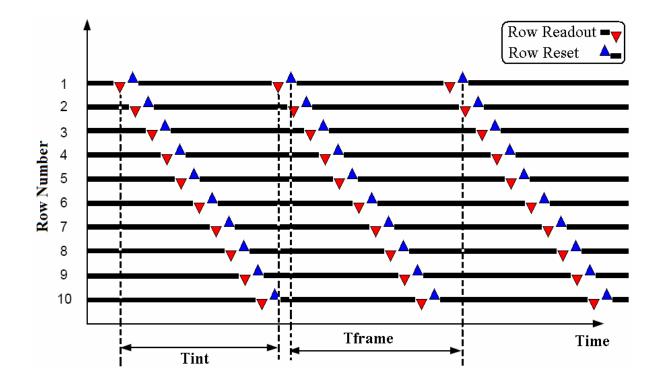

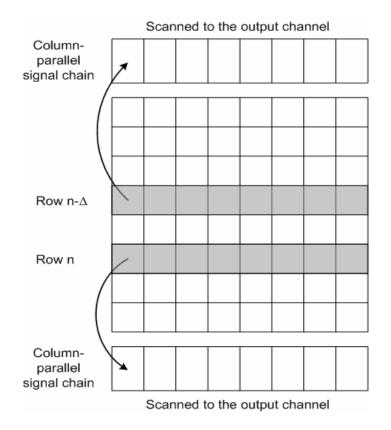

#### 2.1.4 Integration Time & Raster Scanning

In the classical CMOS image sensor architecture, raster scanning was adopted to sample the image at the focal plane. Raster scanning was originally implemented for displaying video images in cathode ray tubes (CRTs), and was later adopted to be the scanning scheme for early solid-state imagers [13] in order to maintain compatibility between acquisition and display systems. This reason is the cause of the statement put forward in section 1.2.2 to propose the new pyramidal sensor with 2-D ring scanning that will be discussed further in section 3.5.8. In raster scanning, the integrated image is sampled row by row, from the first top row until the last bottom row after which the scanning is back to the first row and so on. Because the pixel needs to be reset prior to light integration, every row has to be reset after being read out. The readout is made by sampling the row voltages to a sample and hold bank of capacitors, then the row is reset and sampled again but to another set of sample and hold bank of capacitors, then the same process is repeated for the next row and so on as shown in Fig 2.3. It should be noted that after sampling the row photo and reset signals into their corresponding sampling capacitor banks, the sampled voltages are serially buffered out before proceeding to the next row. Integration time is the time between two successive reset and readout events corresponding to the lapsed time to discharge the reverse-biased (reset) photodiode as a result of light integration. Because of the periodicity of raster scanning, pixel integration time *Tint* is equal to the frame sampling time *Tframe*, unless other techniques such as the rolling shutter<sup>1</sup>, are used. We note here that the raster scan results in a scene update rate that is faster in the column direction than it is in row direction, potentially resulting in spatial distortion in the image capture of moving objects.

Fig 2.3 Pixel frame integration time in raster scanning

<sup>&</sup>lt;sup>1</sup> In the rolling shutter scan, the readout (photo signal sampling) signal is applied ahead (by a number of rows) of the reset signal. The number of the separation rows defines a window that its integration time plays the same role of *Tframe* in the raster scan.

#### 2.1.5 Correlated Double Sampling CDS

The reason behind sampling both photo signal and the reset signal of every pixel, is to reduce residual noise at every pixel by subtracting the photo signal from the reset signal. This technique called correlated double sampling (CDS) was originally invented to process CCD imager video signals to enhance the signal to noise ratio [14] by minimizing principally the reset noise. In general, all correlated spatial noise sources such as the spatial dark current source due to a crystal dislocation at the pixel level are cancelled out (or removed) using CDS as they are present in both the photo signal and the reset signal. The KTC noise related to the reset process (also called reset noise), however, is not removable by CDS in CMOS APS imager whereas it is completely removable in CCD imagers. The reason is the fact that in a CCD the output noise node is reset prior to photo signal transfer and hence both signals are 100% correlated which makes CDS the solution. In CMOS imagers, on the other hand, the photo signal is read first then the reset signal, and thus the reset noise present in the present photo signal is not correlated with the present noise present in the reset signal (but correlated with the previous frame's reset signal). That is why the CDS technique used in CMOS APS imagers is not a "true" CDS which explains why it is sometimes referred as just double sampling (DS) [15]. Furthermore, noise can also be added by this technique and some of the causes of this addition of noise are discussed in Chapter 6.

#### 2.1.6 Fixed Pattern Noise (FPN)

Fixed pattern noise (FPN) is the spatial noise distribution with no illumination of the image sensor array that is explicitly time independent, and hence "fixed". This noise is due to two

types of mismatch between the photo-signals; photo-signal generation mismatch and the photo-signal transportation mismatch.

The photo signal mismatch is due to the variation of the photo-sensing areas related to process variation and photo-mask errors found also in CCD manufacturing [16], and to mismatched dark currents. The dark current is the accumulation of electrical charge in the photodiode from electron-hole pairs that are generated independent of the photo-detection process. The primary sources of this are impurities or lattice defects in the silicon substrate. Because these defects are localized, the dark current is different for each pixel, leading to a fixed pattern noise in the image resembling a starry sky or a dirty window in a dark image at long integration times [17].

Therefore, if we have to classify the sources of the FPN we can categorize them in two: (i) local impurities and silicon crystal imperfections, and (ii) the different paths taken by the signals during readout. CCD does not suffer so much from FPN partly because its high quality silicon substrate is built on for high transfer efficiency requirement as compared with commercially lower quality (and cheaper) CMOS substrate disks. The other principal reason of CCD imagers' relative immunity to FPN compared with CMOS counterparts is because the latter have charge-voltage conversion at every pixel whereas the former have a unique conversion node for all of its pixels. The topological distribution of the FPN noise is further analyzed in section 6.2.

#### 2.2 Non Raster Scanning (Sampling) CMOS Imagers

It is rather interesting to examine the meaning development of the word "scan" [18]. The source of the word "scan" came from the Latin word "scandere" that means "to climb" and which is used in this sense in "scanning a verse of poetry", because one could beat the rhythm by tapping one's foot. The Middle English verb "scannen" is, in this sense, derived from the Latin word "scandere". Later in the 16<sup>th</sup> century other senses of "scan" have been developed towards the sense of "looking at searchingly" (first recoded in later 1798 [18]). With further developments, "scan" eventually broadened to include looking over a surface with or without close scrutiny of details reaching the modern usage of "scan" that means "look over quickly". Therefore, "scan" includes both pattern and speed of the search in addition to resolution (scrutiny degree).

On the technical side, raster scanning was originally proposed for Cathode Ray Tube (CRT) displays using the electrical and magnetic fields influence on a finely focused accelerated electron beam "scanning" its fall on a phosphorescent screen (that emits light on the fall points) for information display purpose. The pattern of the raster scan looks exactly as the scan of poetry passages, namely line by line. The first cathode ray tube scanning device was invented by the German scientist Karl Ferdinand Braun in 1897. Braun introduced a CRT with a fluorescent screen, known as the cathode ray oscilloscope [19]. This method of display was later adopted to be the scanning scheme for early solid-state imagers [20] in order to maintain compatibility between acquisition and display systems in addition to its simplicity in storing and transmitting image data. The raster scan is also the scan of choice in image

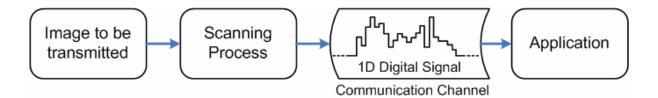

readout at high speed rates since it minimizes discontinuities in reading the image rows, therefore increasing frame rate and thereby reducing motion artifacts such as motion blur. Recall that the integration time is the discharging period spent between the reset and the readout of pixel's photodiode. Consequently, and because high speed imaging is one of the merits of CMOS imagers, few attempts have been tried to deviate from this fundamental image scanning to a more complex scanning patterns. One of these attempts suggests scan patterns such as the Space Filling Curves (SFC) families [21] namely the Morton (Z) and Peano-Hilbert curves [22] for fast and efficient mean computation of 2x2, 4x4 kernels dedicated mainly for multiresolution imaging. The SFC scanning patterns are essentially fractal scan patterns that have the ability to scan the whole 2D image pixels (without missing one) and thus achieve the space filling property. Due to their inherently strong locality property<sup>2</sup>, SFCs in general and Peano-Hilbert curves in particular are useful in exploiting the spatial coherence of nearby pixels which is very useful for image compression (lossless or lossy) [23][24] or pattern recognition [25]. To realize these applications (and others such as halftoning...etc), the image is scanned using an SFC scan generating a sequence of data which is transmitted through a communication channel before being processed by an application, as depicted in Fig 2.4. Using the same SFC scan map the resulting image is reconstructed.

<sup>&</sup>lt;sup>2</sup> Due to the recursive nature of the SFC, neighbouring pixels are traversed before moving to more distant ones.

Fig 2.4 The scanning process framework

Thus far, SFC based scanning was considered mainly for the processing applications and the communication bandwidth needs, rather than image sampling requirements, which make these scanning techniques vulnerable to motion and lighting artefacts. Thus, the implementation in [22] will suffer greatly from these sampling conditions beside its intensive use of wiring which, in addition to its low fill factor (15%), will make the suggested CMOS imager a "light starved" design [26], mainly due to the vignetting phenomenon [27]. In reality, the initial attempt in the implementation of mechanisms allowing flexible scanning was suggested originally in [28] by using individual reset scheme as shown in Fig 2.5.

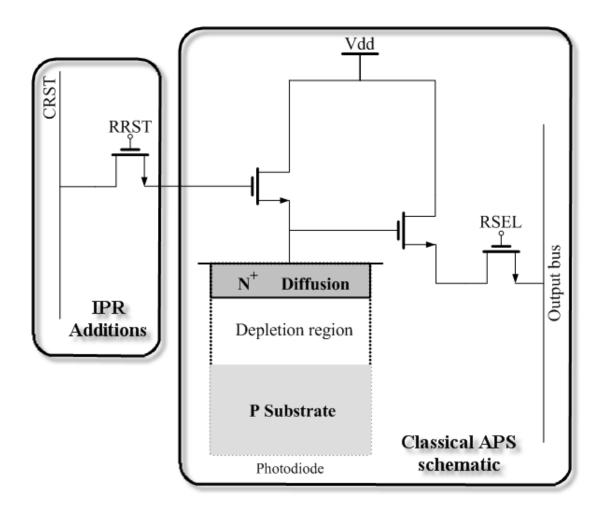

Fig 2.5 Individual pixel reset APS

Using vertical reset (CRST: column reset) and horizontal reset (RRST: row reset) signals the random reset is possible to implement. The main drawback of the approach is the  $V_{th}$  drop sensed at the gate of the APS pixel reset transistor, beside the fill factor decrease as a result of adding an extra transistor. The major drawback can be overcome by using hard reset technique in which the RRST gate voltage uses  $V_{dd} + V_{th}$  instead of  $V_{dd}$  when enabled. One may suggest the use of PMOS reset transistor instead of NMOS. However, this technique

reduces the fill factor due to the n-well and larger size required for the reset PMOS transistor (due to lower hole mobility). Fully realising the random accessibility requires storing the sampled photo charge locally inside each pixel using a capacitor and a shutter (switch) between it and the photodiode [29]. Combining the two previous pixel architectures, any pixel can be reset individually as well as readout multiple times (without destroying the sampled image information). Again, the fill factor is an issue as the number of transistors inside each pixel increases. However, this may be solved in the future with CMOS technology scaling.

Another scanning approach suggested integrating motion detection circuitry beside ADC conversion at the pixel level in order to implement a quad-tree scan scheme. This avoids the redundant cycles<sup>3</sup> of raster scanning [30], thus minimizing energy consumption and increasing frame rate especially for high resolution imagers. Quad (means 4 members)-trees<sup>4</sup> [32] are most often used to partition a two dimensional space by recursively subdividing it into four quadrants, and it was primarily proposed for database searches [31]. This technique has been therefore borrowed from graph theory in order to replace raster scanning so that only active pixels (determined by the motion detection module inside the pixel) are read by jumping from one level to another searching for active nodes. The main drawbacks of this technique are the very large pixel pitch (96  $\mu$ m) and the very low fill factor (3.2%). However,

<sup>&</sup>lt;sup>3</sup> Redundancy in this sense refers to the sampling of pixels that do not change between frames (non active).

<sup>&</sup>lt;sup>4</sup> Trees in this context are graph theory constructs and are graphs in which any two vertices are connected by exactly one path

the attempt target is definitely worth it in the future development of CMOS imagers especially with their inherent architectural flexibility advantage (over CCDs) especially with increasing image resolutions and high frame rate requirements.

# 2.3 Our Approach for Image Sampling

Visions systems found in mammals in general outperform by far silicon based image sensors, not only due to their analog yet stable and powerful signal processing cells at both the sensing site and the neuronal processing layers, but also due to their hierarchical organization. Many attempts have been made to mimic the image processing capabilities of the biological vision systems<sup>5</sup> [33], however, few attempts have been made to investigate the power and influence of sampling architectures on the vision performance. Furthermore, as CMOS imaging technology offers the ability to design complex architectures, as compared to CCDs, a small but increasing number of imagers are designed to test novel CMOS image sensor architectures. Our implementations described in this thesis are an example of this trend of CMOS imagers' development.

In designing novel CMOS imaging architectures, we focus on parallelism and symmetry in order to achieve high speed imaging without much expense in terms of hardware and power. Using this architectural view in image sampling we can implement our goal in building an optimized CMOS imaging solution that minimizes the sampled data while maximizing sampled image information. This is indeed one of the major goals for ever- increasing image

<sup>&</sup>lt;sup>5</sup> Vision systems are imaging based applications encompassing image processing to mimic partly human vision.

resolution and high speed transmission needs for future CMOS imagers for a wide range of imaging applications from scientific remote imaging to military object tracking.

# 2.4 Biological Vision

In this section a qualitative description of the biological vision in general and human vision in particular will be presented. Our interest in this section is to highlight some of the powerful mechanisms characterising human vision making it a 'smart' vision. It is beyond the scope of this section to demonstrate all the vision capabilities of human visual system, but only selective properties will be shown as they may be mimicked in our CMOS imagers [34]. To narrow further the scope of human vision analysis, only the retina where the focal plan image is being spatially sampled is considered [35].

## 2.4.1 Spatial Sampling

*The retina* is the innermost layer of the human eye which contains light-sensitive photoreceptors and their associated neural tissue. There are two kinds of photoreceptors: rods (intensity-resolving) and cones (colour-resolving). Their distribution is further detailed in section 6.4.3 which principally shows the non-uniformity of the sampling architecture of the retina. Finally, it is worth mentioning the roughly circular distribution of the photoreceptors around the central region known as fovea which perfectly coincides with the optical axis of eye's lens [4].

*The plexiform* layer is an intermediate interconnection layer that connects between photocells and ganglion cells whose axons (neuronal communication extensions) make up the fibers of

the optic nerve before reaching the brain visual cortex. Without getting into details of this complex layer, this layer serve many visual functions especially visual resolution where it maps foveal cones (no rod cells are in the fovea) individually to ganglion cells whereas rods are grouped through specific neuron cells before being connected to ganglion cells. This explains why the fovea region of the retina has higher spatial resolution than its periphery. Retinal *ganglion* cells are neurons responsible for converting chemical signals received from the photocells (cones and rods) into electrical firing pulses to be sent to the visual cortex at the brain visual cortex.

It is clearly visible from this short description that the human biological visual system, at least at the spatial sampling level, has great deal of architectural organization allowing it to maximize image sampling in one area (fovea) while keeping it low in other retinal areas. The second important point to notice is the interconnection between the sampling photocells through the *plexiform* [4] enabling the visual system to perform intelligent tasks such as extracting edges and reducing resolution. The first task is performed in the fovea region by the cone photocells and the second is realized by the peripheral rod photocells for motion detection [36]. Both of these two facts may have a great potential influence on future development of CMOS image sensors with their architectural flexibility. In fact in the present thesis the first observation mentioned herein was exploited to design a central foveated architecture called the pyramidal architecture while the second was mainly utilised in designing the multiresolution CMOS image sensor discussed further in Chapter 7.

## 2.5 Previous Foveated Vision CMOS imagers

Spatial resolution is directly related to the size of the pixel with respect to the system optics, which characterizes the detection of fine details of the sensed image, but often simply refers to the number of pixels of the acquisition or display device. However, the frame-scanning rate, data transfer bandwidth as well as power consumption and sensitivity are also key requirements for higher resolutions. Another factor, namely the limitation of the optical system, also plays an important role in determining the usefulness of high-resolution image sensors. It has been claimed that pixels of sizes much below 5µm pitch are not needed because of the diffraction limit of the camera lenses typically used in consumer cameras [37]. Furthermore, for a given technology (CMOS 0.35um), it has been shown [38] that dynamic range and signal-to-noise ratio (SNR) degrades with the decrease of the pixel size in a square root form. On the other hand, smaller pixel sizes increase the spatial resolution by increasing the Nyquist-limit spatial frequency, defined as the half of reciprocal of the center-to-center pixel spacing. Besides, the Modulation Transfer Function MTF that characterizes the ability of the imaging system (CMOS imager in this case), to output the sharpest form of the acquired image<sup>6</sup>, is higher for smaller pixel sizes. Consequently, the optimal pixel size is a trade-off between the above conflicting parameters and a given application requirement.

<sup>&</sup>lt;sup>6</sup> The MTF function is defined as the normalized contrast amplitude response of the retransmission (imaging) system, as a function of the spatial frequency, below the Nyquist limit.

Other alternatives have been suggested to enhance the CMOS image sensor resolution by using different architectures while keeping the above-mentioned key-parameters in mind. These new architectures are developed in the following section.

#### 2.5.1 Foveated CMOS Image Sensor

Biologically speaking, the fovea is the region of highest visual acuity in the human phototransducing retina [4]. It contains no rod cells, which are more sensitive to low light intensities, but contains the highest concentration of cones, which detect colors. This explains why we cannot see very dim sources, such as weak starlight, when we look straight at them. The dim source only becomes visible when it is placed in the periphery and can be detected by the rods. Finally, it is worth mentioning that the dense representation of the foveal cones suggests that the spatial sampling of the cones must be an important aspect of the visual encoding [4]. This explains why humans vision declines (in spatial resolution power) away from the direction of gaze.

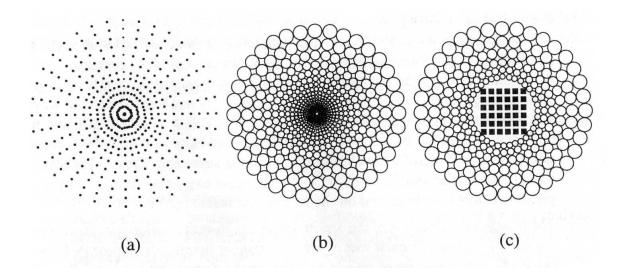

From the CMOS hardware implementation point-of-view, different strategies have been suggested in the literature [33]. Fig 2.6 shows some implemented CMOS image sensors adopting the spatial fovea-distributed pixel mapping such as linear-polar sensor (a), log-polar sensor (b) and log-polar with Cartesian center CMOS image sensor (c).

Fig 2.6 Polar foveated CMOS image sensors [33]

The above-mentioned image sensors are able to map the Cartesian two-dimensional image to polar (circular) (a, b), or mixed coordination (c), facilitating therefore some image processing operations such as scaling and rotation invariance assuming the origin at the center of the fovea. These processing operations are simply implemented with a simple shift operation in the angular axis or the radial axis respectively. Foveated imaging is achieved through the high sensor density near the central part of the image sensor, although in practice the number of pixels in fovea region rings is usually fewer than that of the outer rings due to the finite physical size limits. A significant problem with this type of foveated sensor was the difficulty of forming an acceptable colour image at the low pixel densities in the periphery. Another approach using rectilinear pixels for the implementation of foveated CMOS image sensor was reported recently [39] and is shown in Fig 2.7. It uses the standard CMOS process and

adopts the concept of photo-charge normalization in order to use the same charge amplifier with the different pixels sizes and therefore displays a wide dynamic range response to the incoming light. A drawback of this architecture is the complexity of the synchronization circuitry needed to scan the different image sensor rings.

Fig 2.7 All CMOS rectilinear foveal image sensor

Interestingly enough, important properties of such biologically inspired image sensor, namely the fast frame (scanning), wide field of view (FOV) and high resolution continue to drive interest on this kind of image sensors in low-vision enhancement, communication and target tracking applications. The product of these parameters defines the so-called metric of visual information acquisition power. In a foveal system, the metric is computed as the product of the peripheral field of view, the spatial resolution at the fovea, and the overall frame rate.

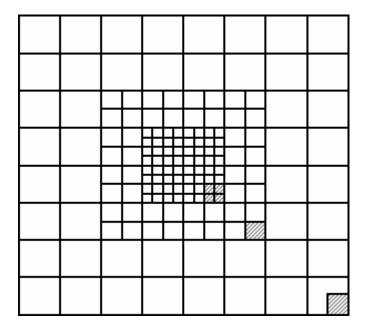

# 2.5.2 Multi-Resolution CMOS Image sensors

Resolution was one of the most important competing factors between CCD technology and CMOS technology for the development of high definition image sensors. Although the CCD image sensor has attained higher resolutions, the present and future development of CMOS technology is leading to smaller and smaller pixel sizes, potentially overcoming the CCD lead. Furthermore, the CMOS ability to add processing elements at the pixel level, column level and at chip level, is adding an impetus in the race to higher imaging performances. Benefiting from this capability, CMOS image sensor can obtain multiple resolutions, and together with their addressability, an electronic zoom capability is achieved [40]. The suggested pixel neighbourhood averaging scheme in [40] (in row and column) is realised at the column level. This averaging mechanism is implemented by using switch capacitors and by using shift registers to control the required resolution i.e. number or averaged rows and columns as shown by Fig 2.8. A dual approach to the previous multiresolution scheme is suggested but, instead of voltage averaging, a current averaging strategy has been adopted [41] and a new scheme for current-mode Correlated Double Sampling (CDS) circuitry is proposed. The applications of multiple resolution image sensors are very wide especially in real world systems that impose some constraints such as format choices, processing speed, and bandwidth such as data reduction, robotics and target tracking.

Fig 2.8 Programmable multiresolution CMOS active pixel sensor architecture

## 2.6 Dynamic Range Enhancement Techniques

Dynamic range (DR) is a term widely used in many fields to describe the ratio of the largest measurable or detectable value (of interest) to the smallest value. In imaging systems, the physical measure of interest is obviously light intensity of the sampled image. In CMOS or CCD image sensors, dynamic range is one of their most significant characteristics because it describes their ability to sample bright and dim areas of a sampled scene within one frame. The minimum detectable light intensity is the intensity that would create an electrical signal enough to equal the noise floor of the imaging device. Another definition of dynamic range is ratio of the voltage saturation level to the readout noise. Because it uses electrical parameters it is referred as the electrical dynamic range and given that the (optical) dynamic range is measured in the linear response of the CMOS image sensors, the electrical dynamic range is equal to the optical dynamic range (although this distinction is important for non-linear devices, such as the logarithmic pixel mentioned in section 2.6.1).

While natural scenes have a very wide dynamic range from illuminations of 10<sup>-3</sup> lux<sup>7</sup> for night vision to illuminations of 10<sup>5</sup> lux for bright sunlight (dynamic range of about 10<sup>8</sup> or 160dB), typical CMOS or CCD image sensors have dynamic range of 65-75dB. Two alternatives are possible to improve DR, either by reducing the noise level of the imager and expanding its dynamic range towards darker illuminations, or by extending the saturation level of the incident light and thus improving the DR towards brighter scenes. With the exception of very few applications such as astronomy, most frequent imaging situations correspond to bright light imaging such as automotive night vision or objects tracking in an uncontrolled lighting condition such as star tracking and aircraft landing. This explains why most of the DR enhancement techniques are mainly for bright light imaging applications. Another reason for this trend of DR enhancement could be due to the fact the noise floor of the imager is an ultimate limit whereas the saturation level could be expanded to a accommodate non-limited bright lighting imaging conditions. Many DR enhancement

<sup>&</sup>lt;sup>7</sup> Lux is an SI illumination unit that is equal to one lumen per square meter. Lumen is an SI unit for luminous flux equal to the light emitted in a unit solid angle by a uniform point source of one candle intensity.

approaches have been suggested to expand the limited electrical dynamic range of CMOS (or CCD) to reach the large optical dynamic range (of natural scenes) and at several levels of the imager design and functionality. An extensive review of these attempts is provided in [46]. We will concentrate on CMOS imagers dynamic range enhancement techniques which can be clustered into two categories:

DR enhancement by compressing or transforming the pixel photo-response.

DR enhancement by manipulating globally or locally pixel integration times. Even further development of these approaches includes external or internal (autonomous) control of the integration time.

## 2.6.1 Dynamic Range Enhancement by Photo-Response Compression

In the first category, the pixel response is changed from integration mode to continuous mode and from linear to logarithmic [42] [43] in a technique originally used in CCDs [44]. This is realised by connecting an active resistor (diode connected MOSFET), that is biased to behave like a continuously–conducting logarithmic resistor, with a photodiode as shown in Fig 2.9.

Fig 2.9 Logarithmic active pixel sensor

Because the NMOS resistor is biased in weak inversion, the NMOS resistor will be biased in the subthreshold regime that exhibits a logarithmic behaviour between its source current (photo current) and the photodiode voltage as shown by the following equation.

$$V = V_{dark} \ln \left( I_{sat} / I_{ph} \right) \dots (2.1)$$

where  $V_{dark}$  is the photodiode dark voltage,  $I_{sat}$  is the leakage current and  $I_{ph}$  the photocurrent. Although the main reason in using MOSFET in resistor configuration was to have a large resistor between the photodiode and Vdd due to the small photocurrent (fA to nA), the logarithmic behaviour of the pixel looks very similar to human vision response to incident light [45]. The logarithmic pixel suffers mainly from the reduced image contrast.

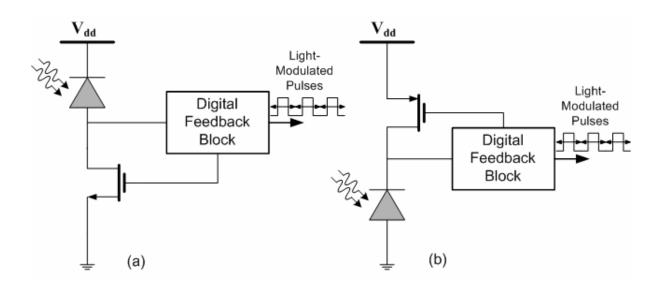

Another biologically analogous alternative is to convert the photo-signal of the pixel in modulated pulses [48] [49] similar to ganglion cells [4] neural (spike signals) response. The basis of this light-modulated pulse generation is the conversion of the linear photo discharging mechanism of the APS photodiode into digital pulses which carry out the light intensity information in their pulse width. This means converting the light intensity into time domain pulse signal <sup>8</sup> [47] and in order to realise this functionality, a digital feedback is realised between the photo diode discharging node and the reset transistor as shown in Fig 2.10. The pixel scheme in Fig 2.10.a is used in [48] while Fig 2.10.b is used by [49]. Using either an external or an internal threshold voltage, a comparison is performed in the digital feedback block and if the photodiode voltage drops below the threshold a reset signal is applied on the reset MOSFET. Therefore, the higher the light intensity, the faster the photodiode discharge will be and thus the shorter the generated pulse is going to be, which demonstrates the light modulation of generated pulse. Despite the high dynamic range achieved by this technique (120dB [49]), its main disadvantage is the multiplicative noise caused by the feedback path. This can be solved by implementing in-pixel noise cancellation circuitry, further reducing the pixel fill factor. This is probably the reason why there is no feedback path between ganglion cells and retinal photocells [4] in the retina.

<sup>&</sup>lt;sup>8</sup> Neural information processing is mainly in time domain because neural responses are discrete in their amplitudes but analog in time. Thus, time plays an essential role in the flow and transformation of information in biological systems.

In conclusion of this description of these different alternatives of dynamic range enhancement, it is apparent that manipulating the pixel photo-response to enhance DR suffers mainly from the reduced fill factor, degradation of sampled image contrast and the non-linear increase of fixed pattern noise due to the feedback loop with the photodiode [46]. The nonlinearity of FPN noise implies the non applicability of CDS unless it is implemented in pixel before light-to-pulse conversion which worsen further fill factor. These factors explain why integration time techniques are the dominant players in DR enhancement of CMOS imaging.

Fig 2.10 Light to pulses conversion forms

#### 2.6.2 Dynamic Range Enhancement using Integration Time Control

In the second category of DR enhancement, the integration time of the imager is programmed globally or locally in order to resolve the scene's bright and dark spots. The importance of using the integration time as a tool to enhance the optical dynamic range, in integration APS sensors, come from its equal effect with light intensity on the photo signal as expressed in equation (2.2).

$$V_{photo-signal} = Ss L_{inc} T^{int} \dots (2.2)$$

where *Ss* is the pixel constant sensitivity,  $L_{inc}$  is the light intensity on the pixel and  $T^{int}$  is its integration time. Therefore, to get the same electrical photo signal, in the APS linear regime, we need have the same product  $L_{inc}$   $T^{int}$  and thus short integration time is needed for high light intensities and long integration time is needed for low light intensities. This simple demonstration explains the use of integration time in extending the optical DR.

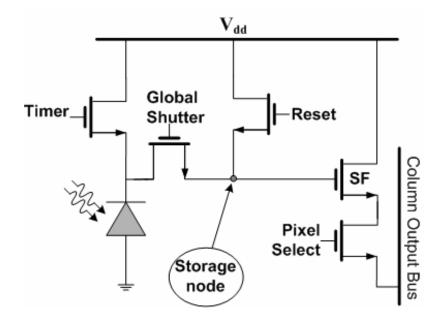

Integration time control has been initially implemented through global control of the frame time using an electronic shutter replacing the mechanical iris used to control incident light intensity in old film imaging cameras [50][51]. A schematic of a typical electronic shutter, which will also be used (with minor changes) in our multiresolution CMOS imager in Chapter 7, is shown in Fig 2.11. The only difference between APS with electronic shutter and the standard APS sensor is the addition of a shutter transistor between the photodiode and source follower (SF) and the extra reset transistor (reset). The capacitance of the drain diffusions from the reset and the shutter transistor beside the gate capacitance of SF constitutes a storage node (that needs to be shielded from light) where the sampled signal charge will be temporarily stored. The global shutter signal is shared for all the CMOS imager pixels and thus comes the global attribute of the shutter. Finally, reset and timer transistors are used to reset the storage node and the photodiode respectively.

Fig 2.11 Global shutter general schematic

The main disadvantage of using of using the global shutter to control integration time emerges in high intrascene dynamic range situations where only bright regions can be visualised with shorter integration times and the darker ones using longer integration times but not both at once. Therefore, the dynamic range of the imager is limited by the electrical dynamic range (~60-75dB) which is substantially less than the optical dynamic range of many natural scenes. The most important application of this structure is found in fast imaging

applications with intermediate (controlled) light intensities [52] because of its minimization of motion blur [53].

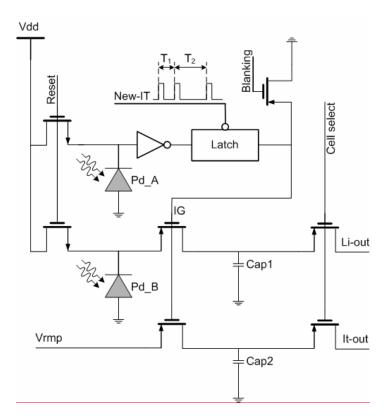

The local integration time technique is based on estimating the integration time independently at every pixel in the image sensor [54] [55]. This technique, called multiple integration time (MIT), is implemented through the automatic selection of integration time (from among a predetermined set of values) corresponding to the closest level to saturation. This technique is sometimes referred as the time-to-saturation technique. The MIT pixel shown in Fig 2.12 is composed of 2 identical photodiodes, a transparent latch, an inverter, 2 NMOS, 5 PMOS transistors and two capacitors.

Fig 2.12 Pixel schematic of MIT photoreceptor

Photodiodes Pd\_A and Pd\_B are initially reset concurrently and left discharged by the impinging light intensity. Pd\_A output discharges continuously and is compared to the inverter's threshold whose output will be latched out at specific time intervals corresponding to the predetermined integration times  $T_1$ ,  $T_2$ ...  $T_N$ . Once the photodiode output crosses the threshold the inverter output is latched out and the integration gate (IG) is closed sampling the photo charge in Cap1 and the corresponding incremental voltage Vrmp, which indicates which integration time interval is being used, at Cap2. These two stored voltages will be output to Li-out and It-out that carry photo signal and the corresponding integration time interval respectively. Although this technique can achieve DR of 120dB, its large pixel size of 110  $\mu$ m pitch reduces the acquisition of high spatial frequency details (resolution) with a reduced fill factor. Autonomous control is mentioned in [55] but again, it suffers from a low fill factor and a large pixel area.

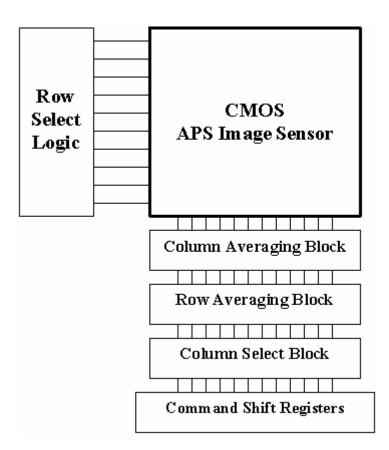

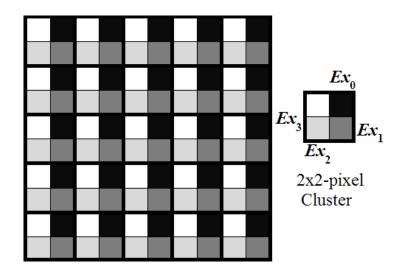

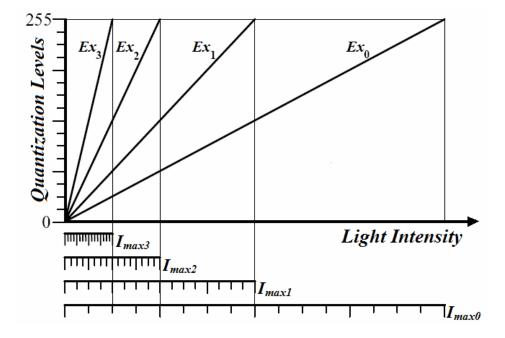

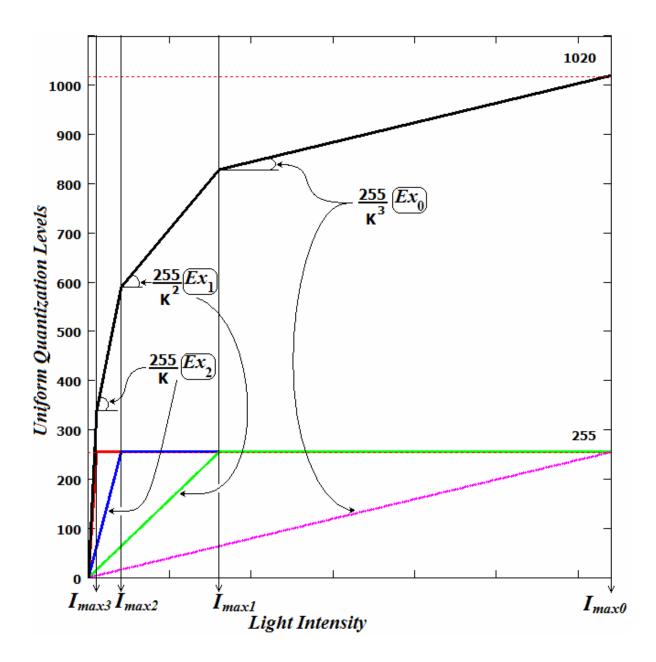

### 2.6.3 Dynamic Range Enhancement using Variable Light Exposures

One may alleviate the integration of the control (of integration time) from the pixel site to its neighbourhood so that instead of having one single-sensitivity pixel, four (or more) pixels of different sensitivities are integrated. Therefore, the pixel of highest sensitivity would integrate better low light intensities and the pixel of the lowest sensitivity would integrate better the high light intensities. However, the sensitivity is a technology constant parameter thus one way to mimic this characteristic is by controlling the exposure [57] of the pixels and to keep all pixels similar. The exposure is varied over a cluster (of pixels) and this cluster structure is mapped over the whole imager as shown in Fig 2.13, where the cluster's pixels

have their exposures so that  $Ex_0 < Ex_1 < Ex_2 < Ex_3$ . In [57], the exposures have been assumed to be uniformly increasing values such that  $Ex_0 = K Ex_1 = K^2 Ex_2 = K^3 Ex_3$ , and K was set to K = 4. The exposure control is realised by masking the pixel with cells of different optical transparencies or directly etching over the pixel on a solid-state imager (CCD or CMOS imager). The idea of using exposure control to extend the dynamic range comes from film imaging technology by using the important concept known as the reciprocity principle [58]. The reciprocity law states that within the normal range<sup>9</sup> (of intensity and time for the film) different choices of aperture and shutter speed that result in identical exposure are equivalent. By definition, exposure = light Intensity x integration time, which explains that for the same integration time, opacity is reversely proportional to exposure.

Fig 2.13 Spatially varying exposure time technique for DR enhancement

<sup>&</sup>lt;sup>9</sup> Normal range refers to the linear range of the film photo-response.

By using similar integration time for all pixels to sample an image, a different exposure value will result in each pixel of the cluster, hence resulting in this technique being known as the spatially varying exposure technique (SVE) [59]. The DR expansion emerges from the assumption that a multiple-exposure cluster shares the same light intensity<sup>10</sup> and thus a low light intensity would be better imaged with a higher exposure pixel and a higher light intensity is well sampled with a lower exposure pixel, thus expanding the original pixel optical DR. The importance of the SVE technique in enhancing the imager DR resides in manipulating the exposure of the imager pixels either by using different microlenses on the array, or using different integration times for different pixels, or embedding pixels of different potential well apertures. All these alternatives (we will review some of them subsequently) fall under the spatially varying exposures technique for DR enhancement. The key feature of the present SVE technique is the simultaneity of spatial dimensions sampling and exposure dimensions sampling (through 4 or more exposures per cluster). Two important questions arise: how much DR enhancement is achieved, and how is the final image reconstructed, using the SVE technique?

The DR definition is

$$DR = 20 \log \left(\frac{I_{\text{max}}}{I_{\text{min}}}\right) \dots (2.3)$$

where  $I_{max}$  and  $I_{min}$  correspond to the maximum and minimum gray levels respectively.  $I_{max}$ and  $I_{min}$  correspond respectively to the full-well capacity (saturation) and the minimum signal

<sup>&</sup>lt;sup>10</sup> True only in the case of an image with low spatial frequency *vis-à-vis* the imager spatial resolution.

(or read noise) detectable by the imager [60]. This correspondence is made by the adjustment of the gain of the analog-to-digital converter ADC and the number of required image gray levels, which has been found to be 8 levels [62] for false-contour-free images [61]. In general the DR of an imager is equal to number of gray levels necessary to encode the imager analog output [16]. Therefore, an 8-bit CCD or CMOS imager has DR equal to

$$DR_{8-bit \ imager} = 20 \log(255) = 48.13 \ dB \dots (2.4)$$

where,  $I_{min}$  is set to 1 as level  $I_{min}=0$  represents a non meaningful information.

Now, using the spatially varying exposure scheme in image sampling will maintain the lowest level at 1 but will extend the maximum detectable light intensity level (after ADC conversion) to  $I_{max}$  ( $Ex_{max}/Ex_{min}$ ) consequently expanding the DR of the resulting image to

$$DR = 20 \log \left( \frac{I_{\max}}{I_{\min}} \frac{Ex_{\max}}{Ex_{\min}} \right) \dots (2.5)$$

The extension of  $I_{max}$  is due to the fact that the saturation of the lowest exposure pixel (the most opaque) requires higher saturating light intensity equal to  $I_{max}$  ( $Ex_{max}/Ex_{min}$ ). This is clarified by the following the mathematical proof where *Ss* is the pixel sensitivity, *Vs* the pixel photo signal and  $Ex = Tr L_{inc} T^{int}$  its exposure, where *Tr* is the transmission factor of the pixel cell mask,  $L_{inc}$  is the incident light intensity and  $T^{int}$  the pixel integration time. Recall also that all pixels are using the same  $T^{int}$  and the pixels cluster is postulated to have the same  $L_{inc}$ .

$$Vs = Ss \ Ex$$

or  $Vs = Ss \ Tr \ L_{inc} \ T^{int} \dots (2.6)$

At the saturation level the saturation photo signal *Vs\_sat* will be

$$Vs\_sat = Ss Tr_{max} L_{inc max} T^{int} \dots (2.7)$$

where  $Tr_{max}$  correspond to the most transparent mask transmission rate, and  $L_{inc\_max}$  is the maximum light intensity causing saturation. However, the product of  $Tr_{max} L_{inc\_max}$  can be achieved, in similar way through reciprocity principle, by the product  $Tr_{min} L_{inc\_max\_ext}$  where  $L_{inc\_max\_ext}$  is the new (extended) saturation light intensity and  $Tr_{min}$  is minimal transmission rate corresponding to the most opaque mask. Therefore, we get

$$L_{inc\_max\_ext} = L_{inc\_max} \frac{Tr_{max}}{Tr_{min}} \text{ or } L_{inc\_max\_ext} = L_{inc\_max} \frac{Ex_{max}}{Ex_{min}} \dots (2.8)$$

It is assumed that the cluster pixels share the same incident light intensity and integration time. This means the maximum light intensity (saturating the most transparent pixel) has been extended by a factor of  $Ex_{max}/Ex_{min}$  (saturating the most opaque pixel). Therefore, and assuming the minimum light intensity remains the same (read noise), the resulting DR becomes

$$DR = 20 \log \left(\frac{I_{\max}}{I_{\min}} \frac{Ex_{\max}}{Ex_{\min}}\right) \text{ or } DR = 20 \log \left(\frac{I_{\max}}{I_{\min}}\right) + 20 \log \left(\frac{Ex_{\max}}{Ex_{\min}}\right) \dots (2.9)$$

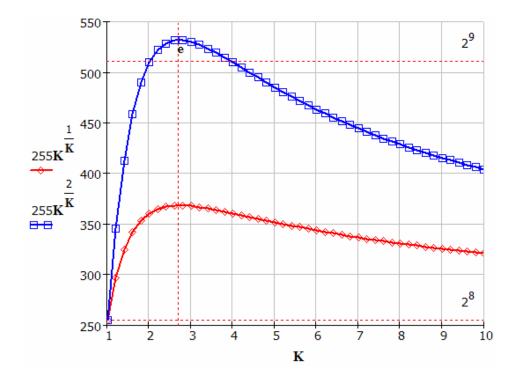

Hence, using variable exposure technique enhances the uniform exposure imager DR by a factor of  $20 \log \left(\frac{Ex_{\text{max}}}{Ex_{\text{min}}}\right)$  and with the present case where  $Ex_{\text{max}} = K^3 Ex_{\text{min}}$ , the final dynamic

range enhancement becomes

$$DR_{enhancement} = 20 \log(K^3)$$

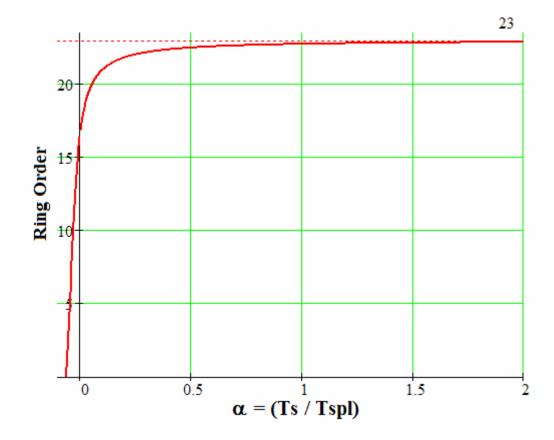

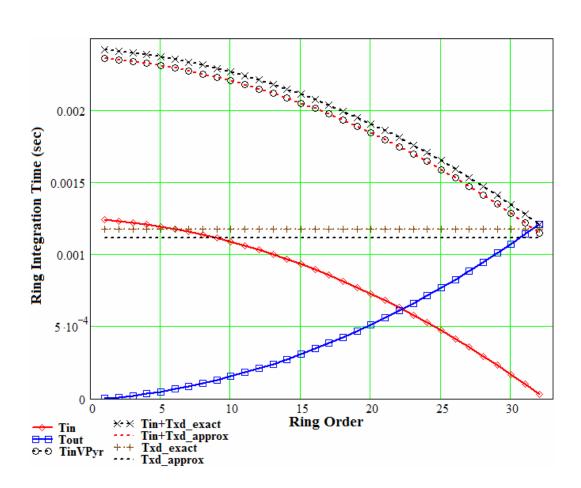

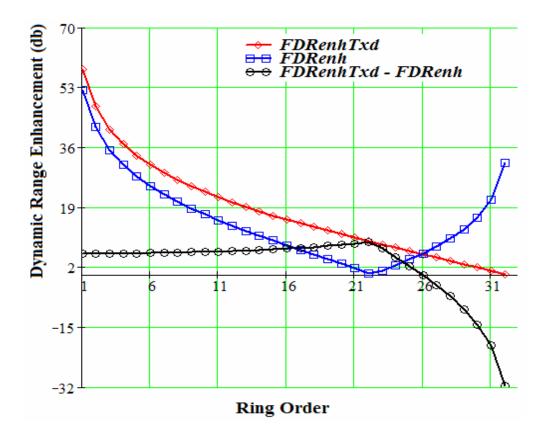

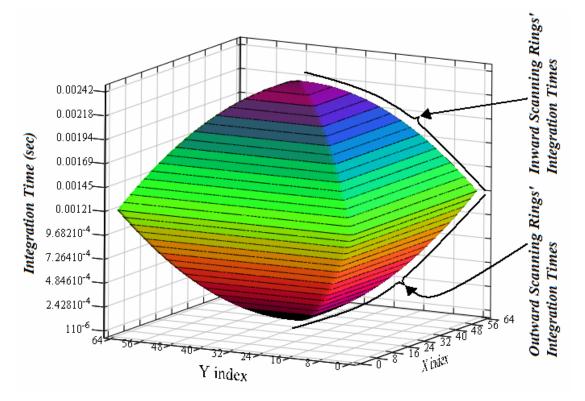

or simpler  $DR_{enhancement} = 60 \log(K) \dots (2.10)$