# Analysis of Analog Sampled Data Circuits

by

#### Bijan Raahemi

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical Engineering

Waterloo, Ontario, Canada, 1996

©Bijan Raahemi 1996

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre niférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced with the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-21384-6

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### **Abstract**

Complex systems consist of a core of digital signal processing (DSP) buffered from external environments by analog interface circuitry. "Analog sampled data" circuits can be predominantly found in the data conversion portions of these mixed-mode integrated circuits. Delta-Sigma modulator is an example. Analog sampled data circuits also perform signal processing tasks, and are used in many filtering applications. Switched-capacitor, and switched-current circuits are the examples of these applications.

Sampled data circuits are dual time systems that contain a rapidly varying clock and a slowly varying input signal. As a result, most of the simulation effort is dedicated to the transient analysis at switching instants, where information is usually not needed. The important required information is the response of the circuit at the end of the clock period, when it reaches the steady state. Searching for a method that can provide the solution of the circuit at discrete instants of time led to the "sampled data simulation" technique [1].

This thesis looks at different aspects of analog sampled data systems. It extends the idea of sampled data simulation to provide an accurate and efficient method of computing the time domain sensitivity of linear circuits. The method is applied to sensitivity analysis of an important class of sampled data systems, Delta-Sigma modulators. We also provide efficient methods for analysis of switched networks, including the group delay and group delay sensitivity of periodically switched linear networks in general, and harmonic distortion of switched-current circuits in particular. Sources of distortion in switched-current circuits are examined, and both upper and lower bounds are derived on total harmonic distortion of a current memory cell.

Acknowledgements

" All praise is due to Allah, the lord of the worlds.

Thee do we serve and Thee do we beseech for help. "

I would like to thank my supervisors, Professor Ajoy Opal and Professor Jiri Vlach,

for their valuable guidances and constant supports. I have been always enjoying

their friendly relationship, and useful advice. I am also indebted to them for their

partial financial support.

I would like to express my gratitude to Professor Jim Barby for his careful

reading of this thesis. I am also grateful to the members of my Ph.D. examination

committee: Prof. M. Nakhla, Prof. M.I. Elmasry, and Prof. D. Brodie.

I would like to express my appreciation to the Ministry of Culture and Higher

Education of the Islamic Republic of Iran for the financial support and sponsorship.

Finally, my most profound gratitude goes to my mother, who spent a lonely

time in Iran, for her unconditional love and support. None of this could have been

achieved without her enthusiasm and prayer.

Bijan Raahemi

December 12, 1996

Waterloo, Ontario, Canada

V

## To my wife for her encouragement, help, and patience

## Contents

| 1 | Inti | coduction                                                   | 1  |

|---|------|-------------------------------------------------------------|----|

|   | 1.1  | Thesis Outline                                              | 4  |

| 2 |      | ne Domain Sensitivity of Linear Circuits Using Sampled Data | 8  |

|   | Sim  | uiation                                                     | C  |

|   | 2.1  | Sampled Data Simulation of Linear Circuits                  | 10 |

|   |      | 2.1.1 Numerical Computation of M and P Matrices             | 13 |

|   | 2.2  | Inconsistent Initial Conditions                             | 15 |

|   | 2.3  | Time Domain Sensitivity Using Sensitivity Network           | 22 |

|   |      | 2.3.1 Example                                               | 25 |

|   | 2.4  | Time Domain Sensitivity Using Adjoint Network               | 31 |

|   |      | 2.4.1 Adjoint Network in Time Versus Frequency Domain       | 33 |

|   |      | 2.4.2 Approach I: Convolution                               | 34 |

|   |      | 2.4.3 Approach II: Numerical Laplace Transform Inversion    | 36 |

| 3 | Ana  | alysis and Sensitivity of Delta-Sigma Modulator                                  | 38 |

|---|------|----------------------------------------------------------------------------------|----|

|   | 3.1  | Oversampled Delta-Sigma A/D Converters                                           | 39 |

|   | 3.2  | Sampled Data Simulation of Delta-Sigma Modulator                                 | 42 |

|   | 3.3  | Sensitivity of Delta-Sigma Modulators                                            | 47 |

|   |      | 3.3.1 Sensitivity Network                                                        | 50 |

|   |      | 3.3.2 Approximations                                                             | 58 |

|   |      | 3.3.3 Example                                                                    | 59 |

| 4 | Gre  | oup Delay and Group Delay Sensitivity of Periodically Switched                   |    |

|   | Line | ear Networks                                                                     | 61 |

|   | 4.1  | Frequency Domain Analysis of Periodically Switched Linear Networks               | 63 |

|   | 4.2  | Group delay                                                                      | 69 |

|   |      | 4.2.1 Example                                                                    | 71 |

|   | 4.3  | Group Delay Sensitivity                                                          | 73 |

|   | 4.4  | The Algorithm                                                                    | 76 |

|   |      | 4.4.1 Example                                                                    | 79 |

|   | 4.5  | Computation of P and $\frac{\partial P}{\partial \omega}$ with Sinusoidal Inputs | 82 |

| 5 | Swi  | tched-Current Circuits                                                           | 86 |

|   | 5.1  | A Review of Switched-Current Circuits                                            | 87 |

|   |      | 5.1.1 Current Mirror                                                             | 87 |

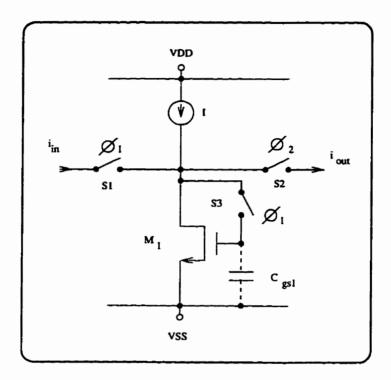

|   |      | 5.1.2 Current Track-and-Hold Circuit                                             | 89 |

|   |     | 5.1.3   | Switched-Current Filters                            | 90  |

|---|-----|---------|-----------------------------------------------------|-----|

|   | 5.2 | Non-F   | Piltering Applications of Switched-Current Circuits | 94  |

|   |     | 5.2.1   | Current-Controlled Oscillator (CCO)                 | 98  |

|   |     | 5.2.2   | Modulator                                           | 98  |

|   |     | 5.2.3   | Full-Wave Rectifier                                 | 10  |

|   |     | 5.2.4   | Oversampled Delta-Sigma Modulator                   | 102 |

| 6 | Har | monic   | Distortion in Switched-Current Circuits             | 108 |

|   | 6.1 | Source  | es of Harmonic Distortion                           | 108 |

|   |     | 6.1.1   | $V_T$ Mismatch                                      | 110 |

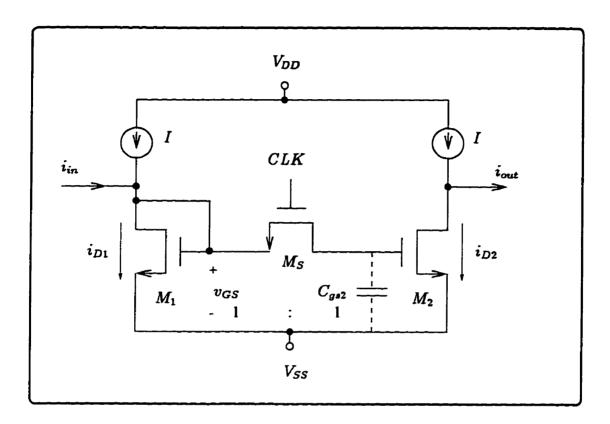

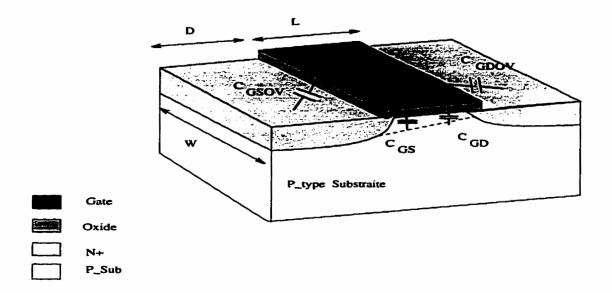

|   |     | 6.1.2   | Clock Feed Through                                  | 111 |

|   |     | 6.1.3   | Operating Frequency                                 | 115 |

|   | 6.2 | Predic  | cting Harmonic Distortion in the SI Memory Cell     | 115 |

|   |     | 6.2.1   | THD Measurement                                     | 116 |

|   |     | 6.2.2   | The Upper Bound on the THD                          | 117 |

|   |     | 6.2.3   | The Lower Bound on the THD                          | 122 |

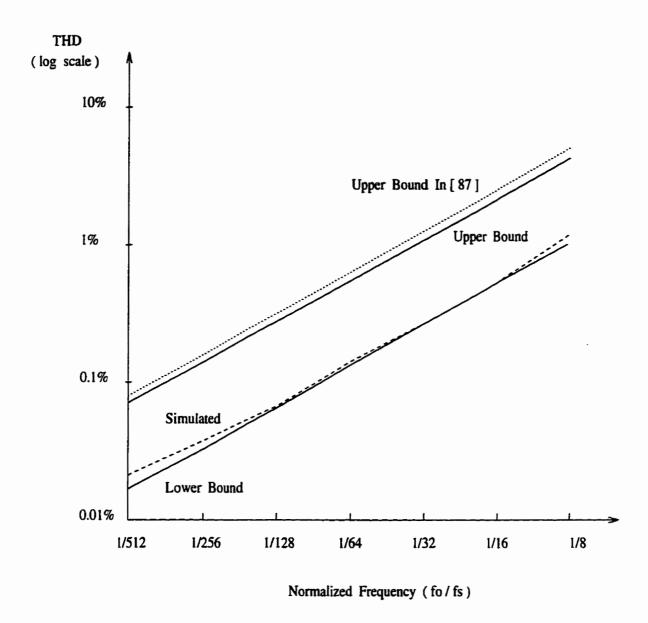

|   |     | 6.2.4   | Comparing the THD Bounds With Simulation Results    | 123 |

| 7 | Cor | ıclusio | ns                                                  | 127 |

|   | 7.1 | Contr   | ibutions                                            | 128 |

|   | 7.2 | Future  | e Research                                          | 129 |

| A | Ca  |         | tion of P. M. and Their Derivatives                 | 122 |

| В  | The Algorithm for Calculation of Group Delay and Its Sensitivity | 137 |

|----|------------------------------------------------------------------|-----|

| C  | Selected Switched-Current Circuits                               | 145 |

| Bi | bliography                                                       | 153 |

## List of Tables

| 2.1        | The output of RC circuit at a few time points                             | 17  |

|------------|---------------------------------------------------------------------------|-----|

| 2.2        | Relationship between the adjoint methods in time and frequency            |     |

|            | domains                                                                   | 33  |

| 3.1        | Sensitivities of the second-order continuous-time DSM (The incre-         |     |

|            | mental sensitivity was calculated by perturbing the element values        |     |

|            | by 1%, and the differential sensitivity was calculated using (3.9))       | 60  |

| 5.1        | Reported SI filters                                                       | 94  |

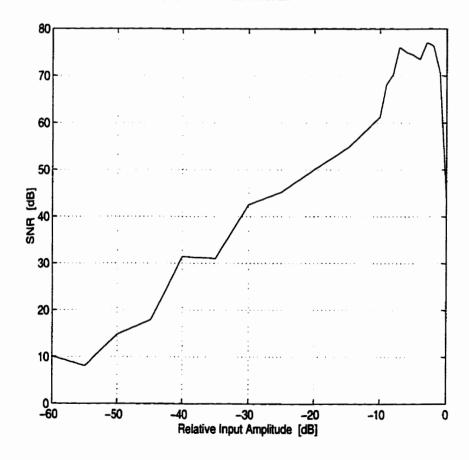

| 5.2        | Simulated switched-current DSM performances                               | 107 |

| <b>A.1</b> | Poles $z_i$ and residues $K_i$ used in numerical Laplace transform inver- |     |

|            | sion (M=10, N=8)                                                          | 134 |

## List of Figures

| 1.1 | A mixed analog and digital (mixed-mode) integrated circuit                     | 2  |

|-----|--------------------------------------------------------------------------------|----|

| 1.2 | The outline of the thesis.                                                     | 5  |

| 2.1 | Network with inconsistent initial voltages                                     | 16 |

| 2.2 | RC circuit with Dirac impulse input.                                           | 17 |

| 2.3 | Switched network with inconsistent initial conditions                          | 21 |

| 2.4 | Unit step response of the network in Fig.2.3 with and without using            |    |

|     | $\mathbf{M}_0$ and $\mathbf{P}_0$ matrices                                     | 21 |

| 2.5 | RC circuit with unit step input                                                | 26 |

| 2.6 | Simulation results for the sensitivity of $v_2(t)$ (a) with respect to $G_1$ , |    |

|     | and (b) with respect to $C$ .                                                  | 30 |

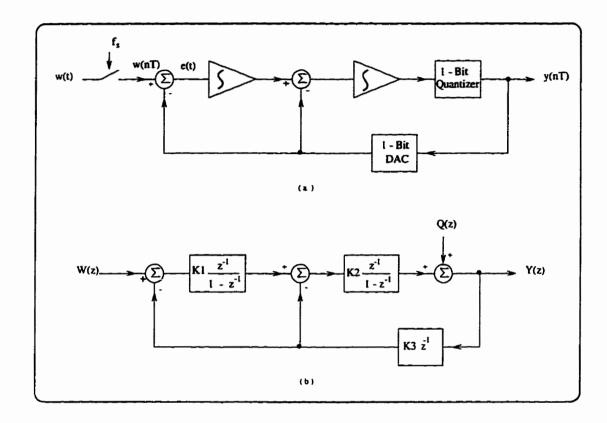

| 3.1 | (a) Block diagram of a second-order Delta-Sigma modulator, (b)                 |    |

|     | Linearized model of modulator                                                  | 41 |

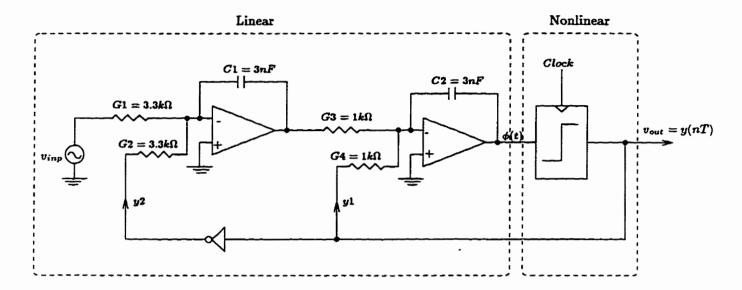

| 3.2 | Second-order continuous-time Delta-Sigma modulator                             | 43 |

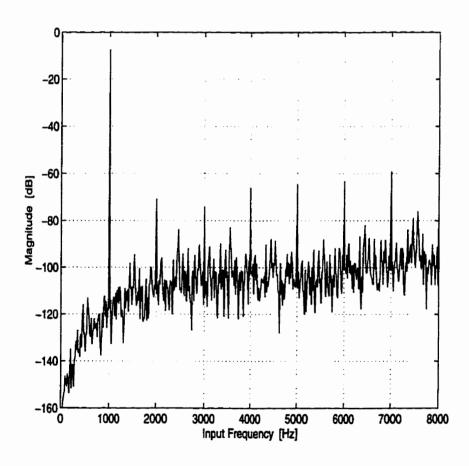

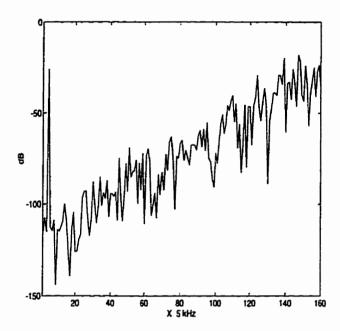

| 3.3 | DSM output spectrum for a 1 kHz sinusoidal input                               | 45 |

| 3.4 | Signal to noise ratio vs. input amplitude for the DSM in Fig. 3.2              | 46 |

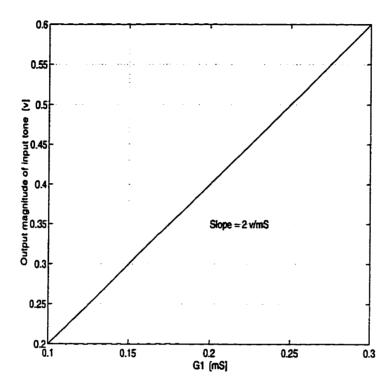

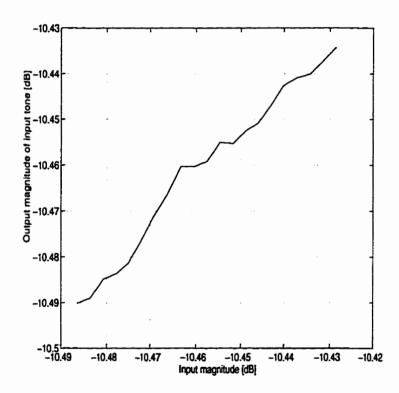

| 3.5  | The DSM output magnitude of input tone for different values of G1.             | 48 |

|------|--------------------------------------------------------------------------------|----|

| 3.6  | The magnified area of the curve in Fig. 3.5 (assuming that the input           |    |

|      | magnitude is changed instead of G1)                                            | 49 |

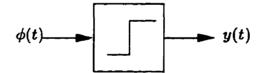

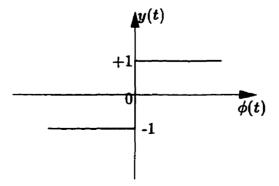

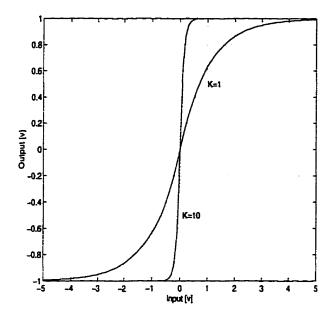

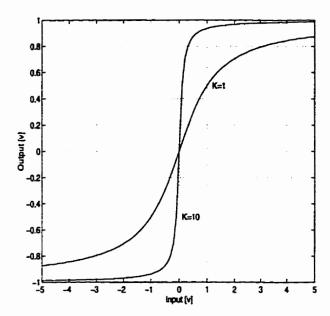

| 3.7  | The comparator and its input-output characteristic                             | 51 |

| 3.8  | The input and output of the unclocked comparator                               | 52 |

| 3.9  | Exponential approximation of the comparator                                    | 53 |

| 3.10 | Trigonometric approximation of the comparator                                  | 54 |

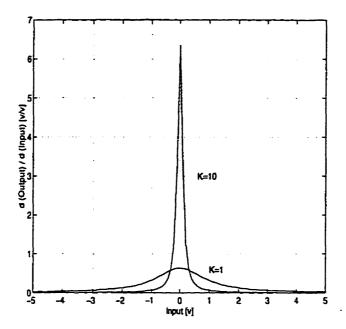

| 3.11 | Differential of the trigonometric approximation of the comparator              | 55 |

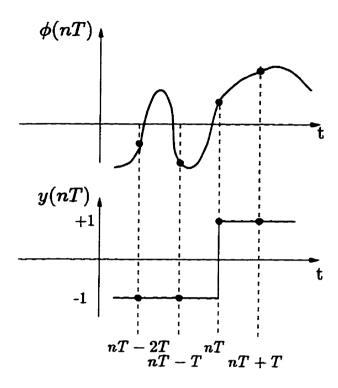

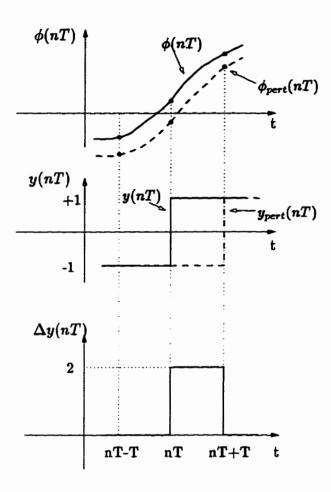

| 3.12 | The input and output of the clocked comparator                                 | 56 |

| 3.13 | The change in the output of the clocked comparator due to the                  |    |

|      | change in its input                                                            | 57 |

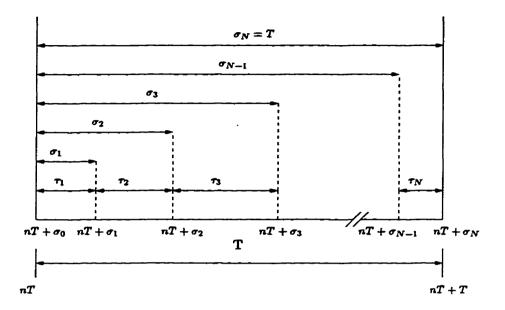

| 4.1  | Timing definitions for an N-phase switched network                             | 64 |

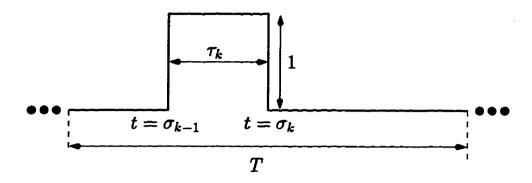

| 4.2  | Definition of the kth window function $\xi_k(t)$                               | 66 |

| 4.3  | Switched RC circuit                                                            | 72 |

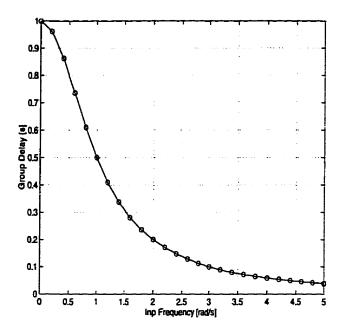

| 4.4  | Group delay of the output in Fig. 4.3                                          | 74 |

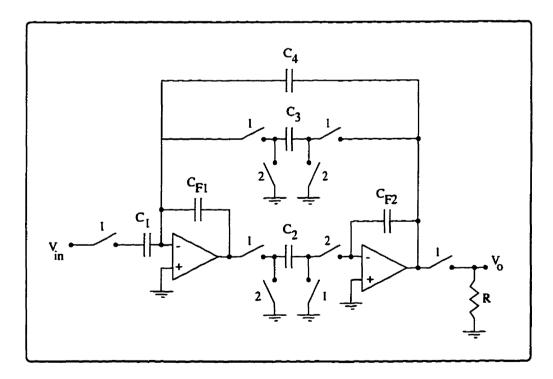

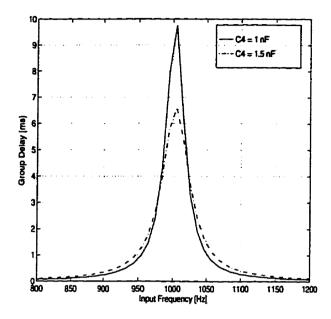

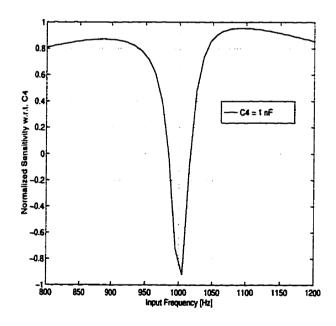

| 4.5  | A standard SC band-pass filter with $f_0 = 1kHz$ , $(C_1 = 10nF, C_2 =$        |    |

|      | $C_3 = 9.781nF, C_4 = 1nF, C_{F1} = C_{F2} = 31.25nF, R = 100\Omega).$         | 79 |

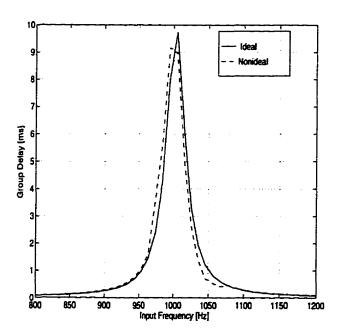

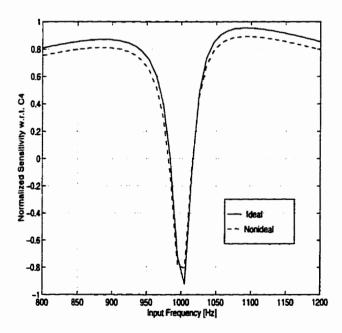

| 4.6  | Group delay of the output in Fig. 4.5                                          | 80 |

| 4.7  | Group delay sensitivity of the output in Fig. 4.5 with respect to $C_4$ .      | 80 |

| 4.8  | Group delay of the output in Fig. 4.5 with ideal opamp (infinite gain-         |    |

|      | bandwidth) and switches $(R_{ON}=0,R_{OFF}=\infty)$ in compare to nonideal     |    |

|      | onamn (gain-handwidth= $10^5$ ) and switches ( $R_{ON} = 1kO, R_{ONR} = 1MO$ ) | 81 |

| 4.9  | Group delay sensitivity of the output in Fig. 4.5 with ideal opamp (infinite |     |  |  |

|------|------------------------------------------------------------------------------|-----|--|--|

|      | gain-bandwidth) and switches $(R_{ON}=0,R_{OFF}=\infty)$ in compare to non-  |     |  |  |

|      | ideal opamp (gain-bandwidth=105) and switches $(R_{ON}=1k\Omega,R_{OFF}=$    |     |  |  |

|      | 1 $M\Omega$ )                                                                | 82  |  |  |

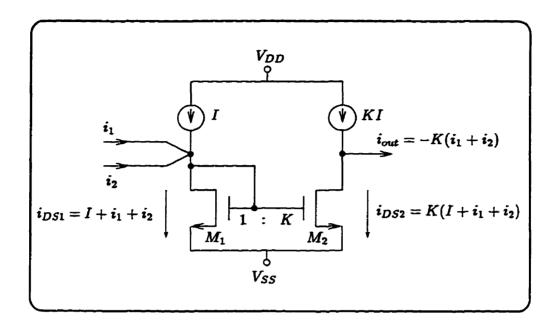

| 5.1  | A simple current mirror                                                      | 88  |  |  |

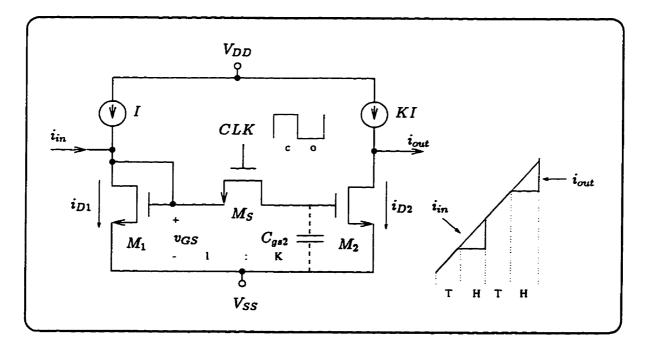

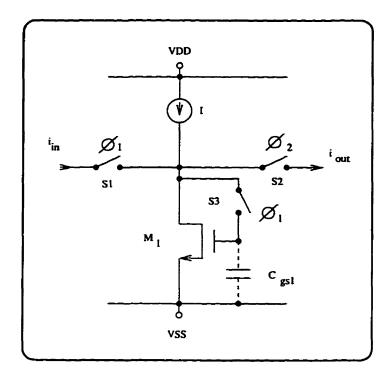

| 5.2  | Current track-and-hold circuit                                               | 89  |  |  |

| 5.3  | Dynamic current mirror (current copier)                                      | 91  |  |  |

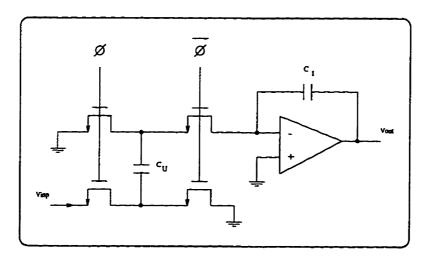

| 5.4  | An SI integrator                                                             | 92  |  |  |

| 5.5  | An SC integrator, the dual of an SI integrator                               | 93  |  |  |

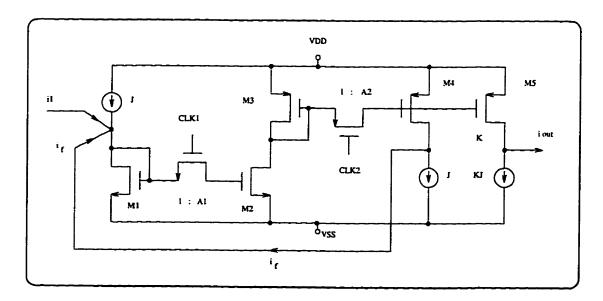

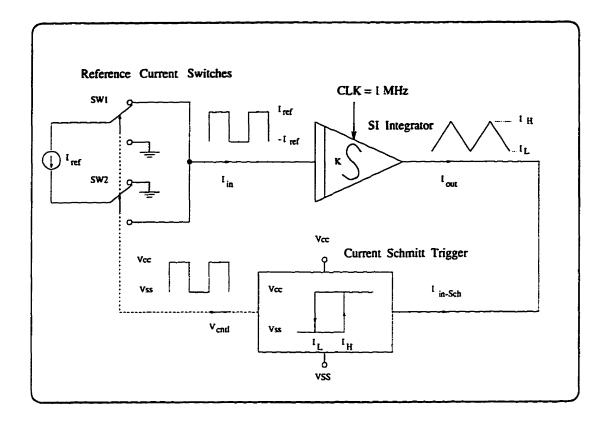

| 5.6  | Block diagram of an SI current-controlled oscillator                         | 95  |  |  |

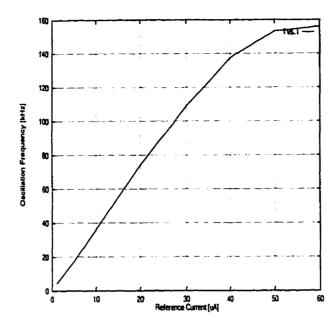

| 5.7  | Oscillation frequency vs. reference current                                  | 97  |  |  |

| 5.8  | Oscillator output for $I_{ref}=10\mu A$                                      | 98  |  |  |

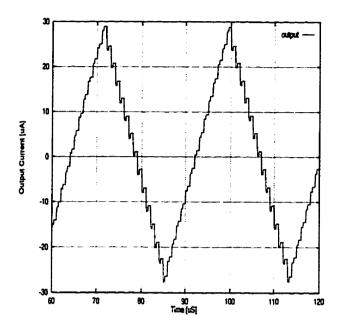

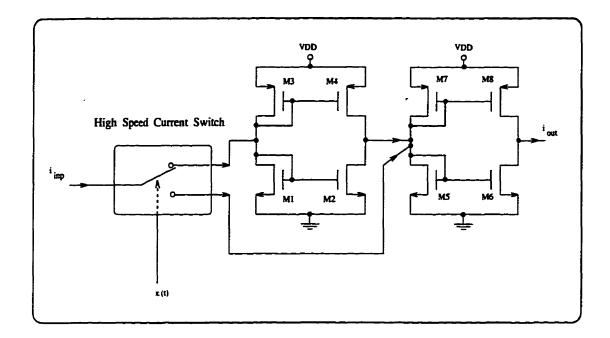

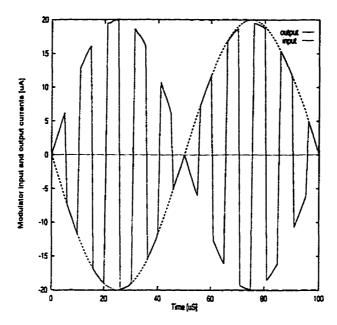

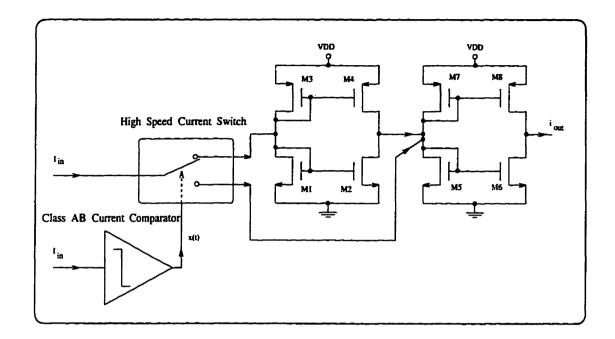

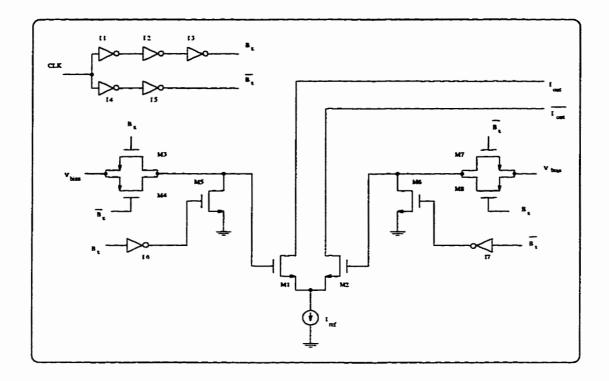

| 5.9  | Switched-current modulator circuit                                           | 99  |  |  |

| 5.10 | Modulator output                                                             | 100 |  |  |

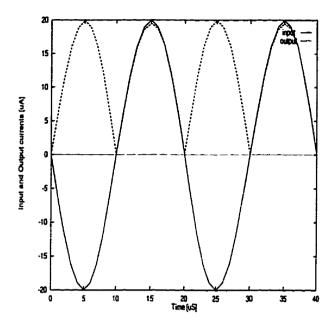

| 5.11 | Full-wave current-mode rectifier                                             | 101 |  |  |

| 5.12 | Input and output currents of full-wave rectifier                             | 102 |  |  |

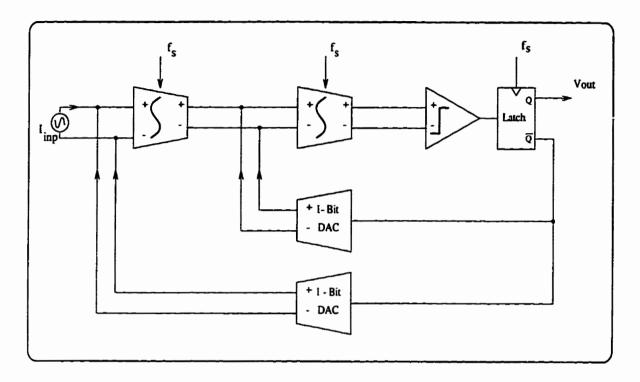

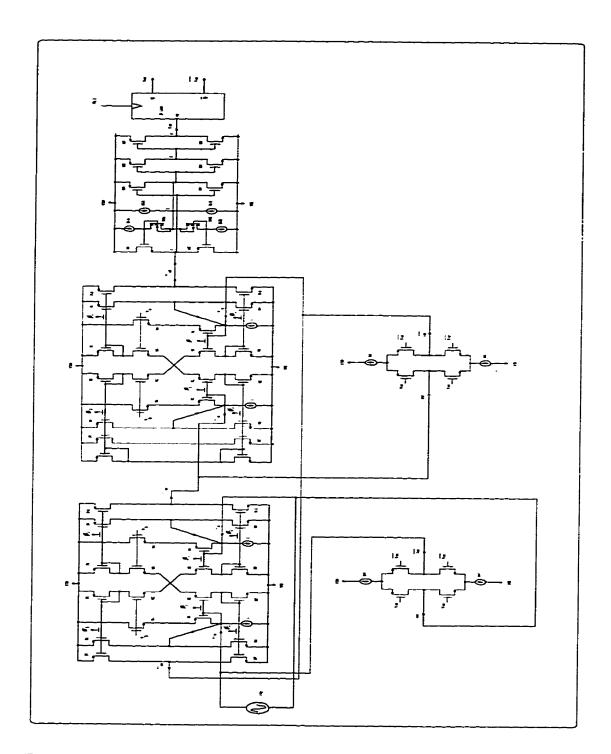

| 5.13 | Block diagram of the switched-current Delta-Sigma modulator                  | 103 |  |  |

| 5.14 | A differential switch as 1-bit D/A converter                                 | 104 |  |  |

| 5.15 | The proposed circuit of switched-current Delta-Sigma modulator               | 105 |  |  |

| 5.16 | Spectrum of the output of switched-current DSM                               | 107 |  |  |

| 6 1  | Current track-and-hold circuit                                               | 109 |  |  |

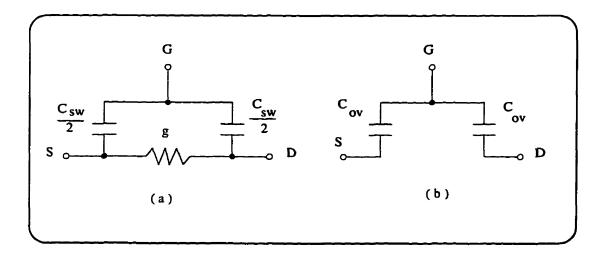

| 6.2        | The structure of a MOS transistor with its parasitic capacitances            | 112 |

|------------|------------------------------------------------------------------------------|-----|

| <b>6.3</b> | Model for switch transistor in (a) ON state, (b) OFF state                   | 113 |

| <b>6.4</b> | Current memory cell (current copier)                                         | 119 |

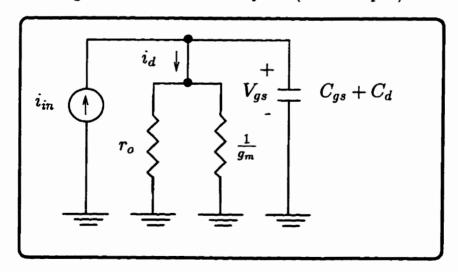

| 6.5        | Small-signal model of the current memory cell for the clock phase $\phi_1$ . | 119 |

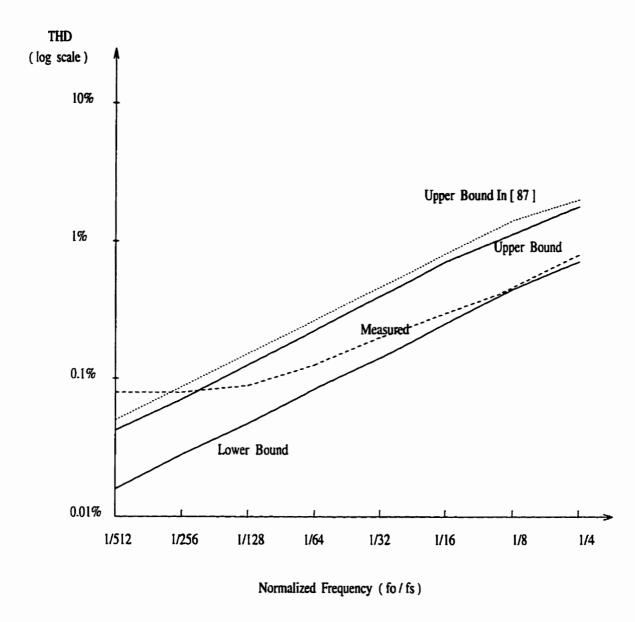

| 6.6        | Comparing the THD computed by HSPICE with results predicted                  |     |

|            | by our method                                                                | 124 |

| 6.7        | Comparing the measured THD of the circuit in Fig.6.1 with results            |     |

|            | predicted by our method.                                                     | 126 |

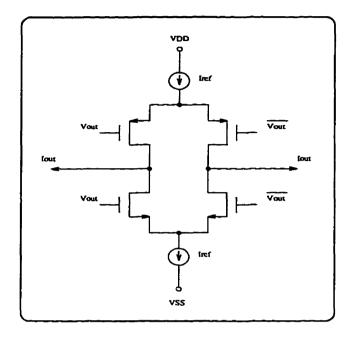

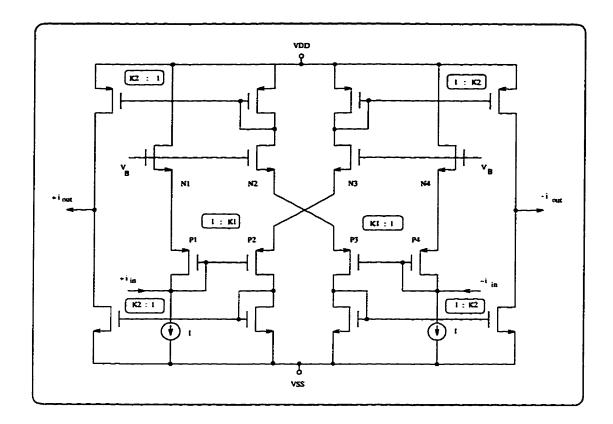

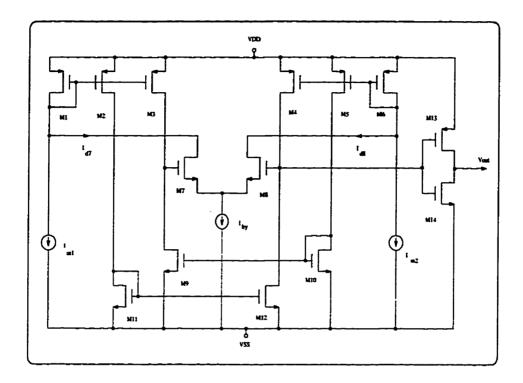

| C.1        | A fully differential current switch                                          | 146 |

| C.2        | A fully balanced current mirror with open loop current gain $2K_1K_2$ .      | 148 |

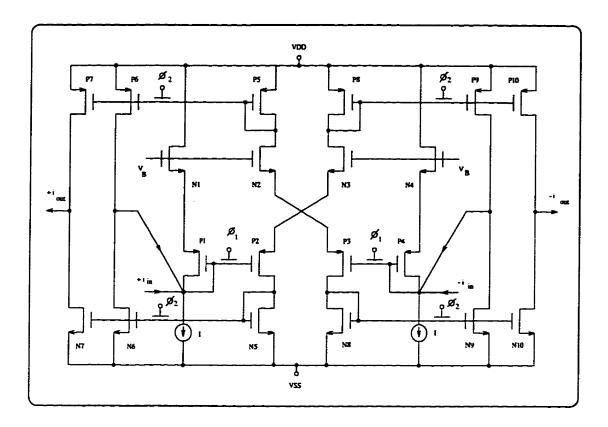

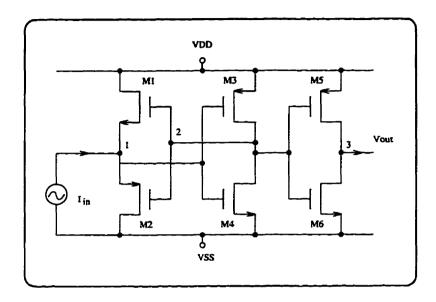

| C.3        | A fully balanced SI integrator                                               | 149 |

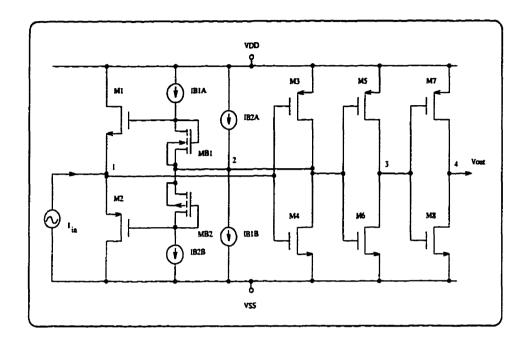

| C.4        | Two-input current Schmitt trigger with adjustable hysteresis                 | 150 |

| C.5        | A class B current comparator                                                 | 151 |

| C.6        | A class AB current comparator                                                | 152 |

## List of Symbols

B The matrix that transfers the final conditions of each phase to

the initial conditions of the next phase

C Capacitance matrix

CCO Current-Controlled Oscillator

CFT Clock Feed Through

d Selector vector that determines the output (output =  $\mathbf{d}^t \mathbf{X}$ )

DSM Delta-Sigma Modulator

F<sub>C</sub> Vector of final conditions

Fourier transform

$\mathcal{F}^{-1}$  Inverse of Fourier transform

G Conductance matrix

GRPSEN The program for computation of group delay and the group delay

sensitivity of periodically switched linear networks

h Parameter value, element variable

I Identity matrix

I<sub>C</sub> Vector of initial conditions

$\mathcal{L}^{-1}$  Inverse of Laplace transform

M Transition matrix for the original network

M<sub>0</sub> Transition matrix for the inconsistent initial condition

M. Transition matrix for the sensitivity network

Opamp Operational amplifier

P Constant vector for the original network

P<sub>0</sub> Constant vector for the inconsistent initial condition

P<sub>s</sub> Constant vector for the sensitivity network

PSLN Periodically Switched Linear Network

SC Switched-Capacitor

SDS Sampled Data Simulation

SDSEN The program for transient and sensitivity analysis of linear

circuits based on sampled data simulation method

SI Switched-Current

SNR Signal to Noise Ratio

T Time step

R System matrix  $(\mathbf{R} = \mathbf{G} + s\mathbf{C})$

THD Total Harmonic Distortion

W Source vector in Laplace domain

w Source vector in time domain

X Nodal vector in Laplace domain for the original network

x Nodal vector in time domain for the original network

Z Nodal vector in Laplace domain for the sensitivity network

z Nodal vector in time domain for the sensitivity network

### Chapter 1

### Introduction

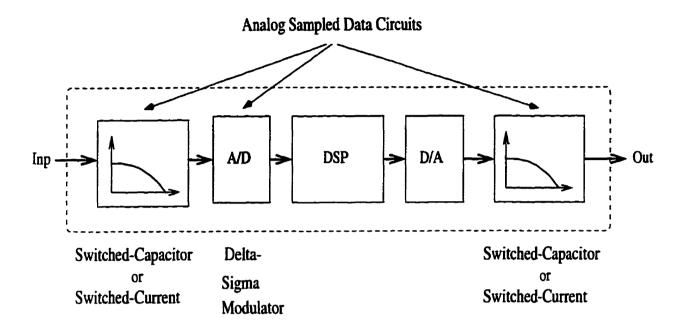

Analog sampled data systems are used as filters and also as interfaces between analog and digital circuits. Complex systems consist of a core of digital signal processing (DSP), buffered from external environments by analog interface circuitry. It is now becoming common to find a single mixed analog and digital (mixed-mode) integrated circuit that contains both the digital signal processor and all the interface circuits required to interact with the outside world, which is inherently analog (Fig.1.1). It is in the data conversion portions of these mixed-mode chips that analog sampled data circuits can be predominantly found. Analog sampled data systems also perform signal processing tasks. As a result, they are used in many filtering applications, such as anti-aliasing filter in Fig.1.1.

Switched-capacitor circuits, switched-current circuits, and Delta-Sigma modulators are examples of sampled data systems. The switched-capacitor technique eliminates resistors from the design of analog filters. It is based on the idea that a periodically switched capacitor can be used to simulate a resistor (provided that the switching frequency is much higher than the signal frequencies of interest).

Figure 1.1: A mixed analog and digital (mixed-mode) integrated circuit.

Switched-current circuits do not require linear floating capacitors, and can be integrated in a standard digital CMOS process. This allows integrated circuit manufacturers to implement both digital and analog circuits on the same chip with the existing low-cost CMOS processes. Operating in the current mode, and eliminating the need for a large voltage swing, make the switched-current technique suitable for low voltage applications.

Delta-Sigma modulators are important blocks of oversampled A/D converters. Oversampling A/D converters depend on relatively simple and modest analog circuitry. They are less insensitive to circuit imperfections and component mismatches, since they usually employ a simple two-level quantizer embedded within a feedback loop.

If analog sampled data systems are to be widely used in signal processing and data conversion, they require a suite of computer aided design (CAD) tools to

simulate the circuits, perform the sensitivity analysis, and automate the design processes. General purpose analog simulation tools, such as SPICE [2], can be used for simulation of these circuits. However, these tools are provided for simulation of general nonlinear circuits and do not simulateneously provide both the accuracy and speed necessary for simulation of specialized circuits.

Sampled data circuits are dual time systems that contain a rapidly varying clock and a slowly varying input signal. As a result, most of the simulation effort is dedicated to the transient analysis at switching instants, where information is usually not needed. Sampled data systems are usually working at frequencies that allow the output become stable. The important required information is therefore the response of the circuit at the end of the clock period, when it reaches the steady state between the switching instants. Consider, for instance, a Delta-Sigma modulator for which we collect the output data at the end of the phase, when modulator reaches the steady state, and take FFT of the data to obtain the frequency spectrum. Searching for a method that can provide the solution of the circuit at discrete instants of time led to the "sampled data simulation" technique proposed in [1]. Sampled data simulation (SDS) is an efficient, accurate, and stable method for transient analysis of lumped linear time invariant circuits. It generates some constant matrices before the simulation, and provides the transient solution at each time point by performing only one matrix-vector multiplication. The time points are equally spaced, and can be chosen arbitrarily regardless of the circuit time constants.

We extend the idea of sampled data simulation to compute the time domain sensitivity of linear circuits (switched and unswitched). There are several reasons for the importance of sensitivity in analog circuit design. In addition to providing more insight into the behavior of a physical system, sensitivity function plays an important part in the design and optimization of reliable circuits. The circuit manufacturing process results in the spread of parameter values, known as the element tolerances. Also, during the lifetime of a manufactured circuit, parameters are subject to change through aging, and environment effects, such as temperature and humidity. A sensitivity analysis is therefore required to find out which circuit parameters are critical, i.e. the network sensitivity with respect to them is very large.

Group delay is another aspect of analog sampled data filters that is analyzed in this thesis. In filter design, the magnitude response requirements are normally considered, and the corresponding phase response is ignored. This is because the reduction of antialiasing by stopband attenuation is the first issue, and phase information can be corrected later. For some applications, such as speech transmission, this consideration is sufficient as the human ear is insensitive to the phase shift. For video applications, however, the distortion caused by system nonlinear phase response is unacceptable. A fast and accurate method for the computation of group delay and the group delay sensitivity of periodically switched linear networks is presented in this thesis.

#### 1.1 Thesis Outline

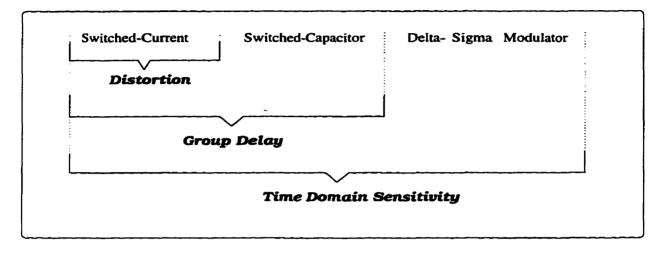

The objectives of this thesis are: (i) to extend the idea of sampled data simulation to compute the time domain sensitivity of linear circuits (switched and unswitched), and a class of nonlinear circuits—Delta-Sigma modulators, (ii) to provide efficient method for analysis of group delay and its sensitivity in periodically switched linear networks, (iii) to compute the harmonic distortion in switched-current circuits. Fig. 1.2 shows the various classes of analog sampled data circuits, and the different

types of analysis considered in this thesis.

Figure 1.2: The outline of the thesis.

Each chapter of this thesis looks at one aspect of sampled data systems. Therefore, each chapter starts with its own introduction in the first section, continued by new material in subsequent sections as my contribution to each topic.

Chapter 2 is dedicated to time domain sensitivity of linear circuits using sampled data simulation. It presents a new method which is accurate, because no approximation is made, and efficient because some parts of the computations are performed only once, in a pre-processing step before simulation starts. We discuss the applications of the method in both sensitivity and adjoint networks, and illustrate the theory with some examples. A program, called SDSEN, was written based on the theory developed in this chapter, and applied to some examples. Extension of sampled data simulation to the case of inconsistent initial conditions is another subject presented in this chapter.

Chapter 3 employs the theory implemented in chapter 2 and applies it to an important class of sampled data circuits, Delta-Sigma modulators. This chapter

presents the formulation of sensitivity networks for Delta-Sigma modulators, from which the sensitivity of the output magnitude with respect to any circuit elements is obtained. The method can be applied to all types/configurations of modulators if all elements, except the comparator, are linear. We establish a set of equations for the sensitivity network by taking the differential of the original network with respect to element h, and solve them in parallel to obtain the sensitivity of all nodes with respect to that element value. During the simulation we also need sensitivity of the output of the comparator with respect to its input. We distinguish between the unclocked and clocked comparators to explain their behavior.

Chapter 4 presents a fast and accurate method for the calculation of group delay and group delay sensitivity of periodically switched linear networks. Group delay is an important measure used in the design of precision filters. In a distortionless filter, the magnitude of the transfer function and the group delay must be flat over the passband. Since the method uses the MNA formulation of the circuit, and considers all types of linear elements, it can be used to simulate the switched-capacitor networks when the switches are replaced by their resistances, and the operational amplifiers have frequency-dependent as well as the other nonideal linear characteristics. Switched-current networks are another application, as long as the MOS transistors are modeled by linear components such as dependent sources, capacitors, and resistors. A program, called GRPSN, was written based on the theory developed in this chapter, and applied to some examples.

Chapter 5 introduces some nonfiltering applications of switched-current circuits. Switched-current is a relatively new analog sampled-data technique that promises to overcome the problems associated with switched-capacitor circuits. Although filtering applications have received most of the attention among switched-current circuits, there are other analog signal processing tasks that can be performed with

the same fabrication technology and circuit elements as those used in switchedcurrent filters. In this chapter, we present some non-filtering applications including a current-controlled oscillator, a modulator and a full-wave rectifier. We also propose a switched-current oversampling Delta-Sigma A/D converter.

Chapter 6 focuses on the distortion analysis of switched-current networks. Harmonic distortion in switched-current circuits is more severe than in switched-capacitor networks. Clock feed through and mismatch in the transistor threshold voltage are two major sources of distortion in switched-current circuits. These sources are introduced in this chapter, and their contributions to distortion are examined. We also present a general expression for the total harmonic distortion (THD) of non-linear circuits. Using this expression, we impose both upper and lower bounds on the THD of a switched-current memory cell.

Chapter 7 summarizes the important aspects of the work performed, and gives future research directions.

The thesis is concluded with three appendices. Appendix-A explains the numerical Laplace inversion and the stepping algorithm used in computation of the constant matrices required in SDSEN. Appendix-B presents the intermediate matrix manipulations used in the computation of group delay and group delay sensitivity. Appendix-C explains some selected switched-current building blocks that are used to implement the non-filtering applications.

## Chapter 2

## Time Domain Sensitivity of Linear Circuits Using Sampled Data Simulation

In the design of any system, it is important to know the effect of the variations of system parameters on the system's performance. In the case of lumped linear time invariant networks, a precise measure of this effect can be expressed in terms of the sensitivity to parameter values. The parameter can be a circuit element, such as a resistor or capacitor, or any other characteristic, such as the gain of the operational amplifier. There are several reasons for the importance of sensitivity in analog circuit design:

1. The study of the network sensitivity enhances insight into circuit behavior. By dividing the circuit parameters into critical and non-critical ones, an effective method is provided to simplify circuit models for efficient circuit analysis.

- Network sensitivity plays an important part in the design and optimization of reliable circuits. The objective of optimization is to minimize the discrepancy between the actual and the desired circuit behavior.

- 3. During the lifetime of a manufactured circuit, parameters are subject to change through aging, and environment effects, such as temperature and humidity. A sensitivity analysis is therefore required to find out which circuit parameters are critical.

- 4. The spread of parameter values resulting from the circuit manufacturing process requires the knowledge of the circuit performance in a certain range of parameter values, known as the tolerance range. This generates the need for tolerance analysis.

- 5. Knowledge of the network sensitivity can be used as a basis for comparing different circuits. It helps the circuit designer in selecting the proper circuit for a specified application.

Various sensitivity definitions of linear networks were introduced in the frequency domain [3]. In this chapter, we focus on the time domain sensitivity analysis using sampled data simulation method. An accurate and efficient method of computing time domain sensitivity is introduced. The method is accurate because no approximation is made, and is computationally efficient because some parts of the computations are performed only once, in a pre-processing step. It is similar to SDS in the manner of generating some constant matrices before simulation, and then providing the sensitivity at each time point by performing only matrix-vector multiplications.

We apply both sensitivity network and adjoint network [4-6] approaches to compute the time domain sensitivity. In the sensitivity network approach, the sensi-

tivities of all variables with respect to one element are found at all time points. In the adjoint network approach, the sensitivities of one variable with respect to all elements are calculated at one time point. The application of the sensitivity at one instant of time is in the calculation of error gradients for linear networks, and in the time domain sensitivity analysis of objective functions used in circuit optimization [3,7].

A review of sampled data simulation is given in section 1. Sections 2, 3, and 4 present my contributions to this topic. In section 2, I extend SDS to the case of inconsistent initial conditions. In section 3, I present the derivations for the time domain sensitivity using SDS. In this section, the derivations are for the sensitivity network. The adjoint network is discussed in section 4. A program was written in MATLAB, based on the theories developed in this chapter. Appendix-A shows the algorithms used in this program for computation of the constant matrices in the pre-processing step.

### 2.1 Sampled Data Simulation of Linear Circuits

Sampled data simulation (SDS) of linear circuits proposed in [1] is an efficient, accurate, stable, and explicit method for the transient analysis of lumped linear time invariant circuits. The method formulates a set of finite difference equations in the time domain. The solution of these equations gives the network response at fixed and equally spaced discrete instants of time. The fixed time interval between each solution can be chosen arbitrarily and does not depend on the circuit time constants. The transient solution at each time point requires only one matrix-vector multiplication. The algorithm is a general computer oriented formulation method that can be applied to any linear circuit.

To explain the method, we assume that the linear circuit is formulated using Modified Nodal Analysis (MNA) [3,8]:

$$\mathbf{G}\mathbf{x} + \mathbf{C}\frac{d\mathbf{x}}{dt} = \mathbf{w}(t), \qquad \mathbf{x}(0^{-}) = \mathbf{x}_{0}$$

(2.1)

where **G** is the conductance matrix  $(m \times m)$ , **C** the capacitance matrix  $(m \times m)$ ,  $\mathbf{w}(t)$  the input source vector  $(m \times 1)$ ,  $\mathbf{x}(t)$  the unknown vector  $(m \times 1)$  containing nodal voltages and some branch currents needed for MNA, and  $\mathbf{x}_0$  the initial condition vector  $(m \times 1)$ . The Laplace transform of (2.1) is

$$\mathbf{RX} = \mathbf{W} + \mathbf{Cx}(0^{-}),\tag{2.2}$$

where  $\mathbf{R} = \mathbf{G} + s\mathbf{C}$  is the system matrix. The formal solution of (2.2) is

$$X = R^{-1}W + R^{-1}Cx(0^{-}).$$

(2.3)

The first term on the right-hand side of (2.3) is related to the zero-state response, and the second term to the zero-input response of the linear circuit. Without loss of generality, we assume that there is one input source, which is a complex exponential  $w(t) = e^{st}$ . If there is more than one input source, the superposition principle is applied to sum the responses due to individual inputs. Taking the inverse Laplace transform of (2.3) and considering the circuit response at the first time point t = T.

$$\mathbf{x}(T) = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{W} \right) \begin{vmatrix} \mathbf{t} & + \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{C} \right) \\ \mathbf{t} & = T \end{vmatrix} \mathbf{x}(0^{-})$$

(2.4)

where  $\mathcal{L}^{-1}(\cdot)$  denotes the inverse Laplace transform. Define the constant matrices M and P as

$$\mathbf{P} = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{W} \right) \bigg|_{t = T} , \qquad (2.5)$$

$$\mathbf{M} = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \right) \middle| \quad \mathbf{t} = T$$

(2.6)

P is a vector with dimension  $m \times 1$ , and M is an  $m \times m$  matrix. Equations (2.5) and (2.6) are formal definitions for the M and P matrices. In practice, as explained in the next section, these matrices are computed numerically by the solutions of two system of equations in the time domain, i.e. by integrating the equations over the interval [0, T]. Rewrite (2.4) using (2.5) and (2.6)

$$\mathbf{x}(T) = \mathbf{P} + \mathbf{M}\mathbf{x}(0^{-}).$$

Next, consider the circuit response at the second time point t = 2T. In lumped linear networks, any time can be selected as the origin by taking the initial conditions into account. These initial conditions "reset" the problem so that the next calculation can start without any reference to previous history. To move the time origin from t = 0 to t = T, we must consider  $\mathbf{x}(T)$  as the initial conditions, and  $w(t) = e^{s(t+T)}$  as the input. The response at the end of the second time slot becomes

$$\mathbf{x}(2T) = \mathbf{P}e^{sT} + \mathbf{M}\mathbf{x}(T).$$

In general, by considering any time instant t = nT + T, the complete response is

$$\mathbf{x}(nT+T) = \mathbf{P} \ e^{snT} + \mathbf{M}\mathbf{x}(nT), \tag{2.7}$$

where T is the interval between two subsequent discrete time points at which the response is calculated. Eq.(2.7) computes the response of the circuit in a sampled data manner after equal intervals of time as long as the M and P matrices are known. These matrices are constant and need to be computed only once, in a pre-processing step before simulation starts.

Sampled data simulation can jump over large time steps and still maintain accuracy whereas simulators like SPICE [2,9] must take many small time steps to maintain accuracy. In addition, SDS is an explicit method that is not slowed down by iterations or time step control algorithms.

The time step T can be chosen arbitrarily and does not depend on the circuit time constants. Thus, if T is larger than the time steps taken by ordinary integration methods to solve (2.1), the sampled data simulation method will be computationally efficient. This is very evident if the response is needed at many time points. Simulation of oversampled Delta-Sigma modulators is an example of such a case.

#### 2.1.1 Numerical Computation of M and P Matrices

As suggested by (2.5), the vector **P** is obtained by setting the initial conditions to zero and numerically integrating the circuit equations (2.1) over the time interval [0,T]. According to (2.6), the matrix **M** is also obtained by integrating (2.1) while the input is an identity matrix (as explained in the next paragraph), over the interval [0,T], and then postmultiplying the result by the matrix **C**.

The matrix M can be computed also by turning all sources off, then considering the circuit response due to initial conditions only, and after a time interval T. This results in

$$\mathbf{x}(T) = \mathbf{M}\mathbf{x}(0^{-}).$$

As explained in [10], if we choose  $\mathbf{x}(0^-)$  to be the j-th column of an  $m \times m$  identity matrix, then, after integrating over the interval [0,T], we obtain  $\mathbf{x}(T)$  equal to the j-th column of M. This suggests that the j-th column of M can be calculated by setting the input sources to zero and by exciting only the j-th initial condition (by setting the j-th entry of  $\mathbf{x}(0^-)$  to unity and all other entries to zero), and numerically integrating the circuit equations (2.1) over the interval [0,T]. The complete M matrix is obtained by repeating this process for each column. The

reader is referred to [11] for more details about computations of M and P matrices, especially when the circuit is formulated using the MNA method.

The computation of M and P requires the time domain solution of (2.1), and hence a numerical integration method for the solution of a set of linear differential equations is required. We use numerical Laplace inversion [12–15] because it provides very accurate results and is equivalent to an absolutely stable, very high order integration method. As shown in [13], the numerical Laplace inversion correctly inverts the first p+1 terms of the Taylor series expansion of the time domain response of the network, and is equivalent to an integration method of order p (in our work we used p=18). If a small time step h is used at each time step, then the total truncation error is proportional to  $h^p$  and can be made arbitrarily small. Other integration methods such as the Backward Differentiation Formula and Runge-Kutta method [3] are normally lower order methods (p < 5), and can not provide the same level of accuracy. Furthermore, finite precision arithmetic on a digital computer limits the smallest time step that can be used with low order integration methods and ultimately the accuracy of the computed results.

#### **Computation Cost**

A computer program, called MPgen, was written in MATLAB [16] to compute M and P matrices. The program accepts the circuit matrices G and C, and the time interval T, then generates the M and P matrices. MPgen proceeds with the stepping algorithm [3] that is explained in Appendix-A. The matrix inversions indicated in (2.5) and (2.6) are performed by LU decompositions followed by forward-backward substitutions. The computation cost is of order  $O(m^3/3)$  [17]. However, the computation can be performed in sparse with the cost of  $O(m^{1.1-1.5})$  [18].

The order of integration used in MPgen is 18, and the local truncation error is set to  $10^{-9}$ , equivalent to 180 dB simulation accuracy per time step. The numerical Laplace inversion performed in MPgen requires complex arithmetic as opposed to real arithmetic in ordinary integration methods, and requires the solution of the network at 5 frequency points for each integration time step. As a result, the cost is usually larger than ordinary integration methods. However, this higher cost can be tolerated because of the accuracy we obtain, and because the calculation of the M and P matrices is needed only once in a pre-processing step, before simulation starts.

#### 2.2 Inconsistent Initial Conditions

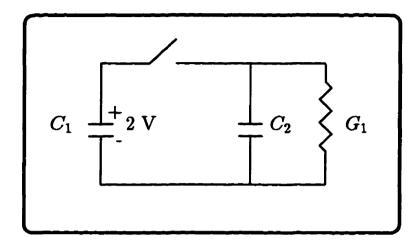

In some situations, especially in networks with ideal switches, it may happen that the initial conditions before switching and just after switching are not the same. Consider the network in Fig. 2.1, where the capacitor on the left is initially charged to 2V and the capacitor on the right has no charge. When the switch is closed, there are simultaneously two different voltages on the node: 2V from the left capacitor and 0V from the right one. This is a case of inconsistent initial conditions [19, 20].

In this section, we propose an extension to SDS by generating the transition matrices needed to integrate the circuit equations from  $nT^-$  to  $nT^+$ . In particular, we are looking for the matrix  $\mathbf{M}_0$  and the vector  $\mathbf{P}_0$  that provide the following relation at each instant nT, (n = 0, 1, ..., N):

$$\mathbf{x}(nT^+) = \mathbf{M}_0 \ \mathbf{x}(nT^-) + \mathbf{P}_0 \ e^{snT}. \tag{2.8}$$

If  $M_0$  and  $P_0$  are computed once at the beginning of the simulation, then the

Figure 2.1: Network with inconsistent initial voltages.

inconsistent initial conditions at each instant nT, (n = 0, 1, ..., N) can be handled very quickly by performing only a matrix-vector multiplication.

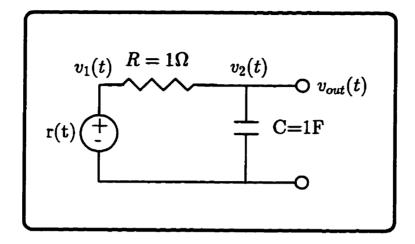

SDS provides the time domain response at either  $(0^-, T^-, \dots, NT^-)$  or  $(0^+, T^+, \dots, NT^+)$ . This means that the method can not detect the presence of Dirac impulses at the time instances nT. However, it considers the effect of impulses in the computation of responses at the next time point. To illustrate this, consider the simple RC circuit in Fig. 2.2 with zero initial condition, and the input of Dirac impulses applied at two different time points,  $r(t) = \delta(t) + \delta(t-3T)$ . The analytical solution of the circuit provides

$$v_{out}(t) = e^{-t}u(t) + e^{-(t-3T)}u(t-3T),$$

where  $u(\cdot)$  denotes the step function. The output  $v_{out}(t)$  at both  $nT^-$  and  $nT^+$  are shown in Table 2.1. The effects of Dirac impulses can be seen as the differences between  $v_{out}(0^-)$  and  $v_{out}(0^+)$ , and  $v_{out}(3T^-)$  and  $v_{out}(3T^+)$ .

To simulate the circuit using the sampled data simulation technique, we consider

Figure 2.2: RC circuit with Dirac impulse input.

| t                 | $v_{out}(t^-)$     | $v_{out}(t+)$      | $v_{out}(t)$       |

|-------------------|--------------------|--------------------|--------------------|

| Time              | Analytical         | Analytical         | SDS                |

| 0                 | 0                  | 1                  | 0                  |

| T                 | $e^{-T}$           | $e^{-T}$           | $e^{-T}$           |

| 2T                | $e^{-2T}$          | $e^{-2T}$          | $e^{-2T}$          |

| 3 <i>T</i>        | $e^{-3T}$          | $e^{-3T} + 1$      | $e^{-3T}$          |

| <b>4</b> <i>T</i> | $e^{-4T} + e^{-T}$ | $e^{-4T} + e^{-T}$ | $e^{-4T} + e^{-T}$ |

Table 2.1: The output of RC circuit at a few time points.

the modified nodal formulation of the circuit, and compute the M and P matrices.

$$\begin{bmatrix}

1 & -1 & 1 \\

-1 & 1+s & 0 \\

1 & 0 & 0

\end{bmatrix}

\begin{bmatrix}

V_1 \\

V_2 \\

I_E

\end{bmatrix} = \begin{bmatrix}

0 \\

0 \\

1

\end{bmatrix}$$

$$\mathbf{M} = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \right) \begin{vmatrix} \mathbf{C} & = \begin{bmatrix} 0 & 0 & 0 \\ 0 & e^{-T} & 0 \\ 0 & e^{-T} & 0 \end{bmatrix}$$

$$\mathbf{P} = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{W} \right) \begin{vmatrix} \mathbf{C} & = \begin{bmatrix} 0 & 0 & 0 \\ 0 & e^{-T} & 0 \end{bmatrix}$$

$$\mathbf{t} = \mathbf{T} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & e^{-T} & 0 \end{bmatrix}$$

The time domain response based on (2.7) becomes

$$\begin{bmatrix} v_{1}(nT+T) \\ v_{2}(nT+T) \\ i_{E}(nT+T) \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & e^{-T} & 0 \\ 0 & e^{-T} & 0 \end{bmatrix} \begin{bmatrix} v_{1}(nT) \\ v_{2}(nT) \\ i_{E}(nT) \end{bmatrix} + \begin{bmatrix} 0 \\ e^{-T} \\ e^{-T} \end{bmatrix} * g(nT)$$

(2.9)

where, because of the Dirac impulse inputs at t = 0 and t = 3T,

$$g(nT) = \begin{cases} 1 & \text{if } n = 0 \text{ or } n = 3T \\ 0 & \text{otherwise} \end{cases}$$

Assuming zero initial condition, (2.9) generates the time domain responses listed in the third column of Table 2.1. The response at t = 0 is valid for  $0^-$ , not for  $0^+$ . Also the response at t = 3T is valid only for  $3T^-$ .

A technique, called two step method, was proposed in [19] to take into account the effects of Dirac impulses and inconsistent initial conditions. In this technique, we first take a relatively long step forward from  $0^-$  to  $T^-$ . At this time point, we have good accuracy for the time domain response, and no Dirac impulse or inconsistent initial conditions are present. Next, we take exactly the same step size backward in time from  $T^-$  to  $0^+$ . The error of this step is very low since we are now dealing with a situation without a Dirac impulse or inconsistent initial conditions.

With the combination of the "two step" and "SDS" methods, we generate  $M_0$  and  $P_0$ , the matrices needed to integrate the circuit equations from  $nT^-$  to  $nT^+$  in

(2.8). First, integrate the circuit equations from  $nT^-$  to (nT + T)

$$\mathbf{x}(nT+T) = \mathbf{M}\mathbf{x}(nT^{-}) + \mathbf{P}e^{snT}.$$

(2.10)

Then, integrate the equations backward from (nT + T) to  $nT^+$

$$\mathbf{x}(nT^{+}) = \widehat{\mathbf{M}}\mathbf{x}(nT+T) + \widehat{\mathbf{P}}e^{-s(nT+T)}. \tag{2.11}$$

Substituting (2.10) into (2.11) yields

$$\mathbf{x}(nT^{+}) = \widehat{\mathbf{M}}\mathbf{M}\mathbf{x}(nT^{-}) + \left[\widehat{\mathbf{M}}\mathbf{P} + \widehat{\mathbf{P}}e^{-s(2nT+T)}\right]e^{snT}.$$

(2.12)

Comparing (2.12) with (2.8) gives

$$\mathbf{M}_0 = \widehat{\mathbf{M}} \mathbf{M} \tag{2.13}$$

$$\mathbf{P}_0 = \widehat{\mathbf{M}} \, \mathbf{P} e^{sT} + \widehat{\mathbf{P}} e^{-s(2nT+T)} \tag{2.14}$$

The matrices M, P,  $\widehat{M}$ , and  $\widehat{P}$  are constant. The matrix  $M_0$  is therefore constant and computed once. Only the last term of  $P_0$  in (2.14) depends on the time point. This is not a big concern because it introduces only a vector-vector addition per time point. In the special case, when the input is a unit step function,  $P_0$  also becomes a constant vector

$$\mathbf{P}_0 = \widehat{\mathbf{M}} \ \mathbf{P} + \widehat{\mathbf{P}}.$$

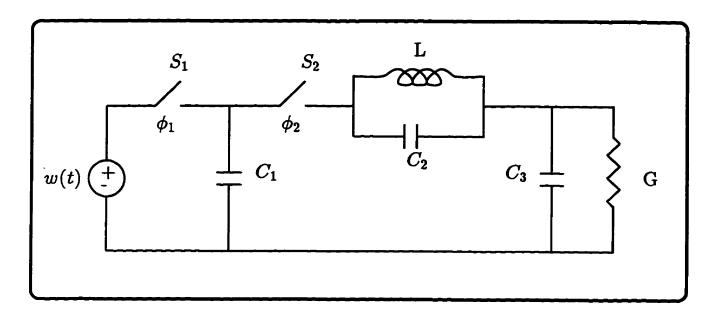

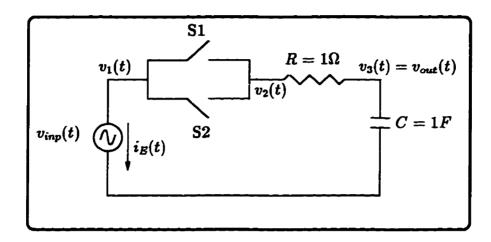

A program was written in MATLAB based on the above equations to generate  $M_0$  and  $P_0$  for switched linear networks. The program was tested on several circuits among which is the circuit in Fig. 2.3. This network was considered in [3] and [19]. It has two switches and two equal phases, the elements have unit values, and the switching frequency is 10 Hz. During the first phase, switch S2 is closed and S1 is open. In the second phase, the positions of the switches are reversed. A unit

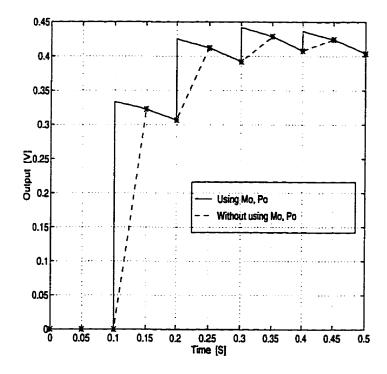

step input is applied. The time domain response is given in Fig.2.4. At the start of phase 1 (t = 0.1, 0.2, ...), the network has a loop of capacitors and thus a jump occurs at the output. To detect these jumps, we use the  $M_0$  and  $P_0$  matrices. After that, we proceed with M and P. For instance, at  $t = 0.1 \, s$ , to detect the jump, we compute

$$\mathbf{x}(0.1^+) = \mathbf{M}_0 \ \mathbf{x}(0.1^-) + \mathbf{P}_0.$$

Then, to integrate for the rest of the phase, we compute

$$\mathbf{x}(0.15) = \mathbf{M} \ \mathbf{x}(0.1^{+}) + \mathbf{P}.$$

The solid line in Fig.2.4 shows the response when using the  $M_0$  and  $P_0$  matrices all each switching instants. The dotted line shows the results when we proceed without using  $M_0$  and  $P_0$  (i.e. when we discard inconsistent initial conditions). Since the use of  $M_0$  and  $P_0$  costs only one matrix-vector multiplication, it is advisable to use them to obtain more reliable answers.

Figure 2.3: Switched network with inconsistent initial conditions.

Figure 2.4: Unit step response of the network in Fig.2.3 with and without using  $\mathbf{M}_0$  and  $\mathbf{P}_0$  matrices.

# 2.3 Time Domain Sensitivity Using Sensitivity Network

This section presents a new method for computation of the time domain sensitivity of linear networks. It is similar to sampled data simulation in the manner of generating some constant matrices before the simulation, and then providing the sensitivity at each time point by performing only matrix-vector multiplications. The method is accurate because no approximation is made, and efficient because most of the computation is performed only once, in a pre-processing step.

To evaluate the sensitivity of all components of the vector  $\mathbf{x}(t)$  with respect to a single parameter h, we start from the MNA formulation (2.1), and differentiate it with respect to h.

$$\frac{\partial \mathbf{G}}{\partial h}\mathbf{x}(t) + \mathbf{G}\frac{\partial \mathbf{x}(t)}{\partial h} + \frac{\partial \mathbf{C}}{\partial h}\frac{\partial \mathbf{x}(t)}{\partial t} + \mathbf{C}\frac{\partial}{\partial h}\frac{\partial \mathbf{x}(t)}{\partial t} = \mathbf{0}, \qquad \frac{\partial \mathbf{x}(0^{-})}{\partial h} = \frac{\partial \mathbf{x}_{0}}{\partial h} \quad (2.15)$$

We assume that h does not depend on the frequency variable s or the time step T, thus  $\frac{\partial \mathbf{w}(t)}{\partial h} = \frac{\partial e^{snT}}{\partial h} = 0$ . Define

$$\mathbf{z}(t) = \frac{\partial \mathbf{x}(t)}{\partial h}$$

and substitute it in (2.15)

$$\mathbf{G}\mathbf{z}(t) + \mathbf{C}\frac{d\mathbf{z}(t)}{dt} = -\left[\frac{\partial \mathbf{G}}{\partial h}\mathbf{x}(t) + \frac{\partial \mathbf{C}}{\partial h}\frac{d\mathbf{x}(t)}{dt}\right]. \tag{2.16}$$

In (2.16) there are the differentials of  $\mathbf{z}(t)$  and  $\mathbf{x}(t)$  with respect to time. Taking the Laplace transform of this equation, and considering the initial conditions of the variables  $\mathbf{z}(t)$  and  $\mathbf{x}(t)$  give

$$(\mathbf{G} + s\mathbf{C})\mathbf{Z} = -\left[\frac{\partial \mathbf{G}}{\partial h} + s\frac{\partial \mathbf{C}}{\partial h}\right]\mathbf{X} + \frac{\partial \mathbf{C}}{\partial h}\mathbf{x}(0^{-}) + \mathbf{C}\mathbf{z}(0^{-}),$$

or

$$\mathbf{RZ} = -\frac{\partial \mathbf{R}}{\partial h} \mathbf{X} + \frac{\partial \mathbf{C}}{\partial h} \mathbf{x}(0^{-}) + \mathbf{Cz}(0^{-}). \tag{2.17}$$

Eq. (2.17) describes the sensitivity network that is the same as the original network but with a different right-hand side. The input of the sensitivity network is composed of the solution of the original network( $\mathbf{X}$ ) and its initial condition ( $\mathbf{x}(0^-)$ ). Substituting  $\mathbf{X}$  from (2.3) into (2.17) gives

$$\mathbf{RZ} = -\frac{\partial \mathbf{R}}{\partial h} \left[ \mathbf{R}^{-1} \mathbf{C} \mathbf{x}(0^{-}) + \mathbf{R}^{-1} \mathbf{W} \right] + \frac{\partial \mathbf{C}}{\partial h} \mathbf{x}(0^{-}) + \mathbf{C} \mathbf{z}(0^{-}),$$

$$\mathbf{RZ} = -\frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1} \mathbf{W} + \left[ -\frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1} \mathbf{C} + \frac{\partial \mathbf{C}}{\partial h} \right] \mathbf{x}(0^{-}) + \mathbf{C} \mathbf{z}(0^{-}),$$

$$\mathbf{Z} = -\mathbf{R}^{-1} \frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1} \mathbf{W} + \underbrace{\left[ -\mathbf{R}^{-1} \frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1} \mathbf{C} + \mathbf{R}^{-1} \frac{\partial \mathbf{C}}{\partial h} \right]}_{\text{Provides } P_{\bullet}} \mathbf{x}(0^{-})$$

$$+ \underbrace{\mathbf{R}^{-1} \mathbf{C}}_{\text{Provides } M} \mathbf{z}(0^{-}). \tag{2.18}$$

The first term in (2.18) corresponds to the zero-state response of the sensitivity network, and its integral over the interval [0, T] provides the vector  $\mathbf{P_s}$

$$\mathbf{P_s} = \mathcal{L}^{-1} \left( -\mathbf{R}^{-1} \frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1} \mathbf{W} \right) \bigg|_{t=T} . \tag{2.19}$$

The second and third terms in (2.18) are related to the zero-input response of the sensitivity network, and their integral over the interval [0,T] provide the  $\mathbf{M_s}$  and  $\mathbf{M}$  matrices

$$\mathbf{M}_{\bullet} = \mathcal{L}^{-1} \left( -\mathbf{R}^{-1} \frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1} \mathbf{C} + \mathbf{R}^{-1} \frac{\partial \mathbf{C}}{\partial h} \right) \bigg|_{t=T} , \qquad (2.20)$$

$$\mathbf{M} = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} C \right) \bigg|_{t = T} . \tag{2.21}$$

In the time domain, (2.18) can be written in sampled data manner as

$$\mathbf{z}(nT+T) = \mathbf{M}_{s}\mathbf{x}(nT) + \mathbf{M}\mathbf{z}(nT) + \mathbf{P}_{s}e^{snT}$$

(2.22)

Eq.(2.22) is the core algorithm used in the sensitivity analysis described in this section. It can be used to compute the time domain sensitivity in a sampled data manner as long as the M<sub>s</sub> and P<sub>s</sub> matrices are known. The computation of P<sub>s</sub> and M<sub>s</sub>, based on (2.19) and (2.20), can be performed simultaneously with the computation of P and M, based on (2.5) and (2.6). These matrices are constant, and need to be computed only once. It is therefore reasonable to spend extra care in their calculations. The reader is referred to Appendix-A for the algorithm of calculating M<sub>s</sub> and P<sub>s</sub> using the numerical Laplace transform inversion. A program called MPMPSgen, was written in MATLAB to generate these matrices.

The accuracy and cost of performing (2.22) are the same as discussed in [1] for computing (2.7). If the matrices M,  $M_s$ , and  $P_s$  are known, then the only operations required in the sensitivity computation given in (2.22) are two matrix-vector multiplications and one vector addition for every sample of T seconds.

To simplify (2.19) and (2.20), we start from the following identity, and differentiate it with respect to h:

$$\mathbf{R} \mathbf{R}^{-1} = \mathbf{I}$$

$$\frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1} + \mathbf{R} \frac{\partial \mathbf{R}^{-1}}{\partial h} = \mathbf{0}$$

$$\frac{\partial \mathbf{R}^{-1}}{\partial h} = -\mathbf{R}^{-1} \frac{\partial \mathbf{R}}{\partial h} \mathbf{R}^{-1}$$

(2.23)

Substituting (2.23) into (2.19) provides

$$\mathbf{P_s} = \mathcal{L}^{-1} \left( \frac{\partial \mathbf{R}^{-1}}{\partial h} \mathbf{W} \right) \middle|_{t = T} = \mathcal{L}^{-1} \left( \frac{\partial}{\partial h} \left( \mathbf{R}^{-1} \mathbf{W} \right) \right) \middle|_{t = T}$$

$$= \frac{\partial}{\partial h} \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{W} \right) \bigg|_{t = T} = \frac{\partial \mathbf{P}}{\partial h}. \tag{2.24}$$

We took the differential operator  $\frac{\partial}{\partial h}$  out of the bracket because h does not depend on the frequency s or the time step T. The source vector  $\mathbf{W}$  is also assumed to be independent of h, thus  $\frac{\partial \mathbf{W}}{\partial h} = 0$ . The matrix  $\mathbf{M}_s$  can be similarly simplified by substituting (2.23) into (2.20)

$$\mathbf{M_s} = \mathcal{L}^{-1} \left( \frac{\partial \mathbf{R}^{-1}}{\partial h} \mathbf{C} + \mathbf{R}^{-1} \frac{\partial \mathbf{C}}{\partial h} \right) \bigg|_{t=T} = \mathcal{L}^{-1} \left( \frac{\partial}{\partial h} \left( \mathbf{R}^{-1} \mathbf{C} \right) \right) \bigg|_{t=T}$$

$$= \frac{\partial}{\partial h} \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{C} \right) \bigg|_{t=T} = \frac{\partial \mathbf{M}}{\partial h}. \tag{2.25}$$

Considering (2.24) and (2.25) in (2.22) results in

$$\mathbf{z}(nT+T) = \frac{\partial \mathbf{M}}{\partial h}\mathbf{x}(nT) + \mathbf{M}\mathbf{z}(nT) + \frac{\partial \mathbf{P}}{\partial h}e^{snT}.$$

(2.26)

It is interesting to note that (2.26) could have been directly derived from (2.7) by differentiating (2.7) with respect to h, and considering  $\frac{\partial e^{snT}}{\partial h} = 0$ . Of course, we still need to compute the  $P_s$  and  $M_s$  matrices by (2.19) and (2.20).

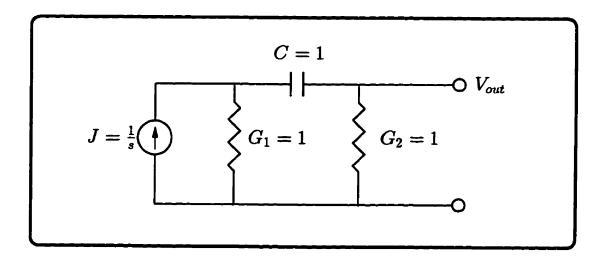

### 2.3.1 Example

We illustrate the procedures developed in the previous section with a simple example. In each step, the analytical solutions in the time domain will be given. Of course, for any nontrivial network, solutions of  $M_s$ ,  $P_s$ , and time domain sensitivities must be obtained numerically with the program MPMPSgen, or the algorithms in Appendix-A and the formula presented in the previous section. Consider the RC

circuit shown in Fig.2.5 with the unit step input and zero initial conditions. We calculate the time domain sensitivity of the output  $v_2(t)$  with respect to  $G_1$  and C.

First, we find the analytical solutions. The system equation is

$$\begin{bmatrix} G_1 + sC & -sC \\ -sC & G_2 + sC \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} \frac{1}{s} \\ 0 \end{bmatrix}, \quad \begin{bmatrix} v_1(0) \\ v_2(0) \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

The Laplace domain output is

$$V_2(s) = \frac{1}{(G_1 + G_2) \left[ s + \frac{G_1 G_2}{C(G_1 + G_2)} \right]}.$$

The exact time domain response is

$$v_2(t) = \frac{1}{(G_1 + G_2)} e^{-\frac{G_1 G_2 t}{C(G_1 + G_2)}}.$$

The derivative with respect to  $G_1$  is

$$\frac{\partial v_2(t)}{\partial G_1} = \frac{-1}{(G_1 + G_2)^2} \left[ 1 + \frac{G_2^2 t}{C(G_1 + G_2)} \right] e^{-\frac{G_1 G_2 t}{C(G_1 + G_2)}}.$$

Figure 2.5: RC circuit with unit step input.

The derivative with respect to C is

$$\frac{\partial v_2(t)}{\partial C} = \frac{G_1 G_2 t}{C^2 (G_1 + G_2)^2} e^{-\frac{G_1 G_2 t}{C(G_1 + G_2)}}.$$

For the element values indicated on Fig.2.5, and assuming the step size of t = T

$$v_2(nT) = \frac{1}{2}e^{-t/2}|_{t=nT} = \frac{1}{2}e^{-nT/2}$$

(2.27)

$$\frac{\partial v_2(nT)}{\partial G_1} = -\frac{1}{4}(1+\frac{t}{2})e^{-t/2} \mid_{t=nT} = -\frac{1}{4}(1+\frac{nT}{2})e^{-nT/2}$$

(2.28)

$$\frac{\partial v_2(nT)}{\partial C} = \frac{\frac{1}{4}te^{-t/2}}{|_{t=nT}} = \frac{1}{4}nTe^{-nT/2}$$

(2.29)

where n = 0, 1, ..., N is the number of time steps.

Next, we compute  $v_2(nT)$  and its sensitivities using M, P, M<sub>s</sub>, and P<sub>s</sub> matrices and the recurrence equations of (2.7) and (2.22).

$$\mathbf{R} = (\mathbf{G} + s\mathbf{C}) = \begin{bmatrix} 1 + s & -s \\ -s & 1 + s \end{bmatrix}$$

$$\mathbf{R}^{-1} = \begin{bmatrix} \frac{1+s}{1+2s} & \frac{s}{1+2s} \\ \frac{s}{1+2s} & \frac{1+s}{1+2s} \end{bmatrix}$$

$$\mathbf{M} = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{C} \right) \bigg|_{t=T} = \begin{bmatrix} \frac{1}{2} e^{-t/2} & -\frac{1}{2} e^{-t/2} \\ -\frac{1}{2} e^{-t/2} & \frac{1}{2} e^{-t/2} \end{bmatrix}_{t=T}$$

$$= \begin{bmatrix} \frac{1}{2} e^{-T/2} & -\frac{1}{2} e^{-T/2} \\ -\frac{1}{2} e^{-T/2} & \frac{1}{2} e^{-T/2} \end{bmatrix}$$

$$\mathbf{P} = \mathcal{L}^{-1} \left( \mathbf{R}^{-1} \mathbf{W} \right) \bigg|_{t=T} = \mathcal{L}^{-1} \begin{bmatrix} \frac{1+s}{(1+2s)s} \\ \frac{1}{1+2s} \end{bmatrix}_{t=T}$$

$$= \begin{bmatrix} -\frac{1}{2} e^{-T/2} + 1 \\ \frac{1}{2} e^{-T/2} \end{bmatrix}$$

To get the time domain response of the circuit at discretized points nT, we use (2.7)

$$\begin{bmatrix} v_1(nT+T) \\ v_2(nT+T) \end{bmatrix} = \begin{bmatrix} \frac{1}{2}e^{-T/2} & -\frac{1}{2}e^{-T/2} \\ -\frac{1}{2}e^{-T/2} & \frac{1}{2}e^{-T/2} \end{bmatrix} \begin{bmatrix} v_1(nT) \\ v_2(nT) \end{bmatrix} + \begin{bmatrix} -\frac{1}{2}e^{-T/2} + 1 \\ \frac{1}{2}e^{-T/2} \end{bmatrix} (2.30)$$

It is clear that (2.30) generates the same response as indicated in (2.27) at time points nT, (n = 0, 1, ..., N).

To find the sensitivity with respect to  $G_1$ , we first calculate  $\frac{\partial \mathbf{R}}{\partial G_1}$ , and then substitute it in (2.19) and (2.20) to obtain the corresponding  $\mathbf{P_s}$  and  $\mathbf{M_s}$  matrices.

$$\frac{\partial \mathbf{R}}{\partial G_{1}} = \begin{bmatrix} 1 & 0 \\ 0 & 0 \end{bmatrix}

\mathbf{P_{s}} = \mathcal{L}^{-1} \left( -\mathbf{R}^{-1} \frac{\partial \mathbf{R}}{\partial G_{1}} \mathbf{R}^{-1} \mathbf{W} \right) \Big|_{t=T} = \mathcal{L}^{-1} \begin{bmatrix} -\frac{(1+s)^{2}}{(1+2s)^{2}s} \\ -\frac{1+s}{(1+2s)^{2}} \end{bmatrix}_{t=T}

= \begin{bmatrix} \frac{1}{8} T e^{-T/2} + \frac{3}{4} e^{-T/2} - 1 \\ \frac{1}{8} T e^{-T/2} - \frac{1}{4} e^{-T/2} \end{bmatrix},

\mathbf{M_{s}} = \mathcal{L}^{-1} \left( -\mathbf{R}^{-1} \frac{\partial \mathbf{R}}{\partial G_{1}} \mathbf{R}^{-1} \mathbf{C} \right) \Big|_{t=T} = \mathcal{L}^{-1} \begin{bmatrix} -\frac{1+s}{(1+2s)^{2}} & \frac{1+s}{(1+2s)^{2}} \\ -\frac{1+s}{(1+2s)^{2}} & \frac{1+s}{(1+2s)^{2}} \end{bmatrix}_{t=T}

= \begin{bmatrix} -\frac{1}{8} T e^{-T/2} - \frac{1}{4} e^{-T/2} & \frac{1}{8} T e^{-T/2} + \frac{1}{4} e^{-T/2} \\ \frac{1}{8} T e^{-T/2} - \frac{1}{4} e^{-T/2} & -\frac{1}{8} T e^{-T/2} + \frac{1}{4} e^{-T/2} \end{bmatrix}.$$

To calculate the time domain sensitivity of all nodes with respect to  $G_1$ , rewrite (2.22) as follows

$$\begin{bmatrix} \frac{\partial v_{1}(nT+T)}{\partial G_{1}} \\ \frac{\partial v_{2}(nT+T)}{\partial G_{1}} \end{bmatrix} = \begin{bmatrix} -\frac{1}{8}Te^{-T/2} - \frac{1}{4}e^{-T/2} & \frac{1}{8}Te^{-T/2} + \frac{1}{4}e^{-T/2} \\ \frac{1}{8}Te^{-T/2} - \frac{1}{4}e^{-T/2} & -\frac{1}{8}Te^{-T/2} + \frac{1}{4}e^{-T/2} \end{bmatrix} \begin{bmatrix} v_{1}(nT) \\ v_{2}(nT) \end{bmatrix} + \begin{bmatrix} \frac{1}{2}e^{-T/2} & -\frac{1}{2}e^{-T/2} \\ -\frac{1}{2}e^{-T/2} & \frac{1}{2}e^{-T/2} \end{bmatrix} \begin{bmatrix} \frac{\partial v_{1}(nT)}{\partial G_{1}} \\ \frac{\partial v_{2}(nT)}{\partial G_{1}} \end{bmatrix} +$$

$$\begin{bmatrix} \frac{1}{8}Te^{-T/2} + \frac{3}{4}e^{-T/2} - 1\\ \frac{1}{8}Te^{-T/2} - \frac{1}{4}e^{-T/2} \end{bmatrix}.$$

(2.31)

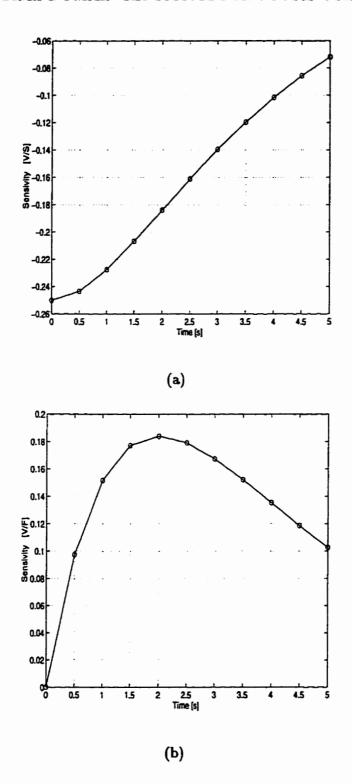

Assuming zero initial conditions for the circuit in Fig. 2.5 and for its sensitivity network, Eq.(2.31) generates the same results as that of (2.28) at discretized time points nT, (n = 0, 1, ..., N).

Without going into the details, and following the same procedure, we find the following equations for the time domain sensitivity of the network with respect to C.

$$\frac{\partial \mathbf{R}}{\partial \mathbf{C}} = \begin{bmatrix} s & -s \\ -s & s \end{bmatrix}$$

$$\mathbf{P_s} = \begin{bmatrix} -\frac{1}{4}Te^{-T/2} \\ \frac{1}{4}Te^{-T/2} \end{bmatrix}$$

$$\mathbf{M_s} = \begin{bmatrix} -\frac{1}{4}Te^{-T/2} & -\frac{1}{4}Te^{-T/2} \\ -\frac{1}{4}Te^{-T/2} & \frac{1}{4}Te^{-T/2} \end{bmatrix}$$

$$\begin{bmatrix} \frac{\partial v_{1}(nT+T)}{\partial C} \\ \frac{\partial v_{2}(nT+T)}{\partial C} \end{bmatrix} = \begin{bmatrix} -\frac{1}{4}Te^{-T/2} & -\frac{1}{4}Te^{-T/2} \\ -\frac{1}{4}Te^{-T/2} & \frac{1}{4}Te^{-T/2} \end{bmatrix} \begin{bmatrix} v_{1}(nT) \\ v_{2}(nT) \end{bmatrix} + \begin{bmatrix} \frac{1}{2}e^{-T/2} & -\frac{1}{2}e^{-T/2} \\ -\frac{1}{2}e^{-T/2} & \frac{1}{2}e^{-T/2} \end{bmatrix} \begin{bmatrix} \frac{\partial v_{1}(nT)}{\partial C} \\ \frac{\partial v_{2}(nT)}{\partial C} \end{bmatrix} + \begin{bmatrix} -\frac{1}{4}Te^{-T/2} \\ \frac{1}{4}Te^{-T/2} \end{bmatrix} (2.32)$$

Again, assuming zero initial conditions for the original and the sensitivity networks, Eq.(2.32) generates exactly the same results as (2.29) at time points nT. Fig. 2.6 shows the simulation results for the sensitivity of the output with respect to  $G_1$  and C at a few time points.

Figure 2.6: Simulation results for the sensitivity of  $v_2(t)$  (a) with respect to  $G_1$ , and (b) with respect to C.

# 2.4 Time Domain Sensitivity Using Adjoint Network

The time domain sensitivity of one variable, which is usually the single output  $\phi$ , with respect to many variable elements  $h_i$  at one instant of time  $(t=t_f)$  is considered in this section. The application of sensitivity at one instant of time is in the calculation of error gradients for linear networks, and in the time domain sensitivity analysis of objective functions used in circuit optimization [3,5,7]. Another application is in the time domain sensitivity analysis of switched networks at the end of each phase when the circuit does not reach the steady state. Transient analysis of rise/fall time in digital circuits and transmission lines are the other types of applications.

In the <u>frequency domain</u>, the application of adjoint network (sometimes called transpose network) in the calculation of sensitivity is well known [3,5]. The procedure for computing frequency domain sensitivity using an adjoint network is summarized as follows:

- I- Solve the given system of linear equations  $\mathbf{R}\mathbf{X} = \mathbf{W}$ .

- II- Solve the adjoint network defined by  $\mathbf{R}^t \mathbf{X}^a = -\mathbf{d}$  where  $\mathbf{d}$  is a constant vector that relates the output  $\phi$  to the nodal vector  $\mathbf{X}$ ,  $\phi = \mathbf{d}^t \mathbf{X}$ .

- III- For each parameter  $h_i$ , form  $\frac{\partial \mathbf{R}}{\partial h_i}$ , and insert this in the following equation to compute  $\frac{\partial \phi}{\partial h_i}$

$$\frac{\partial \phi}{\partial h_i} = (\mathbf{X}^a)^t \frac{\partial \mathbf{R}}{\partial h_i} \mathbf{X} \tag{2.33}$$

As the vector X and  $X^a$  are independent of the parameters  $h_i$ , Eq.(2.33) requires the solution of only two sets of algebraic equations (in steps I and II), irrespective of the number of parameters  $h_i$ .

In the <u>time domain</u>, the sensitivity is computed by the procedure explained in [7] as follows:

- 1- Perform a transient analysis of the original network N for the time interval  $t = [0, t_f]$ . Obtain i(t) or v(t) for resistive,  $\dot{v}(t)$  for capacitive, and  $\dot{i}(t)$  for inductive branches.

- 2- Construct the adjoint network  $\widehat{N}$  according to the fact that the adjoint network of R. L. and C are unchanged, and the adjoint network of dependent sources are dependent sources with a new configuration and transfer function given in [7]. Set all initial conditions and all independent sources equal to zero, and apply a current source of  $-\delta(t)$  between the output nodes.

- 3- Perform a transient analysis of the adjoint network  $\widehat{N}$  for the time interval  $\tau = [0, t_f]$ , where  $\tau = t_f t$  (time reversal). Obtain  $\hat{i}(\tau)$  or  $\hat{v}(\tau)$  for resistive branches,  $\hat{v}(\tau)$  for capacitive, and  $\hat{i}(\tau)$  for inductive branches.

- 4- Evaluate the following equations to find the sensitivity of the output with respect to R, and C (for other elements refer to [7]).

$$\frac{\partial v_{out}(t_f)}{\partial R} = \int_0^{t_f} \left[ \hat{i}_R(\tau) i_R(t) \right]_{\tau = t_f - t} dt$$

$$\frac{\partial v_{out}(t_f)}{\partial C} = -\int_0^{t_f} \left[ \hat{v}_C(\tau) \dot{v}_C(t) \right]_{\tau = t_f - t} dt$$

### 2.4.1 Adjoint Network in Time Versus Frequency Domain

In the time domain, the adjoint network is obtained from a more general principle known as Tellegen's theorem [7,21,22], whereas in the frequency domain, the adjoint network can be obtained after some matrix manipulations [3]. The applications of the adjoint network in these two domains were derived separately without making any explicit link between them. We establish here a one-by-one correspondence between these two applications as shown in Table 2.2. Based on the relations shown in this table, the adjoint network can be established in either the time or frequency domain, and finally, can be transformed to the other one, if necessary. Considering

| Frequency Domain                                        | Time Domain                                               |

|---------------------------------------------------------|-----------------------------------------------------------|

| step I: Solving the original system                     | step 1: Solving the original system                       |

| step II : Creating the transpose system                 | step 2: Constructing the adjoint network                  |

| of $\mathbf{R}^t \mathbf{X}^a = -\mathbf{d}$            | $\widehat{N}$ and applying a source of $-\delta(t)$       |

| step III: Multiplication in the                         | step 3: The solution of the transpose                     |

| frequency domain                                        | system reversed in time, needed for the                   |

|                                                         | convolution involved in step 4                            |

|                                                         | step 4 : Convolution of $i_R(t)$ and $\hat{i}_R(t)$       |

|                                                         | for resistive elements, and convolution of                |

|                                                         | $\hat{v}_C(t)$ and $\hat{v}_C(t)$ for capacitive elements |

| step III: If the parameter h is a                       | step 4: If the parameter h is a frequency                 |

| frequency dependent element,                            | dependent element, use the derivative of                  |

| $\frac{\partial \mathbf{R}}{\partial h}$ produces a $s$ | the voltage, $\dot{v}(t)$                                 |

Table 2.2: Relationship between the adjoint methods in time and frequency domains.

this, and by applying sampled data simulation, we introduce two approaches for time domain sensitivity of linear networks using an adjoint network.

### 2.4.2 Approach I: Convolution

The formulation of the adjoint network in the frequency domain is straightforward. It performs a multiplication in the frequency domain (step III) which can be translated to a convolution in the time domain. Since the sampled data simulation is an accurate and efficient method for computing the circuit response in the time domain, we transform the frequency domain sensitivity analysis into the time domain as follows:

1- Solve the original system of equations  $Gx(t)+C\frac{dx(t)}{dt}=w(t)$  in the time domain using P and M matrices

$$\mathbf{x}(nT+T) = \mathbf{M}\mathbf{x}(nT) + \mathbf{P}e^{snT} , \quad n = 0, 1, \dots, N$$

where P and M are given by (2.5) and (2.6). This step is equivalent to solving RX = W in frequency domain.

2- Solve the system of equations  $Gy(t) + C\frac{dy(t)}{dt} = \frac{dw(t)}{dt}$  in the time domain to get the solution of  $y(t) = \frac{dx(t)}{dt} = \dot{x}(t)$

$$\dot{\mathbf{x}}(nT+T) = \mathbf{M}\dot{\mathbf{x}}(nT) + \dot{\mathbf{P}} e^{inT} , \quad n = 0, 1, \dots, N$$

where M is the same as in the previous step, and

$$\dot{\mathbf{P}} = \mathcal{L}^{-1} \left( s \mathbf{R}^{-1} \mathbf{W} \right) \bigg|_{t = T}$$

We need  $\dot{\mathbf{x}}(t)$  to compute the sensitivity with respect to frequency dependent elements like capacitors and inductors.

3- Solve the transpose system of  $\mathbf{G}^t \mathbf{x}^a(t) + \mathbf{C}^t \frac{d\mathbf{x}^a(t)}{dt} = -\mathbf{d}\delta(t)$  in the time domain which is equivalent to the solution of the transpose system  $\mathbf{R}^t \mathbf{X}^a = -\mathbf{d}$  in the frequency domain.

$$\mathbf{x}^a(nT+T) = \mathbf{M}^t \mathbf{x}^a(nT) + \mathbf{P}^a g(nT)$$

,  $n = 0, 1, \dots, N$

where, because of the Dirac impulse input,

$$g(nT) = \begin{cases} 1 & \text{if } n = 0 \\ 0 & \text{otherwise} \end{cases}$$

and  $M^t$  and  $P^a$  are given by

$$\mathbf{M}^{t} = \mathcal{L}^{-1}\left((\mathbf{R}^{t})^{-1}\right) \left| \begin{array}{c} t = T \end{array} \right| = \mathcal{L}^{-1}\left((\mathbf{R}^{-1})^{t}\right) \left| \begin{array}{c} t = T \end{array} \right| = \operatorname{transpose} \text{ of } M$$

$\mathbf{P}^{a} = \mathcal{L}^{-1}\left(-(\mathbf{R}^{t})^{-1}\mathbf{d}\right) \left| \begin{array}{c} t = T \end{array} \right|$

4- Evaluate the equation  $F(s) = \frac{\partial \phi}{\partial h_i} = (\mathbf{X}^a)^t \frac{\partial \mathbf{R}}{\partial h_i} \mathbf{X}$  in the time domain using discrete-time convolution. For instance, if  $h_i$  is a conductance appearing at column #1 and row #1 of  $\mathbf{R}$

$$F(s) = X_1^a X_1$$

$$f(NT) = x_1^a(NT) \oplus x_1(NT) = \sum_{m=0}^N x_1^a(mT) x_1(NT - mT).$$

If  $h_i$  is a capacitor appearing at column #1 and row #1 of R

$$F(s) = X_1^a \ s \ X_1$$

$$f(NT) = x_1^a(NT) \oplus \dot{x}_1(NT) = \sum_{m=0}^N x_1^a(mT)\dot{x}_1(NT - mT).$$

Since we are interested in the sensitivity at one instant in time, the above convolutions are evaluated at only that time point (NT). The computation cost depends on N. If we do not consider the steady state, and concentrate only on the transient response of the circuit and its sensitivity, N is normally a small number. In switched networks, if one is interested in the time domain analysis within each phase, N could be less than 10.

The drawback of this approach is that we are convolving the samples of two signals  $x_1$  and  $x_1^a$  to generate the time domain equivalent of the multiplication  $X_1^a(s)$   $X_1(s)$  in the Laplace domain. This is accurate only if the original analog signals are sampled at a rate that is twice the maximum frequency component of the signals. Otherwise, some errors are encountered in the discrete-time convolution due to sampling. Another minor drawback may be the need for memory storage for the circuit response from 0 to NT for the purpose of convolution.

## 2.4.3 Approach II: Numerical Laplace Transform Inversion

This approach is basically a translation of the adjoint method from the frequency domain into the time domain. Assume X to be the solution of the original network in the frequency domain

$$RX = W$$

and  $X^a$  to be the solution of the adjoint network

$$\mathbf{R}^t \mathbf{X}^a = -\mathbf{d}$$

.

where d is a selector vector defining the output  $\phi$

$$\phi = \mathbf{d}^t \mathbf{X}.$$

Also assume m to be the size of the system matrix  $\mathbf{R}$ , and l the number of parameters  $h_i$  with respect to which the sensitivities are computed. Define matrix  $\mathbf{Q}$  as