# Noise and Clock Jitter Analysis of Sigma-Delta Modulators and Periodically Switched Linear Networks

by

#### Yikui Dong

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical Engineering

Waterloo, Ontario, Canada, 1999

©Yikui Dong 1999

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-38235-4

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### **Abstract**

This thesis investigates general computer-aided noise and clock jitter analysis of sigma-delta modulators. The circuit is formulated at electrical circuit level. Modulators with either switched-capacitor, switched-current, or continuous-time loop-filters can be analyzed. The methods and algorithms are also applicable to periodically switched linear networks, such as switched-capacitor and switched-current filters.

Thermal noise is an important source limiting circuit resolution, but traditional frequency domain noise analysis is not applicable to sigma-delta modulators. Noise analysis of sigma-delta modulators has not been presented before. In this thesis we give a new time domain method. It is applied to thermal noise analysis and dithering analysis.

Clock jitter is another major source that results in performance degradation of analog sampled-data circuits. Despite the fact that clock jitter is usually random, previous methods were restricted to periodic jitter analysis. They are based on classical switched-capacitor methods that analyze the circuit by exploiting its periodic switching nature. The introduction of random jitter destroys the periodic switching pattern, and classical methods are not applicable. To overcome this problem, we present a new *varying-step* sampled-data method for analysis of linear time invariant circuits. It is applied to clock jitter analysis of periodically switched linear networks and sigma-delta modulators. No restrictions on the jitter waveform were imposed. It can handle either periodic or random clock jitter analysis.

Transition matrix and input-transfer vector play important roles in circuit theory. Evaluations of their time derivatives are needed for the special sampled-data method. In this thesis, direct computation methods for the derivative matrices and vectors are presented. They are based on circuit theory concepts and aimed at numerical computation.

The theories have been implemented in a computer program, and validated on nu-

merical examples. Comparisons are made with exact analysis, physical measurements, or experimental observations. The algorithms are efficient, and transient analysis of a typical sigma-delta modulator for several hundred thousand clock cycles is obtained in the order of minutes.

#### Acknowledgements

This work would have been impossible without the inputs from many people.

A few words cannot express all my gratitude to my supervisor, Professor Ajoy Opal. I would like to thank him for introducing me to this interesting field, for his excellent guidance and valuable comments throughout this research, and for his financial support for my graduate studies at Waterloo.

I am deeply grateful to Professor Jiri Vlach, who not only gave me good advice, but also spent so much time and energy in reading my thesis and helping me to refine it. This dissertation would be much poorer without his generous help.

I am very fortunate to be able to work with Professor Bosco Leung and Professor Stanley Lipshitz, with whom I have had many fruitful discussions on the contents of this thesis. I benefited greatly from their expertise.

I would like to thank all my friends who have provided me with joy and warmth throughout these years.

# To my parents for their love and encouragement

# **Contents**

| 1 | Intr | roduction                          |                                           |    |

|---|------|------------------------------------|-------------------------------------------|----|

|   | 1.1  | Motiva                             | ation                                     | 1  |

|   | 1.2  | Object                             | ives                                      | 4  |

|   | 1.3  | Thesis                             | Organization                              | 5  |

|   | 1.4  | Origin                             | al Contribution                           | 6  |

| 2 | Sign | na Delta                           | a Modulators: Background Review           | 8  |

|   | 2.1  | Introdu                            | uction to Sigma Delta Modulators          | 8  |

|   | 2.2  | 2 Trends in Circuit Implementation |                                           |    |

|   |      | 2.2.1                              | Switched-Capacitor Sigma-Delta Modulators | 13 |

|   |      | 2.2.2                              | Switched-Current Sigma-Delta Modulators   | 14 |

|   |      | 2.2.3                              | Continuous-Time Sigma-Delta Modulators    | 15 |

|   | 2.3  | Simula                             | ation Methods and Tools                   | 16 |

|   |      | 2.3.1                              | Challenge                                 | 17 |

|   |      | 2.3.2                              | Classification and Review                 | 18 |

|   |      | 2.3.3 Summary                                             | 24 |

|---|------|-----------------------------------------------------------|----|

|   | 2.4  | Sampled Data Analysis of Analog Circuits                  | 26 |

|   | 2.5  | A Numerical Laplace Transform Inversion Method            | 30 |

| 3 | Nois | e Analysis                                                | 33 |

|   | 3.1  | Introduction                                              | 33 |

|   | 3.2  | Circuit Noise Sources and Models                          | 34 |

|   | 3.3  | Noise Analysis Methods: Review                            | 37 |

|   |      | 3.3.1 Linear Circuits and Frequency Domain Noise Analysis | 38 |

|   |      | 3.3.2 Nonlinear Circuits and Time Domain Noise Analysis   | 40 |

|   | 3.4  | New Time Domain Noise Analysis Method                     | 42 |

|   |      | 3.4.1 Time Domain Thermal Noise Model                     | 43 |

|   |      | 3.4.2 Noise Simulation Method                             | 45 |

|   | 3.5  | Numerical Examples                                        | 47 |

|   |      | 3.5.1 Simulation Accuracy: A Simple RC Circuit            | 47 |

|   |      | 3.5.2 Linear Time Invariant Circuits                      | 51 |

|   |      | 3.5.3 Periodically Switched Linear Circuits               | 53 |

|   |      | 3.5.4 Oversampled Sigma-Delta Modulators                  | 55 |

|   | 3.6  | Chapter Summary                                           | 59 |

| 4 | Dith | ering Analysis                                            | 62 |

|   | A 1  | Introduction                                              | 62 |

|   | 4.2 | New I    | Dithering Analysis Method                                      | 64         |

|---|-----|----------|----------------------------------------------------------------|------------|

|   | 4.3 | Nume     | rical Examples                                                 | 64         |

|   |     | 4.3.1    | A Switched-Capacitor Sigma-Delta Modulator                     | 65         |

|   |     | 4.3.2    | A Continuous-Time Sigma-Delta Modulator                        | 67         |

|   | 4.4 | Chapte   | er Summary                                                     | 69         |

| 5 | Var | ying-Sto | ep Sampled-Data Analysis                                       | 70         |

|   | 5.1 | Introd   | uction                                                         | 71         |

|   | 5.2 | Clock    | Jitter Analysis: Review                                        | 72         |

|   |     | 5.2.1    | Digital Circuit Approach                                       | 72         |

|   |     | 5.2.2    | Electrical Circuit Approach                                    | 73         |

|   | 5.3 | Varyin   | g-Step Sampled-Data Analysis                                   | 74         |

|   |     | 5.3.1    | Background                                                     | 74         |

|   |     | 5.3.2    | The Algorithm                                                  | 76         |

|   |     | 5.3.3    | Simulation Accuracy                                            | 77         |

|   |     | 5.3.4    | Simulation Cost                                                | 78         |

|   |     | 5.3.5    | Storage Requirements                                           | <b>7</b> 9 |

|   |     | 5.3.6    | Application: Arbitrary Waveform Clock Jitter Analysis          | 80         |

|   | 5.4 | Time I   | Derivatives of the Transition Matrix and Input Transfer Vector | 82         |

|   |     | 5.4.1    | The method                                                     | 83         |

|   |     | 5.4.2    | Example: A RLC Circuit                                         | 85         |

|   |     | 512      | Comments                                                       | 00         |

|    | 5.5             | Numerical Examples                               | 89  |  |

|----|-----------------|--------------------------------------------------|-----|--|

|    |                 | 5.5.1 Simulation Accuracy: A Bandpass Filter     | 90  |  |

|    |                 | 5.5.2 A Switched-Capacitor Filter                | 92  |  |

|    |                 | 5.5.3 A Switched-Current Filter                  | 94  |  |

|    | 5.6             | Chapter Summary                                  | 97  |  |

| 6  | Cloc            | k Jitter Analysis                                | 98  |  |

|    | 6.1             | Introduction                                     | 98  |  |

|    | 6.2             | Clock Jitter Analysis Method                     | 00  |  |

|    | 6.3             | Numerical Examples                               | 101 |  |

|    |                 | 6.3.1 A Switched-Capacitor Sigma-Delta Modulator | 01  |  |

|    |                 | 6.3.2 A Continuous-Time Sigma-Delta Modulator    | 104 |  |

|    |                 | 6.3.3 Comparison with Measurements               | 106 |  |

|    | 6.4             | Chapter Summary                                  | 109 |  |

| 7  | Con             | clusion 1                                        | 110 |  |

|    | 7.1             | Summary and Discussion                           | 110 |  |

|    | 7.2             | Future Work                                      | 112 |  |

| A  | SDN             | oise Simulator 1                                 | 113 |  |

| Bi | Bibliography 12 |                                                  |     |  |

# **List of Tables**

| 2.1 | Simulators for Sigma-delta Modulators             | 25  |

|-----|---------------------------------------------------|-----|

| 3.1 | Magnitudes at Fundamental Frequencies (Bilateral) | 48  |

| 5.1 | SC Filter: Capacitor Ratios                       | 93  |

| 6.1 | Simulation Time for 74k Clock Cycles              | 106 |

# **List of Figures**

| 2.1  | A sigma-delta modulation A/D converter                               | 9  |

|------|----------------------------------------------------------------------|----|

| 2.2  | Quantization noise power spectrum density                            | 10 |

| 2.3  | First-order sigma-delta modulation A/D converter                     | 10 |

| 2.4  | Second-order sigma-delta modulator                                   | 12 |

| 2.5  | Noise transfer characteristics of sigma-delta modulators             | 13 |

| 3.1  | Power spectrum density for thermal noise                             | 35 |

| 3.2  | Resistor thermal noise model                                         | 36 |

| 3.3  | Switch thermal noise model                                           | 37 |

| 3.4  | Opamp thermal noise model                                            | 37 |

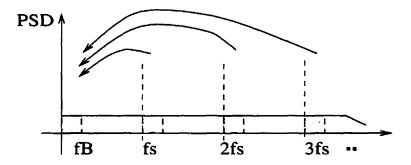

| 3.5  | Aliasing into baseband                                               | 39 |

| 3.6  | Random noise waveform                                                | 41 |

| 3.7  | PSD of a noise waveform (A) 256 samples (B) 10 sets of 256 samples . | 44 |

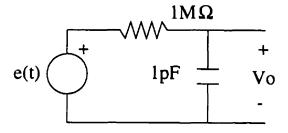

| 3.8  | A RC circuit                                                         | 48 |

| 3.9  | RC circuit: simulation accuracy                                      | 49 |

| 3.10 | RC circuit: thermal noise simulation                                 | 51 |

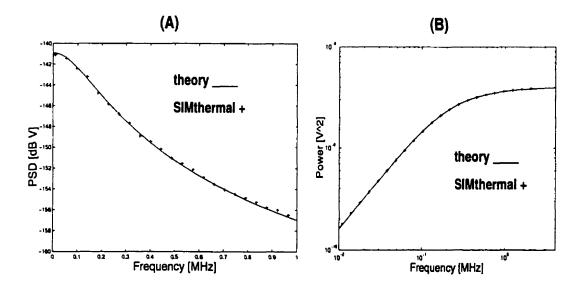

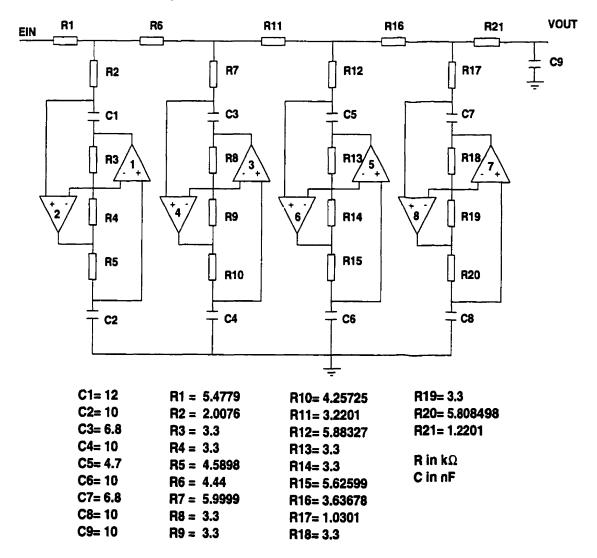

| 3.11 | A ninth order low-pass filter                                              | 52 |

|------|----------------------------------------------------------------------------|----|

| 3.12 | 9th-order filter: thermal noise simulation                                 | 53 |

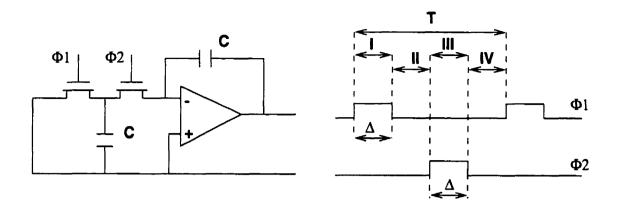

| 3.13 | A switched-capacitor integrator                                            | 54 |

| 3.14 | SC integrator: thermal noise simulation                                    | 54 |

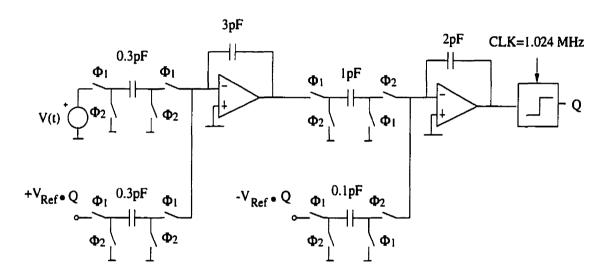

| 3.15 | A second order switched-capacitor SDM                                      | 55 |

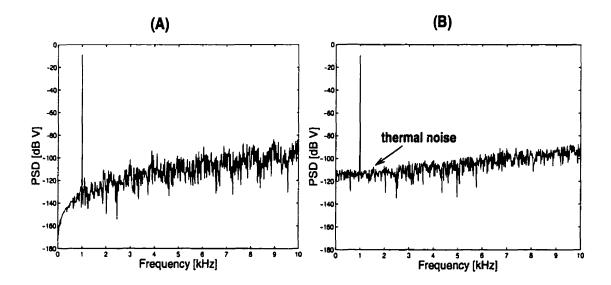

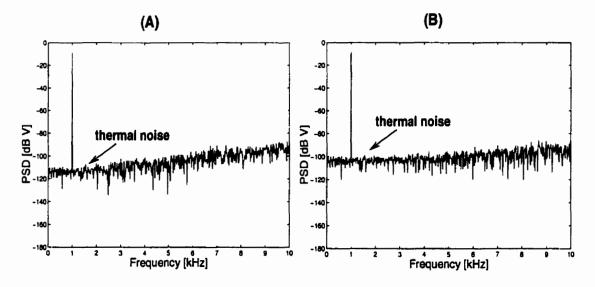

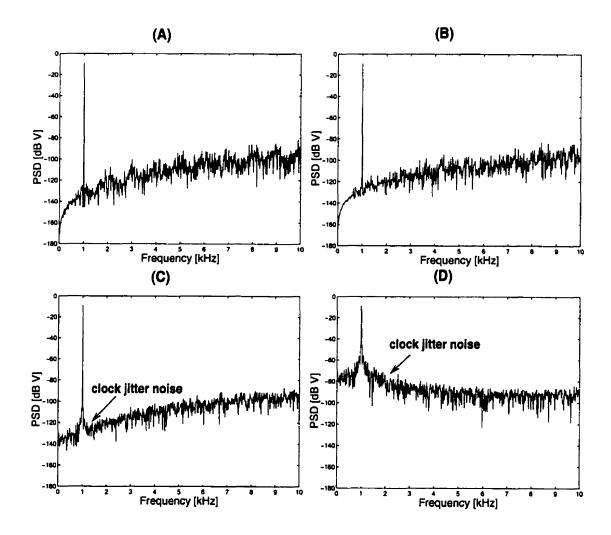

| 3.16 | SC SDM: (A) ideal elements (B) with thermal noise                          | 56 |

| 3.17 | SC SDM: (A) with thermal noise (B) with increased thermal noise            | 57 |

| 3.18 | A second order continuous-time SDM                                         | 58 |

| 3.19 | CT SDM: (A) ideal elements (B) with thermal noise                          | 58 |

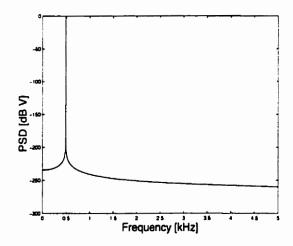

| 3.20 | S. Sen, PhD thesis: $f_s = 10$ MHz, Idle channel test                      | 60 |

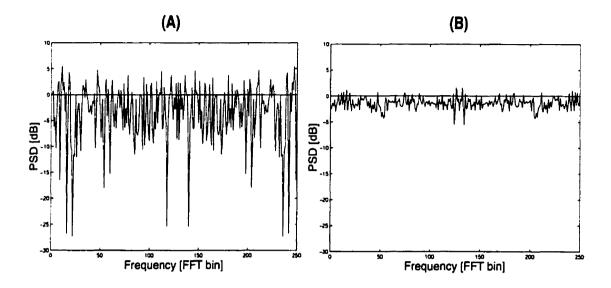

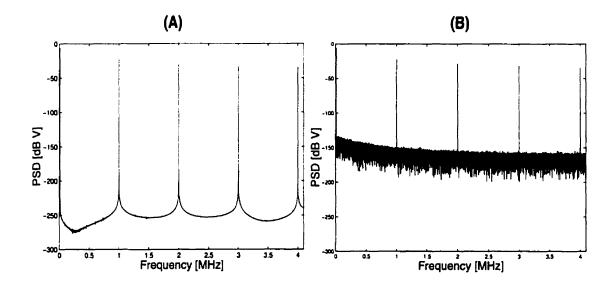

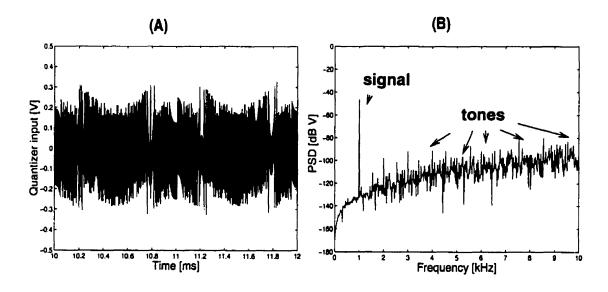

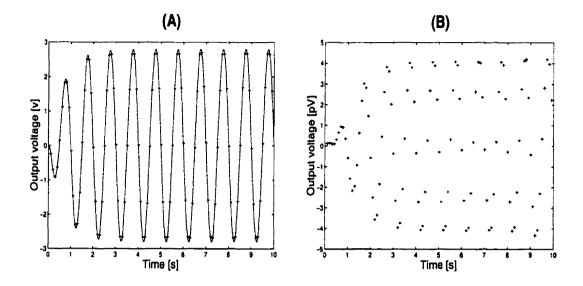

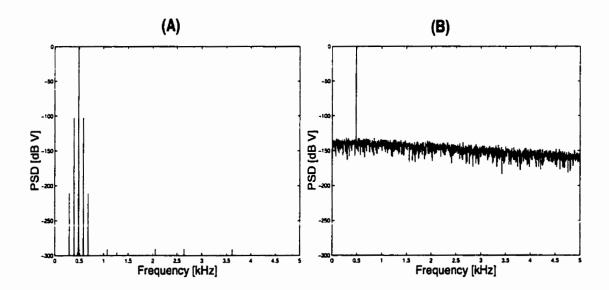

| 4.1  | SC SDM: ideal elements (A) comparator input (B) output spectrum            | 65 |

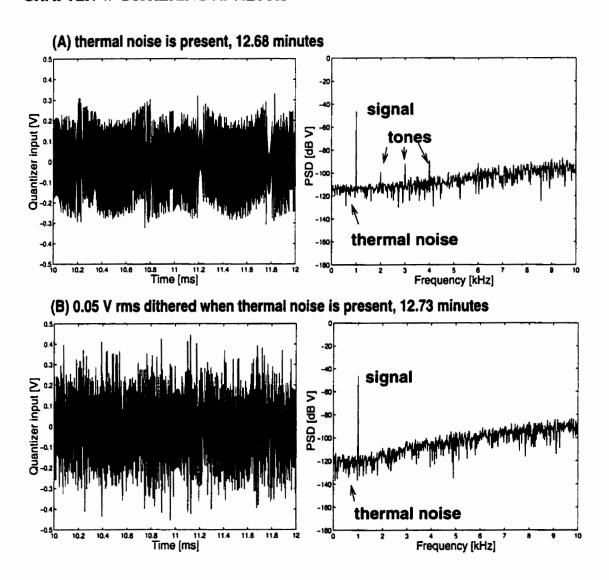

| 4.2  | SC SDM: thermal noise is present (A) original (B) dithered                 | 66 |

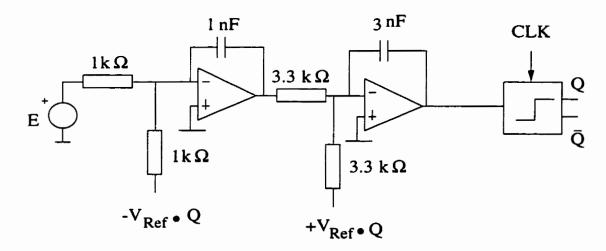

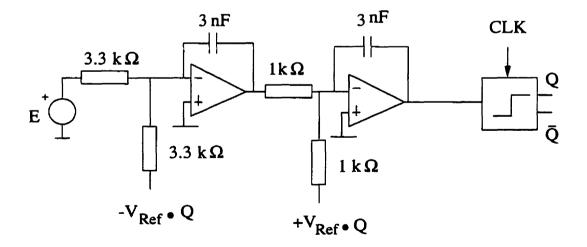

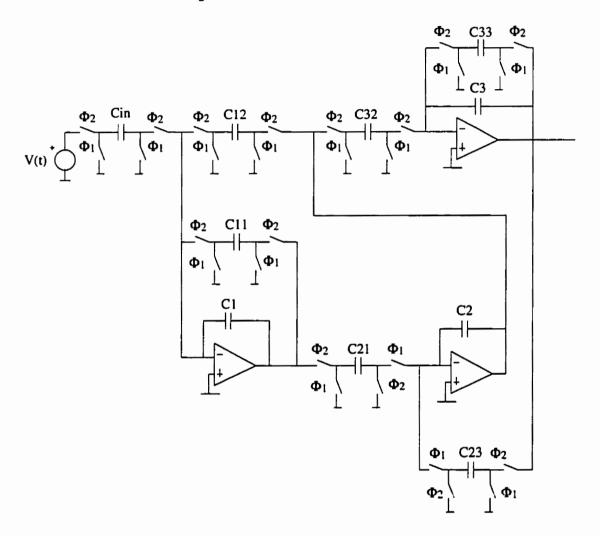

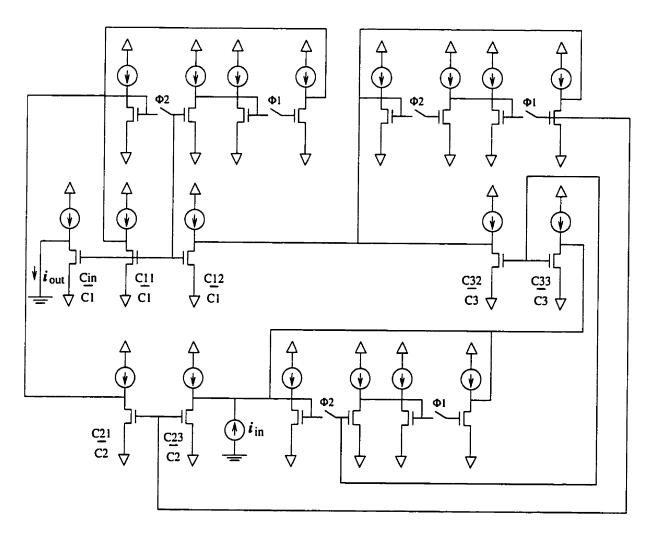

| 4.3  | A continuous-time second order sigma-delta modulator                       | 67 |

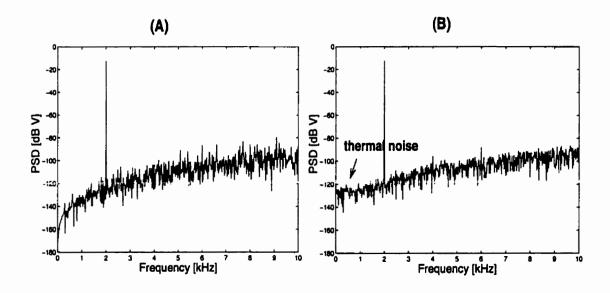

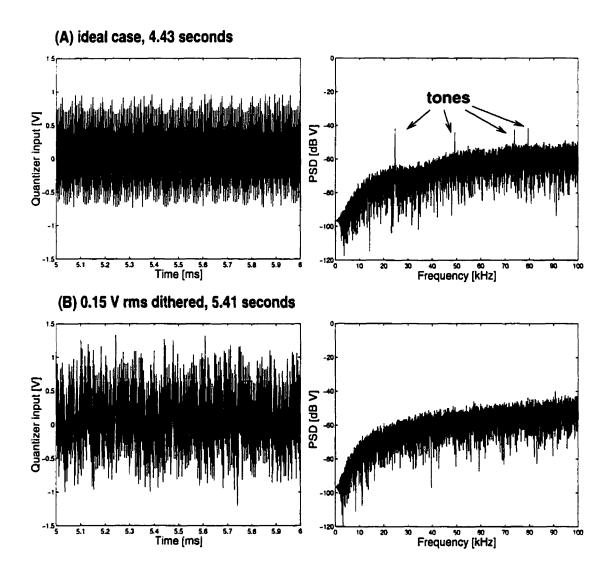

| 4.4  | CT SDM: DC input, ideal elements (A) original (B) dithered                 | 68 |

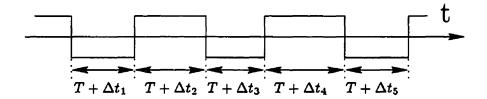

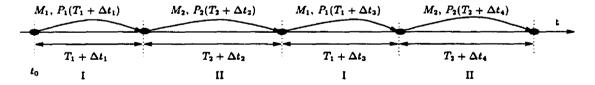

| 5.1  | Clock jitter                                                               | 71 |

| 5.2  | Simulation of periodically switched linear networks                        | 80 |

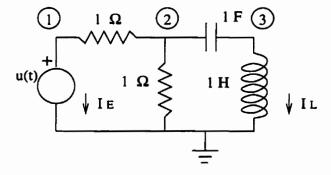

| 5.3  | A simple RLC circuit                                                       | 85 |

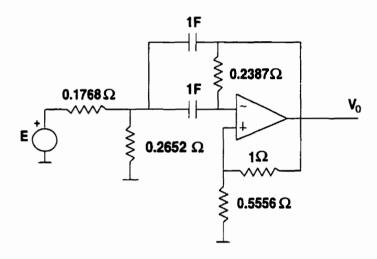

| 5.4  | A bandpass filter                                                          | 90 |

| 5.5  | Bandpass filter (A) simulation results match exact analysis (B) difference |    |

|      | in the order of pV $\dots$                                                 | 91 |

| 5.6  | Third-order Chebyshev switched-capacitor filter                            | 92 |

| 5.7         | SC filter output spectrum: no jitter                                 | 93  |

|-------------|----------------------------------------------------------------------|-----|

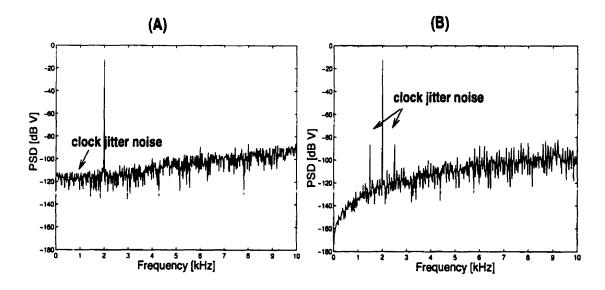

| 5.8         | SC filter: with 0.1% (A) sinusoidal jitter (B) random jitter         | 94  |

| 5.9         | Third-order Chebyshev switched-current filter                        | 95  |

| 5.10        | SI filter output spectrum: no jitter                                 | 96  |

| 5.11        | SI filter: with 0.1% (A) sinusoidal jitter (B) random jitter         | 96  |

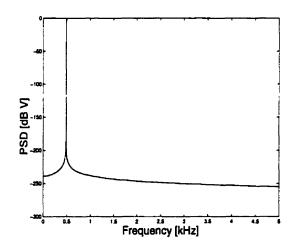

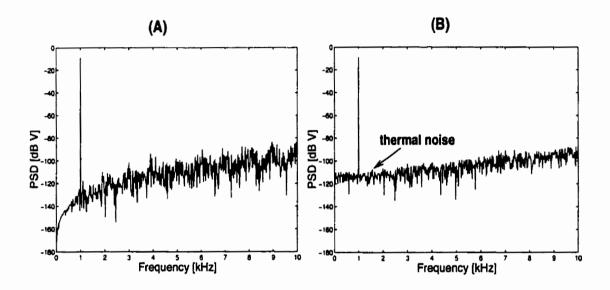

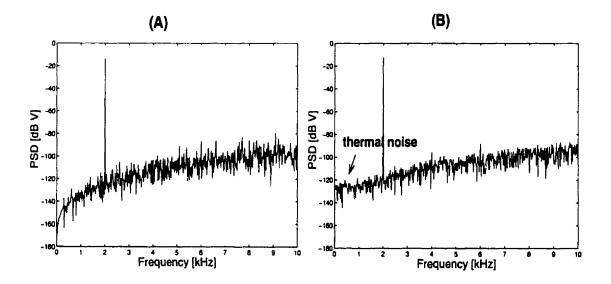

| 6.1         | SC SDM: (A) ideal elements (B) with thermal noise                    | 101 |

| 6.2         | SC SDM: (A) 1 kHz input: no jitter (B) 1025 kHz input: no jitter     | 102 |

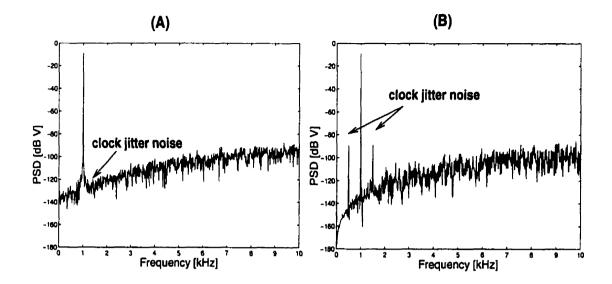

| 6.3         | SC SDM, 1 kHz input: 0.01% (A) Normally distributed (B) 500 Hz si-   |     |

|             | nusoidal clock jitter                                                | 104 |

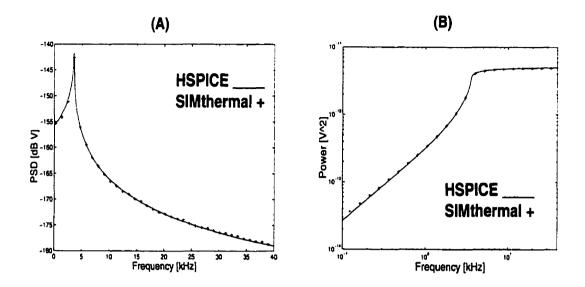

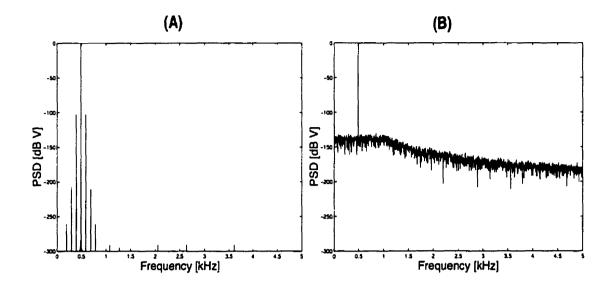

| 6.4         | CT SDM: (A) ideal elements (B) with thermal noise                    | 105 |

| 6.5         | CT SDM: with 0.01% (A) Normally (B) 500 Hz sinusoidal clock jitter . | 105 |

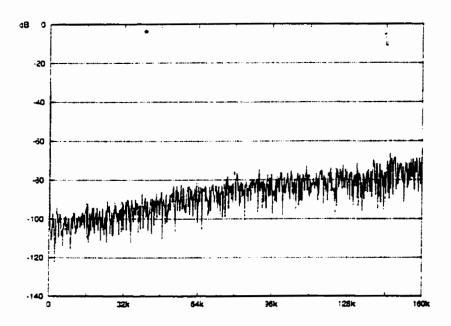

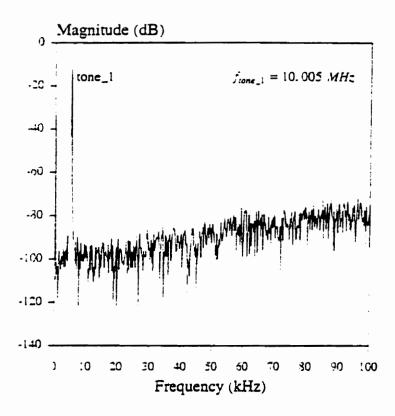

| 6.6         | F. Chen PhD thesis: Clocked at 10 MHz, 10.005 MHz IF input           | 107 |

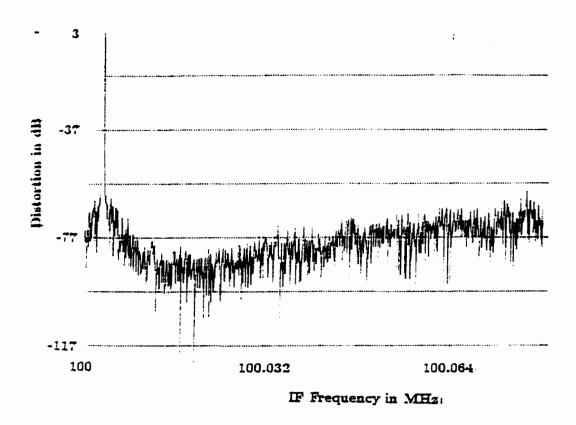

| 6.7         | S. Sen PhD thesis: Clocked at 10 MHz, 100 MHz IF input               | 108 |

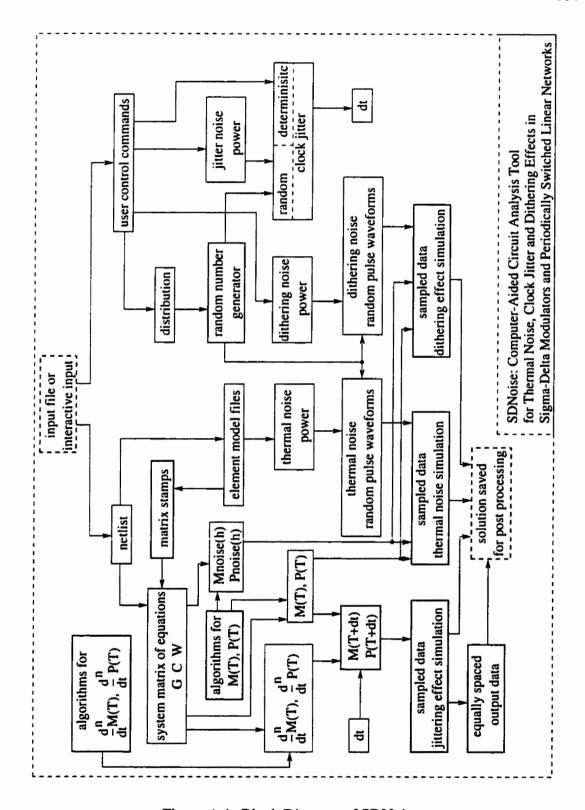

| <b>A</b> .1 | Block Diagram of SDNoise                                             | 114 |

### **List of Abbreviations**

A/D Analog to digital

BDF Backward differentiation formulae

CT Continuous-time

D/A Digital to analog

DAE Differential algebraic equation

**DR** Dynamic range

**DSP** Digital signal processing

**FFT** Fast Fourier transform

IF Intermediate frequency

IV Current-voltage

**LLTI** Lumped linear time invariant

LPTV Linear periodically time varying

LTI Linear time invariant

MNA Modified nodal analysis

**ODE** Ordinary differential equation

opamp Operational amplifier

**PSD** Power spectrum density

PSL Periodically switched linear

PWL Piecewise linear

**QV** Charge-voltage

**RF** Radio frequency

RHS Right hand side

rms Root mean square

SC Switched-capacitor

**SDM** Sigma-delta modulator

SI Switched-current

**SNR** Signal-to-noise ratio

## Chapter 1

#### Introduction

#### 1.1 Motivation

Sigma-delta modulators (SDMs) are an important type of circuits that draw attention from both academia and industry. They are undergoing active research and development. In the last decade, hundreds of papers devoted to the design and analysis of SDMs have appeared in major electronics conferences each year. A paper collection [1] and a book for state-of-the-art reviews and tutorials [2] were also published recently.

Sigma-delta modulators are used for data conversion between analog and digital domains. One of their significant advantages is that the resolution of the overall converter can be much higher than the resolution of the internal quantizer and the precision of the analog circuitry. This enables fabrication of high resolution data converters with digital signal processing (DSP) circuits in a digital compatible process. SDMs are typically implemented as switched-capacitor (SC) circuits. Because of the increasing interest in low-power, low-voltage, and compact electronic circuits in telecommunication, switched-current (SI) and continuous-time (CT) SDMs have also emerged recently.

The performance of a SDM is usually characterized by its signal-to-noise ratio (SNR), which is the ratio of signal power to in-band noise power, or by its dynamic range (DR), which is defined as the input-signal range between 0 dB and maximum SNR. When most of the quantization noise is shaped out of the signal-band, the noise floor of a SDM is dominated by thermal noise, clock jitter, or other noise and distortion effects.

Thermal noise is generated by random thermal motion of electrons in resistors and semiconductors. It limits the resolution of a SDM in a fundamental way, and is a major factor restricting the performance of a voice-band SC SDM [3, 4]. Clock jitter is a small deviation of the clocking from its desired time instants. It increases noise level at the output of a circuit performing sampling operations [5, 6, 7, 8]. Clock jitter is another major contributor to performance degradation. It severely affects modulators designed for high frequency signals, especially when the loop-filters are continuous-time [9].

Although thermal noise and clock jitter are among the major factors limiting circuit performance, their contributions to total noise level remain unknown until physical measurements on the prototype chip are made. During the design cycle, knowledge of the noise and clock jitter performance still depends on guesswork of experienced designers. The hand analysis involved is often difficult and exhaustive. It lengthens the concept-to-market cycle.

With a harsh nonlinearity – the quantizer – placed in the feedback loop, a SDM is difficult to analyze. Many methods and tools [10, 11, 12, 13, 14, 15, 16, 17, 18, 19] have been described in the literature. However, after more than 15 years of constant research and development, methods for noise and clock jitter analysis of SDMs at the electrical circuit level are still not available.

Noise analysis is traditionally done in frequency domain. This includes the classical methods for linear time invariant circuits [20], and the methods developed for switched-

capacitor networks [21, 22, 23, 24, 25]. But because of the highly nonlinear nature of SDMs, frequency domain analysis is not applicable.

Time-domain noise analysis is the only possibility. Approaches based on linearization at each time step using Taylor series [26] or other expansion methods fail, as the state of the circuit is not solely decided by the signal content. At some time point, the noise can be comparable to the signal, and can change the comparator output. A new method for time domain noise analysis is needed. It must be able to work with the circuit without linearizing the quantizer, and, it must be efficient to facilitate the long transient simulation needs. Additional requirements include simulation accuracy to detect noise information in the presence of large signal waveforms. Time domain noise analysis of SDMs is not an easy task, as the circuits are high resolution and their performance measures are based on statistical averages over a very large number of samples.

In real life, clock jitter usually comes from the noise in the clock generating circuitry, or through coupling of various interference sources. It is not necessarily periodic, but often contains a broadband spectrum. Despite the importance of clock jitter on the performance of analog sampled data circuits like SC and SI filters, only a few researchers [27, 28] have touched upon this topic, and they simplified the analysis by restricting their attention to periodic jitter waveforms.

Both SC and PSL (periodically switched linear) network analysis methods are based on the periodic switching nature of the circuit. By partitioning the circuit into a *finite* number of phases, a set of charge-transfer or differential equations can be written. The circuit is analyzed by recursively solving these equations. If only periodic clock jitter exists, a circuit can still be partitioned into a finite, although larger, number of phases [27, 28]. Classical methods can be extended to accommodate their analysis [27, 28].

The introduction of random clock jitter results in an infinite number of phases. This

violates the *fundamental assumption* which classical SC and PSL circuit analysis methods are based on. A new method that can analyze the circuit with periodic and, more importantly, random jitter in the clocking is needed.

All sigma-delta modulator structures suffer from the idle-channel tone phenomenon. These tones degrade the quality of signal conversion [29]. Dithering is a technique that aims at eliminating the unwanted tones by adding small amount of noise to the circuit [30]. Dithering noise can be considered as additional noise source, and the method developed for noise analysis of SDMs can be extended for dithering analysis.

In summary, new methods are needed for thermal noise, clock jitter, and dithering analysis of SDMs at electrical circuit level. The desirable attributes include (i) efficiency and accuracy; (ii) applicable to switched-capacitor, switched-current, and continuous-time SDMs; (iii) suitable for computer application.

#### 1.2 Objectives

This thesis proposes new methods for noise analysis, clock jitter analysis, and dithering analysis. It develops corresponding computational algorithms, and implements them in a computer program.

The result of this research is a set of new methods and algorithms as well as a simulation tool. Equations are formulated at electrical circuit level, and the simulator targets a wide variety of SDMs. The following elements can be included in the circuit representation: ideal or single-pole operational amplifiers, transistors working in small signal condition, external clocked switches, capacitors, resistors, inductors, independent current or voltage sources, all four types of linear controlled sources, and latched comparators or quantizers. General nonlinear and transistor level descriptions are not allowed.

The research is conducted in three steps:

- 1. Propose new methods and develop computational algorithms;

- 2. Implement the algorithms in a computer program;

- Validate the methods, algorithms, and tool on numerical examples by comparing the simulation results with theory predictions, physical measurements, or experimental observations.

#### 1.3 Thesis Organization

Chapter 2 reviews the background information associated with this thesis. After a brief introduction of SDMs, we discuss the trend from the early switched-capacitor to recent switched-current and continuous-time implementations. Comments on the advantages and drawbacks of each implementation are given. The methods and tools for analysis of SDMs are critically reviewed based on the following classifications: block level for conceptual design phase, electrical circuit level for circuit design phase, and low level full circuit simulation for design verification phase. Thermal noise, clock jitter, and dithering analysis at these three levels are discussed. At the end, sampled data analysis methods and a numerical Laplace inversion method are revisited.

Chapter 3 proposes a new method for noise analysis of SDMs. The method is general and systematic. Important electrical noise sources in integrated circuits are identified, and the modeling of thermal noise in frequency domain and time domain is reviewed. An overview of noise analysis methods is given, and an efficient time-domain method is proposed. By using this new noise analysis method, numerical examples are given on LTI (linear time invariant) circuits, PSL networks, and SDMs. The results are compared with exact analysis or physical measurements.

Chapter 4 extends the noise analysis method of chapter 3 to dithering analysis of SDMs. The present state of dithering analysis is briefly reviewed. Numerical examples are given to show the effect of dithering in breaking up limit-cycle patterns, and to demonstrate the effect of thermal noise acting as dithering noise.

Chapter 5 presents a new method for arbitrary waveform clock-jitter analysis of PSL networks. Formulation methods and computational algorithms for the time derivatives of the circuit transition matrix and the input transfer vector are provided. Simulation examples on the influence of random and sinusoidal clock-jitter on SC and SI filter performance are given.

Chapter 6 extends the method of chapter 5 to clock jitter analysis of SDMs. Examples are given to show the usefulness of the method. In particular, we study the role of clock jitter on the performance degradation of SDMs involved in direct RF/IF conversion. Simulation results are compared with experimental observations.

Chapter 7 summarizes the work presented in this thesis. Areas of further research are suggested.

**Appendix A** gives a brief description of the simulation tool developed – SDNoise. A block diagram of the program structure is included.

#### 1.4 Original Contribution

Original contributions in this thesis are made in deriving new methods and algorithms for computer-aided analysis of SDMs, and in implementing them in a practical computer program. The phenomena studied include thermal noise, clock jitter, and dithering noise. To the best of the author's knowledge, they are the *first ever* noise analysis and the *first ever* clock jitter analysis methods available for SDMs at electrical circuit level.

In addition, this thesis contributes to circuit theory: (1) by giving a varying step sampled data analysis method for LTI circuits; (2) by defining time derivatives of the circuit transition matrix and of the input transfer vector, and providing corresponding computational algorithms.

- The methods are general in that no restrictions on circuit topologies or jitter waveforms are made. They are applicable to both switched-capacitor, switched-current, and continuous-time SDMs.

- The methods and the tool can also be used for noise analysis of PSL networks where direct frequency domain analysis is not straightforward.

- The formulation is at electrical circuit level. It allows the study of noise contributions by individual circuit elements. The tool relieves the designer from exhaustive hand analysis and provides accurate results.

- The algorithms are efficient and accurate. Transient simulation of a typical SDM over several hundred thousand clock-cycles is obtained in the order of minutes.

### Chapter 2

# Sigma Delta Modulators: Background Review

In this chapter we review the background associated with noise and clock jitter analysis of SDMs. After a brief introduction of the basic concepts, we give an overview of the trends in circuit implementation. The simulation methods and tools are reviewed with emphasis on the noise and clock jitter analysis. Finally, sampled data analysis methods and a numerical Laplace inversion method are revisited.

#### 2.1 Introduction to Sigma Delta Modulators

In this section, we briefly introduce oversampled sigma-delta modulators. Many excellent papers on this subject are also available [31, 32].

In modern VLSI technology, it is possible to fabricate large and complex digital signal processing circuits on a single chip. Compared with their analog counterparts, digital circuits have many benefits. For example, they are more suitable for design automation and have higher noise immunity. Modern signal processing circuits are usually digital, but signals in the real world are analog. Data converters are needed to convert signals between analog and digital domains.

There are many types of data converters. Among them, oversampled sigma-delta modulation converters are known for trading off speed for resolution, and for shifting complexity from analog circuitry to digital circuitry. The resolution of the converter is much higher than the resolution of its internal quantizer and the precision of its analog circuitry. The price paid for low precision analog circuitry and high conversion resolution is increased complexity of the digital circuitry and low-to-medium signal bandwidth. The benefit brought by low precision analog circuitry is that the circuit can be fabricated in a digital compatible technology.

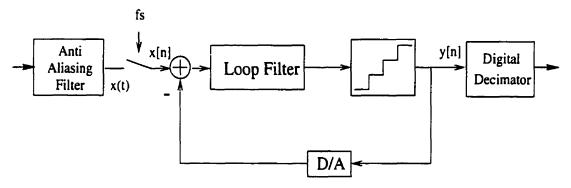

Figure 2.1: A sigma-delta modulation A/D converter

Two steps are needed to convert an analog signal into digital domain. First, the signal is sampled at discrete instants of time, then its amplitude is quantized into a finite set of values. The block level structure of a typical SDM is shown in Fig. 2.1. The anti-aliasing filter limits the bandwidth of the input signal before sampling. The SDM is used to perform the sampling and the quantization operations. Different transfer characteristics are applied to the input signal and the quantization noise. The power spectrum of the quantization noise is shaped over the sampling frequency band  $[-f_{\bullet}/2, f_{\bullet}/2]$ , with most

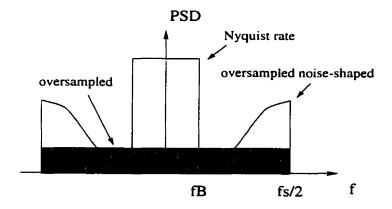

Figure 2.2: Quantization noise power spectrum density

of the noise power moved from low frequencies to high frequencies. This is shown in Fig. 2.2, along with a comparison with the power spectrum densities (PSDs) of Nyquist rate and oversampled data converters. In contrast to the noise shaping of the quantization noise, the signal transfer characteristics are not changed. A digital decimator is employed after the modulator to attenuate out-of-band noise and down-sample the signal to the Nyquist rate for digital signal processing or storage.

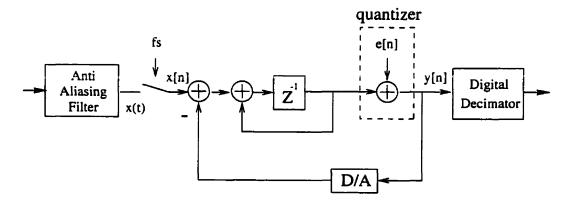

Figure 2.3: First-order sigma-delta modulation A/D converter

A first-order SDM consists of an integrator and a single or multi-bit quantizer in the

feedback loop, as shown in Fig. 2.3. Its transfer function in z-domain is [32]:

$$Y(z) = X(z)z^{-1} + E(z)(1 - z^{-1})$$

(2.1)

where the output, Y(z), is a function of the input, X(z), and of the quantization noise, E(z). The signal is delayed by one sample only, while the quantization noise is shaped by a first-order z-domain differentiator. A popular method<sup>1</sup> linearizes the circuit by replacing the quantizer with a noise source, usually a white noise of uniform probability density function over  $\pm \Delta/2$ , where  $\Delta$  is the input step-size of the quantizer [34]. Based on this model, the in-band quantization noise power is [32]:

$$\sigma_{ey}^2 = \frac{\Delta^2}{12} \frac{\pi^2}{3} (\frac{2f_B}{f_*})^3 \tag{2.2}$$

where  $f_B$  is the signal bandwidth, and  $f_s$  is the sampling frequency. Note that the quantization noise power is inversely proportional to the cube of the oversampling ratio – the ratio of  $f_s/2f_B$ . Higher oversampling ratios result in lower in-band quantization noise power, and higher conversion resolution is obtained. Nevertheless, an upper limit on the oversampling ratio exists because of the fixed signal-bandwidth and the maximum operating speed available in a given technology. Higher order modulators are needed to further improve the conversion resolution.

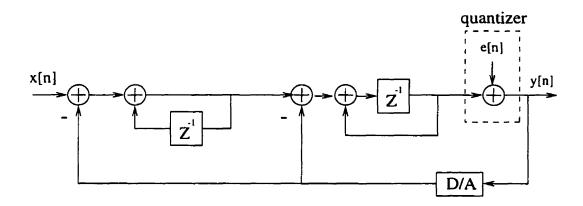

A second-order SDM structure is shown in Fig. 2.4. Its z-domain transfer function is [32]:

$$Y(z) = X(z)z^{-1} + E(z)(1-z^{-1})^{2}$$

(2.3)

The signal is still delayed by one sample only, while the quantization noise is shaped by a second-order z-domain differentiator. Its in-band quantization noise power is [32]:

$$\sigma_{ey}^2 = \frac{\Delta^2 \pi^4}{12 \cdot 5} (\frac{2f_B}{f_c})^5 \tag{2.4}$$

<sup>&</sup>lt;sup>1</sup>Although this approach produces useful insight, it fails to take into account the true nonlinear nature of the system. Many important effects, such as the tonal behavior and the modulator instability, cannot be studied [33]. This method will not be discussed further.

Figure 2.4: Second-order sigma-delta modulator

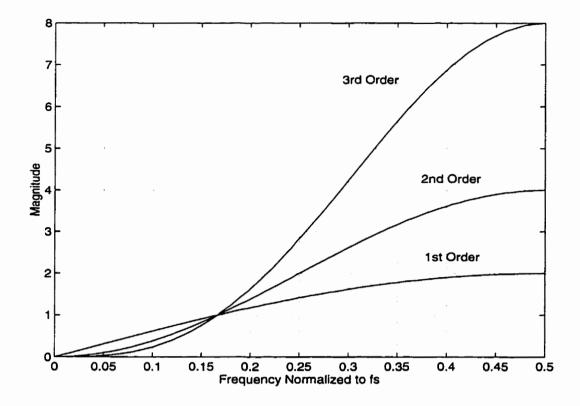

As shown in Fig. 2.5, high order SDMs can be employed to move even more quantization noise power out of the signal-band. They can be constructed as a simple expansion of the first and the second order modulators. However, modulators with this type of topology often suffer from stability problems [35]. An alternative for high-order noise transfer function is the multi-stage (MASH) configuration [36, 37], where the circuit is built by cascading stable single stages. An excellent review of high-order sigma-delta data converters can be found in [38].

Besides traditional lowpass sigma-delta circuits, bandpass systems [39, 40, 41] have also been studied and implemented in recent years.

#### 2.2 Trends in Circuit Implementation

Monolithic analog filters can be classified as either discrete or continuous time circuits. The former include SC and SI filters, the latter include passive RLC, RC active, and  $G_m$ -C filters.

Sigma-delta modulators can be built with either discrete or continuous-time loopfilters. Discrete time implementations, especially SC SDMs, gained most of the attention

Figure 2.5: Noise transfer characteristics of sigma-delta modulators

in the past. However, SI and CT designs have experienced rapid development in recent years. A brief discussion of the reasons behind the evolution is given in this section.

#### 2.2.1 Switched-Capacitor Sigma-Delta Modulators

A SC filter is formed by capacitors, operational amplifiers, and periodically operated switches. Its transfer function is defined by the clock frequency and the capacitor ratios, which are insensitive to process parameter and temperature variations [42]. SC techniques are ideal for realization of stable and accurate analog filters in low-cost digital compatible MOS technology. Most of the early designs of SDMs were implemented in SC technique [1].

The use of SC technique in high frequency applications, however, is limited by their requirement of the operational amplifiers and floating capacitors. Operational amplifiers (opamps) have to be fast enough to settle within half of the clock period. As a rule of thumb, the opamp bandwidth has to be at least 7 times larger than the clock frequency [42]. In addition, an extra layer of polysilicon is required on top of a pure digital CMOS process to implement linear floating capacitors. This is costly when most of the circuitry on the same chip is digital. The additional layer of polysilicon is even more difficult to obtain as the CMOS technologies move to the deep sub-micron range [43].

The trend towards deep sub-micron process also leads to reduced power supply voltages. This makes the design of wide dynamic range, high gain, and high speed voltage-mode circuit more difficult [43].

#### 2.2.2 Switched-Current Sigma-Delta Modulators

Switched-current circuits operate with currents instead of voltages. They have the potential of high-speed and low voltage operation [43].

SI circuits can be implemented in a fully digital technology, as neither floating capacitors nor operational amplifiers are required, and the only building elements are transistors and switches. In addition, by eliminating operational amplifiers, SI circuits can operate at high sampling rates with much lower power consumption [44]. They also have the advantage of smaller size due to simplified circuit structure without floating capacitors [44]. SI technique is an ideal alternative for discrete-time analog circuit design, especially in low voltage and low power applications. It has attracted considerable interest from the integrated circuit design community [45, 46], and was quickly applied to SDMs [47, 48, 49, 44].

A major disadvantage of SI circuits is clock feedthrough, which increases both the

noise and distortion levels [50]. Due to the absence of large capacitors, this effect is much more severe than in SC circuits [42]. The impact of clock feedthrough can be reduced by using lower clock rates [44] with the side effect of limited operating speed.

#### 2.2.3 Continuous-Time Sigma-Delta Modulators

By placing the data converters closer to the antenna, the complexity of a wireless communication system can be reduced and the reliability can be increased [51]. High frequency data converters are needed in this situation.

The majority of SDMs reported to date have discrete-time loop-filters in CMOS technology. The signal bandwidth of these SDMs is very restricted, usually to the audio range [6]. On the other hand, the realization of discrete-time SDMs in other high speed technologies, such as bipolar, is difficult [6].

Additional disadvantages associated with discrete-time SDMs are:

- 1. The design is complicated by the use of anti-aliasing continuous-time filters [42].

- Large amounts of high-frequency noise can be aliased into the baseband. The

increased in-band noise power can drastically reduce the dynamic range of a modulator [42]. Due to aliasing, it is well recognized that thermal noise is a major

source that limits the resolution of a voice-band SC SDM.

It has been demonstrated that a continuous-time SDM designed in a given technology usually possesses higher signal bandwidth than its discrete-time counterparts [6]. Traditional continuous-time filters, such as passive RLC and active RC filters, are not suitable for monolithic implementation [52]. Fortunately, transconductor- $C(G_m-C)$  filters can be implemented in a fully integrated form in any technology [52]. The frequency range of

transconductance circuits in CMOS technology extends well into 50 MHz range, and a frequency range larger than 500 MHz is possible in bipolar technology [52]. Because of the application of  $G_m$ -C filters, design of high-frequency continuous-time telecommunication circuits becomes feasible.

Sigma-delta modulators with  $G_m$ -C loop-filter were widely reported in recent years. The use of CMOS technology in high-frequency applications was explored in [5]. Another investigation in CMOS technology [9] studied low-power design for voice-band applications. Bandpass design in BICMOS technology [7] was also reported. The possible extension of the use of SDMs to intermediate/radio frequencies (IF/RF) by using high speed technologies was demonstrated in [6, 51].

The major complications in continuous-time modulators are:

- Clock jitter contributes to the noise level and can become a significant problem [5, 6, 7, 8]. In a SC circuit, the charge is transferred in a short period of time after the clock edge. But in a CT circuit, the charge is transferred over the entire cycle. It is expected to be more sensitive to clock jitter [9].

- 2. The frequency characteristics of a CT loop-filter are decided by element values and subject to process spread; also, they do not scale with the sampling frequency [9].

#### 2.3 Simulation Methods and Tools

SPICE type transistor level simulation tools are widely used for the analysis of integrated circuits. The circuit is modeled at transistor level, and simulated with device models. This level of analysis provides circuit details, and allows investigation of various circuit imperfections and nonlinearities. However, excessive simulation time for SDM reaches the limits of these simulators [53].

#### 2.3.1 Challenge

The difficulties associated with computer-aided analysis of SDMs are:

- Components with harsh nonlinearity -quantizers exist in the feedback loop.

Direct frequency domain analysis is not possible. Transient analysis is the only choice.

- 2. The circuit is a dual-time system with a rapidly varying clock and a slowly varying input signal.

The typical clock frequency is in the MHz range, while the input signal is in the kHz range. Transient analysis for thousands of clock cycles is needed just to observe a few cycles of the signal.

3. Circuit performance is characterized by frequency components.

The performance is typically specified by the signal-to-noise ratio or dynamic range, which are based on statistical averages over a very large number of samples. Simulation results over several cycles of the input signal, usually tens of thousands of clock cycles, have to be obtained to evaluate the SNR for one particular input amplitude. Furthermore, the dynamic-range is estimated from the SNR versus input-amplitude curve, where many long transient simulations are needed.

4. High simulation accuracy is required.

In order to observe the true circuit behavior, the numerical noise brought by the simulation algorithm and finite precision arithmetic has to be kept much lower than the actual circuit noise floor. Sigma-delta modulators with SNR in excess of 120 dB have been reported [54]. Such high simulation accuracy is hard to obtain with transistor level simulators. SPICE type general purpose analog simulators use classical numerical integration methods, and the accuracy is limited by the

local truncation error. The local truncation error can be reduced by decreasing the integration step, but the penalty is increased simulation time. There is a lower bound on the local truncation error. Beyond this limit, smaller time step will result in increasing error [55].

Simultaneous need of long and accurate transient simulation reaches the limit of a transistor level simulator, and often results in extremely long CPU time, which might be counted in days.

Efficient special purpose simulation methods for SDMs are needed, especially for use in the design cycle. They can be classified into three categories: block level, electrical circuit level, and transistor level. In this section, based on the above classifications, we give a review of the simulation methods and tools for SDMs. Other overviews on this subject can be found in [53, 56].

#### 2.3.2 Classification and Review

Simulation methods for SDMs can be classified by the model abstraction level. Simple models usually lead to fast simulation; detailed models provide more realistic results. Trade-offs between simulation speed and model accuracy are often made in different stages during the design cycle.

#### **Block Level Simulation for Conceptual Design Phase**

In the conceptual design phase, the circuit architecture is determined according to high level specifications. The block level simulation is suitable at this stage. It does not require electrical details of the circuit which are not available at this stage, and provides fast simulation that enables architecture selection from a wide variety of circuit topologies.

The noise shaping and signal transfer functions for a SDM can be designed in the z-domain. This is the easiest and most widely used method. Difference equation simulation for z-domain transfer function is straightforward, and can be easily programmed with several lines of Matlab coding. But such codes are restricted to a specific circuit topology. Dedicated hand analysis is needed for each change of the topology, and a new set of codes has to be developed. This method lacks the flexibility for quick examination of several architectures.

General purpose block level simulation tools like MIDAS(1992) [15] are used. In this type of simulator, the circuit is represented by highly abstract function blocks, such as delay, adder, and quantizer. A simple signal-flow-chart type simulation is performed. The functional blocks in MIDAS are defined in model files, where circuit limitations may be added to the description. However, many circuit nonidealities, like frequency dependent characteristics, are difficult to model.

Simulation tools in this category are event driven. Digital simulation techniques like event tracing and scheduling are used. Typical elements are logic and delay functions. Electrical details of the circuit are avoided, and the circuit operation is characterized by highly abstract mathematical models. Simplicity in the circuit model enables fast simulation.

Additive noise sources can be added to the block level representation. Some general understanding of the noise performance can be obtained this way. However, thermal or other circuit noise analysis by this method could be prohibitively complicated, and the accuracy is not assured: Exhaustive hand-analysis is needed to calculate the noise power for each loop-filter; Caution must be paid to details such as how much wideband noise is aliased into the baseband; It is next to impossible to find a pseudo-random number sequence whose spectrum has the same shape as the filter noise response; Each change of the circuit requires a new hand-analysis and random noise source mapping process.

The clock jitter effect has been studied by some researchers at this level [57, 58]. Sampling of the input signal is considered as the only source of error, and a data sequence of the input sinusoid sampled at unequally spaced time instants is fed to the block level simulation. Again, although this approach can provide general insight during the conceptual design phase, it is not suitable for detailed circuit design or design verification. Additional comments will be given in chapter 5 and chapter 6.

In summary, the block level representation is highly abstract and mathematically oriented. No circuit implementation details are available. It is only suitable for conceptual design.

#### **Electrical-Circuit Level Simulation for Circuit Design Phase**

In the circuit design phase, electrical details are added to the circuit. Specific parameters, like gain-bandwidth of the operational amplifiers and capacitor values, are considered.

Most of the simulation tools for SDMs in this category evolved from those originally designed for SC filters. Additional digital functions like latched comparators and logic gates are included to accommodate the analysis of SDMs. Because of the nonlinear nature of the circuit, simulation is only performed in the time domain.

Switched-capacitor networks can be analyzed either in the charge-voltage (QV) regime or the current-voltage (IV) regime. Approaches in the first category are called ideal switched-capacitor methods. They simplify the analysis by eliminating current from the formulation. This is achieved by restricting the element types to capacitors, ideal switches (open/short circuits), voltage sources, voltage controlled voltage sources, and ideal or finite-gain operational amplifiers. The analysis proceeds by recursively solving a finite set of charge-transfer equations. Tools for analysis of SDMs in this category in-

clude SWITCAP2(1990) [11] and TOSCA(1992)<sup>2</sup> [16]. They are limited to discrete-time SDMs. Modulators with CT loop-filters cannot be handled.

Periodically switched-linear network analysis is necessary when some circuit nonidealities, like finite bandwidth of operational amplifiers and switch ON-resistances, cannot be neglected; or when elements like controlled current sources are critical to model the circuit. Methods in this category view the network as a linear circuit, and the formulation is done in the IV regime. All linear elements are allowed. Simulation tools in this category can be applied not only to SC but also to SI and CT circuits.

Transient analysis in the IV regime usually requires time integration. It is computationally expensive if ordinary numerical integration methods are involved, and can result in extremely long CPU time for dual-time circuits like SDMs and switched analog filters. Some strategies must be followed to speed up the simulation. In SAMBA(1990) [13], the nonlinearities are approximated by piecewise linear (PWL) models. The idea is that if a circuit is restricted to any particular segment of the PWL model, it can be solved as a linear circuit. The responses for these linear circuits are computed symbolically before the simulation starts. During transient analysis, the symbolic expressions are evaluated at the switching instants. This approach has the disadvantage that each combination of PWL segments must be solved separately, which leads to a large number of linear circuit approximations. In AWEswit(1993) [18], an IV formulation is adopted in addition to the conventional QV formulation. This means that while the SC parts are handled in the QV regime, the resistive portions are solved in some form of numerical integration. Asymptotic Waveform Evaluation (AWE) [59] is applied to approximate the transfer function by a low-order dominant pole model. The evaluation of this simplified model can be, depending on circuit size, significantly faster than the classical transient analysis. A sampled-data analysis technique [60] was applied in DELTA(1994) [61] and

<sup>&</sup>lt;sup>2</sup>also has block level simulation capability.

SDSIM(1994) [19, 62] for fast and accurate simulation of SDMs. This method was improved and presented systematically in [19, 62]. Some constant matrices and vectors are computed numerically only once before the simulation starts. During transient analysis, the circuit response at discrete time instants is obtained by manipulation of the precomputed matrices and vectors. A review of this method, together with a summary of the sampled data analysis of analog circuits, is given in section 2.4.

Noise and clock jitter analysis of SDMs at the electrical circuit level are not available elsewhere. A comprehensive overview of noise analysis is given in section 3.3. Clock jitter, especially random jitter, destroys the regular pattern of the circuit operation. Special treatment, other than the conventional circuit analysis techniques, is needed. A state-of-the-art review of the clock jitter analysis of PSL network is given in chapter 5, and additional comments for SDMs are given in chapter 6.

#### Low Level Full Circuit Simulation for Design Verification

Although transistor level analysis allows investigation of many circuit nonidealities and nonlinearities, it is used only in the design verification phase. This is because (1) extremely long simulation time is required; (2) the transistor level circuit details are not available at earlier stages.

In ZSIM(1988) [63, 10], a clever table look-up method is adopted. Some important sub-circuits, such as integrators, are simulated for a single clock cycle under different operating conditions by an external transistor level simulator. The results are saved in look-up-tables. Then, with reference to the interpolated table points, a difference equation simulator is used to simulate the performance of the whole circuit. This approach is useful when the critical blocks have been implemented at transistor level, and quick design verification is needed. Nevertheless, this method has its limitations. The major

drawbacks are: (1) table generation is tedious and requires extensive human interaction and design experience. New tables have to be generated each time the circuit is modified; (2) simulation accuracy is limited by table interpolation error; (3) large memory is needed to store the tables; (4) noise and clock jitter effects cannot be analyzed.

The noise analysis algorithms implemented in SPICE type simulators are applicable only to circuits obtained by linearizing the original network around its DC operating point [64]. Due to the highly nonlinear nature of SDMs, neither thermal noise, nor clock jitter, nor dithering effects can be analyzed this way.

Additional time-domain noise sources might be added to the clocking signal to model clock jitter, and added throughout the circuit to model thermal noise and dithering noise. These noise sources can be included in SPICE transient simulation of SDMs. However, such an approach is hindered by the inherent limitations of the SPICE type transient analysis algorithm:

- In typical versions of SPICE, the accuracy of transient analysis is of the order of 120 dB or less [65]. For a high resolution circuit like a SDM, the noise effects obtained from such a simulation algorithm are more likely to be numerical noise, not true circuit noise.

- 2. The inclusion of many noise sources in the transient analysis will result in excessive increase of the computational burden. It lengthens the already prohibitively long simulation time. Furthermore, in order to model the high frequency noise that might be aliased into the baseband, either a large number of sinusoidal noise sources with random phases [66] must be included, or very small steps [67] must be maintained throughout the analysis. Both cases make the situation even worse.

- 3. In time domain noise analysis, attention must be paid to the amount of noise power injected into the circuit. Noise power is related to the noise bandwidth in frequency

domain. In time domain, it is usually related to the step-size of transient analysis. In SPICE, this step-size is controlled internally. It is not known *a priori*, and makes time domain noise power modeling difficult.

In summary, transistor level simulation of SDMs is restricted to design verification. Noise and clock jitter analysis capabilities at this level are very limited.

## 2.3.3 Summary

The features of the simulation tools available for SDMs are summarized in Table 2.1. They are evaluated on the element abstraction level, the simulation accuracy and efficiency achieved, the computer memory needed, and the noise analysis capabilities. The goal of this research is listed in the column marked as *objective*.

|                  | SPICE      | ZSIM        | SWITCAP2 | SAMBA  | MIDAS   |

|------------------|------------|-------------|----------|--------|---------|

| year             | 1975       | 1988        | 1990     | 1990   | 1992    |

| model accuracy   | transistor | transistor  | ideal SC | PSLN   | block   |

|                  |            | block       |          |        |         |

| simulation acc   | low        | medium      | high     | high   | high    |

| efficiency       | extremely  | block(fast) | fast     | medium | fast    |

|                  | slow       | table(slow) |          |        |         |

| memory needed    | large      | large       | medium   | large  | small   |

| thermal noise    | ×          | ×           | ×        | ×      | general |

| clock jitter     | ×          | ×           | ×        | ×      | noise   |

| dithering effect | ×          | ×           | ×        | ×      | effects |

|                  | TOSCA           | AWEswit | SDSIM / DELTA | objective |

|------------------|-----------------|---------|---------------|-----------|

| year             | 1992            | 1993    | 1994          |           |

| model accuracy   | block, ideal SC | PSLN    | PSLN          | PSLN      |

| simulation acc   | high            | medium  | high          | high      |

| efficiency       | fast            | medium  | fast          | fast      |

| memory needed    | medium          | medium  | medium        | medium    |

| thermal noise    | general         | x       | ×             | ✓         |

| clock jitter     | noise           | x       | ×             | √         |

| dithering effect | effects         | ×       | ×             | ✓         |

Table 2.1: Simulators for Sigma-delta Modulators

# 2.4 Sampled Data Analysis of Analog Circuits

Sampled-data analysis can simultaneously maintain the accuracy and efficiency of simulation. In this thesis, new sampled-data methods for noise and clock jitter analysis are developed. A brief review of the background is provided in this section.

Given a linear time invariant network, the state variable vector  $\mathbf{x}(t)$ , its initial state  $\mathbf{x}_0$  and the input u(t) for  $t \geq t_0$ , we wish to find the output  $\mathbf{y}(t)$  for  $t \geq t_0$ . The State Space equations can be formulated as:

$$\dot{\mathbf{x}}(t) = \mathbf{A}\mathbf{x}(t) + \mathbf{B}u(t), \quad \mathbf{x}(t_0) = \mathbf{x}_0$$

$$\mathbf{y}(t) = \mathbf{C}\mathbf{x}(t) + \mathbf{D}u(t)$$

(2.5)

where A, B, C, D are constant coefficient matrices.

The time-domain solution [68] of the State Space equation (2.5) is:

$$\mathbf{x}(t) = e^{\mathbf{A}(t-t_0)}\mathbf{x}(t_0) + e^{\mathbf{A}t} \int_{t_0}^t e^{-\mathbf{A}\tau} \mathbf{B}u(\tau) d\tau$$

(2.6)

where the first term corresponds to the *natural response* or the *zero-input response*, and the second term corresponds to the *forced response* or the *zero-state response*. The matrix exponential  $e^{\mathbf{A}t}$  is defined as an infinite series:

$$e^{\mathbf{A}t} = \mathbf{I} + \mathbf{A}t + \frac{1}{2!}(\mathbf{A}t)^2 + \dots + \frac{1}{k!}(\mathbf{A}t)^k + \dots$$

(2.7)

The output y(t) can be obtained by straightforward algebraic operations once the solution for x(t) is known.

Chua and Lin [68] considered the time-domain sampled-data analysis of the state equation (2.5). Both  $\mathbf{x}(t)$  and  $\mathbf{y}(t)$  were determined only for some discrete values of t, for example,

$$t = t_0, t_0 + T, t_0 + 2T, \cdots, t_0 + kT, \cdots$$

(2.8)

where k is an integer and T is a suitably chosen time interval. The input u(kT) is assumed to be known for all k, and an equation that relates  $\mathbf{x}(kT+T)$  to  $\mathbf{x}(kT)$  and u(kT) is looked for. Once this difference equation is obtained,  $\mathbf{x}(kT)$  can be calculated successively for all k, which is a special form of numerical integration. Let  $t_0 = kT$  and t = kT + T, equation (2.6) can be written as

$$\mathbf{x}(kT+T) = e^{\mathbf{A}(T)}\mathbf{x}(kT) + e^{\mathbf{A}(kT+T)} \int_{kT}^{kT+T} e^{-\mathbf{A}\tau} \mathbf{B}u(\tau)d\tau$$

(2.9)

Equation (2.9) was transferred into exact difference equation formula for two special input cases, namely, piecewise constant inputs and continuous piecewise linear inputs. For general continuous-time inputs, the forcing function u(t) was approximated by piecewise-constant or piecewise-linear waveforms, and (2.9) was transferred into approximate difference equations.

Sampled data analysis of analog circuits, or analysis of analog circuits by difference equations, reveals the circuit behavior with full analog details at discrete instants of time. The associated computational cost is a cheap difference equation simulation. The usefulness of the approach by Chua and Lin is limited, however, due to the fact that

- It is based on State-Space formulation, where the state transition matrix, e<sup>AT</sup>, is computed, and the simulation is carried out by solving state-variables in a successive fashion. Although useful in theoretical studies, the State-Space formulation is no longer used in computer applications [55]. Approaches based on formulation methods widely used in modern computer-aided analysis tools, such as Modified Nodal Analysis (MNA), are preferred.

- 2. The state transition matrix is approximated by a finite number of terms of the infinite series expansion in (2.7). A large number of terms is needed to avoid the numerical instability problem [68].

3. The representation of the integral by difference equation is exact only for piecewise constant or piece-wise linear inputs. For other common inputs like sinusoids, it is obtained by approximation. This not only complicates the computer code, but also results in significant errors, especially when simulated over a large number of time points.

Opal [19] recognized that for a complex exponential input

$$u(t) = e^{st}, \quad t \ge t_0, \tag{2.10}$$

the integral part of (2.6) corresponding to the zero-state response can be written in closed form as

$$\mathbf{x}_{ZS}(t) = e^{\mathbf{A}t} \int_{t_0}^t e^{-\mathbf{A}\tau} \mathbf{B} u(\tau) d\tau$$

$$= e^{st_0} (s\mathbf{I} - \mathbf{A})^{-1} [e^{s(t-t_0)} \mathbf{I} - e^{\mathbf{A}(t-t_0)}] \mathbf{B}.$$

(2.11)

Define a constant matrix M and a constant vector P as:

$$\mathbf{M} = e^{\mathbf{A}T},$$

$$\mathbf{P} = (s\mathbf{I} - \mathbf{A})^{-1} [e^{sT}\mathbf{I} - e^{\mathbf{A}T}]\mathbf{B}.$$

(2.12)

With  $t_0 = 0$ , formula (2.9) can be written as a difference equation:

$$\mathbf{x}(T) = \mathbf{M}\mathbf{x}_0 + \mathbf{P}, \qquad (2.13)$$

$$\mathbf{x}(nT+T) = \mathbf{M}\mathbf{x}(nT) + \mathbf{P}e^{snT}.$$

Multiple complex exponential inputs can be included by applying the superposition rule for linear circuits

$$\mathbf{x}(nT+T) = \mathbf{M}\mathbf{x}(nT) + \sum_{i=1}^{k} \mathbf{P}_{i}e^{s_{i}nT}, \qquad (2.14)$$

where k is the number of inputs. The benefit of considering complex exponential inputs is obvious. It enables the *exact* expression of the circuit response for a wide variety of common input functions. Sinusoidal inputs are included by setting  $s = j\omega$ , and in the case of  $u(t) = \cos(\omega t)$ , equation (2.13) is modified to:

$$\mathbf{x}(nT+T) = \mathbf{M}\mathbf{x}(nT) + Re(\mathbf{P}e^{j\omega nT}), \tag{2.15}$$

where Re(.) denotes the real part of a complex argument. For input  $u(t) = \sin(\omega t)$ , the imaginary part is used instead. Step inputs are included by setting  $\omega = 0$  in equation (2.15), and the introduction of additional input functions is discussed in [19].

The MNA equations for a LTI circuit are [55]

$$\mathbf{G}\mathbf{v}(t) + \mathbf{C}\frac{d\mathbf{v}(t)}{dt} = \mathbf{d}u(t), \quad \mathbf{v}(0) = \mathbf{v}_0$$

(2.16)

where all conductances and constants arising in the formulation are stored in the matrix G, all capacitor and inductor values are stored in the matrix C, the connection of the input source to the circuit is in d, v(t) is the vector of node voltages and some branch currents needed for MNA, and  $v_0$  is the initial condition vector.

The derivations of the matrix M and vector P in MNA are given in [62], together with the numerical computation algorithms. It provides a solid foundation for the utility of this sampled-data method in computer applications. The matrix M and vector P are defined as

$$\mathbf{M} = \mathcal{L}^{-1}[(\mathbf{G} + p\mathbf{C})^{-1}]\Big|_{t=T}\mathbf{C},$$

$$\mathbf{P} = \mathcal{L}^{-1}[(\mathbf{G} + p\mathbf{C})^{-1}\mathbf{d}U(p)]\Big|_{t=T},$$

(2.17)

where p is the Laplace complex parameter, and  $\mathcal{L}^{-1}(.)$  denotes the inverse-Laplace transform. For an input given by (2.10), the solution of (2.16) at t = nT can be written in a similar way to (2.13):

$$\mathbf{v}(nT+T) = \mathbf{M}\mathbf{v}(nT) + \mathbf{P}e^{snT}. \tag{2.18}$$

This method is efficient. For a given time interval, a constant matrix M and a constant vector P are computed only once. The computational cost associated with each point during simulation is in the order of  $O(m^2)$ , where m is the size of the system matrix. It is also accurate. Since the constant matrices are computed only once, extra effort can be spent on computing them as accurately as necessary. Because a stable system will damp out any numerical errors [19], the error introduced by finite precision arithmetic will not increase with the increase of simulation time. Besides the transient analysis of LTI circuits at fixed discrete instants of time, this method is also applicable to PSL networks and SDMs [19, 62].

# 2.5 A Numerical Laplace Transform Inversion Method

In this section, we review a numerical Laplace Transform inversion method [69, 70, 71]. It can be used for time domain solution of LTI networks, and is equivalent to numerical integration of differential equations. Because this method can provide accurate results and can handle discontinuous functions like Dirac impulses, it was chosen as the integration method for the differential equations formulated in this thesis. In particular, it was used for the computation of the time derivatives of the transition matrix and of the input transfer vector.

The method is based on numerical evaluation of the Laplace transform inversion integral

$$v(t) = \frac{1}{2\pi j} \int_{c-i\infty}^{c+j\infty} V(s)e^{st}ds$$

(2.19)

where s is the complex frequency and V(s) is the Laplace transform. Exact inversion is possible only if the poles of V(s) are known, and some approximations are necessary to avoid root-finding procedures. The change of variables z = st was introduced, and

equation (2.19) becomes

$$v(t) = \frac{1}{2\pi jt} \int_{c'-i\infty}^{c'+j\infty} V(z/t)e^{z}dz.$$

(2.20)

Next,  $e^z$  was approximated by a Padé rational function

$$R_{N,M} = \frac{\sum_{i=0}^{N} (M+N-i)! \binom{N}{i} z^{i}}{\sum_{i=0}^{M} (-1)^{i} (M+N-i)! \binom{M}{i} z^{i}}.$$

(2.21)

The approximation  $\hat{v}(t)$  to v(t) becomes

$$\hat{v}(t) = \frac{1}{2\pi j t} \int_{c'-j\infty}^{c'+j\infty} V(z/t) R_{N,M}(z) dz.$$

(2.22)

Parameters M and N must be chosen so that the function  $V(z/t)R_{N,M}(z)$  has at least two more finite poles than zeros. For N < M,

$$R_{N,M}(z) = \sum_{i=1}^{M} \frac{K_i}{z - z_i}$$

(2.23)

where  $z_i$  are the poles and  $K_i$  are the residues of  $R_{N,M}$ . They were computed with high precision and recorded in tables. The integral in (2.22) can be calculated by residue calculus as

$$\hat{v}(t) = -\frac{1}{t} \sum_{i=1}^{M} K_i V(z_i/t). \tag{2.24}$$

For a given function V(s), its time domain waveform is computed numerically from (2.24). Real-time functions can be evaluated using only the poles in the upper half plane, and the computational cost is reduced by one-half.

The formula (2.24) is exact for time domain functions that are polynomials of t of order upto M + N. For general functions, it exactly inverts the first M + N + 1 terms of the Taylor series expansion. Due to the division by t in (2.24), this method cannot be used for t = 0, but discontinuous functions like unit-step and Dirac impulses at time zero do not cause any problem.

The inversion by (2.24) is very accurate for small values of t, but error grows with time. In order to preserve accuracy, a stepping algorithm is used to reset the time origin after each step. The resetting is easy to apply for lumped linear networks, and is equivalent to numerical integration of differential equations. The order of integration can be changed between 1 and 46 without any difficulty. It is a very high order and absolutely stable integration method. Compared with ordinary integration methods, an additional advantage is: it can correctly handle discontinuous functions, and can be used across the switching instants. The disadvantages are: (1) It is based on the Laplace transform formula, and loses its advantages if the functions are nonlinear; (2) It is based on complex number arithmetic, and requires network solution at multiple frequencies for each integration step. The per step computational cost is usually larger than ordinary integration methods.

The time domain derivatives of the network function can also be evaluated. They are based on the property of Laplace transform

$$\mathcal{L}[v^{(n)}(t)] = s^n V(s) - \sum_{k=1}^n v^{(k-1)}(0^-) s^{n-k}. \tag{2.25}$$

Select N and M so that  $(z/t)^n V(z/t) R_{N,M}(z)$  has at least two more finite poles than zeros. Then all terms after the summation in (2.25) do not contribute to the inversion, and the formula for the n-th derivative of v(t) is obtained as

$$\hat{v}^n(t) = -\frac{1}{t} \sum_{i=1}^M K_i(z_i/t)^n V(z_i/t), \quad t > 0.$$

(2.26)

The derivative can be computed with little extra effort, as most of the time is spent on the evaluation of  $V(z_i/t)$ .

# Chapter 3

# **Noise Analysis**

Although during the design cycle of SDMs, information on the circuit thermal noise performance is very useful [3, 4], general noise analysis methods for SDMs are still not available.

This chapter presents a new time domain noise analysis method at electrical circuit level. It can be applied to thermal noise analysis of SDMs, and is useful for PSL networks, where frequency domain noise analysis cannot be done easily.

The theories were implemented in a computer program. Numerical examples are given and, where possible, comparisons with exact analysis or physical measurements are made. Primitive results of this chapter were reported in [72, 73].

## 3.1 Introduction

Electrical noise is usually small in comparison to other signals and may be ignored. However, given the present trend towards low voltage and low power designs, it can become significant and limit the circuit performance in a fundamental way. Accurate prediction of noise at the output of a circuit becomes necessary to evaluate performance measures like SNR and DR. This is especially true for high resolution circuits like SDMs.

In traditional SPICE type simulators, noise simulation is available in frequency domain. However, frequency domain noise analysis of SDMs is not possible. General methods for simulation of SDMs have been presented by many researchers [63, 10, 65, 14, 11, 16, 18, 61, 19], but nobody has given a method for noise analysis of SDMs at electrical circuit level. Their noise performance remains unknown until physical measurements are made on the manufactured samples.

In this chapter, we present algorithms for *time domain* noise analysis of SDMs. In addition, the algorithms can be applied to periodically switched linear networks, such as SC and SI filters, where frequency domain analysis is complicated. The method computes the complete transient response to noise and other desired signals in a sampled data manner. It simultaneously addresses the issues of accuracy and efficiency. A brief introduction to circuit noise sources in integrated circuits is given in section 3.2. Noise analysis methods for LTI circuits, PSL networks, and nonlinear circuits are reviewed in section 3.3. The new method is presented in section 3.4, and numerical results for the noise analysis of a few circuits are given in section 3.5.

## 3.2 Circuit Noise Sources and Models

Electrical noise is random fluctuations in currents and voltages due to the discrete nature of electronic charge. These fluctuations are called thermal, shot, or flicker noise, based on the physical mechanism that produces them [74]. In this section, we give a brief review of circuit noise sources and their modeling techniques.

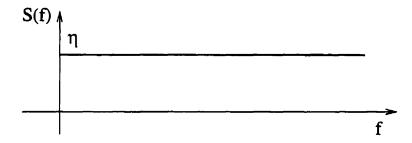

Thermal noise arises from random thermal motion of free electrons in a conducting medium. The net effect of the thermal motion of all electrons constitutes a noise current flowing through the conductor with random directions and zero mean value. Thermal noise spectrum is flat up to 6000 GHz [75], which is much higher than the bandwidth of most circuits. For practical purposes, thermal noise is considered white and contains all frequencies in equal amount. For a conductance of value G, the power spectrum density of the thermal noise current is given as

$$S(f) = 4kTG \quad A^2/Hz, \quad f \ge 0 \tag{3.1}$$

Frequency domain representation of thermal noise consists of a constant PSD  $S(f) = \eta$  versus frequency. It is shown in Fig. 3.1.

Figure 3.1: Power spectrum density for thermal noise

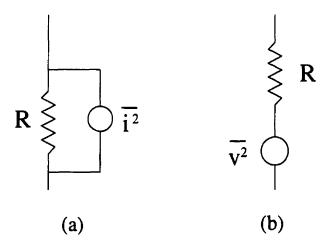

A noisy resistor can be modeled, either by its Norton equivalent as a noiseless resistor in parallel with a current noise source with power  $4kTG\Delta f$ , where  $\Delta f$  is the noise bandwidth of interest, or by its Thevenin equivalent as a voltage source in series with the noiseless resistor, as shown in Fig. 3.2.

**Shot noise** is always associated with direct-current flow. Its power spectrum is [76]

$$S(f) = 2qI_D \quad A^2/Hz, \quad f \ge 0 \tag{3.2}$$

Figure 3.2: Resistor thermal noise model

where q is the electronic charge, and  $I_D$  is the average forward-bias current. Equation (3.2) holds up to gigahertz frequency range.

Flicker noise, also known as 1/f noise, exists in active devices and some discrete passive elements like carbon resistors. In bipolar transistors, it arises from the random capture and release of charge carriers by traps associated with contamination and crystal defects. Flicker noise is always associated with direct current flow. Its power spectrum is [76]

$$S(f) = K_1 \frac{I^a}{f^b} \quad A^2/Hz, \quad f \ge 0$$

(3.3)

where I is the direct current in Amperes, f is frequency in Hertz,  $K_1$  is a device dependent constant, and a, b are constants used in modeling.

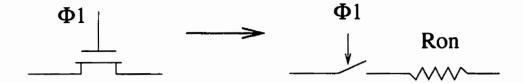

Noise in a MOSFET switch is dominated by the thermal noise associated with its channel ON-resistance, while the noise generated in the OFF state is usually neglected [25]. A common model for a MOSFET switch is shown in Fig. 3.3, as an ideal switch in series with a noisy resistor. An operational amplifier is a complex functional block with a large

Figure 3.3: Switch thermal noise model

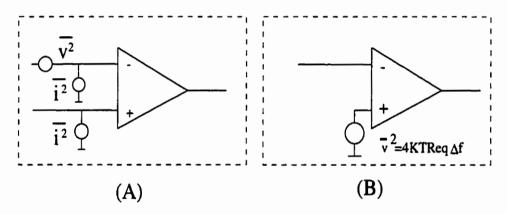

number of noise sources. Its noise behavior is usually characterized by lumped equivalent noise current and noise voltage sources at the input [76], as shown in Fig. 3.4(A). The input noise currents of modern opamps are very small, and are usually neglected [25]. A widely used thermal noise model for opamps is shown in Fig. 3.4(B), where  $R_{eq}$  is the equivalent thermal noise resistance.

Figure 3.4: Opamp thermal noise model

# 3.3 Noise Analysis Methods: Review

Noise analysis of electrical circuits is performed either in time or frequency domain. Electrical circuits are generally classified as linear circuits, where frequency domain analysis methods are used, or as nonlinear circuits, where time domain analysis methods are used. In the following, the noise analysis methods based on these classifications are reviewed.

### 3.3.1 Linear Circuits and Frequency Domain Noise Analysis

In frequency domain noise analysis, the PSD of the noise source is given and the circuit is generally restricted to be lumped, linear and time-invariant (LLTI). If the circuit is nonlinear, it is assumed to have a fixed bias and can be linearized around the DC operating point. Noise analysis is done on the linear small signal model. For LLTI circuits the noise power at the output,  $S_o(f)$ , is related to the input noise power,  $S^i(f)$ , by the frequency domain transfer function from the noise source to the output, H(f), by the relation

$$S_o(f) = |H(f)|^2 S^i(f)$$

(3.4)

Typically, there are many uncorrelated noise sources, and it is necessary to compute the transfer function from each noise source to the output at each frequency of interest. The total noise at the output is then

$$S_o(f) = \sum_{n=1}^{N} |H_n(f)|^2 S_n^i(f)$$

(3.5)

where  $H_n(f)$  is the transfer function from the *n*-th noise source  $S_n^i(f)$  to the output, and N is the total number of noise sources in the circuit. If we are interested in the noise power at only one output, then the computational cost can be reduced by using the adjoint network concept [20, 77]. Noise analysis of LLTI circuits in frequency domain is well established and is available in most SPICE-like analog simulators.

Closely related to LLTI circuits are PSL networks, which are lumped linear circuits with periodically operated switches. Direct frequency analysis of these circuits is possible [78, 79, 80]. As in the case of LLTI circuits, the noise analysis is done in the