# Analog/Mixed Signal Circuit Design with Transparent Oxide Semiconductor Thin-Film Transistors

# Pydi Ganga Mamba Bahubalindruni

Supervisor: Prof. Vitor Grade Tavares

Co-Supervisor: Prof. Pedro Barquinha

Co-Supervisor: Prof. Pedro Guedes de Oliveira

Programa Doutoral em Engenharia Electrotécnica e de Computadores

#### Faculdade de Engenharia da Universidade do Porto

## Analog/Mixed Signal Circuit Design with Transparent Oxide Semiconductor Thin-Film Transistors

#### Pydi Ganga Mamba Bahubalindruni

Dissertation submitted to Faculdade de Engenharia da Universidade do Porto to obtain the degree of

**Doctor Philosophiae in Electronic & Computer Engineering**

President: Name of the President Referee: Name of the Referee Referee: Name of the Referee Referee: Name of the Referee

# **Abstract**

Amorphous Gallium Indium Zinc Oxide (a-GIZO) belongs to the new class of amorphous oxide semiconductors (AOS) that have gained a significant interest in recent years as active layers for thin-film transistors (TFTs). Fabrication with a-GIZO is highly cost effective due to possible low-temperature processes, and the material itself is almost fully transparent to the visible spectrum of light, opening a panoply of new application possibilities. Low-temperature fabrication allows the use of different substrates, with direct device level printing, such as in paper, plastic or glass, allowing the construction of flexible as well as transparent electronic devices at exceedingly competitive prices. Furthermore, a-GIZO presents better electrical characteristics than other TFT technologies, such as a-Si:H and organic TFTs (OTFTs). All these features will push even more the a-GIZO to the mainstream consumer electronics. Up to date, however, the TFT technologies have been almost exclusively used for displays, RFIDs [1, 2] and sensor fabrication [3, 4]. Nevertheless, there is still little emphasis towards circuit design with a-GIZO TFTs. The main goal of this PhD work is then to develop a framework and circuits, which will ultimately accomplish the necessary conditions to design electronic systems with post-silicon technology, specifically with a-GIZO TFTs.

Particular attention will be given in this dissertation to circuit design, with the goal of achieving an integrated system based on a single substrate, where the sensors and signal processing or conditioning circuits can be realized with the same technology. In order to make such system feasible with a-GIZO, the development of analog processing and conditioning circuits are required. Then the present work focuses on the development, design and fabrication of various important analog/mixed signal building blocks needed to perform signal processing and conditioning. Further testing, feasibility and limitations of the technology for circuit design is analysed. As a first step, a neural-based equivalent circuit model is developed from the measured characteristics of the device, both from the static and dynamical perspective. Finally, simulation outcomes are validated against the measured response from the fabricated circuits.

Basic analog building blocks, such as different types of current mirrors, buffers, (common source) CS amplifier, differential pair, novel high-gain amplifiers, adders, multipliers, logic gates, high-gain comparator and four-bit folding analog to digital converter (ADC) were designed, simulated and fabricated. Some of these circuits were successfully characterized. During the comparator design, care has been taken to minimize the bias stress impact. The single stage novel amplifier, in this work, resulted in the highest gain with a-GIZO TFT technology so far. Similarly, the comparator and the folding ADC are the first mixed signal building blocks designed with a-GIZO, at least until the time of writing of this document.

The research work was developed in collaboration with CENIMAT group at UNL, where all the above mentioned circuits were fabricated.

**Keywords:** a-GIZO TFTs. Neural modeling. Circuit design.

## Resumo

Os óxidos amorfos de Índio Gálio e Zinco (a-GIZO) pertencem a uma nova classe de óxidos semicondutores amorfos (AOS) que nos últimos anos tem ganhado um interesse significativo da comunidade científica, como elemento na camada ativa de transístores de filme fino (TFT). A fabricação a baixa temperatura, com consequentes baixos custos de fabricação e melhores características elétricas em comparação com outras tecnologias TFT, como a-Si:H e TFTs orgânicos (OTFTs), são as principais características responsáveis pela atenção que os TFTs baseados em a-GIZO têm recebido. O material a-GIZO é transparente no espectro de luz visível e a fabricação de baixa temperatura possibilita o uso de diferentes substratos, como papel, plástico ou vidro, permitindo a construção de dispositivos eletrónicos flexíveis e transparentes, a custos extremamente competitivos. Sendo um processo de baixo custo que tem como base dispositivos eletrónicos flexíveis e transparentes, potencia um vasto conjunto de novas aplicações. No entanto, e até ao momento, as tecnologias TFT têm sido usadas quase exclusivamente para monitores (flat displays), dispositivos RFID [1, 2] e na fabricação de sensores [3, 4], havendo muito pouca ênfase no projeto de circuitos com dispositivos a-GIZO. O principal objetivo deste trabalho de doutoramento é, então, desenvolver uma estrutura que permita reunir as condições necessárias para projetar circuitos eletrónicos com tecnologia de pós-silício, especificamente com TFTs a-GIZO. Um dos objetivos principais desta dissertação é a concepção de circuitos, no sentido de alcançar um sistema totalmente integrado usando um único substrato, onde os sensores e circuitos de processamento e condicionamento de sinal possam ser realizados com a mesma tecnologia. A fim de tornar possível tal realização com a-GIZO, é necessário desenvolver os respetivos circuitos. Por essa razão o presente trabalho concentra-se no desenvolvimento, projeto e fabricação de vários blocos analógicos e mistos importantes e necessários para a realização do processamento e condicionamento de sinal. Numa primeira fase é desenvolvido um modelo equivalente elétrico, com base em redes neuronais e a partir das características de medição do dispositivo, que caracterize corretamente o comportamento estático e dinâmico do dispositivo, tendo como objeto a possibilidade de simulação elétrica. De seguida, com base neste modelo, circuitos clássicos bem como novas propostas são simulados apenas com TFTs de enriquecimento do tipo n. Finalmente, os resultados da simulação de circuitos são validados com a resposta medida dos respetivos circuitos fabricados. São desenvolvidos e fabricados vários blocos analógicos básicos, tais como diferentes tipos de espelhos de corrente, buffers, amplificador de CS (Common Source ou fonte comum), par diferencial, novos amplificadores de alto ganho, somadores, multiplicadores, portas lógicas, comparador de elevado ganho e um conversor analógico/digital (ADC) de 4 bits. Durante o projeto do comparador, vários cuidados foram tomados no sentido de minimizar o stress de polarização. O amplificador de andar único proposto resultou no maior ganho obtido com TFTs a-GIZO até ao momento. Da mesma forma, o comparador e o ADC são os primeiros blocos de sinal misto até a data. Este trabalho desenvolve-se com o grupo do CENIMAT na UNL, responsáveis pela

fabricação dos circuitos descritos no presente trabalho.

**Keywords:** a-GIZO TFTs. Neural modeling. Circuit design.

# Acknowledgements

I would like to thank my PhD supervisor, Prof. Vtor Grade Tavares, for his continuous encouragement, valuable guidance and motivation. He is always open to new ideas and gave me lot of flexibility in my work. This, in fact helped me not feeling stressed, during the complete period of PhD. Especially, his efforts in meeting deadlines are invaluable. This PhD would have been impossible without his extreme guidance.

I would also like to thank my co-supervisor Prof. Pedro Barquinha, for his great support and help in sharing his knowledge about the GIZO technology. Because of his guidance, we were able to build the chip even in the phase, where, there are no technology files for GIZO technology. His advises on selecting papers for submissions helped me a lot.

I thank to my husband Sujit, who is always with me. His friendly support, motivation, encouragement and suggestions are very helpful in overcoming the hard time. I also would like to thank to my parents and brothers who always supported me and gave enough strength to complete this PhD work.

I thank to Nuno Cardoso and Bruno Silva. Their developments (technology library files for layout design for a-GIZO TFT technology) were extremely helpful, especially, in complex circuit layout designs. Their help in circuits testing is highly appreciable.

I extend my thanks to Prof. Pedro Guedes de Oliveira, Prof. Elvira Fortunato and Prof. Rodrigo Martins for their valuable suggestions.

I would also like to my other friends Paulo, Catarina and Hamza, who were very helpful and on whom I could trust during several cumbersome situations.

I would like to thank my friends, Cristina and Fardin, who are always around. I would also like to thank other friends Andre, Daniel, Antonio, Candido, Iman, Bilal, Bruno, Joao and Xuanle. This stay in Porto was fun due to the presence of my Indian friends Shazia, Asif, Kritika, Vikram, Anuj, Priya, Dakshina, Guru and Shshank.

This acknowledgement cannot be complete with out thanking Dr. Jerome Borme, who performed dicing and wire-bonding of the circuits. His patience and efforts are invaluable. Without the wire-bonding complex circuits testing would have been impossible.

Finally I would like to thank funding organization FCT (SFRH/BD/62678/2009), SELF-PVP project (CMU-PT/SIA/0005/2009), INESC and FEUP

Pydi Ganga Mamba Bahubalindruni

"Arise, awake, and stop not till the goal is reached"

Swami Vivekananda

# **Contents**

| Li | st of I | Figures       |                                                   | xvii |

|----|---------|---------------|---------------------------------------------------|------|

| Li | st of T | <b>Fables</b> |                                                   | xix  |

| Li | st of A | Abbrevi       | ations                                            | xxii |

| 1  | Intr    | oductio       | n                                                 | 1    |

|    | 1.1     | Main o        | objectives                                        | . 2  |

|    | 1.2     | Contri        | bution                                            | . 4  |

|    | 1.3     | publica       | ations                                            | . 4  |

|    |         | 1.3.1         | Journals                                          | . 4  |

|    |         | 1.3.2         | International Conferences                         | . 5  |

|    |         | 1.3.3         | Other Publications                                | . 5  |

|    | 1.4     | Docun         | nent outline                                      | . 6  |

| 2  | a-G     | IZO Teo       | chnology: What it is and what are its Challenges  | 7    |

|    | 2.1     | Thin-F        | Film Transistors Technologies                     | . 7  |

|    |         | 2.1.1         | a-GIZO TFTs as the Next Mainstream TFT technology | . 8  |

|    | 2.2     |               | Device Structures                                 |      |

|    | 2.3     | TFT O         | Operation and Electrical Characterization         |      |

|    |         | 2.3.1         | Parasitic Resistors and Capacitors                |      |

|    |         | 2.3.2         | Channel Length Modulation                         |      |

|    |         | 2.3.3         | On-Resistance                                     |      |

|    | 2.4     |               | nges for Circuit Design                           | . 16 |

|    |         | 2.4.1         | Design Flow                                       |      |

|    |         | 2.4.2         | Hindrances in the Design of Analog Circuits       |      |

|    |         | 2.4.3         | Instabilities                                     | . 19 |

|    | 2.5     |               | arison of TFT Layouts                             |      |

|    | 2.6     |               | abrication Process                                |      |

|    |         | 2.6.1         | Thin-film Deposition Techniques                   | . 23 |

|    |         | 2.6.2         | Pattering Techniques                              |      |

|    |         | 2.6.3         | Annealing:                                        |      |

|    |         | 2.6.4         | Fabricated Devices                                | . 24 |

| 3  | Mod     | leling        |                                                   | 27   |

|    | 3.1     | Introdu       | uction to Modeling                                | . 27 |

|    | 3.2     | Traditi       | ional Modeling Methods                            |      |

|    |         | 3.2.1         | Physical Modeling                                 | . 29 |

|    |         | 3.2.2         | Table Based Modeling                              | . 30 |

xii CONTENTS

|    |       | 3.2.3 Empirical Modeling                           | C      |

|----|-------|----------------------------------------------------|--------|

|    | 3.3   | Model Selection for a-GIZO TFT IC Design           | 1      |

|    | 3.4   | ANNs for Nonlinear Semiconductor Modeling          | 2      |

|    |       | 3.4.1 Multi Layer Perceptron                       | 4      |

|    |       | 3.4.2 Radial Basis Function                        | 7      |

|    |       | 3.4.3 Least Square-Support Vector Machine          | 9      |

|    |       | 3.4.4 Discussion from MOSFET Modeling Results      | -1     |

|    | 3.5   | TFT Static Modeling                                | -2     |

|    |       |                                                    | 4      |

|    |       |                                                    | 6      |

|    | 3.6   | Dynamic Modeling                                   | 8      |

|    |       | 3.6.1 MOSFET Dynamic Modeling                      | 8      |

|    |       | · · · · · · · · · · · · · · · · · · ·              | 0      |

|    |       | · · · · · · · · · · · · · · · · · · ·              | 0      |

|    |       |                                                    | 2      |

|    | 3.7   |                                                    | 3      |

| 4  | Rasi  | Building Blocks for a-GIZO TFT IC Design 5         | 7      |

| •  | 4.1   |                                                    | 7      |

|    | 4.2   |                                                    | 8      |

|    | 7.2   |                                                    | 59     |

|    |       |                                                    | 54     |

|    |       |                                                    | 54     |

|    |       | 4.2.4 Basic Amplifiers                             |        |

|    |       | 4.2.5 Single Stage High-Gain Topologies            |        |

|    | 4.3   |                                                    | ے<br>1 |

|    | т.Э   |                                                    | 31     |

|    |       |                                                    | 3      |

|    |       | 6 6                                                | 35     |

|    | 4.4   | *                                                  | 9      |

| _  | 17-13 | ing ADC with Resistive Interpolation               | 1      |

| 5  |       | 8                                                  |        |

|    | 5.1   | 1                                                  |        |

|    |       | Analog Signal Processing Block                     |        |

|    | 5.3   | Folding ADC Characterization                       | 9      |

| 6  | Con   | clusions and Future Work 10                        |        |

|    | 6.1   | Conclusions                                        | 15     |

|    | 6.2   | Future directions                                  | 16     |

|    |       | 6.2.1 Modeling                                     | 16     |

|    |       | 6.2.2 Circuit Design                               | 16     |

| In | dex   | 11                                                 | 9      |

| Д  | Mas   | er thesis co-supervised 11                         | g      |

| 4. |       | DC-DC converters                                   |        |

|    |       | Analog Circuit Design with Transparent Flortranics |        |

# **List of Figures**

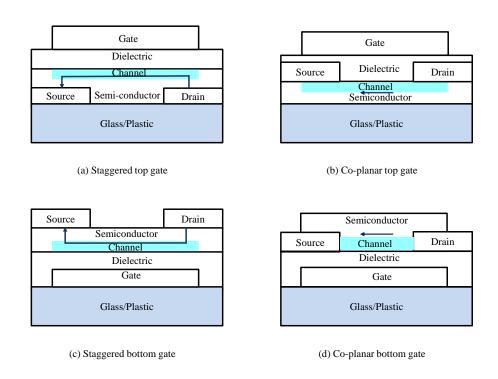

| 2.1  | Four possible TFT structures: solid line with arrow shows the current flow direction                                                                                                                                                                         | 11 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

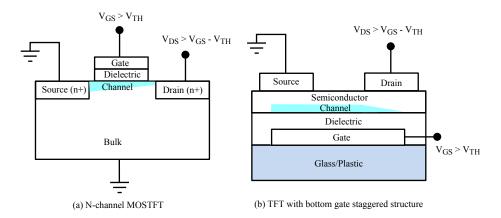

| 2.2  | Structural difference between MOSFET and a-GIZO bottom gate staggered TFT. Schematic shows device operation in saturation regime                                                                                                                             | 12 |

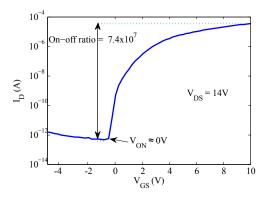

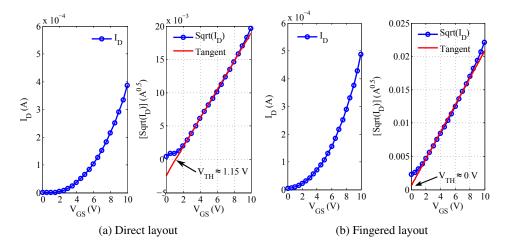

| 2.3  | Transfer characteristics of a-GIZO staggered bottom gate TFT with $W = 40 \mu m$                                                                                                                                                                             |    |

|      | and L = $20 \mu$ m                                                                                                                                                                                                                                           | 12 |

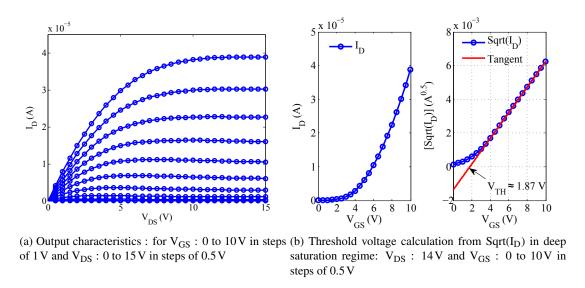

| 2.4  | Electrical characteristics of the TFTs for W = $40 \mu\text{m}$ and L = $20 \mu\text{m}$                                                                                                                                                                     | 13 |

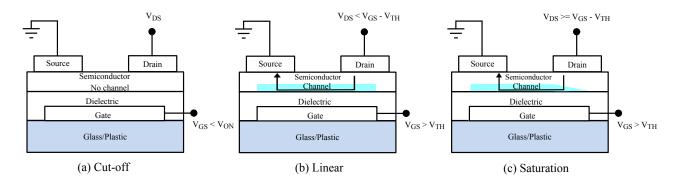

| 2.5  | TFT operation in different regimes                                                                                                                                                                                                                           | 14 |

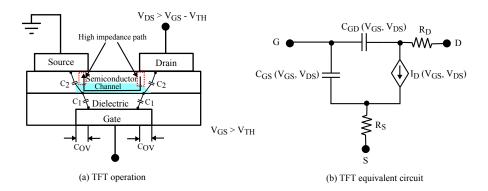

| 2.6  | TFT equivalent circuit                                                                                                                                                                                                                                       | 15 |

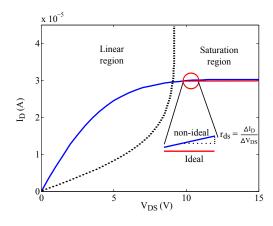

| 2.7  | Channel length modulation                                                                                                                                                                                                                                    | 15 |

| 2.8  | Analog design basic steps                                                                                                                                                                                                                                    | 17 |

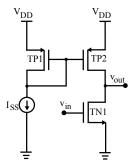

| 2.9  | Simple common-source amplifier with complementary transistors                                                                                                                                                                                                | 19 |

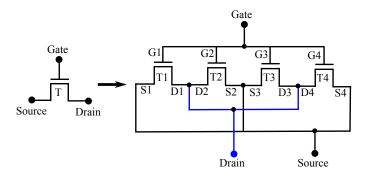

| 2.10 | Wider TFT equivalent in terms of TFT with smaller widths when the transistors                                                                                                                                                                                |    |

|      | have same length and $W_T = W_{T1} + W_{T2} + W_{T3} + W_{T4}$                                                                                                                                                                                               | 21 |

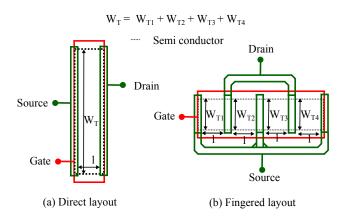

| 2.11 | Wider TFT direct and fingered layout, when the TFTs have same length                                                                                                                                                                                         | 21 |

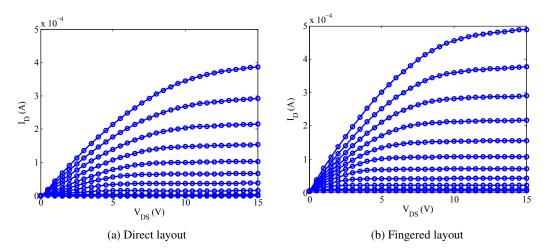

| 2.12 | Drain current of the TFTs with direct and fingered layouts, where width = $320 \mu$ m and length = $20 \mu$ m from the same chip; for $V_{GS}$ : 0 to 10 V in steps of 1 V and                                                                               |    |

|      | $V_{DS}$ : 0 to 15 V in steps of 0.5 V                                                                                                                                                                                                                       | 22 |

| 2.13 | Threshold voltages of the TFTs with direct and fingered layouts, where W =                                                                                                                                                                                   |    |

|      | $320\mu\text{m}$ and L = $20\mu\text{m}$ from the same chip; for V <sub>GS</sub> : 0 to 10 V in steps of 0.5 V                                                                                                                                               |    |

|      | and $V_{DS}$ 15 V i.e., under deep saturation                                                                                                                                                                                                                | 22 |

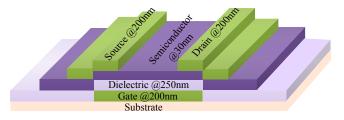

|      | TFT structure                                                                                                                                                                                                                                                | 25 |

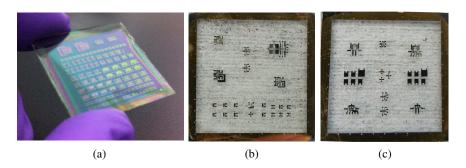

| 2.15 | (a) Fabricated Transparent chip (b) Micrograph of a single a-GIZO TFT                                                                                                                                                                                        | 25 |

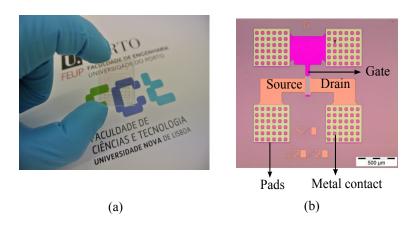

| 3.1  | Employed equivalent circuit from the device structure when the bulk is an insulator (a) TFT equivalent circuit with series resistance components (b) Equivalent circuit components, to be modeled with ANNs: measured $I_D$ includes $R_S$ and $R_D$ impact. | 32 |

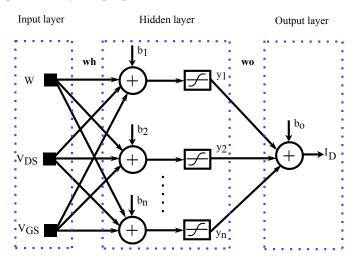

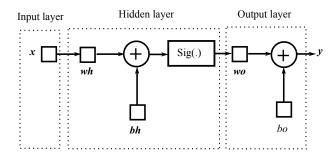

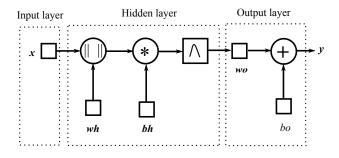

| 3.2  | ANN topology with a single hidden layer                                                                                                                                                                                                                      | 33 |

| 3.3  | MLP Network topology                                                                                                                                                                                                                                         | 35 |

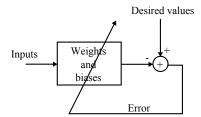

| 3.4  | Backpropagation pictorial representation                                                                                                                                                                                                                     | 35 |

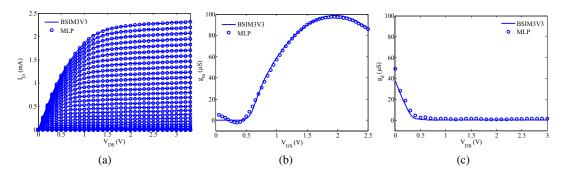

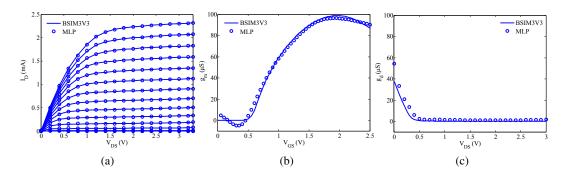

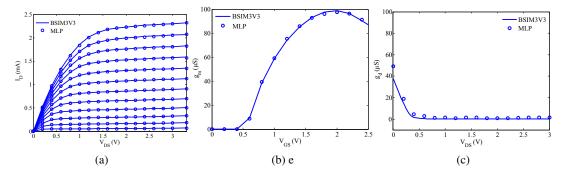

| 3.5  | MLP model results, when the network has 20 hidden layer neurons and trained                                                                                                                                                                                  |    |

|      | with <i>data-set2</i> (a) MOSFET output characteristics (b) Transconductance at V <sub>DS</sub> =1 V                                                                                                                                                         |    |

|      | (c) Output conductance at $V_{GS}=1$ V                                                                                                                                                                                                                       | 36 |

| 3.6  | MLP model results, when the network has 20 hidden layer neurons and trained                                                                                                                                                                                  |    |

|      | with <i>data-set3</i> (a) MOSFET output characteristics (b) Transconductance at $V_{DS}=1$ V                                                                                                                                                                 |    |

|      | (c) Output conductance at $V_{GS}$ =1 $V$                                                                                                                                                                                                                    | 37 |

| 3.7  | RBF/LS-SVM network topology                                                                                                                                                                                                                                  | 37 |

xiv LIST OF FIGURES

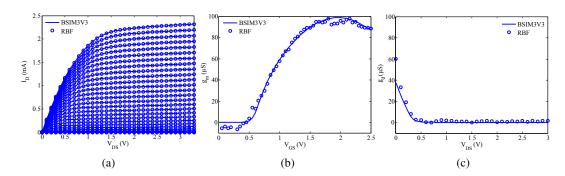

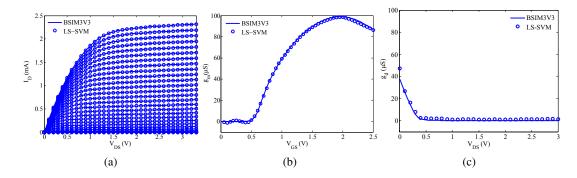

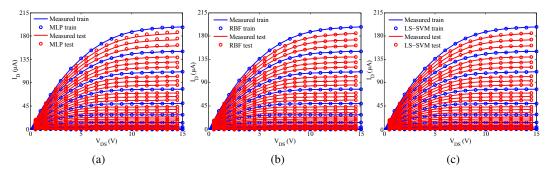

| 3.8  | with $data$ -set2 (a) MOSFET output characteristics (b) Transconductance at $V_{DS}$ 1 V (c) Output conductance at $V_{GS}$ 1 V                                                                                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

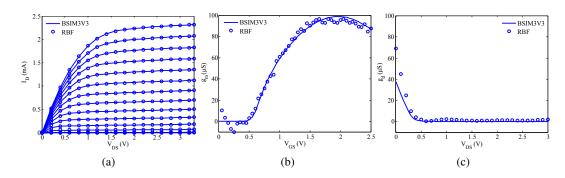

| 3.9  | RBF model results, when the network has 100 hidden layer neurons and trained with <i>data-set3</i> (a) MOSFET output characteristics (b) Transconductance at V <sub>DS</sub> 1 V (c) Output conductance at V <sub>GS</sub> 1 V                                                                                         |

| 3.10 | LS-SVM model results, when the network has 1054 support vectors and trained with $data$ -set2 (a) MOSFET output characteristics (b) Transconductance at $V_{DS}$ 1 V (c) Output conductance at $V_{GS}$ 1 V                                                                                                            |

| 3.11 | LS-SVM model results, when the network has 288 support vectors and trained with $data$ -set3 (a) MOSFET output characteristics (b) Transconductance at $V_{DS}$ 1 V (c) Output conductance at $V_{GS}$ 1 V                                                                                                             |

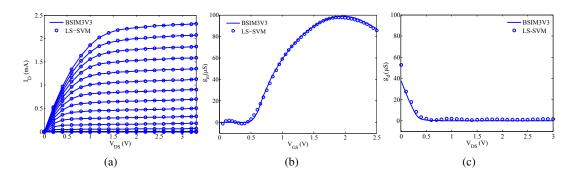

| 3.12 | MLP model response for the testing data, where the transistor $W=5\mu m,0.8 \le V_{GS} \le 3V$ and $0 \le V_{DS} \le 3.3V$ , in steps of 0.2 V and the number of hidden neurons is 50 (a) MOSFET output characteristics (b) Transconductance at $V_{DS}$ 1 V (c) output conductance at $V_{GS}$ 1 V                    |

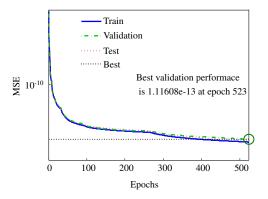

| 3.13 | ANN performance                                                                                                                                                                                                                                                                                                        |

| 3.14 | ANN post-training performance                                                                                                                                                                                                                                                                                          |

| 3.15 | TFT output characteristics, including training (blue - $0 \le V_{GS} \le 10  V$ and $0 \le V_{DS} \le 15  V$ , in steps of $1  V$ ) and testing data (red - $0.25 \le V_{GS} \le 9.75  V$ and $0.5 \le V_{DS} \le 14.5  V$ , in steps of $0.25  V$ and $1  V$ , respectively) from: (a) MLP (b) RBF (c) LS-SVM.        |

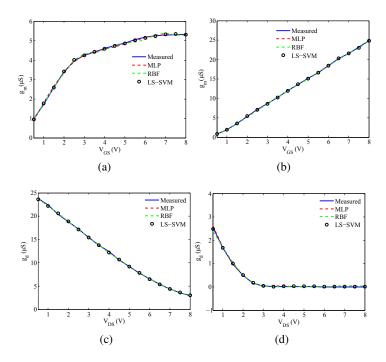

| 3.16 | Small signal parameters (a) $g_m$ : when $V_{DS} = 1.5 \text{ V}$ (b) $g_m$ : when $V_{DS} = 10 \text{ V}$ (c) $g_d$ : when $V_{GS} = 8 \text{ V}$ (d) $g_d$ : when $V_{GS} = 1.5 \text{ V}$                                                                                                                           |

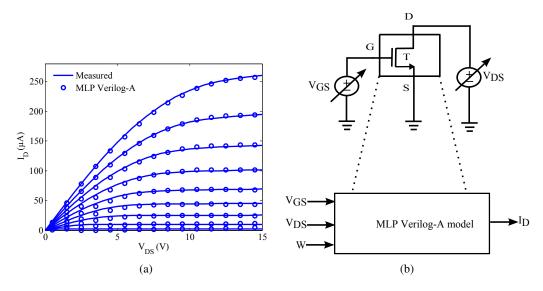

| 3.17 | Verilog-A ANN model (a) TFT output characteristics ( $2 \le V_{GS} \le 10 \text{ V}$ and $0.5 \le V_{DS} \le 14.5 \text{ V}$ , in steps of $1 \text{ V}$ ) (b) Test setup                                                                                                                                              |

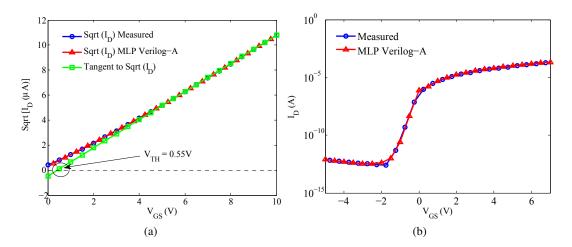

| 3.18 | (a) Threshold voltage ( $V_{TH}$ ) calculation from the measured and simulated data (using the Verilog-A model — example with the $80\mu m$ TFT) (b) Measured and modeled transfer characteristics of transistor whose width is $320\mu m$                                                                             |

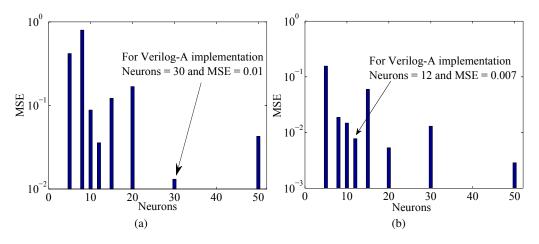

| 3.19 | ANN performance and complexity (number of neurons): (a) $C_{GD}$ (b) $C_{GS}$                                                                                                                                                                                                                                          |

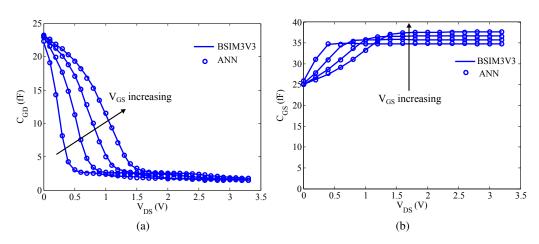

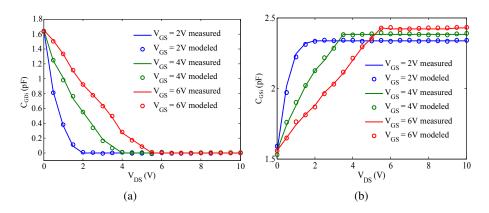

| 3.20 | MLP modeling results for the bias dependent capacitances : $0.05 \le V_{GS} \le 2.95 \text{ V}$ and $0 \le V_{DS} \le 3.3 \text{ V}$ , in steps of 0.1 V (a) $C_{GD}$ (b) $C_{GS}$                                                                                                                                     |

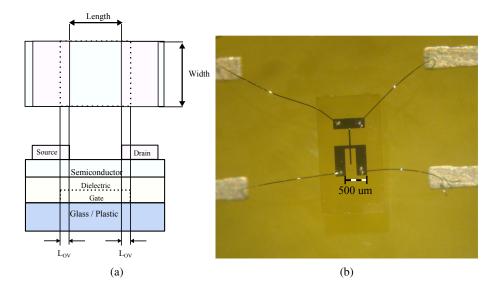

| 3.21 | (a) Schematic view of the a-GIZO TFT fabricated in this work. Channel length L = $20\mu\text{m}$ , and channel width W = $640\mu\text{m}$ . L <sub>OV</sub> represents source/drain overlaps to the gate ( $5\mu\text{m}$ for each side) - figure dimensions are not as per scale (b) Fabricated TFT with wire-bonding |

| 3.22 | Capacitor measurement setup (a) $C_{G-DS}$ (b) $C_{GD}$ (c) $C_{GS}$ + $C_{GD}$                                                                                                                                                                                                                                        |

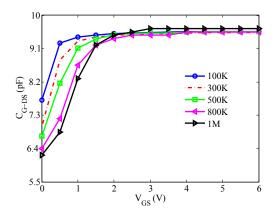

|      | Measured $C_{G\text{-}DS}$ at different frequencies for a gate voltage sweep from 0 to 6 V $$ .                                                                                                                                                                                                                        |

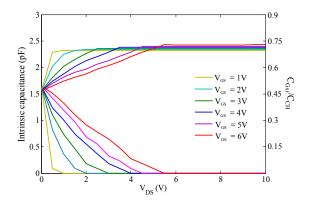

|      | $C_{GSi}$ and $C_{GDi}$ measurements validation with Meyers FET capacitance model $$ .                                                                                                                                                                                                                                 |

|      | Measured and modeled intrinsic capacitances (a) $C_{GDi}$ (b) $C_{GSi}$                                                                                                                                                                                                                                                |

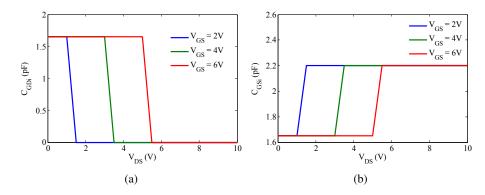

|      | Meyers approximation of the intrinsic capacitances (a) $C_{GDi}$ (b) $C_{GSi}$                                                                                                                                                                                                                                         |

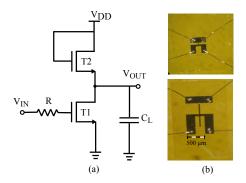

| 3.27 | (a) CS amplifier schematic with $W_{(T1)} = 640 \mu\text{m}$ and $W_{(T2)} = 40 \mu\text{m}$ (b) Micrographs of the TFTs that are used to form the CS amplifier                                                                                                                                                        |

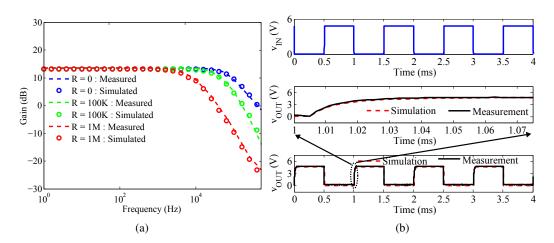

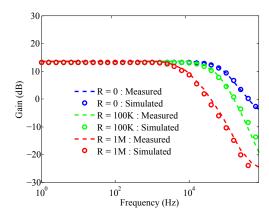

| 3.28 | CS amplifier response with 4pF load: (a) Frequency response with different values of R (b) transient response for 1 KHz input signal frequency - transition part is zoomed to show the model accuracy in predicting parameters that are responsible for the dynamic behavior                                           |

|      |                                                                                                                                                                                                                                                                                                                        |

LIST OF FIGURES xv

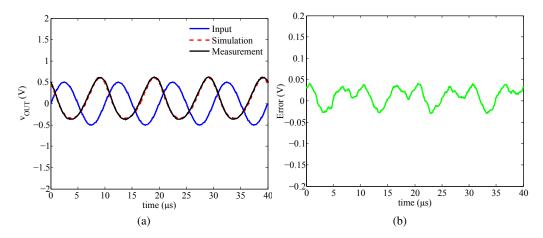

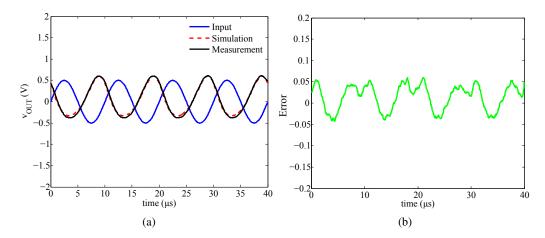

| 3.30       | cs amplifier response form the proposed model and measurements, when the input signal frequency is 100 KHz (a) Output (b) Difference between the measured and simulated response                                                      | 55<br>55 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            |                                                                                                                                                                                                                                       |          |

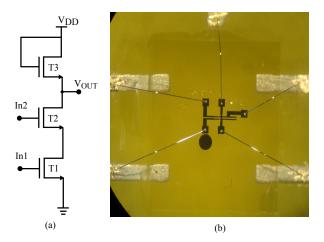

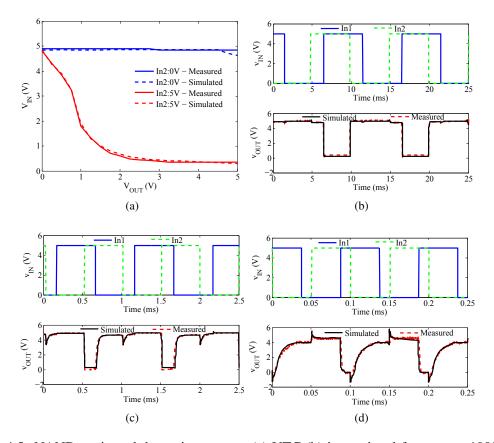

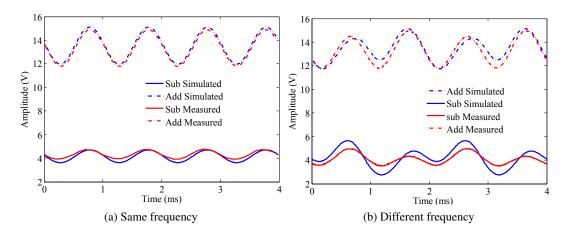

| 4.1<br>4.2 | Fabricated circuits on glass substrate                                                                                                                                                                                                | 59       |

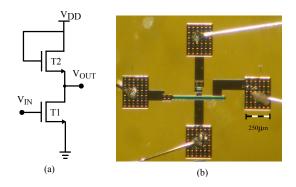

| 4.3        | T2 dimensions - W = $40 \mu$ m and L = $20 \mu$ m                                                                                                                                                                                     | 59       |

| 4.4        | frequency: $10  \text{kHz}$                                                                                                                                                                                                           | 60       |

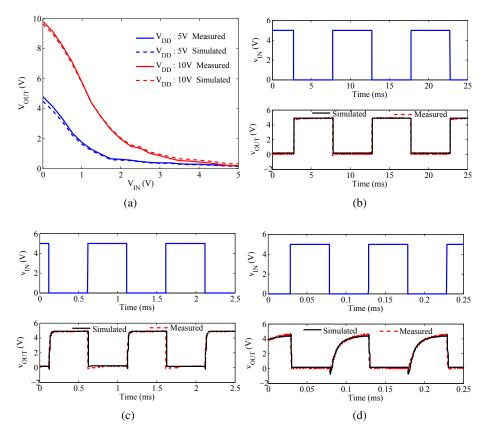

| 4.5        | dimensions - W = $40 \mu$ m and L = $20 \mu$ m                                                                                                                                                                                        | 61       |

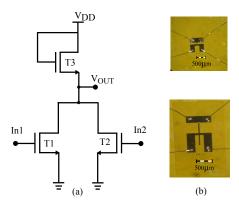

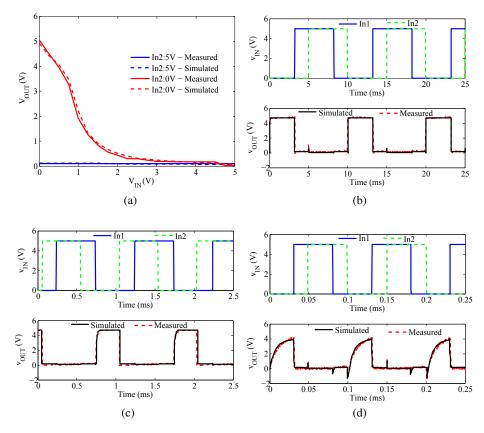

| 4.6        | (c) input signal frequency: 1 kHz (d) input signal frequency: 10 kHz Two input NOR gate (a) Schematic (b) Micrograph of the isolated TFTs: dimensions - W = $40 \mu$ m and L = $20 \mu$ m and T3 dimensions - W = $480 \mu$ m and L = | 61       |

|            | $20 \mu\text{m}$                                                                                                                                                                                                                      | 62       |

| 4.7        | NOR static and dynamic response (a) VTC (b) input signal frequency: 100 Hz (c)                                                                                                                                                        | Ü_       |

|            | input signal frequency:1kHz (d) input signal frequency:10kHz                                                                                                                                                                          | 62       |

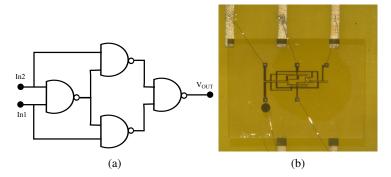

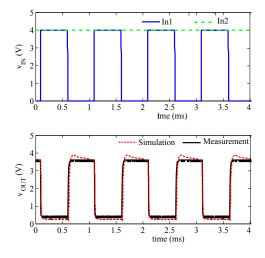

| 4.8        | Two-input XOR (a) Schematic in terms of two-input NAND gate (b) Fabricated circuit with wire-bonding.                                                                                                                                 | 63       |

| 4.9        | Two-input XOR response from simulations and measurements                                                                                                                                                                              | 63       |

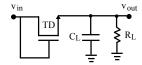

| 4.10       | Half-wave rectifier or a peak detector.                                                                                                                                                                                               | 64       |

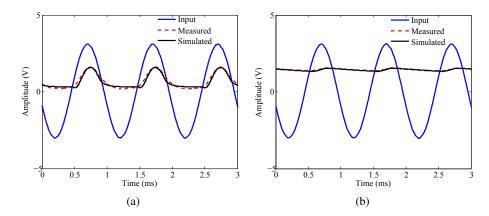

| 4.11       | (a) Half-wave rectifier response (b) Peak detector response                                                                                                                                                                           | 65       |

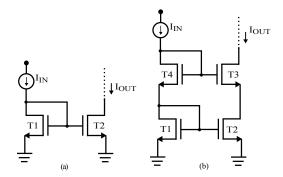

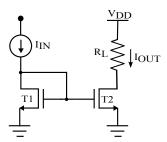

|            | Current mirrors schematics (a) Using Two-TFTs (b) Cascode                                                                                                                                                                             | 65       |

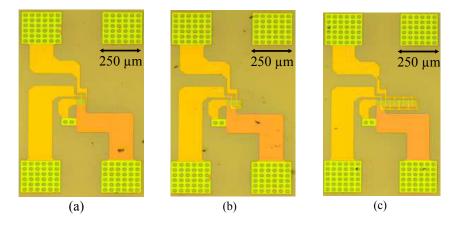

|            | Micrographs of transparent two-TFT current mirrors based on a-GIZO TFTs with                                                                                                                                                          |          |

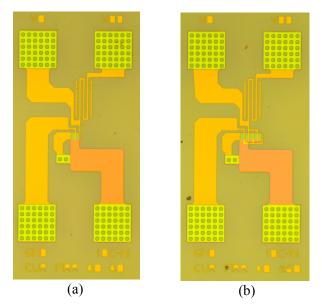

|            | different widths for the output transistor (T2) in $\mu$ m : (a) 40 (b) 80 (c) 320                                                                                                                                                    | 65       |

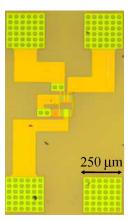

| 4.14       | Micrograph of the transparent cascode current mirror based on a-GIZO TFTs with $W/L = 40/20 \mu m$                                                                                                                                    | 66       |

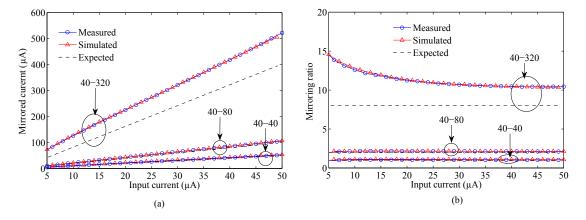

| 1 15       | Two-TFT current mirror response: expected, from neural model simulation and                                                                                                                                                           | UU       |

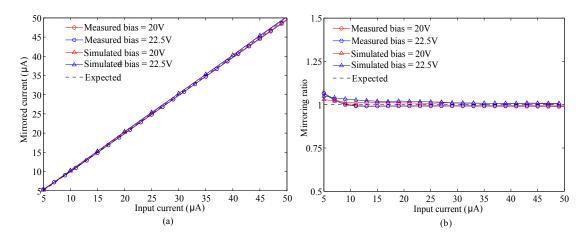

| 7.13       | measured response with fabricated circuits (a) Mirrored current (b) Mirroring ratio.                                                                                                                                                  | 66       |

| 4.16       | Cascode current mirror response at different bias voltages: expected, from neu-                                                                                                                                                       | 00       |

|            | ral model simulation and measured response with fabricated circuit (a) Mirrored                                                                                                                                                       |          |

|            | current (b) Mirroring ratio                                                                                                                                                                                                           | 67       |

|            | Schematic of current mirror with two TFTs and a passive load                                                                                                                                                                          | 67       |

|            | Fabricated current mirrors with two TFTs with (a) $W_2 = 40 \mu m$ (b) $W_2 = 160 \mu m$                                                                                                                                              | 68       |

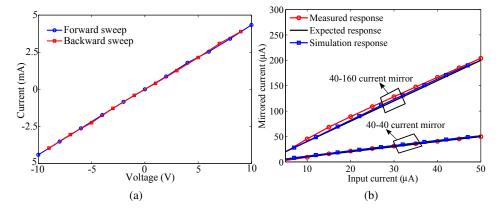

| 4.19       | (a) IZO based resistor characterization (b) Two-TFT current mirrors response with                                                                                                                                                     |          |

|            | different mirroring ratios: from circuit simulations, measured and expected behavior.                                                                                                                                                 | 68       |

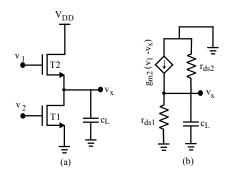

|            | CD amplifier (a) Schematic (b) Small signal equivalent                                                                                                                                                                                | 69       |

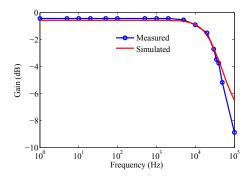

|            | CD amplifier simulation and measured circuit response                                                                                                                                                                                 | 69       |

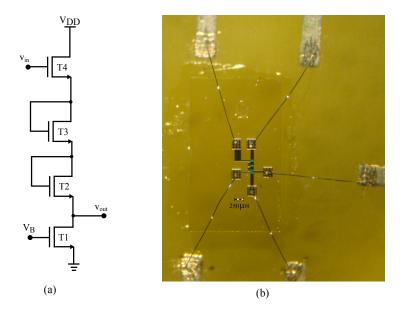

|            | Level shifter (a) schematic (b) Fabricated circuit with wire-bonding                                                                                                                                                                  | 70       |

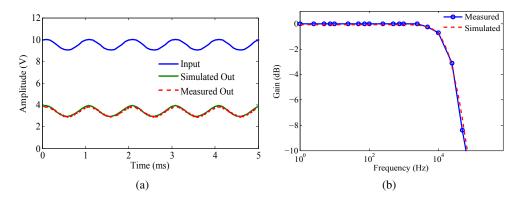

| 4.23       | Level shifter response from simulations and measurements (a) Transient response                                                                                                                                                       | 70       |

|            | (b) Frequency response                                                                                                                                                                                                                | 70       |

xvi LIST OF FIGURES

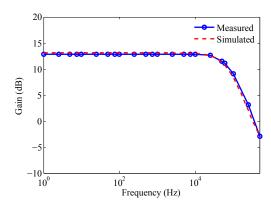

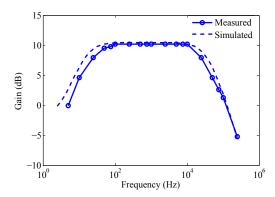

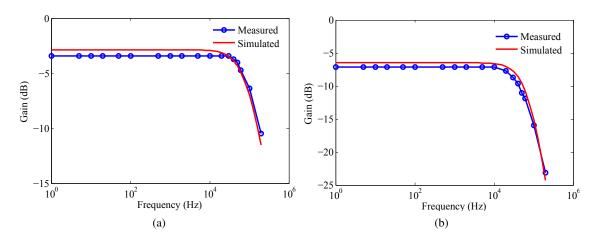

| Frequency response of the amplifier (Fig. 4.2b) with 4pf capacitive load                                    |

|-------------------------------------------------------------------------------------------------------------|

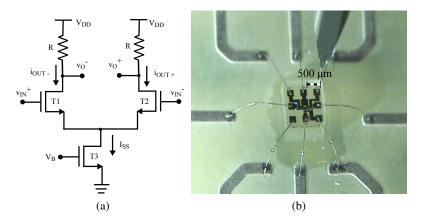

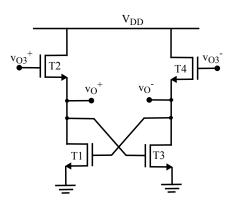

| Differential Amplifier (a) Schematic (b) Micrograph with wire-bonding 7                                     |

| Differential amplifier characterization from simulations and measurements (a) Lin-                          |

| earity response (b) Frequency response                                                                      |

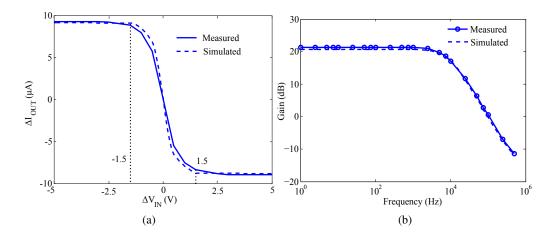

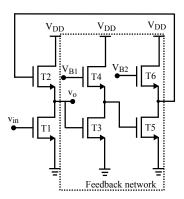

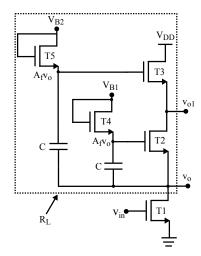

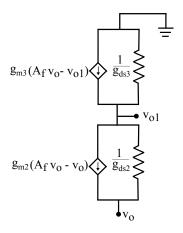

| High gain amplifier employing positive feedback only with n-type enhancement                                |

| transistors (a) Topology (b) Amplifier with capacitive bootstrapping (c) Positive                           |

| feedback path with C and T3                                                                                 |

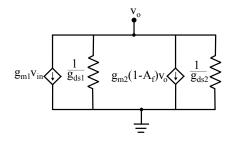

| High gain amplifier small signal equivalent                                                                 |

| Amplifier topologies for high gain: Two stage inverting buffers (Amp2) [5] 7                                |

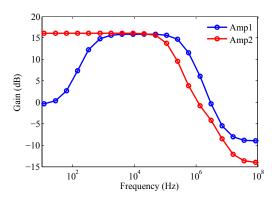

| Amp1 and Amp2 frequency response from simulations                                                           |

| Impact of C value and T3 dimensions on Amp1 gain, from simulations using TFT                                |

| models (a) W = $40 \mu\text{m}$ and L = $20 \mu\text{m}$ (b) W = $160 \mu\text{m}$ and L = $20 \mu\text{m}$ |

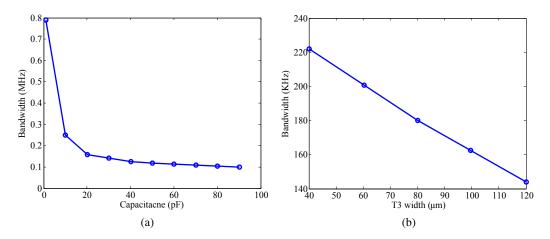

| Impact of C value and T3 dimensions on Amp1 bandwidth, from simulations using                               |

| TFT models (a) T3 dimensions : $W = 40 \mu m$ and $L = 20 \mu m$ (b) $C = 40 pF$ and T3:                    |

| $L = 20 \mu\text{m}. \qquad 7$                                                                              |

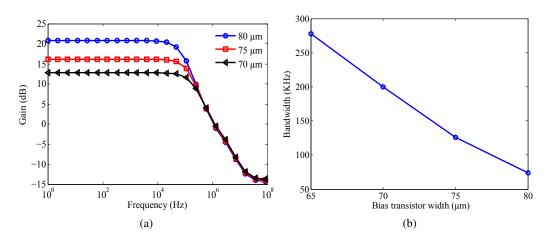

| Impact T3 and T5 dimensions (width) on Amp2 gain and bandwidth, from simu-                                  |

| lations using TFT models (a) Gain variation (b) Bandwidth variation                                         |

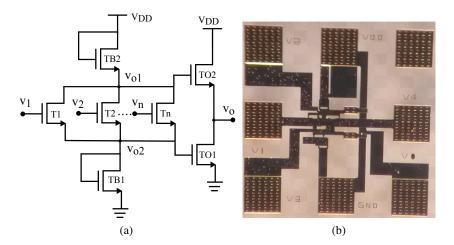

| Proposed high gain amplifier (Amp3) only with n-type enhancement transistors . 7                            |

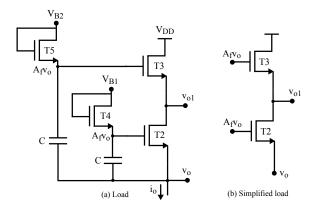

| Active load                                                                                                 |

| Small signal equivalent of R <sub>L</sub> in Amp2                                                           |

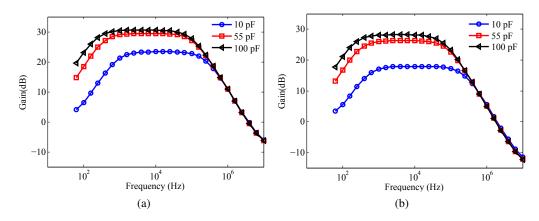

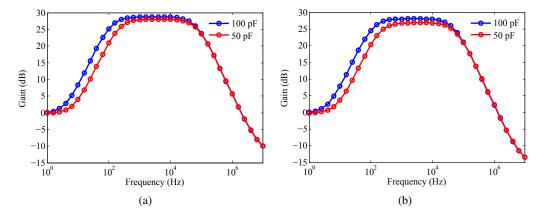

| Impact of C and bias transistors (T4 and T5) widths on the gain and bandwidth of                            |

| Amp3. Simulation results using TFT models (a) $W = 40 \mu m$ (b) $W = 80 \mu m$ 7                           |

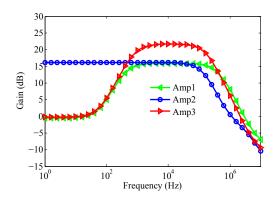

| Amplifiers (Amp1 to Amp3) gain comparison from simulations                                                  |

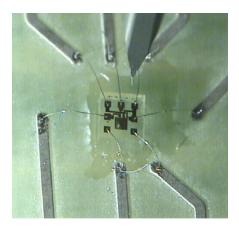

| Amp1 fabricated circuits after dicing and wire-bonding                                                      |

| Amp1 simulation response validation using measured outcome                                                  |

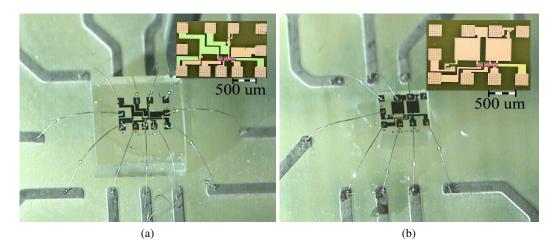

| Amp3 fabricated circuits after dicing and wire-bonding; corresponding micro-                                |

| graphs of the circuits are shown in the inset (a) External capacitance (b) On-chip                          |

|                                                                                                             |

| capacitance                                                                                                 |

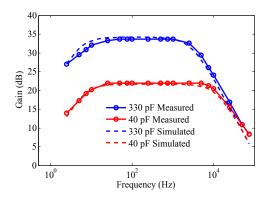

| Amp3 frequency response                                                                                     |

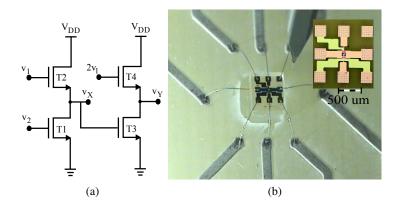

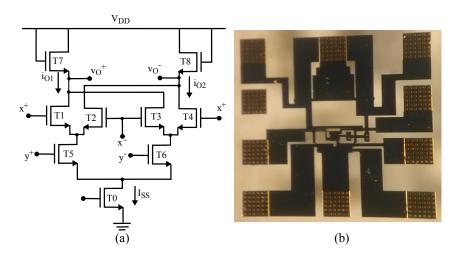

| Adder subtractor circuit (a) Schematic (b) Fabricated circuit after dicing and wire-                        |

| bonding; micrograph of the circuit is shown in the inset                                                    |

| Adder subtractor functional verification from simulation and measured circuit re-                           |

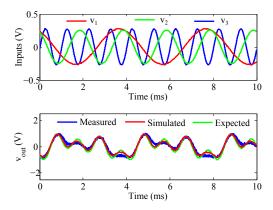

| sponse                                                                                                      |

| Frequency response (a) $v_x$ (b) $v_y$                                                                      |

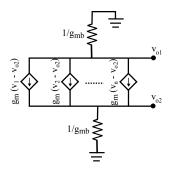

| Novel adder (a) Schematic (b) Micrograph of the fabricated circuit                                          |

| Small signal equivalent formed by the transistors T1 to T5                                                  |

| Novel adder characterization from simulated, measured and expected response 8                               |

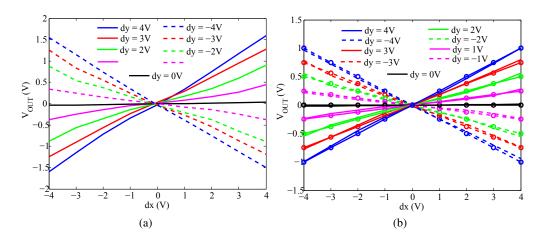

| Gilbert cell with a-GIZO TFTs (Mul1) using a diode connected load (a) schematic                             |

| (b) micrograph of the fabricated circuit                                                                    |

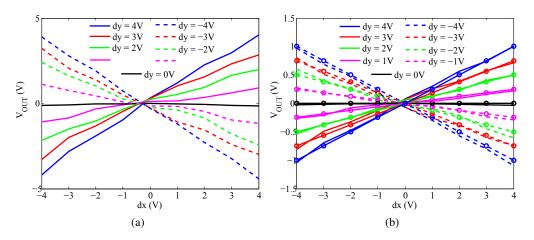

| Mul1 measured linearity response (a) Actual value (b) Validation with the ex-                               |

| pected value in normalized form - line with circle represents the expected value 8                          |

| High gain multiplier (a) Schematic (b) Micrograph of the fabricated circuit 8                               |

| Mul2 measured linearity response (a) Actual value (b) Validation with the ex-                               |

| pected value in normalized form - line with circle represents the expected value 8                          |

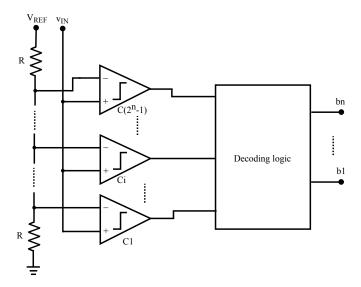

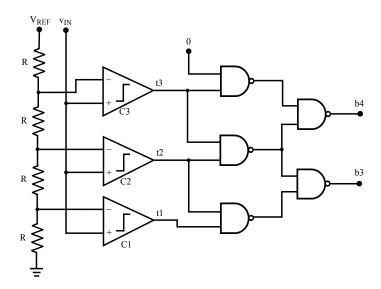

| n-bit flash type ADC                                                                                        |

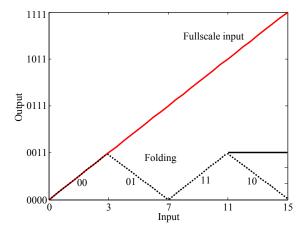

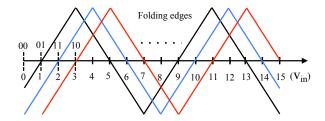

| Folding operation                                                                                           |

| 4-bit folding type ADC                                                                                      |

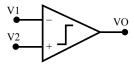

| Comparator symbol                                                                                           |

|                                                                                                             |

| LIST OF FIGURES | xvii |

|-----------------|------|

|                 |      |

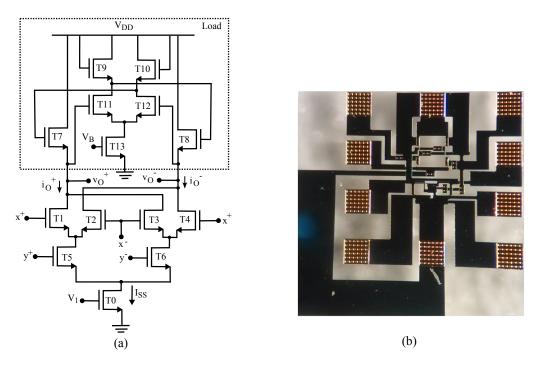

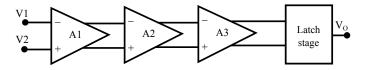

| 5.5  | Comparator block diagram                                                     |

|------|------------------------------------------------------------------------------|

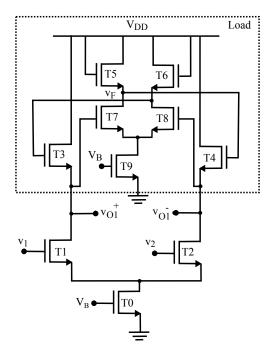

| 5.6  | Amplifier stage in the comparator                                            |

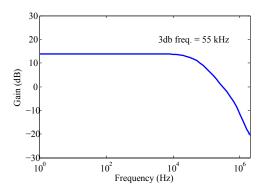

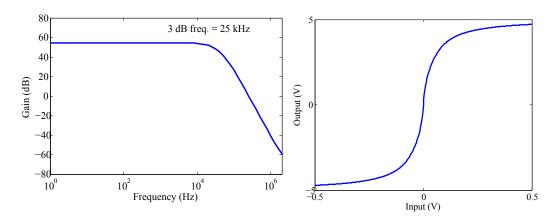

| 5.7  | Amplifier frequency response                                                 |

| 5.8  | Latch schematic                                                              |

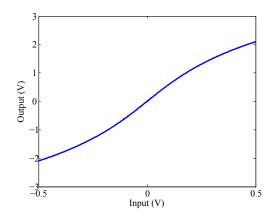

| 5.9  | Latch dc voltage transfer characteristics                                    |

| 5.10 | Comparator frequency response                                                |

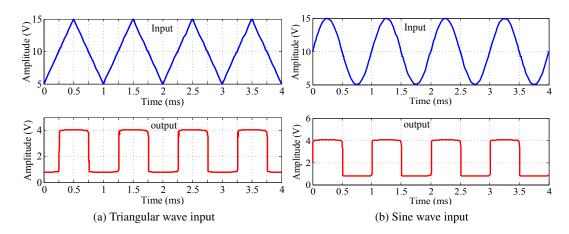

| 5.11 | Comparator transient response, for 1 KHz input signals                       |

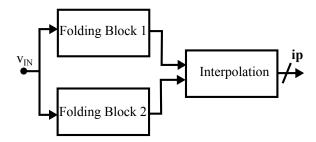

| 5.12 | Analog processing block diagram                                              |

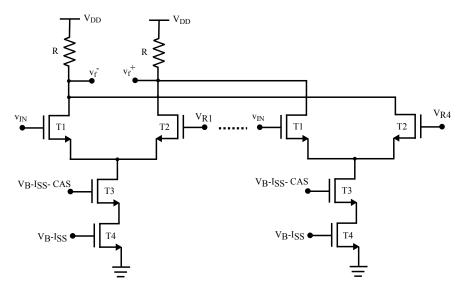

| 5.13 | Folding block                                                                |

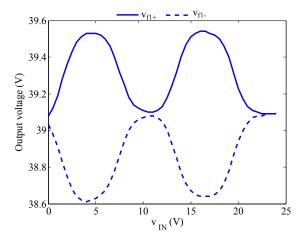

| 5.14 | Folding block response                                                       |

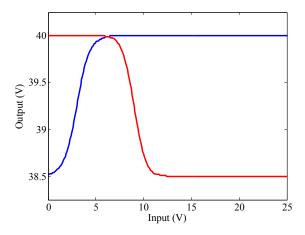

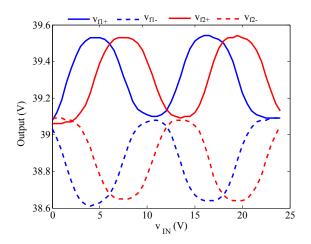

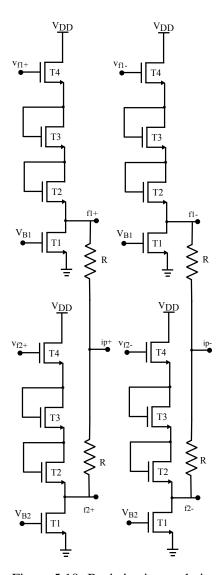

| 5.15 | Characteristics of two isolated differential pairs for folding generation 99 |

| 5.16 | 2-bit flash converter for gray code                                          |

| 5.17 | Folding signal showing different quantization levels (in gray code) 101      |

| 5.18 | Folding blocks response                                                      |

| 5.19 | Resistive interpolation                                                      |

| 5.20 | Folding characteristic with resistive interpolation                          |

| 5.21 | Comparison of ADC simulation response with the expected behavior 103         |

| 5.22 | ADC performance from simulation                                              |

|      |                                                                              |

# **List of Tables**

| 2.1  | Comparison of the main TFT technologies with CMOS                    |

|------|----------------------------------------------------------------------|

| 3.1  | MLP results for single MOSFET                                        |

| 3.2  | RBF results for MOSFET                                               |

| 3.3  | LS-SVM results for MOSFET                                            |

| 3.4  | MLP results for multiple MOSFETs                                     |

| 3.5  | MLP results                                                          |

| 3.6  | RBF results                                                          |

| 3.7  | SVM results                                                          |

| 3.8  | MARE of small signal parameters from all the ANN modeling methods 45 |

| 3.9  | Number of neurons in the ANNs hidden layer                           |

| 3.10 | MLP results for the bias dependent intrinsic capacitances            |

| 3.11 | Dominant pole location from simulation and measurement               |

| 3.12 | THD from simulation and measurement                                  |

| 4.1  | Mirroring Ratios                                                     |

| 4.2  | CS amplifiers performance                                            |

| 4.3  | Circuit components information                                       |

| 4.4  | Amp1 and Amp3 performance comparison                                 |

| 4.5  | Mul1 and Mul2 comparison                                             |

| 4.6  | Summary of characterized circuits and comparison with literature 89  |

| 5.1  | Comparison of ADCs                                                   |

| 5.2  | Comparators with different TFT technologies                          |

| 5.3  | ADC with different TFT technologies                                  |

# Abbreviations, Acronyms and Symbols

$\Delta\Sigma$  Delta sigma

$\sigma$  Gaussian function spread

AC Alternating current

ADC Analog-to-digital converter

AOS Amorphous oxide semiconductor

ANN Artificial neural network

a-GIZO Amorphous gallium-indium-zinc-oxide

a-Si:H Hydrogenated amorphous silicon

BP Back propagation

CAD Computer-aided design

CMOS Complementary metal-oxide-semiconductor

CMRR Common-mode rejection ratio

CS Common source

DAC Digital-to-analog converter

DC Direct current

DRC Design rule check

FPD Flat-panel display

FPGA Filed programmable gate array

IC Integrated circuit IZO Indium zinc oxide

LPCVD Low temperature chemical vapor deposition

LS-SVM Least square support vector machine

LSB Least significant bit

LTPS Low temperature poly silicon

LVS Layout versus schematic

MLP Multi layer perceptron

MSB Mostt significant bit

Mo Molybdenum Ti-Au Titanium gold

MOSFET Metaloxidesemiconductor field-effect transistor

MSE Mean square error

NMOS N-type metal-oxide-semiconductor

OTFT Organic thin-film transistor Opamp Operational amplifier PP Piece-wise polynomial

PV photo voltaic

RBF Radial basis function

xxii Symbols

RFID Radio frequency identification RPI Rensselear polytechnic institute SAR Successive approximation register

SIC MESFET Silicon carbide metal semiconductor field effect transistor SPICE Simulation program with integrated circuit Emphasis

TCO Transparent conductive oxide

TFT Thin-film transistor

ZnO Zinc-oxide

dB decibel

g<sub>ds</sub> Output transconductance

g<sub>m</sub> transconductance

Hz Hertz

r<sub>ds</sub> Intrinsic output resistance of a transistor

$\mu$  Charge carrier mobility

V<sub>TH</sub> threshold voltage

$\mu_n$  Charge carrier mobility in n-type semiconductor

mW milli Watt

$\varepsilon_{r}$  Relative dielectric constant

# **Chapter 1**

# Introduction

Although the first thin-film transistors (TFTs) and metal oxide semiconductor field-effect transistors (MOSFETs) were both conceived during the 1960s, TFT mass production only happened during the 1980-90s, motivated by their application in active matrix liquid crystal displays (AML-CDs) [6]. Low temperature poly-crystalline silicon (LTPS) [7], amorphous hydrogenated silicon (a-Si:H) [8], organic (O) [9] and amorphous oxide semiconductor based (AOS) TFTs [10] are some of the most reported TFT technologies. Even though TFTs are mainly used for displays [7, 8, 11, 12], their application scope is rapidly expanding to the fields of radio-frequency identification (RFID) tags [2], sensing devices [13, 14, 15], X-ray image sensors [3, 4], transparent, large flexible antenna arrays, medicine and low-cost disposable electronics [16].

Amorphous gallium-indium-zinc-oxide (a-GIZO) is an example of a multi-component AOS material. Its usage in active devices is relatively new, but has already gained significant attention from both academia and industry. Competing TFT technologies such as LTPS TFTs provide high-speed electronics due to their high field-effect mobility ( $\mu$ ), which is exceeding 100 cm<sup>2</sup>/V·s, but their poly-crystalline nature hinders uniformity in large area electronics. On the other hand, a-Si:H TFTs and OTFTs are suitable for large area fabrication but the range of applications is limited by the low  $\mu$ , typically below 1 cm<sup>2</sup>/V·s. a-GIZO TFTs provide a combination of the good properties of these technologies, exhibiting high  $\mu$  (10-50 cm<sup>2</sup>/V·s), reliability, uniformity, lowtemperature and low-cost fabrication - allowing for flexible electronics - and transparency in the visible spectrum. In fact, fully transparent TFTs can be realized with a-GIZO when accompanied by transparent conductive oxides (TCOs) [17, 18, 19] for source/drain electrodes, such as indiumzinc oxide (IZO) [20]. Even though, thin-film technologies should not be seen as an alternative to the conventional complementary metal oxide semiconductor (CMOS) technologies, a-GIZO TFT based circuits can find niche applications in some specific areas where CMOS is not able to meet the requirements. For example, cost-effective analog/mixed-signal circuits for signal conditioning could in principle be directly printed on the photovoltaic (PV) panels, by using a-GIZO TFTs with TCO electrodes. Transparent displays with transparent driving circuits can also be realized with this technology. Unique properties of TCOs [21], such as, good optical transparency and low-temperature fabrication makes the above applications realizable. In addition, by integrating 2 Introduction

sensors with the signal conditioning circuits in the same technology results in low-cost and reliable integrated systems that can avoid complex interfacing connections. The above potential applications and good device characteristics strongly incentivize the design of analog/mixed-signal circuits with a-GIZO TFTs, which serves as a token of motivation for the work presented along this dissertation.

Current mirrors, high-gain amplifiers, buffers, logic gates, comparator, adders, subtractor and multipliers are some of the essential building blocks needed in the design of analog/mixed signal circuits. Several of these circuits have already been reported with a-Si:H TFTs and OTFTs, namely basic analog blocks [22, 23, 5], a high-gain operational amplifier [24], comparator [25] and data converters [26, 27, 28]. On the other hand very few are presented with a-GIZO TFTs [29, 30].

#### 1.1 Main objectives

Although a-GIZO TFT technology is very appealing, it still has many shortcomings that results in a number of challenges. Lack of stable complementary (p-type) transistors, bias stress and inferior mobility, compared to the crystalline silicon, are some of the main limiting factors for circuit design. Being a-GIZO TFT an emerging technology, device models or technology libraries that support standard IC design are also not available. In this context, the main objective of the dissertation is to develop a platform in which a-GIZO TFT based circuits can be designed in the same way as any other standard semiconductor integrated circuits and develop and characterize traditional and novel circuits that can be employed in generic electronic design. This goal is accomplished by the following four phases:

1. Model Development: As the semiconductor material (GIZO) is amorphous, the MOSFET models cannot be adopted, since they use crystalline silicon as semiconductor. In addition, MOSFETs operate in inversion modes and strongly depend on the properties of the several p-n junctions existing in the device, contrarily to TFTs, where the device operation relies on accumulation mode and metal-semiconductor junctions. On the other hand, Rensselear polytechnic institute (RPI) model, which is widely used to characterize a-Si:H TFT, is also insufficient to predict unique properties of AOS (a-GIZO) TFT behavior accurately [31, 32]. In literature, very few articles report physical-based modeling for basic characterization of the a-GIZO TFT i.e., static and dynamic behavior and even these models are not optimized for circuit simulators. Consequently, they take a good amount of simulation time when complex circuits are involved. Many groups are working to ensure better behavior of a-GIZO TFTs either by employing new materials (for source/drain, dielectric) [18, 33, 34], different structures for the devices (bottom gate, top gate, multi-channel, dual gate) [35, 36] and alternative fabrication techniques [37]. Whenever there is a change in the material or process, certainly there will be an impact on the carrier flow. Thus, the corresponding device physics needs to be studied further, in order to contemplate the model with the new characteristics. Therefore, for the new technologies, when a quick circuit design is important, physical modeling is not an ideal choice, even though it is required for process optimization. Subse-

3

quently, in this dissertation, artificial neural networks (ANNs) have been employed as they are universal approximators, simple, accurate and continuous (model and its derivatives). In addition, their memory requirements are lower compared to the table-based modeling. Different ANN techniques, such as, multi-layer perceptron (MLP), radial basis functions (RBF) and least square support vector machine (LS-SVM) are experimented and compared in order to characterize the static behavior of the device. These models are developed from the measured characteristics of the device. Among the above mentioned ANN methods, MLP shows a reasonable accuracy level, with minimum complexity. Consequently, MLP network has been further implemented in Verilog-A for circuit simulation. The incorporation of dynamics in the model follows an equivalent-circuit approach, in which the electrical equivalent-circuit, using lumped elements, is firstly devised. Then all the individual elements are modeled by means of ANNs. Later, all the ANN networks are joined as per the equivalent circuit of the device. Finally the model outcome is validated with the measured circuit response. The developed model is able to simulate complex circuits with more than 600 transistors along with few tens of passive elements (resistors and capacitors). Further, characterization of passive devices, namely resistors and capacitors was also carried out. Nonetheless, the interconnect parasitic capacitance to substrate is irrelevant since the substrate is in fact an insulator (glass or plastic).

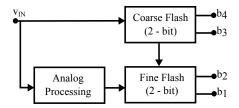

2. Circuit design and simulation: Due to unavailability of stable, and reproducible, p-type TFTs, the circuit design must be confined to only n-type enhancement TFTs. In fact, for the case of high-gain amplifiers, depletion TFT loads would make the design simpler and straight forward. However, fabrication of enhancement and depletion TFT types, on the same chip, demands at least one more mask than with a single type TFT. Thus, by overcoming the design challenges with enhancement TFTs, low-cost circuits can be accomplished. Circuit design was started with fundamental blocks, namely, various types of current mirrors, source follower (buffer), single stage common-source amplifier, differential amplifiers, and amplifiers with various kinds of loads (passive, diode connected transistors and bootstrapping). A single TFT application in a half-wave rectifier and peak detector is also reported. Along with the above, basic signal processing circuits, such as, adder, subtractor, multipliers and individual elements were also fabricated on a single chip. Later, a high-gain comparator was developed. Finally a four-bit folding analog to digital converter (ADC) with resistive interpolation was developed, taking into account the limitations and constraints of the technology. This ADC uses two-bit fine and coarse flash converters, folding blocks and source followers. Such topology tends to be less complex, with conversion speeds close to the flash type converter, which is important given the limited bandwidth, natural for devices with low mobility. The digital decoding logic in the ADC is also completely implemented with n-type enhancement a-GIZO TFTs. This is the first ADC with a-GIZO TFT technology. All the above mentioned circuits simulation were carried out with the MLP Verilog-A model.

4 Introduction

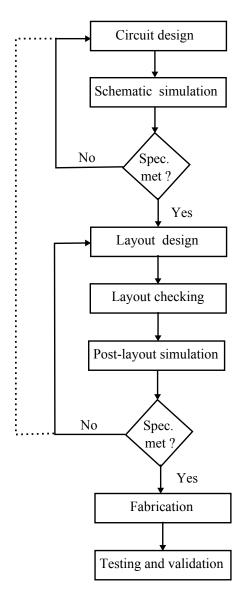

3. **Library development:** An embodiment framework is needed to facilitate IC design. Technology files should be developed to enable the use of IC-CAD software tools for a flexible and accurate layout design, with design verification. Development of device libraries for layout drawing, design rule check (DRC), and layout versus schematic (LVS) in cadence tools is carried out within a team work. The use of technology libraries mainly comes into picture for complex error-free circuit design.

4. Circuit fabrication and validation: Finally, circuit simulation outcomes are validated with fabricated circuit response to verify the ability of the device models to predict its real behaviour. The measured or simulated circuit response also demonstrates that a-GIZO TFTs are possible candidates for complex circuit design and also validates the proposed circuits. For complex circuits, chips have been diced in order to obtain individual blocks that were wire-bonded to PCBs for testing.

#### 1.2 Contribution

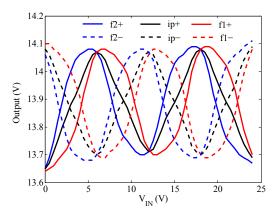

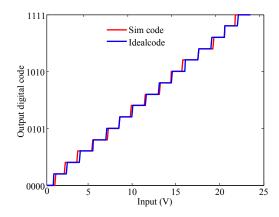

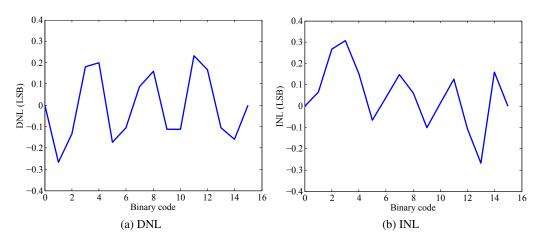

This work proposes and validates an accurate compact behavioral model for a-GIZO TFTs based on equivalent circuit approach using neural networks. By using this model, various analog and mixed signal building blocks such as current mirrors, traditional and novel amplifiers, adders, subtractor, multipliers, logic gates, comparator and ADC were designed, simulated and characterized. The proposed single-stage amplifier has accomplished the highest gain (> 34dB), up to the date, with a-GIZO TFT technology. From simulations, a comparator is promising a gain of 55dB and bandwidth more than 25kHz, while the folding ADC presents -0.26LSB DNL, 0.31LSB INL and 24mW power consumption. To the authors knowledge, these are the first comparator and ADC also done in a-GIZO technology.

#### 1.3 publications

#### 1.3.1 Journals

- 1. P. Bahubalindruni, V. Tavares, P. Barquinha, C. Duarte, P. de Oliveira, R. Martins, and E. Fortunato, "Transparent Current Mirrors With a-GIZO TFTs: Neural Modeling, Simulation and Fabrication," IEEE J. Display Tech., vol. 9, pp. 1001-1006, 2013.

- 2. P. Bahubalindruni, V. Tavares, P. Barquinha, C. Duarte, N. Cardoso, P. de Oliveira, R. Martins, and E. Fortunato, "a-GIZO TFT Neural Modeling, Circuit Simulation and Validation" (accepted J. of Solid State Electronics).

- 3. P. Bahubalindruni, B. Silva, V. Tavares, P. Barquinha, N. Cardoso, P. de Oliveira, R. Martins, and E. Fortunato, "Analog circuits using a-GIZO TFTs" (Revision submitted to IEEE J. Display Tech).

1.3 publications 5

4. P. Bahubalindruni, V. Tavares, P. Barquinha, N. Cardoso, J. Borme, P. de Oliveira, R. Martins, and E. Fortunato, A Compact model for Amorphous Gallium Indium Zinc Oxide Thin-Film-Transistor Using Artificial Neural Networks" (Submitted to Electron Device Letters)

#### **1.3.2** International Conferences

- P. Bahubalindruni, V. Tavares, P. Barquinha, J. Borme, N. Cardoso, R. Martins, E. Fortunato,

P. Oliveira, "IGZO TFT Based Circuits: Logic Gates, Peak Detector and Switch," ISCAS 2015 (submitted).

- 2. P. Bahubalindruni, V. Tavares, P. Barquinha, J. Borme, N. Cardoso, R. Martins, E. Fortunato, P. Oliveira, "Fundamental Analog Circuits on Glass with a-IGZO TFTs," ISCAS 2015 (submitted).

- 3. P. Bahubalindruni, V. Tavares, C. Duarte, N. Cardoso, P. Oliveira, P. Barquinha, R. Martins, and E. Fortunato, "Transparent Current Mirrors Using a-GIZO TFTs: Simulation with RBF Models and Fabrication". In Proceedings of the UKSim. pp. 582-586, 2014.

- 4. P. Bahubalindruni, B. Silva, V. Tavares, P. Barquinha, N. Cardoso, P. Oliveira, R. Martins, E. Fortunato, "Basic Analog Circuits Using a-GIZO TFTs: Simulation Using Neural Models and Validation," ITC 2014 (Poster).

- 5. Bahubalindruni, P.; Grade Tavares, V.; Barquinha, P.; Martins, R.; Fortunato, E., "High-gain topologies for transparent electronics," EUROCON, pp.2041-2046, 1-4 July 2013

- 6. Bahubalindruni, P.; Grade Tavares, V.; Guedes de Oliveira, P.; Barquinha, P.; Martins, R.; Fortunato, E., "High-gain amplifier with n-type transistors," International Conference of Electron Devices and Solid-State Circuits (EDSSC), pp.1-2, 3-5 June 2013

- 7. Bahubalindruni, G.; Duarte, C.; Tavares, V.G.; Barquinha, P.; Martins, R.; Fortunato, E.; de Oliveira, P.G., "Multipliers with transparent a-GIZO TFTs using a neural model," Telecommunications Forum (TELFOR), 2012 20th, pp.955-958, 20-22 Nov. 2012

- 8. Bahubalindruni, G.; Tavares, V.G.; Barquinha, P.; Duarte, C.; Martins, R.; Fortunato, E.; de Oliveira, P.G., "Basic analog circuits with a-GIZO thin-film transistors: Modeling and simulation," International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2012, pp.261-264, 19-21 Sept. 2012

#### 1.3.3 Other Publications

1. P. Bahubalindruni, V. Tavares, P. Barquinha, P. Oliveira, R. Martins, E. Fortunato, "Analog/Mixed Signal Circuits using a-GIZO TFTs" DATE PhD forum, 2014.

6 Introduction

Bruno Silva, Pydi Ganga Bahubalindruni, Vitor Grade Tavares, Pedro Barquinha, Rodrigo Martins, Elvira Fortunato, and Pedro Guedes de Oliveira, A Study of High-Gain Amplifiers for TTFTs in 2nd PhD Student Conference in Electrical and Computer Engineering (StudECE'2013), pp.1-2, 2013

Ganga Bahubalindruni, Vtor Grade Tavares, Pedro Barquinha, Cndido Duarte, Rodrigo Martins, Elvira Fortunato, Pedro Guedes de Oliveira, Circuits for Analog Signal Conditioning with a-GIZO Transparent TFTs in 1st PhD Student Conference in Electrical and Computer Engineering (StudECE'2012), pp.36-37, 2012

#### 1.4 Document outline

The remaining of the dissertation is organized as follows.

- Chapter. 2: Introduces a-GIZO TFT technology and characterization, main advantages and challenges imposed for circuit design, fabrication information, device operation and impact of contact resistance.

- Chapter. 3: Illustrates the modeling requirements, benchmark tests and classification of modeling methodologies along with their pros and cons. Then, a-GIZO TFT static model, which is developed from the measured characteristics of the device, is presented, using different types of ANNs, such as, MLP, RBF and LS-SVM. This is followed by a comparison among these methods in terms of accuracy and complexity. In addition, the complete model is developed based on the equivalent circuit approach that can characterize static and dynamic behavior of the device. Finally, the neural based equivalent circuit model is implemented in Verilog-A for circuit simulations. Before applying the modeling method to a-GIZO TFT, it is experimented with the MOSFET to validate the modeling approach, whose data was obtained from BSIM3V3 model.

- Chapter. 4: Characterizes the basic analog/digital building blocks, namely different types of current mirrors, buffer, logic gates, single-stage amplifiers (common-source, differential, bootstrapping, with positive feedback load) and cascade amplifiers, only with n-type enhancement transistors. A single TFT application in half-wave rectifier and peak detector is also characterized. The novel single-stage high-gain amplifier topologies are demonstrated. Analog signal processing circuits, such as, traditional and novel adders, subtractor, multipliers are explained. Novel high-impedance load to accomplish high-gain is presented.

- Chapter. 5: This chapter is dedicated to the mixed signal circuits. First a high-gain comparator is presented, where the bias stress is compensated to some extent. Finally a four-bit folding ADC is also demonstrated.

- Chapter. 6: This chapter is devoted to the conclusions from the PhD work and the possible future work in terms of modeling and circuit design with a-GIZO TFTs.

# Chapter 2

# a-GIZO Technology: What it is and what are its Challenges

This chapter presents a brief description of the thin film transistor (TFT) technologies, focused on amorphous gallium indium zinc oxide (a-GIZO) materials, in the context of display panel applications, which has been the main driving engine for worldwide research in the area. Well known TFT device structures and device fabrication information, of actual devices used along this work, will also be object of analysis, in addition to the impact of materials on the device performance. This is followed by a description of TFT operation, using a real fabricated TFT as a basis. Finally, different layouts of transistors are discussed.

#### 2.1 Thin-Film Transistors Technologies

TFT technologies have emerged into a huge industry, dedicated mainly for display applications. Since the beginning days that the common choice for TFT material was the hydrogenated amorphous silicon (a-Si:H). This technology was (and still is) devoted principally for active elements of liquid crystal display (LCD) or organic light emitting diode (OLED) active matrix backplanes. However, a-Si:H TFT devices present a relevant threshold-voltage (V<sub>TH</sub>) variation, low carrier mobility  $(\mu)$  and non-transparency in visible spectrum. For these devices,  $V_{TH}$  variation takes place not only during the gate-bias stress but also in off-state bias [38]. Here, the gate-bias stress refers to the variation in the  $V_{TH}$ , with continuous application of gate voltage ( $V_{GS}$ ) that consequently changes the electrical characteristics of the device. The bias stress is not a critical issue in case of LCD drivers, as the gate voltage is applied only for a small fraction of time. But in OLED displays, the driver TFT contained in the pixel circuitry needs to drive a specific current and keep it on as long as the pixel is emitting light. In this case V<sub>TH</sub> shift becomes a critical issue, as it will affect the current being supplied to the OLED, changing its brightness [16]. Nevertheless, the design of pixel circuits can be compensated for some of the threshold shifting at the expense of more TFTs per pixel [16]. Low temperature poly-silicon (LTPS) is an alternative option. The fabrication temperature is around 600°C, which being slightly lower than the melting temperature of glass, naturally establishes this technology as a possible candidate for display applications. Moreover, LTPS TFTs are less prone to bias stress, present higher electrical mobility and also complementary type devices are possible (which are not yet stable in other TFT technologies). In spite of these advantages, LTPS TFTs are not able to easily replace a-Si:H TFTs in displays due to higher manufacturing cost (as it requires more processing steps and masks than a-Si:H TFTs) and lack of uniformity in large areas, as a consequence of the polycrystalline structure of the semiconductor material. Notwithstanding, many research groups still continue working towards obtaining devices with better electrical characteristics, to ensure large-area electronics with better uniformity, either by means of finding new materials, processing steps or different device structures, while keeping fabrication costs low. In this process, other TFT technologies have emerged, mainly focused on organic and metal-oxide semiconductors. Organic semiconductor based (O)TFTs, despite exhibiting great potential for flexible and large area electronics, have shown poor mobility. On the contrary, TFTs based on the conventional metal-oxides (i.e., binary compounds) such as Zinc oxide (ZnO) have shown relatively higher mobility, in some cases even exceeding 20 cm<sup>2</sup>/V·s with room-temperature processing [39]. However, as with LTPS, ZnO and other well known binary compounds such as Indium oxide (In<sub>2</sub>O<sub>3</sub>) and Tin oxide (SnO<sub>2</sub>) are polycrystalline, limiting large area fabrication. Furthermore, depending on grain size and doping level, grain boundaries can significantly affect device performance/stability by trapping free carriers [38]. These difficulties can be overcome by using multicomponent oxides, i.e., materials combining different cations of post-transition metals with electronic configuration  $(n-1)d^{10}$  ns<sup>2</sup>, where ns $\geq 4$  [17]. In this case, given the structural disorder imposed by mixing different cations, amorphous structures are obtained. Still, contrarily to covalent semiconductors like Si, the increased disorder does not lead to a significant degradation of electrical performance, since the conduction band of these multicomponent oxides is primarily derived from spherically symmetric and large radii 4s or 5s orbitals. This results in overlap of adjacent orbitals, hence to the formation of a conduction path to free carriers, regardless of the degree of disorder. In such a case, mobilities in the range of 10-50 cm<sup>2</sup>/V·s are possible, even with processing temperatures below 200°C [40]. One of the most successful multicomponent oxides studied to date has been amorphous Gallium-Indium-Zinc oxide (a-GIZO). Despite having in its composition two cations identified by the European Comission as critical raw materials (In and Ga), compared with other multicomponent oxides such as Zinc-Tin oxide (ZTO), a-GIZO allows for higher mobility at lower processing temperatures [40].

As Table 2.1 summarizes, when compared to CMOS, except for LTPS, all TFT technologies present orders of magnitude less mobility, and also much higher feature sizes. But one should understand that for specific application areas that demand flexible and or transparent and large-area electronics, at very low-cost, or even for generic low-frequency applications, TFTs are highly competitive.

#### 2.1.1 a-GIZO TFTs as the Next Mainstream TFT technology

Room temperature fabrication of TFTs, using a-GIZO as a semiconductor layer, was introduced in 2004 [17]. Since then, intensive research was conducted to obtain devices with improved per-

| Technology    | Feature<br>size | Polarity          | Mobility<br>(cm²/V·s) | Semiconductor<br>fabrication<br>process                              | Process<br>tem-<br>pera-<br>ture | Substrate           | Supply<br>voltage<br>(V)* | Transparency<br>to visible<br>light | Ref.          |

|---------------|-----------------|-------------------|-----------------------|----------------------------------------------------------------------|----------------------------------|---------------------|---------------------------|-------------------------------------|---------------|

| CMOS          | 32/22 nm        | p-type,<br>n-type | 1500                  | Chemical va-<br>por deposition<br>(CVD)-based<br>epitaxial<br>growth | 1000°C                           | Si wafer            | 1                         | Opaque                              | [41]          |

| LTPS          | 3 μm            | p-type,<br>n-type | >100                  | Low-pressure<br>chemical va-<br>por deposition<br>(LPCVD)            | 600°C                            | Glass               | 9                         | Opaque                              | [42],<br>[43] |

| a-Si:H<br>TFT | 8 μm            | n-type            | 0.1–1                 | Plasma enhanced chemical vapor deposition (PECVD)                    | 250°C                            | Glass or<br>Plastic | 20                        | Opaque                              | [41]          |

| OTFT          | 5 μm            | p-type            | 0.1–1                 | Evaporation, spin-coating, inkjet                                    | 150°C                            | Glass or<br>Plastic | 15                        | 25-30%                              | [28]          |