#### **FACULDADE DE ENGENHARIA**

#### UNIVERSIDADE DO PORTO

Doctoral Programme in Electrical and Computer Engineering

# High-Efficiency Linear Transmitters for Mobile Communication Systems

by

Cândido Duarte

April, 2014

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

DOCTORAL PROGRAM IN ELECTRICAL AND COMPUTER ENGINEERING

# High-Efficiency Linear Transmitters for Mobile Communication Systems

by

#### Cândido Duarte

Instituto de Engenharia de Sistemas e Computadores do Porto Faculdade de Engenharia da Universidade do Porto

> Dissertation submitted in partial fulfillment of the requirements for the degree of

#### **Doctor of Philosophy**

Ph.D. Thesis supervised by

Vítor Manuel Grade Tavares, Ph.D.

Instituto de Engenharia de Sistemas e Computadores do Porto Faculdade de Engenharia da Universidade do Porto

and

José Carlos Esteves Duarte Pedro, Ph.D.

Instituto de Telecomunicações – Aveiro Universidade de Aveiro

$\odot$  Copyright by Cândido Duarte 2014

All Rights Reserved

| – Declaration | of | Author | ship - |

|---------------|----|--------|--------|

|---------------|----|--------|--------|

I declare that this thesis and the work presented in it has not been previously submitted for a degree at the University of Porto or any other university and I further declare that the work embodied in it is my own, or else clearly attributed.

## Abstract

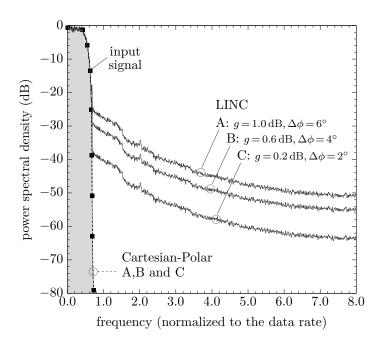

This thesis presents a new wireless transmitter architecture in which both Cartesian and polar topologies are merged into a single structure, herein termed "Cartesian-Polar (C-P) architecture." By exploiting the main advantages of both topologies, the proposed transmitter aims at linear and efficient amplification of signals with high peak-to-average power ratios. Switching-mode polar amplifiers are employed with bipolar envelope modulators targeting high efficiency. These power stages also operate as high-level quadrature modulators, where the I and Q baseband signals directly modulate the dynamic power-supply. Compared to the polar architecture, the now proposed C-P transmitter shows reduced bandwidth requirements for both the envelope amplifiers and PAs. The C-P also compares favorably to the LINC architecture in terms of power efficiency and spectrum regrowth due to impairments in the RF paths.

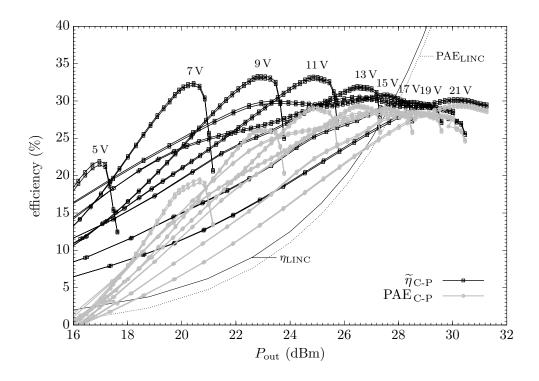

In the present research, the feasibility of implementation of the proposed arquitecture is addressed. Two circuits are studied, as distinct implementation solutions for the PA stages of the C-P architecture. The first circuit consists of a CMOS-PA topology operating in class E with bipolar envelope. A comprehensive analysis is presented, briefly addressing asymmetries of relevant parameters in the RF performance. In a second circuit proposal, an LDMOS topology is addressed. It consists of a switching-mode circuit operating either as an oscillator or amplifier, depending on the power supply. It allows the rejection of common-mode components of two dynamic power-supplies, while the differential mode is amplified. For each of the two topologies included in a C-P architecture, the efficiency is shown to be higher than a LINC transmitter for output signals considerably lower than the peak power.

### Resumo

A presente tese apresenta uma nova arquitetura de transmissão RF onde as configurações cartesiana e polar são combinadas numa única, aqui denominada "transmissor Cartesiano-Polar (C-P)." Ao explorar as principais vantagens de cada uma das arquitecturas, o transmissor proposto visa a amplificação linear e eficiente de sinais com elevados rácios entre a potência de pico e a potência média. Para obter alta eficiência são utilizados amplificadores comutados em que a envolvente é bipolar. Estes andares de potência também funcionam como moduladores de quadratura de alto nível, onde a tensão de alimentação dinâmica dá-se pelos sinais IQ. Em comparação com o polar, o transmissor proposto mostra requisitos de largura de banda mais reduzidos, tanto para o amplificador de envolvente como para o PA. O C-P também se compara favoravelmente com o LINC em eficiência e resposta espectral devido a desigualdades nos caminhos RF.

Na presente investigação estuda-se a viabilidade de implementação da arquitetura proposta. São estudados dois circuitos distintos como possíveis soluções de implementação dos PAs no C-P. A primeira proposta é um circuito CMOS a operar em classe E com envolvente bipolar. É apresentada uma análise detalhada, abordando assimetrias de parâmetros relevantes no desempenho RF. O segundo circuito é uma configuração LDMOS. Tratase de um circuito de comutação que opera como oscilador ou amplificador, dependendo da tensão de alimentação. O circuito permite a rejeição de componentes de modo comum de duas fontes de alimentação dinâmicas, sendo amplificado o modo diferencial. Em cada um dos dois circuitos, incluídos em arquiteturas C-P, mostra-se que a eficiência é superior à de um LINC com sinais de saída muito menores que a potência de pico.

In memory of my grandfather,  $Alexandre\ Duarte$

# Acknowledgments

First and foremost, I wish to acknowledge Professor Pedro Guedes de Oliveira, who has inspired my fascination with analog circuits. I have learned a lot from his teaching approaches and generous insights that had an invaluable influence in my professional perspectives and personal development.

Secondly, to my principal supervisor, Professor Vítor Grade Tavares, I would like to present my sincere and deepest gratitude for the support and the oportunities to improve my background and interest in different research fields.

To my advisor, Professor José Carlos Pedro, I am very grateful for the useful guidelines and brilliant scientific ideas. I also thank for the sharing of some of his interesting scientific challenges, most of which filled my mind on return trips by train from Aveiro.

Additional acknowledgments to university staff, in particular, Nuno Sousa, Isidro Ribeiro, Rosário Macedo, Prof. Ana Maria Mendonça, Prof. Campilho, Prof. Canas Ferreira and Prof. Silva Matos. I want to thank all their constant encouragement words. Thanks also to my colleagues at INESC Porto, Hélder and Mário.

To all my collaborators from the Microelectronics Students' Group at FEUP, I would like to thank for the great experience on leading such an incredible work atmosphere. I would like to thank Daniel, Américo, Coke, and Pina (Silicon Gate), Malheiro, Caetano and Patrício (Synopsys), Cavadas

and Tiago (Cadence), and André Cardoso. Thanks for the great experience on working side by side in numerous design projects and for the valuable friendship. I also want to thank the cooperation of all the other students in this group, specially for believing on the intrinsic value of such an initiative.

I have to give a special mention to a number of my former undergraduate students. Thanks folks for your incessant support: Ana Ribeiro, Licas Miranda and Bruno Augusto, André Morais, Adriano Pereira, Pedro Amaral, Andrea Corte Real, Rui Gomes, Rui Feio, Duarte Silva, Nadia Bischoff, Cátia Viães, Carolina Gaifém, Diogo Meira, Hélder Pedrosa, and Fátima Airosa.

Thanks for welcoming me Jelena, Alena and Mirjana from the University of Novi Sad, Serbia, and Rocco from University of Rome Tor Vergata.

I would like to thank those friends who, despite living abroad, kept regularly motivating me on never giving up. Thanks Ana Belchior and Luís, Ana Filipa, Tó and Liliana. Special thanks to two great friends, Pedro (Infineon) and Caló (CSR). I also thank for constant support from close friends, Mia, Filipa Elias, Elisa Nunes, Mariana Oliveira, Pipa and Tiga(s), Raquel Gaspar, Nuno Pires, Helena and Susana Seromenho, Ângelo, Bernardo and Guilherme, Ana Bastos, Ricardo Faro, and my good friend Sebastian.

I want to thank Cláudia, for her love and understanding.

I must express my deepest gratitude to Eng. Milheiro and Conceição, Flórido and Norvinda for all the help they provided to me and my family during difficult times.

Lastly, my heartfelt gratitude to my family. I am extremely grateful for their support and encouragement along these years on bringing this dissertation towards an end. With the hard work during the last years, I have been postponing vacations, refusing employment offers, missing special family events and so many other meaningful things in life. I want to thank all those who have respected my dedication.

# Contents

| Si               | gnati                  | ure Page                        | VII |

|------------------|------------------------|---------------------------------|-----|

| $\mathbf{A}$     | bstra                  | et                              | ix  |

| $\mathbf{R}_{0}$ | esum                   | .0                              | xi  |

| D                | edica                  | tion                            | iii |

| A                | cknov                  | wledgments                      | ΧV  |

| Ta               | able o                 | of Contents x                   | vii |

| Li               | $\operatorname{st}$ of | Figures                         | ХХ  |

| Li               | $\operatorname{st}$ of | Tables xx                       | iv  |

| 1                | Intr                   | roduction                       | 1   |

|                  | 1.1                    | Linearity-Efficiency Compromise | 3   |

|                  | 1.2                    | Cartesian-Polar Transmitter     | 10  |

|                  | 1.3                    | Original Contributions          | 13  |

|                  | 1.4                    | Outline                         | 13  |

| <b>2</b>         | Tra                    | nsmitter Architectures          | 15  |

|                  | 2.1                    | IQ Transmitters                 | 16  |

|                  |                        | 2.1.1 Doherty Technique         | 17  |

|                  | 2.2                    | Envelope Tracking               | 19  |

|                  | 2.3                    | Polar Transmitter               | 21  |

|   |     | 2.3.1 Envelope amplifier                                 | 23  |

|---|-----|----------------------------------------------------------|-----|

|   |     | 2.3.2 Main drawbacks of polar transmitters               | 26  |

|   | 2.4 | LINC                                                     | 29  |

|   |     | 2.4.1 Generation of outphasing signals                   | 31  |

|   |     | 2.4.2 Effect of path impairments                         | 33  |

|   |     | 2.4.3 Efficiency                                         | 35  |

|   | 2.5 | Digital RF Transmitters                                  | 36  |

| 3 | The | Cartesian-Polar Architecture                             | 39  |

|   | 3.1 | System Description                                       | 39  |

|   | 3.2 | Bandwidth                                                | 43  |

|   |     | 3.2.1 Impact of finite bandwidth of dynamic power-supply | 47  |

|   | 3.3 | Efficiency Analysis                                      | 48  |

|   | 3.4 | Effect of Power Recycling                                | 51  |

|   | 3.5 | Sensitivity to Structural Impairments                    | 54  |

| 4 | C-P | Transmitter based on a Symmetric PA Topology             | 61  |

|   | 4.1 | Output Combiner                                          | 65  |

|   | 4.2 | Class-E Power Amplifier                                  | 68  |

|   | 4.3 | Topology Analysis                                        | 72  |

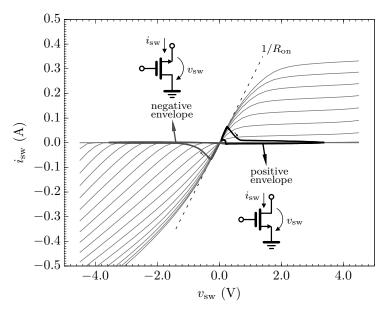

|   |     | 4.3.1 Asymmetric current-voltage characteristic          | 72  |

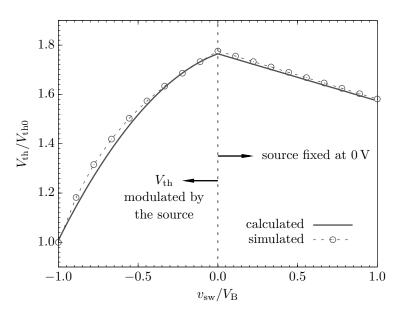

|   |     | 4.3.2 Body effect                                        | 75  |

|   |     | 4.3.3 Parasitic capacitances                             | 76  |

|   |     | 4.3.4 Reliability issues                                 | 78  |

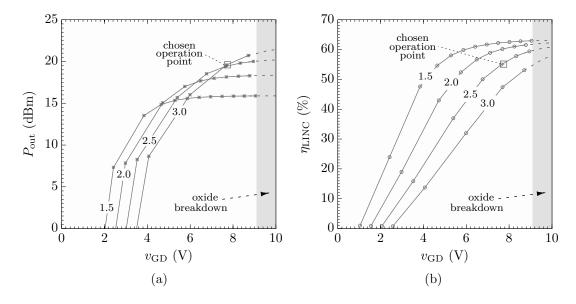

|   |     | 4.3.5 Maximum-power and efficiency dependence            | 80  |

|   |     | 4.3.6 Gate driving                                       | 83  |

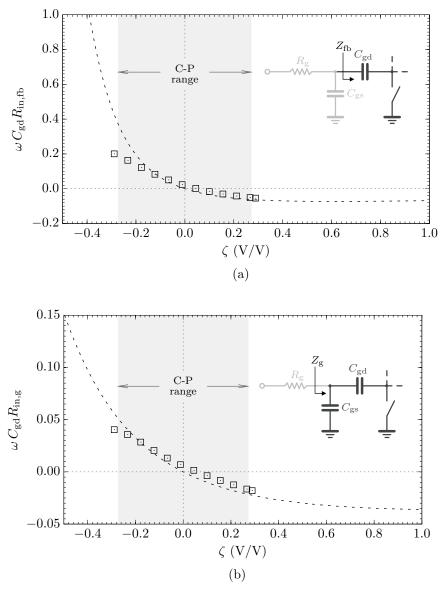

|   |     | 4.3.7 Input impedance                                    | 86  |

|   |     | 4.3.8 Matching considerations                            | 88  |

|   | 4.4 | Performance Overview                                     | 91  |

|   | 4.5 | Simulation Results                                       | 96  |

| 5 | C-P | Transmitter based on a Differential PA Topology 1        | .03 |

|   | 5.1 | Proposed Topology                                        | 105 |

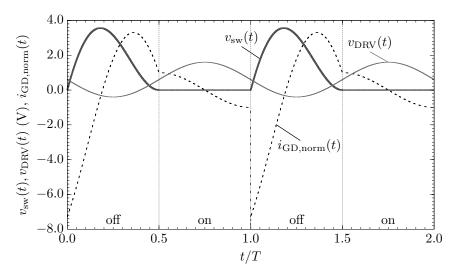

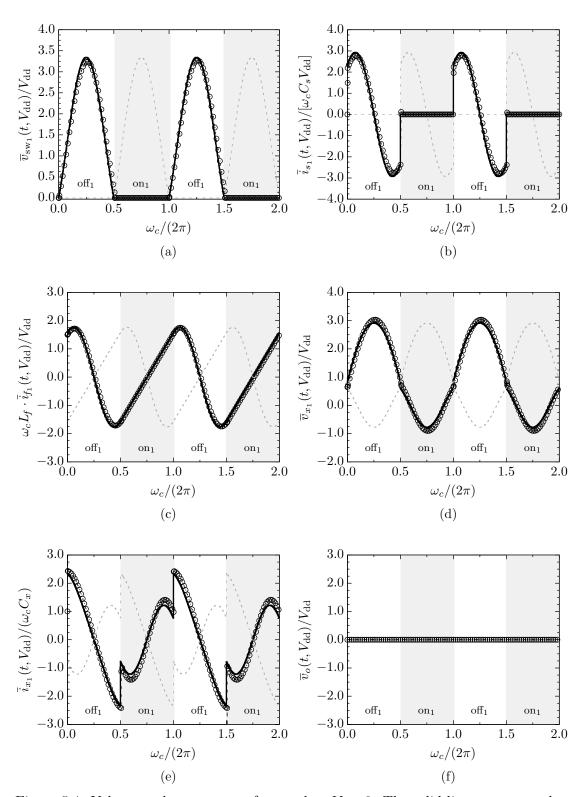

|    |       | 5.1.1                | Circuit waveforms                | <br>108 |

|----|-------|----------------------|----------------------------------|---------|

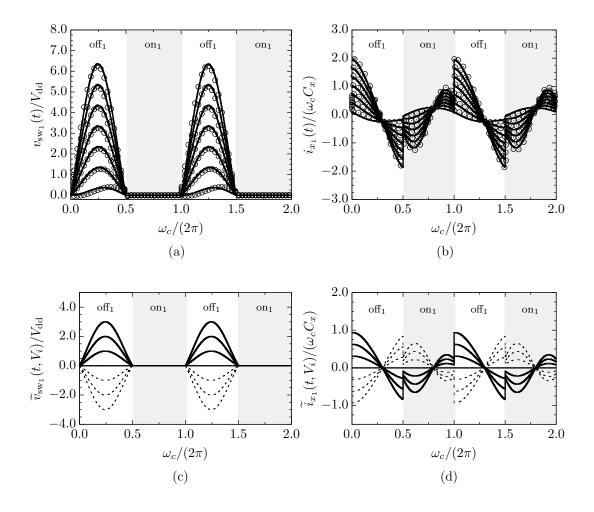

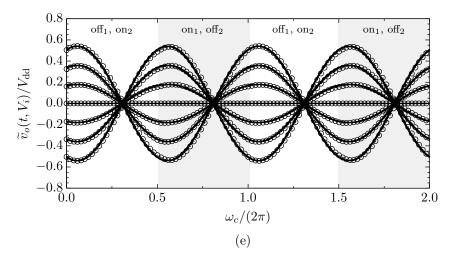

|    | 5.2   | Simula               | ation Results                    | <br>122 |

|    |       | 5.2.1                | Design example                   | <br>129 |

| 6  | Con   | clusio               | n                                | 139     |

|    | 6.1   | Recom                | nmendations for Future Work      | <br>140 |

| Re | efere | nces                 |                                  | 143     |

| Ad | crony | ms an                | d Abbreviations                  | 161     |

| Aı | ppen  | $\operatorname{dix}$ |                                  | 167     |

| A  | I-V   | Mode                 | l for short-channel MOSFETs      | 167     |

| В  | Der   | ivation              | of the Differential-PA Waveforms | 171     |

|    | B.1   | Comm                 | non Mode                         | <br>171 |

|    | B.2   | Differe              | ential Mode                      | <br>172 |

# List of Figures

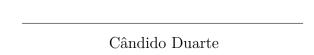

| 1.1  | CDMA PDF and efficiencies of classes A and B                | 4  |

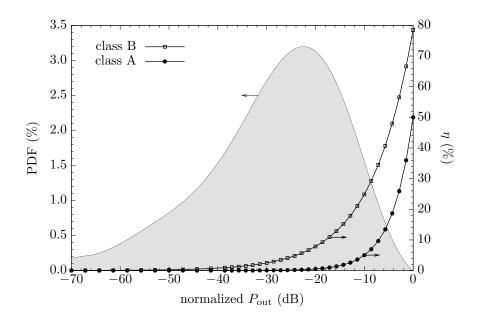

|------|-------------------------------------------------------------|----|

| 1.2  | Techniques to overcome the linearity-efficiency tradeoff $$ | 5  |

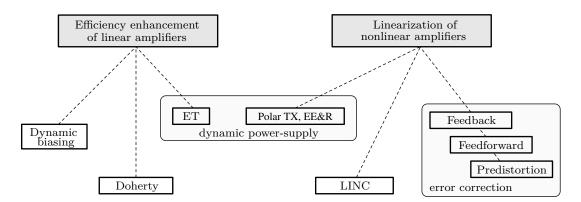

| 1.3  | Cartesian Tx                                                | 6  |

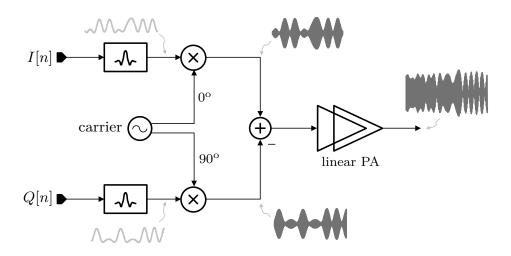

| 1.4  | LINC Tx                                                     | 7  |

| 1.5  | Polar Tx                                                    | 8  |

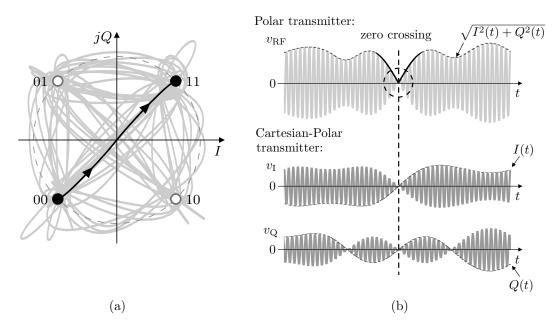

| 1.6  | Representative waveforms for an IQ zero-crossing $\dots$    | 11 |

| 1.7  | Proposed Tx architecture                                    | 12 |

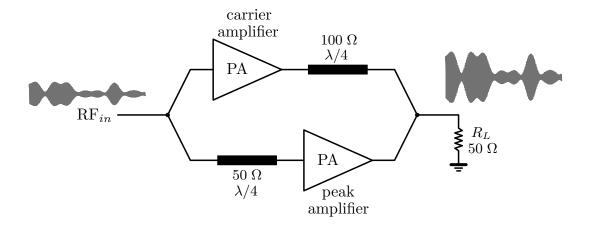

| 2.1  | Doherty amplifier                                           | 17 |

| 2.2  | Operation regions in the Doherty PA                         | 18 |

| 2.3  | Illustrative example on ET                                  | 19 |

| 2.4  | ET implementations                                          | 20 |

| 2.5  | EER and polar Txs                                           | 22 |

| 2.6  | Envelope modulators for polar Txs                           | 24 |

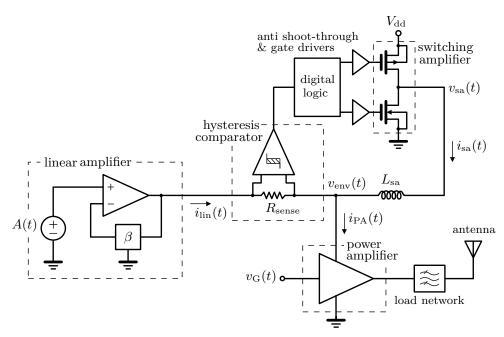

| 2.7  | Hybrid-switching concept                                    | 25 |

| 2.8  | LINC Tx and its phasor representation                       | 30 |

| 2.9  | LINC with digital SCS implemented by I/Q method             | 32 |

| 2.10 | Digital controlled PA structures with AM                    | 38 |

| 3.1  | Build up of the C-P Tx                                      | 40 |

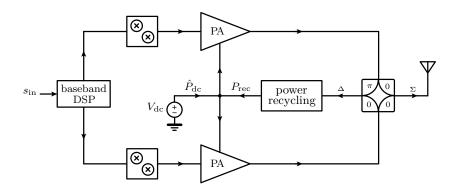

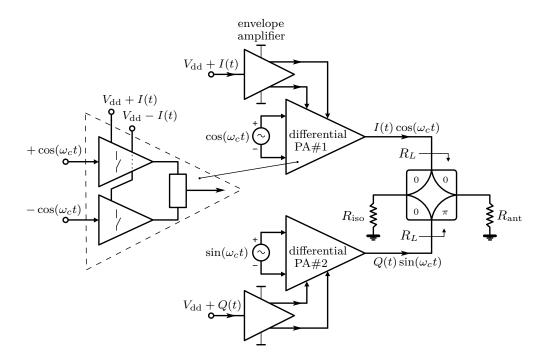

| 3.2  | Block diagram of the C-P Tx architecture                    | 41 |

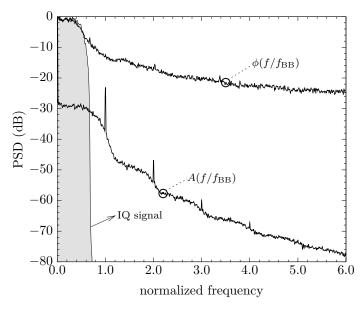

| 3.3  | Complex baseband PSD of a 16-QAM signal                     | 43 |

| 3.4  | Zero-crossings example in polar and C-P Txs                 | 44 |

| 3.5  | Conventional hybrid-switching envelope amplifier $\dots$    | 46 |

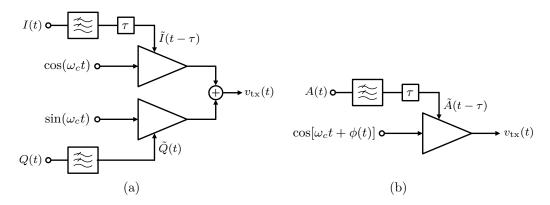

| 3.6  | Finite bandwidth and time delays in polar and C-P Txs       | 47 |

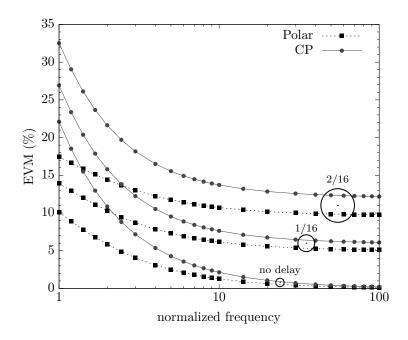

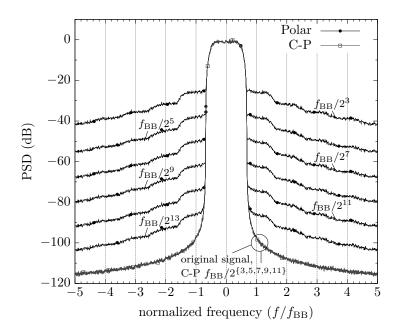

| 3.7  | Spectrum with time misalignments of polar and C-P Txs                     | 48 |

|------|---------------------------------------------------------------------------|----|

| 3.8  | Finite envelope bandwidth in EVM of polar and C-P Txs                     | 49 |

| 3.9  | Signal decomposition at the output combiner of the C-P Tx                 | 50 |

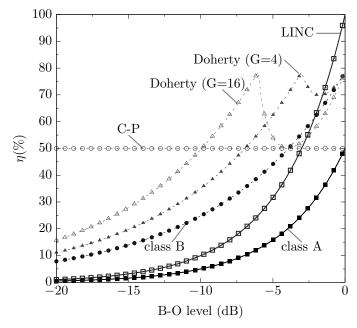

| 3.10 | Drain efficiencies in terms of B-O for different wireless Txs .           | 50 |

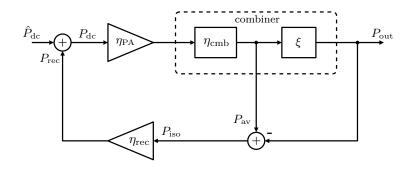

| 3.11 | RF Tx with power recycling                                                | 52 |

| 3.12 | Power-flow diagram of power-recycling Txs                                 | 52 |

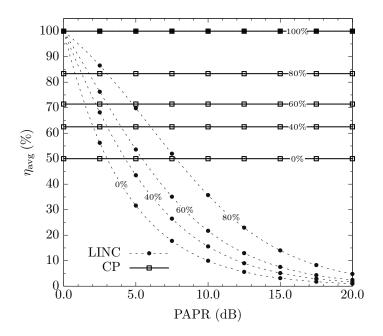

| 3.13 | Efficiencies with recycling systems in LINC and C-P Txs                   | 53 |

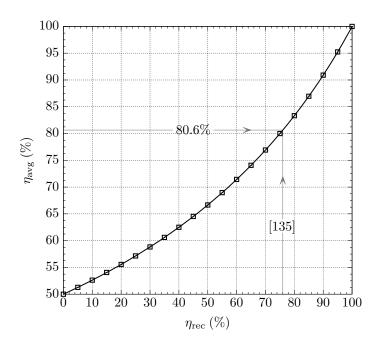

| 3.14 | Efficiency of the C-P Tx for different recycling efficiencies             | 54 |

| 3.15 | Block diagram for study of impairments of the C-P Tx                      | 55 |

| 3.16 | Block diagrams with RF path impairments for analysis                      | 58 |

| 3.17 | 16-QAM EVM comparison between Cartesian/C-P and LINC                      | 59 |

| 3.18 | PSD for C-P and LINC Txs with phase and gain impairments                  | 60 |

| 4.1  | Simplified representation for a C-P architecture (non-isolated)           | 62 |

| 4.2  | Proposed front-end for the C-P architecture (isolated)                    | 64 |

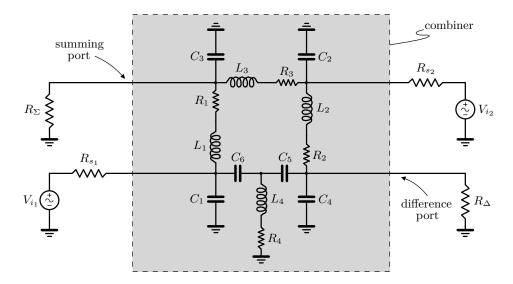

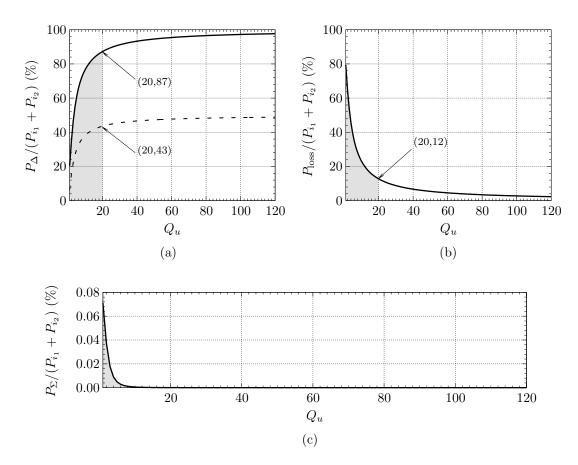

| 4.3  | Lumped-model representation for the hybrid combiner $$                    | 66 |

| 4.4  | Efficiencies in a matched-hybrid combiner in terms of $Q_u$               | 67 |

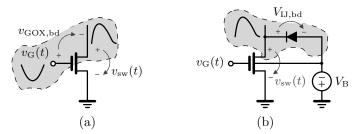

| 4.5  | Class-E bipolar-driven PA                                                 | 69 |

| 4.6  | Voltage/current waveforms at the switch of a bipolar class E              | 71 |

| 4.7  | Load lines for the class-E PA with the bipolar current                    | 72 |

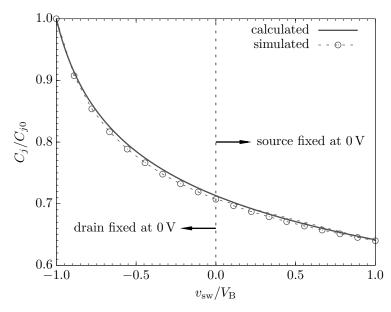

| 4.8  | Asymmetries in threshold voltage of the CMOS C-P PA $$                    | 77 |

| 4.9  | Normalized junction capacitance due to switch voltage                     | 77 |

| 4.10 | Most susceptible types of breakdown in the CMOS C-P $\operatorname{PA}$ . | 79 |

| 4.11 | Drain efficiency versus device on resistance                              | 81 |

| 4.12 | Output power and estimated limits for the CMOS C-P PA $$ .                | 83 |

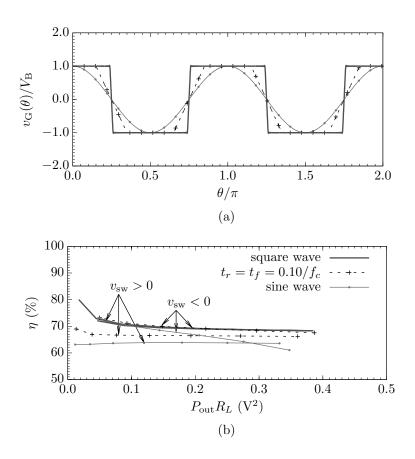

| 4.13 | Impact of gate signal on efficiency in terms of output power              | 84 |

| 4.14 | Voltage at the switch for square wave and sinusoidal driving              | 85 |

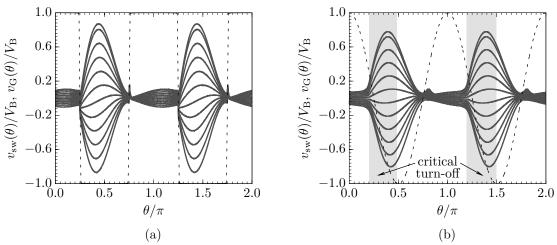

| 4.15 | Drain signal, gate driving and current through $C_{\rm gd}$               | 87 |

| 4.16 | Influence of the feedback capacitance due to power supply .               | 89 |

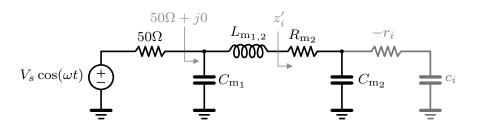

| 4.17 | Input matching network                                                    | 90 |

| 4.18 | Circuit for the CMOS C-P performance overview                             | 91 |

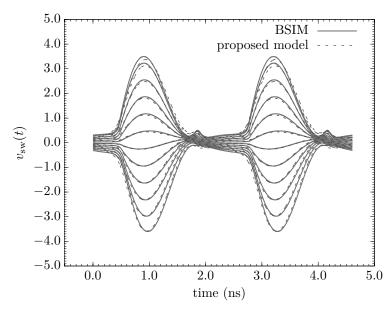

| 4.19 | Switch time-waveforms with BSIM and proposed model                        | 92 |

| 4.20 | Class-E PA efficiency for different load values and switch sizes 93                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

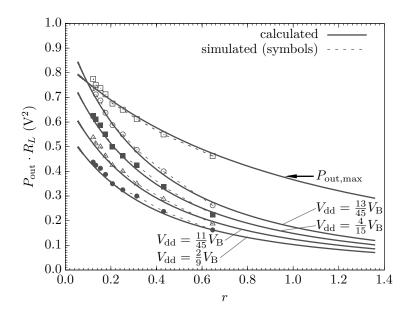

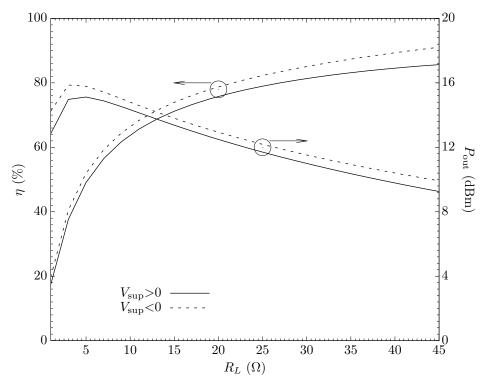

| 4.21 | Efficiency and output power in terms of $R_L$ for a C-P class E 94                                                                                                     |

| 4.22 | $R_{\rm dc}$ in terms of supply voltage                                                                                                                                |

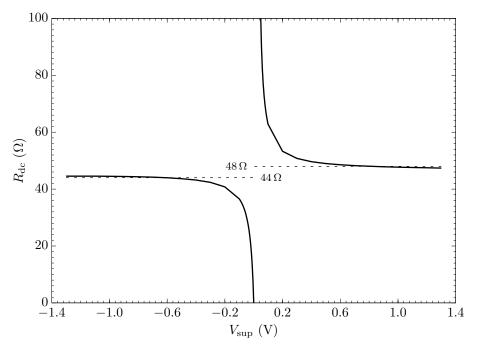

| 4.23 | Influence of $C_{\rm gd}$ in CMOS PA efficiency                                                                                                                        |

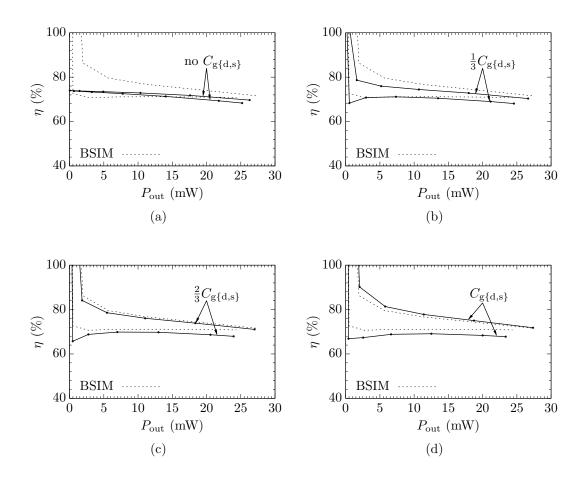

| 4.24 | LINC efficiency and output power in terms of $v_{\mathrm{GD}}$ for differ-                                                                                             |

|      | ent power-supply levels                                                                                                                                                |

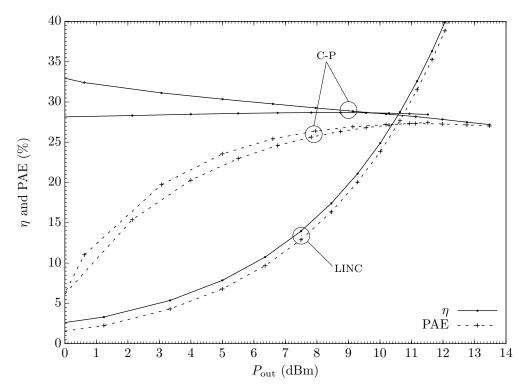

| 4.25 | Efficiencies C-P vs LINC for CMOS implementations 99 $$                                                                                                                |

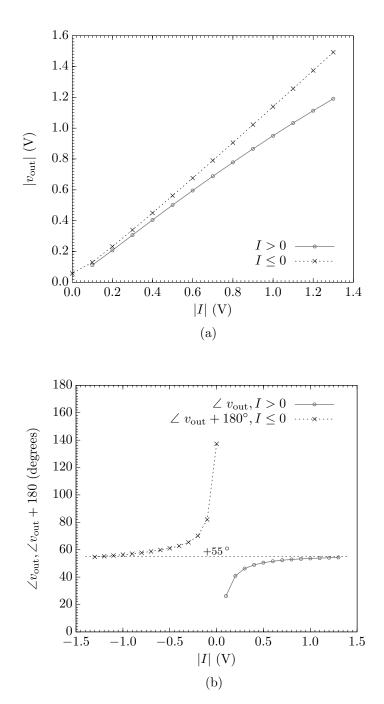

| 4.26 | Simulation results for CMOS C-P $ v_{\text{out}} $ and $\angle v_{\text{out}}$ 100                                                                                     |

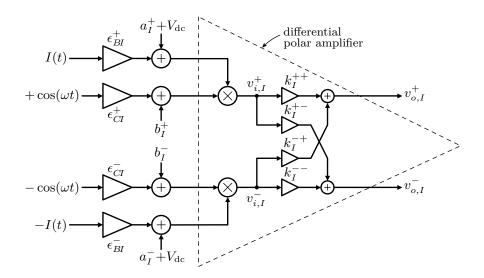

| 5.1  | Block diagram of the LDMOS topology for the C-P Tx 104                                                                                                                 |

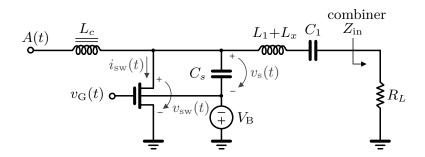

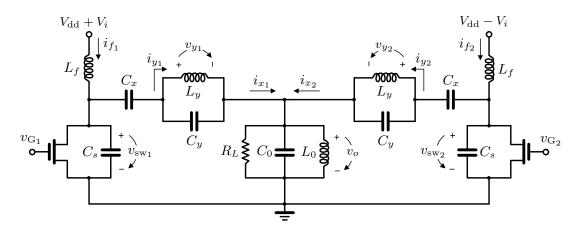

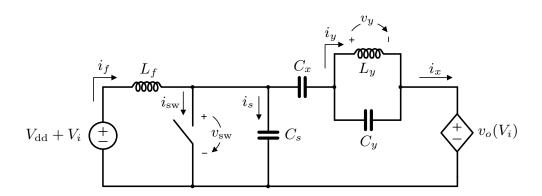

| 5.2  | Schematic of the proposed amplifier                                                                                                                                    |

| 5.3  | Simplification for analysis of the differential PA $\dots \dots \dots$ |

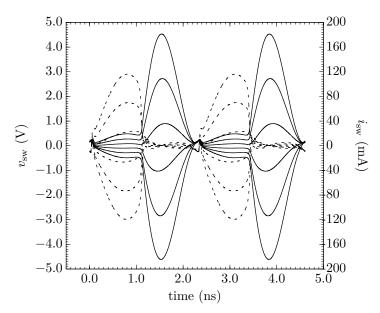

| 5.4  | Voltage and current waveforms when $V_i = 0$                                                                                                                           |

| 5.5  | Voltage and current waveforms when $V_i \neq 0$                                                                                                                        |

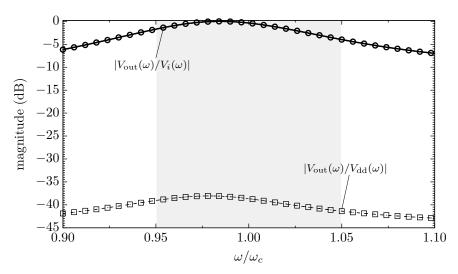

| 5.6  | Frequency response to common and differential modes $126$                                                                                                              |

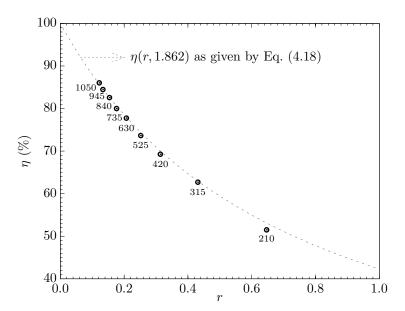

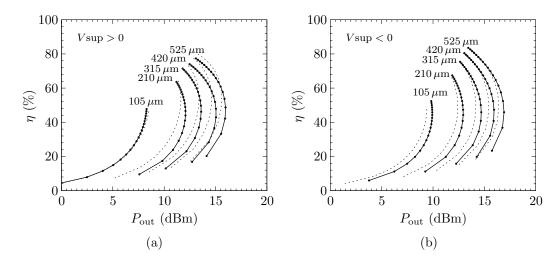

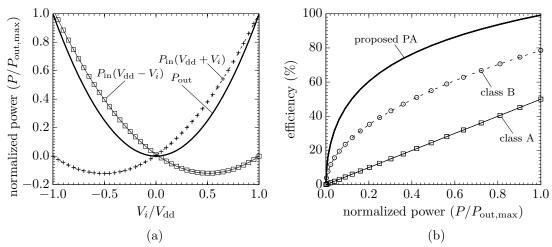

| 5.7  | Theoretical efficiency of the differential PA                                                                                                                          |

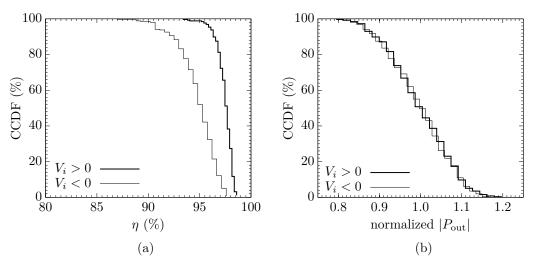

| 5.8  | CCDF for the efficiency of the PA due to asymmetries $$ 128                                                                                                            |

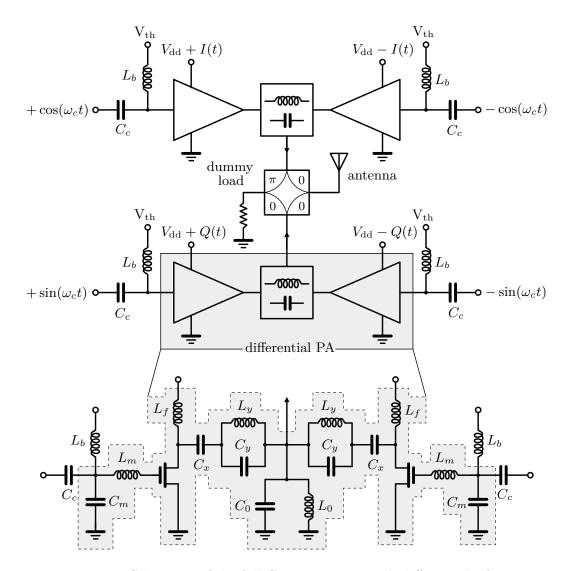

| 5.9  | Schematic of the CP-Tx with differential PAs                                                                                                                           |

| 5.10 | Simulation results for drain and output waveforms                                                                                                                      |

| 5.11 | Power flow in the proposed LDMOS transmitter                                                                                                                           |

| 5.12 | Efficiencies of the differential PA and LINC                                                                                                                           |

| 5.13 | Voltage magnitude and phase for the differential PA 135 $$                                                                                                             |

| 5.14 | Simulation results for the efficiency in the differential PA 136                                                                                                       |

# List of Tables

| 1.1 | Pros and cons of Cartesian and polar Txs               |

|-----|--------------------------------------------------------|

| 2.1 | Performance summary of reported envelope amplifiers 26 |

| 3.1 | PAPR influence in the hybrid switching amplifier 46    |

| 5.1 | Component values for a differential PA                 |

| 5.2 | Parameter values for the design example                |

| 5.3 | Device values for the differential-PA design           |

# Chapter 1

## Introduction

On the lookout for new mobile applications, the telecommunication markets are continuously demanding for higher and higher data rates [1–3]. Conversely, the available frequency bandwidth is relatively limited. The regulated wireless spectrum is shared by numerous subscribers and different communication standards coexist in a wide variety. With such a crowded medium, improving transmission data rates requires spectral-efficient communication schemes, such as those adopted in latest wireless technologies.

Nowadays, advanced digital modulations are commonly employed with pulse-shaped data, e.g. using root or square-root raised cosine filtering. This prevents intersymbol interference (ISI) in detection, and also provides a nearly-rectangular format for the spectrum emission [4]. Modern communications may also comprise other techniques for reducing the sensitivity to multi-path fading and frequency-selective interferences. These are often combined with multi-carrier modulations, such as OFDM<sup>1</sup> used in WiFi IEEE 802.11 (a/g/n), WiMAX, DVB and DAB, along other recent technologies. However, such sophistication comes at a relatively high cost. It ensues a non-constant envelope in the radio frequency (RF) signals to be transmitted. That is, confining large amounts of data in the available channel bandwidths is possible, but requires proper amplitude modulation of

<sup>&</sup>lt;sup>1</sup>For the sake of clarity, acronyms/abbreviated terms for modulation names and communication standards were not spelled out in its first use, because they tend to have very long terms. These are however included in a complete list provided in page 161.

PM/FM signals [5]. Hence, a time-varying envelope, as in typical OFDM systems, entails great linearity requirements in the transmitter (Tx) architecture. In fact, this implies that the transmitted power must not interfere with adjacent channels, otherwise the spectral efficiency would be adversely lowered. Additionally, the near-far problem also limits the channel capacity. To supress shadowing effects, all the mobile units are required to regulate their output powers. This way the interference with other similar mobile equipments is kept to a minimum [6]. The power control is actively applied within some sort of slow feedback. As a result, there is a significant variation of transmitted power levels, although in a time scale much larger than that from the envelope itself. Generally, this effect has no severe implications in terms of linearity, but it raises some efficiency concerns due to the need for a long-term regulation in power supply [7].

Energy efficiency is another factor that plays an important role in current days. In the case of wireless portable devices, in which the energy is already a scarce resource, an ever increasing number of software applications and multiple radio interfaces share the same battery as power supply. Extended operation or smaller battery sizes can only be attained by reducing the overall power dissipation. As a major concern, energy efficiency should be taken into consideration since the early phase of the architectural definition for the RF transmitter, i.e. having in mind the design of its constituent circuits. In fact, this is becoming a critical issue in new wireless products. The semiconductor industry foresees the reduction of one order of magnitude in power consumption as one of the most apprehensive challenges in forthcoming years [8]. Needless to say, any of these technological innovations must be accomplished without slowing down current data communication trends.

To a certain extent, high spectral and energy efficiencies depict contradictory scenarios in the performance of any wireless transmitter system. This is commonly known as the linearity-efficiency compromise [9]. Along the current dissertation, this kind of tradeoff is investigated from the

viewpoint of the transmitter architecture and respective circuits. A novel architecture is addressed, with circuits proposed for its practical implementation. The main goal is to obtain a feasible solution in which the tradeoff between linearity and efficiency can be further improved.

#### 1.1 Linearity-Efficiency Compromise

Traditionally, in transmit mode, the power amplifier (PA) represents the most significant share of power budget in a wireless transmitter. The most conventional linear classes A, AB and B are quite common in amplification of time-varying envelope signals. However, the major drawback of these classes is their low efficiency. Notwithstanding the PAs operating in classes A or B achieve drain efficiencies up to 50 or 80 %, respectively, these theoretical values are solely valid at peak power. The drain efficiency rapidly drops when the transmission power is reduced to mid-range values [10]. This is strongly reflected on the average power usage-efficiency  $(\eta_{\text{avg}})$ , defined as the ratio between output and input average powers [11],

$$\eta_{\text{avg}} \triangleq \frac{\langle P_{\text{out}} \rangle}{\langle P_{\text{dc}} \rangle} = \frac{\int_{0}^{P_{\text{max}}} P_{\text{out}} \cdot f(P_{\text{out}}) \, dP_{\text{out}}}{\int_{0}^{P_{\text{max}}} P_{\text{dc}}(P_{\text{out}}) \cdot f(P_{\text{out}}) \, dP_{\text{out}}}$$

(1.1)

where  $f(P_{\text{out}})$  is the probability density function (PDF) of the output power.

In the majority of sophisticated communication standards, most of the time it is required that the transmitter operates at a level well below the peak envelope power (PEP). As a practical example, Fig. 1.1 shows the PDF for the reverse link of an IS-95 CDMA transmission profile, from field measurements in an urban area [12]. The most probable power level is about 25 dB lower than the PEP of  $\sim 0.5$  W. Indeed, this implies a very high<sup>2</sup> peak-to-average power ratio (PAPR). It means that the PA must be

<sup>&</sup>lt;sup>2</sup>About 6 dB are due to the O-QPSK modulation and pulse shaping, whereas the remainder are due to long-time regulated operation [13].

Figure 1.1: CDMA PDF [12] and efficiencies of classes A and B.

designed far from peak envelope operation to accommodate a wide dynamic range.

The back-off (B-O) level from the saturated power has direct impact on the overall efficiency. In Fig. 1.1, the power efficiency is also depicted for ideal classes A and B at different output power levels. Graphically, comparing the efficiency dependence on  $P_{\text{out}}$  with the CDMA PDF, an overall drain efficiency of solely 2% comes at no surprise for the case of a typical class-AB PA operating in the present context [7,14].

Reducing the output B-O leads to compression in the envelope. Although it improves the efficiency, also degrades the linearity. This compromise between power efficiency and linearity is quite noticeable in these conventional PA classes. It basically resides on the fact it is not possible to maintain a constant gain irrespective of the output power level. The efficiency in class A decreases with  $P_{\rm out}/P_{\rm max}$ , whereas in class B depends on  $\sqrt{P_{\rm out}/P_{\rm max}}$ . In practical terms, depending on the communication standards, the B-O can be slightly reduced by allowing some signal clipping that still meets the error vector magnitude (EVM) and packet error

Figure 1.2: Existing techniques to overcome the linearity-efficiency tradeoff.

rate (PER) [15, 16]. However, this workaround is often not sufficient for satisfactory improvements on the linearity-efficiency compromise.

The energy efficiency is improved whenever the PA operates under strong nonlinear regimes. To the greatest degree, the transistor acts as an RF switch. In principle, high efficiencies can be attained using switching-mode PA (SMPA) classes, such as D, E, and F. This is possible because of the minimum overlapping between current and voltage across the switch. Theoretically, SMPAs offer the possibility to obtain drain efficiencies well above 80%, i.e. above the limit for ideal classes A to B. Nonetheless, as the power drawn from power-supply spreads over the frequency spectrum, the spectral efficiency is sacrificed. In fact, SMPA classes can only find a straightforward application in modulations for which the envelope is constant (e.g. GSM systems). For amplitude modulation, the switching-mode topology requires adequate modifications, which brings the linearity issues back into play.

In essence, there have been two distinct strategies on dealing with the linearity-efficiency tradeoff. One of those approaches relies on the efficiency enhancement of linear amplifiers, while the other consists of improving the linearity on efficient transmitters. As depicted in Fig. 1.2, numerous techniques can be divided between both approaches. Linearization techniques such as feedback, feedforward and predistortion are herein categorized as error correction methods. Such techniques are associated

Figure 1.3: Cartesian (IQ) Tx.

to significant drawbacks [17]. For instance, RF feedback requires excessive loop-bandwidth to ensure stability. Since this is rather complex to achieve in practice, linearization at RF is performed at an intermediate frequency (IF) or baseband using down-conversion mixers within a feedback loop [18]. The feedforward linearization also meets pratical implementation difficulties, in particular due to misalignments between RF paths [19]. Predistortion is perhaps the most successful scheme in reducing effects of nonlinear distortion on the performance of some systems [20]. It can be applied digitally and in conjunction with other systems, e.g. Doherty amplifier [21], but its main drawback is the difficulty on obtaining the inverse transfer function of the PA. In envelope tracking [22] and dynamic biasing [14], the power supply and/or bias voltages are controlled so that the PA operates close to saturation. Instead, in the Doherty amplifier, the load is actively modulated to improve the efficiency [23–26].

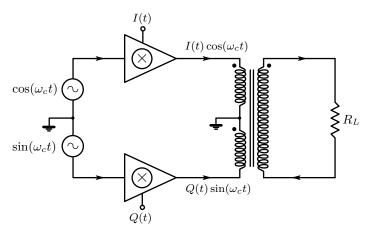

Traditionally, most of the transmitter implementations are based on the Cartesian (or IQ) architecture, because it is well suitable for the amplification of non-constant amplitude signals. Fig. 1.3 shows a simple block-diagram representation of the Cartesian transmitter. The in-phase (I) and quadrature (Q) signals are combined resulting in an RF signal with time-varying envelope, which is then amplified using a linear PA. But, as men-

Figure 1.4: LINC Tx.

tioned, due to high PAPRs the required power B-O significantly lowers the overall efficiency. This makes the IQ transmitter less attractive for modern high data-rate systems.

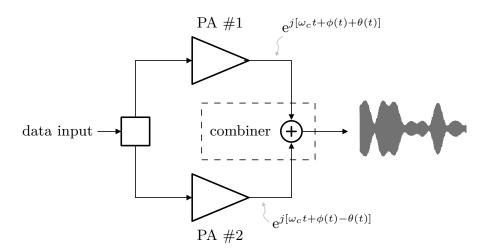

Linearization of SMPAs mostly implies the modification of transmitters at an architectural level. Lately, this has driven research and industry into the renaissance of amplitude modulation architectures, some of which were proposed still in the early days of radio. The LINC (linear amplification using nonlinear components) is such an example [27]. Fig. 1.4 shows the representation of a LINC transmitter system. It is based on the outphasing principle [28], in which two phase-deviated signals with constant amplitudes are combined to generate non-constant envelope signals. Hence, high-efficiency SMPAs can be used.

Recently, this technique has received renewed interest because apparently the efficiency can actually improve without great impact on linearity [29, 30]. The linearity-efficiency problem has been universally focused onto the PA, but the LINC concept embraces a distinct approach. First, it requires that the input data is translated in a specific way to provide constant-envelope signals for the use of SMPAs. Then, the linearity-efficiency compromise is more constrained by the output combining of the two PAs than the PAs themselves [31–33].

Figure 1.5: Polar Tx.

Power combining the two PAs of the LINC transmitter demands isolating and lossless passive networks. However, there is no theoretical possibility to meet these requirements simultaneously [34]. Therefore, one option is combining the PAs with lossy networks that isolate the outputs of each amplifier. In this case, the linearity should not be compromised, although the efficiency depends on the power combiner. The other solution is to use a non-isolated power combiner so that the efficiency can be improved, but at the expense of linearity. That is, each amplifier contributes to the impedance seen by the other (i.e., dynamic load modulation) and the gain is no longer preserved constant. As a result, nonlinearity is induced in the overall performance of the transmitter.

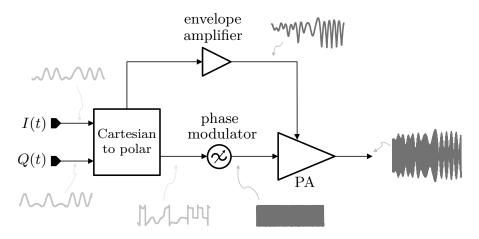

Fig. 1.5 depicts the polar transmitter, which is another promising alternative to Cartesian transmitter. As in the LINC, it also tackles the linearity-efficiency compromise by introducing modifications at the architectural level. That is, the IQ signals are converted into PM and AM signals. In the PM branch it is possible to use efficient PAs, whereas the linear amplification of the envelope is accomplished by drain modulation. As in the LINC, the net result from the combination of RF signals is a linear transmitter using a nonlinear PA.

Although the output waveforms at the load for any of these architectures

are the same (for the same data input), the signal characteristics of the analog paths are quite distinct. The digital data consists of I and Q symbols filtered at baseband. This is accomplished by pulse-shaping filters that limit the bandwidth occupied by data pulses. The bandwidth in the branches of the IQ modulator is imposed by the spectrum of pulse-shaped signals. However, as the conversion between Cartesian and polar coordinates takes place, the resulting signals are no longer limited in spectrum. As a result, in a polar transmitter the envelope |A(t)|

$$|A(t)| = \sqrt{I^2(t) + Q^2(t)}$$

(1.2)

and phase signals  $\phi(t)$

$$\phi(t) = \tan^{-1}\left(\frac{Q(t)}{I(t)}\right) \tag{1.3}$$

are wider in spectrum than the input signal itself. The circuits in the two analog paths have to deal with incredible large bandwidths to drive the PA. The envelope modulator, which is often implemented with switching-mode topologies, demands excessive oversampling ratios [35–38]. As the sampling frequencies get higher, also the associated switching-losses increase. Moreover, any time misalignment between phase and envelope paths degrades linearity as it results in spectral regrowth.

Table 1.1 summarizes some of the characteristics of Cartesian and polar transmitters. There is a compromise between efficiency and demanded input bandwidth in both architectures. Nevertheless, balancing these characteristics is not straightforward. It requires structural modifications in the architectures to expand the degrees of freedom in the overall efficiency-linearity tradeoff.

Such classical tradeoff has always been a challenge in the RF research. The growing demand for increased data rates has been driving investigation into different solutions in wireless architectures. Most works attempt improving the RF performance of linear transmitters either introducing

|             | Cartesian                             | Polar                                     |

|-------------|---------------------------------------|-------------------------------------------|

| B and width | +                                     | _                                         |

|             | Narrow bandwidth in                   | Extensive bandwidth in typical            |

|             | the $I$ and $Q$ baseband signals.     | $ A(t) $ and $\phi(t)$ signals.           |

| Efficiency  | _                                     | +                                         |

|             | Low-efficiency due to the             | High-efficiency in the PA due to possible |

|             | mandatory use of conventional         | use of dynamic biasing in                 |

|             | linear PAs at constant $V_{\rm DD}$ . | linear classes or drain modulation in     |

|             |                                       | switched-mode PAs.                        |

Table 1.1: Pros "+" and Cons "-" of Cartesian and Polar transmitters.

digital control techniques, or modifying the architecture itself – or even both ways. To address likely divergences on the linearity and efficiency requirements, the present thesis addresses the complete structure of a new transmitter, which is based on slight modifications of the classical Cartesian architecture.

#### 1.2 Cartesian-Polar Transmitter

The present thesis aims at studying the implementation feasibility of a novel transmitter architecture, herein termed "Cartesian-Polar (C-P) transmitter". As described next, the proposed architecture presupposes particular specifications, which require the investigation of circuit topologies suitable for a hardware realization.

Basically, this new transmitter scheme explores the benefits of polar and Cartesian architectures. As shown in Table 1.1, both offer distinct and interesting features, which motivated the current research work. The proposed solution is a combination of the two transmitter architectures. Without degrading efficiency, the proposed architecture aims at surpassing the typical drawbacks associated with the wide-bandwidth requirements in the analog paths of the conventional IQ transmitters.

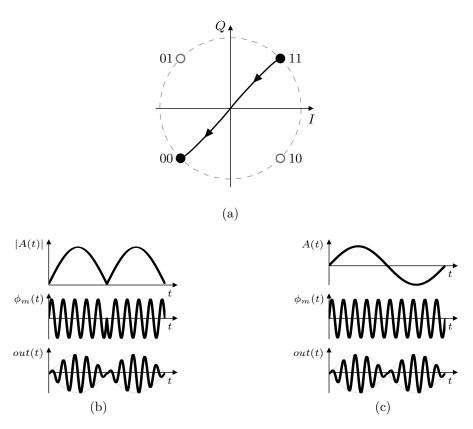

In a polar architecture, one of the underlying causes for large band-

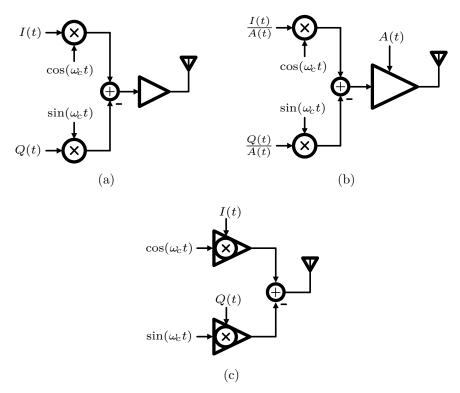

Figure 1.6: Representative waveforms for an (a) IQ zero-crossing in a (b) typical and (c) modified transmitter.

widths in phase and amplitude signals is the zero-crossing in an IQ diagram. Fig. 1.6(a) exemplifies such a case. In the conventional polar architecture, this leads to a phase reversal and an abrupt change in the envelope, as depicted in Fig. 1.6(b). To overcome this problem, it is proposed a different scheme in which the envelope is treated as a bipolar signal. Fig. 1.6(c) illustrates how such basic modification alleviates the bandwidth problems mentioned previously. Clearly, there are no abrupt changes in the signals. However, the generation of the required negative-valued envelope, and respective PM signal, cannot be obtained in a simple way. A slightly different approach and more adequate is therefore applied. Hence, if this type of amplifier is thought as a multiplier, an IQ transmitter can be actually implemented based upon the combination of two of these "bipolar transmitters". The most obvious advantage over the classical Cartesian<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>The terms "Cartesian" and "IQ" transmitters will be used interchangeably along the text.

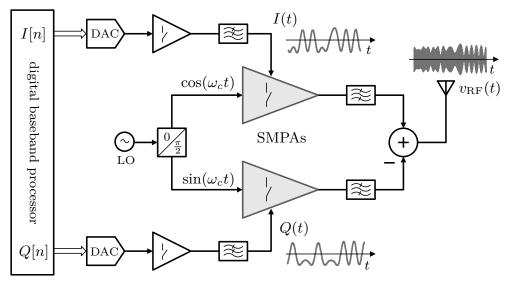

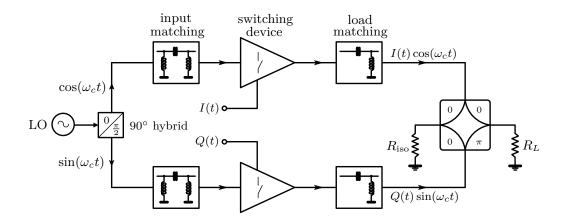

Figure 1.7: Proposed architecture.

transmitter is that now one can employ SMPAs to improve the overall efficiency.

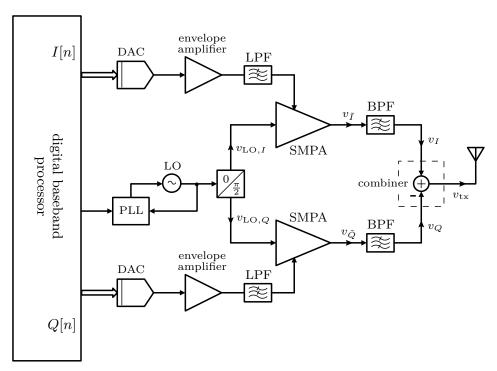

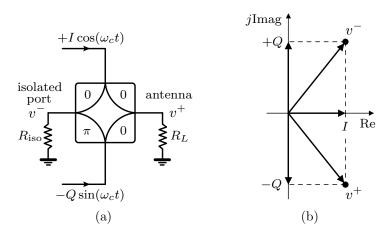

Fig. 1.7 depicts the proposed topology for the C-P transmitter, wherein each bipolar transmitter is driven by single tones in quadrature. Hence, the amplifiers (or power mixers as we might call them) are driven by narrowband signals. These signals have constant amplitude and thus allow the use of SMPA classes. Instead of an envelope signal, the I and Q signals modulate the power-supply of the bipolar amplifiers. This way, the drain modulation is performed by baseband signals that are limited in spectrum due to pulse shaping. As so, the bandwidth requirements of the envelope paths are much more relaxed than in the conventional polar transmitter, which allows an easier implementation of power supplies operating in switching mode. Hence, with this new architecture the bandwidth issues of the common polar transmitter are virtually solved, and low-efficiency of the IQ transmitters is also avoided. Compared to a LINC transmitter, as it will be demonstrated latter, the proposed C-P structure presents some benefits in terms of overall efficiency. It overcomes practical limitations of the LINC when dealing with signals having large PAPRs, an issue that has been restricting its use with modern communication standards.

## 1.3 Original Contributions

In this thesis, the proposed C-P architecture is analyzed at a system level and from a hardware design perspective as well. Two circuit topologies are proposed for the implementation of the C-P transmitter. In short, the main contributions of the present work are the following:

- introduction of a novel architecture, named "C-P transmitter". This architecture consists of a high-level multiplier and envelope modulator. It aims the use of efficient SMPAs, while avoiding typical bandwidth limitations in the envelope amplifiers.

- the structural analysis of the proposed architecture in terms of performance, e.g. efficiency (proven to be advantageous for high B-O), power recycling, and impairments sensitivity.

- proposal of a CMOS circuit for practical realization of the C-P transmitter, comprehensive study of its performance, validation through simulation and comparison against a LINC implemented in the same CMOS process.

- proposal of a new switching topology for the realization of a C-P transmitter for semiconductor technologies other than CMOS. The circuit provides up-conversion of the differential components of time-varying power supplies.

#### 1.4 Outline

Following this introductory chapter, this thesis comprises other five chapters, which can be briefly described next.

• Chapter 2 gives a brief reference on wireless systems and current trends for data improvement. It addresses the fundamental aspects

as well as the latest developments in transmitter technologies and architectures.

- Chapter 3 presents the proposed transmitter architecture on a system level perspective. The system is studied in terms of bandwidth, efficiency and linearity. These characteristics are further compared to the LINC and polar transmitters.

- Chapter 4 describes a circuit topology for implementation of the proposed transmitter architecture using CMOS processes for the active devices. A comprehensive analysis of the circuit is presented, describing the impact of different parameters in the asymmetric performance of the C-P transmitter.

- Chapter 5 presents the study of another circuit for the implementation of the C-P transmitter. The analysis of the circuit includes the derivation of waveforms equations and computation of the electronic components for the circuit. An LDMOS implementation is addressed for its conceptual validation.

- Chapter 6 concludes this thesis with final remarks on the presented research work and a discussion on future work.

# Chapter 2

## Transmitter Architectures

Wireless communication is perhaps the best example of a technology having fast global spreading and development. Today's systems encompass a wide range of easy-to-use RF technologies and services – from GPS and Bluetooth to WiFi and DVB. Numerous developments point towards ubiquitous wireless accesses in future, with device interfaces operating at much higher data-rates. This high-speed communication trend is crucial to achieve real-time responsiveness in wireless services. However, such demands push the linearity requirements to the limits of performance of AM transmitters.

The improvements on the spectral efficiency of wireless communications are dependent on the technical progress at successive levels, i.e. from the RF network system, to the transmitter and receiver architectures, and respective hardware implementations. Briefly, the present chapter focuses on the fundamental aspects related with RF transmitters, in terms of architecture and circuit implementation. It departs from the most conventional transmitter structure, i.e. the IQ transmitter. It then describes other transmitters that, despite being considered as classical architectures (from a historical perspective), they recently gained momentum with the need for high-performance AM systems. A few ways for improving the transmitter front-ends are also described, such as RF circuits for the synthesis of AM signals, as well as the use of digital control on the PA stage.

## 2.1 IQ Transmitters

Most transmitters are based on Cartesian coordinates to transmit digital information. In-phase and quadrature data paths are combined and then amplified by a PA at the end of the transmitter chain. In an IQ transmitter, the RF signal can be described by band-limited I and Q components as

$$x_{\rm RF}(t) = \operatorname{Re}\left\{ [I(t) + jQ(t)] \cdot e^{j\omega_c t} \right\}$$

(2.1)

$$= I(t)\cos(\omega_c t) - Q(t)\sin(\omega_c t) \tag{2.2}$$

For non-constant envelope signals, the combination of I and Q components needs to be amplified by linear PAs. However, in conventional transconductance-mode classes (such as A, AB and B) the efficiency strongly depends on the PAPR. That is, the PA must be designed with reasonable B-O from its maximum output power to ensure that the peak power can be achieved within a linear operation range.

Typically, the maximum drain efficiency will most likely occur at maximum output power. However, since most of time the PA operates at power levels much lower than its maximum, high-PAPR values lead to very reduced power efficiencies. Typical PAPR values for commercial standards are in the order of 3.4 dB for EDGE, 3.1–6.5 dB in W-CDMA, and more than 10 dB for systems using OFDM. When highly-linear PAs are used, the power-added efficiency (PAE) values are below 30–40 % [39, 40].

For a long time, the Cartesian architecture has been the standard technology for RF transmitters. Indeed, even CMOS implementations have adopted the Cartesian transmitter in null-PAPR systems. In such cases, the PA operates in class C or in a saturated AB/B mode. In [41], a fully-integrated solution for GSM (DCS-1800) is presented in a 0.35  $\mu$ m CMOS process, using a differential cascode configuration operating in class C. The PA uses two pairs of very large transistors (9 and 18 mm widths each), to

provide 25 dBm of output power. Another version of the same implementation reaches over 30 dBm of peak output power using off-chip inductors. Other examples can be found in Bluetooth systems with GFSK, for which a linear envelope amplification is not required, but saturated PAs are employed in an IQ transmitter for maximizing the efficiency [42–45].

#### 2.1.1 Doherty Technique

With the increased interest in AM formats, the Doherty technique has been lately revisited. It is perhaps one of the most promising techniques to improve the efficiency in actual IQ transmitters without degrading the linearity. The Doherty technique improves the efficiency of a linear amplifier by adding an auxiliary amplifier to the transmitter. The concept dates back to 1936 [23]. The operation relies on a very interesting principle, which is "load modulation" (or "active load-pull" [46]). Fig. 2.1 shows the classical Doherty topology with two PAs. One is commonly termed as "main amplifier" (or "carrier amplifier") and the other "auxiliar amplifier" (also known as "peak amplifier"). The auxiliar amplifier is normally a class-C amplifier biased at a given voltage below threshold so that only turns on for a specific input level, i.e. the transition point. Depending on the transition point,

Figure 2.1: Doherty amplifier.

Figure 2.2: Operation regions in the Doherty PA.

two operation regimes are defined: full power and B-O. Fig. 2.2 gives a simplified representation of this type of operation. For a classical Doherty, the main amplifier begins to saturate at 1/4 of the PEP, which means 6 dB of B-O. The value of the transition point also dictates the load network characteristics.

The classical Doherty is capable of obtaining significant improvements in the overall efficiency for signals with PAPRs up to  $\sim 6\,\mathrm{dB}$ . Below the transition point, for higher PAPRs, the efficiency drops abruptly. Nonetheless, the efficiency boost along other PAPR ranges is possible by design, arbitrating the turn-on voltage of the auxiliary PA close to the required B-O.

At 10 dB B-O, Iwamoto et al. demonstrated an improvement of 2.6 times over the class B, maintaining the PAE above 39 % within the B-O range [24]. The efficiency enhancement is in fact significant over a simple class-B version. If more than two amplifier stages are used, in spite of the additional complexity there are still meaningful improvements. In the case of a three stage Doherty, with transition points at 1/4 and 1/2 of the PEP, it has been demonstrated an efficiency improvement in the order of 7 times the class B, at a B-O of 12 dB [25].

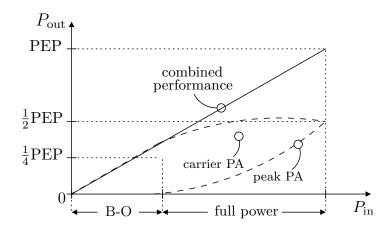

## 2.2 Envelope Tracking

In a linear PA (classes A/AB/B), if the power delivered to the PA is somehow controlled according to the signal to be transmitted, the efficiency can be properly optimized. Fig. 2.3(a) shows an example<sup>1</sup> in which it is clear how the fixed power-supply can have a great impact on power consumption. As shown in figure, the power dissipated is highly dependent on the input signal magnitude and sometimes can be even higher than the output power. Evidently, the power consumption is elevated because the power supply is fixed regardless the output power required. Therefore, when very low-power signals are to be transmitted, the PA has to dissipate all the power that the load does not demand.

Figure 2.3: Illustrative example on ET. (a) High power dissipated due to fixed power supply; (b) Lowering power consumption is achieved by ET.

If the power supply follows a long-term envelope, as it is illustrated in Fig. 2.3(b), then the power consumption can be fairly reduced at the PA. This can be seen as moving the PA gain compression always closer to the output power level. Such technique is commonly known as envelope tracking (ET), or envelope following. It requires a dynamic power-supply (i.e., an envelope amplifier) with its output defined by a slow variation of the envelope, e.g. the average power [13,52] or other shaping function for the drain voltage [51]. This results in a time-varying load for the envelope amplifier, which must be carefully designed to account for any resultant

<sup>&</sup>lt;sup>1</sup>The example given here is merely illustrative. It is not intended to represent any realistic time relationships.

Figure 2.4: ET implementations.

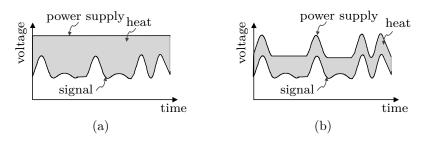

nonlinearity. Fig. 2.4 shows average efficiencies for transmitter implementations in different applications using ET<sup>2</sup>. State-of-the-art performances are in the 30 to 45 % range, decreasing with the PAPR. Here, the PAPR denotes the loading conditions, meaning that a high PAPR implies wide load variations for the envelope amplifier.

To avoid efficiency degradation, almost every ET implementation makes use of a switching-mode configuration as its dynamic power-supply. Compared to a stand-alone PA, the efficiency enhancement due to the ET is in the typical range of 5 to 8% [48,51]. The way the envelope is tracked makes some influence on the results. Instead of an average (slow) tracking, some works employed an ET system with a wide-bandwidth configuration in the envelope amplifier, e.g. [51] and [53]. This implies a fast tracking that almost results in following the envelope instantaneously. In literature, such schemes are usually referred to as wideband ET (WBET) or envelope following [13]. However, the usage of such approach in ET is not always possible. When the signal has a considerable PAPR, it gets difficult to switch between high power values. Hence, to mitigate the efficiency degradation, the power supply has to be adjusted in steps [54]. This results in a very-slow tracking of the envelope, being only suitable for implementations in which the PAPR is in the order of 10 dB or more [53].

<sup>&</sup>lt;sup>2</sup>These results account for the power losses in envelope amplifier and PA as well.

However, ET can be used in conjunction with other approaches. For instance, ET has been implemented with the regulation of the gate voltage (of the PA) according to supply voltage, to optimize the overall efficiency instead of the PA efficiency itself [55]. It turns out that both the envelope shaping function and linearity get improved. Furthermore, in a quite distinct approach, [47], the inclusion of ET in a Doherty amplifier allowed to improve not the efficiency, but the linearity measured by the EVM. In fact, the linearity enhancement by means of an ET approach has been demonstrated using a proper shaping function for the envelope modulator. Based on sweet spots [56,57], the work in [48] uses ET to lower the power-supply level, targeting an optimum IMD<sub>3</sub> for each power level. As a result, for W-CDMA/LTE at PEP, both efficiency and EVM are slightly better than a stand-alone PA solution.

#### 2.3 Polar Transmitter

Polar transmitters are the present renaissance of an amplification method from the 1950s<sup>3</sup>, namely the envelope elimination and restoration (EER) or Kahn technique [59]. With the ever-increasing data-rate in communication standards, the polar transmitters are also receiving increased attention. The possibility to use saturated RF PAs together with non-constant envelope signals makes them suitable for such applications. Using nonlinear PAs, the power efficiency is significantly higher than conventional linear classes used in IQ transmitters.

In polar and EER transmitters, instead of tracking the envelope, the drain is modulated precisely with the amplitude signal. As so, the PA can be used in switching-mode improving its efficiency. In an EER transmitter, the signals are not promptly generated, but require intermediate stages to obtain them. Fig. 2.5 depicts a simple representation for both types of

$<sup>^3</sup>$ It is not generally known but polar modulation techniques had already been proposed in 1915 [58].

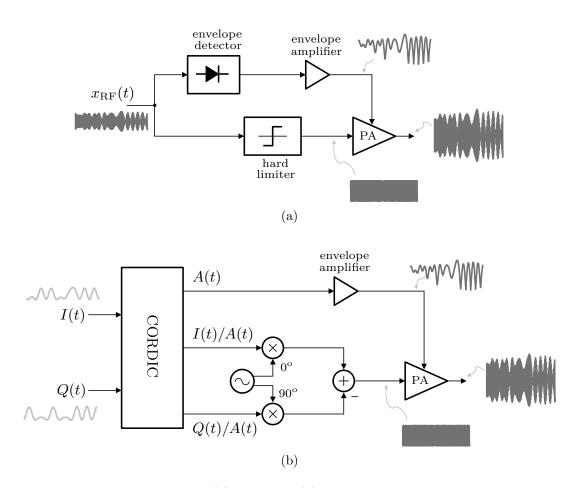

Figure 2.5: (a) EER and (b) polar transmitters.

polar transmitters. In the EER architecture the IQ data is decomposed in amplitude and phase signals by employing a envelope detector and a limiter, respectively. A delay line can also be included in the phase path to synchronize envelope and phase. The signal is then restored and amplified in the PA.

The polar transmitter is a modern version of the EER architecture, in which the IQ data is pulse shaped firstly by digital baseband filters and then transformed into polar form by means of rectangular-to-polar CORDIC algorithms [60]. Fig. 2.5(b) shows the basic diagram of a polar transmitter. Since the PA efficiency is unaffected by the power-supply level, the PAPR impact is mitigated. Currently, the envelope amplifiers are the hot-topic

research for polar transmitters. Note that the overall efficiency is given by

$$\eta_{\rm ovr} = \eta_{\rm env} \times \eta_{\rm PA}$$

(2.3)

where  $\eta_{\text{env}}$  is the efficiency of the envelope amplifier and  $\eta_{\text{PA}}$  is the drain efficiency of the PA. Since the PA itself has the same structure used in constant-amplitude amplification, the drain efficiency should remain nearly unchanged. Consequently, the most important characteristic that dictates the overall efficiency in state-of-the-art implementations is the performance of the envelope amplifier.

#### 2.3.1 Envelope amplifier

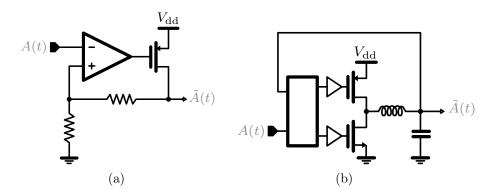

Several approaches have been reported on the design of envelope amplifiers [35, 37, 53, 61–68]. Fig. 2.6(a) depicts a basic circuit used in the envelope amplification, namely the low-dropout (LDO). LDOs are linear regulators with low power-efficiency. Characteristically, an LDO provides wide bandwidth, low-output impedance and high-current driving capability [61]. A CMOS-LDO fully-integrated on a chip (with the PA) has been proposed by Reynaert et al. [37] as an envelope modulator for a polar transmitter. The target of this application is the EDGE (class E3) standard. At the peak power of 27 dBm, using a constant envelope, the efficiency is 30% for the transmitter system comprised of a class-E PA, its driver and envelope modulator. Nonetheless, this is fairly low compared to some state-of-the-art approaches avoiding the usage of LDOs, e.g. 45.3% peak PAE at 27.8 dBm in [62] based on a switching-mode topology.

Alternatively, dc-dc converters based on switching-mode power supply (SMPS) regulators are much more efficient over a wide range of amplitudes. Fig. 2.6(b) shows a very common SMPS, usually known as synchronous buck-converter. The downside of such converter is its limited operation speed. When the SMPS is not sufficiently fast, the elimination of switching noise by the reconstruction filter requires very large values for L and C,

Figure 2.6: Envelope modulators for the polar Tx - (a) LDO [37], (b) synchronous-buck converter.

typically in the order of  $\mu$ H and  $\mu$ F. This greatly increases the delay in amplitude path, which can lead to time misalignment between RF paths leading to spectral re-growth.

When pulse-width modulation (PWM) is used in SMPS, high-sampling rates are required. This leads to increased switching losses and difficulties in driving circuitry. Moreover, EM interference (EMI) can be a problem when PWM is used in buck converters with inductor and free-wheeling diode [35]. Instead, PWM can find its use with envelope signals having reduced bandwidths, such as those in ET transmitters [53]. However, pure ET systems require linear PAs, which then leads to an efficiency tradeoff between PWM-SMPS and linear PAs.

There are alternative approaches in which both fundamental types of converters are used as some kind of mixed topology. Linear-assisted SMPSs employing delta modulation have been reported in [63] and [64]. Delta modulation reduces the number of switching transitions within a given sampling rate when compared to PWM. In [63], a delta-modulated synchronous buck-converter controls the power supply of an LDO, compensated through feedback. A similar scheme is presented in [64], demonstrating its ability to reduce quantization noise due to delta modulation.

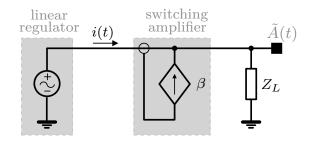

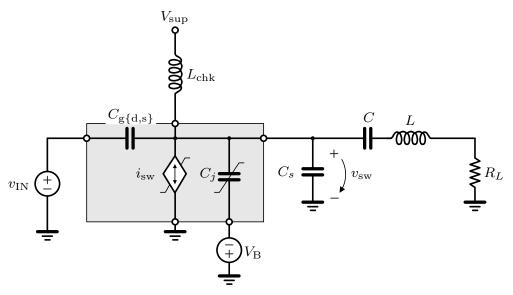

More complex circuits, suitable for wide-band signals, have been implemented using hybrid-switching amplifiers [53,61,62,65]. The concept is

Figure 2.7: Hybrid-switching concept [53, 61, 65].

illustrated in Fig. 2.7. Basically, it uses a SMPS regulated by a linear amplifier. The technique has been used in audio to improve fidelity in class-D amplifiers. In hybrid-SMPSs, feedback of a hysteresis current seems to be the most promising control technique [53,62,67].

Table 2.1 summarizes the results of some more reported works. The envelope amplifier recently published by Choi et al. in [62] can be used for EDGE, W-CDMA and WiMAX. Remarkably, in any of these standards the peak efficiency of the envelope modulator is above 75 %, and the transmitter average efficiency is always higher than 34%. Although the amplitude modulator is built in CMOS 130 nm, the PA is implemented in a different semiconductor technology (InGaP/GaAs HBT). In [67], a hybrid envelope modulator in a 65 nm CMOS process is proposed for a WLAN transmitter. Due to such reduced lengths of the transistors, the envelope modulator is capable of maintaining high-speed switching operation and, as a result, it improves its efficiency about 20 % at 10 dB when compared to a stand-alone AB amplifier. Nonetheless, for the efficiency measurements, the RF-PA has been characterized by a  $5.3 \Omega$  load, hence it admits a perfectly isolated RF-PA with fixed load (which differs considerably from a practical case). For a class-E1 EDGE, about 4W has been achieved for using a standard CMOS process [65]. For the current-sensing feedback, sample-and-hold circuits are used at 40 MHz. To achieve such high output power, the hybrid envelope modulator has been divided into a master-slave configuration.

Envelope modulation using digital techniques are valid alternatives to

23

29

88 %

75%

[67]

[62]

| ref  | peak       | peak  | target       | TOO.               |                    |      |

|------|------------|-------|--------------|--------------------|--------------------|------|

|      | efficiency | (dBm) | nomenclature | $\Delta f$         | $f_c$              | year |

| [7]  | 74%        | 30    | CDMA IS-95   | $1.22\mathrm{MHz}$ | $950\mathrm{MHz}$  | 1999 |

| [61] | 88%        | 34    | EDGE         | $384\mathrm{kHz}$  | $1.88\mathrm{GHz}$ | 2007 |

| [63] | 76%        | 31    | _            | $4\mathrm{MHz}$    | $900\mathrm{MHz}$  | 2007 |

| [66] | 89%        | 33    | W-CDMA       | $3.84\mathrm{MHz}$ | $1.88\mathrm{GHz}$ | 2010 |

802.11g WLAN

WiMAX

$20\,\mathrm{MHz}$

$5\,\mathrm{MHz}$

$2.45\,\mathrm{GHz}$

2009

2009

Table 2.1: Performance summary of some envelope amplifiers reported in literature for different wireless technologies

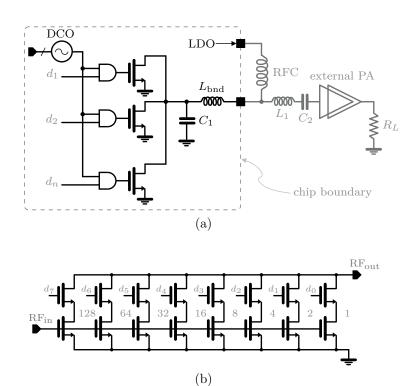

typical dc-dc converters. These schemes have gained particular interest in recent publications. One remarkable approach has been introduced by Shameli et al. in [68]. It relies on a new scheme based on two-point modulation, with the envelope data injected at two different PA inputs. The amplitude signal is applied by means of a digital 7 bit word that controls the current of a differential switched amplifier. The power supply is modulated with a 95% efficiency dc-dc converter, which uses a second-order  $\Delta\Sigma$  modulator. Another interesting approach is the interleaving version of delta-modulation introduced in [35]. An array of modulators acts in parallel with phase-shifted clocks, but all at the same frequency. Therefore, narrow streams of driving pulses are treated as parallel contributions of wider pulses, which alleviates the hardware speed requirements.

## 2.3.2 Main drawbacks of polar transmitters

While in Cartesian modulators the I and Q are band-limited signals, in the polar form the magnitude and phase signals are (theoretically) unlimited in spectrum. The polar representation can be written as follows

$$x_{\rm RF}(t) = \operatorname{Re}\left\{A(t) \cdot e^{j[\omega_c t + \phi(t)]}\right\}$$

(2.4)

$$= \sqrt{I^2(t) + Q^2(t)} \cdot \cos\left[\omega_c t + \phi(t)\right]$$

(2.5)

where A(t) is the time-varying amplitude of the RF signal, and  $\phi(t)$  the

phase given by (1.3), where

$$I(t) = A(t)\cos[\phi(t)] \tag{2.6}$$

$$Q(t) = A(t)\sin\left[\phi(t)\right] \tag{2.7}$$

In a polar transmitter the spectra of amplitude and phase signals are wider when taken separately than the original complex form [35, 69, 70]. The non-limited bandwidth poses serious challenges in the design of phase and amplitude signal paths, and is considered one of the major bottlenecks of present designs. Since both signal paths can be regarded as separate systems, time misalignment contributes to spectral re-growth [36]. As a rule of thumb, the maximum differential delay is in the order of  $\pm 20$  ns per MHz of RF bandwidth. For instance, in 200 kHz EDGE signals a  $\pm 100$  ns delay is tolerable [35, 37].

For signals with zero-crossing trajectories in IQ constellations, such as pulse-shaped W-CDMA signals, a great design effort is required to fulfill the spectrum emission mask. In particular, HSDPA and HSUPA include constellation data points at the IQ origin [40]. Due to the limited bandwidth of practical circuits, the IQ diagram can present a hole since envelope trajectories cannot reach null voltages, thus degrading the EVM [40,71]. This is a growing problem for emerging technologies, such as UTRA-LTE [72] and UWB [38]. For instance, in order to satisfy the EVM required for multiband OFDM of an UWB system, [38] reports that, while amplitude suffices at least 1.1 times, phase bandwidth of a polar transmitter needs to be 7.1 times higher than the bandwidth in an IQ transmitter. About 5 times the RF bandwidth is indicated in [35], assuming perfect synchronization of phase and amplitude signals.

Other contributions to non-ideal performance of polar transmitters include AM-to-AM and AM-to-PM nonlinear behaviors. The analysis of the distortion mechanisms in polar amplifiers has been presented by J. C. Pedro *et al.* in [73]. It has been shown that: AM-to-AM distortion is mainly

caused by the nonlinear characteristic of the envelope modulator; AM-to-PM distortion is a result of residual output carrier modulation due to low power-supply values; and this low-voltage region is quite susceptible to carrier feedthrough. For null amplitude values, corresponding to the IQ origin, the amplifier must present null output. However, some configurations may be less immune to null-supply values and produce undesired output power, lowering efficiency. This kind of leakage is hardly removed since it contains in-band frequency components.

The feedforward is established through  $C_{\rm gd}$ , resulting in adverse effects. In very large transistors, when the AM signal is relatively low, the feedforward currents flowing through  $C_{\rm gd}$  are converted into a voltage level comparable to the envelope signal. Since the phase signal is broadband in frequency, the spectral emission mask is affected [37]. At low-supply modes, AM-to-PM dominates over AM-to-AM distortion, while for high power-supply levels the AM-to-AM distortion can be predominant [73].

The AM-to-AM and AM-to-PM distortion effects require always proper compensation to meet spectrum emission masks. In linear amplifiers, AMto-PM distortion can be compensated through gate capacitance modulation [74]. But in switching-mode PAs, AM-to-PM distortion requires much more complex compensation mechanisms. On one hand, feedback effectively improves the linearity. The main challenge, for instance in case of polar-loop (with the RF feedback of phase/magnitude signals), is the design of a precision receiver capable to operate with wide-bandwidth signals. [75]. Even though, Sowlati et al. [76] implemented a complete polar modulator with excellent results for EVM in GSM/GPRS/EDGE using a  $0.35 \,\mu\mathrm{m}$ BiCMOS process. Another common technique used for linearization is predistortion, but it requires accurate modeling of the PA nonlinear behavior. Recent works have described predistortion studies for EDGE [77,78] including memory effects [70], W-CDMA [79] and multi-mode standards [80]. The main advantage of digital predistortion (DPD) is its implementation in digital baseband processing, which avoids an increased complexity at the RF

circuitry. Due to so many implementation difficulties in hardware, one can say that every transmitter requires DPD to comply with linearity standards of current standards. This is not limited to the polar transmitter, but it is in fact applicable to any other RF architecture.

#### 2.4 LINC

The concept of "outphasing" has been originally conceived in 1935. This technique has been introduced by H. Chireix [28] as a high-efficient modulation system, when power expenses started to be a major concern in operating costs of base stations. Chireix proposed this technique to avoid two typical problems at that time. One problem was the relatively low efficiency of power tubes, when used under linear amplification. The other problem was the alternative itself. That is, anode modulation was challenging because of the low efficiency of time-varying power-supplies. Curiously, inasmuch as radio evolved, some problems remain nearly the same almost eight decades later.

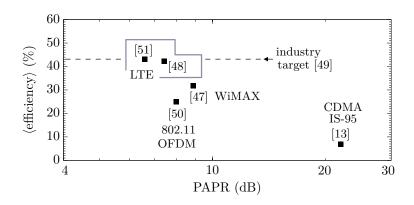

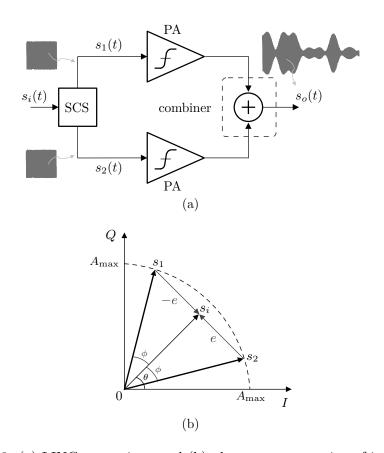

In the outphasing technique, two phase-deviated signals with constant amplitudes are combined to generate AM signals. Fig. 2.8(a) shows the basic representation of a LINC transmitter. Let us admit the generic data signal  $s_i(t)$ , modulated both in amplitude A(t) and phase  $\theta(t)$  as

$$s_i(t) = A(t) \cdot \cos\left[\omega_c t + \theta(t)\right], \qquad 0 \le A(t) \le A_{\text{max}}$$

(2.8)

In a LINC transmitter, this input signal is then split by a signal component separator (SCS) into two constant-envelope signals,

$$s_1(t) = s_i(t) + e(t)$$

(2.9)

$$= A_{\text{max}} \cdot \cos\left[\omega_c t + \theta(t) + \phi(t)\right] \tag{2.10}$$

and

$$s_2(t) = s_i(t) - e(t) (2.11)$$

$$= A_{\text{max}} \cdot \cos\left[\omega_c t + \theta(t) - \phi(t)\right] \tag{2.12}$$

Figure 2.8: (a) LINC transmitter and (b) phasor representation of its signals.

where  $s_1(t) + s_2(t) = 2 \cdot s_i(t)$ . The phase  $\phi(t)$  can be written as

$$\phi(t) = \cos^{-1} \left[ \frac{A(t)}{A_{\text{max}}} \right], \qquad 0 \le \phi(t) \le \pi$$

(2.13)

and  $\theta(t)$  refers to the four-quadrant inverse tangent

$$\theta(t) = \tan^{-1}\left(\frac{Q(t)}{I(t)}\right), \qquad |\theta(t)| \le \pi$$

(2.14)

Fig. 2.8(b) shows e(t), which is the quadrature signal used in equations (2.9) and (2.11) to express the outphased signals. This signal can be written as follows

$$e(t) = j \cdot s_i(t) \cdot \sqrt{\frac{A_{\text{max}}^2}{|s_i(t)|^2} - 1}$$

(2.15)

Since the introduction of the LINC concept, the practical reason preventing its wide-spread use was the implementation of the SCS. Only with

an accurate SCS would be possible to generate the correct phase for the signals. In the seventies, D. Cox brought to life the outphasing technique under the name of LINC [27]. Any signal applied to the SCS could generate the two constant-envelope signals needed to drive the two output amplifiers with the appropriate phases. This further extended the concept of outphasing to generalized schemes with quadrature modulation.

#### 2.4.1 Generation of outphasing signals

The LINC transmitter is generally seen as a promising candidate for highly-linear highly-efficient transmitters. However, in practice, the LINC transmitter still finds stringent constraints in its application. The SCS remains one of such problems. Note that, the system required to obtain  $s_1(t)$  and  $s_2(t)$  signals represents a process that must be capable of performing very precise AM-to-AM and AM-to-PM distortions.

Two basic approaches exist for implementation of the SCS, namely: i) the phase-modulation method, and ii) in-phase/quadrature method. Alternatives to these two exist in literature, but are less abundant and require complex circuits [81, 82] – although with the advantage of not requiring phase modulators.

Earlier versions of the phase-modulation method were entirely analog [27, 83]. These basically consisted of arc-cosine (or arc-sine) phase-modulators operating at an intermediate frequency or RF. The digital version of an SCS is preferred instead. In fact, the great advances on digital computation are responsible for reviving the actual interest on an ancient technique used for AM broadcasting. Digital processing presently available allows cost-effective implementations in communication systems with flexible compensation performed in real time [84]. As so, digital implementations of the phase-modulation method are already feasible for W-CDMA signals, both in field-programmable gate arrays (FPGAs) [85,86] and digital signal processors (DSPs) [86].

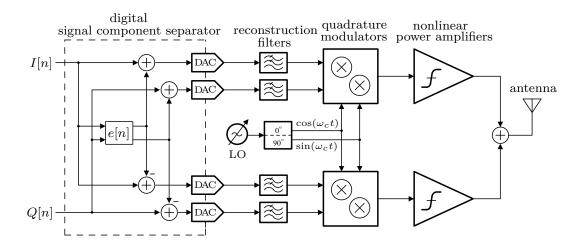

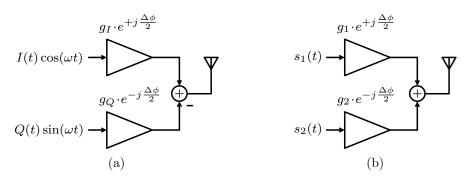

Figure 2.9: LINC with digital SCS implemented by in-phase/quadrature method.

The in-phase/quadrature approach for the SCS is based on generating the quadrature signal e(t) – Fig. 2.8(b). Throughout the quadrature signal and the input signal itself, the required out-phased signals can be produced – Fig. 2.9. Several nonlinear operations are required to compute e(t). Some systems rely on baseband digital processing implemented in a DSP, assisted by look-up tables (LUTs) to minimize division and square-root operations [87,88]. The LUT is used to store values of a limited number of quadrature signals. The main drawbacks associated with a true-digital implementation are related to high-oversampling rates, which impose the level of power consumption and required bandwidth. The SCS digital signals, generated at baseband, are followed by digital-to-analog converters (DACs), reconstruction filters and then by quadrature up-converters. Mismatches on these components also limit the overall performance of a digital-based solution.

Several analog implementations of the in-phase/quadrature method exist in literature [89–91]. The major limitation in these analog approaches is the accuracy needed to deal with less-relaxed linearity requirements. For instance, a potential problem for the envelope signal crossing the origin (of the IQ constellation) is due to the difficulties in generating the quadrature signal e(t) [92]. The signal e(t) is typically obtained through implemen-

tation of a variable-gain amplifier (VGA), and when  $|s_i(t)| \to 0$  in (2.15), the gain of the VGA should be infinite, which is not feasible in practice. This also explains why some implementations were validated through  $\pi/4$ -shifted DQPSK, which are modulation schemes designed to avoid IQ zero crossings [90], or simply by preventing the signal to have the null value as minimum magnitude [89,93].

#### 2.4.2 Effect of path impairments

Ideally, in the LINC transmitter, the outphased signals cancel out any nonlinearity at the output. That is, the quadrature signal e(t) in each branch is supposedly eliminated at power combining. Consider the gain imbalance  $\Delta g$  and phase imbalance  $\Delta \phi$  at one of the branches. After combining both signals, the output is given by

$$s_o(t) = s_1(t) + s_2(t) = s_i(t) \cdot (2 + \Delta g) \cdot e^{j\Delta\phi}$$

$$+ e(t) \cdot \left[ (1 + \Delta g)e^{j\Delta\phi} - 1 \right]$$

(2.16)

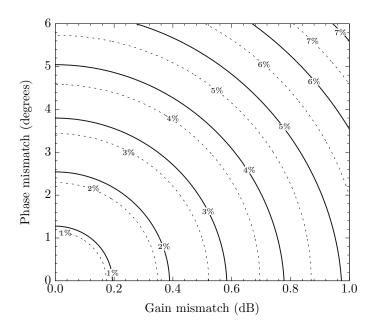

It can be concluded from (2.16) that inherent imbalances between the two RF branches lead to distortion in a LINC transmitter [94, 95]. This distortion widens the radiated power along the frequency spectrum, increasing the adjacent channel interference (ACI) [96]. Particularly in the case of systems with high-spectral efficiencies, such as 64-QAM or other high-order modulations, it has been shown that the LINC is very sensitive to path imbalances [97].

Different nonlinear behaviors of the pair of amplifiers can affect distortion at the output. If similar highly-nonlinear PAs are used, the overall performance is not significantly affected. But, if less similar PAs are available, then linear PA regimes are preferable over SMPSs [95], hence directly affecting the overall efficiency. The digital SCS can also be responsible for ACI degradation due to quantization. Nonetheless, small words are required for

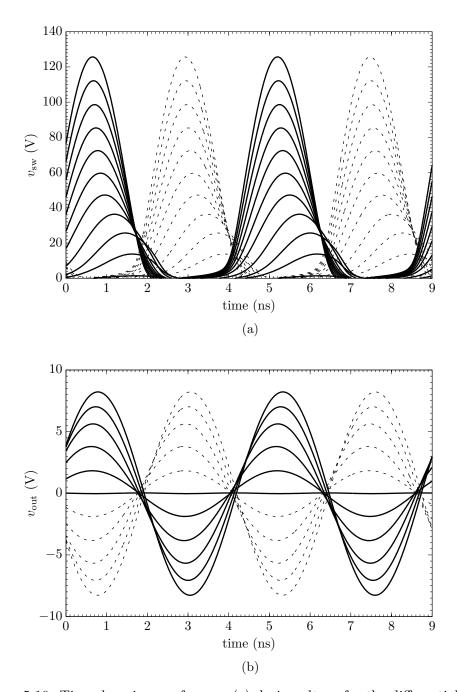

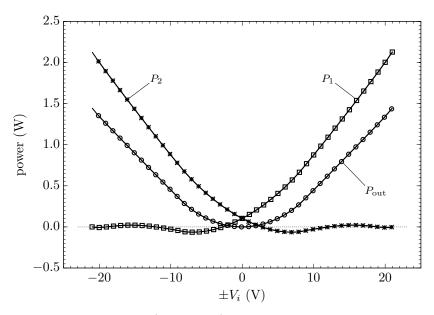

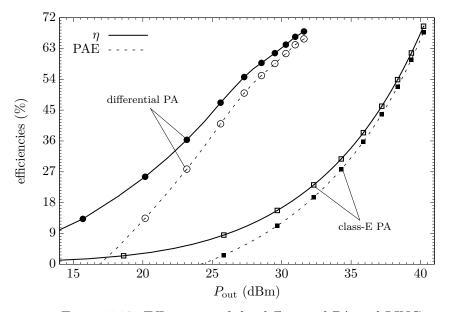

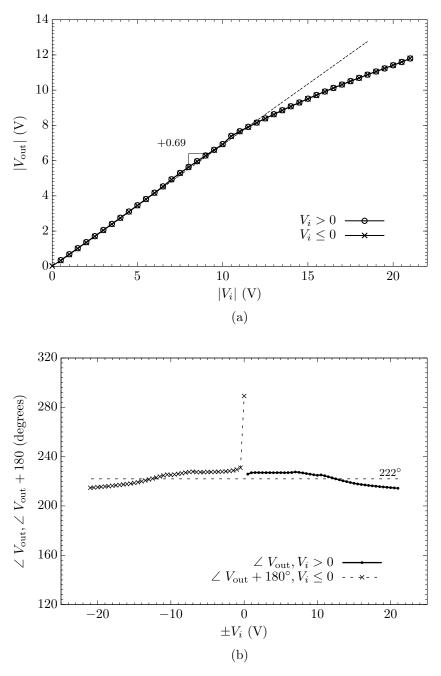

the SCS to meet with reasonable low-levels of ACI [98]. Other sources of ACI degradation created by the digital SCS architecture include the reconstruction filters. These filters are used to eliminate the sampling images. However, its effect is seen in the ripple produced in the driving signals of the PA, when such signals are supposed to be constant [99]. The ACI can also be degraded due to non-ideal quadrature modulators [100,101]. These effects are difficult to compensate, demanding quite complex systems [102].