# ADVANCED FAST HVDC CIRCUIT BREAKERS

# ADVANCED FAST HVDC CIRCUIT BREAKERS

Dissertation

submitted to the Faculty of Engineering of University of Porto, in partial fulfilment of the requirements for the degree of Doctor of Philosophy

### Ataollah MOKHBERDORAN

Electrical Engineering, Bachelor's Degree, Iran University of Science and Technology Electrical Power Engineering, Master's Degree, Azarbaijan University of Shahid Madani Supervisor:

| Prof. Adriano da Silva Carvalho,                                                                                                                                                                                                                                  | Faculdade de Engenharia, Universidade do Porto                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Co-supervisors:<br>Prof. Helder Filipe Duarte Leite,<br>Dr. Nuno Filipe Gonçalves da Silva,                                                                                                                                                                       | Faculdade de Engenharia, Universidade do Porto<br>Efacec Energia, Máquinas e Equipamentos Eléctricos                                                                                                                                                                                                                                    |

| Jury President:<br>Prof. José Alfredo Ribeiro da Silva Matos,                                                                                                                                                                                                     | Faculdade de Engenharia, Universidade do Porto                                                                                                                                                                                                                                                                                          |

| Jury Members:                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                         |

| Prof. Jun Liang,<br>Prof. João Jose Esteves Santana,<br>Prof. Júlio Manuel de Sousa B. Martins,<br>Prof. Rui José Oliveira Pestana,<br>Prof. Carlos João Rodrigues Costa Ramos,<br>Prof. Maria Teresa Costa P. d. S. de Leão,<br>Prof. Adriano da Silva Carvalho, | School of Engineering, Cardiff University<br>Técnico Lisboa, Universidade de Lisboa<br>Escola de Engenharia, Universidade do Minho<br>Redes Energéticas Nacionais, SGPS, S.A (REN)<br>Faculdade de Engenharia, Universidade do Porto<br>Faculdade de Engenharia, Universidade do Porto<br>Faculty of Engineering of University of Porto |

©2017 A. Mokhberdoran. All rights reserved.

Then of the Thee in Me who works behind The Veil of Universe I cried to find A Lamp to guide me through the darkness; and Something then said - 'An Understanding blind.'

Omar Khayyam, Iranian Mathematician, Philosopher, and Poet, 1048-1131.

Translated by Edward FitzGerald, British Poet and Writer, 1809-1883.

To my wife, Fatemeh,

for her love, her patience, and her faith. To my parents, Naiemeh & Rahim,

for guiding me, supporting me, and for missing me.

$\mathcal{E}$

## Summary

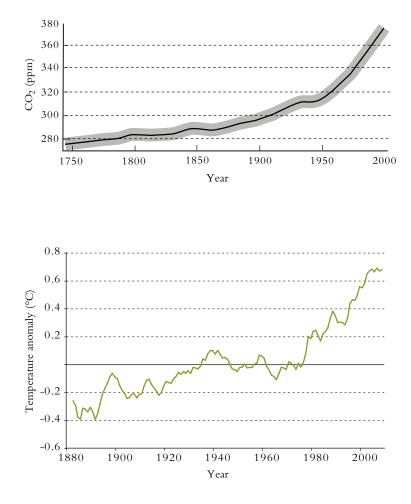

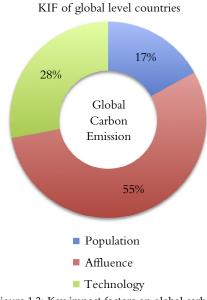

Climate change will be one of the biggest threatening challenges for mankind in the following decades. This phenomenon is caused by global temperature rise on the surface of Earth which is called global warming. The main reason for global warming is the increasing emissions of man-made greenhouse gases (GHGs) in the atmosphere. Increasing population of the world will increase the total consumption and demand for energy. More population together with the growing economy in the developing countries will increase the amount of GHG emissions in the future if strict measures are not taken.

In order to mitigate the GHG emissions, the demanded energy must be supplied from carbon-free resources such as hydro, wind, solar and etc. European Union (EU) as the third producer of GHG plays a significant role in preventing the destructive consequences of the climate change from happening. EU is now leading the world in harvesting green energy from offshore and onshore wind farms.

Due to the geographical location, average distance and size of newly constructed and planned offshore wind farms, High Voltage Direct Current (HVdc) has been employed as the power transmission technology by the project developers. The interconnections between the HVdc converters and offshore wind farms can form a Multi-terminal HVdc (MT-HVdc) grid. The MT-HVdc grid can reduce the effects of fluctuation in renewable energy generation, enhance the security of supply and improve the reliability.

Although a European offshore MT-HVdc grid connecting offshore wind farms to shore could provide significant financial, technical and environmental benefits to the European electricity market, it has not been yet realized due to a few technical drawbacks. The main obstacle to the establishment of an MT-HVdc grid is immaturity of HVdc current interrupting technologies. The existing HVdc circuit breaker solutions suffer from either long interruption time, high conduction losses or high implementation cost.

Therefore, the main objective of this thesis is to propose and study improved HVdc circuit breaker topologies. The main challenges associated with the solid-state and hybrid dc circuit breakers include the need for a large number semiconductor switches in their main breaker branch and large surge arresters to limit the transient recovery voltage and absorb the system energy. This thesis proposes novel approaches for improving the performance if HVdc circuit breakers in order to tackle the mentioned problems. Furthermore, this thesis proposes a new type of dc circuit breaker with additional functionality as a current flow controller.

A comprehensive literature review on different types of HVdc circuit breakers including electromechanical, solid-state and hybrid dc circuit breakers has been carried out. The dc circuit breakers have been classified in several categories. The superiorities of each topology have been highlighted and the main drawbacks of each dc circuit breaker type have been identified.

In order to reduce the conduction power losses of the solid-state dc circuit breaker a couple of topological changes have been proposed and studied. Firstly, the semiconductor switches of the solid-state dc circuit breaker are connected unidirectionally. This approach halves the number of series connected switches. Secondly, a new current releasing branch is proposed and employed instead of the surge arrester branch. The new current releasing branch limits the transient recovery voltage across the solid-state dc circuit breaker more effectively and reduce the number of series connected switches. Therefore, the conduction power losses of the solid-state dc circuit breaker can be reduced significantly using the proposed scheme.

Unidirectional HVdc circuit breakers are technically attractive due to the less number of switches and peripheral circuitries and also the reduced requirement for cooling systems. A unidirectional protection strategy is proposed for the protection of MT-HVdc grid using the unidirectional dc circuit breakers. The proposed strategy has been validated through the integration of unidirectional hybrid dc circuit breaker into the MT-HVdc grid. In addition, the proposed unidirectional solid-state dc circuit breaker is integrated to the MT-HVdc grid and the results are compared with the typical solutions.

Another identified issue is related to the requirement for employment of parallel branches in the structure of main breaker unit and large surge arrester branch in the hybrid dc circuit breaker structure. A superconducting fault current limiter unit is integrated into the hybrid dc circuit breaker and its impact on the current interruption capability and the amount of absorbed energy by the surge arresters are assessed. The results show a significant reduction in the maximum fault current interruption capability of the hybrid dc circuit breaker after employment of superconducting fault current limiter. Moreover, the amount of absorbed energy by the surge arresters is notably reduced. Furthermore, the size of the current limiting inductor can be reduced without increasing the current interruption capability.

The number of required semiconductor switches by the hybrid dc circuit breaker can be comparable to a converter station in some HVdc configurations. A novel concept of multi-port hybrid dc circuit breaker is proposed for offshore MT-HVdc applications. The proposed hybrid dc circuit breaker has n ports and can substitute n - 1 hybrid dc circuit breakers at a dc node with one converter station and n - 1 adjacent transmission lines. The proposed scheme can mitigate the number of semiconductor switches and the size of surge arresters dramatically, particularly when the number of adjacent transmission lines increases.

The power flow control is also one of the identified challenges in the realization of a complex form of MT-HVdc grid called meshed HVdc grid. In order to control the power flow in the meshed HVdc grids, additional power flow controller devices are required. A novel three-port hybrid dc circuit breaker is proposed to address both protection and power flow problems in meshed HVdc grids. This circuit breaker can connect a power converter station with two adjacent transmission lines. The proposed hybrid dc circuit breaker possesses an embedded dual H-bridge current flow controller and can control the power flow in one of the adjacent transmission lines. This method can reduce the number of required semiconductor switches and the size of surge arresters, significantly.

Since this thesis proposes a few novel concepts in dc circuit breaker field, a notable amount of future work can be planned. Briefly, the medium voltage implementation and tests of the proposed surge-less dc circuit breaker, lab-scale prototype development of multi-port hybrid dc circuit breaker, and lab-scale prototype implementation of the current flow controlling hybrid dc circuit breaker can be listed as some of the future experimental works. In addition, the theoretic analysis will continue to cover the current commutation process in the multi-port hybrid dc circuit breakers, failure modes of hybrid dc circuit breaker, common failure modes of multi-port and current flow controlling hybrid dc circuit breaker and reliability analysis of the multi-port and the current flow controlling hybrid dc circuit breakers.

### Sumário

As alterações climáticas serão, nas próximas décadas, um dos mais ameaçadores desafios que a humanidade enfrentará. Na sua origem está o aumento global da temperatura à superfície do planeta, fenómeno habitualmente designado de aquecimento global. A principal causa do aquecimento global é o crescente aumento das emissões de gases de efeito de estufa (GEE) para a atmosfera, com origem sobretudo na atividade humana. O aumento da população, conjugado com o crescimento das economias, sobretudo nos países em vias de desenvolvimento, traduzir-se-á no curto/médio prazo num aumento da procura de energia, o que terá como consequência certa, no caso de não serem tomadas as medidas adequadas para o seu controlo, o aumento das emissões de GEE.

De forma a mitigar as emissões de GEE, o aumento da procura de energia deverá ser satisfeita a partir de fontes renováveis, livres de carbono, tais como as energias hídrica, eólica ou solar. Detendo a terceira posição a nível mundial no que diz respeito às emissões de GEE, a União Europeia (UE) tem um papel determinante na prevenção do aquecimento global, cujas consequências podem ser devastadores. A UE é atualmente líder mundial na produção de energia verde com origem eólica, tendo centrais instaladas tanto em terra como ao longo da plataforma marítima continental.

Devido à sua posição geográfica na plataforma marítima continental, à distância média a terra e ao tamanho dos parques eólicos já construídos e projetados, a opção escolhida para transportar a energia neles produzida tem sido a alta tensão em corrente contínua, HVdc na sigla inglesa. A constituição de uma rede HVdc Multi-terminal (MT-HVdc), englobando vários parques eólicos localizados na plataforma marítima continental, pode contribuir para a redução da flutuação na produção associada a este tipo de energia, melhorando o aprovisionamento e a fiabilidade da rede de abastecimento. Apesar de apresentar consideráveis vantagens a nível técnico e económico e, consequentemente, benefícios a nível ambiental, a concretização deste objetivo não tem sido fácil, sobretudo devido a limitações técnicas. A principal dificuldade prende-se com a imaturidade da tecnologia associada aos disjuntores para HVdc. As soluções atualmente existentes apresentam limitações, nomeadamente no que diz respeito aos tempos de abertura elevados e às perdas em condução, para além do elevado custo de implementação.

O objetivo principal desta tese é o de propor novas soluções tendo em vista a melhoria das topologias dos disjuntores para HVdc. Os principais desafios associados aos disjuntores baseados em semicondutores ou disjuntores de híbridos prendem-se com a necessidade de incluir um elevado número de comutadores no ramo principal do disjuntor, assim como um número elevado de supressores de sobretensões, por forma a limitar o transitório de tensão e a absorver a energia do sistema. A tese propõe soluções inovadoras para melhorar o desempenho dos disjuntores para HVdc com o objetivo minorar os problemas descritos. Para além disso, é ainda proposto um novo tipo de disjuntor para HVdc, com funcionalidades adicionais, nomeadamente um controlador de intensidade da corrente elétrica.

Após uma ampla revisão bibliográfica que incluiu diferentes tipos de disjuntores para HVdc - eletromecânicos, de estado sólido e híbridos, estes foram classificados por categoria, tendo-se identificado as vantagens apresentadas por cada topologia e os problemas associados a cada tipo.

Com o objetivo de reduzir as perdas em condução associadas aos disjuntores de estado sólido, foram

estudadas e propostas algumas alterações de ordem topológica. A primeira delas prende-se com a unidirecionalidade da condução, medida que permite a redução para metade do número de comutadores ligados em série. Em segundo lugar, é proposta a criação de um ramo alternativo para desviar a corrente em alternativa ao ramo utilizado para suprimir sobretensões. O novo ramo limita a amplitude do transitório de tensão aplicado ao disjuntor de estado sólido de forma mais eficiente, reduzindo igualmente o número de comutadores ligados em série. Desta forma, as perdas de condução do disjuntor de estado sólido podem ser significativamente reduzidas.

Os disjuntores unidirecionais para HVdc são tecnicamente atrativos devido ao menor número de comutadores e circuitos periféricos necessários e, consequentemente, menores requisitos em termos do sistema de arrefecimento associado. A estratégia proposta de proteção unidirecional para redes MT-HVdc suportada por disjuntores unidirecionais para HVdc foi validada com a integração de um disjuntor unidirecional híbrido para HVdc numa rede MT-HVdc, sendo os resultados obtidos comparados com outras soluções já conhecidas.

Outro dos problemas identificados prende-se com a utilização de ramos em paralelo com o ramo principal do disjuntor e no ramo supressor de sobretensões que fazem parte da estrutura do disjuntor dc híbrido. Uma unidade supercondutora, limitadora da corrente de falha foi integrada no disjuntor dc híbrido, tendo sido avaliado o seu impacto na capacidade de corte do disjuntor e na energia absorvida pelos supressores de sobretensões. Os resultados mostram uma redução significativa da corrente de falha. Acresce também que a quantidade de energia absorvida pelos supressores de sobretensões é notavelmente reduzida, ao passo que o tamanho da bobine limitadora de corrente pode ser reduzida sem comprometer a capacidade de corte do disjuntor.

O número de comutadores de estado sólido do disjuntor de híbrido é comparável ao número de comutadores de um conversor de potência para HVdc. Um novo conceito para disjuntor dc híbrido multiporta é proposto para aplicações MT-HVdc localizadas na plataforma marítima continental. Este disjuntor inclui n portas e pode substituir n-1 disjuntores de híbridos existentes num nó de constituido por um conversor de potência e n-1 linhas de transmissão adjacentes. O esquema proposto mitiga o número de comutadores de estado sólido e o tamanho dos supressores de sobretensões de forma dramática, particularmente se existir um aumento no número de linhas de transmissão adjacentes. O controlo do trânsito de potência é também um dos desafios identificados na conceção de um sistema MT-HVdc de maior complexidade, denominado malha de redes MT-HVdc. O controlo do trânsito de potência nesta malha de redes MT-HVdc requere controladores adicionais. Como forma de colmatar esta necessidade, é proposto um novo disjuntor híbrido de de três portas, o qual suporta funções de proteção e outras relacionadas com o trânsito de potência em malha de redes MT-HVdc. Este disjuntor, que inclui no seu seio um controlador de trânsito de corrente suportado por duas pontes H, permite interligar um conversor de potência a duas linhas de transmissão adjacentes, sendo capaz de controlar o trânsito de potência numa dessas linhas. Este método reduz o número de comutadores necessários e o tamanho dos supressores de sobretensões de forma significativa.

Dado que esta tese propõe vários conceitos inovadores na área dos disjuntores dc, uma quantidade apreciável de trabalho futuro pode ser desde já identificado. De forma breve, destaca-se a implementação e teste do disjuntor proposto para média tensão sem supressor de sobretensões e o desenvolvimento de um disjuntor dc híbrido multiporta e de um protótipo do disjuntor dc híbrido capaz de controlar o trânsito de potência, ambos em escala laboratorial. Para além disto, a continuação da análise teórica incidirá no processo de comutação de corrente nos disjuntores dc híbridos multiporta, na identificação dos modos de falha do disjuntor dc híbrido e do disjuntor dc híbrido multiporta controlado por corrente e na análise da fiabilidade do disjuntor dc híbrido multiporta controlado por corrente.

# Contents

| Ι  | Intr                                          | oduction & Literature Review                                                                                                                                                                                                                                                                                                                                           |

|----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Intr                                          | oduction                                                                                                                                                                                                                                                                                                                                                               |

|    | 1.1<br>1.2<br>1.3<br>1.4                      | General Background                                                                                                                                                                                                                                                                                                                                                     |

| 2  | Lite                                          | rature Review 1                                                                                                                                                                                                                                                                                                                                                        |

|    | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Voltage Source Converters Under dc Fault112.1.1Conventional Voltage Source Converters112.1.2Half-Bridge Modular Multilevel Converter142.1.3Fault Tolerant Power Converters14dc Circuit Breakers202.2.1Electromechanical dc Circuit Breakers202.2.2Solid-state dc Circuit Breakers202.2.3Hybrid dc Circuit Breakers32.2.4Current Limiting dc Circuit Breakers3Remarks34 |

| II | Su                                            | rge-less dc Circuit Breaker & its Application in MT-HVdc 4                                                                                                                                                                                                                                                                                                             |

| 3  | Surg                                          | e-less dc Circuit Breaker 4.                                                                                                                                                                                                                                                                                                                                           |

|    | 3.1<br>3.2                                    | Transient Recovery Voltage       4         3.1.1 Definition       4         3.1.2 Typical Solution       4         Proposed Surge-less dc Circuit Breaker       5         3.2.1 Topology       5         3.2.2 Operation Principles       5                                                                                                                            |

|    | 3.3                                           | Theoretic Analysis       56         3.3.1       Charging Mode       56         3.3.2       Fault Interruption Mode       66         3.3.3       Power Losses       66         3.3.4       Bipolar System       66         3.3.5       Symmetric Monopole System       66                                                                                               |

|     | 3.4  | Detailed Design Process                                                                                                                                                                |     |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |      | 3.4.2 Current Limiting Inductor                                                                                                                                                        |     |

|     |      | 3.4.3 Discharging Branch                                                                                                                                                               |     |

|     |      | 3.4.4 Charging Branch                                                                                                                                                                  |     |

|     | 3.5  | Computational Analysis                                                                                                                                                                 |     |

|     |      | 3.5.1 Verification                                                                                                                                                                     |     |

|     |      | 3.5.2 Conceptual Design Example                                                                                                                                                        |     |

|     |      | 3.5.3 Detailed Simulation Study                                                                                                                                                        |     |

|     | 3.6  | Lab-scale Prototype                                                                                                                                                                    | 124 |

|     | 3.7  | Conclusion                                                                                                                                                                             | 128 |

| 4   | Uni  | directional Protection of MT-HVdc Grid                                                                                                                                                 | 129 |

|     | 4.1  | Typical Protection Strategy                                                                                                                                                            | 131 |

|     |      | 4.1.1 <i>dc Bus Fault</i>                                                                                                                                                              | 131 |

|     |      | 4.1.2 Transmission Line Fault                                                                                                                                                          | 132 |

|     | 4.2  | Unidirectional Protection Strategy                                                                                                                                                     |     |

|     |      | 4.2.1 <i>dc Bus Fault</i>                                                                                                                                                              |     |

|     |      | 4.2.2 Transmission Line Fault                                                                                                                                                          |     |

|     | 4.3  | Application of Unidirectional Hybrid dc Circuit Breakers in Protection of MT-HVdc Grid                                                                                                 |     |

|     |      | 4.3.1 Typical and Unidirectional Hybrid dc Circuit Breaker                                                                                                                             |     |

|     |      | 4.3.2 Models                                                                                                                                                                           |     |

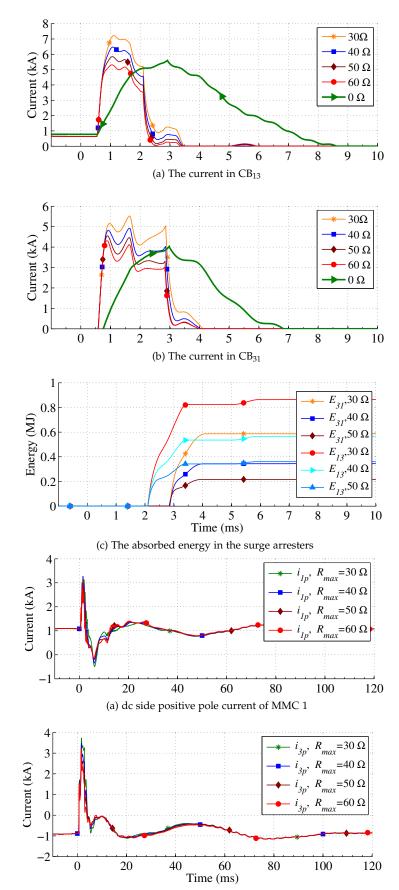

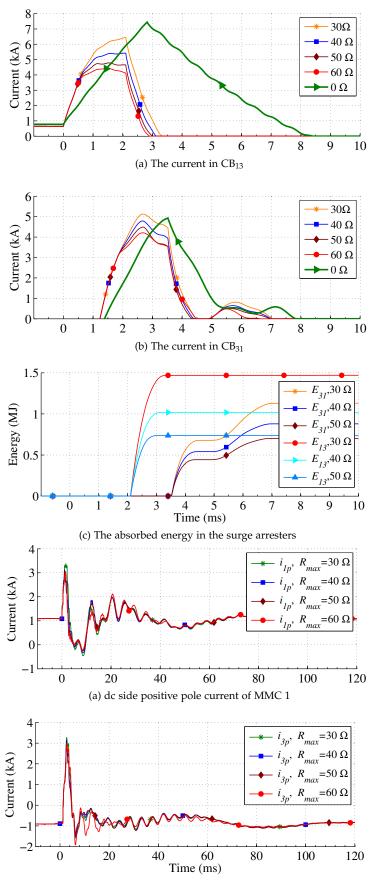

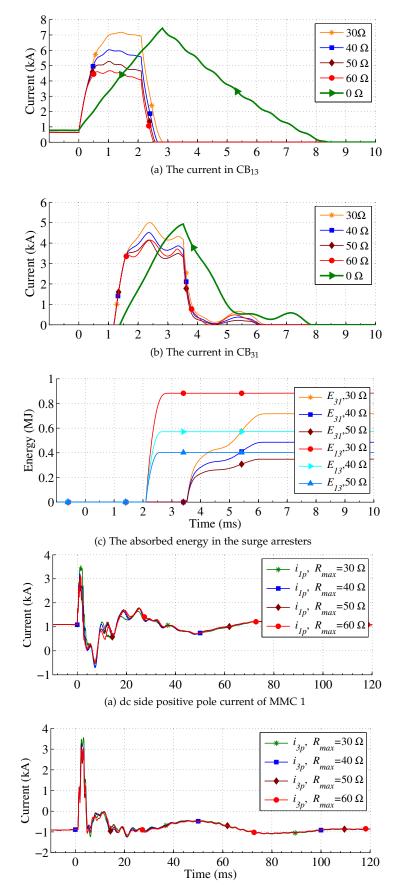

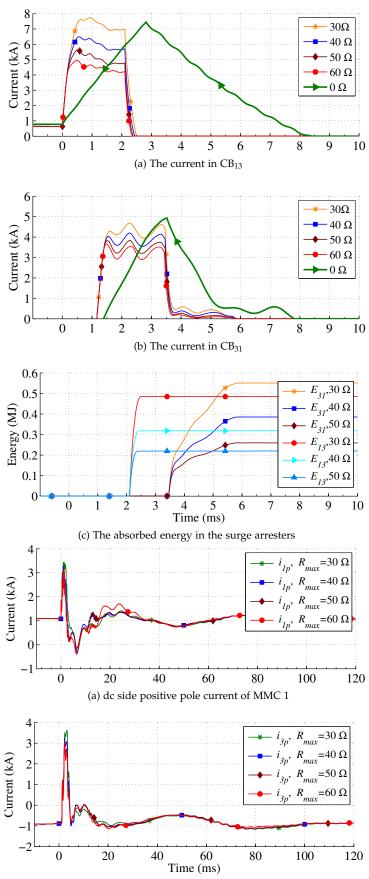

|     |      | 4.3.3 Simulation Results                                                                                                                                                               |     |

|     |      | 4.3.4 Impact on the HCB Current Interruption Capability                                                                                                                                |     |

|     |      | 4.3.5 Impact on the Surge Arrester Energy Rating                                                                                                                                       |     |

|     |      | <ul> <li>4.3.6 Impact on the Converters</li> <li>4.3.7 Impact on the Number of Required Semiconductor Switches</li> </ul>                                                              |     |

|     | 4.4  | 4.3.7 Impact on the Number of Required Semiconductor Switches                                                                                                                          |     |

|     | 4.4  | 4.4.1 The CRCB Integration into the MT-HVdc Grid                                                                                                                                       |     |

|     |      | 4.4.2 Models                                                                                                                                                                           |     |

|     |      | 4.4.3 Simulation Results                                                                                                                                                               |     |

|     |      | 4.4.4 Impact on the Current Interruption Capability                                                                                                                                    |     |

|     | 4.5  | Conclusion                                                                                                                                                                             |     |

|     |      |                                                                                                                                                                                        |     |

| III | Γ Fi | ault Current Limiting dc Circuit Breaker                                                                                                                                               | 161 |

| 5   |      | lt Current Limiting Hybrid dc Circuit Breaker                                                                                                                                          | 163 |

|     | 5.1  | Fault Current Limiting Hybrid dc Circuit Breaker         Madula                                                                                                                        |     |

|     | 5.2  | Models                                                                                                                                                                                 |     |

|     |      | 5.2.1 Test System                                                                                                                                                                      |     |

|     |      | 5.2.2       Superconducting Fault Current Limiter Model         5.2.3       dc Circuit Breaker Model                                                                                   |     |

|     |      | 5.2.5 <i>ac Circuit Breaker Model</i>                                                                                                                                                  |     |

|     | 5.3  | 5.2.4       Protection System Model                                                                                                                                                    |     |

|     | 5.5  | $5.3.1  t_{d2} < t_{tr} \text{ and } I_{ff2} < I_{peak1} \qquad \dots \qquad $ |     |

|     |      | 5.3.2 $t_{d2} > t_{tr}$ and $I_{ff2} > I_{peak1}$                                                                                                                                      |     |

|     |      | 5.3.3 $t_{d2} > t_{tr}$ and $I_{ff2} < I_{peak1}$                                                                                                                                      |     |

|     |      |                                                                                                                                                                                        | 107 |

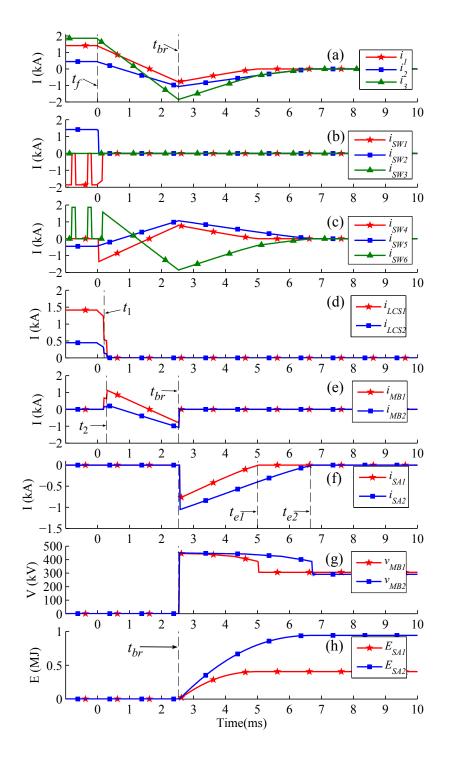

| 5.4 | Simulation Results                                           |

|-----|--------------------------------------------------------------|

|     | 5.4.1 System Without Superconducting Fault Current Limiter   |

|     | 5.4.2 System With Superconducting Fault Current Limiter      |

| 5.5 | Remarks on Application                                       |

| 5.6 | Sensitivity Analysis                                         |

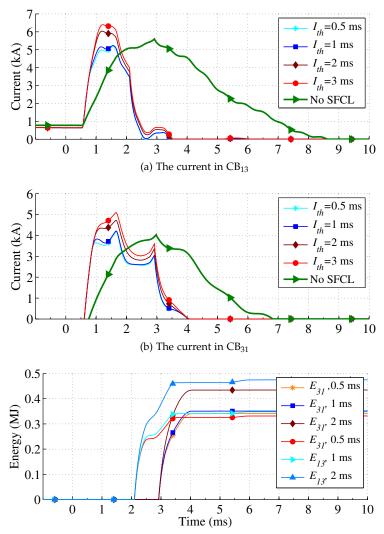

|     | 5.6.1 Superconducting Fault Current Limiter Transition Time  |

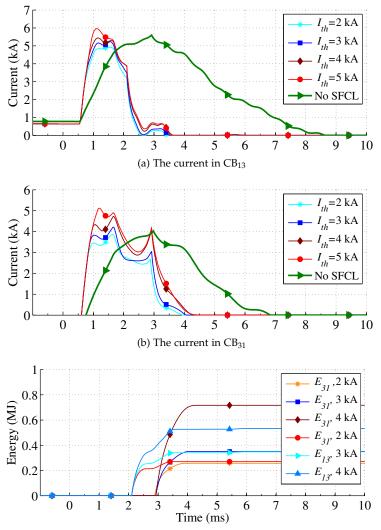

|     | 5.6.2 Superconducting Fault Current Limiter Critical Current |

| 5.7 | Conclusion                                                   |

### IV Multi-port HVdc Circuit Breakers

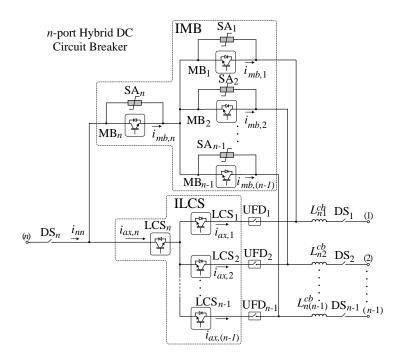

| 6 | Mul  | ti-port Hybrid dc Circuit Breaker                       | 187 |

|---|------|---------------------------------------------------------|-----|

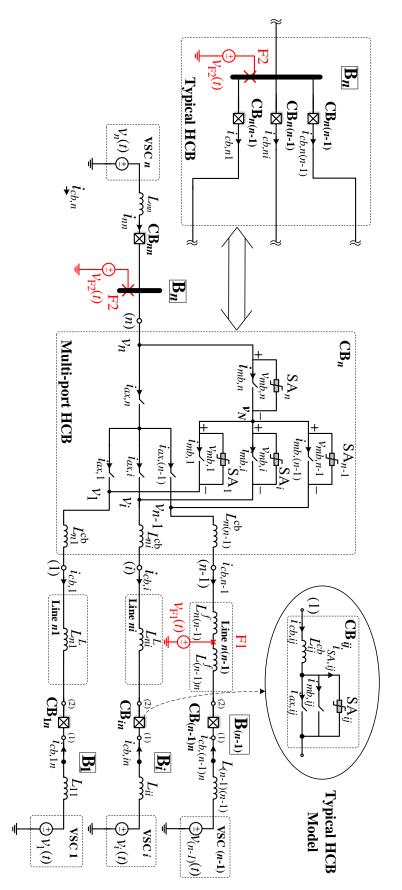

|   | 6.1  | Multi-port Hybrid dc Circuit Breaker                    | 188 |

|   |      | 6.1.1 Basic Representation                              |     |

|   |      | 6.1.2 Mp-HCB Topology                                   | 188 |

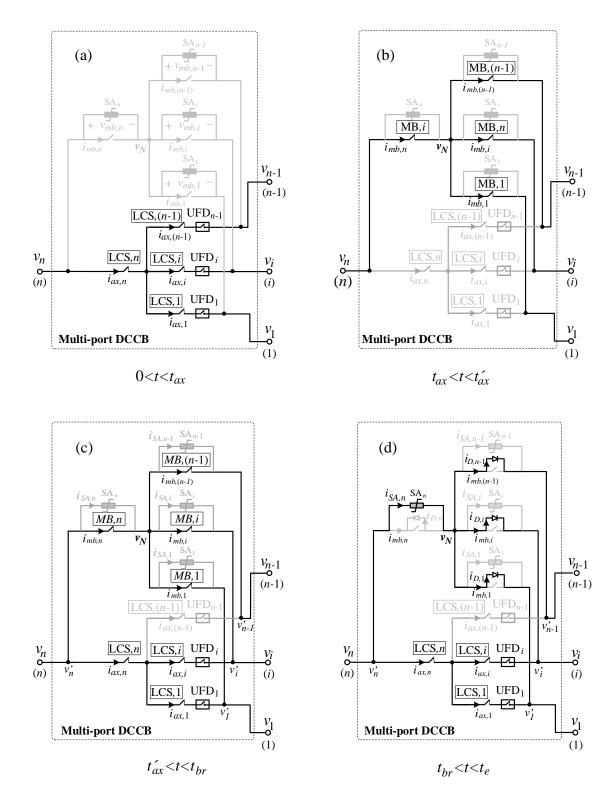

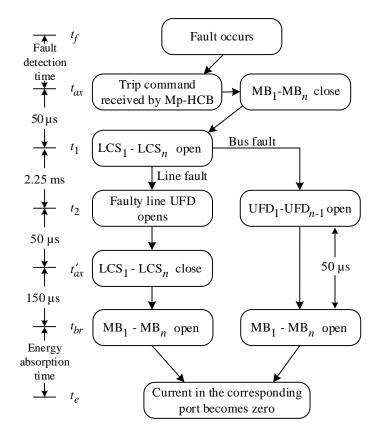

|   | 6.2  | Operation Principles                                    | 190 |

|   |      | 6.2.1 Normal Conduction Mode                            | 190 |

|   |      | 6.2.2 Fault Current Interruption Mode                   | 190 |

|   |      | 6.2.3 Fault on Adjacent Transmission Line i (Port i)    | 190 |

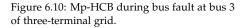

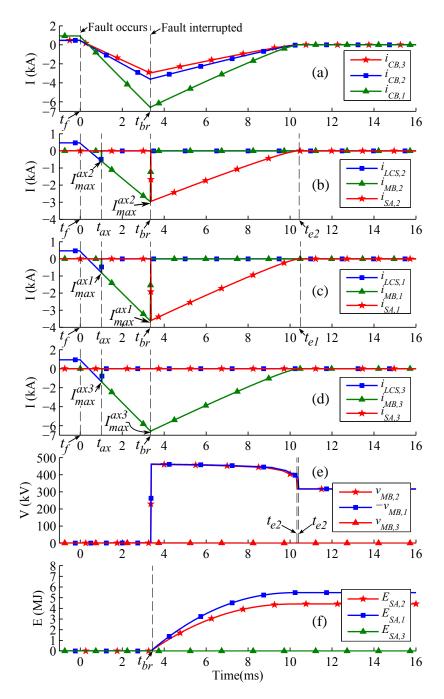

|   |      | 6.2.4 Fault at dc Bus (port n)                          | 192 |

|   |      | 6.2.5 Recloser Mode                                     | 193 |

|   | 6.3  | Analysis                                                |     |

|   |      | 6.3.1 Transmission Line Fault F <sub>1</sub> and Mp-HCB |     |

|   |      | 6.3.2 <i>dc</i> Bus Fault $F_2$ and $Mp$ -HCB           |     |

|   |      | 6.3.3 Transmission Line Fault and HCB                   |     |

|   |      | 6.3.4 <i>dc Bus Fault and HCB</i>                       | 200 |

|   | 6.4  | Simulation Results                                      |     |

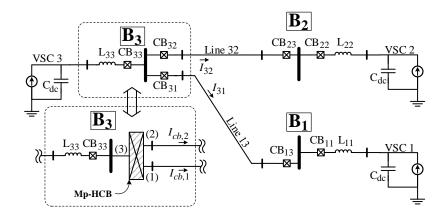

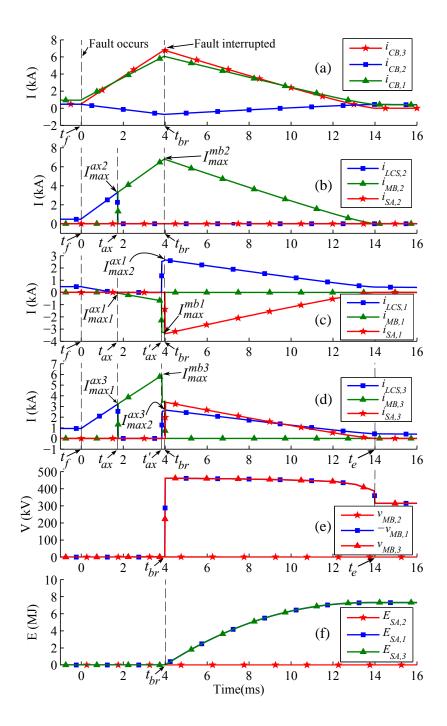

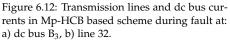

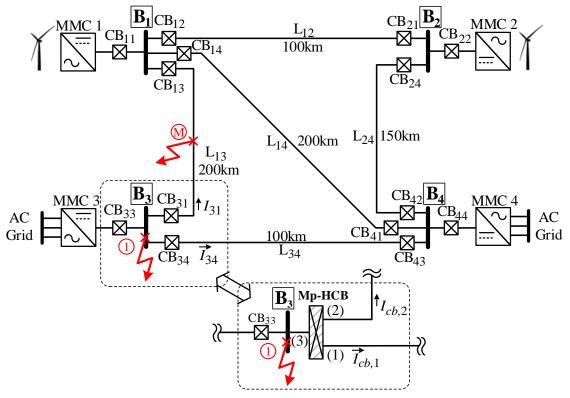

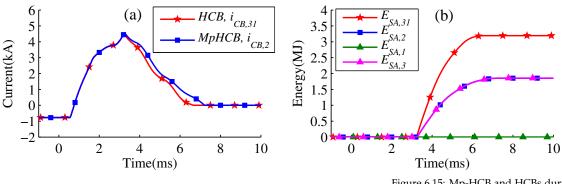

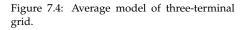

|   |      | 6.4.1 Three-terminal Grid                               |     |

|   |      | 6.4.2 Four-terminal Grid                                |     |

|   | 6.5  | Comparison                                              |     |

|   |      | 6.5.1 Load Commutation Switches                         |     |

|   |      | 6.5.2 Main Breaker Units                                |     |

|   |      | 6.5.3 Surge Arresters                                   |     |

|   |      | 6.5.4 Ultra-Fast Disconnector                           |     |

|   |      | 6.5.5 Current Limiting Inductors                        |     |

|   |      | 6.5.6 Multiple Fault Handling                           |     |

|   | 6.6  | Conclusion                                              | 212 |

| 7 | Curr | rent Flow Controlling                                   |     |

| - |      |                                                         | 213 |

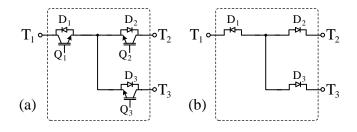

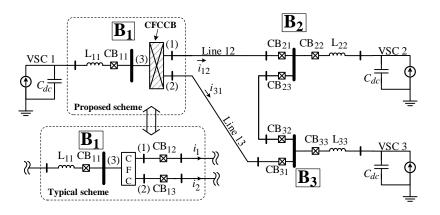

|   | 7.1  | Current Flow Controlling dc Circuit Breaker             | 215 |

|   | 7.2  | CFCCB Operation Principles                              |     |

|   |      | 7.2.1 CFC Bypassed Mode                                 |     |

|   |      | 7.2.2 Active CFC Mode                                   |     |

|   |      | 7.2.3 Fault Mode                                        | 217 |

|   | 7.3  | Case Study Model                                        | 219 |

|   | 7.4  | Analysis                                                | 219 |

|     | 7.4.1  | Impact of the Embedded CFC on the Fault Current |

|-----|--------|-------------------------------------------------|

|     | 7.4.2  | Transmission Line Fault $F_1$ and CFCCB         |

|     | 7.4.3  | <i>dc</i> Bus Fault F <sub>2</sub> and CFCCB    |

| 7.5 | Туріса | <i>il scheme</i>                                |

|     | 7.5.1  | Transmission Line Fault and HCB 225             |

|     | 7.5.2  | <i>dc</i> Bus Fault and HCB                     |

| 7.6 | Simul  | ation Results                                   |

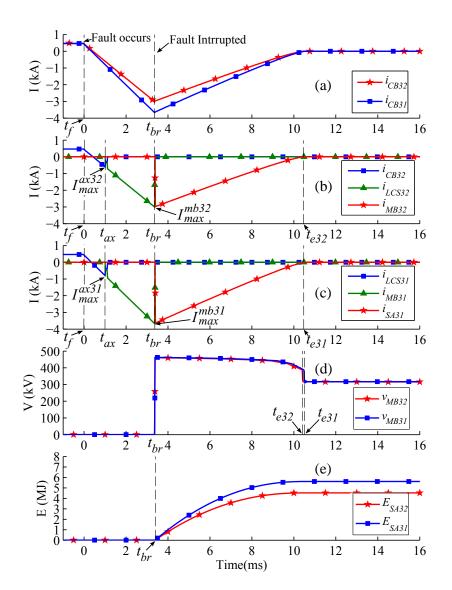

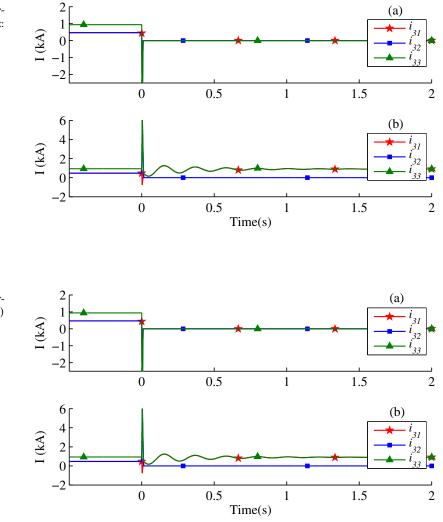

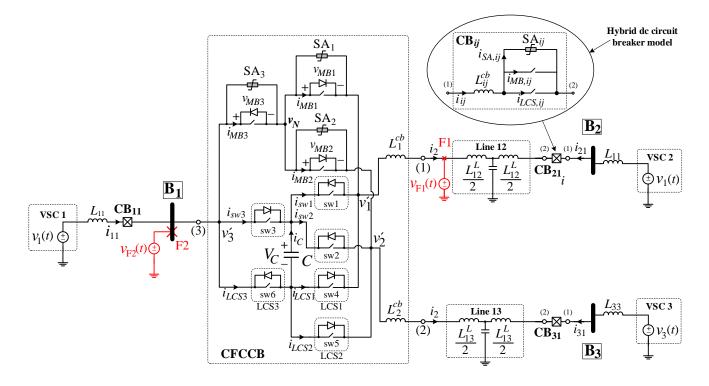

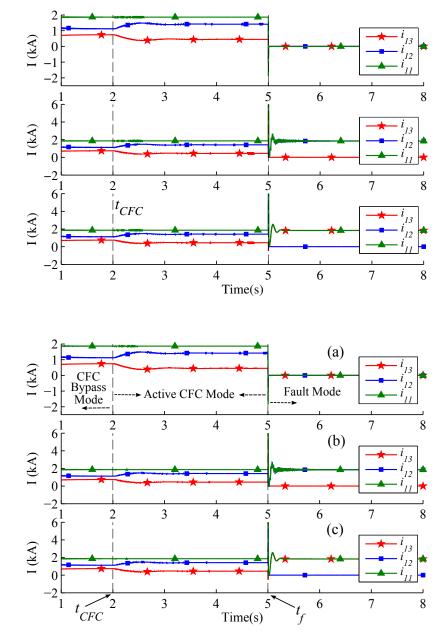

|     | 7.6.1  | Power Flow                                      |

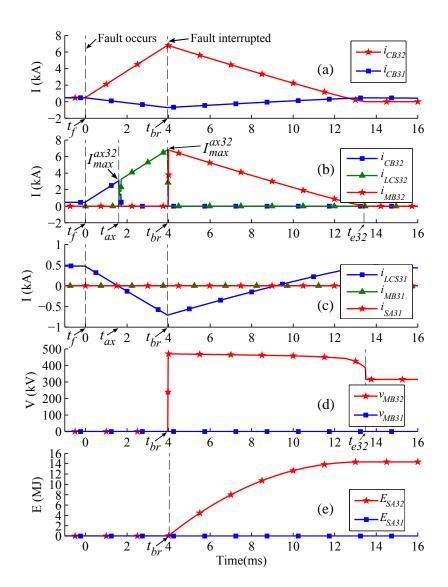

|     | 7.6.2  | Transmission Line Fault                         |

|     | 7.6.3  | <i>dc Bus Fault</i>                             |

| 7.7 | Сотр   | arison                                          |

|     | 7.7.1  | CFC                                             |

|     | 7.7.2  | Rated Voltage                                   |

|     | 7.7.3  | Discharge Current                               |

|     | 7.7.4  | Energy                                          |

|     | 7.7.5  | Ultra-Fast Disconnector                         |

|     | 7.7.6  | Current Limiting Inductors                      |

| 7.8 | Concli | usion                                           |

|     |        |                                                 |

| V | Conclusions | & Future  | Work |

|---|-------------|-----------|------|

| v | Concinsions | O I ninic | WOIN |

| 8 | Con | clusions                                          | 239 |

|---|-----|---------------------------------------------------|-----|

|   | 8.1 | Surge-less dc Current Interruption                | 239 |

|   | 8.2 | Unidirectional dc Circuit Breakers                | 240 |

|   | 8.3 | Superconducting Fault Current Limiters            | 241 |

|   | 8.4 | dc Current Interruption Using a Multi-port Device | 242 |

|   | 8.5 | dc Current Flow Control and Interruption          | 242 |

|   | 8.6 | Future Work                                       | 243 |

237

245

### Bibliography

| VI  | Ap                               | pendixes                                 | 259 |  |

|-----|----------------------------------|------------------------------------------|-----|--|

| A   | 4-Te                             | rminal HVdc Grid Model                   | 261 |  |

|     |                                  | HVdc System Model                        |     |  |

| В   | Faul                             | t Identification Schemes                 | 263 |  |

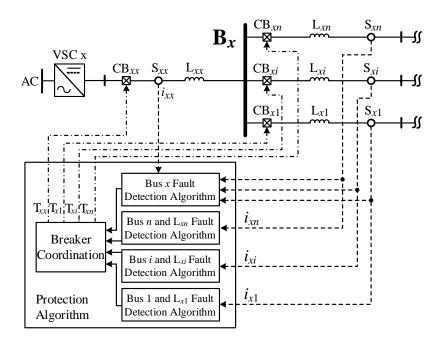

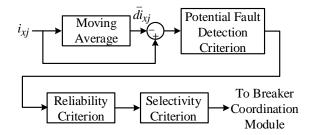

|     | B.1                              | Employed Non-unit Fast Protection Scheme | 263 |  |

|     | <i>B</i> .2                      | Bus Fault Detection Module               | 264 |  |

|     | В.З                              | Line Fault Detection Module              | 264 |  |

|     | B.4                              | Breaker Coordination Module              | 265 |  |

| Ab  | brevi                            | ations                                   | 269 |  |

| Lis | List of Patents and Publications |                                          |     |  |

| Ac  | knou                             | oledgements                              | 275 |  |

Curriculum Vitae

# List of Figures

| 1 | Intr | roduction                                                                                                                                  | 3  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Atmospheric CO <sub>2</sub> content from 1750 to 2000. The pale gray strip covers the range of variation between the different studies [4] | 4  |

|   | 1.2  | The global land-based temperature anomaly (5-year running mean). The base period for the anomaly (black line) is 1951-80 [4].              | 4  |

|   | 1.3  | Key impact factors on global carbon emission [6]                                                                                           | 5  |

| 2 | Lite | erature Review                                                                                                                             | 11 |

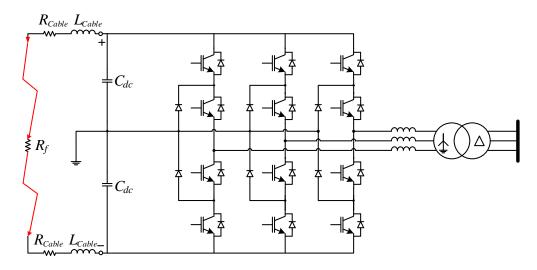

|   | 2.1  | Two-level VSC during pole-to-ground short circuit dc fault.                                                                                | 12 |

|   | 2.2  | Two-level VSC during pole-to-pole short circuit dc fault.                                                                                  | 13 |

|   | 2.3  | Three-level NPC converter topology.                                                                                                        | 14 |

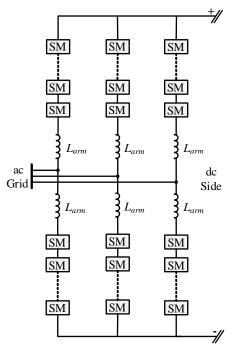

|   | 2.4  | The structure of a modular multilevel converter.                                                                                           | 14 |

|   | 2.5  | Half-bridge MMC under dc pole-to-pole short circuit fault                                                                                  | 15 |

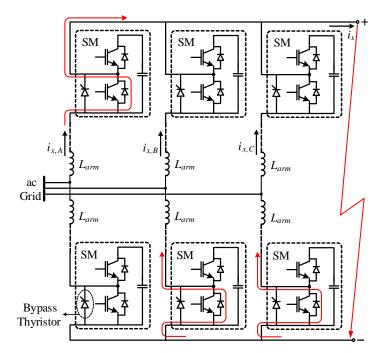

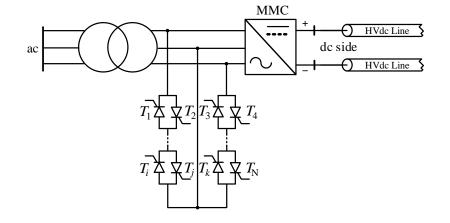

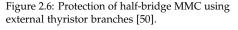

|   | 2.6  | Protection of half-bridge MMC using external thyristor branches [50].                                                                      | 16 |

|   | 2.7  | Protection of half-bridge MMC using external pre-charged capacitors [51].                                                                  | 16 |

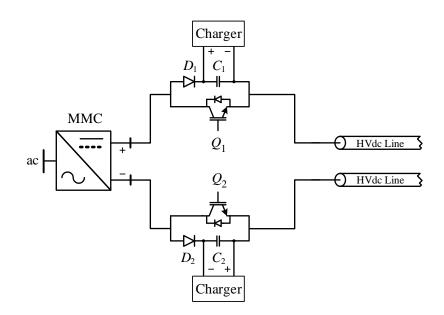

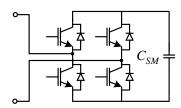

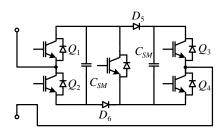

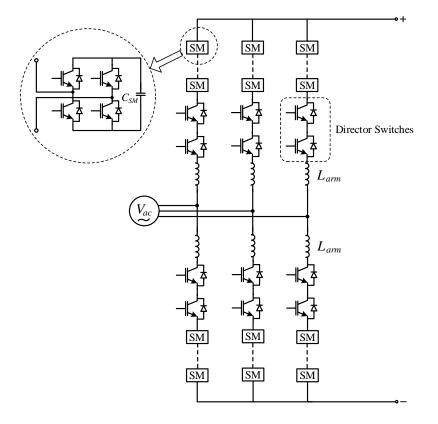

|   | 2.8  | A full-bridge submodule for MMC application.                                                                                               | 17 |

|   | 2.9  | Clamped-Double-Submodule configuration for MMC application.                                                                                | 17 |

|   | 2.10 | Three-level cross-connected submodule.                                                                                                     | 17 |

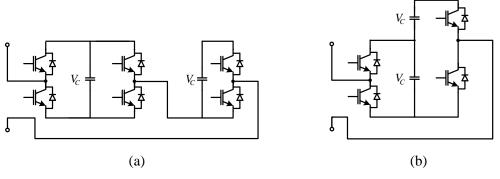

|   | 2.11 | Mixed commutation cell structures [27,58]                                                                                                  | 18 |

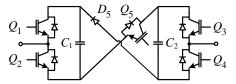

|   | 2.12 | Parallel connected full-bridge cells [27]                                                                                                  | 18 |

|   |      | Cross connected full-bridge cells [27].                                                                                                    | 18 |

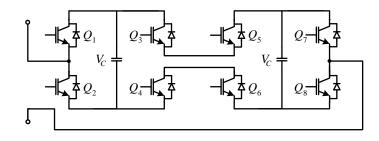

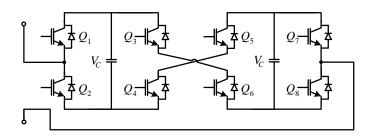

|   | 2.14 | Seven-level submodule [60].                                                                                                                | 19 |

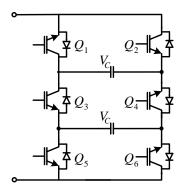

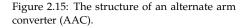

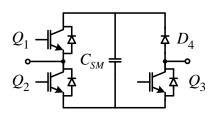

|   | 2.15 | <i>The structure of an alternate arm converter (AAC)</i>                                                                                   | 19 |

|   | 2.16 | Unipolar voltage full-bridge submodule                                                                                                     | 19 |

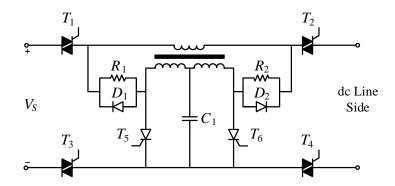

|   | 2.17 | Electromechanical dc circuit breaker with pre-charged capacitor [63].                                                                      | 20 |

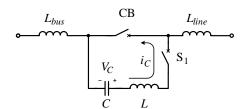

|   |      | Crossed field interrupt tubes based MCB for HVdc applications [67].                                                                        | 21 |

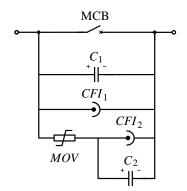

|   |      | MCB for HVdc applications using trigger gap and pulse transformer [72].                                                                    | 22 |

|   | 2.20 | MCB for HVdc applications using trigger gap and pulse transformer with parallel surge arrester [73].                                       | 22 |

|   |      | The configuration of developed prototype for the interruption of 8 kA at 250 kV [75]                                                       | 22 |

|   |      | The configuration of 500 kV airblast HVdc circuit breaker [76].                                                                            | 22 |

|   |      | The configuration of 500 kV SF <sub>6</sub> based HVdc circuit breaker [78]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                  | 23 |

|   |      | The configuration of MCB using power diode in the commutation path [80].                                                                   | 23 |

|   |      | The configuration of MCB based on series connection of the vacuum interrupters [81]                                                        | 23 |

|   |      | The configuration of MCB based on series connection of the vacuum and $SF_6$ interrupters [83]                                             | 23 |

|   | 2.27 | The configuration of MCB with reduced rating auxiliary semiconductors [88].                                                                | 24 |

|   |      |                                                                                                                                            |    |

|      |                                                                                                                                                                         | ~        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | The configurations of bidirectional MCBs [91].                                                                                                                          |          |

| 2.29 | The configurations of bidirectional MCBs [91].                                                                                                                          | 24       |

| 2.30 | Active resonance MCB topology [92].                                                                                                                                     | 24       |

| 2.31 | The configuration of a typical solid-sate dc circuit breaker.                                                                                                           | 25       |

|      | The configuration of a solid-sate dc circuit breaker with freewheeling diode.                                                                                           | 25       |

|      | The configurations of bidirectional MCBs [101].                                                                                                                         | 25       |

|      | Thyristor based solid-state dc circuit breaker [102].                                                                                                                   | 26       |

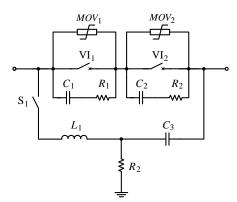

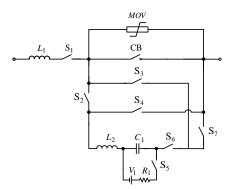

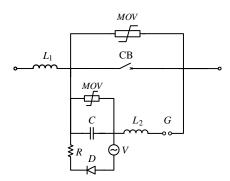

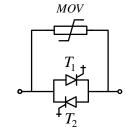

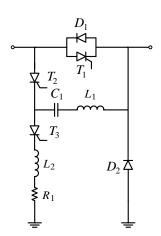

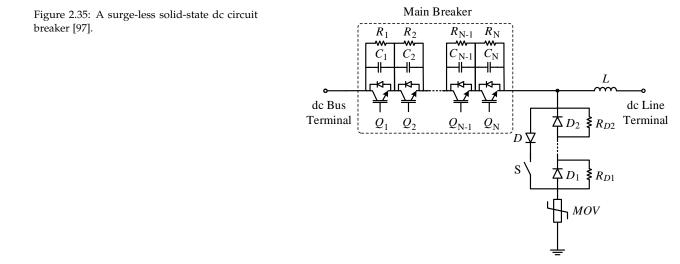

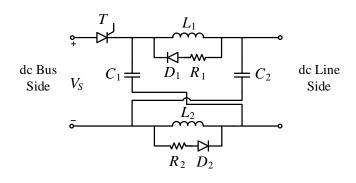

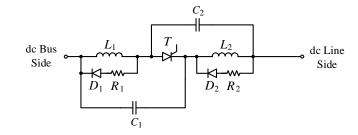

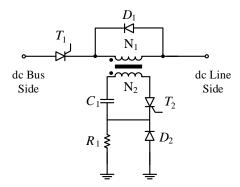

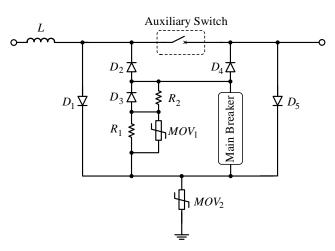

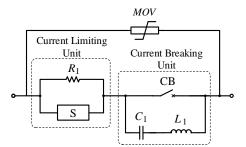

| 2.35 | A surge-less solid-state dc circuit breaker [97].                                                                                                                       | 26       |

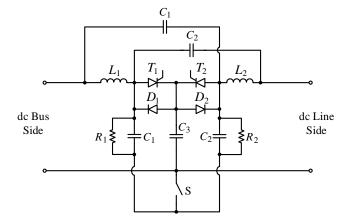

|      | Basic topology of z-source solid-state dc circuit breaker [102].                                                                                                        | 27       |

|      | Modified z-source solid-state dc circuit breaker [107]                                                                                                                  | 28       |

|      | Bidirectional z-source solid-state dc circuit breaker [113]                                                                                                             | 28       |

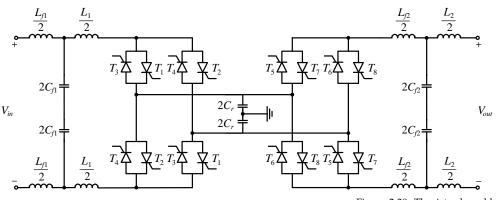

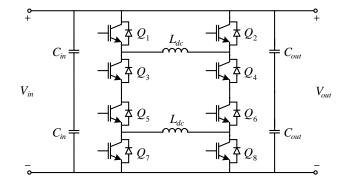

|      | Thyristor based bidirectional dc/dc converter for high power applications [123]                                                                                         | 29       |

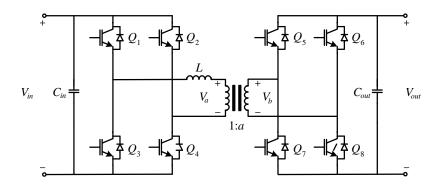

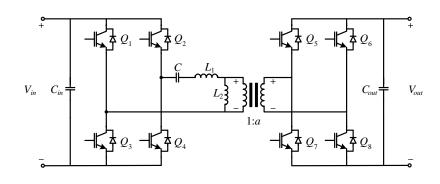

|      | Dual active bridge dc/dc converter as dc circuit breaker [124].                                                                                                         | 30       |

|      | Bidirectional dc/dc chopper as dc circuit breaker [125].                                                                                                                | 30       |

|      | A double switch topology of a dc/dc chopper [126].                                                                                                                      | 30       |

|      | A modified double switch topology of a dc/dc chopper [126].                                                                                                             |          |

|      | Single switch topology of a dc/dc chopper [126].                                                                                                                        | 30       |

|      | Bidirectional dc/dc chopper as dc circuit breaker [127].                                                                                                                | 31       |

|      | The configurations of SSCB based on coupled inductors [128].                                                                                                            | 31       |

|      | A unidirectional SSCB based on coupled inductors [128].                                                                                                                 | 31       |

|      | A bidirectional SSCB based on coupled inductors [128].                                                                                                                  | 31       |

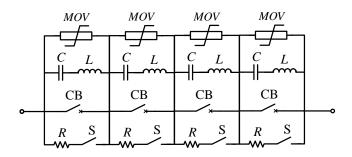

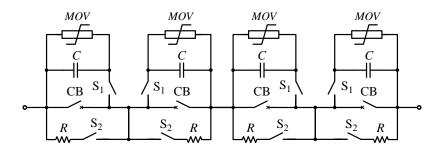

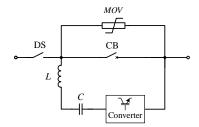

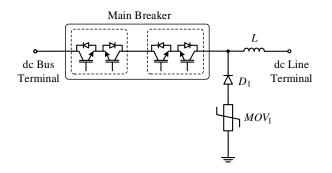

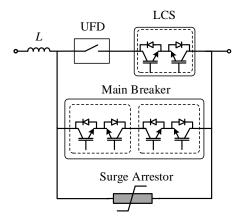

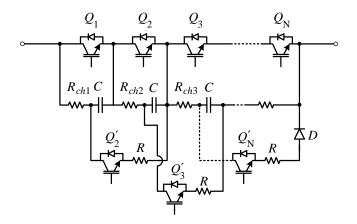

|      | The basic topology of hybrid dc circuit breaker [134].                                                                                                                  |          |

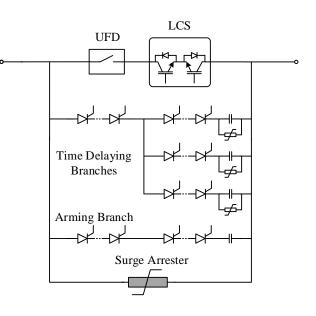

|      | The topology of proactive hybrid dc circuit breaker [134].                                                                                                              |          |

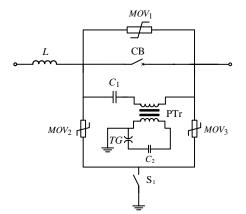

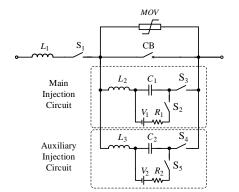

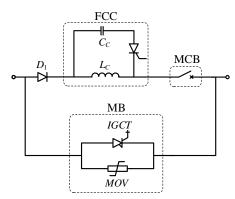

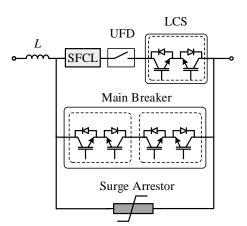

|      | The topology of forced commutation hybrid dc circuit breaker [153].                                                                                                     | 33       |

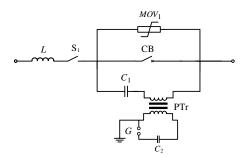

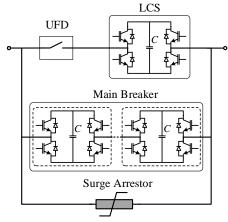

|      | The topology of hybrid dc circuit breaker proposed by Alstom Grid [154].                                                                                                | 33<br>34 |

|      | The topology of a current injecting hybrid dc circuit breaker [155]                                                                                                     | 34<br>34 |

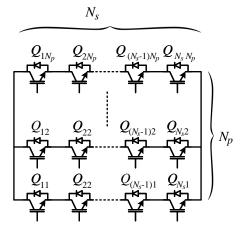

|      | The configuration of main breaker unit of current injecting hybrid dc circuit breaker [155].                                                                            |          |

|      | The configuration of full-bridge based hybrid dc circuit breaker [156].                                                                                                 | 35<br>35 |

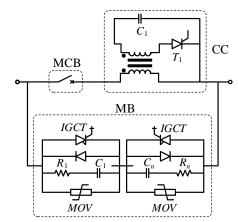

|      | The configuration of a hybrid dc circuit breaker with current commutation drive circuit [158,159].                                                                      | 35<br>35 |

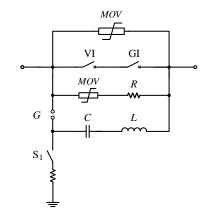

|      | The configuration of an H-bridge based hybrid dc circuit breaker [160].                                                                                                 | 35<br>36 |

|      |                                                                                                                                                                         |          |

|      | The topology of SiC based hybrid dc circuit breaker with unidirectional MB unit [161].                                                                                  | 36<br>37 |

|      | The configuration of assembly hybrid dc circuit breaker [162].                                                                                                          |          |

|      | <i>The configuration of thyristor controlled resistor in parallel with the current limiting inductor</i> [163]. <i>The configuration of a normal limiting MCB</i> [179] | 37       |

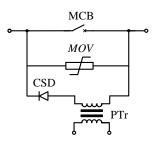

|      | The configuration of a current limiting MCB [178].                                                                                                                      | 38       |

| 2.62 | The configuration of proactive HCB with SFCL in its main current path [182]                                                                                             | 38       |

|      |                                                                                                                                                                         |          |

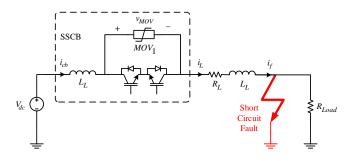

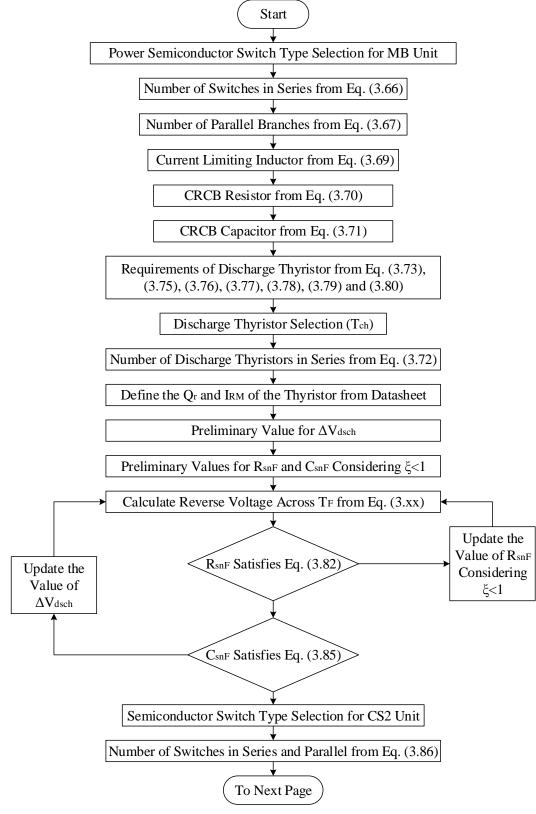

| Surg | ge-less dc Circuit Breaker                                                                                                                                              | 43       |

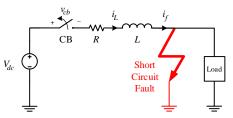

| 3.1  | dc current interruption.                                                                                                                                                | 45       |

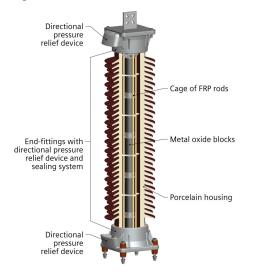

| 3.2  | Metal oxide elements [192].                                                                                                                                             | 46       |

| 3.3  | A Siemens MOV with porcelain housing [192].                                                                                                                             | 46       |

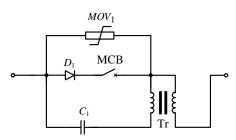

| 3.4  | MOV application in solid-state dc circuit breaker [196].                                                                                                                | 47       |

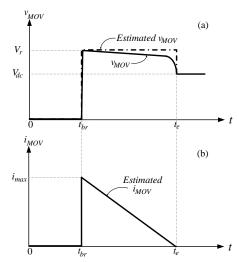

| 3.5  | Surge arrester approximated current and voltage.                                                                                                                        | 47       |

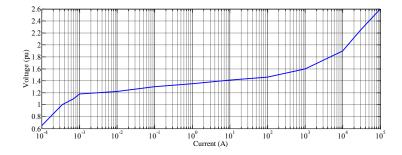

| 3.6  | Nonlinear $V - I$ characteristic for an MOV [195].                                                                                                                      | 48       |

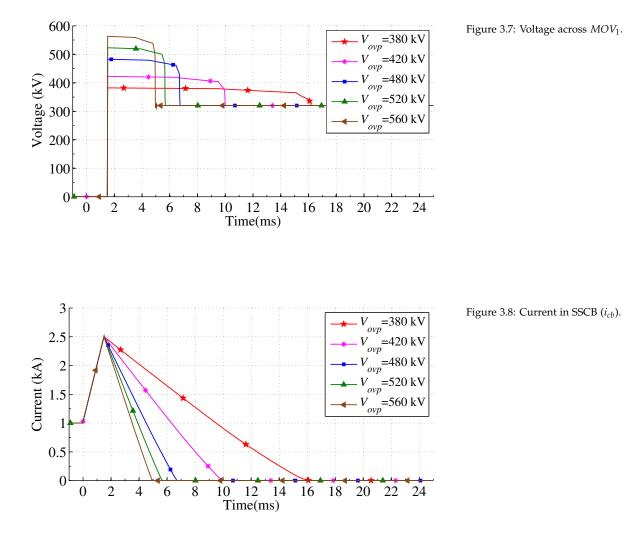

| 3.7  | $Voltage across MOV_1$ .                                                                                                                                                | 49       |

| 3.8  | <i>Current in SSCB</i> ( <i>i</i> <sub>cb</sub> ).                                                                                                                      | 49       |

| 3.9  | Absorbed energy in $MOV_1$ .                                                                                                                                            | 49       |

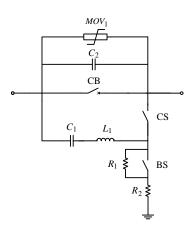

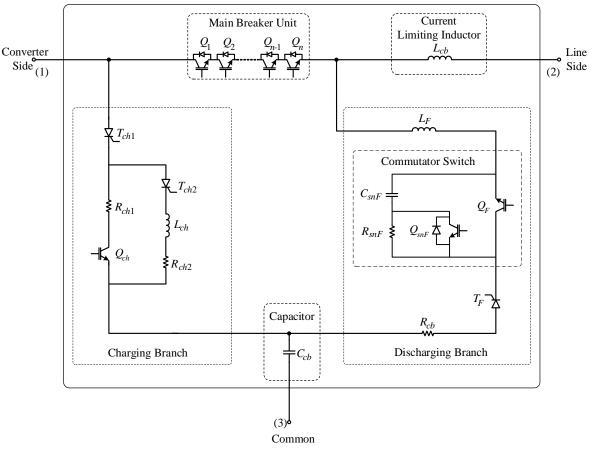

| 3.10 | Topology of the current releasing dc circuit breaker (CRCB).                                                                                                            | 51       |

|      |                                                                                                                                                                         | ~ -      |

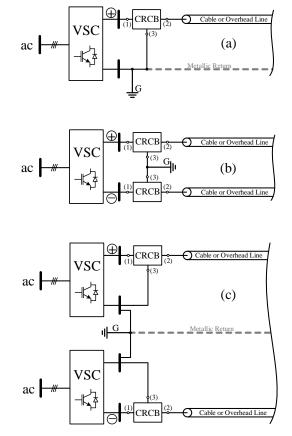

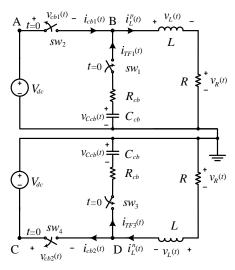

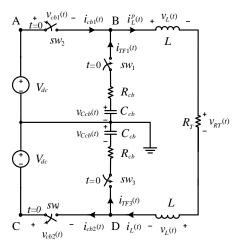

| 3.11 | CRCB integrated to different HVdc configurations: (a) Asymmetric monopole, (b) Symmetric monopole, |     |

|------|----------------------------------------------------------------------------------------------------|-----|

|      | (c) Bipolar                                                                                        |     |

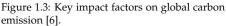

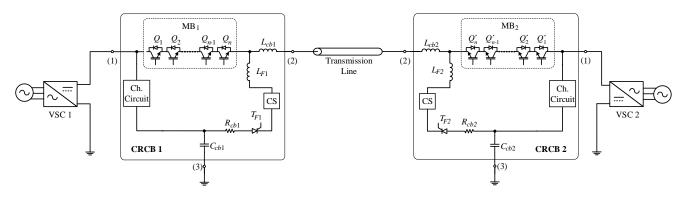

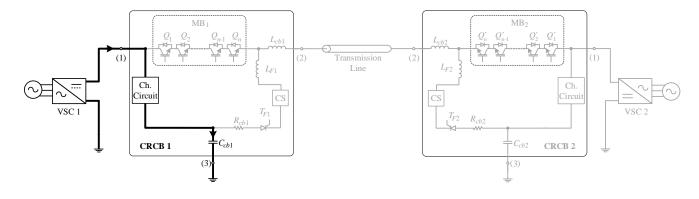

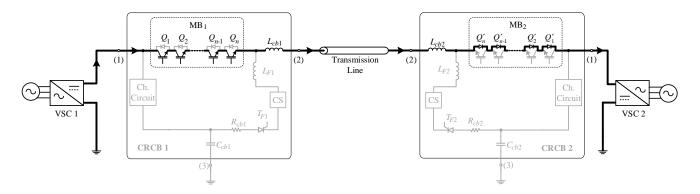

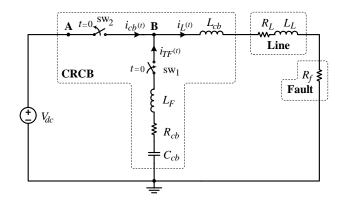

| 3.12 | Detail schematic of the CRCB integration into an asymmetric monopole HVdc system                   | 53  |

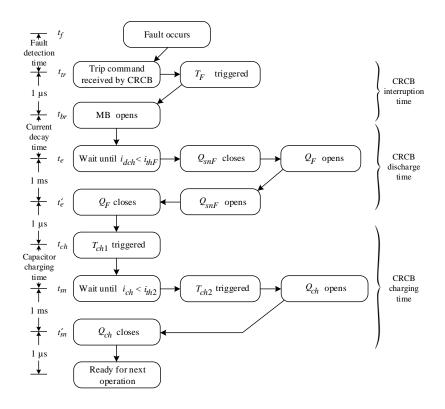

| 3.13 | The capacitor charging stage                                                                       | 53  |

| 3.14 | Normal conduction stage.                                                                           | 54  |

| 3.15 | Current interruption stage.                                                                        | 54  |

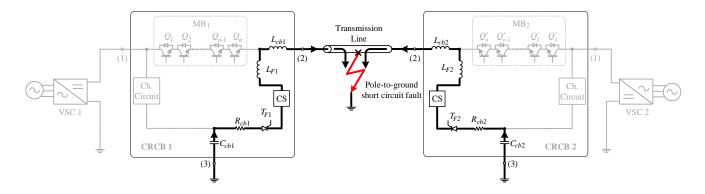

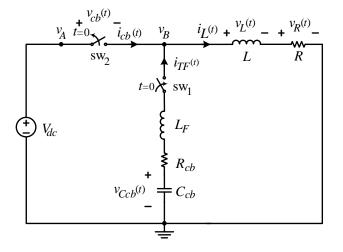

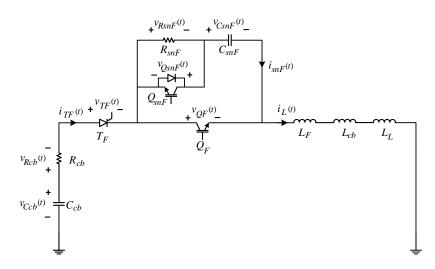

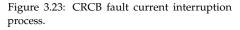

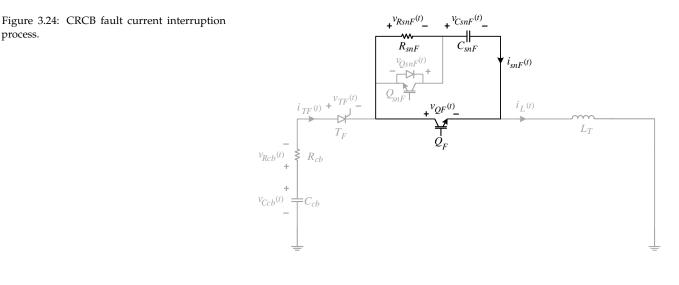

| 3.16 | CRCB fault current interruption process.                                                           | 55  |

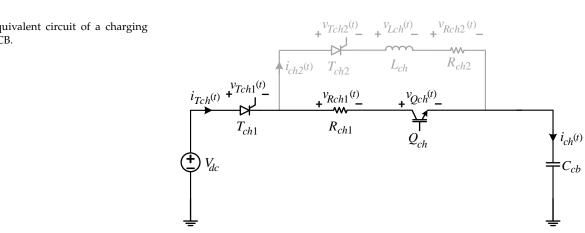

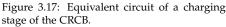

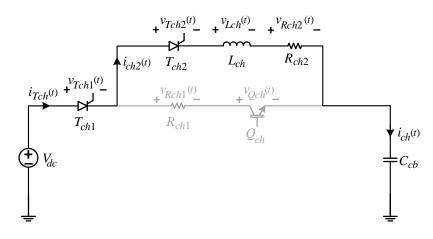

|      | Equivalent circuit of a charging stage of the CRCB.                                                |     |

| 3.18 | Equivalent circuit of a charging stage of the CRCB.                                                | 56  |

|      | Equivalent circuit of a charging stage of the CRCB.                                                |     |

|      | Equivalent circuit of a simplified dc system in presence of the CRCB.                              |     |

|      | Aggregated equivalent circuit of a dc system in presence of the CRCB                               |     |

|      | CRCB fault current interruption process.                                                           |     |

|      | CRCB fault current interruption process.                                                           |     |

|      | CRCB fault current interruption process.                                                           |     |

|      | CRCB fault current interruption process.                                                           |     |

|      | Equivalent circuit of the bipole HVdc system during Pole-to-pole-to-ground short circuit fault     |     |

|      | Equivalent circuit of the bipole HVdc system during Pole-to-pole short circuit fault.              |     |

|      | CRCB fault current interruption process.                                                           |     |

|      | CRCB fault current interruption process                                                            |     |

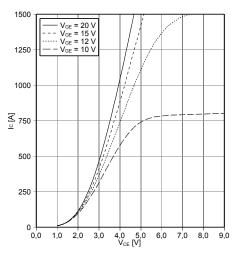

|      | $Typical I_C - V_{CE} curve [206].$                                                                |     |

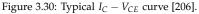

| 3 31 | <i>Typical</i> $I_C - V_{CE}$ <i>curve</i> [205,206]                                               | 72  |

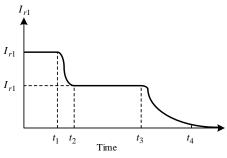

|      | Typical curve for thyristor reverse recovery current [210].                                        |     |

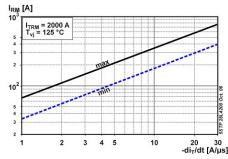

|      | A typical curve for peak reverse recovery current [211]                                            |     |

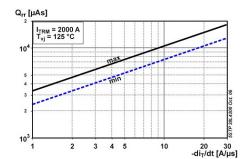

|      | A typical curve of recovered charge vs thyristor current derivative [211].                         |     |

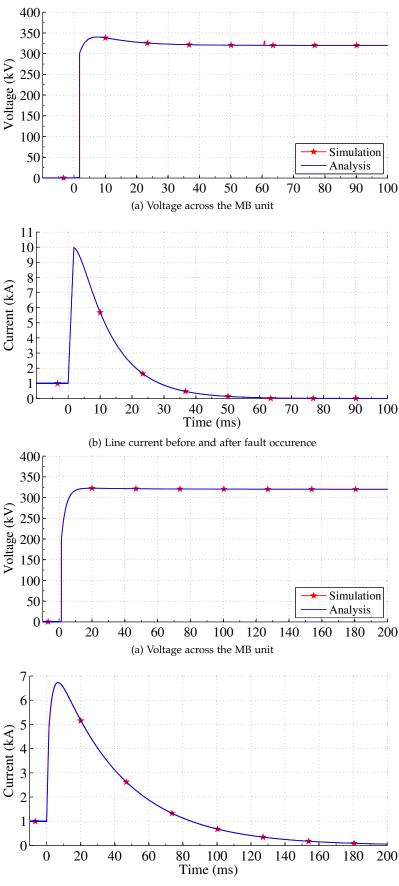

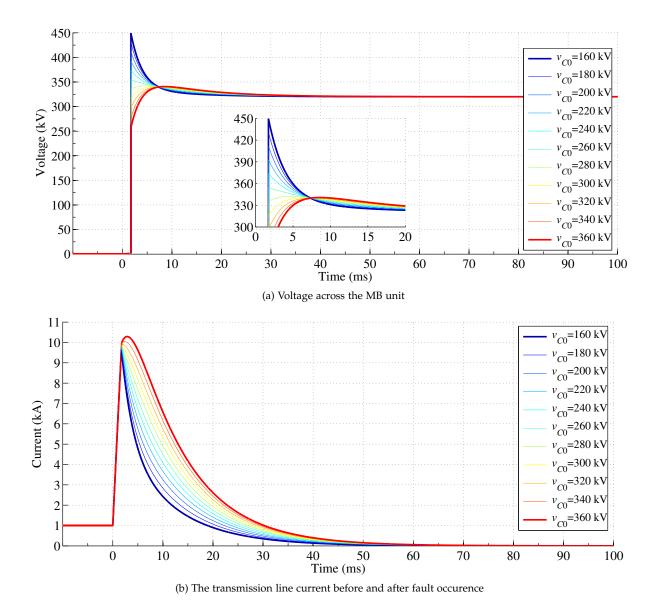

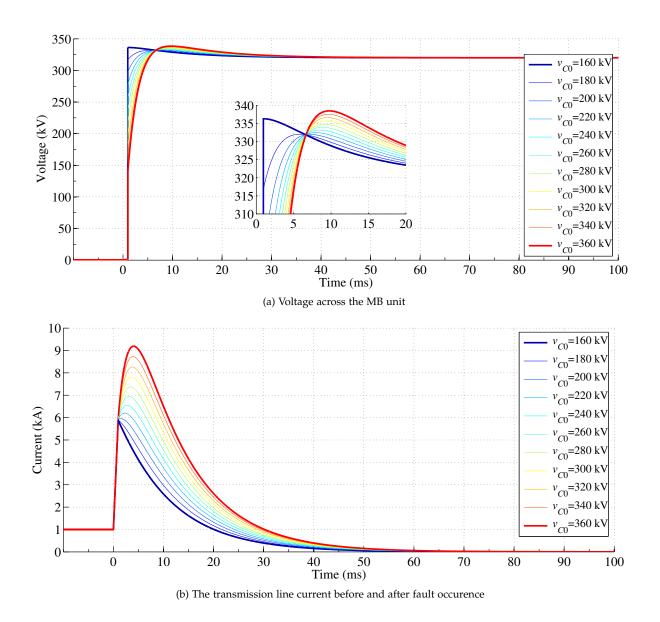

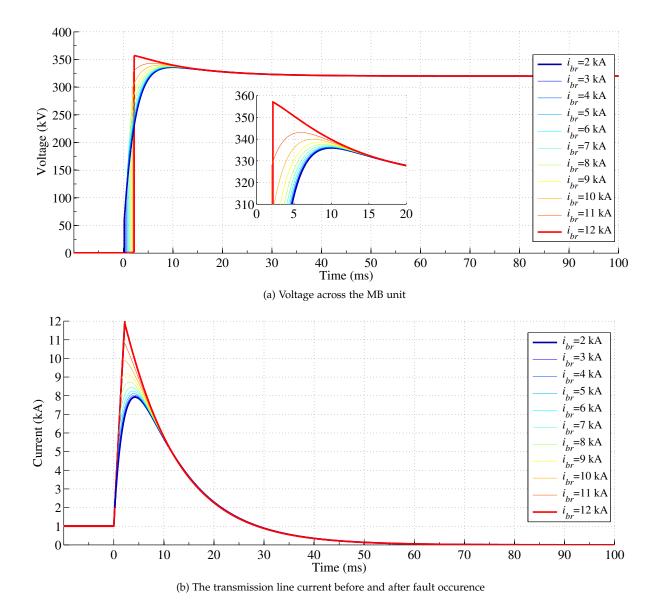

|      | (a) Voltage and (b) current waveforms for set 1.                                                   |     |

|      | (a) Voltage and (b) current waveforms for set 2                                                    |     |

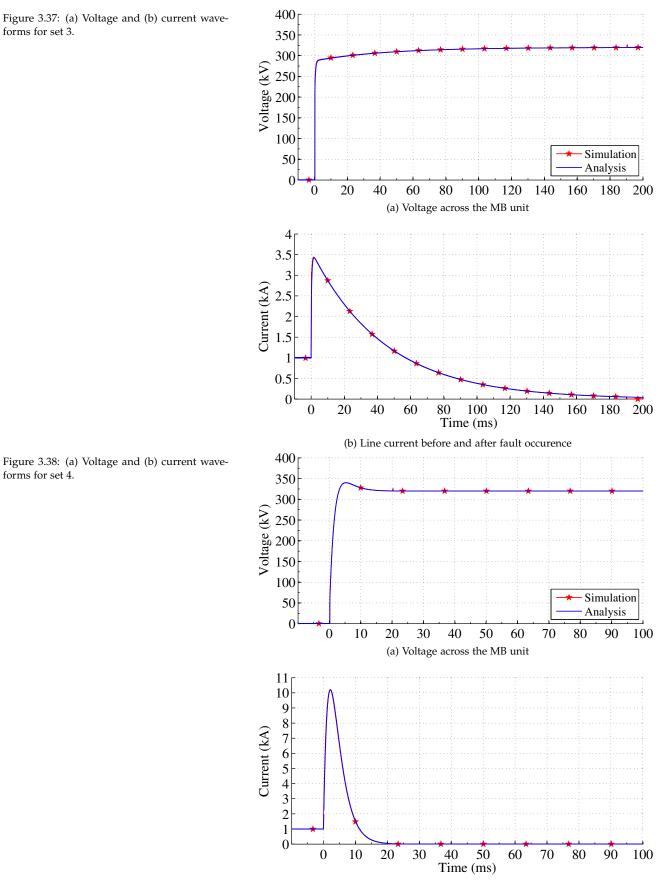

|      | (a) Voltage and (b) current waveforms for set 3                                                    |     |

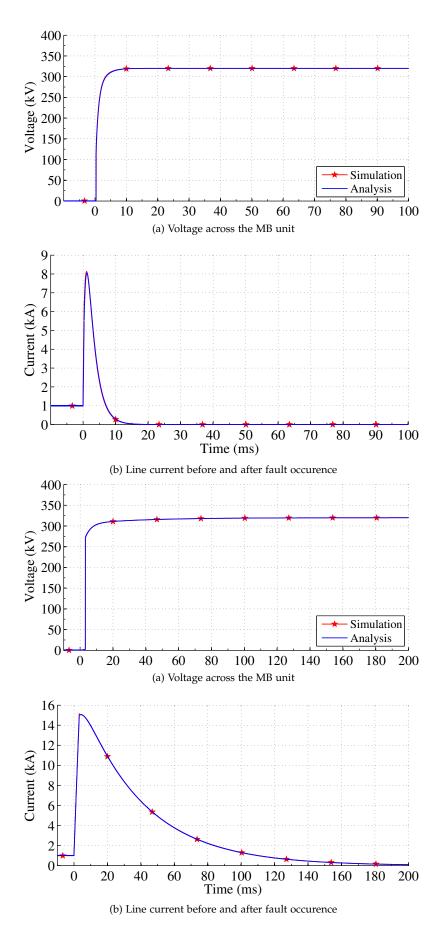

|      | (a) Voltage and (b) current waveforms for set 4                                                    |     |

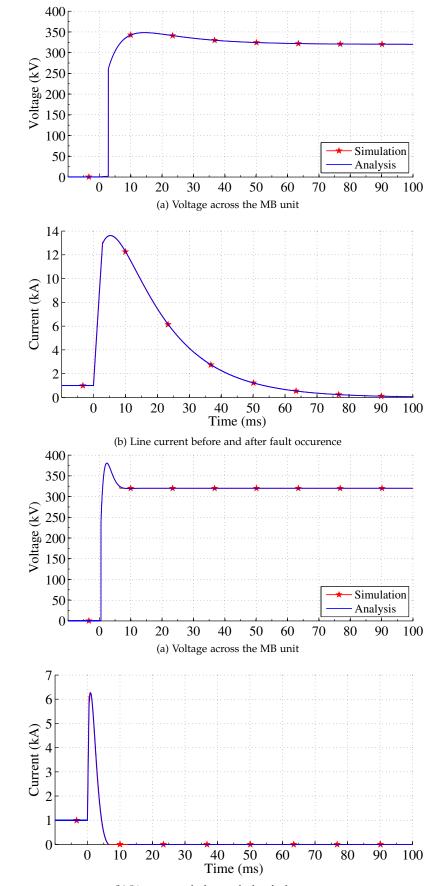

|      | (a) Voltage and (b) current waveforms for set 5                                                    |     |

|      | (a) Voltage and (b) current waveforms for set 6                                                    |     |

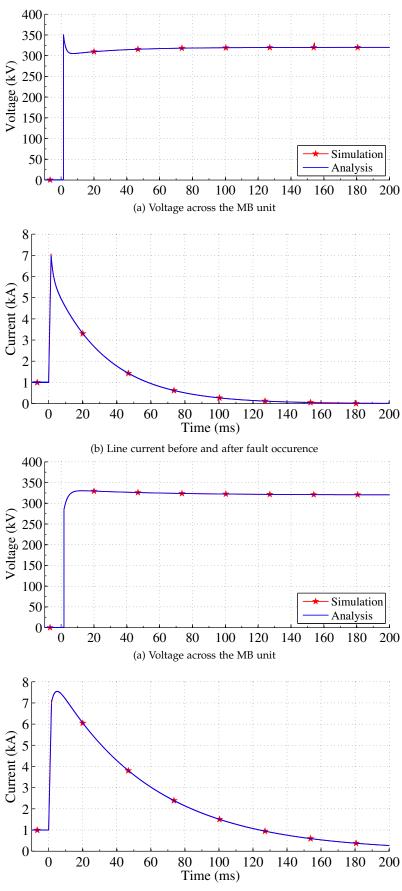

|      | (a) Voltage and (b) current waveforms for set 7                                                    |     |

|      | (a) Voltage and (b) current waveforms for set 8                                                    |     |

|      | 0                                                                                                  |     |

|      | (a) Voltage and (b) current waveforms for set 9                                                    |     |

|      | (a) Voltage and (b) current waveforms for set 10                                                   |     |

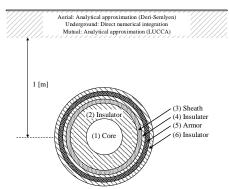

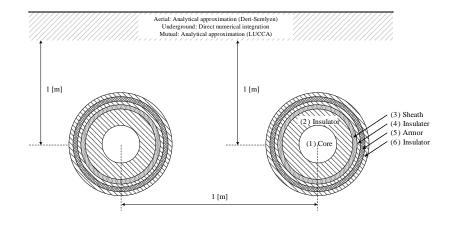

|      | XLPE cable cross-section [212].                                                                    |     |

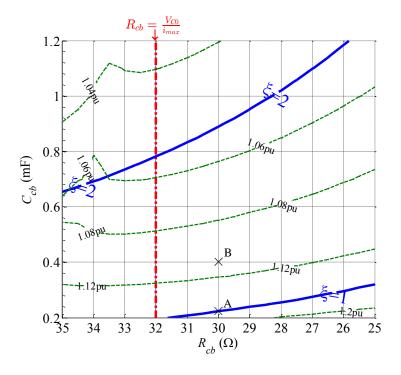

|      | Design area considering the circuit damping factor.                                                |     |

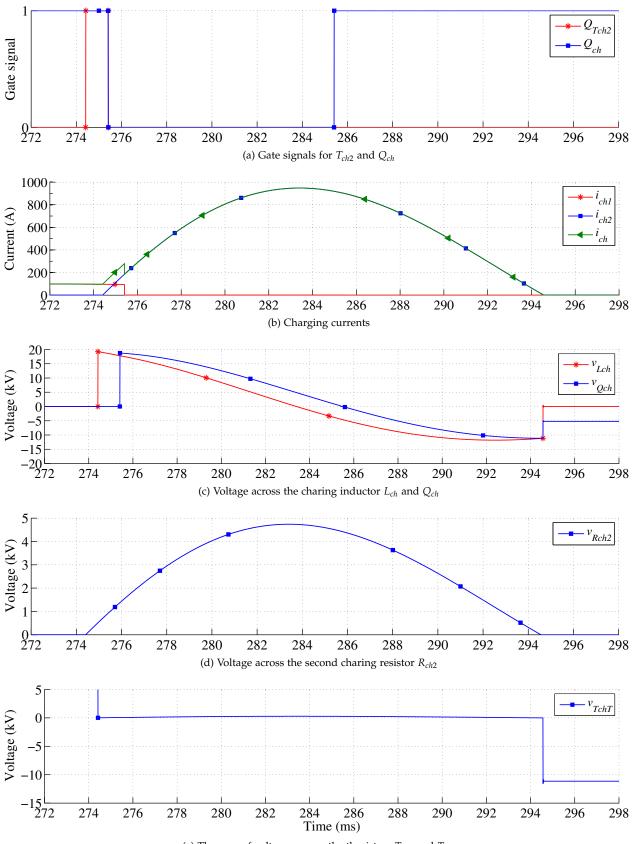

|      | Various CRCB parameters during a full cycle of operation.                                          |     |

|      | Various CRCB parameters during a full cycle of operation.                                          |     |

|      | Voltage and currents during the second stage of charging.                                          |     |

|      | Voltage and currents during the final stage of the CRCB discharging.                               |     |

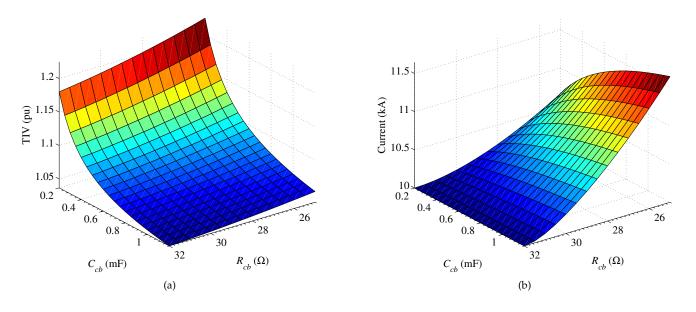

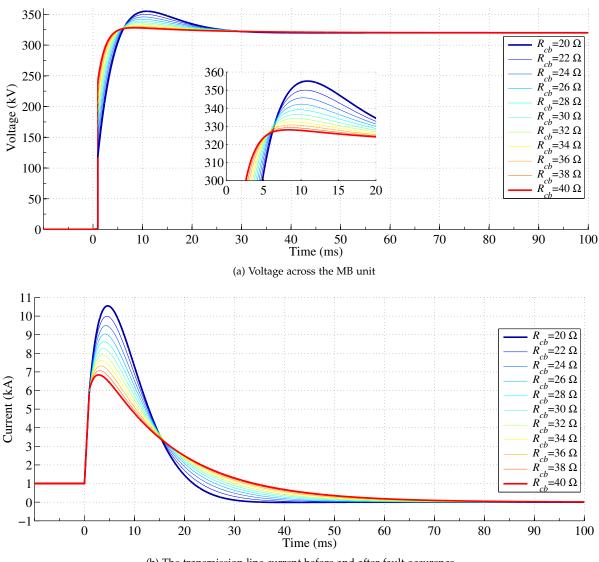

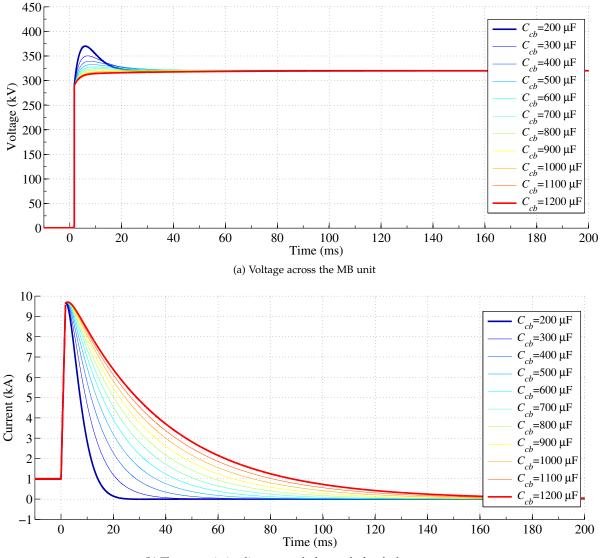

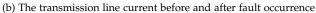

|      | (a) TIV and (b) maximum line current variation by changing $C_{cb}$ and $R_{cb}$ .                 |     |

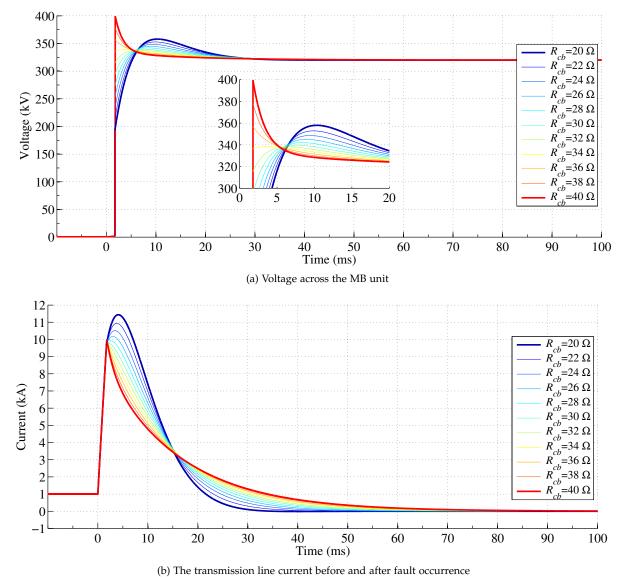

|      | (a) Voltage and (b) current waveforms for designed CRCB.                                           |     |

|      | (a) Voltage and (b) current waveforms for designed CRCB.                                           |     |

|      | (a) Voltage and (b) current waveforms for designed CRCB.                                           |     |

|      | (a) Voltage and (b) current waveforms for designed CRCB.                                           |     |

|      | (a) Voltage and (b) current waveforms for designed CRCB.                                           |     |

| 3.57 | (a) Voltage and (b) current waveforms for designed CRCB                                            | 103 |

| 3.58 | (a) Voltage and (b) current waveforms for designed CRCB                                                                       | 104 |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.59 | (a) Voltage and (b) current waveforms for designed CRCB                                                                       | 105 |

| 3.60 | (a) Voltage and (b) current waveforms for designed CRCB                                                                       | 106 |

| 3.61 | (a) Voltage and (b) current waveforms for designed CRCB                                                                       | 107 |

| 3.62 | (a) Voltage and (b) current waveforms for designed CRCB                                                                       | 108 |

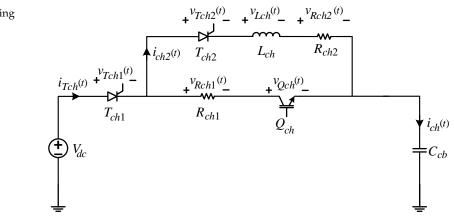

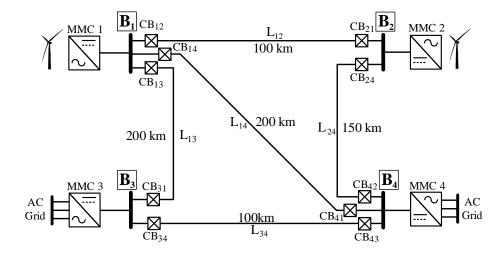

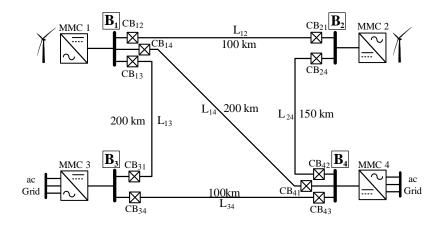

| 3.63 | Test multi-terminal HVdc grid.                                                                                                | 109 |

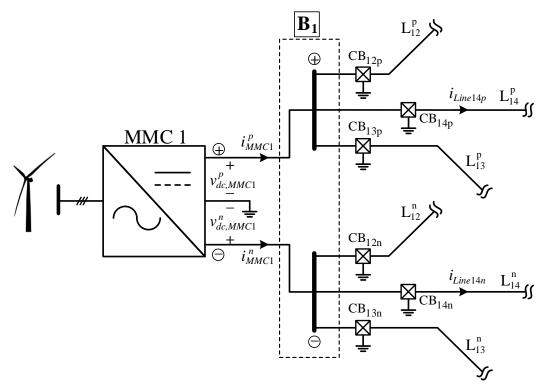

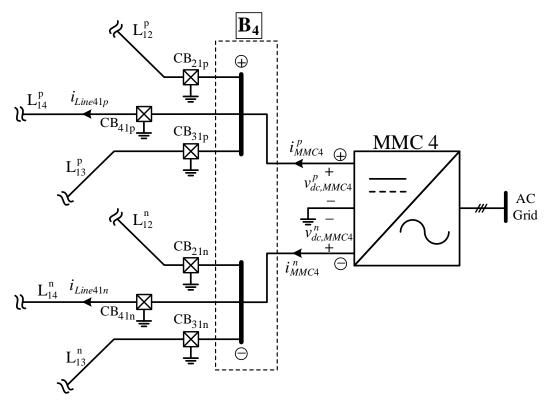

| 3.64 | MMC 1 and 4 and their associated buses and lines                                                                              | 110 |

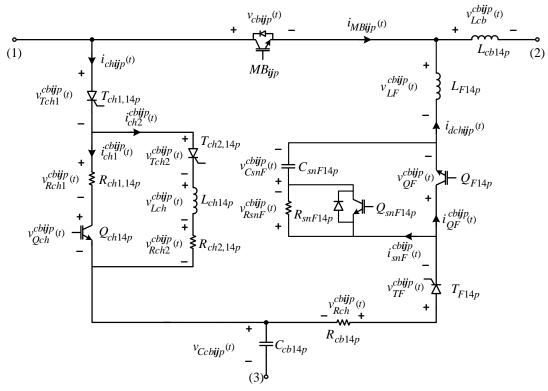

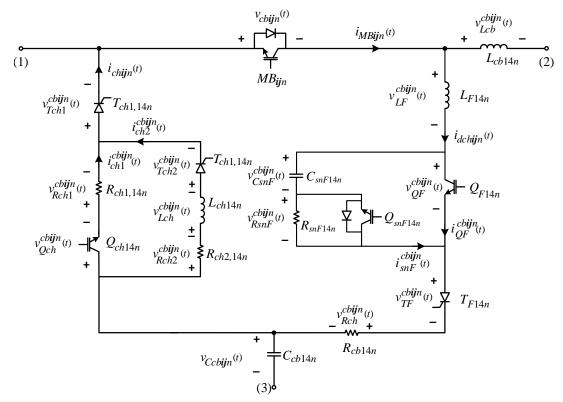

| 3.65 | Simulation model for the positive and negative poles CRCBs                                                                    | 111 |

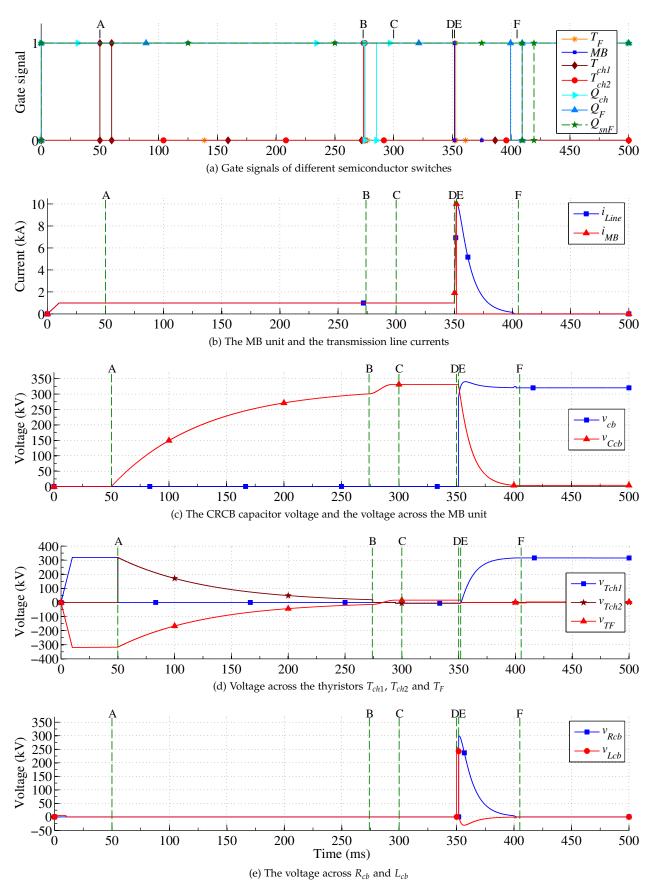

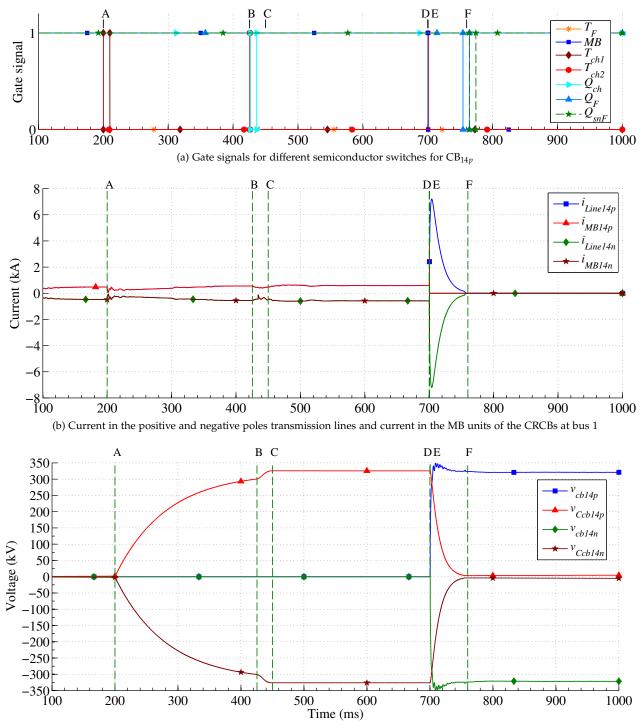

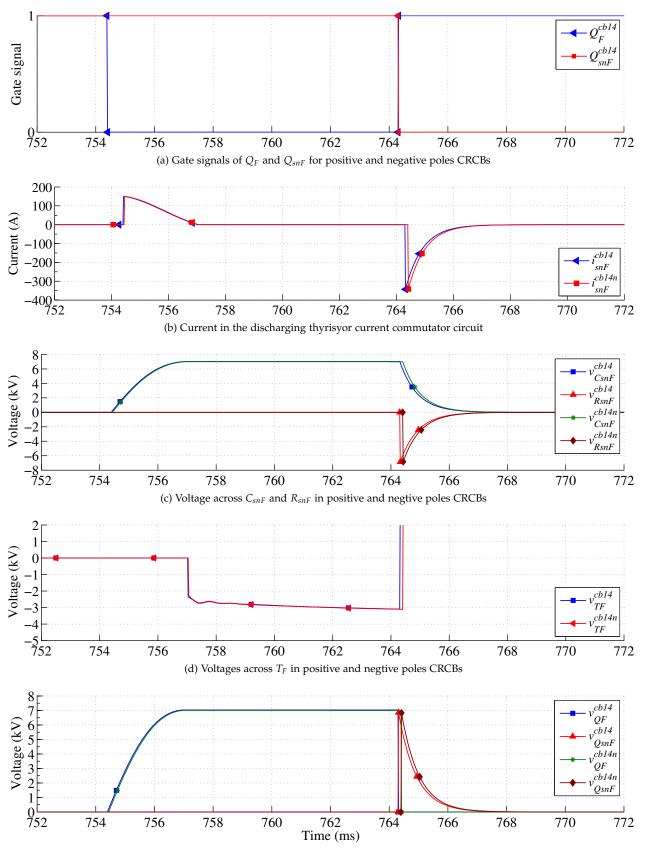

| 3.66 | Gate signals and current and voltage waveforms of positive and negative poles CRCBs during an                                 |     |

|      | operation cycle in a symmetric monopole HVdc grid                                                                             | 113 |

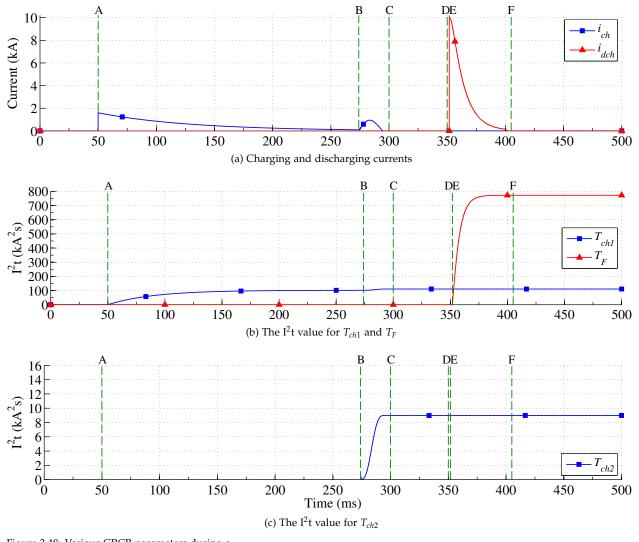

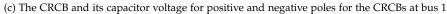

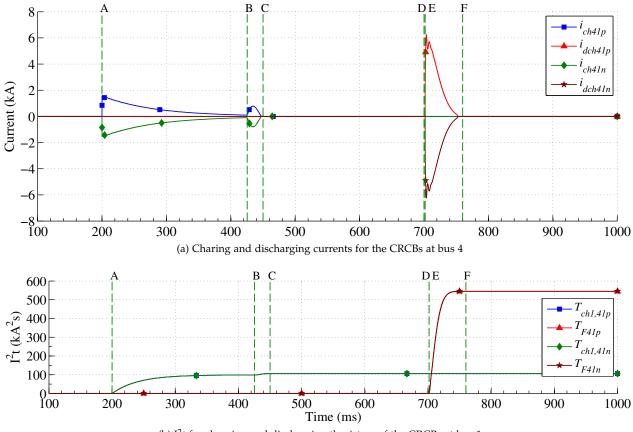

| 3.67 | <i>Charging and discharging currents and I<sup>2</sup>t value of thyristors in positive and negative poles CRCBs</i>          |     |

|      | during an operation cycle in a symmetric monopole HVdc grid                                                                   | 114 |

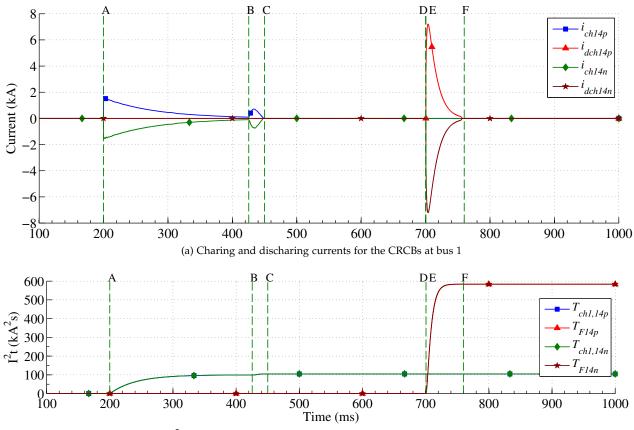

| 3.68 | Current and voltage waveforms of relevant components' during the second charging stage in positive                            |     |

|      | and negative poles CRCBs                                                                                                      | 116 |

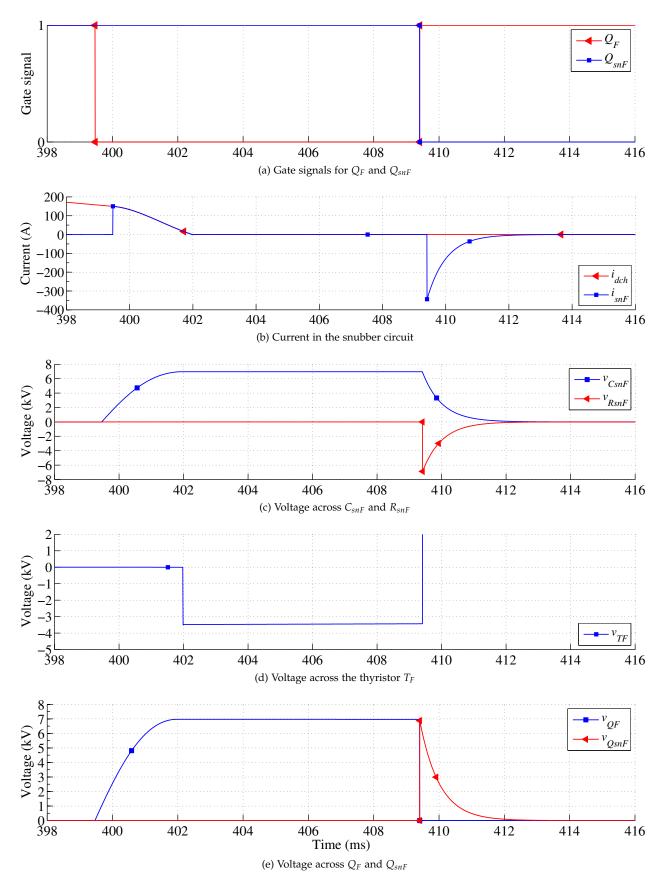

| 3.69 | Current and voltage waveforms of relevant components' during discharging thyristor current commuta-                           |     |

|      | tion stage in positive and negative poles CRCBs                                                                               |     |

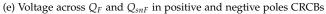

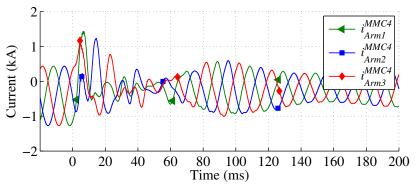

| 3.70 | Arm currents and dc side currents in MMCs                                                                                     | 118 |

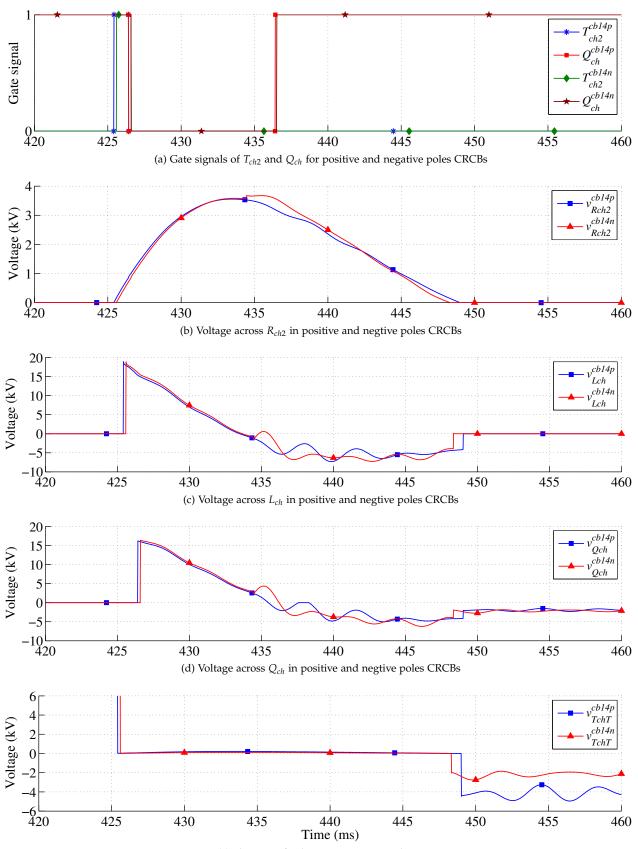

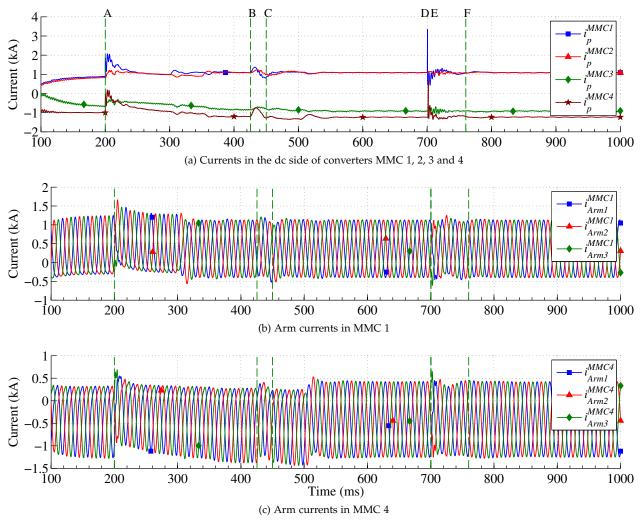

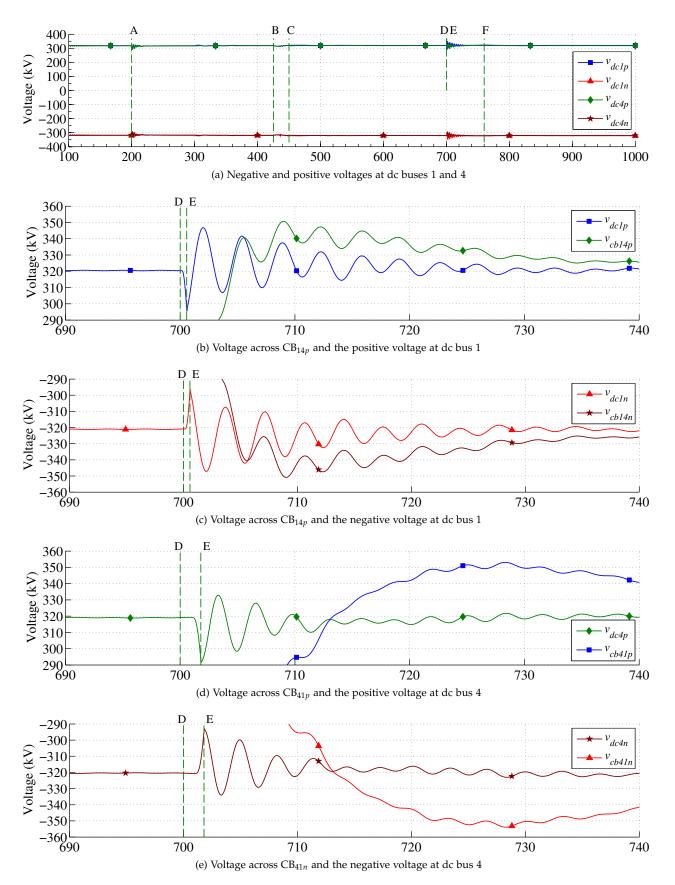

|      | Gate signals, current and voltage waveforms of positive and negative poles CRCBs                                              | 121 |

| 3.72 | <i>Charging and discharging currents and</i> I <sup>2</sup> <i>t value of thyristors in positive and negative poles CRCBs</i> |     |

|      | during an operation cycle in a symmetric monopole HVdc grid                                                                   |     |

|      | The voltage across CRCBs and corresponding dc buses                                                                           |     |

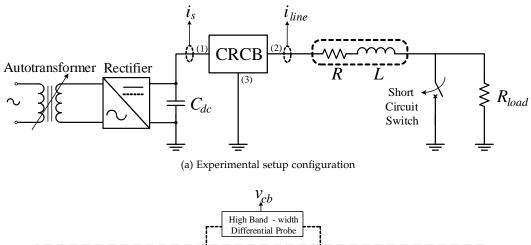

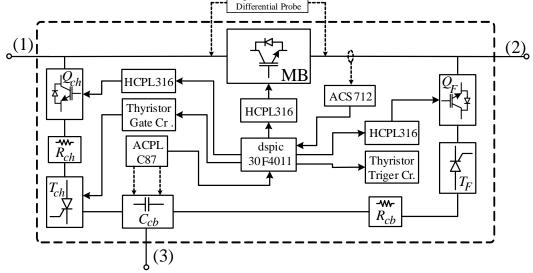

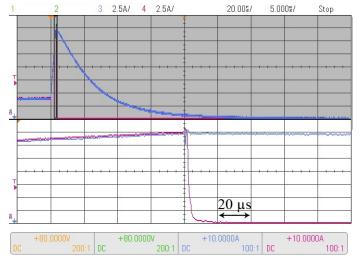

|      | Experimental setup configuration and implemented CRCB block diagram                                                           |     |

|      | The lab-scale prototype                                                                                                       |     |

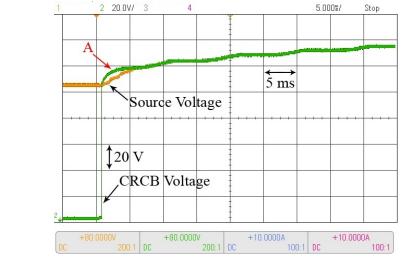

|      | CRCB (green) and dc link (orange) voltages                                                                                    |     |

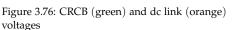

|      | <i>Line</i> (blue) <i>and dc source</i> (red) <i>currents</i>                                                                 |     |

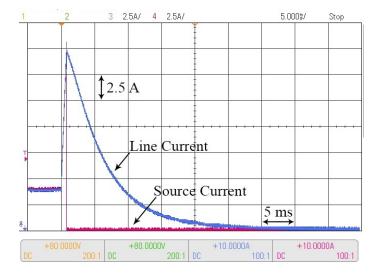

|      | CRCB (green) and capacitor voltage (orange) waveforms                                                                         |     |

| 3.79 | Magnified line (blue) and dc source (red) currents                                                                            | 127 |

|      |                                                                                                                               |     |

### 4 Unidirectional Protection of MT-HVdc Grid

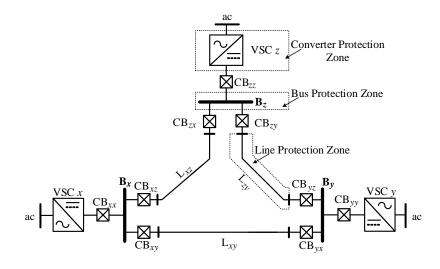

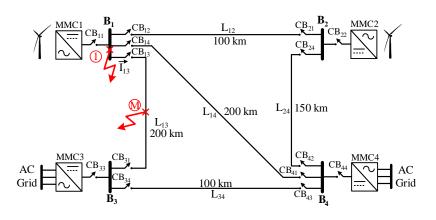

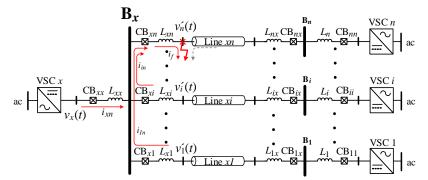

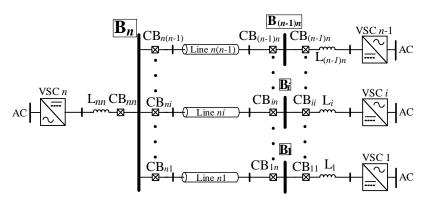

| 4.1  | BCBs arrangement in a multi-terminal HVdc grid                                                                                          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

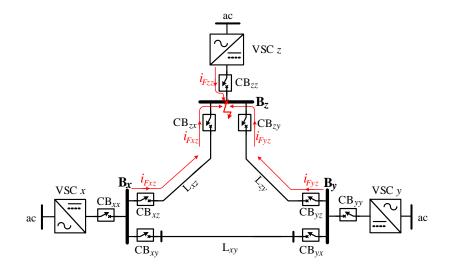

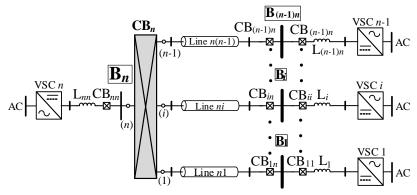

| 4.2  | UCBs arrangement and directions and fault current directions during dc bus fault                                                        |

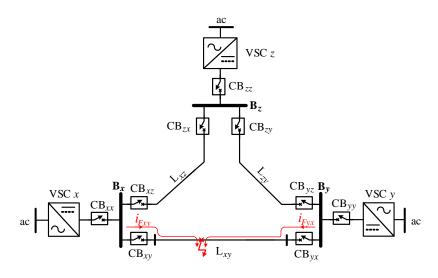

| 4.3  | UCBs arrangement and directions and fault current directions during dc transmission line fault 133                                      |

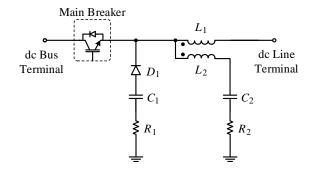

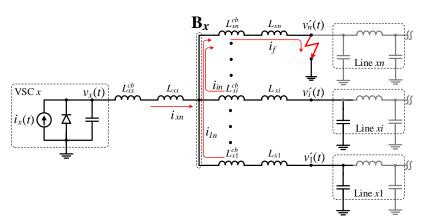

| 4.4  | Unidirectional hybrid dc circuit breaker schematic                                                                                      |

| 4.5  | Test multi-terminal HVdc grid                                                                                                           |

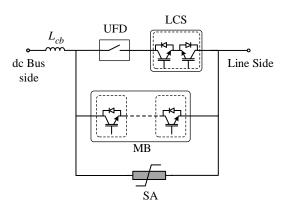

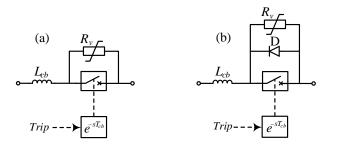

| 4.6  | Aggregated models (a) typical HCB, (b) UHCB                                                                                             |

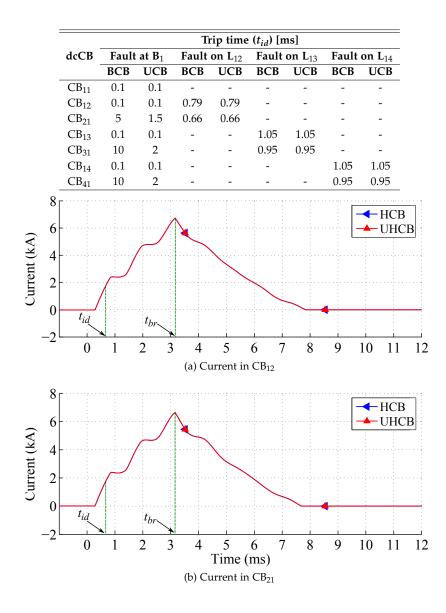

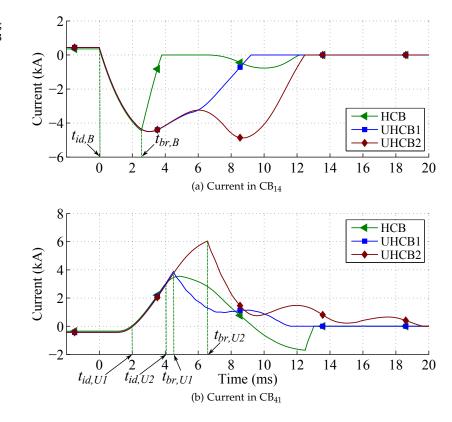

| 4.7  | Current in CB <sub>21</sub> and CB <sub>12</sub> during fault on transmission line L <sub>12</sub> for HCB based and UHCB based         |

|      | protection schemes                                                                                                                      |

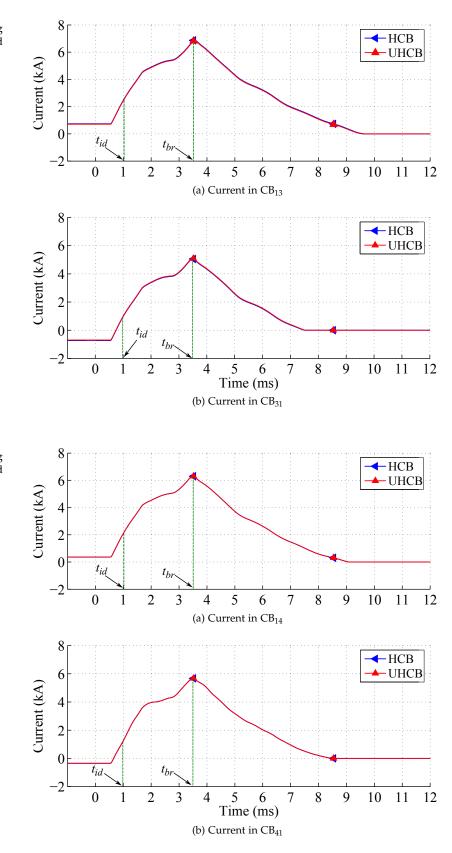

| 4.8  | Current in $CB_{31}$ and $CB_{13}$ during fault on transmission line $L_{13}$ for HCB based and UHCB based                              |

|      | <i>protection schemes.</i>                                                                                                              |

| 4.9  | Current in CB <sub>41</sub> and CB <sub>14</sub> during fault on transmission line L <sub>14</sub> for HCB based and UHCB based         |

|      | <i>protection schemes.</i>                                                                                                              |

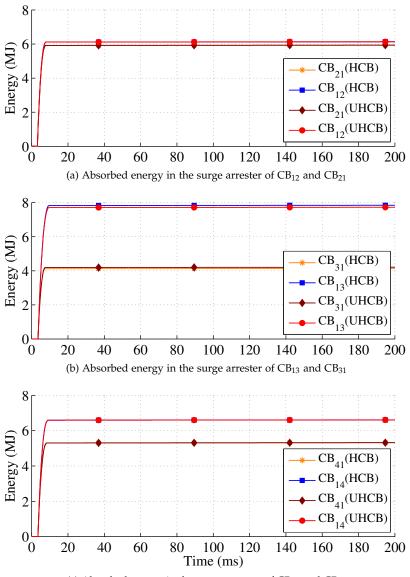

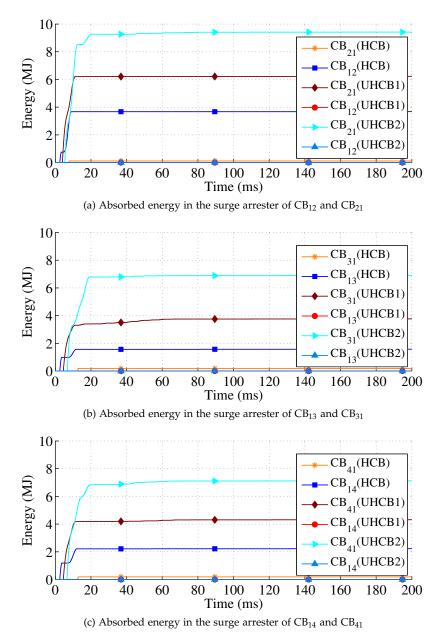

| 4.10 | Absorbed energy in the surge arresters of corresponding dcCBs for HCB based and UHCB based systems.139                                  |

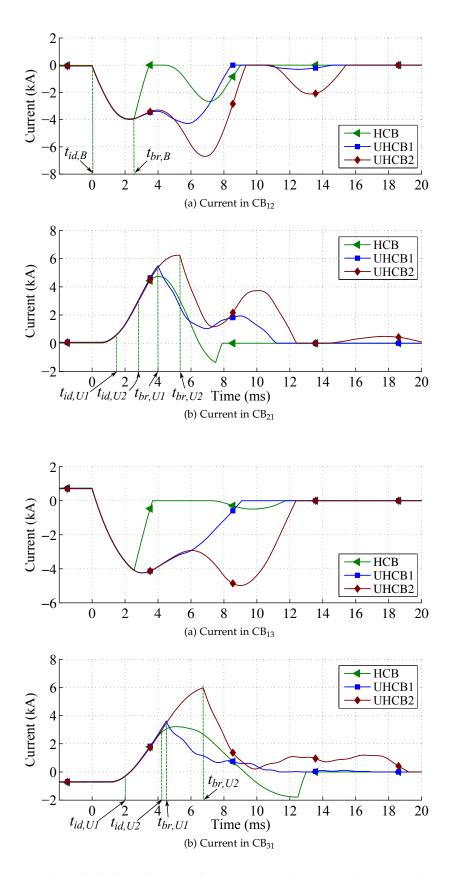

| 4.11 | <i>Current in</i> $CB_{21}$ <i>and</i> $CB_{12}$ <i>during fault at dc bus</i> $B_1$ <i>for HCB based and two UHCB based protection</i> |

|      | schemes                                                                                                                                 |

| 4.12 | <i>Current in</i> $CB_{31}$ <i>and</i> $CB_{13}$ <i>during fault at dc bus</i> $B_1$ <i>for HCB based and two UHCB based protection</i> |

|      | schemes                                                                                                                                 |

| 4.13       | <i>Current in</i> $CB_{31}$ <i>and</i> $CB_{13}$ <i>during fault at dc bus</i> $B_1$ <i>for</i> HCB <i>based and two</i> UHCB <i>based protection</i> |      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1 7 1      | schemes.                                                                                                                                              | 142  |

| 4.14       | Absorbed energy in the surge arresters of corresponding dcCBs for a short circuit fault at dc bus 1 for HCB based and two UHCB based systems.         | 1/13 |

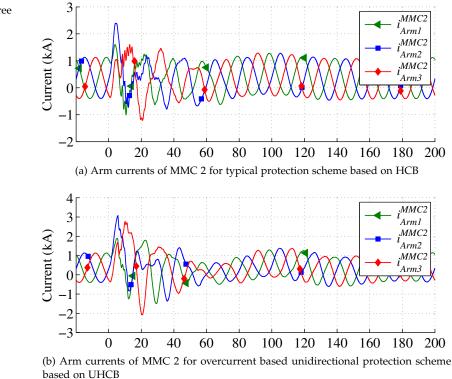

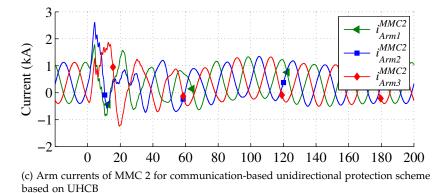

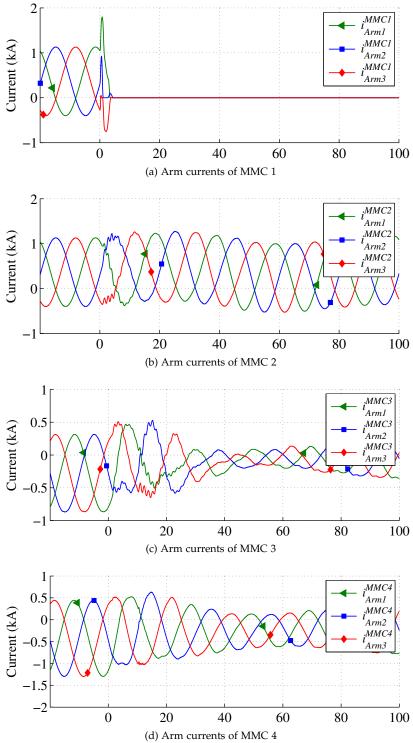

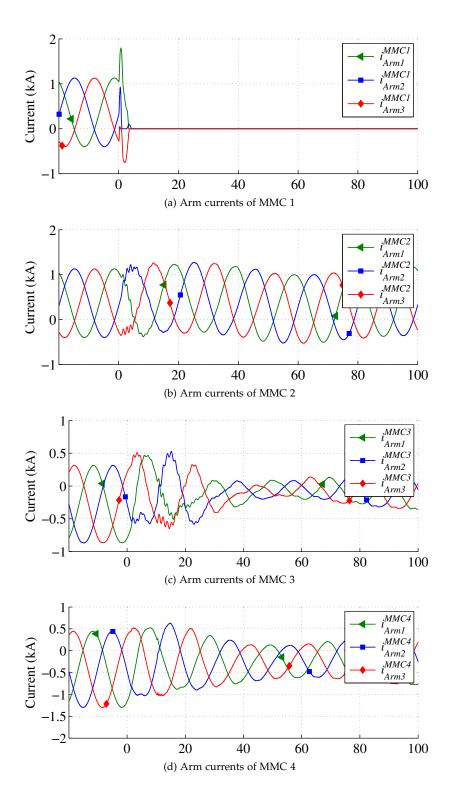

| 415        | Arm currents of MMC 2 for three studied protection schemes.                                                                                           |      |

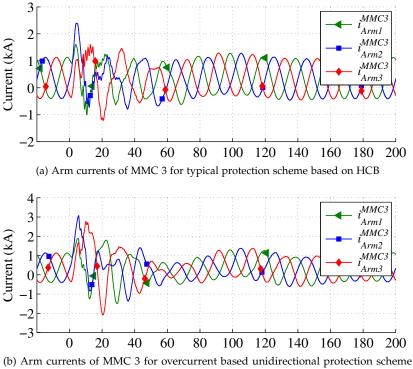

|            | Arm currents of MMC 3 for three studied protection schemes.                                                                                           |      |

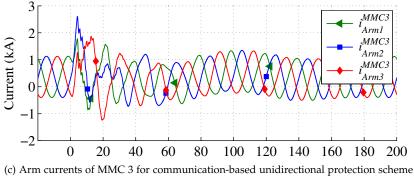

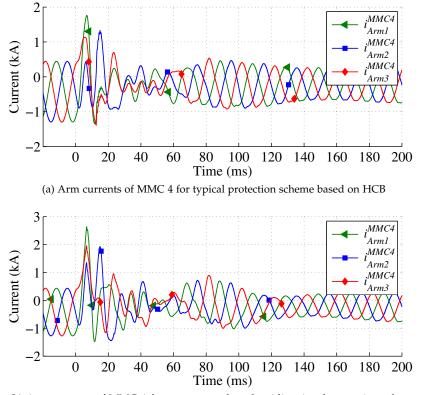

|            | Arm currents of MMC 4 for three studied protection schemes.                                                                                           |      |

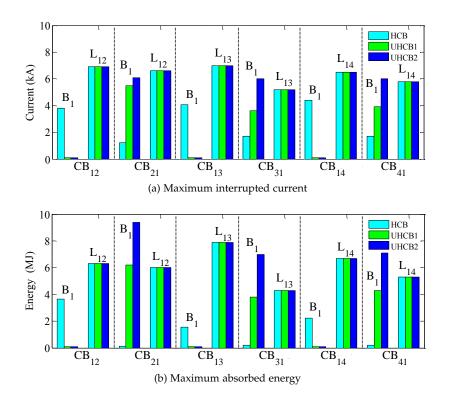

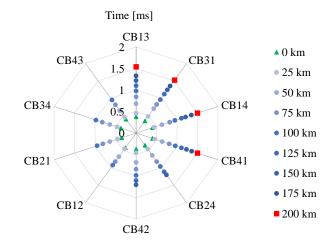

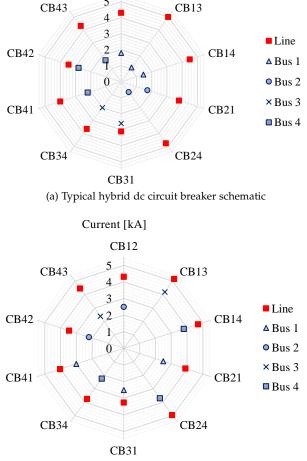

|            | Maximum interrupted current and absorbed energy in different dc circuit breakers during dc bus and                                                    | 110  |

|            | line faults                                                                                                                                           | 147  |

| 4.19       | UCBs arrangement and directions and fault current directions.                                                                                         |      |

|            | (a) Maximum interrupted current and (b) absorbed energy in different dc circuit breakers during dc bus                                                |      |

|            | and line faults.                                                                                                                                      |      |

|            | The topology of typical solid-state dc circuit breaker.                                                                                               | 150  |

| 4.22       | (a) Maximum interrupted current and (b) absorbed energy in different dc circuit breakers during dc bus                                                | 151  |

| 1 73       | and line faults                                                                                                                                       | 151  |

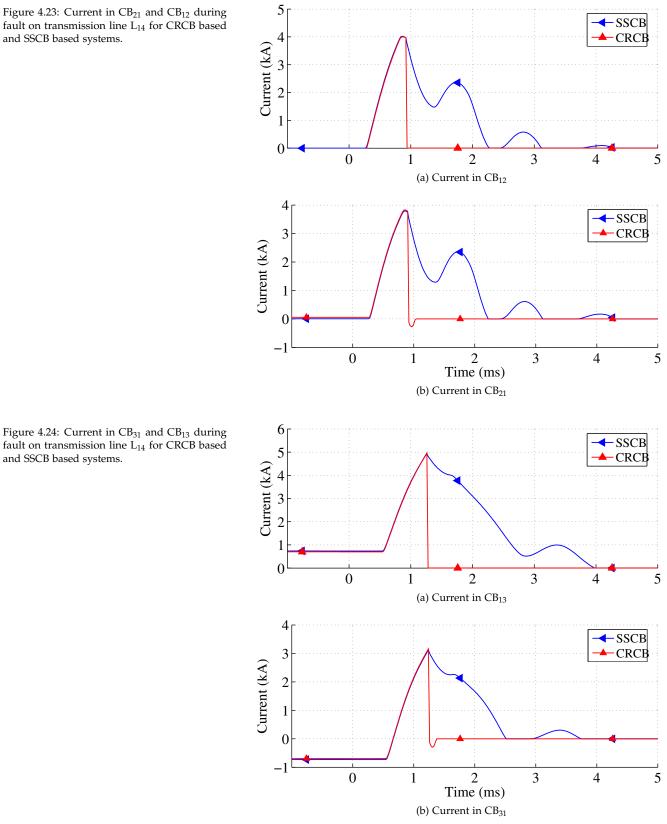

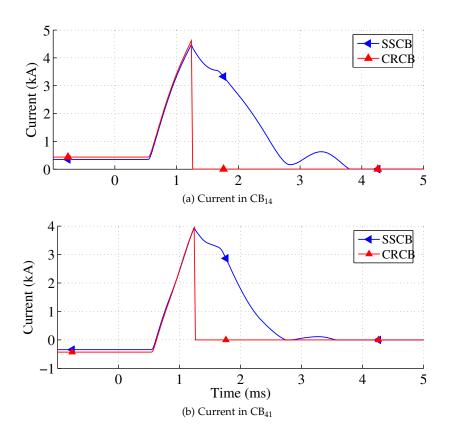

| 4.23       | systems                                                                                                                                               | 152  |

| 4 74       | <i>Current in</i> $CB_{31}$ <i>and</i> $CB_{13}$ <i>during fault on transmission line</i> $L_{14}$ <i>for</i> CRCB based and SSCB based               | 152  |

| 1.21       | systems.                                                                                                                                              | 152  |

| 4.25       | <i>Current in</i> $CB_{31}$ <i>and</i> $CB_{13}$ <i>during fault on transmission line</i> $L_{14}$ <i>for</i> CRCB based and SSCB based               | 102  |

| 1.20       | systems                                                                                                                                               | 153  |

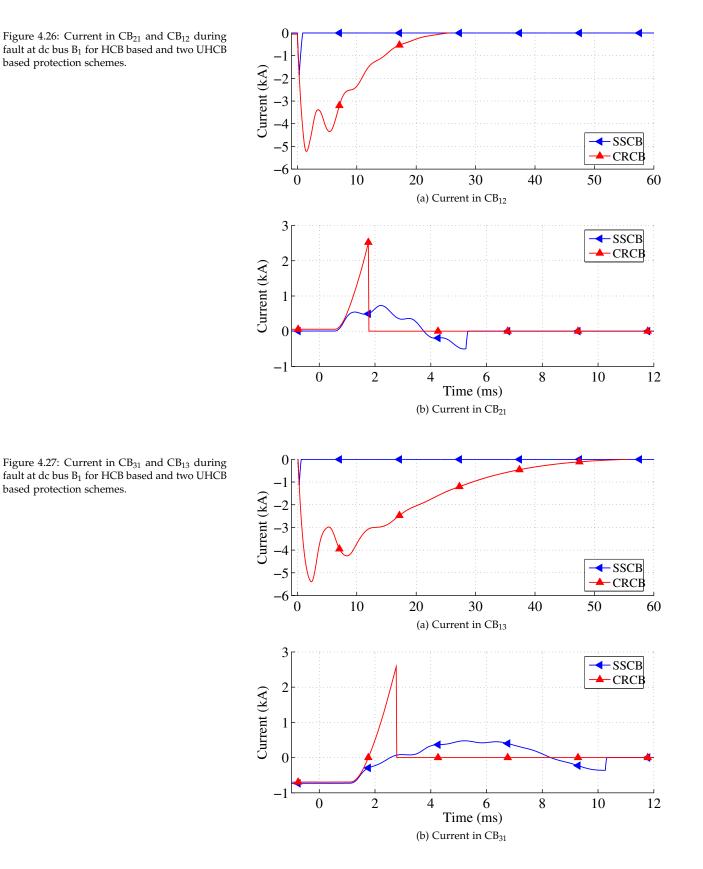

| 4.26       | <i>Current in</i> $CB_{21}$ <i>and</i> $CB_{12}$ <i>during fault at dc bus</i> $B_1$ <i>for</i> HCB <i>based and two</i> UHCB <i>based protection</i> |      |

|            | schemes                                                                                                                                               | 154  |

| 4.27       | <i>Current in</i> $CB_{31}$ <i>and</i> $CB_{13}$ <i>during fault at dc bus</i> $B_1$ <i>for</i> HCB <i>based and two</i> UHCB <i>based protection</i> |      |

|            | schemes                                                                                                                                               | 154  |

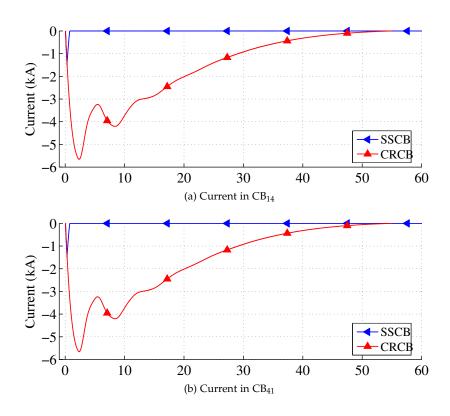

| 4.28       | Current in $CB_{31}$ and $CB_{13}$ during fault at dc bus $B_1$ for HCB based and two UHCB based protection                                           |      |

|            | schemes                                                                                                                                               | 155  |

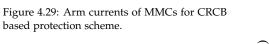

|            | Arm currents of MMCs for CRCB based protection scheme                                                                                                 |      |

|            | Arm currents of MMCs for SSCB based protection scheme.                                                                                                | 157  |

| 4.31       | (a) Maximum interrupted current and (b) absorbed energy in different dc circuit breakers during dc bus                                                |      |

|            | and line faults.                                                                                                                                      |      |

| 4.32       | UCBs arrangement and directions and fault current directions.                                                                                         | 158  |

| Fau        | It Current Limiting Hybrid dc Circuit Breaker                                                                                                         | 163  |

|            |                                                                                                                                                       |      |

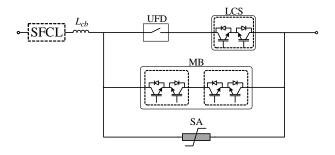

| 5.1<br>5.2 | SFCL integration into the structure of hybrid dc circuit breaker.                                                                                     |      |

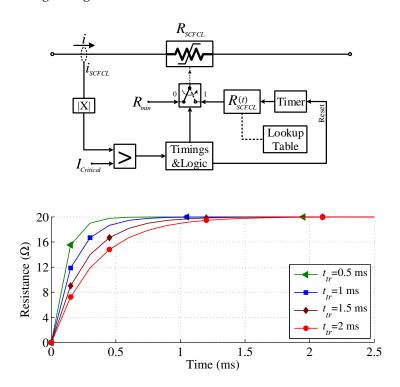

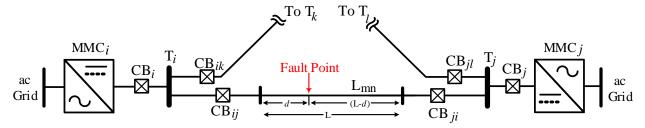

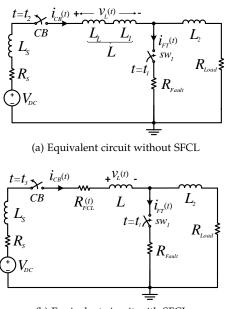

| 5.2        |                                                                                                                                                       |      |

| 5.3<br>5.4 | Generic SFCL characteristics plotted out of look up table                                                                                             |      |

| 5.4<br>5.5 | Simplified equivalent circuit.                                                                                                                        |      |

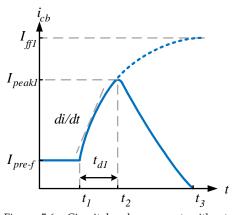

| 5.6        | Circuit breaker current without SFCL.                                                                                                                 |      |

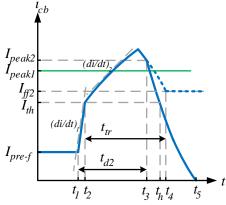

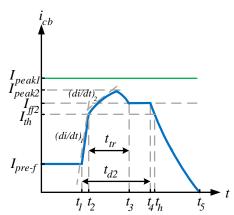

| 5.7        | Circuit breaker current with SFCL when $t_{d2} < t_{tr}$ and $I_{ff2} < I_{peak1}$ .                                                                  |      |

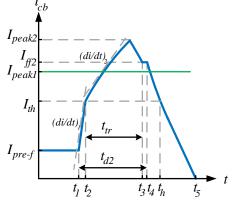

| 5.8        | Circuit breaker current with SFCL when $t_{d2} > t_{tr}$ and $I_{ff2} > I_{peak1}$                                                                    |      |

| 5.9        | Circuit breaker current with SFCL when $t_{d2} > t_{fr}$ and $I_{ff2} < I_{peak1}$ .                                                                  |      |

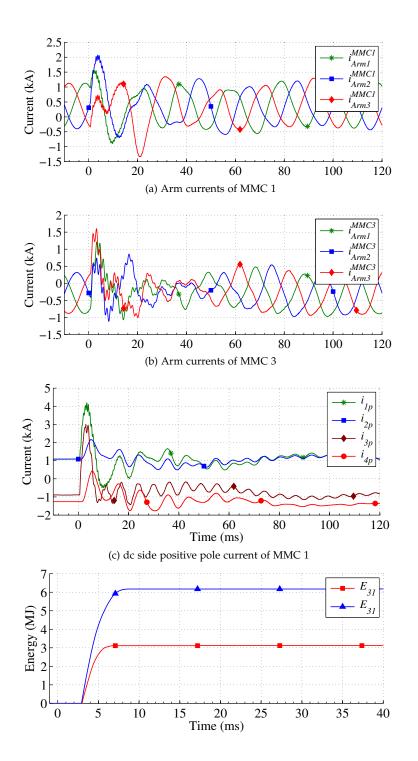

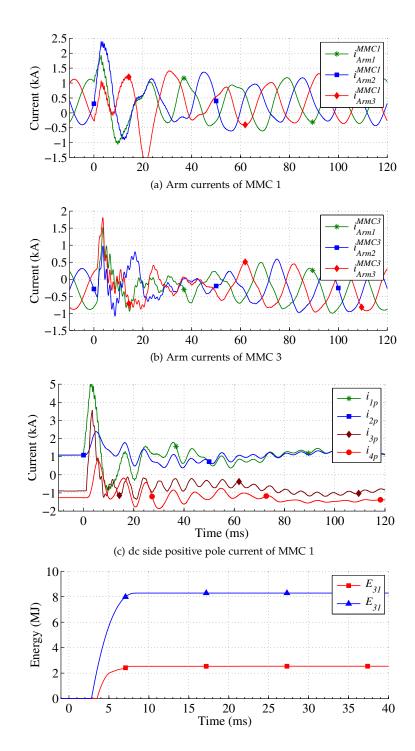

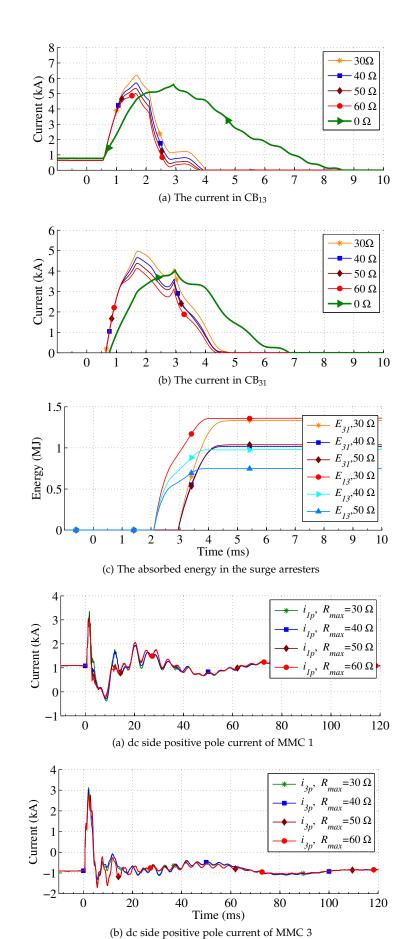

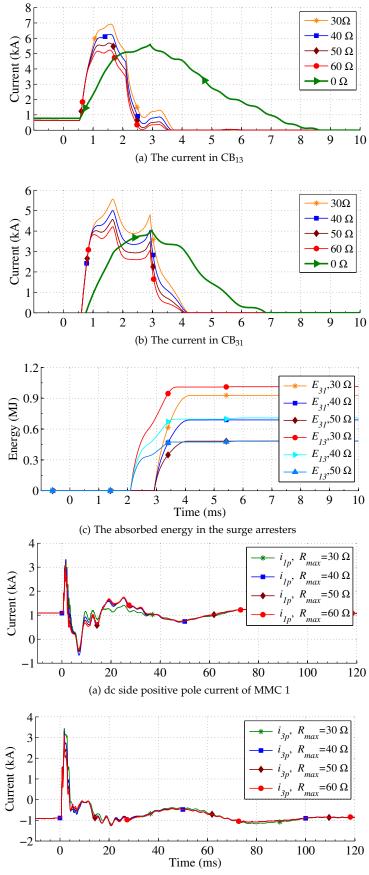

|            | The MMCs arm currents during a midpoint fault on transmission line $L_{13}$ without SFCL.                                                             |      |

|            | Absorbed energy in the surge arresters of corresponding dcCBs during a midpoint fault on transmission                                                 | 1    |

|            | line $L_{13}$ without SFCL.                                                                                                                           | 171  |

| 5.12       | The MMCs arm currents during an endpoint fault on transmission line $L_{13}$ without SFCL                                                             |      |

7 Current Flow Controlling

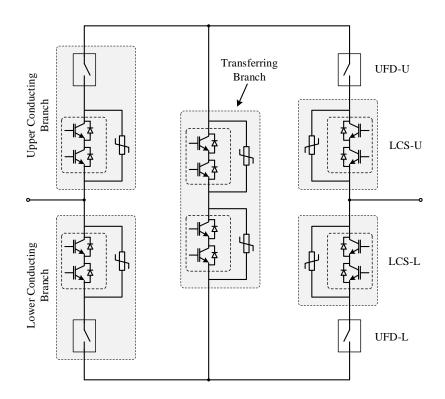

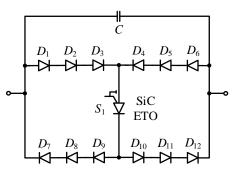

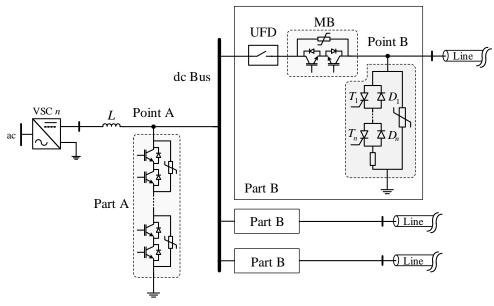

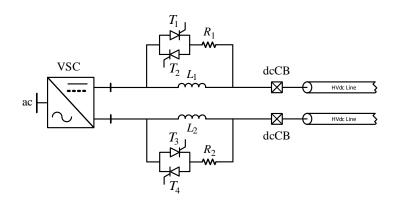

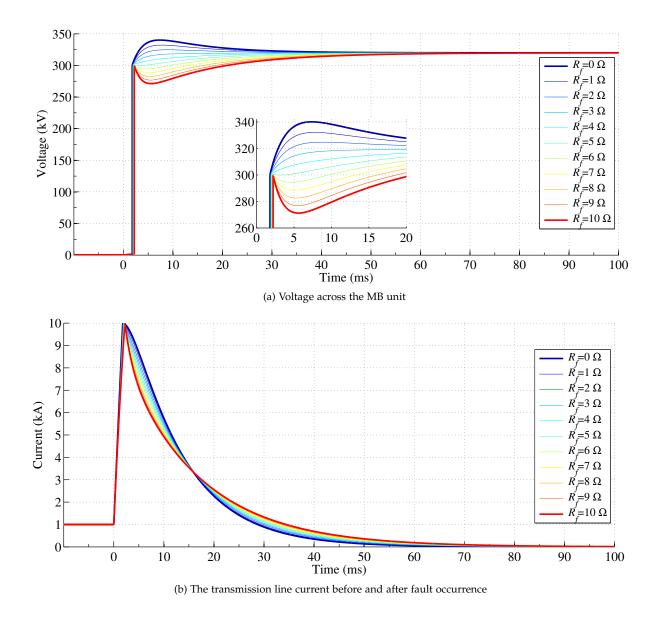

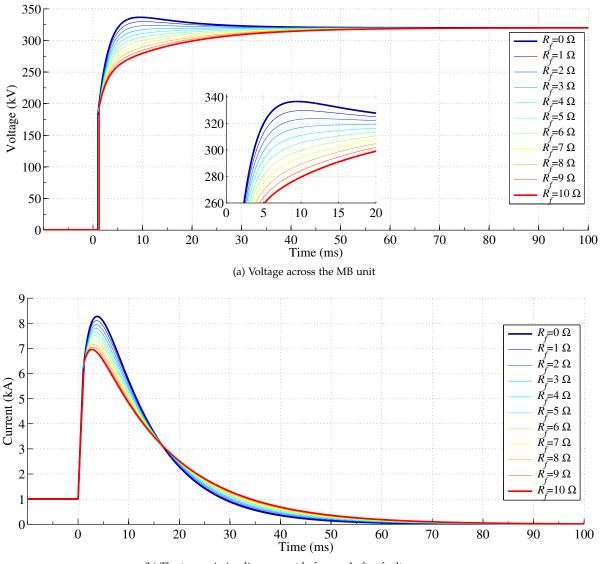

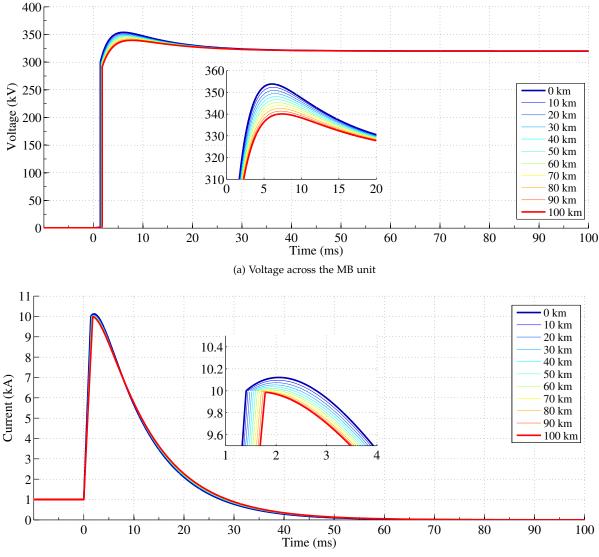

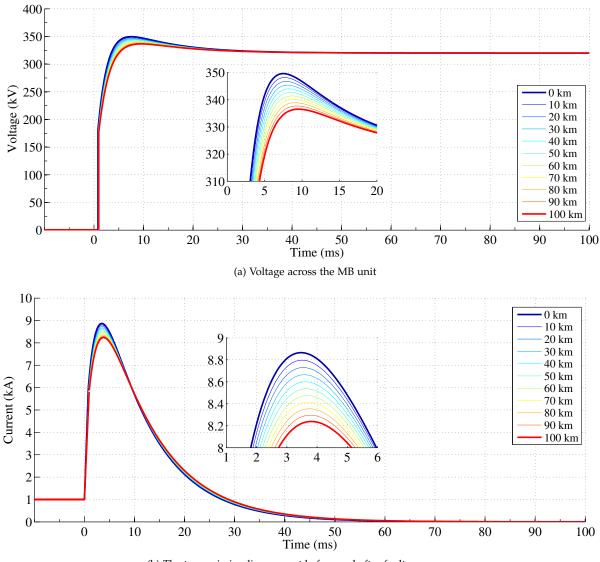

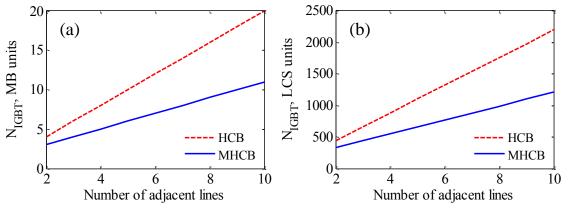

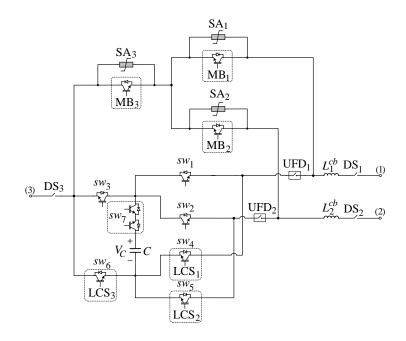

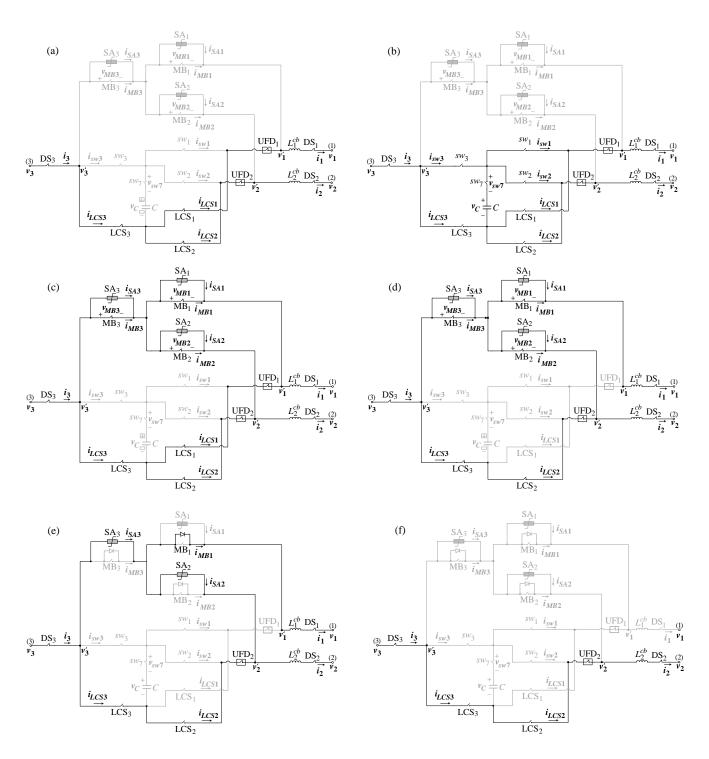

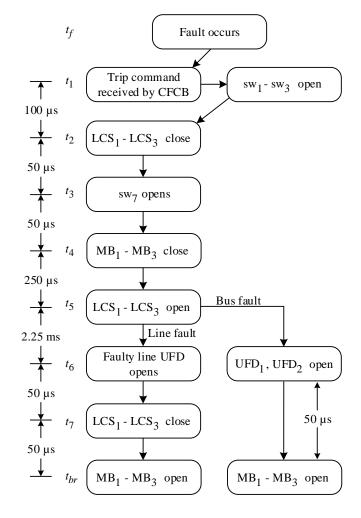

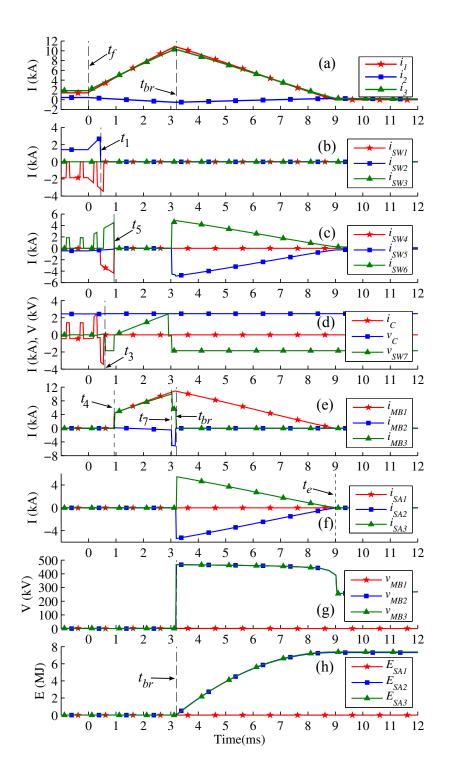

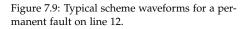

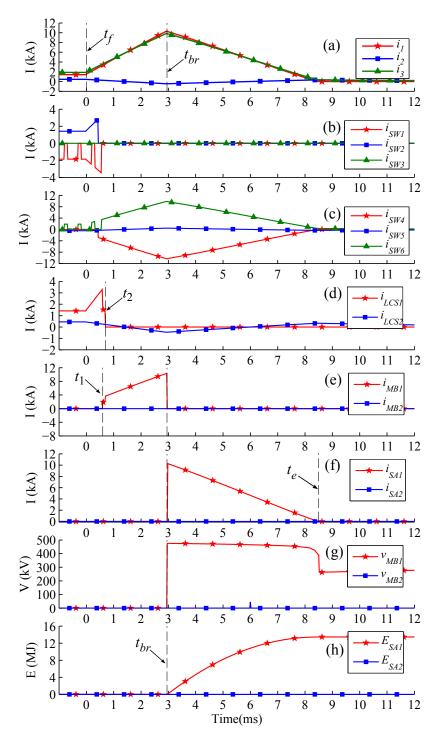

|   | 5.13                                                                                                                      | Absorbed energy in the surge arresters of corresponding dcCBs during an endpoint fault on transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                         |