FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Automatic implementation of a re-configurable logic over ASIC design flow

José Delfim Ribeiro Valverde

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Advisor: Prof. João Canas Ferreira Second Advisor: Eng. Luis Cruz

July 4, 2017

© José Delfim Ribeiro Valverde, 2017

# Resumo

A indústria semicondutora tem enfrentado desafios devido à evolução dos circuitos integrados (*Integrated Circuits, IC*) para *System–on–a–Chip* (*SoC*), cujo *design* se encontra cada vez mais complexo. Assim, tem-se intensificado a necessidade de se efetuarem validações extensas dos circuitos, antes do processo de fabrico, de forma a assegurar um circuito produzido mais correto.

Simultaneamente, com o intuito de dar resposta à atual procura de ciclos de produção mais rápidos, têm sido executados importantes testes de interoperabilidade no circuito final, em silício. Contudo, destes testes poderão resultar erros inesperados, obrigando à completa recusa do *chip* produzido e à necessidade de se iniciar novamente todo o ciclo de produção, despendendo tempo e recursos extra.

Uma das soluções para este tipo de problemas corresponde à substituição do circuito original, de lógica fixa, por um implementado em lógica reconfigurável.

Ao recorrer a este tipo de arquiteturas, o projetista fica habilitado a realizar pequenas alterações, localmente e em tempo útil, alterando algumas funcionalidades e corrigindo pequenos erros, resultantes dos testes de interoperabilidade efetuados em silício. De forma a incluir circuitos reconfiguráveis em projetos para *SoC*, alguns fornecedores produzem e vendem núcleos programáveis do tipo *hard* para serem incluídos em projetos. Em oposição, outros fornecedores utilizam uma abordagem chamada *soft*, na qual vendem uma versão *RTL* (*Register Transfer Level*) da lógica programável, que pode ser sintetizada utilizando uma abordagem *standard cell*.

Porém, uma vez que as soluções geradas por estes métodos estão dependentes de decisões dos próprios fornecedores, nenhum destes métodos permite criar dispositivos lógicos que estejam otimizados para as aplicações de um projetistas de circuitos integrados.

Portanto, surge a necessidade de se estudar um novo fluxo de projeto, de modo a que este possa ser integrado num processo habitual de produção efetuado pelo projetista, e reutilizado em múltiplos projetos e tecnologias, de forma a criar uma arquitetura programável otimizada para diferentes implementações.

Desta forma, fazendo uso do fluxo de projeto produzido no âmbito desta dissertação, foi possível comparar a área, consumo energético e velocidade lógica de um dispositivo programável com um não – programável. Nesta análise observou-se um aumento médio do tamanho na ordem das 380 vezes, uma diminuição da velocidade lógica em 4 vezes e um aumento da ordem das 40 vezes do consumo energético.

Tendo em conta que a abordagem utilizada se baseou numa estratégia em *standard cell*, na qual existe uma falta de otimização dos elementos utilizados numa perspetiva da criação de um dispositivo programável, denotou-se que os valores obtidos estavam de acordo com o expectável. Assim sendo, devida à elevada magnitude dos valores encontrados, esta solução apresenta-se como impraticável e pouco apelativa para a indústria. Todavia foi demonstrado que é possível melhorar o fluxo de projeto do projetista de *ICs* de forma a que este possa produzir uma arquitetura programável sem ter de mudar o seu processo normal de produção extensivamente.

ii

# Abstract

The available density and complexity on Integrated Circuits (IC) have been increasing, following the improvement of technologies to design and fabric ICs leading to a challenging evolution, in the complex nature of digital ICs on System on a Chip (SoC) design, to the semiconductor industry. As such an extensive validation before fabrication has become a demanding pressure to ensure design correctness for the produced circuit.

At the same time, with the current demand for faster turnaround development cycles, major interoperability tests are already performed in actual silicon, as errors can result in testing, the disposal of the produced chip and the need to create a new production cycle results in time and resources waste.

One of the clear solutions to this problem is the replacement of the original fixed logic with a reprogrammable one. As this type of architecture can empower the designer with the ability to perform minor updates, on site, changing minor errors resulted from interoperability tests already performed in silicon or/and adding some necessary, minor functionalities.

To add reconfigurability, some vendors sell programmable cores in a "hard" macro style, that can be included in the developer design; others, supply Register-transfer level (RTL) versions of their programmable logic that can be synthesized using standard cell approach often called a "soft" approach. However, none of this method answer to the question of replacing the fixed logic standard application produced from a standard IC designer flow, into a re-configurable logic, that can be used

So, a new workflow must be studied, so that can be integrated into the standard work of the IC developer, that can be used in multiple projects and technologies, to create a flexible architecture suitable for different implementations.

Using the design flow produced in this dissertation, the programmable device that was produced was compared to the non-programmable architecture, where the solution exhibited an average size increase of 380 times, a speed decrease of 4 times, and a power increase of around 40 times.

These values are high and be impractical and non-appealing to an industry standard. Nonetheless, this work found that was possible to create a design flow that could empower the IC developer to create, from the same Verilog representation, a programmable device in his standard IC workflow. iv

# Acknowledgments

First I would like to thank my Supervisors Prof. João Canas Ferreira and to Eng. Luis Cruz, for all the help, encouragement and suggestions that helped me to research, and developing and writing this dissertation. All Synopsys Engineers, but especially to Helder Campos and to João Martins, that were timeless help me in many problems faced during this dissertation. Also, I must express my profound gratitude to my parents and to Beatriz, for all advice, unfailing support, and encouragement throughout my years of study and through the process of developing this dissertation. Obrigado.

José Delfim Ribeiro Valverde

vi

"The mind is like a parachute... It only works if we keep it open."

Albert Einstein

viii

# Contents

| 1 | Intr | oduction                                                                            | 1        |

|---|------|-------------------------------------------------------------------------------------|----------|

|   | 1.1  | Motivation                                                                          | 1        |

|   | 1.2  | Objectives                                                                          | 2        |

|   | 1.3  | Thesis Organization                                                                 | 4        |

| 2 | Lite | rature Review and Background Work                                                   | 7        |

|   | 2.1  | Application-Specific Integrated Circuits (ASICs)                                    | 9        |

|   | 2.2  | Introduction to Programmable Logic Devices (PLD)                                    | 10       |

|   |      | 2.2.1 Programmable Logic applications                                               | 10       |

|   | 2.3  | Field Programmable Gate Array (FPGAs)                                               | 11       |

|   |      | 2.3.1 FPGA Architecture                                                             | 12       |

|   |      | 2.3.2 FPGA Logic Blocks                                                             | 13       |

|   |      | 2.3.3 Embedded FPGA                                                                 | 16       |

|   | 2.4  | Computer-aided design (CAD) Flows                                                   | 17       |

|   |      | 2.4.1 ASIC Design Flow                                                              | 17       |

|   |      | 2.4.2 FPGA Design Flow                                                              | 18       |

|   |      | 2.4.3 eFPGA Design Flow                                                             | 19       |

|   | 2.5  | Summary                                                                             | 21       |

| 3 | Proc | grammable Device Generation Design Flow                                             | 23       |

| · | 3.1  | Global Considerations                                                               | 24       |

|   | 3.2  | Phase 1: VTR                                                                        | 25       |

|   | 3.3  | Phase 2: Pre-VTR                                                                    | 28       |

|   | 3.4  | Phase 3: VTR to Programmable Device Generator                                       | 28       |

|   | 3.5  | Phase 4: Reconfigurability addition                                                 | 30       |

|   | 3.6  | Conclusions                                                                         | 31       |

| 4 | Dear | cription of Tools used in the Design Flow                                           | 35       |

| 4 |      | Design Compiler                                                                     | 35<br>36 |

|   | 4.1  | 4.1.1    GTECH Python Parser                                                        | 30<br>38 |

|   | 4.2  | -                                                                                   | 38       |

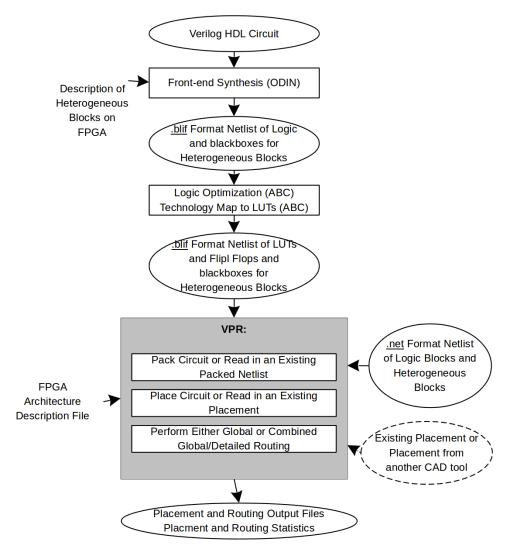

|   | 4.2  | VTR flow                                                                            |          |

|   |      | 4.2.1 FPGA Architecture Description Input File                                      | 39       |

|   |      | 4.2.2 ODIN 2                                                                        | 43       |

|   |      | 4.2.3 ABC                                                                           | 44       |

|   |      | 4.2.4 VPR                                                                           | 45       |

|   | 4.3  | VTR to Programmable Device Generator                                                | 46       |

|   |      |                                                                                     |          |

|   | 110  | 4.3.1       Input Reading         4.3.2       Internal Architectural Representation | 47<br>47 |

|   |             | 4.3.3     | Bitstream Creation                                                 | 48        |

|---|-------------|-----------|--------------------------------------------------------------------|-----------|

|   |             | 4.3.4     | Output generation                                                  | 50        |

|   | 4.4         | Conclu    | isions                                                             | 51        |

| 5 | Desc        | ription   | of a Programmable Architecture                                     | 53        |

|   | 5.1         | -         | c programmable cores                                               | 53        |

|   | 5.2         | -         | Architectures and Production                                       | 55        |

|   |             | 5.2.1     | Complex Logic Blocks                                               | 55        |

|   |             | 5.2.2     | FPGA Routing                                                       | 58        |

|   |             | 5.2.3     | Configuration Bits                                                 | 59        |

|   |             | 5.2.4     | Summary                                                            | 60        |

|   | 5.3         |           | g Structure Studies                                                | 60        |

|   | 5.5         | 5.3.1     | Routing Structure based on basic Modules                           | 61        |

|   |             | 5.3.2     | Routing Structure based on Multiplexers                            | 62        |

|   | 5.4         |           | ecture Decisions Details                                           | 63        |

|   | 5.4         | 5.4.1     | Architectures Comparison                                           | 63        |

|   |             | 5.4.2     | Architecture Details                                               | 65        |

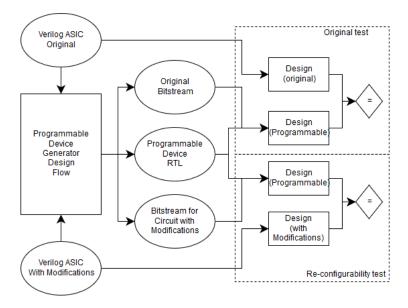

|   | 5.5         |           | onal correctness                                                   | 66        |

|   |             |           |                                                                    |           |

|   | 5.6         | Conclu    | usions                                                             | 67        |

| 6 | Imp         | lementa   | tion and Results                                                   | <b>69</b> |

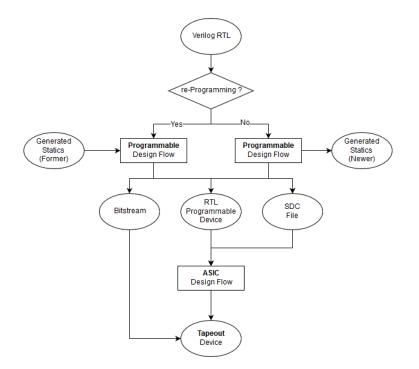

|   | 6.1         | Program   | mmable Device Design Flow                                          | 70        |

|   |             | 6.1.1     | Creation of Programmable Device                                    | 71        |

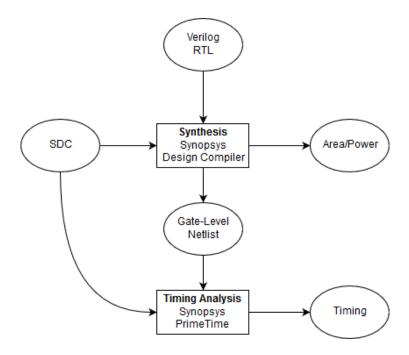

|   |             | 6.1.2     | ASIC Design Flow                                                   | 71        |

|   | 6.2         | Implen    | nentation process                                                  | 72        |

|   |             | 6.2.1     | Design problems                                                    | 72        |

|   |             | 6.2.2     | Synthesis approach                                                 | 75        |

|   | 6.3         | Compa     | rison Metrics and Generated Results                                | 77        |

|   |             | 6.3.1     | Measures to compare implementations                                | 77        |

|   |             | 6.3.2     | Comparison between ASIC fixed logic to the Programmable device im- |           |

|   |             |           | plementation                                                       | 77        |

|   |             | 6.3.3     | Comparison between "soft" and "hard" eFPGA to the Programmable De- |           |

|   |             |           | vice implementation                                                | 82        |

|   |             | 6.3.4     | Modification experiment                                            | 84        |

|   | 6.4         | Conclu    | sion                                                               | 86        |

| 7 | Con         | clusions  | and Future work                                                    | 89        |

|   | 7.1         | Future    | developments                                                       | 91        |

| A | XMI         | L file us | ed                                                                 | 93        |

| р | Ever        | nnla Or   | strute Concreted by VTD to Programmable Device Concreter           | 97        |

| B | Exar<br>B.1 | -         | Itputs Generated by VTR to Programmable Device Generator           | 97<br>97  |

|   | В.1<br>В.2  |           | mmable device RTL                                                  | 97<br>98  |

|   | <b>D</b> .2 | riogral   |                                                                    | 70        |

| С | Circ        |           | l to test Reprogramability                                         | 103       |

|   | <b>C</b> .1 | -         | al Verilog                                                         | 103       |

|   | C.2         |           | cation A                                                           | 105       |

|   | C.3         | Modifi    | cation B                                                           | 105       |

|    | C.4    | Modifi  | cation D                             | 106 |

|----|--------|---------|--------------------------------------|-----|

|    | C.5    | Modifi  | cation C                             | 108 |

| D  | Desi   | gn Flov | v Example                            | 109 |

|    | D.1    | Work 1  | Directory                            | 109 |

|    | D.2    | Runnii  | ng the generation script             | 110 |

|    | D.3    | Script  | description                          | 110 |

|    |        | D.3.1   | Initial configuration                | 110 |

|    |        | D.3.2   | Pre-VTR                              | 111 |

|    |        | D.3.3   | Programmable device generation       | 112 |

|    |        | D.3.4   | Bitstream generation                 | 114 |

|    |        | D.3.5   | VTR to Programmable device generator | 115 |

| Re | eferen | ces     |                                      | 117 |

## CONTENTS

# **List of Figures**

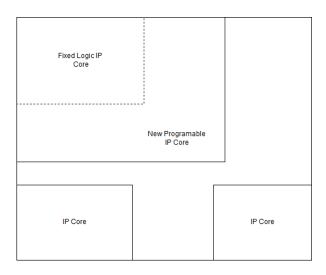

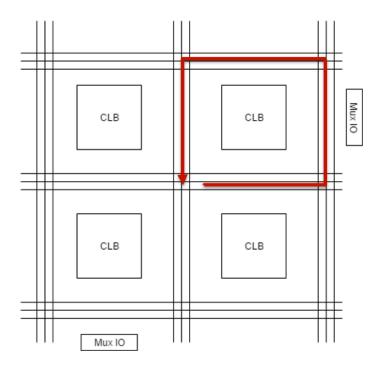

| 1.1        | Example of the created device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

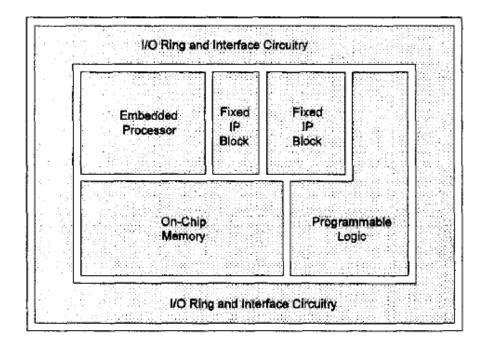

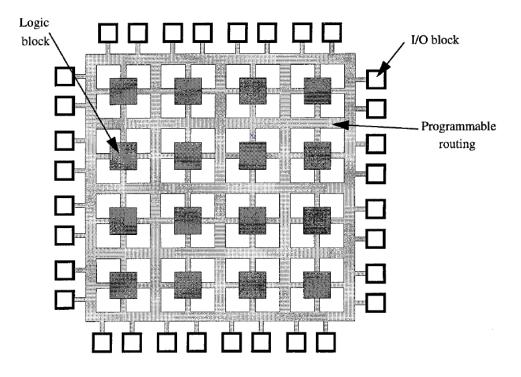

| 2.1<br>2.2 | Example of a SoC design    Image: Constraint of the second | 8<br>12 |

| 2.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12      |

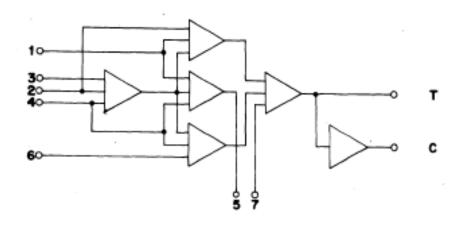

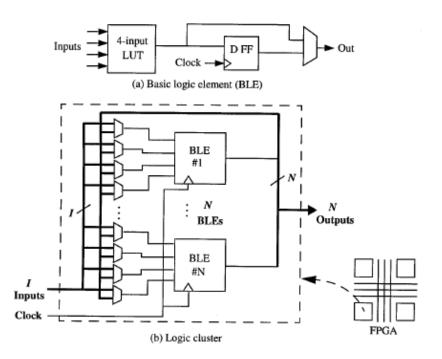

| 2.3<br>2.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16      |

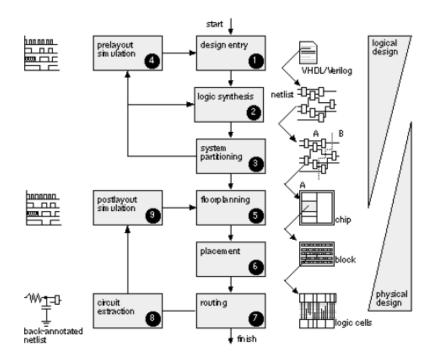

| 2.4        | 6 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18      |

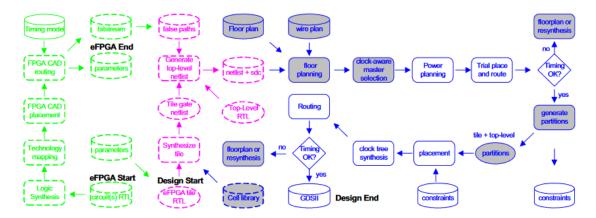

| 2.5<br>2.6 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21      |

| 2.0        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21      |

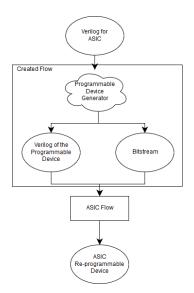

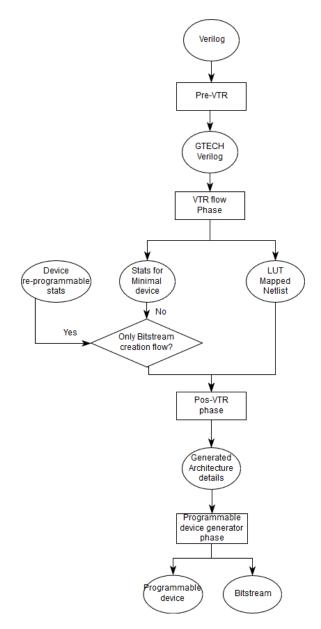

| 3.1        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24      |

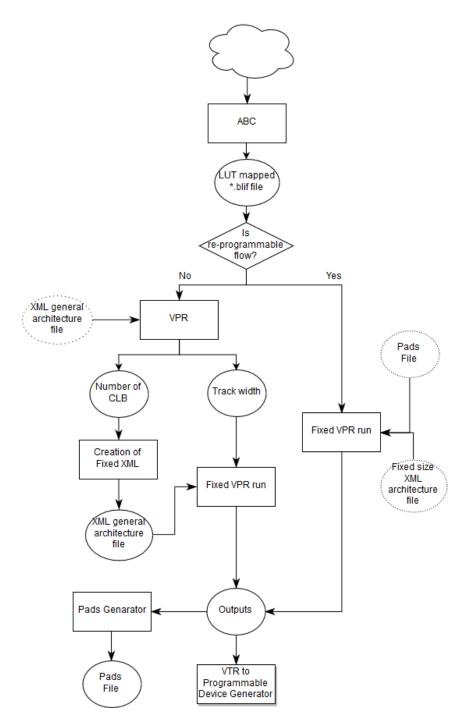

| 3.2        | Overview of the Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26      |

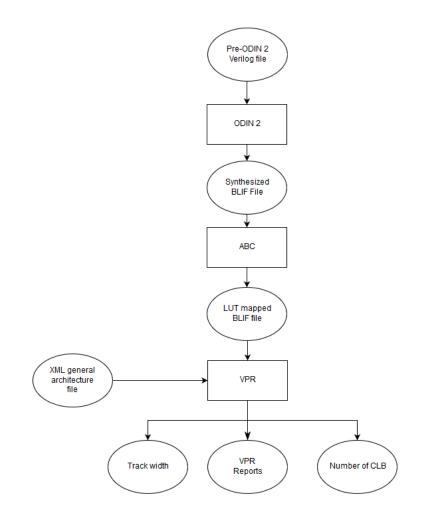

| 3.3        | VTR phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27      |

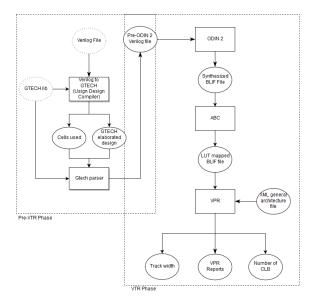

| 3.4        | Pre-VTR and VTR phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29      |

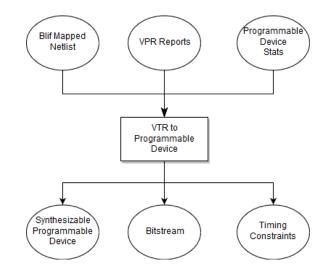

| 3.5        | VTR to Programmable Device Generator phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31      |

| 3.6        | Post-VTR phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32      |

| 4 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

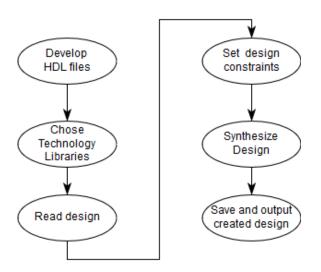

| 4.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36      |

| 4.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37      |

| 4.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39      |

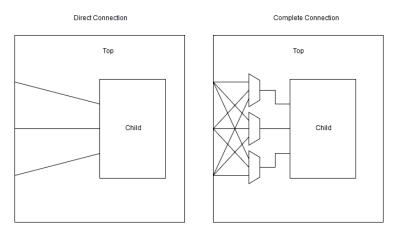

| 4.4        | Direct connection and Complete connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43      |

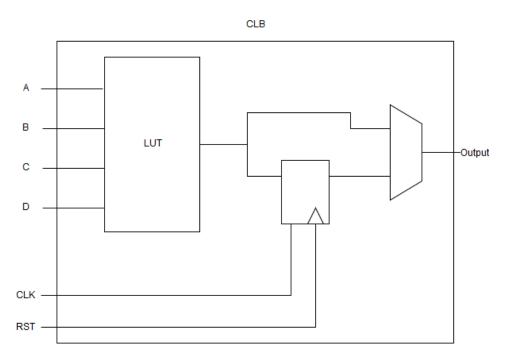

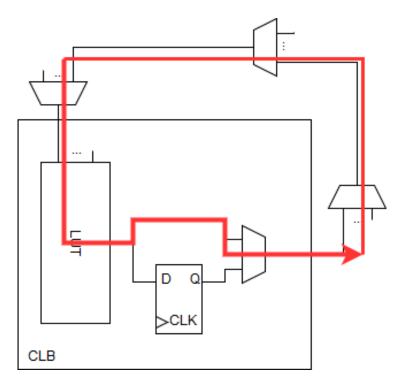

| 5.1        | CLB Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56      |

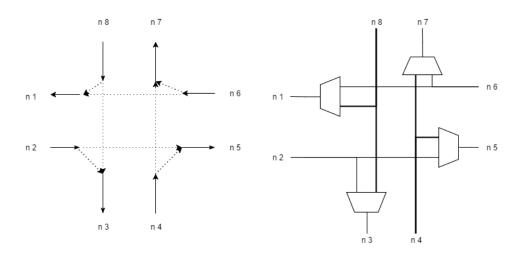

| 5.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59      |

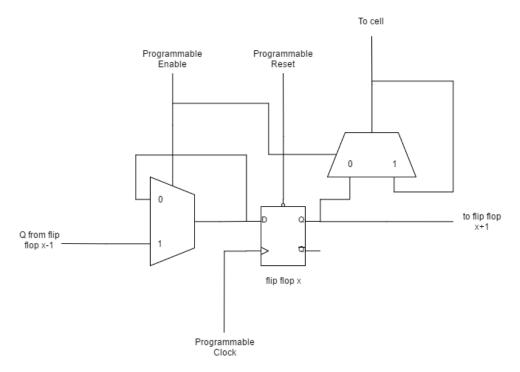

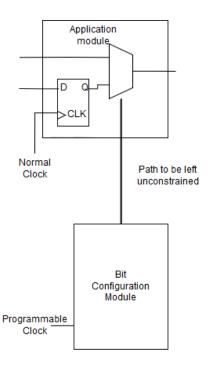

| 5.3        | Configuration Flip-Flop Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50      |

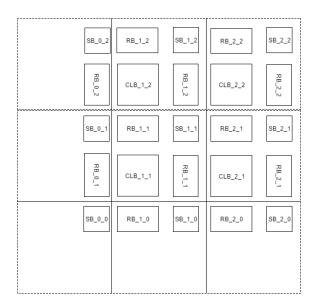

| 5.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51      |

| 5.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55      |

| 5.6        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57      |

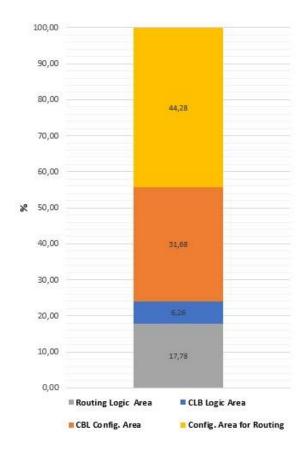

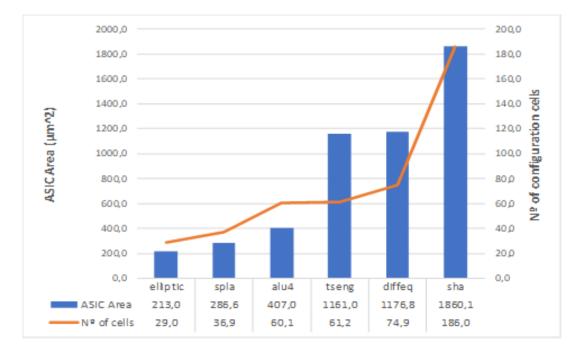

| 6.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -0      |

| 6.1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70      |

| 6.2        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72      |

| 6.3        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73      |

| 6.4        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73      |

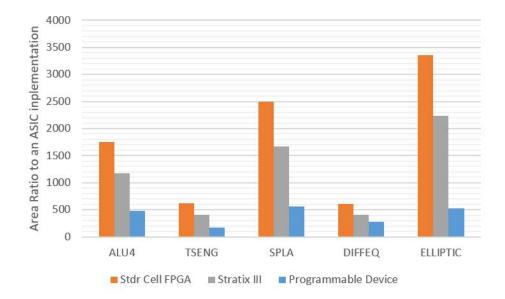

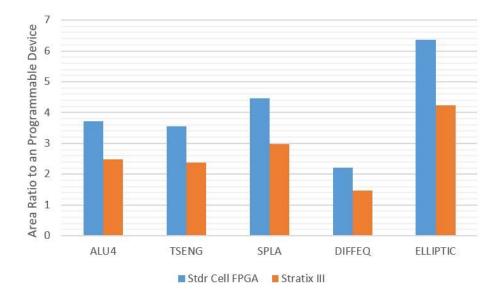

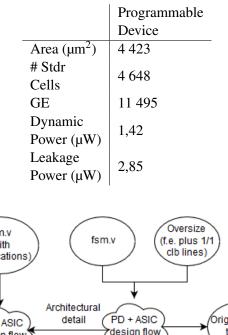

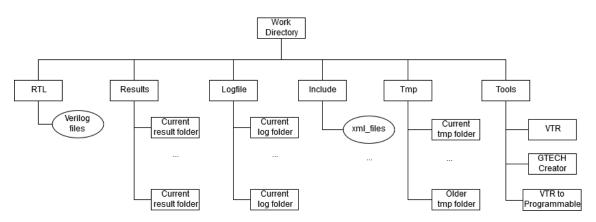

| 6.5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74      |