FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# **Real-Time Scheduling on Multi-core: Theory and Practice**

Paulo Manuel Baltarejo de Sousa

Doctoral Program in Informatics Engineering Supervisor: Prof. Eduardo Manuel Medicis Tovar Second Supervisor: Prof. Luís Miguel Pinho Almeida

October 29, 2013

© Paulo Manuel Baltarejo de Sousa, 2013

### **Real-Time Scheduling on Multi-core: Theory and Practice**

Paulo Manuel Baltarejo de Sousa

Doctoral Program in Informatics Engineering

October 29, 2013

## Abstract

Nowadays, multi-core platforms are commonplace for efficiently achieving high computational power, even in embedded systems, with the number of cores steadily increasing and expected to reach hundreds of cores per chip in near future. Real-time computing is becoming increasingly important and pervasive, as more and more industries, infrastructures, and people depend on it. For real-time systems too, multi-cores offer an opportunity for a considerable boost in processing capacity, at relatively low price and power. This could, in principle, help with meeting the timing requirements of computationally intensive applications which could not be met on single-cores. However, real-time system designers must adopt suitable approaches for their system to allow them to fully exploit the capabilities of the multi-core platforms. In this line, scheduling algorithms will, certainly, play an important role.

Real-time scheduling algorithms for multiprocessors are typically categorized as global, partitioned, and semi-partitioned. Global scheduling algorithms store tasks in one global queue, shared by all processors. Tasks can migrate from one processor to another; that is, a task can be preempted during its execution and resume its execution on another processor. At any moment, the *m* highestpriority tasks are selected for execution on the *m* processors. Some algorithms of this kind achieve a utilization bound of 100% but generate too many preemptions and migrations. Partitioned scheduling algorithms partition the task set and assign all tasks in a partition to the same processor. Hence, tasks cannot migrate between processors. Such algorithms involve few preemptions but their utilization bound is at most 50%. In semi-partitioned (or task-splitting) scheduling algorithms most tasks are fixed to specific processors (like partitioned), while a few tasks migrate across processors (like global). This approach produces a better balance of the workload among processors than partitioning and consequently presents higher utilization bounds, additionally, it also reduces the contention on shared queues and the number of migrations (by reducing the number of migratory tasks). However, it must ensure that migratory tasks never execute on two or more processors simultaneously.

For all of the categories of scheduling algorithms mentioned, it generally holds that the realtime scheduling theory is based on a set of concepts and assumptions that have little correspondence with practice. The gap between theory and practice is wide, and this compromises both the applicability but also the reliability. Therefore, we believe that efficient scheduling algorithm implementations in real-operating systems can play an important role in reducing the gap between theory and practice. We defined that (i) real-time theory cannot be detached from practical issues and (ii) the schedulability analysis must incorporate practical issues, such as context switch (or task switch) and task release overheads, just to mention a few. Therefore, the real-time theory must be overhead-aware in order to be reliable and must also consider the practical (in most cases, operating system-related) issues to increase its implementability in real operating systems.

In this dissertation, we deal with semi-partitioned scheduling algorithms that are categorized as slot-based task-splitting to achieve the above mentioned claims. To this end, we define a set of design principles to efficiently implement those scheduling algorithms in a real operating system REEMPT-RT-patched L

ii

(a PREEMPT-RT-patched Linux kernel version). Grounded on implementations of the slot-based task-splitting scheduling algorithms in the Linux kernel, we identify and model all run-time overheads incurred by those scheduling algorithms. We, then, incorporate them into a new schedulability analysis. This new theory is based on exact schedulability tests, thus also overcoming many sources of pessimism in existing analysis. Additionally, since schedulability testing guides the task assignment under the schemes in consideration, we also formulate an improved task assignment procedure. The outcome is a new demand-based overhead-aware schedulability analysis that permits increased efficiency and reliability. We also devise a new scheduling algorithm for multiprocessor systems, called Carousel-EDF. Although, it presents some similarities with slotbased task-splitting scheduling algorithms, we classify the Carousel-EDF scheduling algorithm as a reserve-based scheduling algorithm. The underlying theory is also overhead-aware and we also implement it in the Linux kernel.

### Resumo

Hoje em dia, a utilização de plataformas multi-processador de modo a obter maior poder de computação é bastante comum e é expectável que o número de processadores atinja as centenas por plataforma num futuro próximo. Por outro lado, tem-se verificado um aumento da importância da computação de tempo real à medida que é mais usada na indústria, em diversas infraestruturas e mesmo pelas pessoas. Dadas as especificidades dos sistemas de tempo real, estas plataformas representam uma oportunidade para aumentar a capacidade de processamento a baixo custo e com baixo consumo de energia. Todo este poder computacional pode, em princípio, ajudar a satisfazer os requisitos temporais de aplicações com elevada exigência computacional que não consegue ser satisfeita por plataformas equipadas com um só processador. No entanto, na engenharia destes de sistemas de tempo real devem ser adoptadas abordagens adequadas por forma a tirar o máximo proveito destas plataformas multi-processador. Nesse sentido, certamente que os algoritmos de escalonamento de tarefas desempenham um papel importante.

Os algoritmos de escalonamento para sistemas de tempo real em plataformas multi-processador são, geralmente, categorizados como globais, particionados e semi-particionados. Os algoritmos de escalonamentos globais guardam todas as tarefas numa fila global, partilhada por todos os processadores. As tarefas podem migrar entre os processadores; isto é, a execução de uma tarefa pode ser interrompida (preemptada) num processador e recomeçar a execução noutro processador. A qualquer instante, as m tarefas com mais prioridade estão em execução nos m processadores que compõem a plataforma. Alguns algoritmos globais conseguem taxas de utilização de 100%, no entanto à custa de muitas preempções e migrações. Os algoritmos de escalonamentos particionados, dividem (criam partições) as tarefas que compõem o conjunto de tarefas pelos processadores. As tarefas atribuídas a um processador só podem ser executadas por esse processador. Desta forma, as migrações de tarefas não são permitidas e desta forma diminuem o número de preempções. Porém, a taxa de utilização é de 50%. Os algoritmos semi-particionados criam partições com a maior parte das tarefas (como os algoritmos particionados) e as restantes (poucas) podem migrar entre os processadores (como os algoritmos globais). Se por um lado, esta abordagem permite um melhor balanceamento das tarefas entre os processadores e consequentemente uma taxa de utilização maior. Por outro lado, reduz a disputa pelo acesso às filas partilhadas que armazenam as tarefas migratórias e o número de migrações (porque diminuem as tarefas que podem migrar). Contudo, estes algoritmos têm que assegurar que uma tarefa migratória não executa em dois ou mais processadores simultaneamente.

Geralmente, a teoria subjacente a todas as categorias de algoritmos de escalonamento para sistemas de tempo real descritas anteriormente é baseada num conjunto de conceitos e suposições que têm pouca correspondência com a prática; isto é, não têm em conta as especificidades das plataformas e dos sistemas operativos. A diferença entre a teoria e a prática é enorme e consequentemente compromete quer a sua aplicabilidade quer a sua confiabilidade. Portanto, nós acreditamos que implementações eficientes dos algoritmos de escalonamento num sistema operativo podem ajudar a diminuir a diferença entre a teoria e a prática. Assim sendo, nós definimos que (i) a teoria de sistemas de tempo real não pode estar dissociada dos detalhes de implementação e (ii) a análise de escalonabilidade deve incorporar os detalhes da prática, tais como, o custo associado à troca de tarefas no processador, ao aparecimento das tarefas no sistema, entre outras. Portanto, a teoria de sistemas de tempo real deve ter em conta os custos por forma a ser mais confiável e também mais implementável nos sistemas operativos.

Nesta dissertação, nós focamo-nos nos algoritmos semi-particionados, mais especificamente, num conjunto de algoritmos de escalonamento para sistemas de tempo real (para plataformas multi-processador) cuja principal característica é a divisão do tempo em reservas temporais. Com o propósito de alcançar os requisitos enumerados anteriormente, nós definimos um conjunto de princípios para uma implementação eficiente num sistema operativo (neste caso, numa versão do sistema operativo Linux melhorada com funcionalidades apropriadas para sistemas de tempo real). Fundamentado em implementações dos algoritmos em causa no sistema operativo Linux, nós identificamos e modelamos todos os custos operacionais associados à execução desses algoritmos no referido sistema operativo. Então, nós incorporamos todos esses custos operacionais numa nova análise de escalonamento. Esta nova teoria é baseada em testes de escalonabilidade exactos eliminando, desta forma, muitas fontes de pessimismo da análise existente. Esta nova análise permite uma melhoria no processo de criação de partições, isto é, mais tarefas por partição, logo menos partições. O resultado desta nova análise é um aumento da eficiência e da confiabilidade dos algoritmos. Também criamos um novo algoritmo de escalonamento para sistemas multi-processador, designado de "Carousel-EDF". Este algoritmo apresenta algumas semelhanças com os algoritmos em consideração nesta dissertação. A teoria desenvolvida para este novo algoritmo também é baseada em testes de escalonabilidade exactos que também incorpora os inerentes custos operacionais.

## Acknowledgements

The research work leading to this dissertation was developed at the Real-Time Computing Systems Research Centre (CISTER), from the School of Engineering of the Polytechnic Institute of Porto (ISEP/IPP).

I would like to express my thanks to Prof. Eduardo Tovar. He provided me crucial support to successfully develop my research work. Prof. Eduardo Tovar provided me constructive criticism and invaluable guidance that have significantly improved the quality of the work presented in this dissertation.

I am also thankful to Prof. Luís Almeida, for accepting to be my supervisor and also by the great effort in reviewing this dissertation.

Officially, I had two supervisors. Nevertheless, I would like to thank my third, unofficial, supervisor: Konstantinos Bletsas. I have no words to express my gratitude to his outstanding collaboration.

I would like to express my thanks to Prof. Pedro Souto for his insightful comments, discussions, and help, which far exceeded what anyone can ever ask for.

Thanks also to Nuno Pereira for his collaboration in part of the work and especially for his encouragement and friendship. I would like to express my gratitude and appreciation to all my co-authors.

I spent the last 10 years as CISTER collaborator. Therefore, I would like to thank all my colleagues in CISTER for all the great support at various levels and for their encouragement. My special thanks to Sandra Almeida and also to Inês Almeida for the administrative support.

I am teaching assistant at the Department of Computer Engineering of ISEP. I am deeply thankful to all the coordinators of the courses I teach (Luís Lino Ferreira, Luís Nogueira, Alexandre Bragança and Luís Miguel Pinho) for their support, comprehension, and, especially, for freeing me from some teaching-related labour.

I cannot forget my LATEX helper and friend Paulo Matos, thank you.

Finally, I have to express my gratitude and, especially, my happiness for the unconditional love, continuous support, and patience that I have received from my lovely daughters, Rita and Matilde, and from my wife, Elisa. Elisa, this work that I am finishing now is one more step in our life's journey that we started 17 years ago. Without you, I would not be able to finish this work. I love you so much.

This work was supported by FCT (Fundação para a Ciência e Tecnologia) under the individual study grant SFRH/BD/46199/2008.

Paulo Baltarejo Sousa

vi

"All things are difficult before they are easy"

Dr. Thomas Fuller

viii

## Contents

| 1 | Intro | oduction 1                                           |

|---|-------|------------------------------------------------------|

|   | 1.1   | Motivation                                           |

|   | 1.2   | Challenges                                           |

|   | 1.3   | Approach                                             |

|   | 1.4   | Thesis statement                                     |

|   | 1.5   | Contributions                                        |

|   | 1.6   | Outline                                              |

| 2 | Bacl  | kground on multiprocessor platforms 9                |

|   | 2.1   | Introduction                                         |

|   | 2.2   | Hardware in multiprocessor systems                   |

|   |       | 2.2.1 Single-core processors                         |

|   |       | 2.2.2 Multiprocessor systems                         |

|   |       | 2.2.3 Sources of unpredictability                    |

|   | 2.3   | Software in multiprocessor systems                   |

|   |       | 2.3.1 Linux kernel overview                          |

|   |       | 2.3.1.1 Clock and timers                             |

|   |       | 2.3.1.2 Tasks and run-queues in the Linux kernel     |

|   |       | 2.3.1.3 Linux modular scheduling framework           |

|   |       | 2.3.1.4 The real-time scheduling class of Linux      |

|   |       | 2.3.2 The Linux PREEMPT-RT patch                     |

|   |       | 2.3.2.1 Priority inversion and Priority inheritance  |

|   |       | 2.3.2.2 Fully preemptible kernel                     |

|   |       | 2.3.2.3 Locking primitives                           |

|   |       | 2.3.2.4 Threaded ISRs                                |

|   |       | 2.3.2.5 Scheduling policies                          |

|   |       | 2.3.3       Real-time scheduling add-ons       29    |

|   |       | 2.3.4       Micro kernel-based approaches       30   |

|   | 2.4   | Summary         33                                   |

| 3 | Bacl  | kground on real-time systems 35                      |

|   | 3.1   | Introduction                                         |

|   | 3.2   | Basic concepts                                       |

|   |       | 3.2.1 System model                                   |

|   |       | 3.2.2 Fundamental concepts of scheduling             |

|   | 3.3   | Review of relevant work on multiprocessor scheduling |

|   | 3.4   | Comparison of scheduling algorithms                  |

|   | э.т   | 3.4.1 Global scheduling                              |

|   |       |                                                      |

|   |      | 3.4.2 Partitioned scheduling                                                                        |

|---|------|-----------------------------------------------------------------------------------------------------|

|   |      | 3.4.3 Semi-partitioned scheduling                                                                   |

|   |      | 3.4.4 Discussion                                                                                    |

|   | 3.5  | Historical perspective of slot-based scheduling algorithms                                          |

|   | 3.6  | Summary                                                                                             |

| 4 | Slot | -based task-splitting scheduling algorithms 57                                                      |

|   | 4.1  | Introduction                                                                                        |

|   | 4.2  | Assumptions about the hardware architecture                                                         |

|   | 4.3  | Generic slot-based task-splitting 58                                                                |

|   | 4.4  | Overview of specific scheduling schemes                                                             |

|   |      | 4.4.1 Discussion of S-EKG and its original theory                                                   |

|   |      | 4.4.2 Discussion of NPS-F and its original theory                                                   |

|   |      | 4.4.3 Reasoning about the parameter $\delta$                                                        |

|   | 4.5  | Instantaneous migration problem                                                                     |

|   | 4.6  | Implementation of the slot-based task-splitting dispatcher                                          |

|   |      | 4.6.1 Scheduler implementation                                                                      |

|   |      | 4.6.2 Adding support for slot-based task-splitting scheduling algorithms to the RT scheduling class |

|   | 4.7  | Scheduling overheads                                                                                |

|   | 4.8  | Summary         75                                                                                  |

| 5 | Slat | -based task-splitting overhead-aware schedulability analysis 77                                     |

| 5 | 5.1  | Introduction                                                                                        |

|   | 5.2  | Basis for the overhead-aware schedulability analysis                                                |

|   | 5.3  | New demand-based and overhead-aware schedulability analysis                                         |

|   | 5.5  | 5.3.1 New demand-based schedulability test for mapping tasks to servers 80                          |

|   |      | 5.3.2 New demand-based schedulability test for assigning servers to processors 84                   |

|   |      | 5.3.2.1 Non-split servers                                                                           |

|   |      | 5.3.2.2 Split servers                                                                               |

|   | 5.4  | New server-to-processor assignment procedure                                                        |

|   |      | 5.4.1 Assignment rules                                                                              |

|   |      | 5.4.2 Assignment procedure                                                                          |

|   |      | 5.4.2.1 Task to processor assignment procedure in S-EKG 96                                          |

|   |      | 5.4.2.2 New server-to-processor assignment for NPS-F                                                |

|   |      | 5.4.2.3 Effect of assignment rules on the schedulability analysis 98                                |

|   | 5.5  | Schedulability tests                                                                                |

|   | 5.6  | Summary                                                                                             |

| 6 | Rese | erve-based scheduling algorithm 103                                                                 |

|   | 6.1  | Introduction                                                                                        |

|   | 6.2  | Basics of the reserve-based scheduling algorithm                                                    |

|   |      | 6.2.1 Off-line procedure                                                                            |

|   |      | 6.2.2 Run-time task-dispatching algorithm                                                           |

|   | 6.3  | Implementation of the Carousel-EDF task-dispatching algorithm 105                                   |

|   |      | 6.3.1 Scheduler implementation                                                                      |

|   |      | 6.3.2 Releasing jobs                                                                                |

|   | 6.4  | Overhead-aware schedulability analysis                                                              |

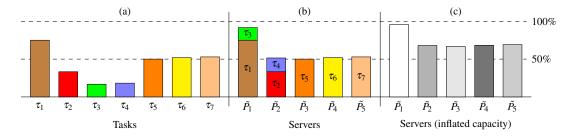

|   |      | 6.4.1 Server inflation                                                                              |

|    |             | 6.4.2 Generation of the carousel                                                  | 11  |

|----|-------------|-----------------------------------------------------------------------------------|-----|

|    |             | 6.4.3 Supporting other job release mechanisms                                     | 12  |

|    | 6.5         | Utilization bound                                                                 | 13  |

|    | 6.6         | Upper bounds on preemptions                                                       | 16  |

|    | 6.7         | Summary                                                                           | 16  |

|    |             |                                                                                   |     |

| 7  |             | luation 11                                                                        |     |

|    | 7.1         | Introduction                                                                      |     |

|    | 7.2         | The off-line schedulability analysis                                              |     |

|    |             | 7.2.1 Quantification of overheads                                                 |     |

|    |             | 7.2.2 Experiment design                                                           | 21  |

|    |             | 7.2.3 Preliminary evaluation of the merits of slot-based task-splitting over par- |     |

|    |             | titioning, when overheads are considered                                          |     |

|    |             | 7.2.4 Evaluation of the new analysis in the absence of overheads                  |     |

|    |             | 7.2.4.1 Experiments for the S-EKG scheduling algorithm 12                         |     |

|    |             | 7.2.4.2 Experiments for the NPS-F scheduling algorithm                            |     |

|    |             | 7.2.5 Evaluation of the new analysis in the presence of overheads 13              |     |

|    |             | 7.2.6 Reliability of the schedulability analysis                                  |     |

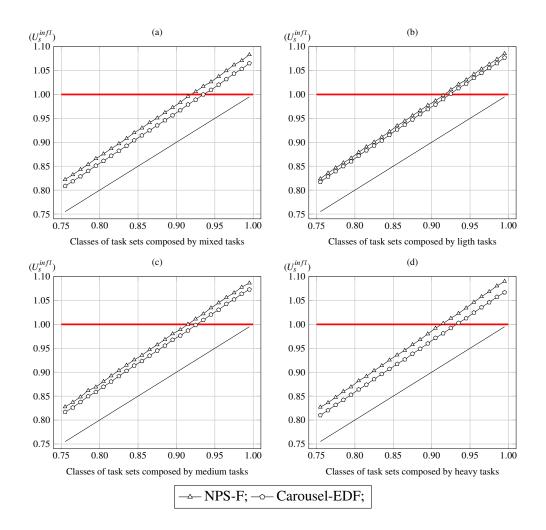

|    |             | 7.2.7 Slot-based <i>vs.</i> reserve-based                                         |     |

|    | 7.3         | The run-time task-dispatching algorithm                                           |     |

|    |             | 7.3.1 Experimental setup                                                          |     |

|    |             | 7.3.2 Why overheads have to be accounted for                                      |     |

|    |             | 7.3.3 Enhancing real-time capabilities of the Linux kernel                        |     |

|    | 7.4         | Summary 14                                                                        | 43  |

| 8  | Con         | clusions and future work 14                                                       | 45  |

| -  | 8.1         | Introduction                                                                      |     |

|    | 8.2         | Summary of results                                                                | 45  |

|    | 8.3         | Future work                                                                       | 48  |

|    |             |                                                                                   |     |

| Re | eferen      | nces 15                                                                           | 51  |

| A  | Inte        | errupts 16                                                                        | 61  |

| В  | Oth         | er results                                                                        | ( = |

| D  | B.1         |                                                                                   |     |

|    | B.1<br>B.2  | 1 0                                                                               |     |

|    | <b>D</b> .2 | Run-time task-dispatching algorithm                                               | 50  |

| С  | Pap         | ers and materials 17                                                              | 73  |

|    | C.1         | List of papers by the author                                                      | 73  |

|    | C.2         | Materials                                                                         | 74  |

### CONTENTS

# **List of Figures**

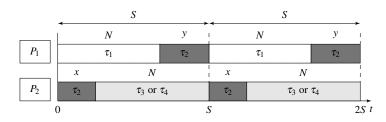

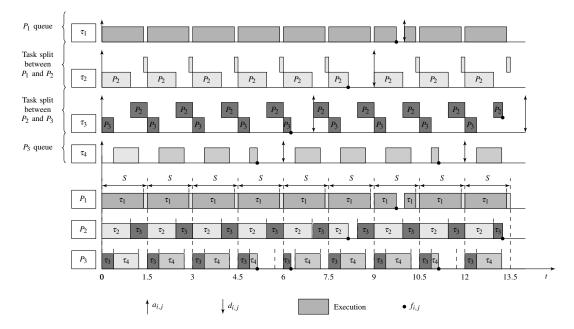

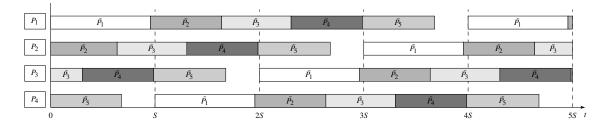

| 1.1  | An example of the operation of a slot-based task-splitting multiprocessor sche-<br>duling. Task $\tau_2$ is a split-task while tasks $\tau_1$ , $\tau_3$ , and $\tau_4$ are non-split tasks that |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | execute only on one processor.                                                                                                                                                                   | 5  |

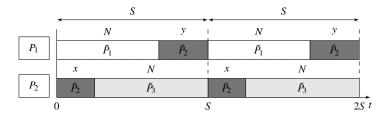

| 1.2  | An example of the operation of the hierarchical approach for slot-based task-<br>splitting multiprocessor scheduling.                                                                            | 5  |

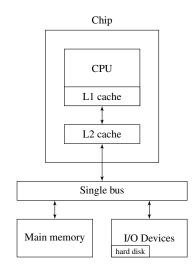

| 2.1  | Illustration of a computer according to the von Neumann architecture.                                                                                                                            | 11 |

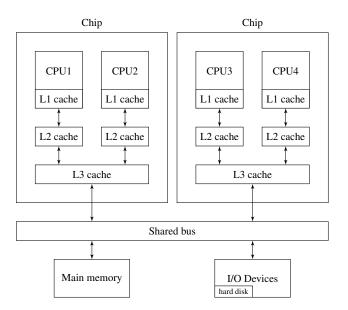

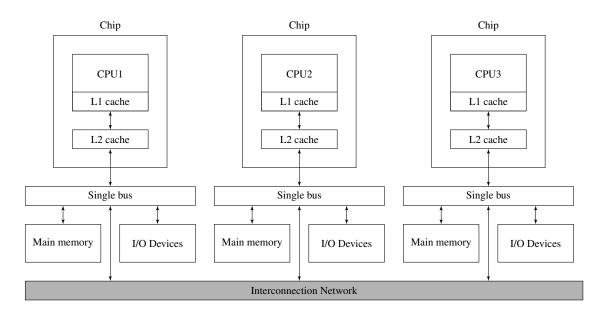

| 2.2  | Illustration of a multiprocessor architecture according to the shared memory model.                                                                                                              | 12 |

| 2.3  | Illustration of a multiprocessor architecture according to the distributed memory                                                                                                                |    |

|      | model                                                                                                                                                                                            | 13 |

| 2.4  | The cache coherence problem for a single memory location $(X)$ , read and written                                                                                                                |    |

|      | by two processors (A and B).                                                                                                                                                                     | 14 |

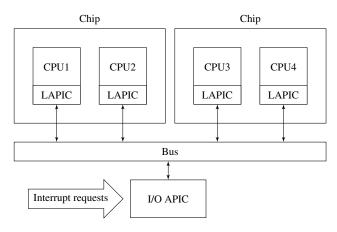

| 2.5  | Illustration of the use of an Advanced Programmable Interrupt Controller (APIC)                                                                                                                  |    |

|      | in multiprocessor systems.                                                                                                                                                                       | 15 |

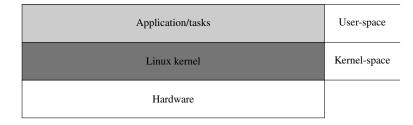

| 2.6  | Linux-based computer system architecture.                                                                                                                                                        | 17 |

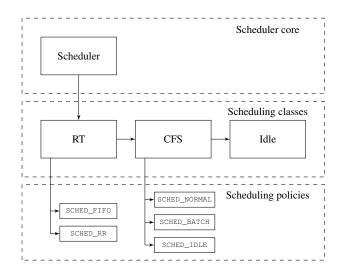

| 2.7  | Scheduling framework architecture.                                                                                                                                                               | 22 |

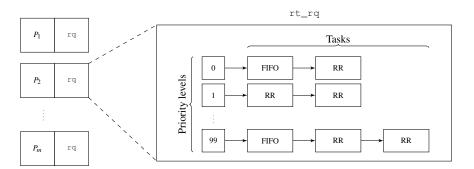

| 2.8  | RT scheduling class ready-queue                                                                                                                                                                  | 25 |

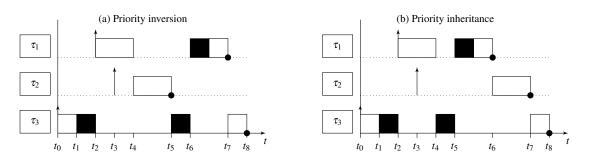

| 2.9  | Illustration of the priority inversion and priority inheritance.                                                                                                                                 | 26 |

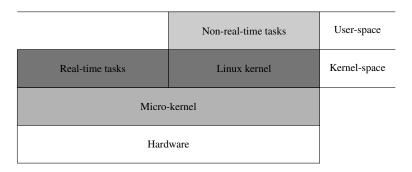

| 2.10 | 1 5 5                                                                                                                                                                                            | 30 |

| 2.11 | Xenomai computer system architecture                                                                                                                                                             | 32 |

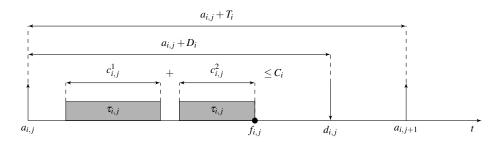

| 3.1  | Illustration of the job timing parameters.                                                                                                                                                       | 37 |

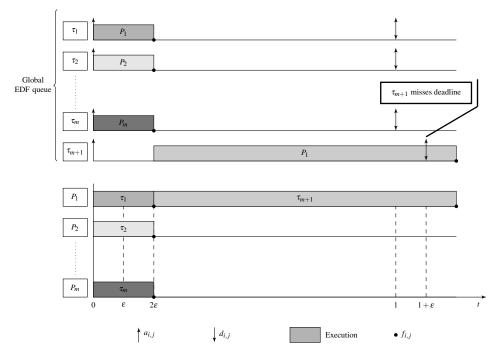

| 3.2  | Illustration of Dhall's effect.                                                                                                                                                                  | 41 |

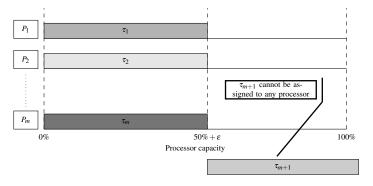

| 3.3  | Illustration of the partitioning problem                                                                                                                                                         | 41 |

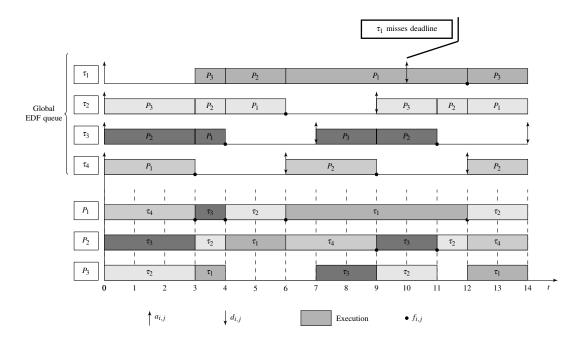

| 3.4  | Global-EDF execution time-line                                                                                                                                                                   | 44 |

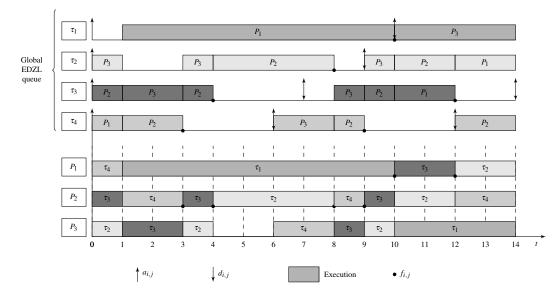

| 3.5  | Global EDZL execution time-line.                                                                                                                                                                 | 45 |

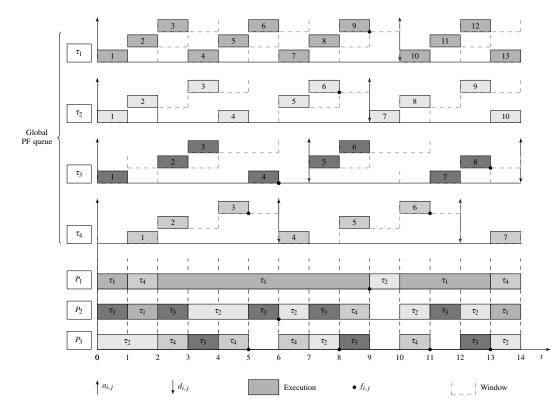

| 3.6  | PF execution time-line                                                                                                                                                                           | 46 |

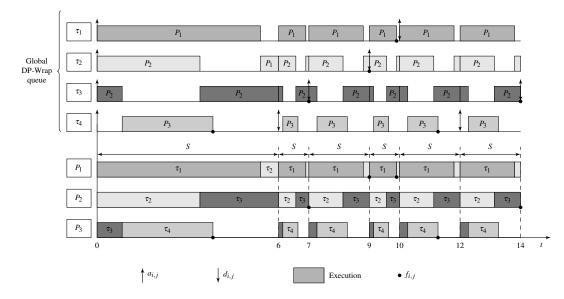

| 3.7  | DP-Wrap execution time-line.                                                                                                                                                                     | 47 |

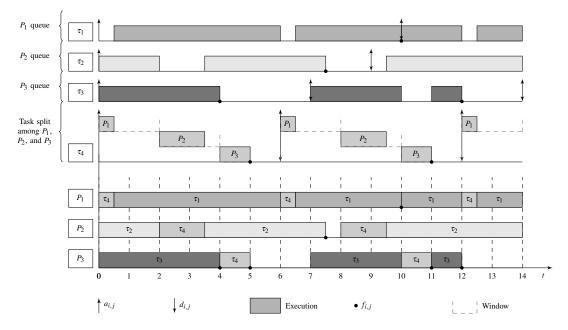

| 3.8  | EDF-WM execution time-line.                                                                                                                                                                      | 49 |

| 3.9  | S-EKG execution time-line                                                                                                                                                                        | 50 |

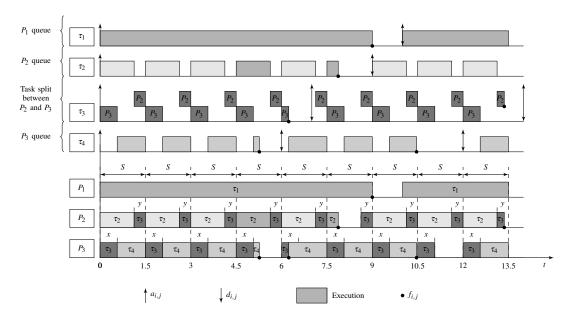

| 3.10 | NPS-F execution time-line.                                                                                                                                                                       | 51 |

| 4.1  | Task-to-server mapping.                                                                                                                                                                          | 59 |

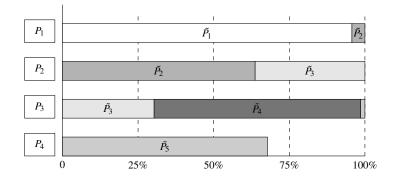

| 4.2  | Server-to-processor assignment.                                                                                                                                                                  | 60 |

| 4.3  | Run-time dispatching time-line produced by the slot-based task-splitting algo-                                                                                                                   |    |

|      | rithm for the task set example.                                                                                                                                                                  | 61 |

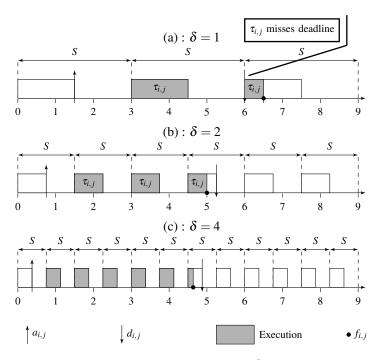

| 4.4  | The intuition beyond $\delta$ parameter                                                                                                                                                          | 64 |

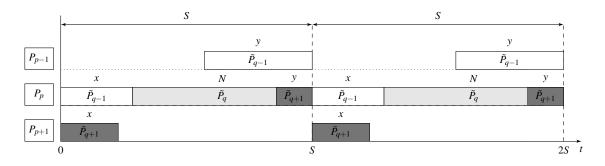

| 4.5  | Illustration of the adjacent time slots that cause the instantaneous migration problem.                                                                                                          | 65 |

| 4.6<br>4.7  | Illustration of the time slot shifting to solve the instantaneous migration problem.<br>In spite of it is not shown in the figure there is no penalty for non-split servers; that is, the system supplies the same execution time to the non-split servers Experimental evaluation of the impact of the cache and bus memory contention | 65       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.8         | on the reading time of an array. These experiments highlight the benefit of the staggered against the aligned versions                                                                                                                                                                                                                  | 68       |

|             | nization                                                                                                                                                                                                                                                                                                                                | 70       |

| 5.1         | Illustration of the execution demand of a task against the processing supplied by the system.                                                                                                                                                                                                                                           | 79       |

| 5.2         | Illustration of the execution demand of a task against the processing supplied by                                                                                                                                                                                                                                                       | 20       |

| 5.3         | the system considering time reserves                                                                                                                                                                                                                                                                                                    | 80<br>82 |

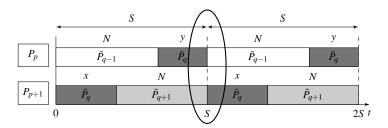

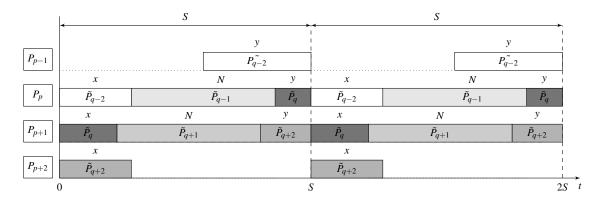

| 5.4         | Illustration of the release interference for non-split servers. In this example server $\tilde{P}_q$ may suffer release interference from the arrivals of tasks served by $\tilde{P}_{q-1}$ and $\tilde{P}_{q+1}$ (if these occur at an instant when $\tilde{P}_q$ is mapped to processor $P_p$ )                                       | 86       |

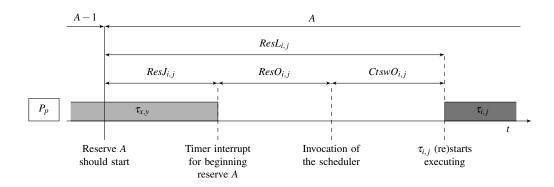

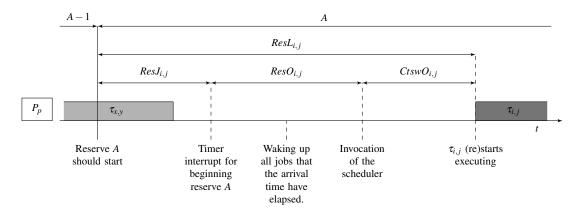

| 5.5         | Illustration of the reserve overhead. In this example, the execution of job $\tau_{i,j}$ , inside reserve A, is delayed by $ResL_{i,j}$ , the overhead of that reserve.                                                                                                                                                                 | 88       |

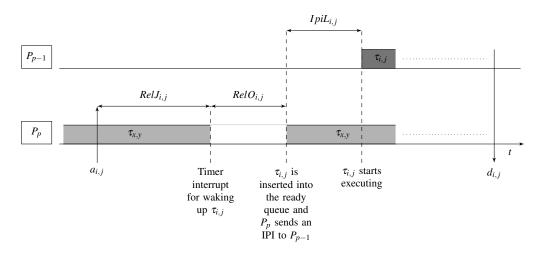

| 5.6         | Illustration of the IPI latency at the release of a split job. It does not include the                                                                                                                                                                                                                                                  | 00       |

| 5.7         | time for context switching                                                                                                                                                                                                                                                                                                              | 90       |

|             | at an instant when $\tilde{P}_q$ is mapped to processor $P_{p+1}$ ).                                                                                                                                                                                                                                                                    | 91       |

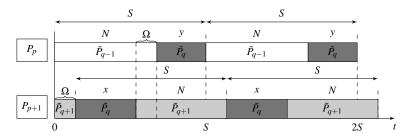

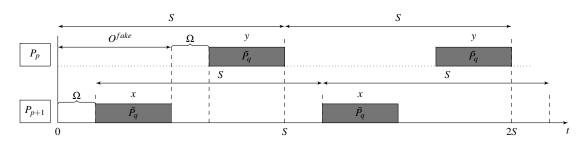

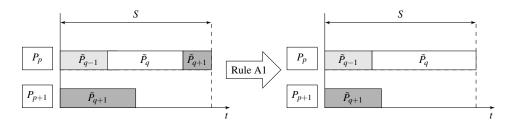

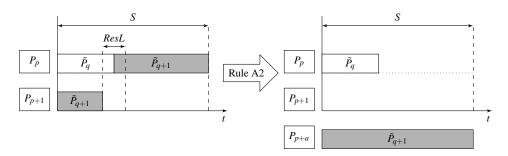

| 5.8         | Illustration of the $\Omega$ and $O^{fake}$ parameters                                                                                                                                                                                                                                                                                  | 92<br>05 |

| 5.9<br>5.10 | Illustration of the assignment rule A1.       Illustration of the assignment rule A2.                                                                                                                                                                                                                                                   | 95<br>96 |

|             | Illustration of the S-EKG task-to-processor mapping.                                                                                                                                                                                                                                                                                    | 90<br>96 |

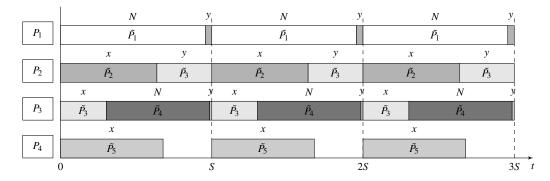

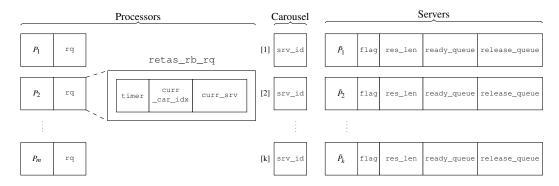

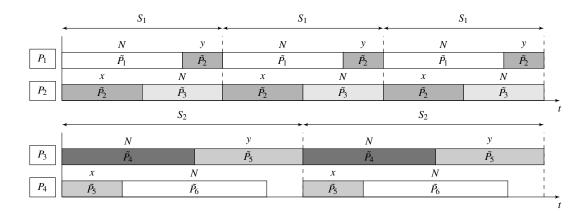

| 6.1         | Run-time dispatching time-line produced by the Carousel-EDF for the task set example presented in Section 4.3.                                                                                                                                                                                                                          | 105      |

| 6.2         | Data required to implement the Carousel-EDF scheduling algorithm in Linux kernel                                                                                                                                                                                                                                                        |          |

| 6.3         | Illustration of the reserve latency. The <i>ResL</i> incorporates the release of jobs that                                                                                                                                                                                                                                              |          |

|             | arrival time has elapsed                                                                                                                                                                                                                                                                                                                | 110      |

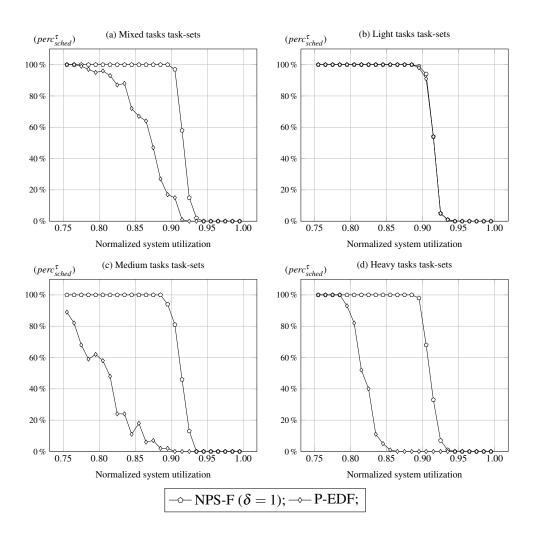

| 7.1         | Comparison of between NPS-F and P-EDF scheduling algorithms in the presence                                                                                                                                                                                                                                                             | 104      |

| 7.2         | of overheads                                                                                                                                                                                                                                                                                                                            | 124      |

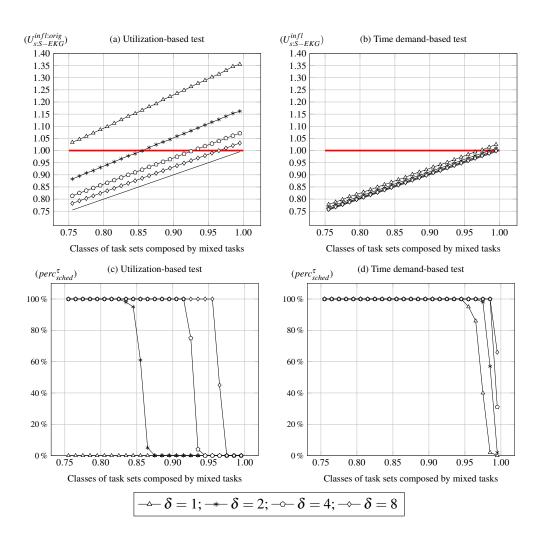

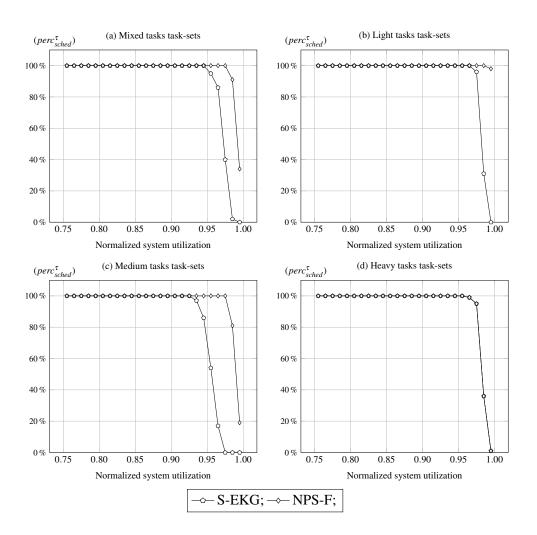

| 1.2         | task sets composed by mixed, $u_i \in [0.05, 0.95)$ , tasks.                                                                                                                                                                                                                                                                            | 126      |

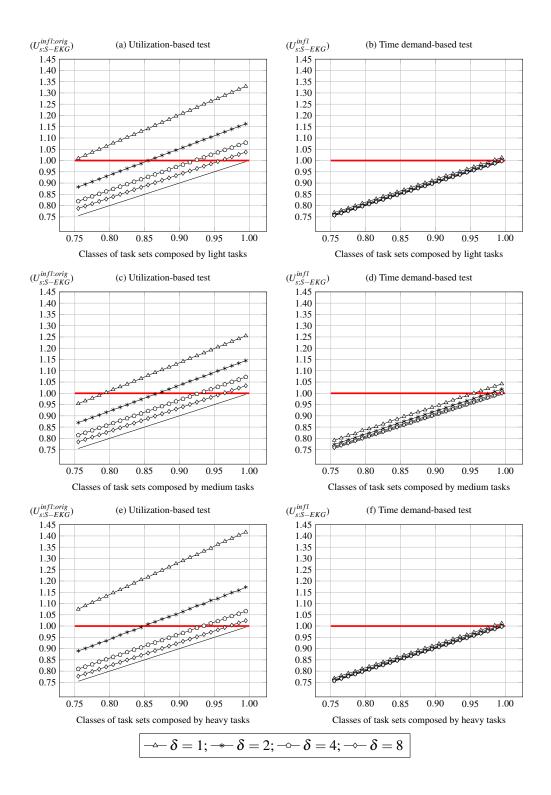

| 7.3         | Comparison between the original S-EKG and the new schedulability analysis considering task sets composed by light, $u_i \in [0.05, 0.35)$ , medium, $u_i \in [0.35, 0.65)$ ,                                                                                                                                                            |          |

|             | and heavy tasks, $u_i \in [0.65, 0.95)$                                                                                                                                                                                                                                                                                                 | 127      |

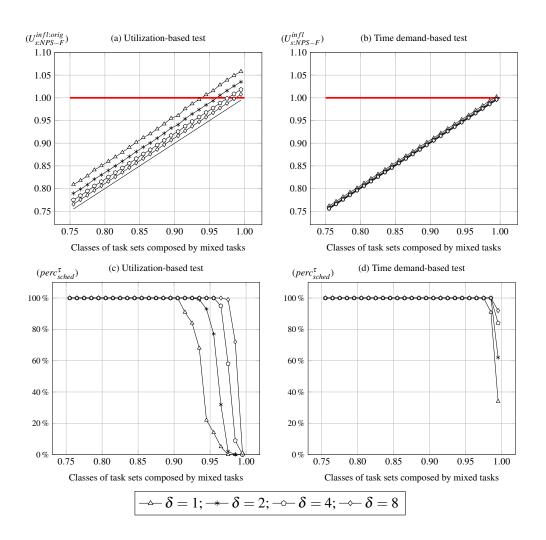

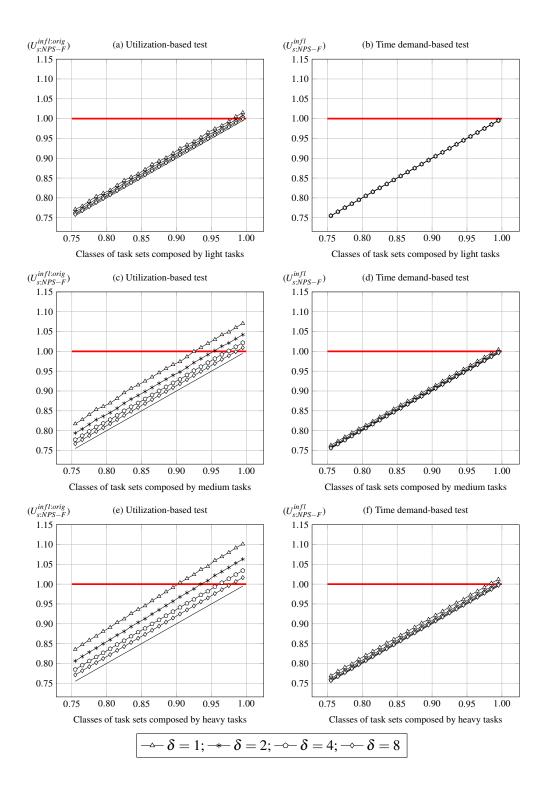

| 7.4         | Comparison between the original NPS-F and the new schedulability analysis con-                                                                                                                                                                                                                                                          | 100      |

| 7.5         | sidering task sets composed by mixed, $u_i \in [0.05, 0.95)$ , tasks Comparison between the original NPS-F and the new schedulability analysis considering task sets compared by light $u_i \in [0.05, 0.25)$ medium $u_i \in [0.25, 0.65)$                                                                                             | 128      |

|             | sidering task sets composed by light, $u_i \in [0.05, 0.35)$ , medium, $u_i \in [0.35, 0.65)$ ,<br>and heavy tasks, $u_i \in [0.65, 0.95)$ .                                                                                                                                                                                            | 129      |

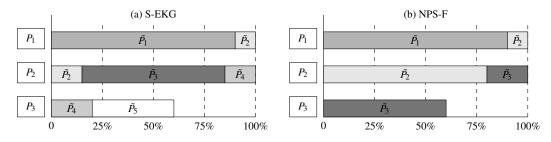

| 7.6         | Comparison between S-EKG and NPS-F scheduling algorithms according to the                                                                                                                                                                              |      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|             | new demand-based schedulability analysis using $\delta$ equal to one                                                                                                                                                                                   | 130  |

| 7.7         | Task-to-processor assignment patterns of the S-EKG and NPS-F                                                                                                                                                                                           | 131  |

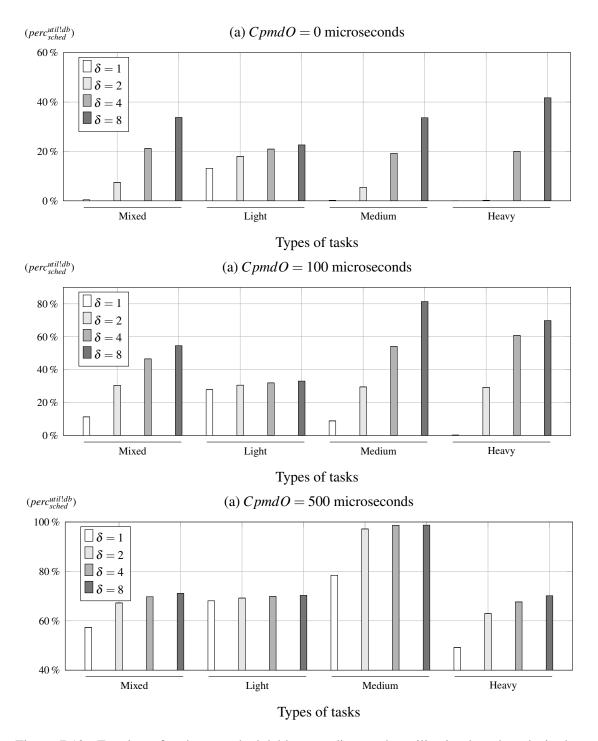

| 7.8         | Evaluation of the effect of the overheads on the new schedulability analysis                                                                                                                                                                           | 132  |

| 7.9         | Multiple time slot lengths in a system.                                                                                                                                                                                                                | 133  |

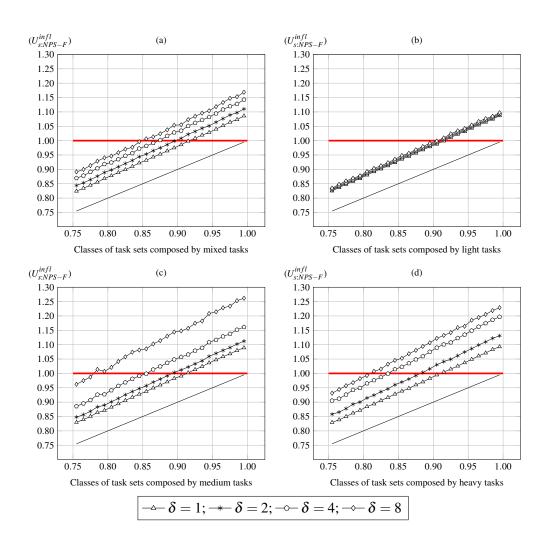

| 7.10        | Fraction of task sets schedulable according to the utilization-based analysis, but not schedulable according to the new demand-based overhead-aware schedulabil-<br>ity analysis, as a function of the type of tasks of the task set and of the design | 10.4 |

| - 11        | parameter $\delta$                                                                                                                                                                                                                                     | 134  |

| 7.11        | Fraction of mixed task sets that are considered schedulable by the original schedu-<br>lability analysis but are not by the schedulability with overheads ( <i>CpmdO</i> equal to                                                                      |      |

|             | zero)                                                                                                                                                                                                                                                  | 136  |

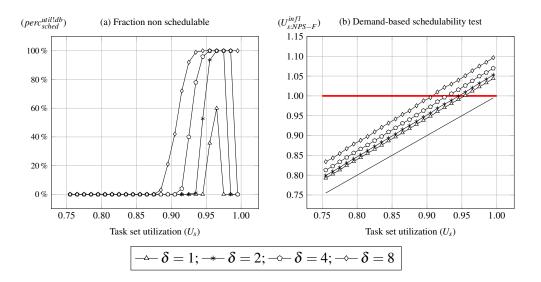

| 7.12        | Comparison between the NPS-F and Carousel-EDF based on the normalized in-<br>flation                                                                                                                                                                   | 137  |

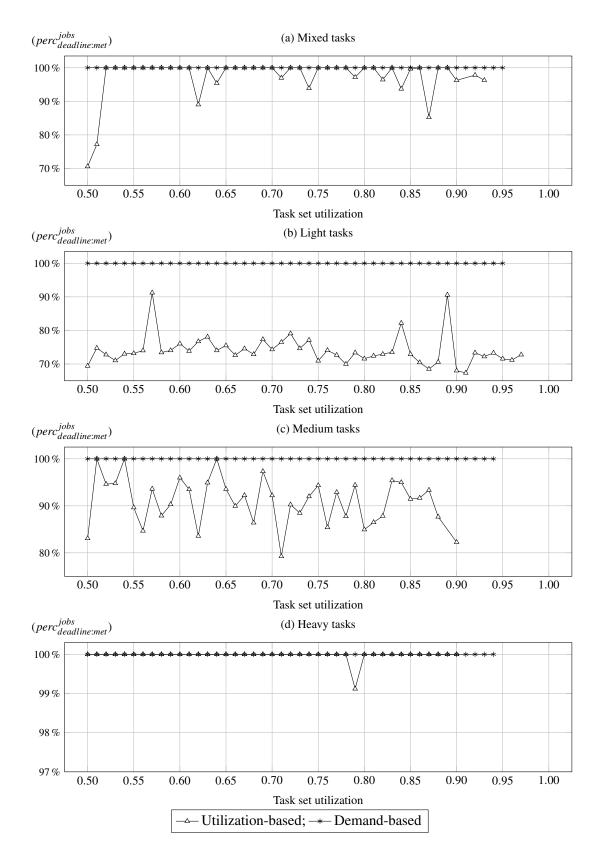

| 7.13        | A comparison between the utilization-based and the demand-based schedulability                                                                                                                                                                         |      |

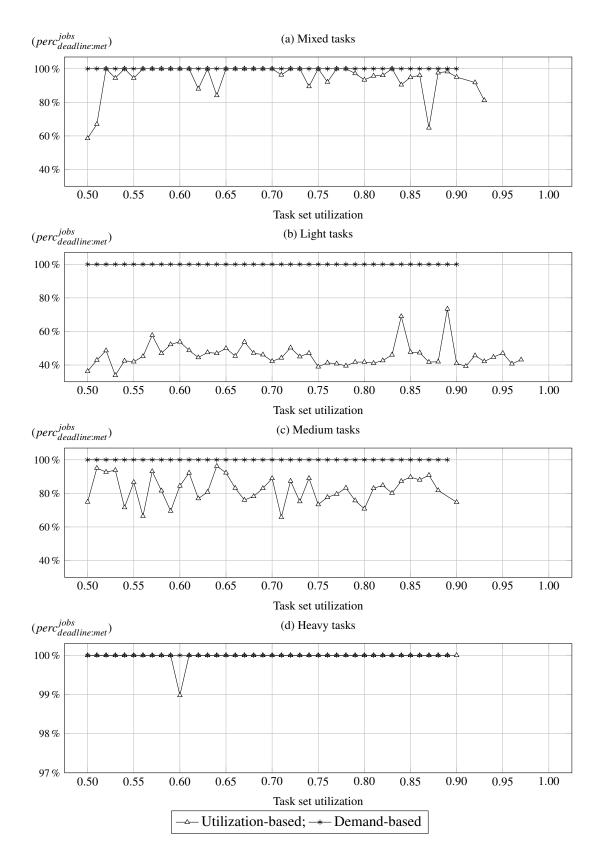

|             | analyses based on percentage of deadlines met                                                                                                                                                                                                          | 141  |

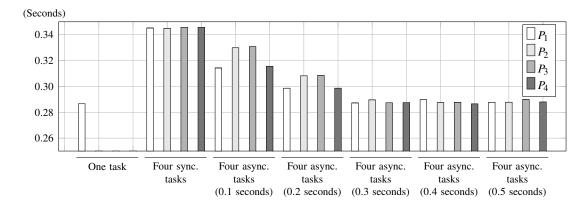

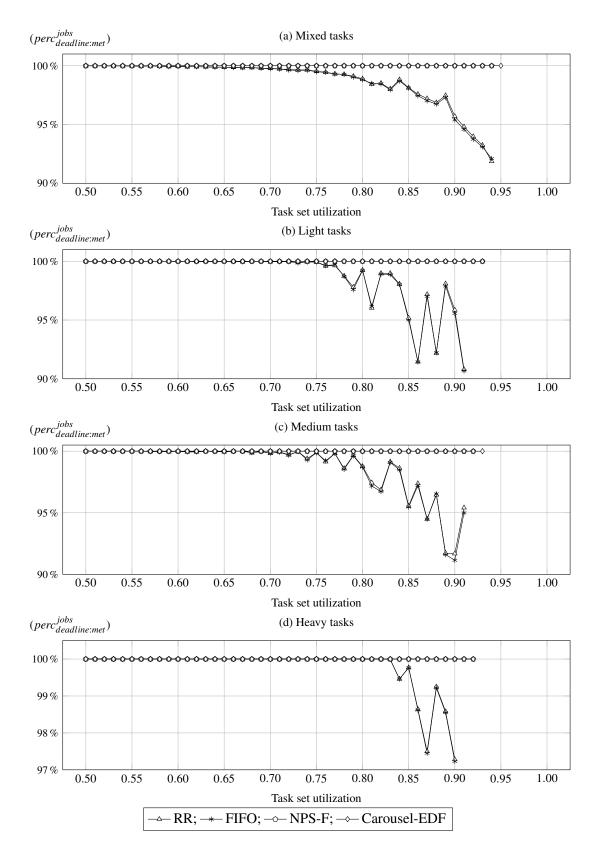

| 7.14        | A performance comparison among RR, FIFO, NPS-F, and Carousel-EDF based                                                                                                                                                                                 |      |

|             | on percentage of deadlines met.                                                                                                                                                                                                                        | 142  |

| <b>B</b> .1 | Comparison of the new NPS-F demand-based overhead-aware schedulability anal-                                                                                                                                                                           |      |

|             | ysis for short-, mixed-, and long-period task sets.                                                                                                                                                                                                    | 166  |

| B.2         | The mean and the standard deviation of the time slot length for short-, mixed-, and                                                                                                                                                                    |      |

|             | long-period task sets according to the type of tasks.                                                                                                                                                                                                  | 167  |

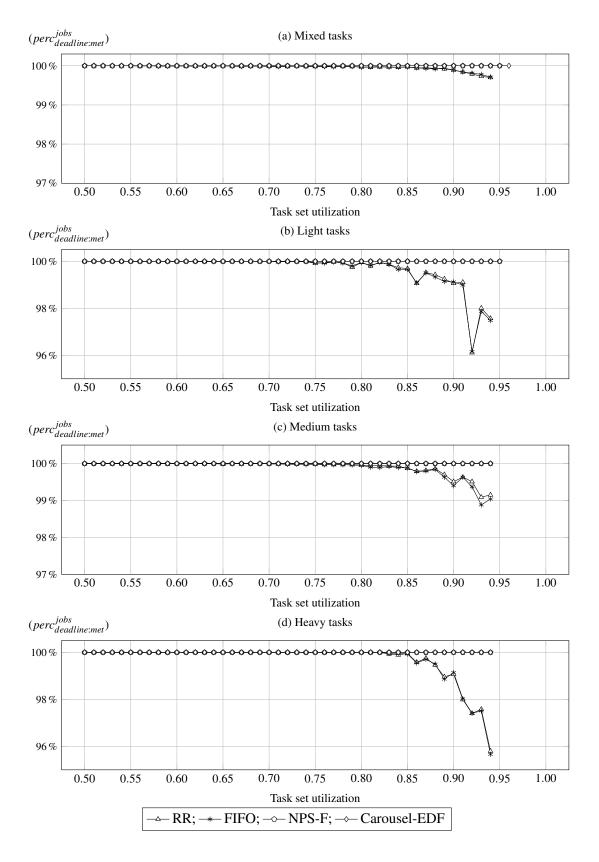

| B.3         | A comparison between the utilization-based and the demand-based schedulability                                                                                                                                                                         |      |

|             | analyses based on percentage of deadlines met for mixed-period, in the range [5,                                                                                                                                                                       | 1.0  |

| D 4         | 250] milliseconds                                                                                                                                                                                                                                      | 168  |

| B.4         | A comparison between the utilization-based and the demand-based schedulability<br>analyses based on percentage of deadlines met for long-period, in the range [50,                                                                                     |      |

|             | 250] milliseconds                                                                                                                                                                                                                                      | 169  |

| B.5         | A performance comparison among RR, FIFO, NPS-F, and Carousel-EDF based on                                                                                                                                                                              | 107  |

|             | percentage of deadlines met for mixed-period (in the range [5, 250] milliseconds)                                                                                                                                                                      |      |

|             | task sets.                                                                                                                                                                                                                                             | 170  |

| B.6         | A performance comparison among RR, FIFO, NPS-F, and Carousel-EDF based on                                                                                                                                                                              |      |

|             | percentage of deadlines met for long-period (in the range [50, 250] milliseconds)                                                                                                                                                                      |      |

|             | task sets.                                                                                                                                                                                                                                             | 171  |

## **List of Tables**

| 3.1 | Task set example.                                                                | 43  |

|-----|----------------------------------------------------------------------------------|-----|

| 7.1 | Experimentally-derived values for the various scheduling overheads (in microsec- |     |

|     | onds)                                                                            | 120 |

# **List of Algorithms**

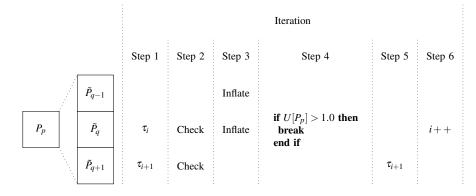

| 5.1 | Pseudo-code of the new task-to-server mapping algorithm.              | 84  |

|-----|-----------------------------------------------------------------------|-----|

| 5.2 | <pre>Pseudo-code algorithm of the inflate_sb_non_split function</pre> | 89  |

| 5.3 | Pseudo-code of the new server-to-processor assignment algorithm.      | 99  |

| 5.4 | Pseudo-code algorithm of the schedulability test functions            | 101 |

| 6.1 | Pseudo-code algorithm of reserve sequence generator                   | 112 |

| 6.2 | Pseudo-code algorithm of first reserve generator                      | 113 |

| 7.1 | Pseudo-code algorithm of the task set generator                       | 122 |

## **List of Code Listings**

| 2.1 | The required steps to implement a high resolution timer in the Linux kernel                 | 20  |

|-----|---------------------------------------------------------------------------------------------|-----|

| 2.2 | The struct task_struct data structure                                                       | 20  |

| 2.3 | The struct rq data structure.                                                               | 21  |

| 2.4 | The rt_sched_class definition                                                               | 23  |

| 2.5 | The schedule function                                                                       | 24  |

| 4.1 | The C language code of the task used to investigate the impact of the contention            |     |

|     | for shared cache and also for memory bus                                                    | 67  |

| 4.2 | Changes to the enqueue_task_rt function                                                     | 72  |

| 4.3 | Changes to the check_preempt_curr_rt function.                                              | 73  |

| 4.4 | Changes to the pick_next_task_rt function                                                   | 73  |

| 6.1 | Timer callback function that release all jobs whose $a_{i,j}$ is earlier that the beginning |     |

|     | of the current reserve                                                                      | 108 |

| 7.1 | The C language code of the task for experiments.                                            | 139 |

|     |                                                                                             |     |

# **Acronyms and Symbols**

| ADEOS                | Adaptive Domain Environment for Operating Systems                                |

|----------------------|----------------------------------------------------------------------------------|

| API                  | Application Programming Interface                                                |

| APIC                 | Advanced Programmable Interrupt Controller                                       |

| BF                   | Best-Fit                                                                         |

| BKL                  | Big Kernel Lock                                                                  |

| CFS                  | Completely Fair Scheduling                                                       |

| CPMD                 | Cache-related Preemption and Migration Delay                                     |

| CPU                  | Central Processing Unit                                                          |

| dbf                  | demand bound function                                                            |

| DMA                  | Direct Memory Access                                                             |

| DP-Fair              | Deadline Partitioning Fairness                                                   |

| EDF                  | Earliest Deadline First                                                          |

| EDF-SS               | Earliest Deadline First scheduling of non-split tasks with Split tasks scheduled |

|                      | in Slots                                                                         |

| EDF-US               | Earliest Deadline First Utilization Separator                                    |

| EDF-WM               | Earliest Deadline First Window-constraint Migration                              |

| EDZL                 | Earliest Deadline first until Zero Laxity                                        |

| EKG                  | Earliest deadline first with task splitting and K processors in a Group          |

| FF                   | First-Fit                                                                        |

| FIFO                 | First-In-First-Out                                                               |

| FPZL                 | Fixed Priority until Zero Laxity                                                 |

| GPOS                 | General Purpose Operating System                                                 |

| HPET                 | High Precision Event Timer                                                       |

| HRT                  | High-Resolution Timer                                                            |

| I/O                  | Input/Output                                                                     |

| I/O APIC             | Input/Output APIC                                                                |

| ILP                  | Instruction-Level Parallelism                                                    |

| IPI                  | Inter-Processor Interrupt                                                        |

| ISR                  | Interrupt Service Routine                                                        |

| LAPIC                | Local Advanced Programmable Interrupt Controller                                 |

| LITMUS <sup>RT</sup> | LInux Testbed for MUltiprocessor Scheduling in Real-Time systems                 |

| LLF                  | Least-Laxity-First                                                               |

| LXRT                 | LinuX-RT                                                                         |

| NF                   | Next-Fit                                                                         |

| NP-hard              | Non-deterministic Polynomial-time hard                                           |

| NPS                  | Notional Processor Scheduling                                                    |

| NPS-F                | Notional Processor Scheduling - Fractional                                       |

| NUMA                 | Non-Uniform Memory Access                                                        |

| 11010111             |                                                                                  |

| P-EDF      | Partitioned Earliest Deadline First                                              |

|------------|----------------------------------------------------------------------------------|

| P-Fair     | Proportionate Fairness                                                           |

| PF         | P-Fairness                                                                       |

| PI         | Priority Inheritance                                                             |

| PIT        | Programmable Interval Timer                                                      |

| POSIX      | Portable Operating System Interface                                              |

| PREEMPT-RT | Linux kernel PREEMPT-RT patch                                                    |

| QPA        | Quick Processor-demand Analysis                                                  |

| RESCH      | REal-time SCHeduler                                                              |

| ReTAS      | Real-time TAsk-Splitting scheduling algorithms framework                         |

| RM         | Rate Monotonic                                                                   |

| RM-US      | RM Utilization Separator                                                         |

| RR         | Round-Robin                                                                      |

| RT         | Real-Time                                                                        |

| RTAI       | Real-Time Application Interface                                                  |

| RTLinux    | Real-Time Linux                                                                  |

| RTOS       | Real-Time Operating System                                                       |

| S-EKG      | Sporadic Earliest deadline first with task splitting and K processors in a Group |

| sbf        | supply bound function                                                            |

| SMT        | Simultaneous MultiThreading                                                      |

| TSC        | Time Stamp Counter                                                               |

| UMA        | Uniform Memory Access                                                            |

| WF         | Worst-Fit                                                                        |

| Symbol                    | Interpretation                                                                      | Definition                          |

|---------------------------|-------------------------------------------------------------------------------------|-------------------------------------|

| τ                         | A task set                                                                          |                                     |

| $	au_i$                   | The $i^{th}$ task                                                                   |                                     |

| C                         | The worst-case execution requirement of task                                        | See Section 3.2                     |

| $C_i$                     | $	au_i$                                                                             | See Section 5.2                     |

| $T_i$                     | The minimum inter-arrival time of task $\tau_i$                                     | See Section 3.2                     |

| $D_i$                     | The relative deadline of task $\tau_i$                                              | See Section 3.2                     |

| $u_i$                     | The utilization of task $\tau_i$                                                    | See Section 3.2                     |

| п                         | The number of tasks of $\tau$                                                       |                                     |

| $	au_{i,j}$               | The $j^{th}$ job of task $\tau_i$                                                   | See Figure 3.1                      |

| $a_{i,j}$                 | The arrival time of job $\tau_{i,j}$                                                | See Figure 3.1                      |

| $d_{i,j}$                 | The absolute deadline of job $\tau_{i,j}$                                           | See Figure 3.1                      |

| $f_{i,j}$                 | The execution finishing time of job $\tau_{i,j}$                                    | See Figure 3.1                      |

| $P_p$                     | The $p^{th}$ processor                                                              |                                     |

| $x[P_p]$                  | The processor $P_p$ 's <i>x</i> reserve length                                      | See Equation 5.34                   |

| $N[P_p]$                  | The processor $P_p$ 's N reserve length                                             | See Equation 5.34                   |

| $y[P_p]$                  | The processor $P_p$ 's y reserve length                                             | See Equation 5.34                   |

| $U[P_p]$                  | The utilization of processor $P_p$                                                  |                                     |

| $\frac{m}{\tilde{p}}$     | The number of processors                                                            |                                     |

| $\tilde{P}_q$             | The $q^{th}$ server<br>The set of table assigned to the server $\tilde{\mathbf{p}}$ |                                     |

| $	au[	ilde{P}_q]$         | The set of tasks assigned to the server $\tilde{P}_q$ .                             | San Equation 4.1                    |

| $U[	ilde{P}_q]$           | The utilization of server $\tilde{P}_q$                                             | See Equation 4.1                    |

| $U^{infl}[	ilde{P}_q]$    | The inflated utilization of server $\tilde{P}_q$                                    | See Algorithm 5.2 and Section 6.4.1 |

|                           | Part of the inflated utilization of server $\tilde{P}_q$                            | Section 0.4.1                       |

| $U_x^{infl}[	ilde{P}_q]$  | assigned to the <i>x</i> reserve of the respective                                  | See Equation 5.34                   |

| $O_X  [I q]$              | processor                                                                           | See Equation 5.5 T                  |

|                           | Part of the inflated utilization of server $\tilde{P}_q$                            |                                     |

| $U_y^{infl}[	ilde{P}_q]$  | assigned to the y reserve of the respective                                         | See Equation 5.34                   |

| - y [- q]                 | processor                                                                           | 1                                   |

| k                         | The number of servers                                                               |                                     |

| C                         | The time slot log oth                                                               | See Equations 4.2 and               |

| S                         | The time slot length                                                                | 5.41                                |

| δ                         | A designer-set integer parameter controlling                                        | See Section 4.4.3                   |

| 0                         | the migration frequency of split tasks                                              | 500 5000011 4.4.5                   |

| α                         | The inflation factor of S-EKG                                                       | See Equation 4.2                    |

| Ω                         | The time interval between the two split                                             | See Equation 4.8                    |

|                           | server reserves                                                                     |                                     |

| $U_s$                     | Utilization of the system                                                           | See Equation 3.2                    |

| UB <sub>S-EKG</sub>       | Utilization bound of S-EKG                                                          | See Equation 4.3                    |

| UB <sub>NPS-F</sub>       | Utilization bound of NPS-F                                                          | See Equation 4.7                    |

|                           | The cumulative processing capacity                                                  |                                     |

| $U_{s:S-EKG}^{infl:orig}$ | requirements for all (inflated) servers under                                       | See Equation 4.5                    |

| 3.3-EKU                   | the original analysis for S-EKG                                                     | -                                   |

|                           | The cumulative processing capacity                                                  |                                     |

| $U_{s:NPS-F}^{infl:orig}$ | requirements for all (inflated) servers under                                       | See Equation 4.6                    |

| 5.1.1 5-1                 | the original analysis for NPS-F                                                     |                                     |

| Symbol  | Interpretation                                                 | Definition                              |

|---------|----------------------------------------------------------------|-----------------------------------------|

| Rule A1 | The server should not be split                                 | See Figure 5.9                          |

| Rule A2 | The minimum separation between two reserves of the same server | See Figure 5.10                         |

| RelJ    | A upper bound for the release jitter                           | See Section 4.7 and<br>Figure 5.3       |

| RelO    | A upper bound for the release overhead                         | See Section 4.7 and Figure 5.3          |

| ResJ    | A upper bound for the reserve jitter                           | See Section 4.7 and Figures 5.5 and 6.3 |

| ResO    | A upper bound for the reserve overhead                         | See Section 4.7 and Figures 5.5 and 6.3 |

| CtswO   | A upper bound for the context (or task) switch overhead        | See Section 4.7 and Figures 5.5 and 6.3 |

| ResL    | A upper bound for the reserve latency                          | See Section 4.7 and Figures 5.5 and 6.3 |

| IpiL    | A upper bound for IPI latency                                  | See Section 4.7 and Figure 5.6          |

| CpmdO   | A upper bound of the CPMD overhead                             | See Section 4.7                         |

### **Chapter 1**

## Introduction

### **1.1 Motivation**

The computer era has been characterised by a continuous (and probably unfinished) *race* between processor manufacturers against processor consumers. Every new performance advance (permitting computational tasks to be executed faster by the processor) leads to another level of greater performance demands from consumers. Traditionally, performance advances were mainly achieved by increasing the *clock speed*. However, such increases have become limited by power consumption and heat dissipation [Low06].

In this context, *multi-core* architectures (consisting of multiple processing units or cores integrated in a single chip) offer an ideal platform to accommodate the recurrent increase of performance demands from consumers and solve the performance limitation of single-core architectures. The increase in processing capacity can be achieved by incorporating multiple cores in one single chip, with each core being able to run at a lower frequency, reducing heat and power consumption. Nowadays, multi-core platforms are commonplace for efficiently achieving high computational power [SMD<sup>+</sup>10], even in embedded systems, with the number of cores steadily increasing, expected to reach hundreds of cores per-chip in the future [TIL12].

Nevertheless, what is the actual impact of multi-core platforms in current computing technology? In [Bak10], the author makes the following question: "*What will we make of these new processors?*". He then continues with: "*This question should be on the minds of the developers of every kind of software.*" This lead us to another question: do multi-core platforms represent an evolution or a revolution? We believe that multi-core platforms are more than an evolution, since system designers must adopt suitable approaches for their system that allow them to exploit the full capabilities of multi-core platforms. Therefore, this can imply giving up or, at least, reassessing the approaches followed in the context of single-cores during the last decades.

Real-time computing is becoming increasingly important and pervasive, as more and more industries, infrastructures, and people depend on it. For real-time systems too, multi-cores offer an opportunity for a considerable boost in processing capacity, at relatively low price and power.

Introduction

This could, in principle, help with meeting the timing requirements of computationally intensive applications that could not be met on single-cores.

Real-time systems are defined as those systems in which the correctness of the system depends not only on the logical result of computation, but also on the time at which the results are produced [Sta88]; that is, the computation results must be delivered within a time bound, called *deadline*. Therefore, one of the most characteristic features of real-time systems is the notion of *time*. The time granularity is not necessarily the same across all real-time systems. In other words, microseconds could be suitable for some real-time systems, while for other, the timing requirement could be in the scale of milliseconds, seconds, minutes, or even hours. Therefore, the time granularity depends on the environment where the system operates.

Typically, real-time applications are composed by a set of tasks. Among other characteristics, each real-time task has an associated relative deadline. The results produced by each task must be delivered to the application during the *execution time window* defined by the *arrival time* (the time instant when a task becomes ready to be executed) of each task plus the respective relative deadline (which is typically different for each task). Naturally, each task requires some amount of time for computing its results (which is also typically different for each task). This imposes the use of some mechanism to schedule those tasks in the available processing units. In other words, real-time applications require a scheduling mechanism, usually denoted as *scheduling algorithm*, to create a task execution order such that their temporal constraints are satisfied. One frequent metric used to evaluate scheduling algorithms is the *utilization bound*, which is defined as a threshold for the task set workload such that all tasks meet their deadlines when the task set workload does not exceed such threshold.

Real-time applications are employed in a wide variety of fields. Given the particularities of some fields it must be assured, prior run-time, that the applications will not fail, especially, in application domains where a failure can have catastrophic consequences. This is assured by the *schedulability test*. The schedulability test establishes, at design time, whether the timing constraints are going to be met at run-time or not.

The real-time systems research community has developed a comprehensive toolkit comprised of scheduling algorithms, schedulability tests, and implementation techniques, which have been very successful: they are currently taught at major universities world-wide; they are incorporated in design tools and they are widely used in industry. Unfortunately, the big bulk of those results were limited to systems equipped with a single-core processor (or uniprocessor) only. Today, the increasing number of real-time systems running on multi-core (or multiprocessor) platforms impose the need for developing an analogous toolkit for those platforms.

#### **1.2** Challenges

Multiprocessor scheduling algorithms have been categorized as *global*, *partitioned*, or *semi-partitioned*. Global scheduling algorithms store all tasks in one global queue, shared by all processors (or cores). At any time instant, the *m* highest-priority tasks among those are selected for execution

on the *m* processors. Tasks can migrate from one processor to another during the execution; that is, an execution of a task can be stopped (or preempted) in one processor and resumed on another processor. Some scheduling algorithms [BGP95, BCPV96, AS00, AS04, CRJ06, RLM<sup>+</sup>11] of this class present a utilization bound of 100%. However, the global shared queue imposes the use of some locking mechanisms to serialize the access to that queue. This compromises the scalability of global scheduling algorithms, as stated in [Bra11]: "*it would be unrealistic to expect global algorithms to scale to tens or hundreds of processors*". Another disadvantage of global scheduling is related to the fact that the higher number of preemptions and migrations could cause *cache misses*; that is, a failed attempt to read or write data from the processor cache, implying a main memory access that has a much higher latency.

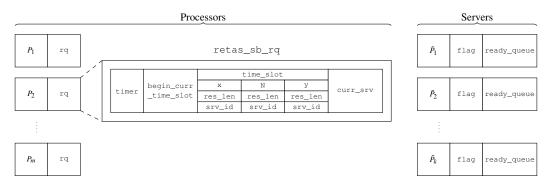

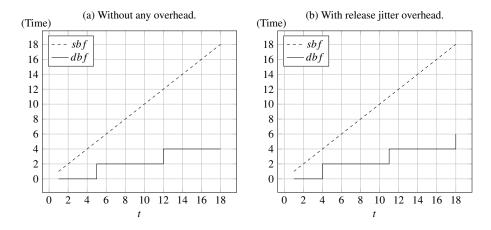

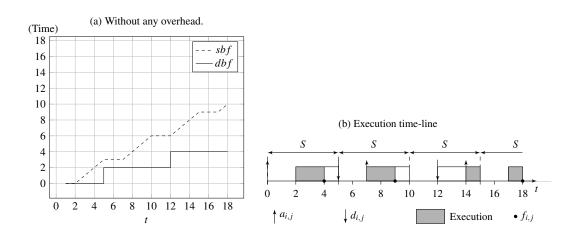

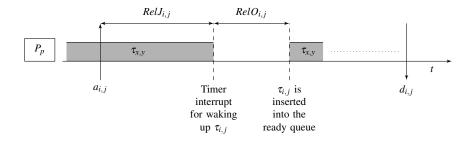

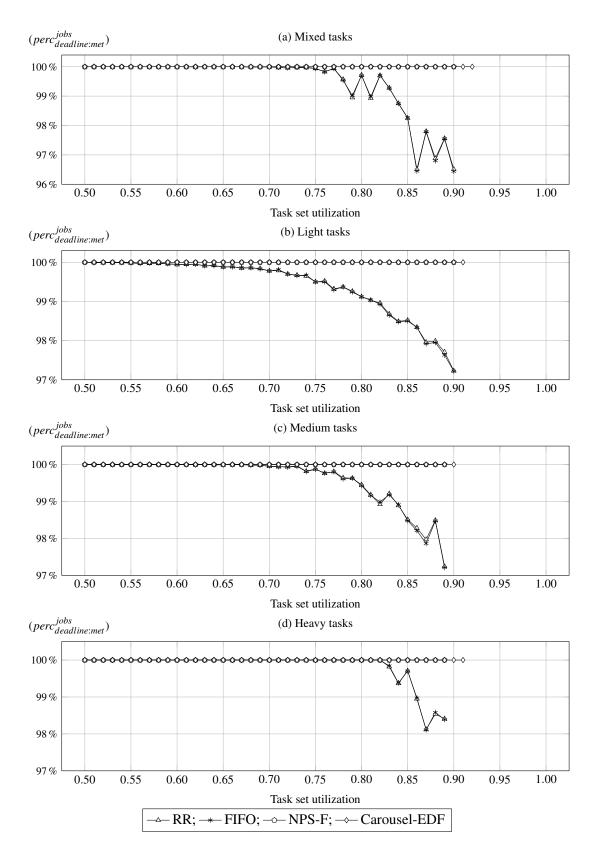

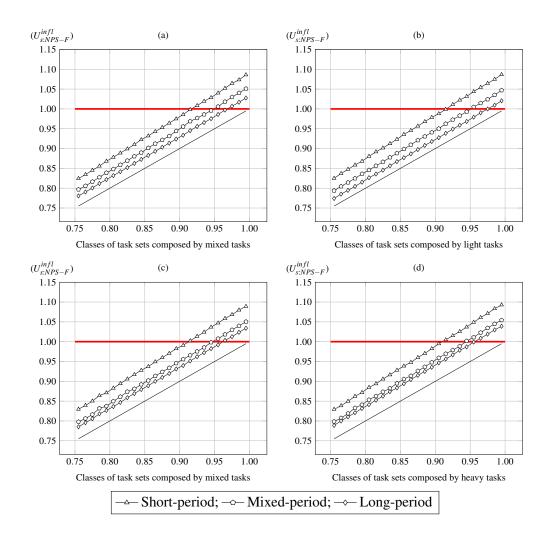

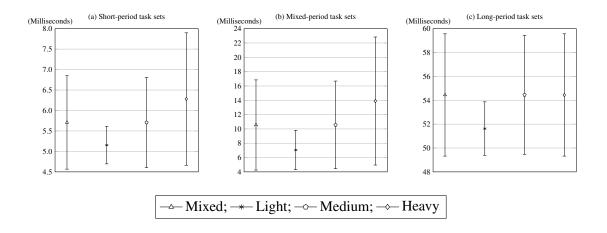

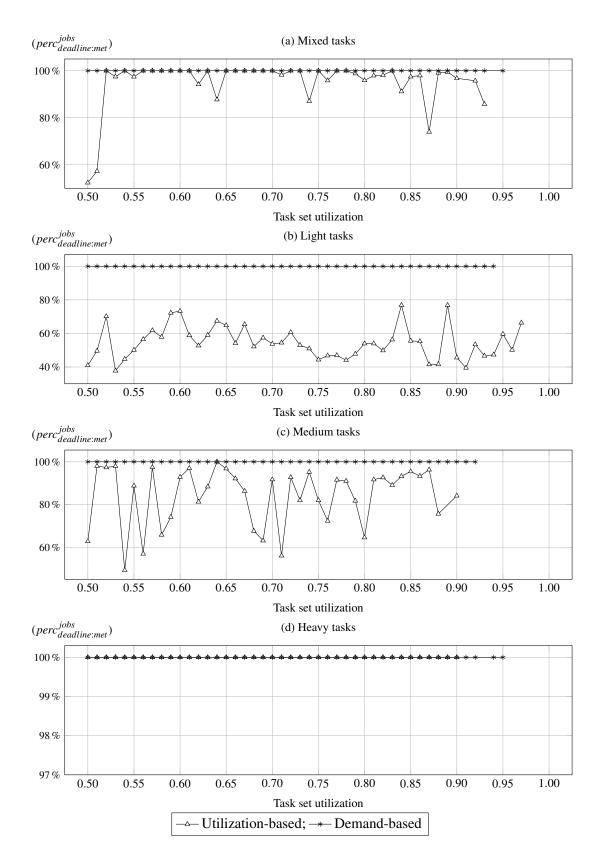

In contrast, partitioned scheduling algorithms partition the task set such that all tasks in a partition are assigned to the same core (or processor) and tasks are not allowed to migrate from one processor to another. This class of scheduling algorithms presents a utilization bound of at most 50%. However, it conceptually transforms a multiprocessor system composed by m processors into *m* single-core (or uniprocessor) systems, thus simplifying the scheduling problem. Therefore, partitioned scheduling schemes require two algorithms: the off-line task-to-processor assignment algorithm and the *run-time* task-dispatching algorithm. The first one assigns tasks to processors and the second one schedules tasks at run-time to execute on the processor(s). However, assigning tasks to processors is a bin-packing problem, which is known to be NP-hard [CGJ97]. The task-dispatching algorithm schedules the statically assigned tasks using a uniprocessor scheduling algorithm, such as the Earliest Deadline First (EDF) [Liu69], which assigns the highest-priority to the most urgent ready task; that is, it assigns the highest-priority to the task with less remaining time until the end of its execution time window. One advantage of partitioned scheduling algorithms when compared with global scheduling algorithms, is the absence of migrations and respective overheads, namely those related to increased cache misses. However, the processor manufacturers have largely addressed this issue using a hierarchical cache approach. Therefore, this allows migrative scheduling approaches to be considered for real-time multiprocessor systems.