FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# **Real-Time Scheduling on Heterogeneous Multiprocessors**

**Gurulingesh Raravi**

Doctoral Programme in Electrical and Computer Engineering

Supervisor: Dr. Vincent Nélis

March 11, 2014

© Gurulingesh Raravi, 2014

## **Real-Time Scheduling on Heterogeneous Multiprocessors**

**Gurulingesh Raravi**

Doctoral Programme in Electrical and Computer Engineering

March 11, 2014

### Abstract

Embedded computing is one of the most important areas in computer science today, witnessed by the fact that 98% of all computers are embedded. Given that many embedded systems have to interact "promptly" with their physical environment, the scientific community has invested significant efforts in developing algorithms for scheduling the workload, which is generally implemented as a set of tasks, at the *right time* and in proving before run-time that all the timing requirements will be satisfied at run-time. This field of study is referred to as the *real-time scheduling theory*.

The scheduling theory for a unicore processor is well-developed; the scientific results are taught at all major universities world-wide and the results are widely-used in industry. Scheduling theory for multicores is emerging but the focus so far has been for multicores with identical processing units. This is unfortunate because the computer industry is moving towards *heterogeneous multicores* with a constant number of distinct processor types — AMD Fusion, Intel Atom and NVIDIA Tegra are some of the examples of such multicores.

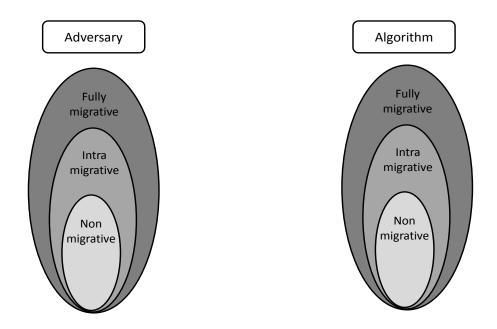

This work deals with the problem of scheduling a set of tasks to meet their deadlines on *het-erogeneous multiprocessors* with a constant number of distinct processor types. On heterogeneous multiprocessors, not all the processors are of the same type and further, the execution time of a task depends on the type of processor on which it executes. For such platforms, designing scheduling algorithms assuming that, tasks during their execution, can migrate between *processors of different types* is hard to achieve (if not impossible) for many practical systems since processors of different types typically vary in instructions sets, register formats, etc. Hence, designing algorithms in which either tasks cannot migrate between any two processors (referred to as *non-migrative*) or tasks can migrate between *processors of same type* (referred to as *intra-migrative*) is of greater practical significance.

For the *non-migrative* scenario, the scheduling problem can be solved in two steps: (i) assigning *tasks to individual processors* before run-time and (ii) once the assignment is done, scheduling the tasks on each processor using a uniprocessor scheduling algorithm at run-time. Scheduling tasks that are assigned to an individual processor is a well-studied problem and *optimal scheduling algorithms* exist for this problem, in the sense that, if there exists a schedule that meets all deadlines of the tasks then the optimal algorithms succeed in finding such a schedule as well. Hence, assuming that the tasks are scheduled during run-time on each processor using such optimal scheduling algorithms, this work focuses on designing algorithms for assigning tasks to individual processors on heterogeneous multiprocessors with a constant number of distinct processor types such that there exists a schedule that meets all deadlines for the assignment obtained by the algorithm.

Similarly, for *intra-migrative* scenario, the scheduling problem can be solved in two phases: first, *assigning tasks to processor types* (rather than to individual processors) before run-time and then *scheduling* the tasks on each processor type using a multiprocessor scheduling algorithm at run-time. Scheduling tasks that are assigned to a processor type is also a well-researched topic as this problem is equivalent to identical multiprocessor scheduling problem and *optimal schedul*-

*ing algorithms* exist for this problem. Hence, the focus of this work is to design algorithms for assigning tasks to processor types on heterogeneous multiprocessors with a constant number of distinct processor types assuming that the tasks are later scheduled using the optimal scheduling algorithms. Therefore, assuming that the tasks are scheduled during run-time on each processor type using such optimal scheduling algorithms, this work focuses on designing algorithms for assigning tasks to processor types such that there exists a schedule that meets all deadlines for the assignment output by the algorithm.

For the non-migrative scenario as well as the intra-migrative scenario, this work considers both the *two-type* heterogeneous multiprocessors in which the number of distinct processor types is *two* and the generic *t-type* heterogeneous multiprocessors in which the number of distinct processor types is  $t \ge 2$ .

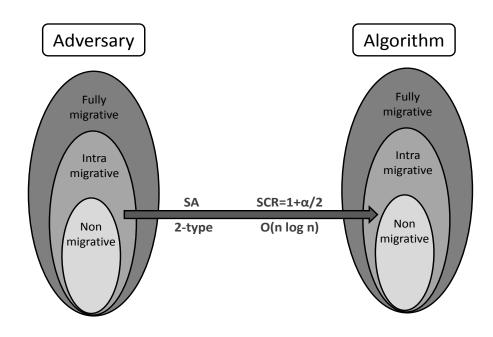

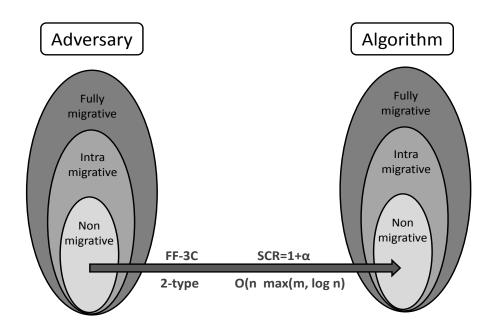

For the task assignment problems under consideration, it is not possible to design an optimal algorithm with polynomial time-complexity unless P = NP. Hence, non-optimal algorithms with polynomial time-complexity are designed and a metric referred to as the *speed competitive ratio* is used to quantify the the performance of these algorithms. The speed competitive ratio of an algorithm *A* is the smallest number *S*, such that any task set that can be assigned by an optimal algorithm upon a particular platform before run-time to meet all deadlines when scheduled at run-time, can also be assigned by *A* to meet all deadlines if given a platform in which each processor is *S* times as fast.

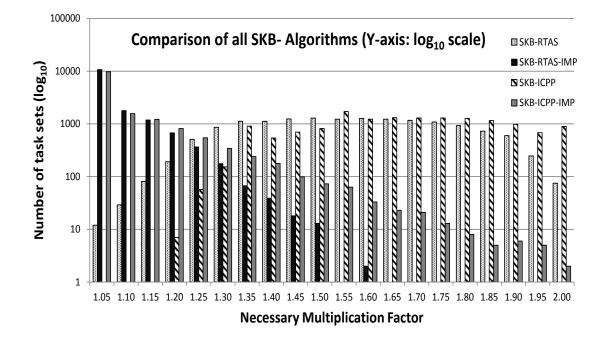

For the problem of assigning *tasks to processor types*, polynomial time-complexity algorithms with finite speed competitive ratios are proposed for two-type and t-type heterogeneous multi-processors. Similarly, several polynomial time-complexity algorithms with different speed competitive ratios are also proposed for the problem of assigning *tasks to individual processors* on two-type and t-type heterogeneous multiprocessors.

This work also studies the problem of scheduling tasks that share resources such as data structures and sensors on heterogeneous multiprocessors — referred to as the *shared resource scheduling* problem. Tasks must operate on such resources in a *mutually exclusive* manner while accessing the resource, that is, at all times, when a task holds a resource, no other task can hold that resource. For this problem, polynomial time-complexity algorithms with finite speed competitive ratios are proposed for two-type and t-type heterogeneous multiprocessors.

Overall, the proposed algorithms have the following advantages. The proposed algorithms for shared resource scheduling problem are first of their kind since no previous algorithm exists for this problem. The other algorithms proposed in this work either have a better speed competitive ratio and/or a better time-complexity and/or a better average-case performance compared to the existing algorithms in the literature.

### Resumo

Hoje em dia, os sistemas embebidos são uma das áreas mais importantes no contexto das ciências da computação, visto que 98% dos computadores são desse tipo. A maior parte dos sistemas embebidos albergam aplicações de controlo que têm que interagir de uma forma quase "instantânea" (isto é, as tarefas que compõem este tipos de aplicações têm que disponibilizar os resultados da suas computações dentro de uma meta temporal) com o meio onde estão inseridos. Dada a importância das áreas onde estes sistemas são usados, eles têm sido objecto de um grande esforço por parte da comunidade científica na procura de algoritmos de escalonamento que permitam, por um lado, quando em execução, satisfazer os requisitos das aplicações e por outro, antes da execução, garantir que esses requisitos serão satisfeitos. Isto é designado de *teoria de escalonamento para sistemas de tempo real.*

A teoria de escalonamento para sistemas de tempo real baseados em sistemas uni-processador está bem desenvolvida; os resultados científicos dessa teoria são ensinados em universidades e são bastante usados na indústria. A teoria de escalonamento para sistemas de tempo real baseados em sistemas multi-processador é uma área emergente, no entanto, a maior parte dos trabalhos considera somente sistemas multi-processador compostos por processadores idênticos. Porém, a indústria de processadores está a dirigir a sua produção para sistemas com uma arquitectura heterogénea, isto é, sistemas multi-processador compostos por processadores heterogéneos. como são exemplo o AMD Fusion, o Intel Atom e o NVIDIA Tegra.

Este trabalho aborda o problema de escalonar conjuntos de tarefas por forma a cumprirem as metas temporais em sistemas com arquitecturas heterogéneas. Nestes sistemas a execução das tarefas depende to tipo de processador no qual está a ser executada. Para plataformas com este tipo de arquitecturas, criar algoritmos de escalonamento assumindo que as tarefas podem, durante a sua execução, migrar livremente entre processadores de diferentes tipos é bastante difícil de conseguir (senão impossível), porque diferentes tipos de processadores têm conjuntos de instruções diferentes assim como formatos de registos e etc. Neste contexto, torna-se imperativo do ponto de vista prático criar algoritmos de escalonamento nos quais as tarefas não possam migrar entre processadores (designadas de não-migratórias) ou que possam migrar somente entre processadores do mesmo tipo (designadas de intra-migratórias).

Assumindo uma aplicação em que todas as tarefas são não-migratórias, o problema pode ser resolvido em dois passos: (i) atribuir previamente as tarefas aos processadores e (ii) em execução escalonar as tarefas usando um algoritmo apropriado para sistemas uni-processador. Os algoritmos para sistemas uni-processador têm sido estudados durante as últimas décadas e são, hoje-em-dia, considerados bem desenvolvidos. Existem alguns algoritmos para sistemas uniprocessador que são considerados óptimos (isto é, são capazes de escalonar qualquer conjunto de tarefas escalonável). Portanto, o foco deste trabalho é criar algoritmos para atribuição de tarefas aos processadores heterogéneos e depois estas tarefas são escalonadas de acordo com um qualquer algoritmo de escalonamento (preferencialmente óptimo) apropriado para sistemas uniprocessador. De uma forma semelhante, para aplicações compostas por tarefas intra-migratórias, o problema pode ser resolvido, também, em dois passos: (i) atribuir tarefas aos tipos de processadores (ao invés de atribuir aos processadores) e (ii) em tempo de execução escalonar essas tarefas de acordo com um algoritmo apropriado para sistemas multi-processador. Os algoritmos de escalonamento para sistemas multi-processador (assumindo sistemas com uma arquitectura idêntica, isto é, todos os processadores são iguais) têm sido estudados durante os últimos anos, e existem alguns que são considerados óptimos. Deste modo, este trabalho também endereça o problema de atribuição de tarefas a tipos de processadores heterogéneos. Em execução as tarefas são escalonadas usando algoritmos de escalonamento apropriados para sistemas com uma arquitectura idêntica.

Como estratégia de investigação foram assumidas as seguintes configurações: 2-tipos e t-tipos. Na configuração 2-tipos assume-se que o sistema multi-processador é composto por dois tipos de processadores heterogéneos enquanto que na configuração t-tipos assume-se que o sistema tem t (mais do que dois) tipos de processadores heterogéneos. Para o problema de atribuição de tarefas neste contexto, não é possível criar algoritmos de atribuição óptimos com uma complexidade temporal do tipo polinomial. Portanto, os algoritmos de atribuição de tarefas (a atribuição de tarefas é sempre feita antes da execução) desenvolvidos são considerados não-óptimos e é usado "speed competitive ratio" (SCR) como métrica para quantificar o seu desempenho. O SCR representa a relação da capacidade de processamento dos processadores. Assumindo que para um conjunto de tarefas existe um qualquer algoritmo de atribuição de tarefas para uma dada plataforma e que assegure que quando em execução, escalonadas de acordo com um algoritmo A é o menor número S (em que S representa a capacidade de processamento dos processadores) por forma a atribuir esse conjunto de tarefas e assegurar que esse conjunto de tarefas é escalonável.

Para o problema de atribuir tarefas aos tipos de processadores, neste trabalho são propostos dois algoritmos, um para os sistemas 2-*tipos* e outro para os sistemas *t-tipos*. Ambos algoritmos apresentam um SCR finito. Para os sistemas 2-*tipos*, o algoritmo apresenta baixa complexidade temporal do tipo polinomial enquanto que para os sistemas *t-tipos* apresenta complexidade temporal do tipo polinomial. Para o problema de atribuir tarefas aos processadores, neste trabalho também são propostos vários algoritmos para os sistemas 2-*tipos* e um para os sistemas *t-tipos*. Todos algoritmos apresentam um SCR finito. Para os sistemas 2-*tipos*, alguns algoritmos apresentam baixa complexidade temporal do tipo polinomial do tipo polinomial do tipo polinomial enquanto que para os sistemas *t-tipos*, alguns algoritmos apresentam baixa complexidade temporal do tipo polinomial do tipo polinomial do tipo polinomial enquanto que para os sistemas *t-tipos*, alguns algoritmos apresentam baixa complexidade temporal do tipo polinomial enquanto que para os sistemas *t-tipos*.

Em muitos sistemas de computação, além da partilha do processador, as tarefas também partilham outros recursos como estruturas de dados, sensores e etc. Portanto, nestes casos as tarefas devem usar tais recursos de uma forma exclusiva. Isto é, um recurso só pode ser usada por uma tarefa de cada vez. Neste trabalho também foi estudado o problema associado a este tipo de tarefas (que partilham outros recursos além do processador) em sistemas multi-processador composto por processadores heterogéneos. Neste trabalho são propostos dois algoritmos para este tipos de tarefas, um para os sistemas 2-*tipos* e outro para os sistemas *t-tipos*. Ambos algoritmos apresentam um SCR finito. Para os sistemas 2-*tipos*, o algoritmo apresenta baixa complexidade temporal do tipo polinomial enquanto que para os sistemas *t-tipos* apresenta complexidade temporal do tipo polinomial.

Os algoritmos propostos apresentam as seguintes vantagens quando comparados com os algoritmos existentes: (i) alguns dos algoritmos propostos são pioneiros (nomeadamente os que se referem à atribuição de tarefas que partilham recursos); (ii) apresentam SCR melhor; (iii) apresentam uma complexidade temporal melhor e (iv) também apresentam um desempenho médio melhor.

## Acknowledgments

First and foremost, I would like to express my deepest gratitude to Björn Andersson for his excellent guidance during the first two years of my PhD when he was at CISTER Research center. I thoroughly enjoyed the experience of working with him. Björn's commitment to the highest standards, his enthusiasm towards research inspired and motivated me. He always made me comfortable during the discussions which I might have abused a couple of times with my stupid remarks during some of our discussions in the middle of the nights.

I am deeply grateful to Vincent Nélis, my supervisor, for the guidance, motivation and invaluable support that he has provided over the last couple of years. Vincent is someone you will instantly like and never forget once you meet him. I think he is one of the friendliest supervisors that any student can wish for. It was really a pleasant experience to work with him as he gave me so much freedom and always encouraged me to make my own choices. Of course, our various coffee-table conversations on almost all the random topics in the world were always entertaining.

Thanks to all the people at CISTER for the great support at various levels. I would like to specially address a few of them. I am thankful to Eduardo Tovar for creating such a great environment at CISTER and for going out of his way sometimes to make my stay at CISTER and Porto a memorable one. I would like to thank some of my research collaborators, especially Konstantinos Bletsas and Geoffrey Nelissen, who have enhanced my enthusiasm and understanding of real-time systems. I would like to acknowledge Paulo Baltarejo Sousa for translating the abstract of the thesis in Portuguese. Thanks to all the students at CISTER, who have given me hours of helpful and enjoyable discussions; probably, the fact that most of us came from different parts of the world with different perspectives made it a memorable experience. My thanks also go to Sandra Almeida and Inês Almeida for the administrative support. Inês in particular has been extremely helpful with all the logistics during my initial days in Porto. Thanks to all the 'desi junta' for innumerable and unforgettable "Puerto Rico" moments; I will cherish those days/nights that we spent playing the game, those post-game discussions, arguments, wins and losses, and of course, the great food will stay with me for a long time.

Most importantly, none of this would have been possible without the love and patience of my family. My parents have been a constant source of love, concern, support and strength all these years. I would like to express my heart-felt gratitude to them. Finally, I would like to thank my best friend and wife, Dakshina for her understanding and love during the past few years. Her support, encouragement and care have helped me overcome setbacks and stay focused on my studies and her sense of humor and perspective about life has helped me stay sane through these years.

This work was partially supported by FCT (Fundação para a Ciência e Tecnologia) under the individual doctoral grant SFRH/BD/66771/2009.

vi

## **List of Author's Publications**

This is a list of papers and publications that reflects the results achieved during the development of the research work presented in this dissertation.

#### Journals

- Gurulingesh Raravi, Björn Andersson, Vincent Nélis and Konstantinos Bletsas, "Task Assignment Algorithms for Two-Type Heterogeneous Multiprocessors", *Real-Time Systems* (Accepted for publication).

- Gurulingesh Raravi, Björn Andersson and Konstantinos Bletsas, "Assigning Real-time Tasks on Heterogeneous Multiprocessors with Two Unrelated Types of Processors", *Real-Time Systems*, Volume 49, Number 1, pages 29–72, January, 2013.

#### Conferences

- Gurulingesh Raravi and Vincent Nélis, "A PTAS for Assigning Sporadic Tasks on Twotype Heterogeneous Multiprocessors", *In Proceedings of the 33rd IEEE Real-Time Systems Symposium*, pages 117–126, San Juan, Puerto Rico, December 4–7, 2012.

- Gurulingesh Raravi, Björn Andersson, Konstantinos Bletsas and Vincent Nélis, "Task Assignment Algorithms for Two-Type Heterogeneous Multiprocessors", *In Proceedings of the 24th Euromicro Conference on Real-Time Systems*, pages 34–43, Pisa, Italy, July 11–13, 2012. (Outstanding Paper Award)

- Gurulingesh Raravi, Björn Andersson and Konstantinos Bletsas, "Provably Good Scheduling of Sporadic Tasks with Resource Sharing on a Two-Type Heterogeneous Multiprocessor Platform", *In Proceedings of the 16th International Conference On Principles Of Distributed Systems*, pages 528–543, Toulouse, France, December 12–16, 2011.

- Björn Andersson, Gurulingesh Raravi and Konstantinos Bletsas, "Assigning Real-Time Tasks on Heterogeneous Multiprocessors with Two Unrelated Types of Processors", *In Proceedings of the 31st IEEE Real-Time Systems Symposium*, pages 239–248, Washington, DC, USA, November 30 December 3, 2010.

#### **Technical Reports**

• Gurulingesh Raravi and Björn Andersson, "Real-Time Scheduling with Resource Sharing on Heterogeneous Multiprocessors", 2013.

- Gurulingesh Raravi and Björn Andersson, "Task Assignment Algorithm for Two-type Heterogeneous Multiprocessors using Cutting Planes", 2013.

- Gurulingesh Raravi and Vincent Nélis, "Task assignment algorithms for heterogeneous multiprocessors", 2013.

# Contents

| Ι | Intr                                                                 | oduction                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                              |

|---|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1 | Back<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                              | seground on Real-Time Systems         Introduction to real-time systems         Modeling real-time systems         Categorization of real-time systems         Real-time scheduling paradigms         Background on real-time scheduling theory                                                                                                                                                               | <b>3</b><br>5<br>6<br>14<br>16<br>17                                                           |

| 2 | Over<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7                | rview of This Research         Problem definition         Hardness of the problem         Why study heterogeneous multiprocessors?         Common assumptions         Performance metrics         Contributions and significance of this work         Organization of the report                                                                                                                              | <ul> <li>23</li> <li>25</li> <li>26</li> <li>27</li> <li>28</li> <li>34</li> <li>36</li> </ul> |

| Π | Tw                                                                   | o-type Heterogeneous Multiprocessors                                                                                                                                                                                                                                                                                                                                                                          | 39                                                                                             |

| 3 | Intra<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | a-migrative Scheduling on Two-type Heterogeneous MultiprocessorsIntroductionSystem modelThe hardness of the intra-migrative task assignment problemMILP-Algo: An optimal intra-migrative task assignment algorithmLP-Algo: An intra-migrative task assignment algorithmSA: An intra-migrative task assignment algorithmSpeed competitive ratio of SA algorithmAverage-case performance evaluationsConclusions | <b>41</b><br>41<br>44<br>45<br>49<br>52<br>57<br>58<br>68<br>71                                |

| 4 | Non<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                        | -migrative Scheduling on Two-type Heterogeneous Multiprocessors         Introduction         The hardness of the non-migrative task assignment problem         FF-3C algorithm and its variants         SA-P algorithm         Cutting plane algorithm         A polynomial time approximation scheme                                                                                                         | <b>73</b><br>73<br>76<br>80<br>118<br>129<br>154                                               |

|     | 4.7         | Conclusions and Discussions                                                                             | 182 |

|-----|-------------|---------------------------------------------------------------------------------------------------------|-----|

| 5   | Shar        | ed Resource Scheduling on Two-type Heterogeneous Multiprocessors                                        | 187 |

|     | 5.1         | Introduction                                                                                            | 187 |

|     | 5.2         | System model and assumptions                                                                            | 189 |

|     | 5.3         | The hardness of the shared resource scheduling problem                                                  | 190 |

|     | 5.4         | Overview of our approach                                                                                | 192 |

|     | 5.5         | Few notations and useful results                                                                        | 193 |

|     | 5.6         | FF-3C-vpr algorithm and its speed competitive ratio                                                     | 201 |

|     | 5.7         | Conclusions                                                                                             | 206 |

| III | [ <b>T-</b> | type Heterogeneous Multiprocessors                                                                      | 209 |

| 6   | Intr        | a-migrative Scheduling on T-type Heterogeneous Multiprocessors                                          | 211 |

| U   | 6.1         |                                                                                                         | 211 |

|     | 6.2         | System model                                                                                            | 211 |

|     | 6.3         | MILP-Algo: An optimal intra-migrative algorithm                                                         | 214 |

|     | 6.4         | An overview of our intra-migrative task assignment algorithm, LPG <sub>IM</sub>                         | 215 |

|     | 6.5         | Step 1 of $LPG_{IM}$ : Solving the LP formulation                                                       | 210 |

|     | 6.6         | Step 2 of $LPG_{IM}$ : Forming the bi-partite graph                                                     | 217 |

|     | 6.7         | Step 3 of LPG <sub>IM</sub> : Detecting and removing the circuits in the graph $\ldots \ldots \ldots$   | 21) |

|     | 6.8         | Step 4 of LPG <sub>IM</sub> : Integrally assigning the fractional tasks $\dots \dots \dots \dots \dots$ | 221 |

|     | 6.9         | Conclusions                                                                                             | 235 |

|     | 0.9         |                                                                                                         | 233 |

| 7   | Non         | -migrative Scheduling on T-type Heterogeneous Multiprocessors                                           | 237 |

|     | 7.1         | Introduction                                                                                            | 237 |

|     | 7.2         | System model                                                                                            | 240 |

|     | 7.3         | $LPG_{NM}$ : The non-migrative task assignment algorithm                                                | 241 |

|     | 7.4         | Conclusions                                                                                             | 244 |

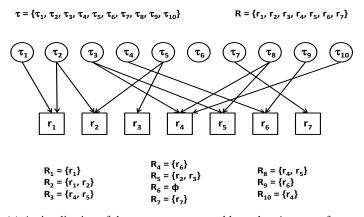

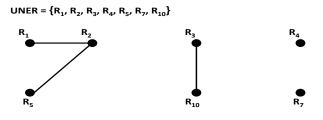

| 8   | Shar        | ed Resource Scheduling on T-type Heterogeneous Multiprocessors                                          | 245 |

|     | 8.1         | Introduction                                                                                            | 245 |

|     | 8.2         | System model                                                                                            | 247 |

|     | 8.3         | Overview of our algorithm                                                                               | 251 |

|     | 8.4         | The new algorithm, LP-EE-vpr                                                                            | 253 |

|     | 8.5         | Speed competitive ratio of LP-EE-vpr algorithm                                                          | 260 |

|     | 8.6         | Discussion                                                                                              | 280 |

|     | 8.7         | Conclusions                                                                                             | 282 |

| IV  | Co          | onclusions                                                                                              | 285 |

| 9   | Con         | clusions, Discussions and Future Directions                                                             | 287 |

|     | 9.1         | Summary of results                                                                                      | 288 |

|     | 9.2         | Implication of the results                                                                              | 289 |

|     | 9.3         | Future directions                                                                                       | 290 |

|     | 9.4         | Concluding remarks                                                                                      | 292 |

| Re  | feren       | ces                                                                                                     | 295 |

Part I

# Introduction

### **Chapter 1**

## **Background on Real-Time Systems**

For the past 40 years, the transistor/semi-conductor density has roughly doubled every 18 months as observed by Gordon Moore [BC03]. Also, since 1980s, the processor clock speed has increased about 30% every year. The microprocessor vendors improved their silicon technology to go faster and faster until early 2000s. However, during this time, they realized that the clock speed has hit a wall since it started violating the principles of fundamental physics. Although computing power increases linearly with the clock speed, the power density increases with the square or cube, depending on the electrical model. It was seen that clock frequencies beyond about 5GHz could result in melting the chip unless cooled using exotic cooling technologies [LM08].

In order to overcome the limitations imposed by this clock speed wall and to continue leveraging Moore's Law to increase performance and reduce power, microprocessor vendors decided to go the *multiprocessor/multicore chip* way. Instead of increasing the clock rate of power-hungry monolithic cores, chip vendors adapted a design in which multiple slower processors are integrated on a single chip which collectively increase the computational capability while consuming lesser power. With this design choice, the number of processing cores per chip started doubling with each new generation of microprocessor chips, a trend which will continue for the foreseeable future [LM08], which in turn is leading to a significant increase in the number of applications being deployed on such chips.

Subsequently, computer controlled systems have percolated in all aspects of our daily lives. From mobile phones to nuclear reactor controllers, computer controlled systems have reached all aspects of human life in merely a few decades. In near future, it is expected that day-to-day activities such as cleaning the house, driving the car, etc. will be performed by computer controlled systems without human intervention. Actually, research prototypes that can perform such activities already exist and a few of these are even commercially available. The complexity of such computer-controlled systems is continuously increasing due to the increase in the functionalities, the increase in the interactivity between different functionalities and the increase in the responsiveness requirement. Hence, many of these computer-controlled systems demand more and more performance from the processors that implement these functionalities and multicores have emerged as an inevitable choice for such systems due to their high performance, low cost and low power consumption characteristics and also due to the aggressive marketing of multicores by all the chip vendors.

Most of the computer controlled systems these days are *embedded systems*. An embedded system is defined as a computer-controlled system (sometimes, it can even be a simple monitoring system) in which the hardware and software is specifically designed for a particular functionality. For example, mobile phones, set-top boxes, cruise control systems in cars and autopilot system in an airplane. It is estimated that over 98% of all computing devices are "embedded" in nature and hence they do not even look like computers [RM09, Tan07, Zha03]. In other words, computers are moving away from the well-known desktop and can be found in everyday devices like credit cards, microwaves, mobile phones and cars. Let us consider an example of such an embedded system listed in [And03].

**Example 1.** Consider a hypothetical car where a computer in the car is given a street address and the computer automatically drives to that address with no human intervention (research prototypes that can do things similar to this exist [JPKA95, Spe] but are not commercially available). Think about yourself as being the computer in the car.

You are driving your car and approach a crossing. You see that there is no pedestrian there (a sensor reading) so you close your eyes for a few seconds and listen to the radio while your car approaches the intersection, and after those seconds you conclude that you can drive straight ahead without any need to slow down (an action). If, during those seconds, a pedestrian starts to walk at the crossing, an accident may occur, neither because your sensor reading was incorrect nor because you inferred an incorrect action based on your sensor reading, but because your action was based on a sensor reading that was too old. If you had monitored your environment with periodic sampling of a high enough rate, an accident would not have occurred. Let us assume that you woke up in time to see the pedestrian (a sensor reading) so you conclude that you should break or steer away (an action). Although you computed the right answer (that is, made the right decision) this is not sufficient for successful driving; you need to apply a break force quickly enough, that is, before a deadline. This deadline depends on states in the environment, for example, the speed of your car and the distance from your car to the pedestrian.

Observe that in the embedded system described in Example 1, it is not only essential to perform the computations or actions in a logically correct manner but it is also important to perform them at the *right time*. For example, failing to detect the pedestrian at the right time or failing to apply the brakes with the right force at the right time may lead to an undesired output. Such embedded systems in which the correctness of the output not only depends on the value but also depends on the time of delivery, are referred to as real-time systems which is the topic of next section.

**Organization of the chapter.** The rest of the chapter is organized as follows. Section 1.1 introduces the concept of real-time systems. Section 1.2 discusses how such systems are modeled. Section 1.3 discusses the classification of real-time systems. Section 1.4 introduces the design space of real-time scheduling and finally a brief background on real-time scheduling theory is provided in Section 1.5.

#### **1.1 Introduction to real-time systems**

A real-time system is a system in which the correctness of the computations not only depends upon the logical correctness of the computation but also upon the time at which the result is produced. As mentioned earlier, in Example 1, if the pedestrian is not detected at the *right time* and/or if the brakes are not applied at the right time with the right force to bring the car to a halt then it may lead to an accident. Similarly, all real-time systems have *temporal requirements* which need to be guaranteed in order to avoid an undesirable behavior from the system.

The temporal requirements in a real-time system generally have their origin in the design process [And03]. Specifically, the designer specifies how the computer-controlled system in general should behave. For example, consider Adaptive Cruise Control (ACC) in a car. The objective of an ACC system is to ensure that the car approximately maintains a *safe distance* (typically set by the driver) from any *leading vehicle* (i.e., a vehicle in front of the car in the same lane). Once the behavior is defined, the designer derives the timing constraints such that, if these constraints are satisfied, the behavior is said to be as desired. These derived timing requirements depend on the state of the environment. For example, in an ACC system, the temporal delay that can be tolerated between detecting the leading vehicle (sensing) and taking actions in order to maintain the car at a pre-set safe separation distance from the leading vehicle depends on (i) the tolerable error margin, (ii) the dynamics of the car, (iii) the current distance of separation between the car and the leading vehicle, the speed of the leading vehicle, etc.

The consequence of violating the temporal requirements of a real-time system can depend on the environment. In some cases, not satisfying the temporal requirements may lead to a catastrophe such as severe damage to the equipment or even loss of human lives — such systems are referred to as *hard real-time systems*. For example, failing to maintain the safe distance between the car and the leading vehicle may lead to an accident which in turn may lead to loss of human lives. In other cases, the consequence may not be that harmful and instead the user experiences a degradation in the quality-of-service provided by the system which does not endanger the integrity of the user or the equipment or the environment — such systems are referred to as *soft real-time systems*. For example, in a multimedia application, failing to decode a video frame on time once in a while is acceptable for the user as long as certain quality of service is ensured. (More discussion about hard and soft real-time systems is provided later in the chapter.) Therefore, it is very essential to ensure that all the timing requirements are met for hard real time systems and to ensure that an acceptable quality-of-service is provided for soft real-time systems. This can be achieved using schedulability analysis.

**Scheduling and Schedulability Analysis.** An important aspect in the process of designing realtime systems is to ensure before run-time that the timing requirements are met at run-time. In order to do this, the *entities* which perform computations (such as reading the sensor data, computing the current distance of separation between the car and the leading vehicle based on the sensor readings, computing the speed of the car) need to be *scheduled* using an algorithm so as to meet all the timing requirements. In other words, these entities need to be *allocated* sufficient *resources*  such that they finish their execution before certain time thereby meeting all the timing requirements of the system. The process of verifying whether the timing requirements of the real-time system will be met or not when entities are scheduled using an algorithm on the computing resources, is referred to as the *schedulability analysis* of the algorithm. For hard real-time systems, the analysis needs to be rigorous and performed before run-time to provide a guarantee that all the timing requirements will be met during the run time. Whereas for soft real-time systems, some kind of stochastic analysis is sufficient as such systems need not meet *all* the timing requirements and may afford to miss *some* of its timing requirements as long as the system continues to provide an acceptable quality-of-service.

We now describe how the entities that perform computations (also referred to as the *workload*) are modeled and the resources that need to be allocated to these entities (also referred to as the *computing platform*) are modeled. Overall, modeling of real-time systems is discussed next.

#### **1.2 Modeling real-time systems**

First, the description of modeling the real-time workload is provided and then the modeling of the computing platform on which the workload is executed is discussed.

#### 1.2.1 Modeling real-time workload

This section describes how the real-time workload is modeled using the notion of *job* and *task*.

#### 1.2.1.1 Job and its characterization in real-time systems

**Definition 1 (Job).** A unit of work (say, a set of instructions) that performs some computations and which needs to be scheduled and executed is referred to as a job.

Informally, a job is a set of instructions in the context of the application that executes sequentially and provides a given application-relevant logical result. In real-time systems, each job is characterized by the following parameters:

- **Release time of a job:** The time instant at which a job becomes available for execution is referred to as the release time of the job. So, a job can be scheduled and executed any time instant at or after its release time<sup>1</sup>.

- **Deadline of a job:** The time instant by which the execution of a job needs to be completed is referred to as the deadline of the job. The deadline can be expressed in two ways:

- Relative deadline of a job: It is the maximum allowable *response time* of the job, where the response time of the job is the duration of time interval spanning from the release time of the job to its completion time.

<sup>&</sup>lt;sup>1</sup>Note that there may be other constraints as well such as data dependency and control dependency that need to be considered before scheduling and executing the job.

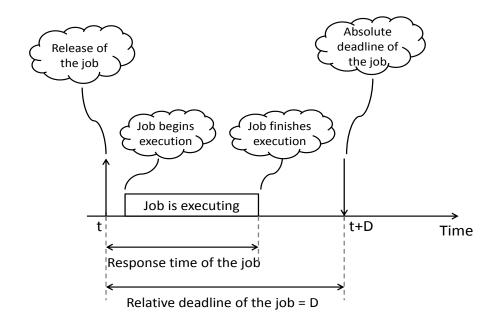

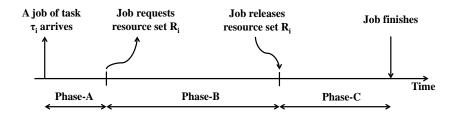

Figure 1.1: The parameters used to characterize a job in real-time systems. In this example, the release time of the job is t and its relative deadline is D which implies that the absolute deadline of the job is t + D.

Absolute deadline: It is the absolute time instant by which the job is required to finish its execution. In other words, it is given by the release time of the job plus the relative deadline of the job.

Figure 1.1 illustrates the above discussed terms. As shown in the figure, the job has a release time of t and a relative deadline of D.

#### 1.2.1.2 Task and its characterization in real-time systems

This section defines a task, lists different kinds of tasks and parameters used to characterize the tasks in the context of real-time systems.

**Definition 2** (Task). A collection of related jobs which jointly provide some system function is referred to as a task. Stated another way, a task releases a (potentially infinite) sequence of jobs. A task is generally denoted by  $\tau_i$  where *i* is the task index.

**Remark about notation.** From the definition of the job and the task, it can be seen that, a task is an abstract entity which releases many jobs over a period of time and every job of a task executes on some processor. However, to avoid tedium, in the rest of the thesis, instead of saying "a job of a task executes", we say that, "a task executes".

A task is characterized by the following parameters.

• Worst-case execution time of a task: The worst-case execution time (WCET) of a task is defined as the maximum duration of time that the task (i.e., any job of this task) could

take to execute on a given processor. All the jobs of a task will have the same worst-case execution time which is that of the task. In other words, the WCET of a task is the upper bound on the execution duration of any job of this task and hence the actual execution times of some of the jobs of this task may be less than the WCET of the task. The WCET of a task  $\tau_i$  is commonly denoted by  $C_i$ .

• Relative Deadline of a task: The relative deadline of a task is defined as the maximum allowable response time of any job of this task. Hence, all the jobs of a task have the same relative deadline which is that of the task. The deadline of a task  $\tau_i$  is generally denoted by  $D_i$ .

**Remark about notation.** To avoid tedium, in the rest of the thesis, we refer to "Relative Deadline" as "Deadline".

#### **Definition 3** (Task set). A collection of tasks is referred to as a task set and is denoted by $\tau$ .

In real-time systems, tasks can be classified into three categories depending on the job release pattern:

- **Periodic:** These tasks generate jobs *periodically*, separated by a fixed time interval, in the sense that, after the arrival of the first job at any time instant, the arrival of subsequent jobs are separated by a fixed time interval which is given by the *period* of the task. The period of such a task  $\tau_i$  is generally denoted by  $T_i$ .

- **Sporadic:** In this task model, jobs arrive *sporadically*, i.e, after the arrival of the first job at any time instant, the subsequent jobs of this task may arrive at any time once a *minimum inter-arrival time* has elapsed since the arrival of the previous job of the same task. The minimum inter-arrival time of such a task  $\tau_i$  is generally denoted by  $T_i$ .

- Aperiodic: The jobs of these tasks may arrive at any time instant, in the sense that, no information about their arrival pattern is given.

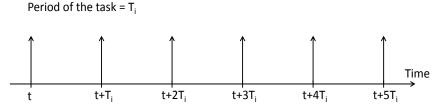

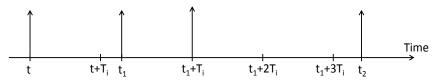

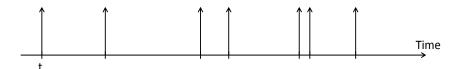

Figure 1.2 illustrates the above discussed three categories of tasks. Figure 1.2a shows a periodic task with a period of  $T_i$ . As shown in this figure, the first job of the task is released at time tand then subsequent jobs of this task are released exactly  $T_i$  time units apart, i.e., the second job is released at  $t + T_i$ , the third job is released at  $t + 2T_i$  and so on. Figure 1.2b shows a sporadic task with a minimum inter-arrival time of  $T_i$ . As shown in this figure, release of two consecutive jobs is always separated by a time duration of at least  $T_i$  units; for example, the first job is released at t, the second job is released at  $t_1 \ge t + T_i$ , the third job is released at  $t_1 + T_i$ , the fourth job is released at time  $t_2 \ge t_1 + 2T_i$  and so on. Figure 1.2c shows an aperiodic task for which nothing can be said about the job release pattern.

A periodic task is characterized by its worst-case execution time, period and deadline. A sporadic task is characterized by its worst-case execution time, minimum inter-arrival time and deadline. An aperiodic task is characterized by its worst-case execution time and deadline.

(a) Periodic task with a period of  $T_i$  — the duration between the arrival of any two consecutive jobs is exactly equal to  $T_i$  units.

Minimum inter-arrival time of the task =  $T_i$

(b) Sporadic task with a minimum inter-arrival time of  $T_i$  — the duration between the arrival of any two consecutive jobs is either equal to or greater than  $T_i$  units.

Arrival information of the task is not known

(c) Aperiodic task with no information on release pattern — the duration between the arrival of any two consecutive jobs is unknown.

Figure 1.2: A visualization of different categories of tasks — an upward arrow indicates the arrival of a job of a task.

This research considers sporadic tasks.

We now define valid job arrival pattern for a sporadic task set.

**Definition 4** (Valid job arrival pattern of a sporadic task set.). A job arrival pattern of a sporadic task set is said to be valid if every task in the task set respects its minimum inter-arrival time while releasing the jobs. For a given sporadic task set, there can be multiple valid job arrival patterns.

The following example illustrates the concept of valid job arrival pattern for a given sporadic task set.

**Example 2.** Consider a sporadic task set  $\tau = {\tau_1, \tau_2}$ . Let the minimum inter-arrival time of task  $\tau_1$  be given by  $T_1 = 4$  and let the minimum inter-arrival time of task  $\tau_2$  be given by  $T_2 = 5$ . Figure 1.3a and Figure 1.3b show a valid job arrival pattern each for this task set. Note that, it is

Figure 1.3: Examples of valid and invalid job arrival patterns for the task set of Example 2.

easy to construct many more valid job arrival patterns for this task set in a similar manner. For the sake of completeness, Figure 1.3c shows an invalid job arrival pattern for this task set (since the release time of second and third job is not separated by at least 4 units).

The sporadic task sets can be classified into three categories depending on the relation between the deadlines and the minimum inter-arrival times of every task in the task set.

- Implicit-deadline: In implicit-deadline sporadic task set, every task has its deadline *equal* to its minimum inter-arrival time, i.e.,  $\forall \tau_i \in \tau : D_i = T_i$ .

- Constrained-deadline: In such a task set, every task has its deadline *no greater than* its minimum inter-arrival time, i.e., ∀τ<sub>i</sub> ∈ τ : D<sub>i</sub> ≤ T<sub>i</sub>.

- Arbitrary-deadline: In arbitrary-deadline sporadic task set, there is no relation between deadlines and minimum inter-arrival times of tasks. In other words, in such task sets, the deadline of every task may be less than or equal to or greater than its minimum inter-arrival time.

This work considers implicit-deadline sporadic task sets.

For the sake of completeness and future references, we now formally define an implicit-deadline sporadic task set.

**Definition 5** (**Implicit-deadline sporadic task set**). In an implicit-deadline sporadic task set  $\tau$ , each task  $\tau_i \in \tau$  is characterized by a worst-case execution time (WCET) and a minimum interarrival time  $T_i$  (which is equal to its deadline). Each task  $\tau_i$  releases a (potentially infinite) sequence of jobs, with the first job released at any time and subsequent jobs released at least  $T_i$  time units apart. Each job released by task  $\tau_i$  has to complete its execution within  $T_i$  time units from its release.

We now define a parameter that is used to characterize an implicit-deadline sporadic task and a parameter that is used to characterize a set of implicit-deadline sporadic tasks. These parameters are extensively used while performing the schedulability analysis of algorithms in real-time literature and also in subsequent chapters of this document.

**Definition 6** (Utilization of an implicit-deadline sporadic task). For an implicit-deadline sporadic task, the ratio of its worst-case execution time and its minimum inter-arrival time is referred to as the utilization of the task. The utilization of a task  $\tau_i$  is denoted by  $u_i$  and is formally defined as:  $u_i \stackrel{\text{def}}{=} \frac{C_i}{T_i}$ .

**Definition 7** (Utilization of an implicit-deadline sporadic task set). It is the sum of utilizations of all the tasks in the task set. The utilization of a task  $\tau$  is denoted by  $U_{\tau}$  and is formally defined as:  $U_{\tau} \stackrel{\text{def}}{=} \sum_{\tau_i \in \tau} u_i$ .

#### **1.2.2** Modeling the computing platform

This section describes how the computing resources, also referred to as computing platform, on which the workload needs to be allocated and executed, is modeled. In the context of the work, we are interested in modeling the computing platform as a set of *processing elements* which has a limited computational capacity. This is sufficient for the purpose of this work since the end objective is to assign and execute the workload on these processing elements such that on each processing element (a group of processing elements, respectively), the total computational demand of the workload assigned on the processing element (the group of processing elements, respectively) should not exceed the capacity of that processing element (that group of processing elements, respectively) which in turn guarantees that all the timing requirements of the workload will be met — more details are provided in the next chapter. For this reason, we ignore modeling the other architectural features of the computing platform such as caches, memory, system bus, etc. and hence do not consider the impact of sharing such hardware resources on the execution behavior of the tasks.

If the computing platform on which the real-time workload needs to be executed consists of a single processor then it is referred to as a *uniprocessor* platform. If the computing platform consists of multiple processors then it is referred to as a *multiprocessor* platform or a *multicore* platform. The real-time scheduling theory for uniprocessor system is well-understood. However,

the same cannot be said about the multiprocessor real-time scheduling theory (more details are given in the subsequent parts of this chapter). Hence, in this work, we focus on multiprocessor systems.

**Remark about notation.** In this dissertation, very often, the terms "processor" and "core" are interchangeably used and they both refer to the processing element on which the tasks are assigned and scheduled.

#### This work considers multiprocessor computing platforms.

Multiprocessor systems can be categorized into three groups as follows:

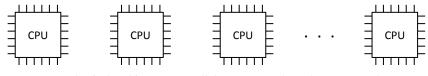

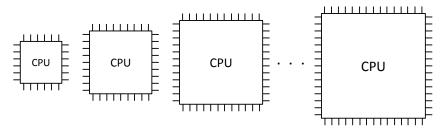

- Identical: In identical multiprocessors, all the processors are identical, in the sense that, they all have exactly the same computing capacity. Hence, the rate of execution of all tasks is the same on all processors. These multiprocessors are sometimes referred to as *homogeneous* multiprocessors. Some example of such multiprocessors are: Intel Core 2 Quad Processor [Int13e], Intel Core 2 Extreme Processor [Int13d], AMD Dual Core Processors [AMD13b] and ARM Cortex-A9 MPCore [ARM13a].

- Uniform: By contrast, in uniform multiprocessors, each processor is characterized by its own speed or computing capacity. Hence, the rate of execution of a task depends on the speed of the processor. Thus, a processor of speed *s* > 1 will execute all tasks *s* times faster than a processor of speed 1. Some examples of uniform multiprocessors are: ARM big.LITTLE Processing [ARM13b] and Samsung Exynos 5 Octa [Sam13b].

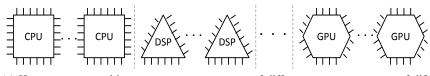

- Heterogeneous: These are multiprocessors in which the processors are of different *types*. For example, in a heterogeneous multiprocessor, some processors can be of type Central Processing Units (CPUs), some processors can be of type Graphics Processing Units (GPUs), some other processors can be of type network processors and so on. The processors of different types generally differ in their instruction sets, register formats, etc. Hence, the rate of execution of a task depends on both the processor type and the task. Indeed, not all tasks may be able to execute on all processors. These multiprocessors are sometimes referred to as *unrelated* multiprocessors. Some examples of heterogeneous multiprocessors are: AMD Fusion [AMD13a], Intel Atom [Int13c], Nvidia Tegra 3 [Nvi12].

Figure 1.4 illustrates the above discussed three categories of multiprocessors.

A special case of heterogeneous multiprocessor is a t-type heterogeneous multiprocessor which is defined as follows.

**Definition 8** (t-type heterogeneous multiprocessor). A heterogeneous multiprocessor in which the number of distinct types of processors is a constant,  $t \ge 2$ , is referred to as a t-type heterogeneous multiprocessor. It is also referred to as a t-type platform.

A special case of t-type heterogeneous multiprocessor is a two-type heterogeneous multiprocessor which is defined as follows.

(a) Identical multiprocessors: all the processors have the same speed.

(b) Uniform multiprocessors: processors have different speeds — size is proportional to the speed.

(c) Heterogeneous multiprocessors: processors are of different types; processors of different types can differ in their instruction sets, register formats, etc. — different shapes correspond to different processor types.

Figure 1.4: A visualization of different categories of multiprocessor systems.

**Definition 9** (Two-type heterogeneous multiprocessor). A two-type heterogeneous multiprocessor is a special case of t-type heterogeneous multiprocessor in which there are only two distinct types of processors, i.e., t = 2, and thus each processor in the system belongs to one of these types. It is also referred to as a two-type platform.

This research considers both two-type and t-type heterogeneous multiprocessors.

The reason for studying heterogeneous multiprocessor systems is that the heterogeneous multiprocessor model is more generic than identical or uniform multiprocessor model, in terms of the systems that it can accommodate. Hence, the results obtained for this model are also applicable to identical or uniform multiprocessor models. The reason for studying heterogeneous multiprocessors with a constant number of distinct types of processors (i.e., both two-type and t-type) is that, (i) in practice, most of the heterogeneous multiprocessors are of this nature since many chip manufacturers offer chips having a constant number of distinct types of processors, especially two types of processors, for example, see [AMD13a, Int13b, Nvi12, App13, Qua13, Sam13a, ST 12, Tex13] and (ii) studying the generic t-type heterogeneous multiprocessors (in which  $t \ge 2$ ) helps in understanding the problem better and solutions to such generic models may cater to complex systems in near future.

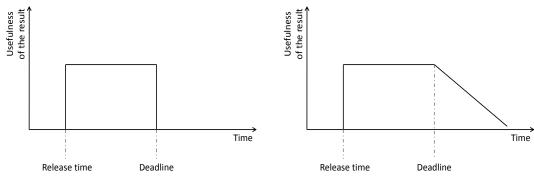

(a) Hard real-time job — usefulness of the result drops to zero (or even becomes negative) when tardiness exceeds zero. (b) Soft real-time job — usefulness of the result degrades gracefully as the tardiness increases.

Figure 1.5: A visualization of hard and soft jobs in real-time systems.

#### **1.3** Categorization of real-time systems

With the understanding of a job and a task, we now discuss the earlier mentioned two categories of real-time systems in detail. In literature, the real-time systems are generally categorized as either hard or soft real-time systems [Kop11, Liu00, Bur91]. One way the distinction is done is based on the usefulness of the result measured using the *tardiness* of jobs [Liu00].

**Definition 10** (**Tardiness of a job**). The tardiness of a job indicates how late the job execution is compared to its deadline. The tardiness of a job is zero if it completes execution on or before its deadline; otherwise, the tardiness of a job is given by the difference between its completion time and its deadline.

Based on the usefulness of the result measured using tardiness, the jobs in real-time systems are categorized as follows:

- hard real-time job: the usefulness of the result (in the scope of the application) of a hard real-time job falls abruptly and even may become negative (i.e., may be harmful or catastrophic) when the tardiness of such a job exceeds zero. The implication of this is that missing the deadline of a hard real-time job can lead to a catastrophe and hence the user requires a rigorous validation by provably correct and efficient procedures to ensure that such jobs always meet their deadlines.

- **soft real-time job:** the usefulness of the result of a soft real-time job decreases gradually as the tardiness of such a job increases. The implication of this is that missing some deadlines of a soft real-time job is acceptable. The user in this case only requires a demonstration that the job meets some statistical constraint, for example, average number of deadlines that are met using techniques such as performance profiling.

The above defined hard and soft real-time jobs are illustrated in Figure 1.5.

Note that the above definitions can be extended for a task to obtain the terms *hard real-time task* and *soft real-time task*.

**Definition 11 (Hard real-time system.).** A system that consists of only hard real-time tasks is referred to as hard real-time system.

For hard real-time systems, the designer of the system has to prove rigorously before run-time that all the deadlines will be met and as a result system will not exhibit any undesired behavior at run-time. We now give an example of a hard real-time system [Liu00].

**Example 3.** we consider an automatically controlled train. It cannot stop instantaneously. When the signal is red (stop), its braking action must be activated a certain distance away from the signal post at which the train must stop. This braking distance depends on the speed of the train and the safe value of deceleration. From the speed and safe deceleration of the train, the controller can compute the time for the train to travel the braking distance. This time in turn imposes a constraint on the response time of the jobs which sense and process the stop signal and activate the brake. This system is a hard real-time system as failing to meet the timing constraints here may lead to a catastrophe as it can cause loss of human lives and and/or significant damage to the equipment (i.e., train infrastructure) and hence this system needs to be formally validated at design time to guarantee that all timing requirements will be met.

**Definition 12 (Soft real-time system.).** A system with all soft real-time tasks is referred to as soft real-time system.

For soft real-time systems, the designer of the system is rarely required to prove rigorously that the system meets its real-time performance objectives. However, in many systems, a statistical based guarantee (for example, the average number of deadlines that are met) needs to be provided. The following example of a soft real-time system is listed in [Liu00].

**Example 4.** Let us consider multimedia systems that provide the user with services of "guaranteed" quality. For example, a frame of a movie must be delivered every thirtieth of a second, and the difference in the times when each video frame is displayed and when the accompanied speech is presented should be no more than 80 msec. In fact, it is common to subject each new video stream to be transmitted by a network to an acceptance test. If the network cannot guarantee the satisfaction of timing constraints of the stream without violating the constraints of existing streams, the new stream is rejected, and its admission is requested again at some later time. However, the users are often willing to tolerate a few glitches, as long as the glitches occur rarely and for short lengths of time. At the same time, they are not willing to pay the cost of eliminating the glitches completely. For this reason, we often see timing constraints of multimedia systems guaranteed on a statistical basis, (e.g., the average number of late/lost frames per minute is less than 2). Moreover, users of such systems rarely demand any proof that the system indeed honor its guarantees. The quality-of-service guarantee is soft, the validation requirement is soft, and the timing constraints defining the quality are soft.

This work focuses on hard real-time systems.

#### 1.4 Real-time scheduling paradigms

In real-time systems, and especially in hard real-time systems, an important aspect while building such systems is to schedule the tasks on the computing platform so as to meet all the deadlines. Scheduling is an act of allocating resources (especially, processors) between various tasks with the objective of meeting the deadlines of all the tasks. In real-time systems, there are at least two different ways to schedule the tasks [RS94].

- **Table-driven scheduling:** In table-driven scheduling, a table is generated before run-time with the time slots in which each task must be executed. During this process, it is ensured that, on a processor, at any time, at most one task is executing. Later, at run time, this table is used to execute the tasks in their respective time slots.

- **Priority-driven scheduling:** In priority-driven scheduling, a number referred to as *priority* is assigned to each task often based on the task parameters. For example, the priority assignment can be based on periods, say a task with smaller period has a higher priority compared to the priority of a task with a higher period. Then, among the tasks that are ready to execute, the task with the highest priority is executed. The priority-driven scheduling techniques can in turn be categorized as follows [DB11].

- Task-static priority scheduling. Each task has a single static priority that applies to all of its jobs, i.e., every job of a task gets the same priority as that of the task. Rate Monotonic scheduling (RM) [LL73] is an example of such a scheduling.

- Job-static priority scheduling. Different jobs of the same task may have different priorities, but each job has a single static priority. An example of such a scheduling technique is Earliest Deadline First (EDF) [LL73].

- Dynamic-priority scheduling. A job of a task may have different priorities at different times. Least Laxity First (LLF) [Mok83a] is an example for this category.

This research considers job-static priority scheduling.

Every scheduling approach in general falls into one of the two categories: *preemptive* or *non-preemptive* as defined below.

- **Preemptive scheduling:** In preemptive scheduling, a task executing on a processor can be forced by the scheduler to relinquish the processor before it completes execution (i.e., *preempted*) in order to execute some other ready-to-run higher priority task. The task that is interrupted is resumed sometime later for execution.

- Non-preemptive scheduling: In non-preemptive scheduling, a task executing on a processor will not be preempted and will therefore execute until completion.

This work considers preemptive scheduling.

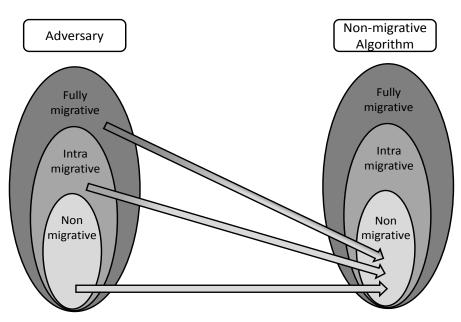

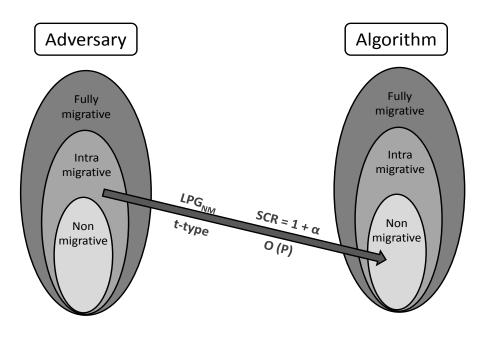

Another way to categorize the scheduling techniques, especially the ones intended for multiprocessors is based on whether a task is allowed to migrate from one processor to another or not. This is describe next and is illustrated in Figure 1.6.

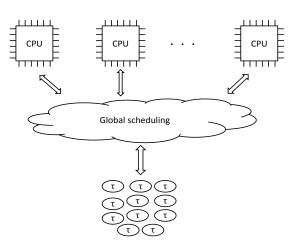

- **Fully-migrative scheduling.** In fully-migrative scheduling, tasks are not assigned/pinned to individual processors and all the processors are scheduled using a single algorithm. This scheduling technique is sometimes also referred to as *global scheduling*. Depending on the granularity of migration, fully-migrative scheduling approaches are categorized as follows:

- Task-level migration: Different jobs of the same task may execute on different processors; however, each job must execute entirely on a single processor.

- Job-level migration: Here, even a job may migrate during its execution and continue to execute on a different processor; however, the job cannot execute in parallel on more than one processor, i.e., a job can only execute on at most one processor at any time.

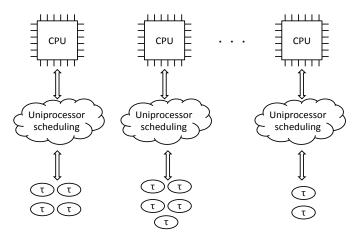

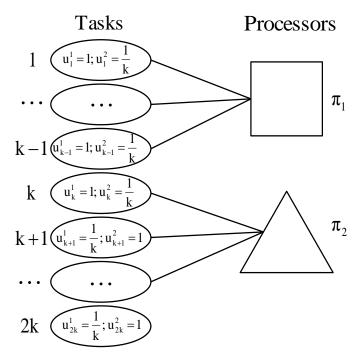

- Non-migrative scheduling. In non-migrative scheduling, each task is assigned to a single processor, on which each of its jobs will execute. In this model, each processor is scheduled independently. This scheduling technique is also referred to as *partitioned scheduling*.

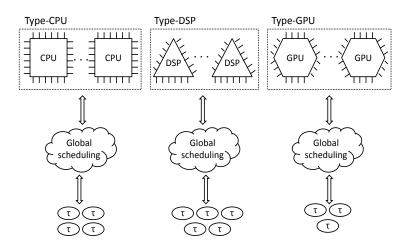

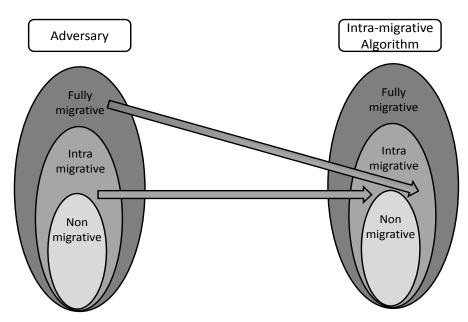

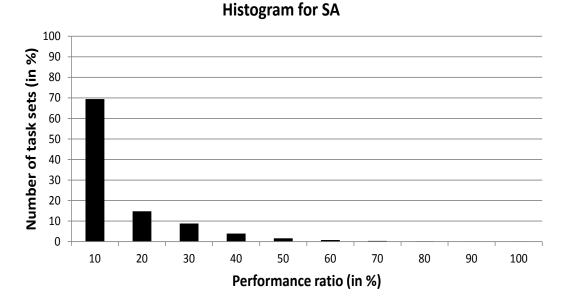

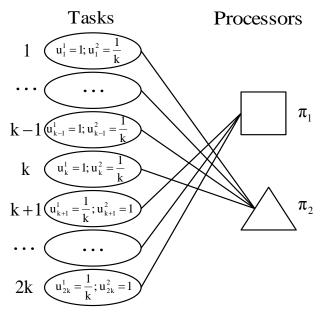

For heterogeneous multiprocessor systems, we define another category, namely "intra-migrative" scheduling, as follows.

**Definition 13 (Intra-migrative scheduling.).** In intra-migrative scheduling for heterogeneous multiprocessors, each task is statically assigned to a processor type and the jobs of that task will execute only on those processors that belong to the processor type to which the task is assigned. In other words, tasks/jobs assigned to a processor type can only migrate between processors of same type. Each processor type is scheduled independently.

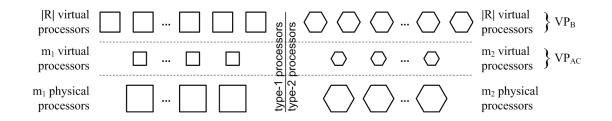

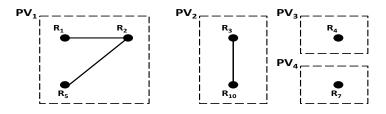

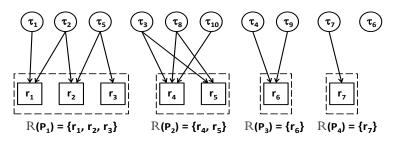

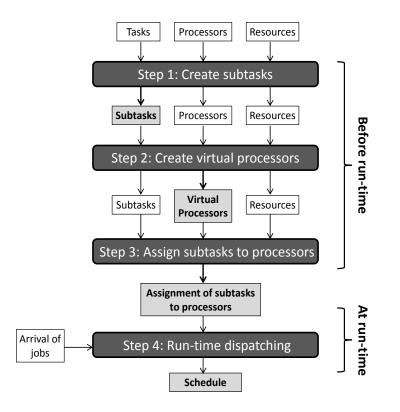

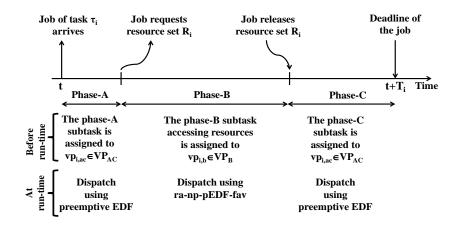

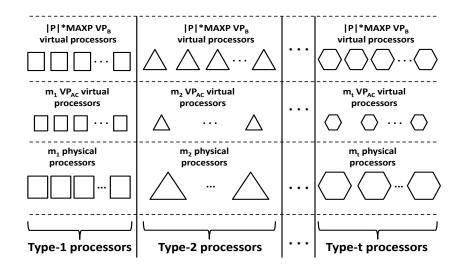

Figure 1.7 illustrates intra-migrative scheduling approach in heterogeneous multiprocessors.

This research focuses on both intra-migrative and non-migrative scheduling.

#### **1.5** Background on real-time scheduling theory

The real-time scheduling theory has its origin as early as 1960s during the Apollo space mission in US. It was during this time, the first couple of real-time scheduling algorithms were designed, analyzed and were used to schedule the real-time workload on the on-board computer in the first manned space mission to the moon [LL73, Liu69].

The paper by Liu and Layland [LL73] is regarded as the foundational and most influential work in real-time scheduling theory. The paper addressed the problem of scheduling implicit-deadline periodic tasks with hard deadlines on a uniprocessor system. The paper presented two historical algorithms — one on *task-static priority scheduling* and another on *job-static priority scheduling*. These scheduling algorithms were preemptive in nature and made a couple of assumptions about

(a) Fully-migrative scheduling — no static assignment of tasks to processors; tasks/jobs can migrate between processors.

(b) Non-migrative scheduling — static assignment of tasks to processors; no migration is allowed.

Figure 1.6: A visualization of different categories of scheduling approaches.

the workload and the computing platform; some of the assumptions were: (i) tasks should be implicit-deadline periodic, (ii) tasks should be independent and hence not share any resources (except the processor) and (iii) computing platform should have a single processor.

The task-static priority algorithm proposed in [LL73] is referred to as Rate Monotonic (RM) algorithm and it assigns the priority based on the periods of the tasks — the priority of a task is inversely proportional to its period. Specifically, the task with the shortest period is given the highest priority and the task with the longest period is given the lowest priority. For this algorithm, following properties were shown. First, for any task set  $\tau$  comprising *n* tasks, if it holds that the utilization of the task set  $U_{\tau} \leq n \times (2^{\frac{1}{n}} - 1)$  then upon scheduling such a task set with RM guarantees that all deadlines are met. Observe that as *n* approaches infinity, the value of  $n(2^{1/n} - 1)$  approaches  $\ln(2)$  which is approximately 69%. Second, it was shown that RM is an *optimal* task-static priority algorithm with the interpretation that, if a task set can be scheduled to

Figure 1.7: Intra-migrative scheduling on heterogeneous multiprocessors — static assignment of tasks to processor types; tasks/jobs can migrate between processors of same type.

meet all deadlines by any task-static priority algorithm then scheduling the same task set with RM will also guarantee that all deadlines are met.

The job-static priority algorithm proposed in [LL73] is referred to as Earliest-Deadline First (EDF) and it assigns the priority based on the deadlines of the tasks. The priorities assigned to tasks are inversely proportional to the deadlines of the ready-to-run jobs. For this algorithm, it was shown that, for any task set  $\tau$ , if it holds that the utilization of the task set  $U_{\tau} \leq 1$  then upon scheduling such a task set with EDF guarantees that all deadlines are met. Also, it has been shown that [LL73, Der74] EDF is an *optimal* job-static priority algorithm, in the sense that, if a task set can be scheduled to meet all deadlines by any job-static priority algorithm then scheduling the same task set with EDF will also guarantee that all deadlines are met.

Since then the real-time scheduling theory has evolved gradually by relaxing the assumptions made by Liu and Layland and imposing more constraints as per the requirements/demands of the new systems (e.g., embedded systems), applications (e.g., electronic software in cars, mobiles, etc) and architectures (e.g., multi-cores).

After that seminal paper, lot of research has been done on real-time scheduling on uniprocessor systems (e.g., [KAS93, BTW95, Leh90, SRL90, BMR90, BRH90, LW82, LSD89, SAA<sup>+</sup>04]). For example, the work in [KAS93, BTW95] provided a methodology for considering the preemption overhead into schedulability analysis that arises due to context switching, task queue manipulation and interrupt handling; the authors of [Leh90] provided an analysis technique for arbitrary-deadline tasks; the work in [SRL90] provided analysis techniques for systems where tasks can communicate/synchronize with each other and so on. Today, uniprocessor scheduling techniques are considered mature, taught in undergraduate courses worldwide and they are also adapted by the industry as well.

Although the multiprocessor real-time scheduling theory originated at the same time as that of uniprocessor (i.e., in the late 1960s and early 1970s), unfortunately, it did not experience similar

success. In 1969, Liu [Liu69] observed that: "Few of the results obtained for a single processor generalize directly to the multiple processor case; bringing in additional processors adds a new dimension to the scheduling problem. The simple fact that a task can use only one processor even when several processors are free at the same time adds a surprising amount of difficulty to the scheduling of multiple processors."

Dhall and Liu [Dha77], [DL78] observed that popular uniprocessor algorithms such as RM and EDF will not scale to multiprocessor when used as global scheduling algorithms and suffer from the so called "*Dhall effect*" leading to deadline misses even when the computational capacity requested by the workload from the underlying computing platform is nearly 0%. The following example illustrates this scenario.

| Example 5. | Consider a s | ystem with n | tasks and m | processors | (n > m) | ) as shown in | <i>Table</i> 1.1. |

|------------|--------------|--------------|-------------|------------|---------|---------------|-------------------|

|------------|--------------|--------------|-------------|------------|---------|---------------|-------------------|

| Tasks          | Ci | $T_i = D_i$ |

|----------------|----|-------------|

| $\tau_1$       | 2ε | 1           |

| $	au_2$        | 2ε | 1           |

| •••            |    | 1           |

| $	au_{n-1}$    | 2ε | 1           |

| $\tau_{\rm n}$ | 1  | 1+E         |

Table 1.1: An example to illustrate *Dhall effect* — deadlines can be missed on multiprocessors even though the computational capacity requested is nearly 0%.

If the task set is globally scheduled using either RM or EDF algorithms, the task  $\tau_n$  with period  $1 + \varepsilon$  will miss the deadline. (The exact number of processors is irrelevant here since task  $\tau_n$  will miss deadline as long as the number of processors m is less than the number of tasks m). Note that the total utilization of this task set is:  $U_{\tau} = (n-1) \times 2\varepsilon + \frac{1}{1+\varepsilon}$  and as  $\varepsilon \to 0$ ,  $U_{\tau} \to 1$ . Thus, even with a multiprocessor system, i.e., m > 1, a task set with a utilization just above 1 may not be schedulable to meet all deadlines.

Therefore, in those days, the research efforts were mostly focused on the partitioned approaches where tasks are assigned to individual processors and then a well-known uniprocessor scheduling algorithm is used on each processor to schedule the respective tasks. However, from 1997 onwards, when Phillips et. al. [PSTW97] showed that the "Dhall effect" was more to do with task sets having some tasks with high utilization than the nature of global scheduling algorithms itself, there was a renewed interest in global scheduling policies [RSS90, BCPV96, AJ03, ABJ01, GFB03, BCL05, BCL09] along with the continued interest in partitioned scheduling [OS95, LBOS95, LGDG03, LDG04, FBB06, BF07b]. See the surveys [CFH<sup>+</sup>04, DB11] for a more comprehensive list of contributions in multiprocessor scheduling.

Most of the multiprocessor scheduling theory has been developed for identical [FBB06, LDG04, BCL05, GFB03] and uniform multiprocessors [FB03, CG06, DJ06, HS86] and only a few results are available for heterogeneous multiprocessors [HS76, LST90, Bar04c, Bar04b, Bar04a, CSV12, WBB13]. This is unfortunate because many chip manufacturers offer heterogeneous multicores

these days [AMD13a, Int13b, Nvi12, App13, Qua13, Sam13a, ST 12, Tex13]. Hence, in this work, we focus on heterogeneous multiprocessor scheduling.

In a heterogeneous multiprocessor system, fully-migrative scheduling algorithms that allow tasks to migrate between processors of different types [Bar04a] are hard to realize (if not impossible as shown in [DVT12]) since processors with different functionalities (i.e., processors of different types) typically have different instructions sets, register formats, etc. Hence, the problem of assigning tasks to processors (to processor types, respectively) and then scheduling them with an uniprocessor scheduling algorithm (an identical multiprocessor scheduling algorithm, respectively) is of much greater practical significance. This however requires that the following two sub-problems be solved: (i) assigning tasks to processors (to processor types, respectively) and (ii) once tasks are assigned, performing uniprocessor scheduling on each processor (identical multiprocessor scheduling on each processor type, respectively). The latter problem is well-understood: it can be performed with an optimal uniprocessor scheduling algorithm such as EDF [LL73] for example (an optimal identical multiprocessor scheduling algorithm such as DP-Fair [LFS<sup>+</sup>10], respectively). But assigning tasks to processors is the difficult part (to avoid tedium, we will only speak about assigning tasks to processors in the rest of this paragraph). Several approaches for assigning real-time tasks to processors are available but for achieving provably good performance, only the following classes are known

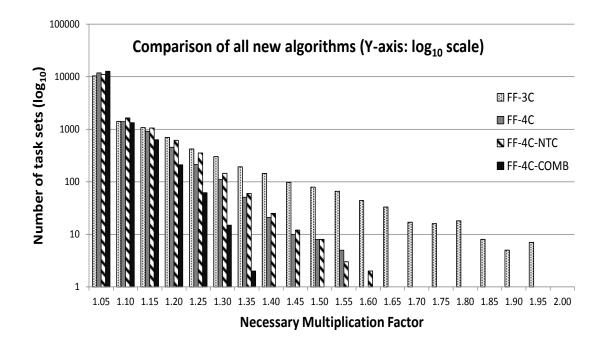

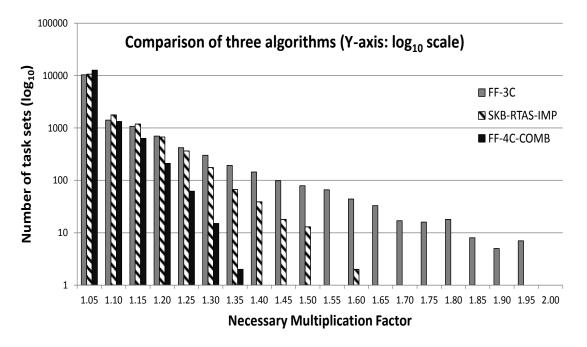

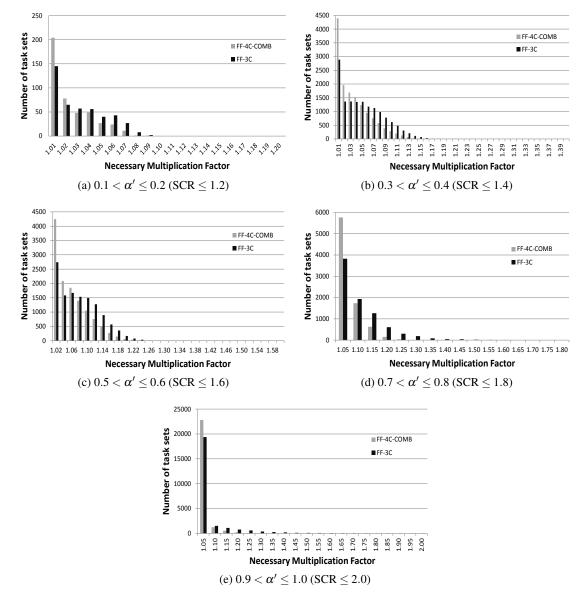

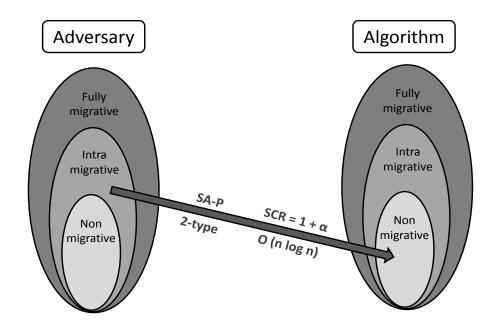

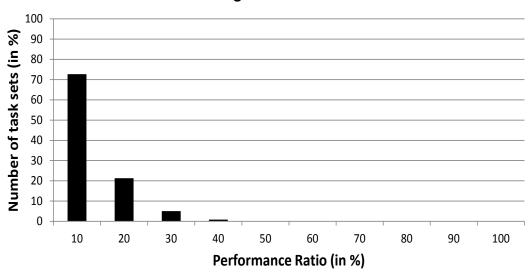

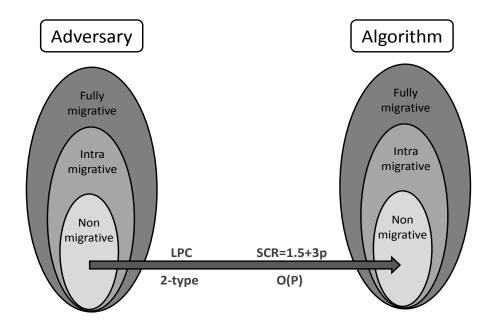

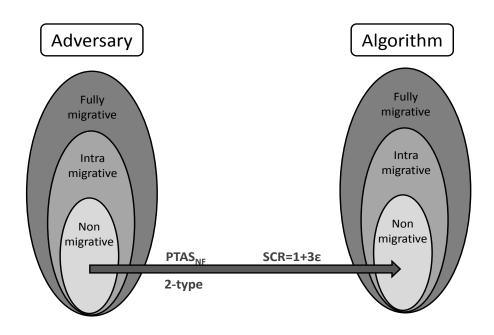

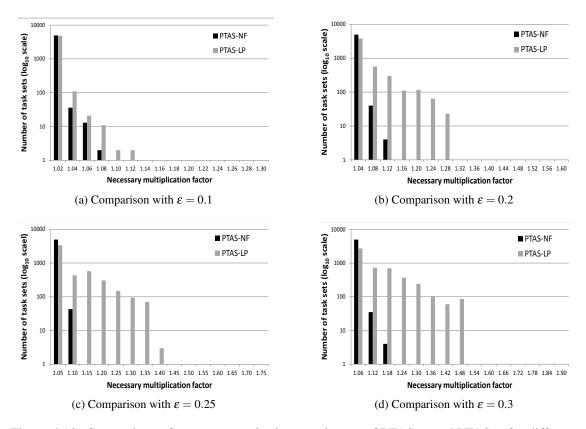

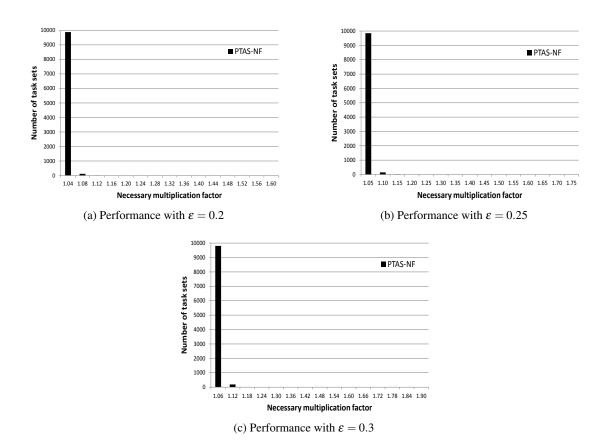

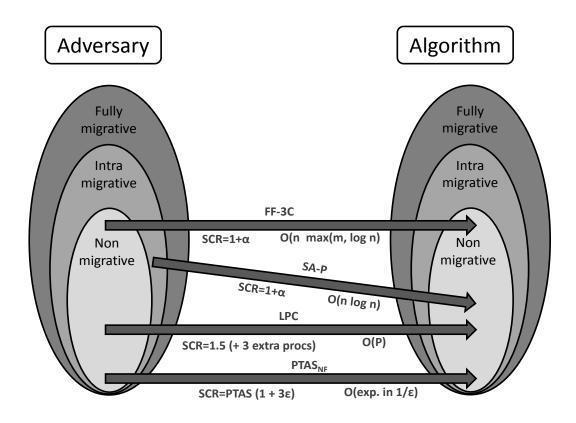

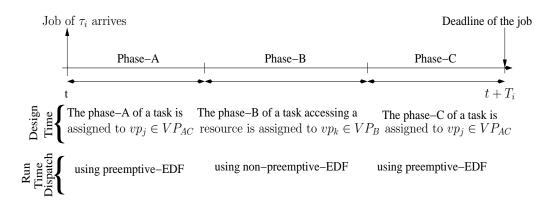

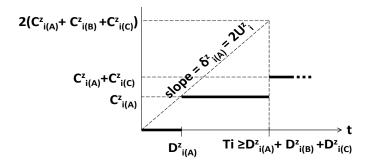

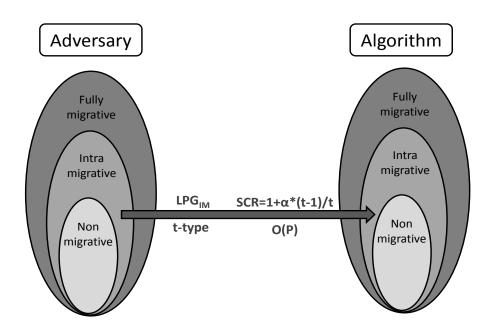

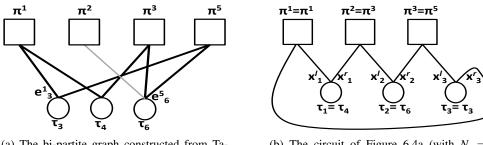

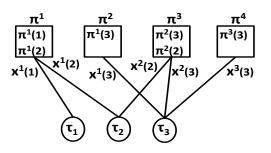

- **Bin-packing schemes:** Bin-packing schemes are popular for assigning tasks to processors but unfortunately the proof techniques used on identical multiprocessors do not easily translate to heterogeneous multiprocessors and consequently, no bin-packing schemes exist for assigning real-time tasks on heterogeneous multiprocessors. Hence, in this work, we propose task assignment techniques that based on bin-packing heuristics and show how to prove the performance of these algorithms for heterogeneous multiprocessor model.