FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Many-Core Platforms in the Real-Time Embedded Computing Domain

Borislav Nikolić

Doctoral Programme in Electrical and Computer Engineering

Supervisor: Dr. Stefan Markus Ernst Petters

April 24, 2015

© Borislav Nikolić, 2015

## Many-Core Platforms in the Real-Time Embedded Computing Domain

**Borislav Nikolić**

Doctoral Programme in Electrical and Computer Engineering

### **Approved by:**

President: Dr. José Silva Matos External Referee: Dr. Petru Eles External Referee: Dr. Leandro Soares Indrusiak Internal Referee: Dr. Luís Miguel Pinho FEUP Referee: Dr. Pedro Ferreira do Souto FEUP Referee: Dr. Mário Jorge Rodrigues de Sousa Supervisor: Dr. Stefan Markus Ernst Petters

April 24, 2015

## Abstract

Over the past few decades, the technological advancements made our lives increasingly permeated by and dependent on embedded systems. At the present day, these devices account for more than 98% of all produced computing systems, with applications that span over a wide range of areas, from medicine to avionics. Some embedded systems interact with the physical environment and have to guarantee not only that a certain action will be performed correctly, but also that the action will complete within a certain time. These devices are called *real-time embedded systems*, and some notable examples are medical pacemakers, airbags in cars and autopilots in airplanes.

The process of analysing the temporal behaviour of a real-time embedded system is called *real-time analysis*. In many cases, the purpose of the analysis is to derive guarantees that a device will perform its functions correctly, while at the same time meeting all timing requirements. A real-time analysis is mostly performed at design-time, thus its efficiency highly depends on the amount of predictability of the entire system, whereas any non-deterministic aspect of the system behaviour has to be accounted for in the analysis with a certain degree of pessimism. A pessimistic analysis may cause a significant resource over-provisioning in the design phase, and consequently lead to a severe underutilisation of available resources at runtime. Therefore, reducing the analysis pessimism is one of the ever-present objectives in the real-time embedded computing domain.

The first real-time embedded systems were predominantly single-core devices with limited sets of functionalities. However, constantly increasing demands for more advanced and sophisticated functionalities required more powerful computational devices. When faced with the same challenge, the other computing areas (e.g. general-purpose or high-performance computing) opted for platforms consisting of several cores – *multi-cores* and more than a dozen of cores – *many-cores*. It comes as no surprise that the same trends, although with an offset, are noticeable in the evolution of the real-time embedded systems, where many-core platforms present the new frontier technology.

Besides giving the options to implement more advanced functionalities, many-core platforms offer other beneficial possibilities as well. For instance, multiple functionalities, that were previously implemented on a set of single-core devices, can be integrated within fewer many-core platforms with significant design-cost reductions. Moreover, the abundance of available cores allows to implement efficient thermal and power management strategies by deliberately performing temporary shutdowns of idle cores. At the same time, the existence of idle cores, which can be used if necessary, makes these devices more resilient to hardware failures.

Yet, despite the aforementioned benefits, the integration of many-cores into the real-time embedded domain is a big challenge. The most notable reasons are (i) increasingly complex designs of hardware components, promoting performance, often at the expense of predictability, and (ii) more significant and hard-to-analyse contention patterns for accesses to shared resources. These facts may contribute to a non-deterministic system behaviour, while, as explained above, every non-deterministic aspect of the system behaviour has to be accounted for in the real-time analysis with a certain degree of pessimism. In this dissertation, the focus is on the analysis of real-time embedded systems deployed on many-core platforms. Specifically, a comprehensive collection of techniques and design choices is presented, with the common objective to make many-cores more amenable to the real-time analysis, and consequently more suitable and applicable to the real-time embedded domain. The proposed methods achieve this end in several ways: (i) by extending the state-of-the-art approaches in order to reduce the analysis pessimism, (ii) by exploiting novel hardware features, as well as enforcing constraints which cause a more deterministic and analysable system behaviour, and (iii) by elaborating on promising OS and workload paradigms, which have not been previously considered in the real-time embedded computing domain.

The contributions of this dissertation can be classified into two groups. In the first set of contributions the focus is on the interconnect medium, which is one of the most complex-to-analyse resources in many-core platforms. Initially, the target interconnect is the network-on-chip with a 2-D mesh topology, which utilises the wormhole switching mechanism and the XY routing technique. For such a generic model, which is present in the most of contemporary many-cores, a novel worst-case communication delay analysis is proposed, and subsequently compared with the state-of-the-art method. Then, assuming the additional hardware support in the form of virtual channels, improvements over the state-of-the-art approaches are proposed, which, not only reduce the analysis pessimism, but also significantly reduce the requirements for hardware resources. Finally, a novel arbitration policy for NoC routers is proposed.

In the second set of contributions the focus is on a novel paradigm in the real-time embedded domain, called the *Limited Migrative Model*. This model is inspired by the latest trends in the high-performance and general-purpose computing. First, the model is introduced and the cost of maintaining it is analytically estimated, both in terms of computational and interconnect resources, where, for the later aspect, the findings from the first set of contributions are used (see the previous paragraph). Then, three aspects of the application workload are studied, namely: (i) communication requirements, (ii) memory requirements, and (iii) computation requirements. The first aspect is addressed by imposing several constraints, which make the communication patterns more predictable, and subsequently allow to derive a communication delay analysis. Moreover, the workload assignment to computational resources is investigated, but only from the communication perspective, with the objective to spatially distribute the workload in such a way that all timing constraints posed on communication delays are met. Then, the focus is shifted towards the memory requirements, and a set of analysis techniques are proposed, which can be used to check whether the memory traffic requirements are also fulfilled. In the final part, the computation requirements of the application workload are studied. However, for this aspect only a coarse-grained analysis with several simplifying assumptions is presented. The proposed method represents an initial step towards the complete analysis related to the computation requirements. Subsequently, assuming this initial analysis, the problem of the workload assignment to computational resources is revisited, but this time with an orthogonal objective, which is to assure that the computational requirements of the workload are fulfilled.

The findings suggest that the first set of contributions significantly improves over the state-ofthe-art methods in the real-time analysis of interconnects. The improvements are manifested with the reduced analysis pessimism, as well as reduced hardware requirements. Both these aspects are essential for mitigating the resource over-provisioning effects when designing a new system. Additionally, the findings suggest that the Limited Migrative Model has a lot of potential, and represents a promising step towards the application of many-core platforms into the real-time embedded computing domain.

## Resumo

Ao longo da últimas décadas, os avanços tecnológicos tornaram a vida das pessoas cada vez mais dependentes de sistemas embebidos. Actualmente, estes dispositivos representam mais de 98% de todos os sistemas computacionais produzidos e são usados numa grande variedade de áreas, desde a medicina até à aviação. Alguns destes sistemas embebidos interagem com o meio envolvente e têm que garantir não só que determinada acção é executada correctamente, mas também que essa acção é terminada dentro de um certo limite temporal. Este tipo de dispositivos são designados de sistemas embebidos de tempo real e alguns exemplos são os "pacemakers" usados na saúde, "airbags" nos automóveis e os pilotos automáticos nos aviões.

O processo de analisar o comportamento temporal de um sistema de embebido de tempo real é designado de análise de tempo real. Em muitos casos, o propósito da análise é garantir que o dispositivo vai executar correctamente e que as restrições temporais vão ser respeitadas. A análise de tempo real é essencialmente efectuada antes de execução, isto é, na fase de projecto. Deste modo, a sua eficiência depende muito do determinismo do sistema, uma vez que qualquer não determinismo resultará na introdução de pessimismo na análise. Uma análise pessimista pode causar um excessivo uso de recursos na fase de projecto, o que, geralmente, tem como consequência uma baixa utilização desses recursos em tempo de execução. Portanto, reduzir o pessimismo na análise é um dos objectivos prementes nesta área dos sistemas embebidos de tempo real.

Os primeiros sistemas embebidos de tempo real eram maioritariamente dispositivos com uma única unidade de execução (designados de "single-core") com um conjunto limitado de funcionalidades. Porém, a crescente necessidade de suportar funcionalidades cada vez mais avançadas e mais sofisticadas viria a exigir dispositivos com maior capacidade computacional. Noutras áreas da computação (como por exemplo, computação de alto desempenho e mesmo na computação usada sem nenhuma especificidade, isto é, de uso geral) este requisito de maior poder computacional foi abordado com recurso a sistemas compostos por várias unidades de execução (designados por "many-cores"). Consequentemente, e sem qualquer surpresa, a mesma estratégia tem vindo a ser seguida no domínio dos sistemas embebidos de tempo real, onde as plataformas "many-core" constituem o mais recente desafio tecnológico.

Além da possibilidade de implementar funcionalidades mais avançadas, as plataformas "manycore" oferecem outras possibilidades. Por exemplo, muitas funcionalidades que eram implementadas num conjunto de sistemas "single-core", podem ser integradas num conjunto mais reduzido de plataformas "many-core" com uma redução significativa dos custos de projecto. Para além disso, a abundância de unidades de execução permite implementar estratégias eficientes de gestão energética e térmica, desligando ou "adormecendo", temporariamente, as unidades de execução que não tenham nenhuma tarefa para executar. Ao mesmo tempo, a existência de unidades de execução "adormecidas", que podem ser "acordadas" sempre que necessário, torna estes dispositivos mais resilientes a falhas de hardware.

Contudo, apesar dos benefícios referidos anteriormente, a integração das plataformas "manycore" nos sistemas embebidos de tempo real apresenta-se como um grande desafio. As razões para tal são (i) a cada vez maior complexidade dos componentes de hardware, que permite aumentar o desempenho, contudo, muitas vezes diminuindo a previsibilidade dos sistemas, e (ii) a crescente dificuldade na análise da contenção no acesso à utilização dos recursos partilhados. Estes factos podem contribuir para um comportamento menos determinista dos sistemas, o que, como referido anteriormente, implica adopção de níveis de pessimismo na analise.

O enfoque desta dissertação é a analise de sistemas embebidos de tempo real para plataformas "many-core". Especificamente, uma compreensiva colecção de técnicas e opções de projecto é apresentada, com o objectivo comum de tornar as plataformas "many-core" mais acessíveis (ou menos complexas) à analise de tempo real e consequentemente, mais apropriadas e aplicadas na área dos sistemas embebidos de tempo real. Os métodos propostos alcançam este objectivo de vários formas: (i) estendendo as abordagens existentes por forma a reduzir o pessimismo na analise, (ii) explorando novas características (ou elementos) de hardware e aplicando restrições que aumentem o determinismo e a analisabilidade dos sistemas e, por fim (iii) explorando novos paradigmas e funcionalidades presentes em alguns Sistemas Operativos e estratégias inovadoras ainda não consideradas no domínio dos sistemas computacionais de tempo real.

As contribuições apresentadas nesta dissertação podem ser classificadas em dois grupos. O primeiro grupo de contribuições está relacionada com o meio de interconexão, que é o mais complexo de analisar nas plataformas "many-core". Inicialmente, o meio de interconexão considerado foi o "Network-on-Chip" (NoC) com uma topologia em malha 2-D, que utiliza o mecanismo de comutação "wormhole" e a técnica de encaminhamento XY. Nesta dissertação é proposta uma nova análise para determinar o pior atraso nas comunicações para este modelo tão presente na maior parte das plataformas "many-cores" de hoje. Depois, assumindo suporte adicional de hardware na forma de canais virtuais, foram propostos melhoramentos às analises existentes, que além de reduzirem o pessimismo, também reduzem significamente os requisitos de recursos de hardware. Finalmente, foi também proposta uma nova política de arbítrio para os encaminhadores NoC.

O segundo grupo de contribuições está relacionado com um novo paradigma no domínio dos sistemas embebidos de tempo real designado de "Limited Migrative Model". Este modelo é inspirado na tendência actual dos sistema computacionais de alto desempenho e de utilização geral. Em primeiro lugar, o modelo é descrito e o custo da sua manutenção é estimado analiticamente, quer em termos de recursos computacionais quer em termos de recursos de interconexão, sendo para este caso, utilizadas as primeiras contribuições apresentadas no último parágrafo. Depois, são estudados três requisitos relacionados com cada tarefa, nomeadamente requisitos de: (i) comunicações, (ii) memória e (iii) computacionais. Em relação ao primeiro requisito, é imposto um conjunto de restrições, que tornam os padrões de comunicação mais determinísticos e consequentemente permitem a derivação analítica do atraso das comunicações. Para além disso, e de forma a garatir que os requisitos temporais impostos às comunicações são cumpridos, a carga atribuída aos diversos recursos computacionais é tratada apenas da perspectiva das comunicações. Em seguida, o enfoque é alterado para a memória, e é proposto um conjunto de métodos de análise tendo como objectivo verificar se os requisitos são também aqui cumpridos. Por fim, são estudados os requisitos computacionais para uma determinada carga. Contudo, em relação a este último aspecto, a análise apresentada é bastante simplificada uma vez que se trata de uma primeira abordagem para uma análise mais completa. Assim, o problema a alocação de carga computacional é revisitado, desta vez com o objectivo ortogonal de garantir que também os requisitos computacionais são cumpridos.

Os resultados mostram que o primeiro grupo de contribuições melhora substancialmente o estado da arte na análise de tempo real de interconexões. Estas melhorias estão sobretudo patentes na redução do pessimismo da análise e também na diminuição dos requisitos de hardware. Estes dois aspectos revelam-se essenciais para mitigar os efeitos do sobre-provisionamento aquando do

projecto de um novo sistema. Para além disso, os resultados sugerem que o "Limited Migrative Model" possui bastante potencial e este apresenta-se como bastante promissor para a suportar a aplicação de plataformas "many-core" no domínio dos sistemas embebidos e de tempo real.

vi

# Acknowledgements

Working towards the Ph.D. Degree was the most demanding and challenging activity in my life. It took me four hard working years to finish all the cool things described in this dissertation. During that period, I was never alone, and I would like to express my most sincere gratitude to the people that made me feel this way:

- Stefan M. Petters my Supervisor, for everything he has done for me, from the day when he selected me to be his Ph.D. student, until the day he finished the review of the last page of this dissertation. Stefan, thank you for always believing in me, for pushing me when I needed to be pushed, and for teaching me many valuable things, not only about research, but also about life.

- **Dobrica** and **Ivan Nikolić** my parents, and **Özge Güngör** my girlfriend, for giving me strength, courage and motivation to persist on this long journey, especially during the most challenging period, when I was writing this dissertation. Mum, dad, Özge, you are the best support that I could ever have, and with you by my side nothing is impossible.

- Leandro Soares Indrusiak, for giving me the opportunity to spend three months under his supervision, with the Real-Time Systems Group of the University of York, and for always being available and enthusiastic to discuss new ideas. Leandro, like we said several times already: *"This is just the beginning!"*. I truly believe that.

- Hazem Ismail Ali, for being an excellent friend and colleague, and for always having words of encouragement, a priceless advice and a pack of Dutch waffles up his sleeve. Mr. President, from the bottom of my heart I wish you to reach this stage very soon, *mabrouk we 32bel 3endak*.

- **Patrick Meumeu Yomsi**, for joining my crew during the second half of my Ph.D. trip, and for becoming an invaluable part of it ever since. Patrick, you know which are my favourite publications. As I always say during CISTER Seminars: "*Mömö, you are the man!*".

- Muhammad Ali Awan, Dakshina Dasari and Konstantinos Bletsas, for very productive collaborations, as well as very interesting and enjoyable discussions, especially those not related to the work. "*Guys, I want to tell you a story*...".

- **Paulo Baltarejo Sousa** and **Ricardo Severino**, for translating the abstract into Portuguese. Paulo, Ricardo, muito obrigado pela vossa ajuda e força F.C. Porto!

- Eduardo Tovar, for creating an outstanding work environment in CISTER Research Center.

This work was partially supported by FCT (Fundação para a Ciência e a Tecnologia) under the individual doctoral grant SFRH/BD/81087/2011.

viii

# **List of Publications**

The following publications and technical reports have been developed in the scope of the research activities presented in this dissertation.

### Journals (in chronological order)

- [27] Dakshina Dasari, Borislav Nikolić, Vincent Nélis and Stefan M. Petters, "NoC Contention Analysis using a Branch and Prune Algorithm", *ACM Transactions on Embedded Computing Systems (TECS) - Special Issue on Design Challenges for Many-Core Processors*, Volume 13, Issue 3s, Article number 113, March 2014.

- [70] Borislav Nikolić and Stefan M. Petters, "Real-Time Application Mapping for Many-Cores Using a Limited Migrative Model", *Real-Time Systems*, To appear.

### **Conferences (in chronological order)**

- [73] Borislav Nikolić, Muhammad Ali Awan and Stefan M. Petters, "SPARTS: Simulator for Power Aware and Real-Time Systems", *In Proceedings of the 8th IEEE International Conference on Embedded Software and Systems (IEEE ICESS-11)*, pages 999-1004, Changsha, China, November 16-18, 2011.

- [68] Borislav Nikolić and Stefan M. Petters, "Towards Network-On-Chip Agreement Protocols", *In Proceedings of the 10th ACM International Conference on Embedded Software* (*EMSOFT 2012*), pages 207-216, Tampere, Finland, October 7-12, 2012.

- [75] Borislav Nikolić, Patrick Meumeu Yomsi and Stefan M. Petters, "Worst-Case Memory Traffic Analysis for Many-Cores using a Limited Migrative Model", *In Proceedings of the* 19th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA 2013), pages 42-51, Taipei, Taiwan, August 19-21, 2013.

- [74] Borislav Nikolić, Hazem Ismail Ali, Stefan M. Petters and Luís Miguel Pinho, "Are Virtual Channels the Bottleneck of Priority-Aware Wormhole-Switched NoC-Based Many-Cores?", *In Proceedings of the 21st International Conference on Real-Time Networks and Systems (RTNS 2013)*, pages 13-22, Sophia Antipolis, France, October 16-18, 2013.

- [76] Borislav Nikolić, Patrick Meumeu Yomsi and Stefan M. Petters, "Worst-Case Communication Delay Analysis for Many-Cores using a Limited Migrative Model", *In Proceedings* of the 20th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA 2014), pages 1-10, Chongqing, China, August 20-22, 2014.

Short-listed for the best paper award and invited for the journal extension.

[69] Borislav Nikolić and Stefan M. Petters, "EDF as an Arbitration Policy for Wormhole-Switched Priority-Preemptive NoCs – Myth or Fact?", *In Proceedings of the 12th ACM International Conference on Embedded Software (EMSOFT 2014)*, pages 1-10, New Delhi, India, October 12-17, 2014.

### **Technical Reports**

- [71] Borislav Nikolić, Konstantinos Bletsas and Stefan M. Petters, "Priority Assignment and Application Mapping for Many-Cores Using a Limited Migrative Model", 2013.

- [72] Borislav Nikolić, Leandro Soares Indrusiak and Stefan M. Petters, "A Tighter Real-Time Communication Analysis for Wormhole-Switched Priority-Preemptive NoCs", 2014.

"The dawn cannot come before the morning."

Nebojša Čović

"If you do not believe in miracles, then miracles will not happen to you."

Dejan Radonjić

xii

# Contents

| Al | bstrac  | et        |                                                                                                                                              | i   |

|----|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A  | cknow   | ledgem    | ients                                                                                                                                        | vii |

| Li | st of I | Publicat  | tions                                                                                                                                        | ix  |

| 1  | Intr    | oductio   | n                                                                                                                                            | 1   |

|    | 1.1     | Real-T    | Time Embedded Systems                                                                                                                        | 1   |

|    | 1.2     | Real-T    | ime Analysis                                                                                                                                 | 2   |

|    | 1.3     | Single    | -Core $\Rightarrow$ Multi-Core $\Rightarrow$ Many-Core $\ldots \ldots \ldots$ | 3   |

|    | 1.4     | Benefi    | ts of Many-Cores                                                                                                                             | 4   |

|    | 1.5     | Many-     | Cores in Real-Time Embedded Computing Domain                                                                                                 | 4   |

|    |         | 1.5.1     | Computation Process                                                                                                                          | 4   |

|    |         | 1.5.2     | Interconnect medium                                                                                                                          | 9   |

|    |         | 1.5.3     | Data Input and Output                                                                                                                        | 27  |

|    |         | 1.5.4     | Recapitulation                                                                                                                               | 32  |

|    | 1.6     | Thesis    | Statement                                                                                                                                    | 34  |

| 2  | Seve    | eral Step | ps Closer to Real-Time NoCs                                                                                                                  | 35  |

|    | 2.1     | Traffic   | Model                                                                                                                                        | 35  |

|    | 2.2     | NoCs      | with the Round-Robin Arbitration Policy                                                                                                      | 36  |

|    |         | 2.2.1     | State-of-the-Art Method                                                                                                                      | 36  |

|    |         | 2.2.2     | Analysis Pessimism                                                                                                                           | 40  |

|    |         | 2.2.3     | Branch and Prune (BP) Method                                                                                                                 | 43  |

|    |         | 2.2.4     | Branch, Prune and Collapse (BPC) - More Efficient Method                                                                                     | 48  |

|    |         | 2.2.5     | Experimental Evaluation                                                                                                                      | 52  |

|    |         | 2.2.6     | Discussion                                                                                                                                   | 59  |

|    | 2.3     | NoCs      | with Priority-Preemptive Arbitration Policies                                                                                                | 59  |

|    |         | 2.3.1     | State-of-the-Art Method for NoCs with Fixed-Priority Arbitration Policy                                                                      | 61  |

|    |         | 2.3.2     | Priority-Share Policy                                                                                                                        | 63  |

|    |         | 2.3.3     | Relaxing Hardware Requirements                                                                                                               | 65  |

|    |         | 2.3.4     | EDF as Arbitration Policy                                                                                                                    | 78  |

|    |         | 2.3.5     | Reducing Analysis Pessimism                                                                                                                  | 93  |

| 3  | Lim     | ited Mi   | grative Model - LMM                                                                                                                          | 107 |

|    | 3.1     | LMM       | in Detail                                                                                                                                    | 107 |

|    |         | 3.1.1     | Operating System (OS)                                                                                                                        | 107 |

|    |         | 3.1.2     | Application Layer                                                                                                                            | 108 |

|    |         | 3.1.3     | LMM Benefits                                                                                                                                 | 109 |

|    | 3.2    | Applica  | ation Workload                                        | 110           |  |  |  |  |

|----|--------|----------|-------------------------------------------------------|---------------|--|--|--|--|

|    | 3.3    | Agreen   | nent Protocols                                        | 111           |  |  |  |  |

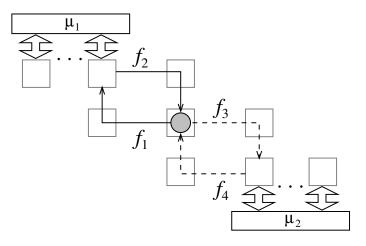

|    |        | 3.3.1    | Master-Slave Protocol                                 | 112           |  |  |  |  |

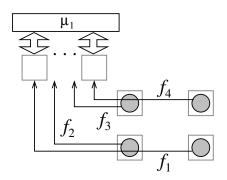

|    |        | 3.3.2    | List Protocol                                         | 120           |  |  |  |  |

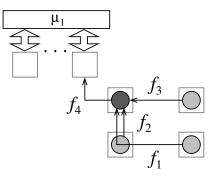

|    |        | 3.3.3    | Hybrid Protocol                                       | 125           |  |  |  |  |

|    |        | 3.3.4    | Experimental Evaluation                               | 132           |  |  |  |  |

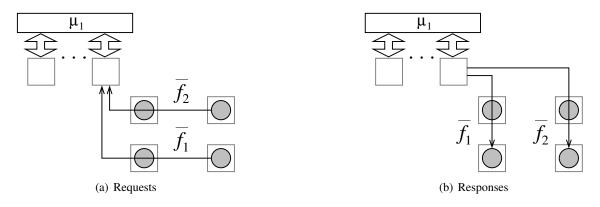

|    | 3.4    | Inter-ap | oplication Communication                              | 136           |  |  |  |  |

|    | 3.5    | Toward   | Is More Deterministic Communication Patterns          | 139           |  |  |  |  |

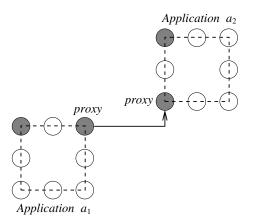

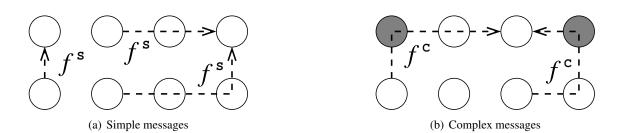

|    |        | 3.5.1    | Supermessages and Proxies                             | 140           |  |  |  |  |

|    |        | 3.5.2    | Maximum Number of Message Occurrences                 | 142           |  |  |  |  |

|    |        | 3.5.3    | Performing the Analysis                               | 148           |  |  |  |  |

|    |        | 3.5.4    | Discussion                                            | 150           |  |  |  |  |

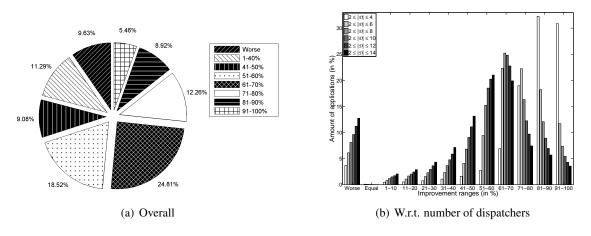

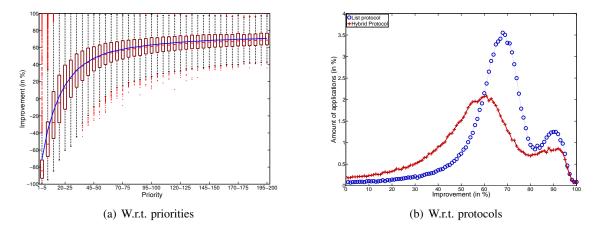

|    |        | 3.5.5    | Experimental Evaluation                               | 151           |  |  |  |  |

|    | 3.6    | Applica  | ation Mapping                                         | 159           |  |  |  |  |

|    |        | 3.6.1    | Problem Statement                                     | 160           |  |  |  |  |

|    |        | 3.6.2    | Mapping Quality                                       | 160           |  |  |  |  |

|    |        | 3.6.3    | Mapping Process                                       | 163           |  |  |  |  |

|    |        | 3.6.4    | Experimental Evaluation                               | 170           |  |  |  |  |

|    |        | 3.6.5    | Discussion                                            | 178           |  |  |  |  |

|    | 3.7    | Memor    | y Traffic                                             | 179           |  |  |  |  |

|    |        | 3.7.1    | Workload                                              | 179           |  |  |  |  |

|    |        | 3.7.2    | Challenges and Inapplicability of Existing Techniques | 179           |  |  |  |  |

|    |        | 3.7.3    | Access Constraints and Bounding Messages              | 180           |  |  |  |  |

|    |        | 3.7.4    | Solution to Mutually Exclusive Bounding Messages      | 182           |  |  |  |  |

|    |        | 3.7.5    | Approach One: Per-Packet Analysis                     | 182           |  |  |  |  |

|    |        | 3.7.6    | Intermediate Step: Partial Per-Pattern Analysis       | 183           |  |  |  |  |

|    |        | 3.7.7    | Approach Two: Full per-pattern analysis               | 184           |  |  |  |  |

|    |        | 3.7.8    | Experimental Evaluation                               | 185           |  |  |  |  |

|    | 3.8    |          |                                                       | 189           |  |  |  |  |

|    | 010    | 3.8.1    | Core Shutdowns                                        | 189           |  |  |  |  |

|    |        | 3.8.2    | Workload                                              |               |  |  |  |  |

|    |        | 3.8.3    | Problem Statement                                     | 191           |  |  |  |  |

|    |        | 3.8.4    | Offline Schedulability Guarantees                     | 191           |  |  |  |  |

|    |        | 3.8.5    | Online Schedulability                                 | 192           |  |  |  |  |

|    |        | 3.8.6    | Semi-Schedulability Guarantees                        | 193           |  |  |  |  |

|    |        | 3.8.7    | Blind Synchronisation                                 | 197           |  |  |  |  |

|    |        | 3.8.8    | Parent-Child Relationship                             | 198           |  |  |  |  |

|    |        | 3.8.9    | Schedulability and Agreement Protocols                | 198           |  |  |  |  |

|    |        |          | Priority Assignment and Mapping                       | 199           |  |  |  |  |

|    |        | 3.8.11   | Experimental Evaluation                               | 201           |  |  |  |  |

|    |        |          | Discussion                                            | 201           |  |  |  |  |

| 4  | C      |          |                                                       |               |  |  |  |  |

| 4  |        |          | and Future Work                                       | 209           |  |  |  |  |

| Aj | opend  | ix       |                                                       | 211           |  |  |  |  |

| Re | eferen | ces      |                                                       | eferences 215 |  |  |  |  |

# **List of Figures**

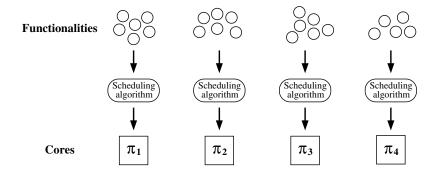

| 1.1        | Fully partitioned scheduling                                                         | 5        |

|------------|--------------------------------------------------------------------------------------|----------|

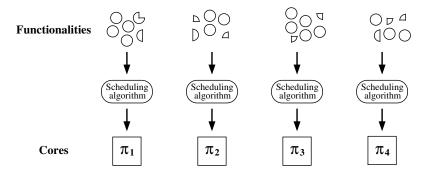

| 1.2        | Semi-partitioned scheduling                                                          | 6        |

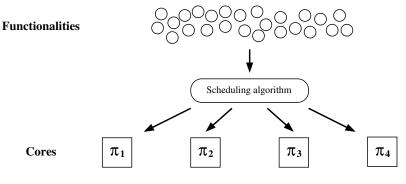

| 1.3        | Global scheduling                                                                    | 7        |

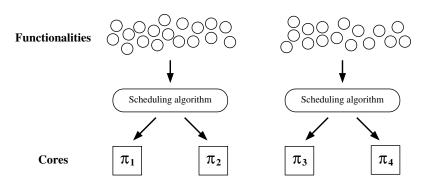

| 1.4        | Clustered scheduling                                                                 | 8        |

| 1.5        | Point-to-point communication                                                         | 9        |

| 1.6        |                                                                                      | 10       |

| 1.7        |                                                                                      | 11       |

| 1.8        |                                                                                      | 12       |

| 1.9        |                                                                                      | 13       |

| 1.10       |                                                                                      | 14       |

| 1.11       |                                                                                      | 14       |

| 1.12       | Wormhole switching                                                                   | 15       |

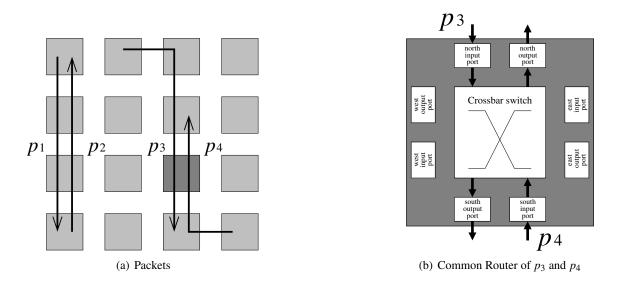

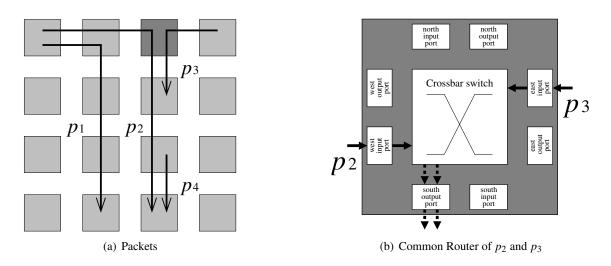

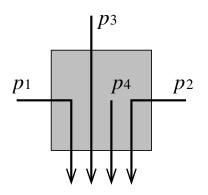

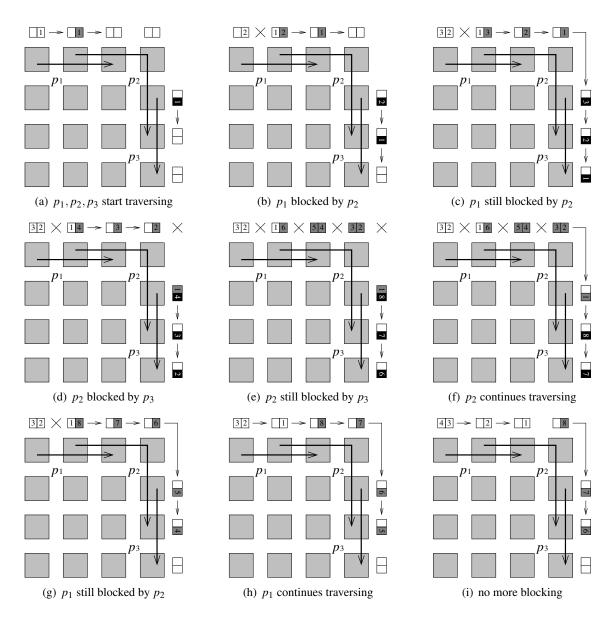

|            |                                                                                      | 16       |

| 1.14       | Packet traversals without contentions                                                | 17       |

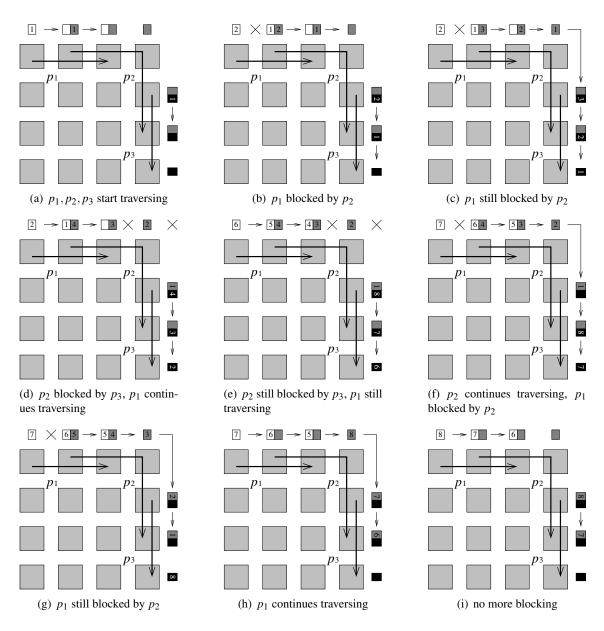

| 1.15       | Packet traversals with contentions                                                   | 18       |

| 1.16       | Contending packets                                                                   | 18       |

|            |                                                                                      | 20       |

| 1.18       | Indirect interference with virtual channels                                          | 22       |

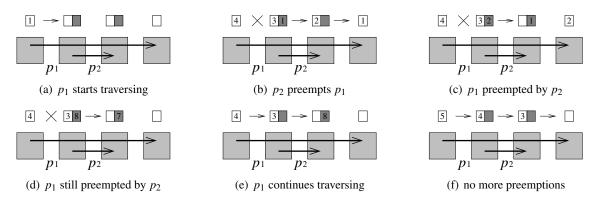

| 1.19       | Packet preemptions                                                                   | 23       |

|            |                                                                                      | 26       |

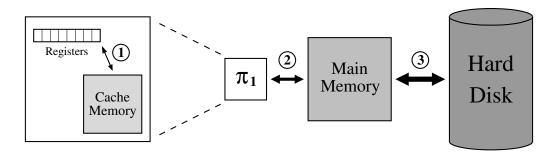

|            |                                                                                      | 28       |

|            |                                                                                      | 29       |

|            |                                                                                      | 32       |

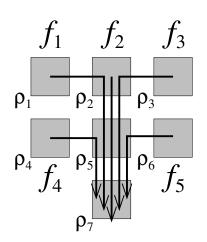

| 2.1        | Traffic flows (example 1)                                                            | 36       |

| 2.1        |                                                                                      | 37       |

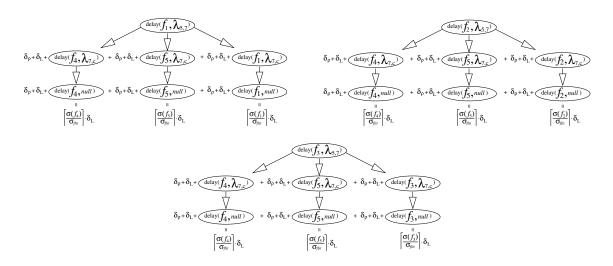

| 2.2        | Computation tree for flow $f_2$ from Figure 2.2, in isolation (Ferrandiz et al. [32] | 51       |

| 2.3        |                                                                                      | 39       |

| 2.4        |                                                                                      | 39<br>40 |

| 2.4<br>2.5 |                                                                                      | 40<br>40 |

|            |                                                                                      | 40<br>41 |

| 2.6        | 1 J I                                                                                | 41<br>42 |

| 2.7        | 1 1                                                                                  |          |

| 2.8        | $J_{2} = J_{2} = J_{2}$                                                              | 44       |

| 2.9        |                                                                                      | 44<br>50 |

| 2.10       |                                                                                      | 50       |

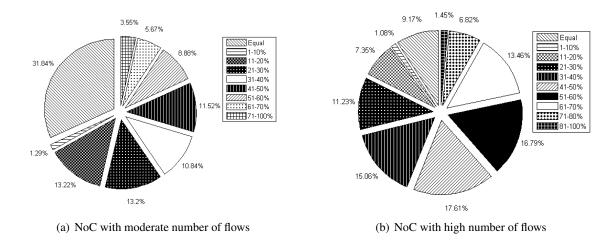

| 2.11       |                                                                                      | 54       |

|            |                                                                                      | 55       |

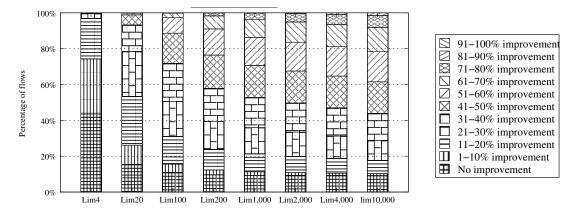

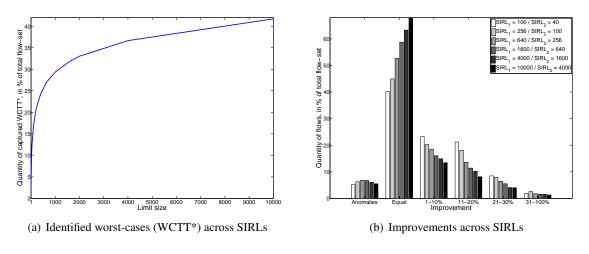

| 2.13       | Inter-SIRL ratios                                                                    | 56       |

| 2.14                                                                                                                                                                   | All-to-one contending flows                                                                                                                                                                                                          |                                                                                                                                            |                        | 57                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------|

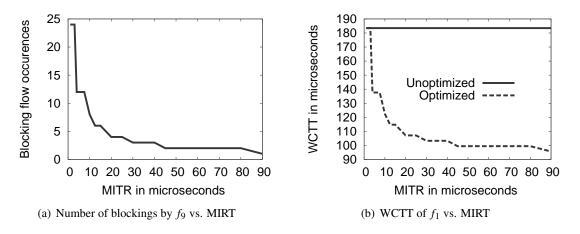

| 2.15                                                                                                                                                                   | Impact of MIRT on flow $f_1$                                                                                                                                                                                                         |                                                                                                                                            |                        | 58                                                                                                                         |

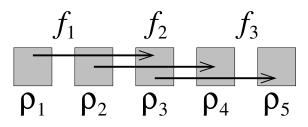

| 2.16                                                                                                                                                                   | Traffic flows (example 3)                                                                                                                                                                                                            |                                                                                                                                            |                        | 61                                                                                                                         |

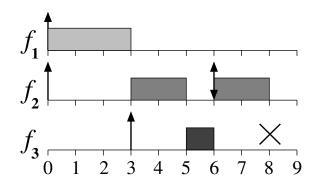

| 2.17                                                                                                                                                                   | Deadline miss for flow-set from Figure 2.16 and Table 2.2                                                                                                                                                                            |                                                                                                                                            |                        | 62                                                                                                                         |

| 2.18                                                                                                                                                                   | Assignment of virtual channels to flow-set with distinctive priorities                                                                                                                                                               |                                                                                                                                            |                        | 66                                                                                                                         |

|                                                                                                                                                                        | Assignment of virtual channels to flow-set with priority-share policy                                                                                                                                                                |                                                                                                                                            |                        | 66                                                                                                                         |

|                                                                                                                                                                        | Per-router assignment of virtual channels to flow-set with distinctive prioritie                                                                                                                                                     |                                                                                                                                            |                        | 66                                                                                                                         |

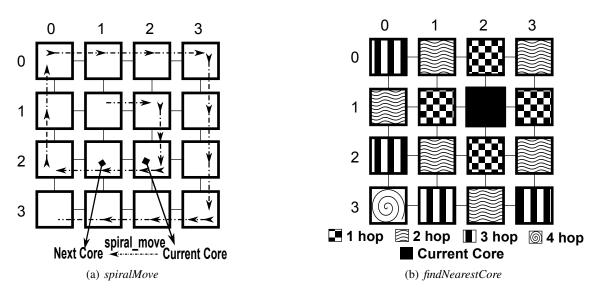

|                                                                                                                                                                        | Core selection methodology proposed by Ali et al. [4]                                                                                                                                                                                |                                                                                                                                            |                        | 70                                                                                                                         |

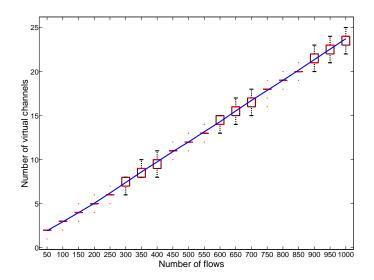

|                                                                                                                                                                        | Virtual channels do scale with respect to number of flows                                                                                                                                                                            |                                                                                                                                            |                        | 75                                                                                                                         |

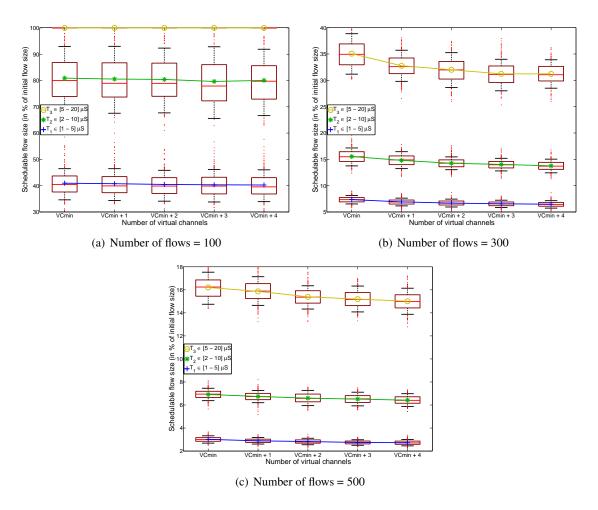

|                                                                                                                                                                        | Additional virtual channels do <b>not</b> help in schedulability guarantees                                                                                                                                                          |                                                                                                                                            |                        | 76                                                                                                                         |

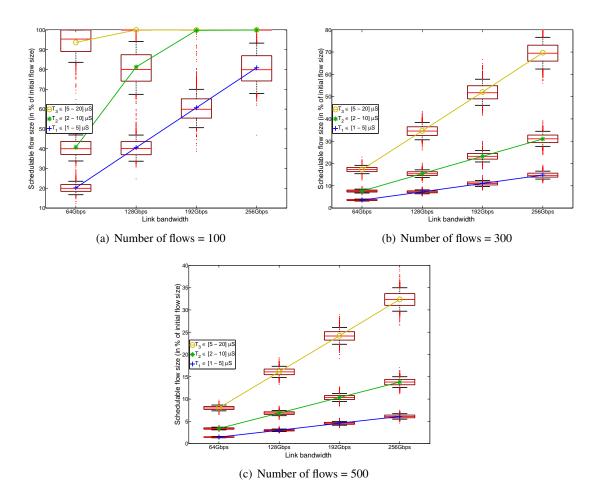

|                                                                                                                                                                        | Link bandwidths are bottlenecks                                                                                                                                                                                                      |                                                                                                                                            |                        | 77                                                                                                                         |

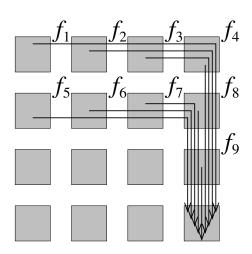

|                                                                                                                                                                        | Traffic flows (example 4)                                                                                                                                                                                                            |                                                                                                                                            |                        | 80                                                                                                                         |

|                                                                                                                                                                        | Deadline miss for flow-set from Figure 2.25 and Table 2.5                                                                                                                                                                            |                                                                                                                                            |                        | 81                                                                                                                         |

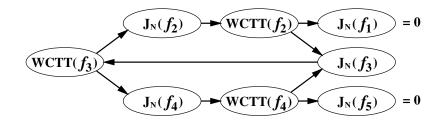

|                                                                                                                                                                        | Chain of dependencies for Figure 2.25                                                                                                                                                                                                |                                                                                                                                            |                        | 83                                                                                                                         |

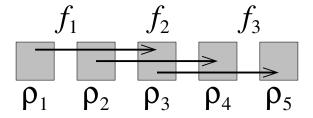

|                                                                                                                                                                        | Traffic flows (example 5)                                                                                                                                                                                                            |                                                                                                                                            |                        | 86                                                                                                                         |

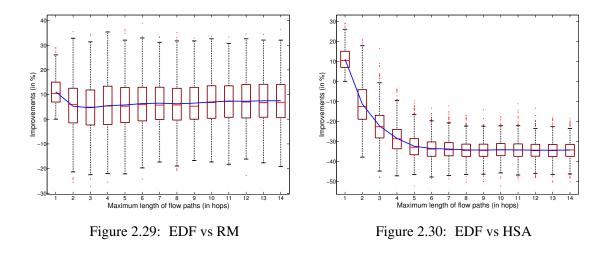

|                                                                                                                                                                        | EDF vs RM                                                                                                                                                                                                                            |                                                                                                                                            |                        | 90                                                                                                                         |

|                                                                                                                                                                        | EDF vs HSA                                                                                                                                                                                                                           |                                                                                                                                            |                        | 90                                                                                                                         |

|                                                                                                                                                                        | EDF vs RM,HSA (1-hop)                                                                                                                                                                                                                |                                                                                                                                            |                        | 91                                                                                                                         |

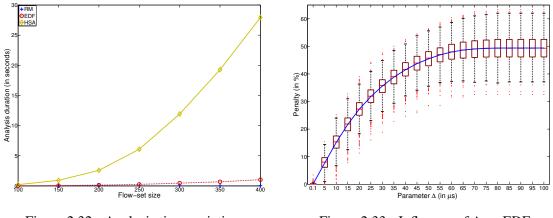

|                                                                                                                                                                        | Analysis time variations                                                                                                                                                                                                             |                                                                                                                                            |                        | 92                                                                                                                         |

|                                                                                                                                                                        | Influence of $\Delta$ on EDF                                                                                                                                                                                                         |                                                                                                                                            |                        | 92                                                                                                                         |

|                                                                                                                                                                        | Traffic flows (example 6)                                                                                                                                                                                                            |                                                                                                                                            |                        | 94                                                                                                                         |

|                                                                                                                                                                        | Detailed interference analysis                                                                                                                                                                                                       |                                                                                                                                            |                        | 95                                                                                                                         |

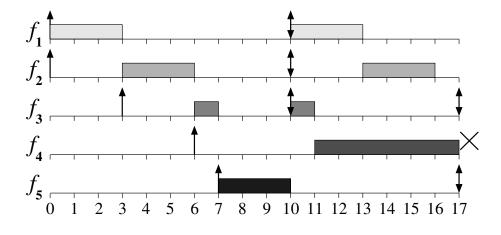

|                                                                                                                                                                        | Traffic flows (example 7)                                                                                                                                                                                                            |                                                                                                                                            |                        | 99                                                                                                                         |

|                                                                                                                                                                        | Traffic flows (example 8)                                                                                                                                                                                                            |                                                                                                                                            |                        | 100                                                                                                                        |

| 2.57                                                                                                                                                                   |                                                                                                                                                                                                                                      | • •                                                                                                                                        | •                      | 100                                                                                                                        |

|                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                            |                        |                                                                                                                            |

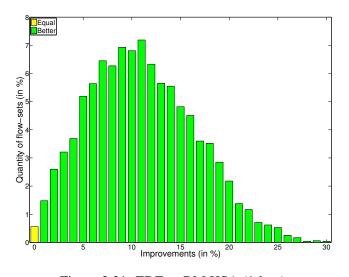

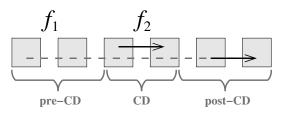

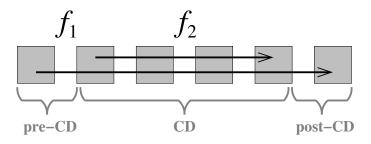

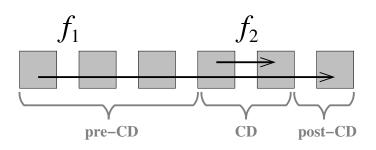

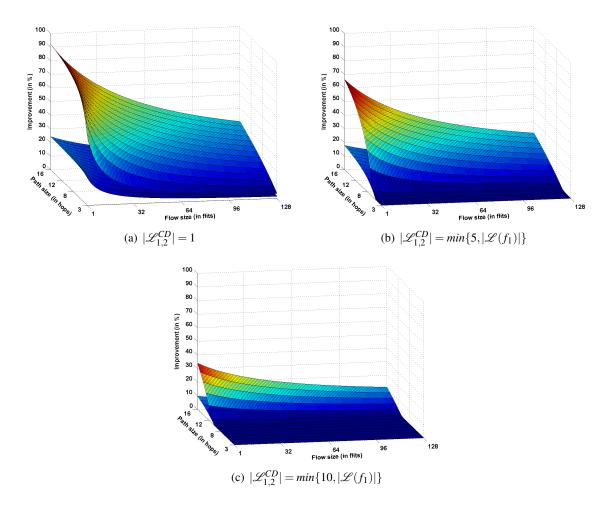

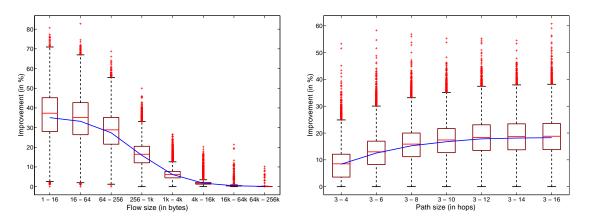

|                                                                                                                                                                        | Improvement in the worst-case traversal time of $f_2$ , for two contending flow                                                                                                                                                      | s f                                                                                                                                        | r<br>1                 | 101                                                                                                                        |

| 2.38                                                                                                                                                                   | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or                                | /s f<br>nce                                                                                                                                | 1                      | 101<br>103                                                                                                                 |

| <ul><li>2.38</li><li>2.39</li></ul>                                                                                                                                    | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s f<br>nce<br>                                                                                                                            | 1<br>•                 | 103                                                                                                                        |

| <ul><li>2.38</li><li>2.39</li><li>2.40</li></ul>                                                                                                                       | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br>                                                                                                                     | -1                     | 103<br>103                                                                                                                 |

| <ol> <li>2.38</li> <li>2.39</li> <li>2.40</li> <li>2.41</li> </ol>                                                                                                     | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br>                                                                                                                 | f1<br>•<br>•<br>•      | 103<br>103<br>104                                                                                                          |

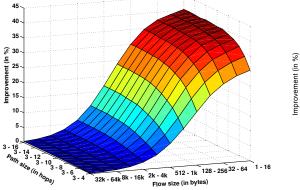

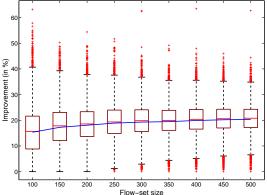

| <ul><li>2.38</li><li>2.39</li><li>2.40</li><li>2.41</li><li>2.42</li></ul>                                                                                             | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br>                                                                                                             | f1                     | 103<br>103<br>104<br>104                                                                                                   |

| <ul><li>2.38</li><li>2.39</li><li>2.40</li><li>2.41</li><li>2.42</li><li>2.43</li></ul>                                                                                | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s f<br>nce<br><br><br>                                                                                                                    | f1                     | 103<br>103<br>104<br>104<br>105                                                                                            |

| <ul><li>2.38</li><li>2.39</li><li>2.40</li><li>2.41</li><li>2.42</li><li>2.43</li></ul>                                                                                | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s f<br>nce<br><br><br>                                                                                                                    | f1                     | 103<br>103<br>104<br>104                                                                                                   |

| <ul> <li>2.38</li> <li>2.39</li> <li>2.40</li> <li>2.41</li> <li>2.42</li> <li>2.43</li> <li>2.44</li> </ul>                                                           | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br>                                                                                                             | °1<br>•<br>•<br>•<br>• | 103<br>103<br>104<br>104<br>105                                                                                            |

| <ul> <li>2.38</li> <li>2.39</li> <li>2.40</li> <li>2.41</li> <li>2.42</li> <li>2.43</li> <li>2.44</li> </ul>                                                           | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | vs j<br>nce<br><br><br><br>                                                                                                                | (1                     | 103<br>103<br>104<br>104<br>105<br>105                                                                                     |

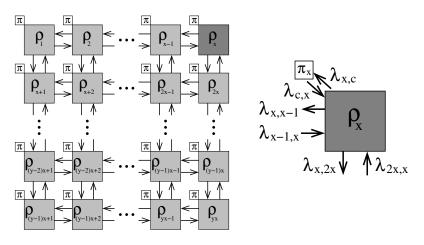

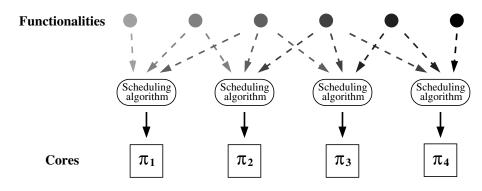

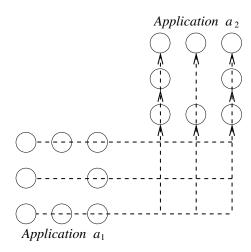

| <ul> <li>2.38</li> <li>2.39</li> <li>2.40</li> <li>2.41</li> <li>2.42</li> <li>2.43</li> <li>2.44</li> <li>3.1</li> </ul>                                              | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | vs <i>f</i> nce<br><br><br><br><br>atte                                                                                                    | c1                     | 103<br>103<br>104<br>104<br>105<br>105                                                                                     |

| <ul> <li>2.38</li> <li>2.39</li> <li>2.40</li> <li>2.41</li> <li>2.42</li> <li>2.43</li> <li>2.44</li> <li>3.1</li> <li>3.2</li> </ul>                                 | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | vs <i>f</i><br>nce<br><br><br><br><br><br>                                                                                                 | 61                     | 103<br>103<br>104<br>104<br>105<br>105<br>108<br>111                                                                       |

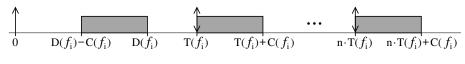

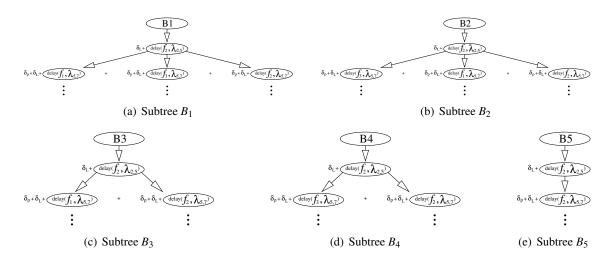

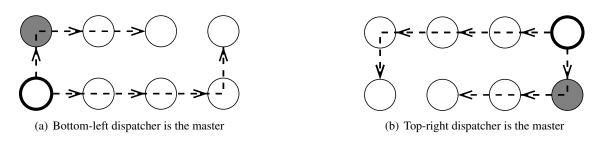

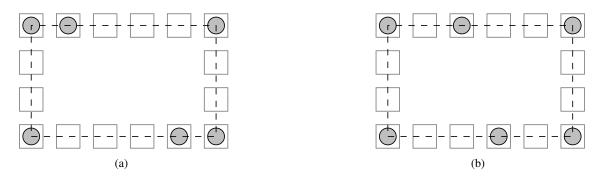

| <ul> <li>2.38</li> <li>2.39</li> <li>2.40</li> <li>2.41</li> <li>2.42</li> <li>2.43</li> <li>2.44</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> </ul>                    | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | vs f<br>nce<br><br><br><br><br><br>                                                                                                        | c1                     | 103<br>103<br>104<br>104<br>105<br>105<br>108<br>111<br>114<br>134                                                         |

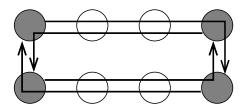

| <ul> <li>2.38</li> <li>2.39</li> <li>2.40</li> <li>2.41</li> <li>2.42</li> <li>2.43</li> <li>2.44</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> </ul>       | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | vs f<br>nce<br><br><br><br><br><br><br>                                                                                                    | f1                     | 103<br>104<br>104<br>105<br>105<br>108<br>111<br>114<br>134                                                                |

| 2.38<br>2.39<br>2.40<br>2.41<br>2.42<br>2.43<br>2.44<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br><br><br><br><br><br><br>                                                                                     | c1                     | 103<br>104<br>104<br>105<br>105<br>108<br>111<br>114<br>134                                                                |

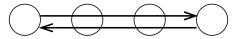

| 2.38<br>2.39<br>2.40<br>2.41<br>2.42<br>2.43<br>2.44<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                         | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br><br><br><br><br>                                                                                                            | c1                     | 103<br>104<br>104<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137                                                  |

| 2.38<br>2.39<br>2.40<br>2.41<br>2.42<br>2.43<br>2.44<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                                                  | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br><br><br><br><br>                                                                                             | f1                     | 103<br>104<br>104<br>105<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137<br>140                                    |

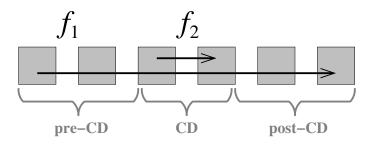

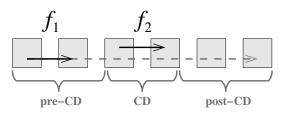

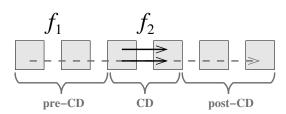

| 2.38<br>2.39<br>2.40<br>2.41<br>2.42<br>2.43<br>2.44<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                                                           | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathscr{L}(f_1)  =  \mathscr{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br><br><br><br><br><br><br>                                                                                     | f1                     | 103<br>104<br>104<br>105<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137<br>140<br>140                             |

| 2.38<br>2.39<br>2.40<br>2.41<br>2.42<br>2.43<br>2.44<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                                                    | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathscr{L}(f_1)  =  \mathscr{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br><br><br><br><br><br><br><br>                                                                                 | f1                     | 103<br>104<br>104<br>105<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137<br>140<br>140                             |

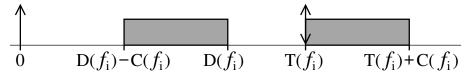

| 2.38<br>2.39<br>2.40<br>2.41<br>2.42<br>2.43<br>2.44<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11                                    | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathcal{L}(f_1)  =  \mathcal{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br><br><br><br><br><br><br>                                                                                     | f1                     | 103<br>104<br>104<br>105<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137<br>140<br>142<br>143                      |

| $\begin{array}{c} 2.38\\ 2.39\\ 2.40\\ 2.41\\ 2.42\\ 2.43\\ 2.44\\ 3.1\\ 3.2\\ 3.3\\ 3.4\\ 3.5\\ 3.6\\ 3.7\\ 3.8\\ 3.9\\ 3.10\\ 3.11\\ 3.12 \end{array}$               | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathscr{L}(f_1)  =  \mathscr{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> | f1                     | 103<br>104<br>104<br>105<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137<br>140<br>140<br>142<br>143               |

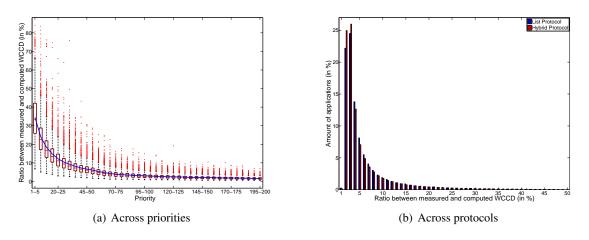

| 2.38<br>2.39<br>2.40<br>2.41<br>2.42<br>2.43<br>2.44<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13                    | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathscr{L}(f_1)  =  \mathscr{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i><br>nce<br><br><br><br><br><br><br><br><br>                                                                                     | f1                     | 103<br>104<br>104<br>105<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137<br>140<br>140<br>142<br>143<br>153<br>154 |

| $\begin{array}{c} 2.38\\ 2.39\\ 2.40\\ 2.41\\ 2.42\\ 2.43\\ 2.44\\ 3.1\\ 3.2\\ 3.3\\ 3.4\\ 3.5\\ 3.6\\ 3.7\\ 3.8\\ 3.9\\ 3.10\\ 3.11\\ 3.12\\ 3.13\\ 3.14 \end{array}$ | Improvement in the worst-case traversal time of $f_2$ , for two contending flow<br>and $f_2$ , where $P(f_1) > P(f_2)$ , $ \mathscr{L}(f_1)  =  \mathscr{L}(f_2) $ , and $f_1$ preempts $f_2$ only or<br>Improvements wrt flow sizes | /s <i>f</i>                                                                                                                                | f1                     | 103<br>104<br>104<br>105<br>105<br>105<br>108<br>111<br>114<br>134<br>135<br>137<br>140<br>142<br>143<br>153<br>154        |

| 3.17 | Analysis tightness                                                             | 158 |

|------|--------------------------------------------------------------------------------|-----|

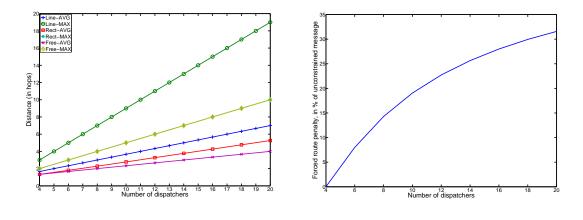

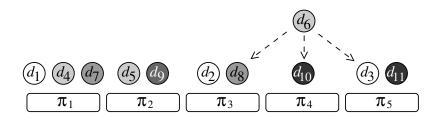

|      | Different dispatcher mappings for the same application-shape                   | 162 |

| 3.19 | Shape comparison                                                               | 171 |

| 3.20 | Rerouting penalty estimation                                                   | 171 |

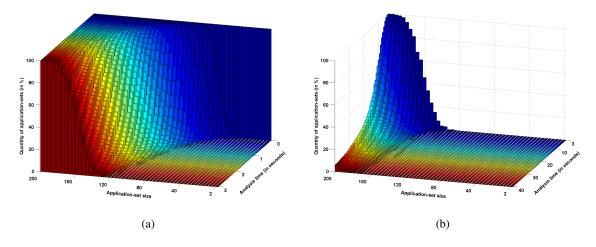

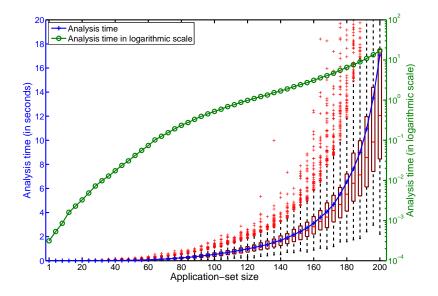

| 3.21 | Influence of application-set size on analysis time (1/2)                       | 173 |

| 3.22 | Influence of application-set size on analysis time (2/2)                       | 174 |

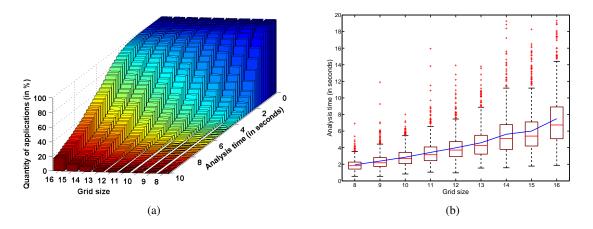

| 3.23 | Influence of grid size on analysis time                                        | 175 |

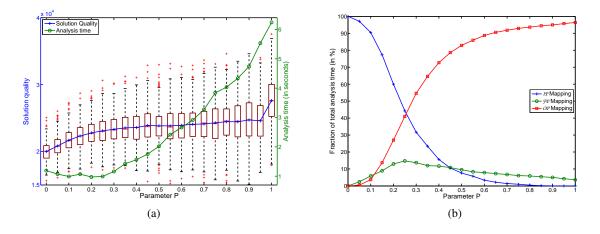

| 3.24 | Influence of parameter P on mapping process                                    | 176 |

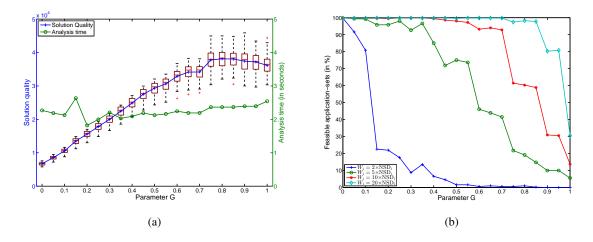

| 3.25 | Influence of parameter G on mapping process                                    | 177 |

| 3.26 | Memory operations                                                              | 179 |

|      | Master volatility problem for memory operations                                | 180 |

| 3.28 | Memory operations via proxy dispatchers                                        | 180 |

| 3.29 | Bounding messages                                                              | 181 |

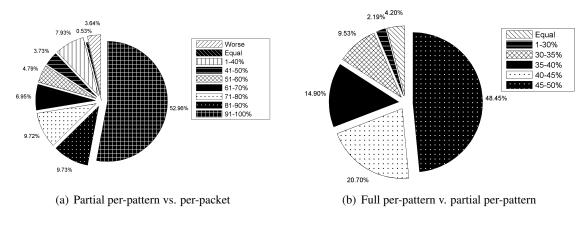

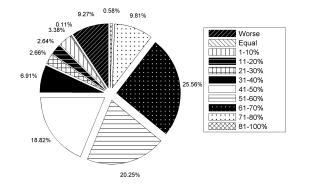

| 3.30 | Analyses comparison                                                            | 186 |

| 3.31 | Improvement with single controller                                             | 187 |

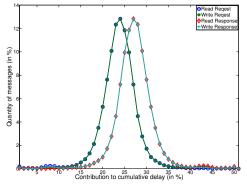

| 3.32 | Different memory operations                                                    | 187 |

| 3.33 | Full per-pattern vs. per-packet                                                | 188 |

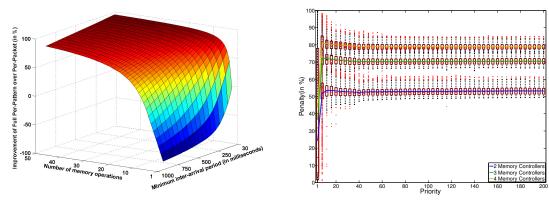

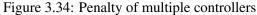

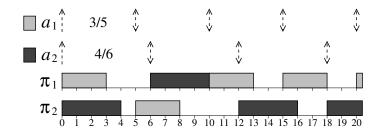

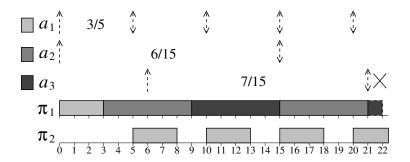

| 3.34 | Penalty of multiple controllers                                                | 188 |

| 3.35 | Semi-schedulability                                                            | 194 |

| 3.36 | Non-synchronised semi-schedulability                                           | 195 |

| 3.37 | Future release schedulability                                                  | 196 |

| 3.38 | Priority assignment upon dispatchers                                           | 199 |

| 3.39 | Speculative mapping                                                            | 200 |

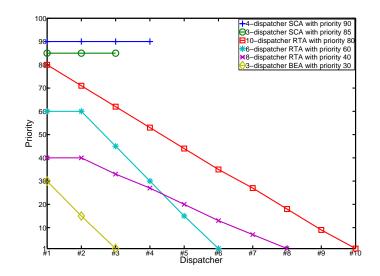

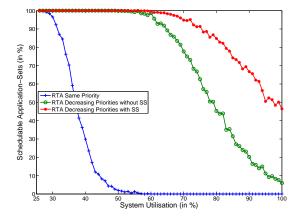

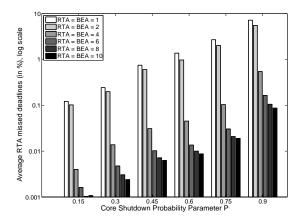

| 3.40 | Impact of RTA priorities and SS on schedulability guarantees                   | 203 |

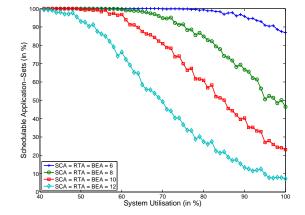

| 3.41 | Impact of number of dispatchers on schedulability guarantees                   | 203 |

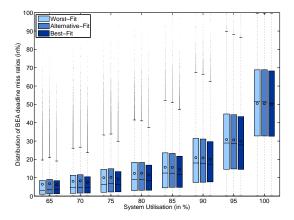

| 3.42 | Impact of mapping strategies on schedulability guarantees                      | 204 |

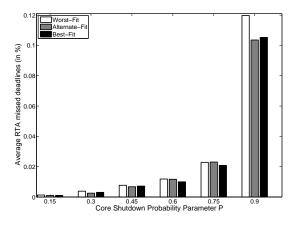

| 3.43 | Efficiency of online tests when using remaining computation times              | 204 |

| 3.44 | Efficiency of online tests without remaining computation times                 | 205 |

| 3.45 | Impact of number of dispatchers on runtime behaviour, without core shutdowns . | 205 |

| 3.46 | Impact of number of dispatchers on runtime behaviour, with core shutdowns      | 206 |

| 3.47 | Impact of mapping strategies on runtime behaviour, without core shutdowns      | 206 |

| 3.48 | Impact of mapping strategies on runtime behaviour, with core shutdowns         | 207 |

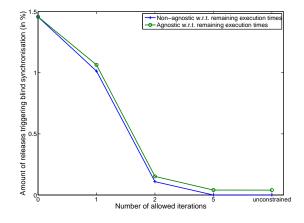

| 3.49 | Blind synchronisation mode (BSM)                                               | 207 |

| 4 1  |                                                                                | 010 |

| 4.1  | General form of Bordered Hessian for $n$ variables and one constraint $\ldots$ | 213 |

| 4.2  | Bordered Hessian for $\lambda = 0$                                             | 213 |

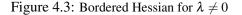

| 4.3  | Bordered Hessian for $\lambda \neq 0$                                          | 213 |

# **List of Tables**

| 1    | List of symbols used in this dissertation (1/6)          | xxi       |

|------|----------------------------------------------------------|-----------|

| 2    | List of symbols used in this dissertation (2/6)          | xxii      |

| 3    | List of symbols used in this dissertation (3/6)          | xxiii     |

| 4    | List of symbols used in this dissertation (4/6)          | xxiv      |

| 5    | List of symbols used in this dissertation (5/6)          | xxv       |

| 6    | List of symbols used in this dissertation (6/6)          | xxvi      |

| 1.1  | List of symbols related to the assumed platform          | 33        |

| 2.1  | Analysis parameters for Section 2.2.5                    | 53        |

| 2.2  | Flow-set parameters for Figure 2.16 (example 1)          | 62        |

| 2.3  | Flow-set parameters for Figure 2.16 (example 2)          | 64        |

| 2.4  | Analysis parameters for Section 2.3.3.5                  | 74        |

| 2.5  | Flow-set parameters for Figure 2.25                      | 80        |

| 2.6  | Flow-set parameters for two contending flows             | 86        |

| 2.7  | Flow-set parameters for Figure 2.28                      | 87        |

| 2.8  | Comparison of approaches (schedulability)                | 88        |

| 2.9  | Analysis parameters for Section 2.3.4.5                  | 89        |

| 2.10 | Flow-set parameters for Figure 2.34 (example 1)          | <b>98</b> |

| 2.11 | Flow-set parameters for Figure 2.34 (example 2)          | 100       |

| 2.12 | Analysis parameters for Section 2.3.5.5                  | 102       |

| 3.1  | OS operations related to agreement protocols             | 112       |

| 3.2  | Analysis and simulation parameters for Section 3.3.4     | 133       |

| 3.3  | OS operations related to inter-application communication | 136       |

| 3.4  | Analysis and simulation parameters for Section 3.5.5     | 152       |

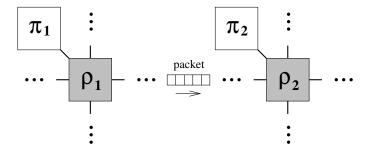

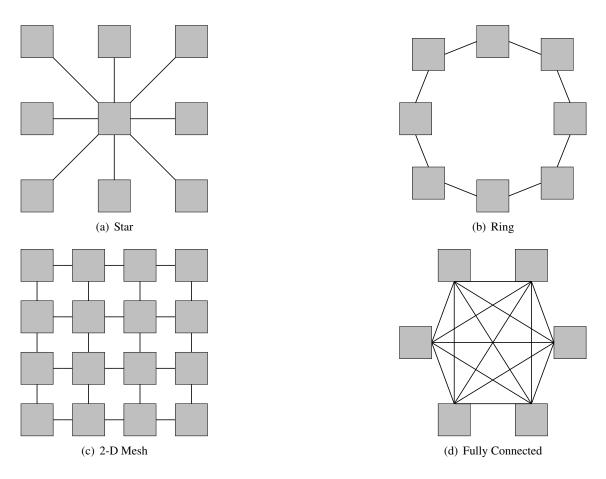

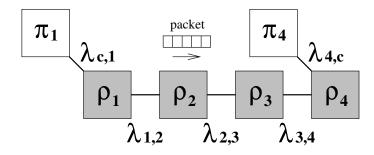

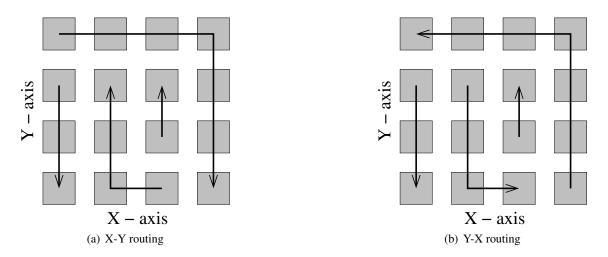

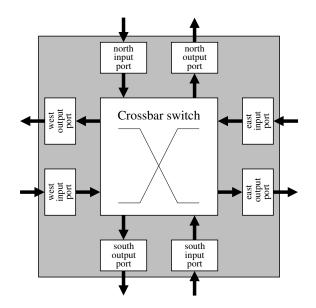

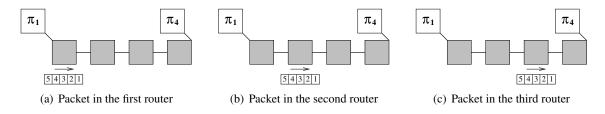

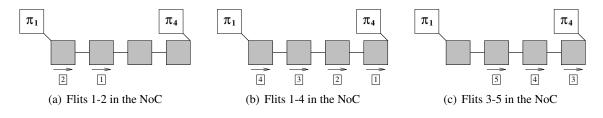

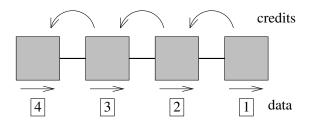

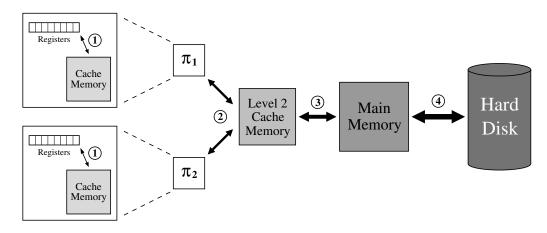

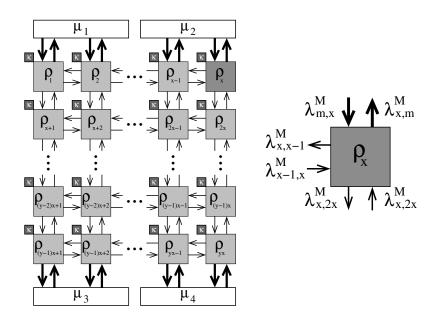

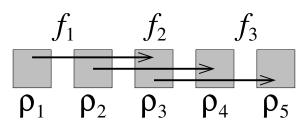

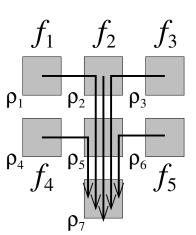

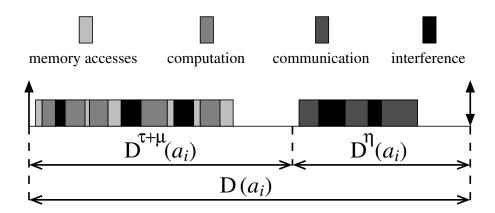

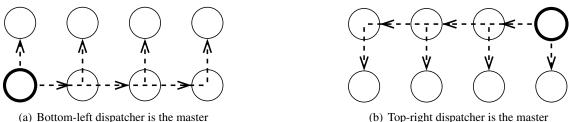

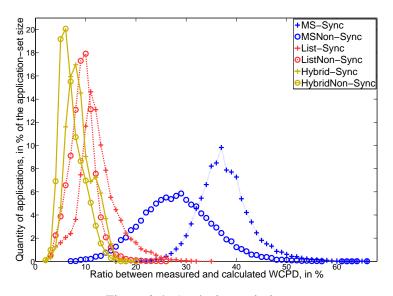

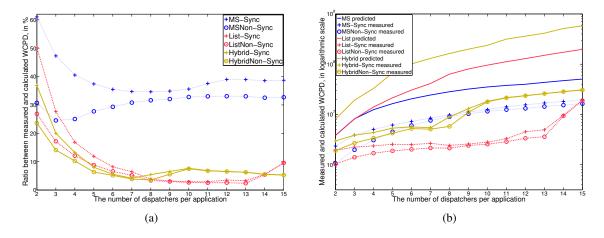

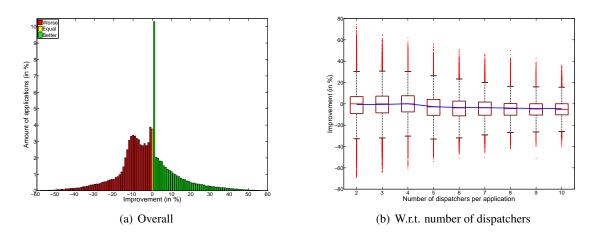

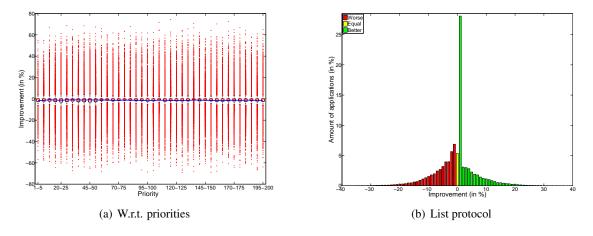

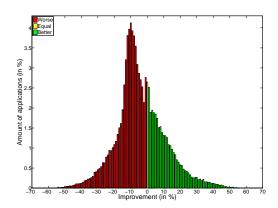

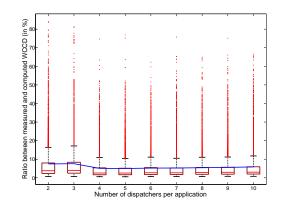

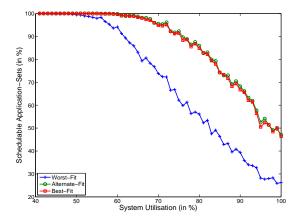

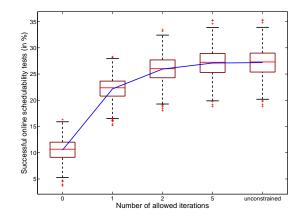

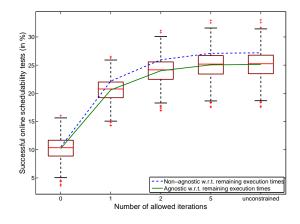

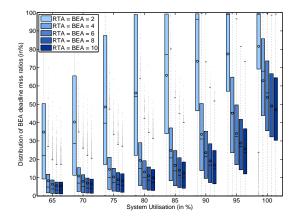

| 3.5  | Analysis and simulation parameters for Section 3.6.4     | 172       |