# Measurements in 1149.4 environments – correcting the infrastructure switches influence

Manuel C. Felgueiras<sup>1</sup>, Gustavo R. Alves<sup>1</sup>, J. M. Martins Ferreira<sup>2</sup>

{mcf, gca}@isep.ipp.pt, jmf@fe.up.pt

1 ISEP / LABORIS – Rua Dr. António B. de Almeida – 4200-072 Porto – PORTUGAL

2 FEUP / DEEC – Rua Dr. Roberto Frias – 4200-465 Porto - PORTUGAL

#### **Abstract**

Measuring the values of discrete components frequently takes place during the test or debug phase of Printed Circuit Boards (PCB). This operation requires tools that are based on some access type. The shrinking geometries constrain the straightforward use of tools based on physical access. One of the aims of the IEEE1149.4 Std. is to facilitate those on-board measurements. This infrastructure relies on electronic access that includes high quality analog buses and a set of electronic switches, which enable to completely isolate a component under characterization, e.g. by injecting a known current and measuring the voltage across it. During this process, the infrastructure switches have a negative impact in the measurement accuracy. This paper analyses the measurement of one resistor in two situations: connected between a pin and ground and between two pins. The infrastructure switches that affect the measurement quality are identified and the upper limit of its systematic error is characterized. When the systematic error is completely defined then it is possible to remove its negative effect from the final result.

### 1. Introduction

In many PCB's, discrete components are mainly used for coupling different circuit stages and for device configuration. The IEEE1149.4 [1] test infrastructure was presented as a formal extension of the IEEE1149.1 [2] Std. for the Mixed-Signals (MS) area. Its scope includes:

- interconnect test

- parametric test (characterization of discrete components)

- internal test

The IEEE1149.4 test infrastructure includes high quality internal analog buses that can be used as

embedded analog probes, when the PROBE mandatory instruction is selected. The standard stipulates a minimal set of mandatory requirements while also allowing its reuse for many others purposes. The infrastructure reuse are suggested to:

- detect deviations to the nominal performance [3]

- perform RF measurements [4]

- on-line monitoring and reconfiguring functions in safety critical applications [5]

- perform analog diagnosis through the quiescent nodal analog voltage [6]

- support the testing of ADCs and DACs [7]

- support debug operations in MS circuits [8,9]

- test specific parameters of digitals circuits (e.g.  $V_{\rm IH}$ ) [10]

The market acceptance of this test infrastructure has been slow and to promote it, several actions have taken place: (a) one compliant Integrated Circuit (IC) has been produced [11]; (b) analog extension to BSDL has been proposed to support automatic test generation [12]; (c) a check integrity procedure has been proposed [13]; (d) its use for monitoring internal analog/digital nodes [9]. It is clear today the benefits due to the use of analog buses to support measurements, even in digital circuits, as presented and patented by INTEL [14]. The tradeoffs associated to the costs and the benefits are encouraging the use of this test infrastructure [15,16]. The analog infrastructure bus characterisation and some experimental results have been presented [17,18].

The present work analyses the individual errors introduced by the 1149.4 switches during the measurement process of one resistor. We describe a methodology to remove the effect introduced by each involved switch, whenever possible. We use the 1149.4 compatible IC SCANSTA400 [19] to verify and validate our analysis. This work intends to provide a simple formula to correct the measurement process errors caused by non-ideal switches. This formula is

especially useful for those people that use the analog bus to perform measurements through electronic access.

## 2. Determining the value of one resistor placed between an ABM and GND

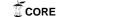

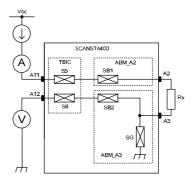

The methodology to calculate the value of a resistor, via the 1149.4 infrastructure, consists on: (1) injecting a known current value in the resistor, via AB1, and (2) measuring the voltage across the resistor, via AB2, as presented in Figure 1.

Figure 1 – Determining the value of one resistor placed between an ABM and GND.

The source current is recommended to provide a stable current value and also to prevent excessive current values that may damage test infrastructure during the measurement operation. The initial value for  $R_X$  is  $R_{1,1}$  and its value is calculated by:

$$R_1 = V_1 / I_1 \tag{2.1}$$

where  $V_1$  and  $I_1$  correspond to the initial measured values of the voltage and current across  $R_x$ , respectively. The resistor calculated value is affected by several error sources:

- $\varepsilon_V$  associated to the voltmeter accuracy

- $\varepsilon_A$  associated to the ammeter accuracy

- $\varepsilon_{\text{M1}}$  associated to the switches resistance  $R_{\text{SB2}}$  and  $R_{\text{S6}}$  ( $R_{\text{SB2}} + R_{\text{S6}} > 0 \Omega$ )

- $\varepsilon_{M2}$  associated to the voltmeter resistance  $(R_V \neq \infty\Omega)$

The total relative error in the calculation process of  $R_x$  is given by:

$$\varepsilon_{\text{RX}} = \varepsilon_{\text{V}} + \varepsilon_{\text{A}} + |\varepsilon_{\text{M1}}| + |\varepsilon_{\text{M2}}|$$

[2.2]

$\epsilon_V$  is the relative error due to the voltmeter limited accuracy and its value is usually indicated in the

respective instrument manual.  $\varepsilon_{\rm A}$  is the similar relative error for the ammeter.  $\varepsilon_{\rm M1}$  corresponds to the error introduced by the measurement methodology, and is due to the influence of the switch resistances SB2 ( $R_{\rm SB2}$ ) and S6 ( $R_{\rm S6}$ ). The voltage measured by the voltmeter is lower than the actual voltage across  $R_{\rm X}$ , as it includes the voltage drop at  $R_{\rm SB2}$  and  $R_{\rm S6}$ . The reduction of the voltage measured by the voltmeter is given by:

$$\Delta V = -(R_{SB2} + R_{S6}) \cdot I_V$$

[2.3]

and the associated error is:

$$\varepsilon_{\text{M1}} = \Delta V / V = -(R_{\text{SB2}} + R_{\text{S6}}) / R_{\text{V}}$$

[2.4]

where  $R_V$  is the voltmeter internal resistance. The minus signal means that the voltage measured by the voltmeter is less than the expected value and hence the calculated  $R_X$  will be lower than the correct value. To remove this error, a new value should be calculated as follows:

$$V_2 = V_1 [1 + (R_{SB2} + R_{S6}) / R_V]$$

[2.5]

The IEEE1149.4 Std. defines that value of RSW2 (equal to RSB2 plus RS6, i.e. RSW2 = RSB2 + RS6) should be lower than 10 k $\Omega$ 1 (a similar definition is made for RSW1). We now have two possibilities: (1) if the exact value of RSB2 + RS6 is known, we calculate V2 and hence  $\varepsilon M1 = 0$ ; (2) if only the upper limit of RSB2 + RS6 is known, a new voltage value V2, equal to V1, will be used in the following calculations. In this last case,  $\epsilon M1$  should be calculated through formula [2.4]. In both we consider a new current value I2, equal to I1, to be used in the following calculations. EM2 is the other method error and is due to the voltmeter internal resistance. The V2 / I2 relation does not correspond to the desirable calculated resistance but to a parallel association between R2 and RV, i.e.:

$$V_2/I_2 = R_2 = (R_3 R_V)/(R_3 + R_V)$$

[2.6]

To remove this error, a new resistance value  $R_3$  must be calculated as follows:

$$R_3 = R_2 / [1 - (R_2 / R_V)]$$

[2.7]

where:

$$\varepsilon_{\rm M2} = -\left(R_2/R_{\rm V}\right) \tag{2.8}$$

<sup>&</sup>lt;sup>1</sup> IEEE1149.4Std., 9.4.1.b

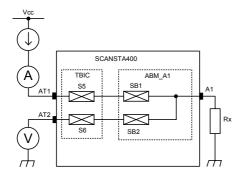

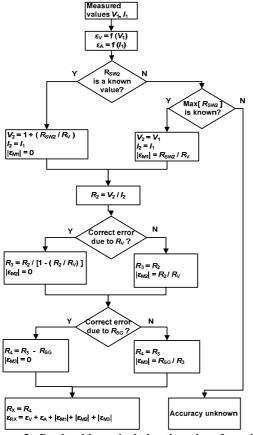

In order to better understand the previous operations, a chart with the implicit algorithm is presented in Figure 2.

Figure 2 – Rx algorithm calculating the value of a resistor placed between an ABM and GND.

The chart includes all possible decisions in the  $R_{\rm X}$  calculation process, allowing the user to evaluate the impact of a given error source (e.g. the non-zero  $R_{\rm SB2}$  ohmic value) in the final result. Notice that not every switch included in the measurement path (e.g.  $R_{\rm SB1}$ ) affects the  $R_{\rm X}$  calculation process.

## 3. Determining the value of one resistor placed between two ABMs

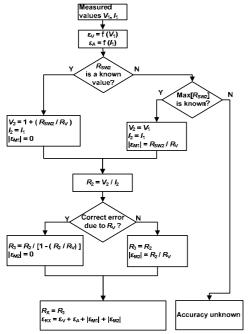

The measurement of one resistor placed between two ABMs is similar to the case analysed in the previous section, as we can see in the Figure 3.

Figure 3 - Determining the value of one resistor placed between two ABMs.

The difference is that we now have a new error source due the presence of  $R_{SG}$ . The initial value for the calculated  $R_X$  is again given by:

$$R_1 = V_1 / I_1 ag{3.1}$$

However, the total relative error of  $R_x$  is now:

$$\varepsilon_{\text{RX}} = \varepsilon_{\text{V}} + \varepsilon_{\text{A}} + |\varepsilon_{\text{M1}}| + |\varepsilon_{\text{M2}}| + |\varepsilon_{\text{M3}}|$$

[3.2]

Errors  $\varepsilon_{M1}$  and  $\varepsilon_{M2}$  were explained in the previous section.  $\varepsilon_{M3}$  is a new method error associated to the presence of  $R_{SG}$ . The calculus of  $R_X$  follows the same steps as explained in the previous section until a value for  $R_3$  is obtained. However this value does not correspond to the real resistance between the two pins, but rather to a series formed by  $R_4$  and  $R_{SG}$ , i.e.:

$$R_3 = R_4 + R_{SG} ag{3.3}$$

The error value  $\varepsilon_{M3}$  is given by:

$$\varepsilon_{\rm M3} = R_{\rm SG} / R_3 \tag{3.4}$$

To remove this error, R4 must be calculated as follows:

$$R_4 = R_3 - R_{SG}$$

[3.5]

which, by its turn, requires characterizing the internal resistor  $R_{SG}$ . This may be done with an additional test, as presented in Figure 4.

Figure 4 – Determining the resistance value of the  $R_{SG}$  switch.

To determine the ohmic value of  $R_{\rm SG}$  the rules explained in the previous section should be applied. Notice that in the configuration presented in Figure 4,  $R_{\rm X}$  is in series with  $R_{\rm S5}$  and  $R_{\rm SB1}$ , which do not affect the measurement process, as the resistor under characterization is now  $R_{\rm SG}$ . In order to better

understand the previous operations a new chart with the implicit algorithm is presented in figure 5.

Figure 5 - Rx algorithm calculating the value of a resistor placed between two ABMs.

## 4. The case study

Our analysis was validated with the IC SCANSTA400, an 1149.4 compatible IC. The datasheet of this IC contains only the basic information and the values for  $R_{\rm SW1}$  and  $R_{\rm SW2}$  are not supplied. Thus we have made some tests to determine them. The obtained results are presented in Table 1.

Table 1 -  $R_{SW1}/R_{SW2}$  resistor values for the IC SCANSTA400.

| Pin<br>name | Current<br>value<br>(mA) | Voltage<br>value<br>(V) | R <sub>SW1/2</sub><br>location | R <sub>SW1/2</sub> value (kΩ) |

|-------------|--------------------------|-------------------------|--------------------------------|-------------------------------|

| A1          | 0,436                    | 0,3955                  | $R_{\mathrm{SW1 A1}}$          | 0,907                         |

| A1          | 0,435                    | 0,3957                  | $R_{ m SW2~A1}$                | 0,909                         |

| A2          | 0,435                    | 0,3978                  | $R_{\mathrm{SW1 A2}}$          | 0,914                         |

| A2          | 0,435                    | 0,3957                  | $R_{\mathrm{SW2\_A2}}$         | 0,909                         |

| A3          | 0,435                    | 0,3980                  | $R_{\rm SW2~A3}$               | 0,915                         |

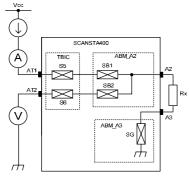

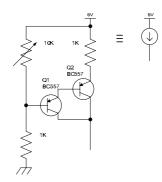

The schematic of the used current source is presented in Figure 6, for illustrative purposes.

Figure 6 - Current source used during the measurement operations.

For measuring one resistor placed between an ABM and GND we used the circuit showed in Figure 1. To control the IC TAP (Test Access Port) we used an in house PC application, named JTAGer [20], which can control two TAPs. The program is presented in Annex 1. The voltage and current values read are:

$$V_1 = 2,176 \text{ V}$$

[4.1]

$$I_1 = 0.458 \text{ mA}$$

[4.2]

The initial value for  $R_X$  is:

$$R_1 = 2,176 / 0,458 \cdot 10^{-3} = 4,75 \text{ k}\Omega$$

[4.3]

The relative error  $\varepsilon_{RX}$  is calculated as follows:

$$\varepsilon_V = 0.05\% RDG + 3 DIG = 0.0019 \text{ or } 0.19\%$$

[4.4]

$$\varepsilon_{A}$$

= 0,05%RDG + 3 DIG = 0,0071 or 0,71% [4.5]

$$|\varepsilon_{\text{M1}}| = \Delta V/V = (R_{\text{SB2}} + R_{\text{S6}})/R_{\text{V}} = R_{\text{SW2\_A2}}/R_{\text{V}} =$$

$907 / 10.10^6 = 0.01\%$  [4.6]

$$|\varepsilon_{\rm M2}| = R_{\rm M}/R_{\rm V} = 4,75 \cdot 10^3 / 10 \cdot 10^6 = 0,0005$$

or  $0,05\%$

$$\epsilon_{RX} = \epsilon_V + \epsilon_A + |\epsilon_{M1}| + |\epsilon_{M2}| = 0.19 + 0.71 + 0.01 + 0.05 = 0.96 \%$$

[4.8]

In this case it is not possible to remove errors  $\varepsilon_{M1}$  and  $\varepsilon_{M2}$  because they are much less than the sum given by  $\varepsilon_V + \varepsilon_A$ , thus the correcting operations have no effect. In this case, using a voltmeter and an ammeter with higher accuracy (i.e. equal to or less than 0,1%) would cause the errors associated to the method ( $\varepsilon_{M1}$  and  $\varepsilon_{M2}$ ) to have an higher impact in the calculation of  $R_X$ . The resulting  $R_X$  is:

$$R_{\rm X} = R_1 = 4{,}75 \text{ k}\Omega$$

[4.9]

The overall accuracy in this calculation method is less than 1%. The value of  $R_{\rm X}$  measured with a high accuracy instrument is:

$$R_{\rm XH} = 4.757,0 \ \Omega$$

[4.10]

so a coherent value has been obtained. For measuring one resistor placed between two ABMs we used the circuit illustrated in Figure 3. The correspondent JTAGer program is presented in the Annex 2. The voltage and current values read are:

$$V_1 = 2,412 \text{ V}$$

[4.11]

$$I_1 = 0.448 \text{ mA}$$

[4.12]

To characterize  $R_{SG}$  we use the circuit illustrated in Figure 4. The obtained results are:

$$V_{\rm SG} = 0.2732 \text{ V}$$

[4.13]

$$I_{SG} = 0.447 \text{ mA}$$

[4.14]

$$R_1 = 2,412 / 0,448 \cdot 10^{-3} = 5,38 \text{ k}\Omega$$

[4.15]

The relative error  $\varepsilon_{RX}$  is :

$$\epsilon_V = 0.05\% RDG + 3 DIG = 0.0017 \text{ or } 0.17\%$$

[4.16]

$$\varepsilon_A$$

= 0,05%RDG + 3 DIG = 0,0072 or 0,72% [4.17]

$$|\varepsilon_{\text{M1}}| = \Delta V/V = (R_{\text{SB2}} + R_{\text{S6}})/R_{\text{V}} = R_{\text{SW2\_A2}}/R_{\text{V}} = 909 / 10.10^6 = 0.01\%$$

[4.18]

$$|\varepsilon_{\rm M2}| = R_{\rm M}/R_{\rm V} = 5,38 \cdot 10^3 / 10 \cdot 10^6 = 0,0005 \text{ or } 0,05\%$$

[4.19]

The calculated value for  $R_{SG}$  is:

$$R_{SG} = 0.2732 / 0.447 \cdot 10^3 = 611 \Omega$$

[4.20]

Notice that in the calculation process of  $R_{SG}$  the associated  $\varepsilon_{M1}$  and  $\varepsilon_{M2}$  errors may be disregarded. Returning to the calculation of  $R_{X}$ , the value for  $\varepsilon_{M3}$  is obtained through:

$$\varepsilon_{\text{M3}} = R_{\text{SG}} / R_{\text{M}} = 611 / 5,38 \cdot 10^3 =$$

0,114 or 11,4% [4.21]

This error source is unacceptable and must be removed.

$$R_4 = R_{\text{M3}} - R_{\text{SG}} = 5.38 \cdot 10^3 - 0.611 \cdot 10^3 = 4.77 \text{ k}\Omega$$

4.22]

The total error and the final value for  $R_X$  are, respectively.

$$\begin{split} \epsilon_{\text{RX}} &= \epsilon_{\text{V}} + \epsilon_{\text{A}} + |\epsilon_{\text{M1}}| + |\epsilon_{\text{M2}}| + |\epsilon_{\text{M3}}| = \\ &= 0.17 + 0.72 + 0.01 + 0.05 + 0 = 0.95 \% \\ R_{\text{X}} &= R_4 = 4.77 \text{ k } \Omega \end{split} \tag{4.24}$$

The obtained result is also coherent. Notice that the  $\epsilon_{M3}$  error source has been removed. To achieve better results it is imperative to use T&M instruments with better accuracy.

#### 5. Conclusion

The measurement in discrete components using electronic access mechanisms is an usual task in present integrated systems. In this work we proposed a methodology to analyse the errors introduced by the 1149.4 infrastructure in order to evaluate when its impact in the measurement quality is acceptable or be removed. Although the presented analysis has been conducted on an IEEE1149.4 compliant device, the calculation method may be applied to other analog buses. The impact of each switch has also been characterized, which may help analog designers to better understand which particular switch type to use in a particular location.

#### Annex 1

;Determining the value one resistor placed :ABM\_A1 - GND  $\,$

```

;IC: SCANSTA400-National

; Author: M. Felgueiras

;Test conditions:

Mode=0

C0 = 0

C1 = 0

CE=1

CE1=0

seltap0;

serflg0;

A:

state irshift;

ld cnt,20d;

nshfcp 1FFFEh,80000h,C0000h; //

jerr ERROR;

tms1;

// IR<- SAMPLE/PRELOAD

state drshift;

ld cnt,48d;

nshf 00000300C000h;

jerr ERROR;

// BSR <- DATA

tms1;

state irshift;

//

ld cnt,20d;

nshfcp 00000h,80000h,C0000h;

jerr ERROR;

//

IR <- EXTEST:Read V1, I1</pre>

tms1;

imp A;

ERROR:

halt;

```

#### Annex 2

```

;Determining the value one resistor placed

:ABM_A1 - GND

;IC: SCANSTA400-National

;Author: M.Felgueiras

;Test conditions:

Mode=0

C0 = 0

C1=0

CE=1

CE1=0

start:

seltap0;

serflg0;

rst;

state irshift;

ld cnt,20d;

nshfcp 1FFFEh,80000h,C0000h;

jerr ERROR;

// TR <- SAMPLE/PRELOAD

tms1;

state drshift;

ld cnt,48d;

nshf 0000030100c0h;

jerr ERROR;

// BSR <- DATA

tms1;

state irshift;

ld cnt,20d;

nshfcp 00000h,80000h,C00000h;

jerr ERROR;

```

### Acknowledgements

We would like to thank Mr. Adan Osseiram for providing the SCANSTA400 ICs used in the validation phase of this work.

#### References

- [1] IEEE Standard for a Mixed-Signal Test Bus, March 2000, IEEE Std. 1149.4, ISBN 0-7381-1755-2.

- [2] IEEE Standard Test Access Port and Boundary-Scan Architecture, October 1993, IEEE Std. 1149.1, ISBN 1-55937-350-4.

- [3] J. McDermid, "Limited Access Testing: IEEE1149.4", Proceedings of the International Test Conference, 1998, pp388-395.

- [4] P. Syri, J. Hakinen, M. Moilanen, "1149.4 Compatible ABMs for Basic RF measurements", Proceedings of the Design Automation and Test in Europe, 2005, pp 172-173.

- [5] C. Jeffrey, R. Cutajar, S. Prosser, M. Lickess, A. Richardson, S. Riches "The integration of on-line monitoring and reconfiguration functions using IEEE1149.4 into critical automotive electronic contro unit", Proceedings of the Design Automation and Test in Europe, 2005, pp 153-158.

- [6] O. Decoudray-Acevedo J. Ramirez-Angulo, "Inovative built-in self-test schemes for on-chip diagnosis, compliant with the IEEE1149.4 mixed signal test bus standard", Journal of Electronic Testing, vol 9, pp 21-28, 2003.

- [7] S. K. Sunter, "Testing High Frequency ADCs and DACs with a low Frequency Analog Bus", Proceedings of the International Test Conference, 2003, PP 228-235.

- [8] U. Kac, F. Novak, F. Azais, P. Nouet, M. Renovell, "Extending IEEE std. 1149.4 Analog Boundary Modules to Enhance Mixed-Signal Test", IEEE Design & Test of Computers, March-April 2003, pp 32-39.

- [9] M. Felgueiras, G. Alves, J, Ferreira, "Debugging mixed-signal circuits via the IEEE1149.4 Std. analysis of limitations and requirements", Proceedings of the 12<sup>th</sup> IEEE International Mixed Signal Testing Workshop, June, 2006, pp 2-7.

- [10] S. K. Sunter, B. Nadeau-Dostie, "Complete, Contactless I/O Tesing – Reaching the Boundary in Minimizing Digita IC, Testing Cost", Proceedings of the International Test Conference, 2002, pp 446-455.

- [11] S. Sunter, K. Filiter, J. Woo, P. McHugh, "A general purpose 1149.4 IC with HF Analog Test Capabilities", Proceedings of International Test Conference, 2001, pp38-45.

- [12] B. Suparjo, A. Ley, A. Cron, H. Hhrenberg, "Aalog Boundary-Scan Description Language (ABSDL) for Mixed-Signal Board Test", Proceedings of the International Test Conference, 2006.

- [13] M. Felgueiras, G. Alves, J. Ferreira, "Integrity checking of 1149.4 extensions to 1149.1", Proceedings of the XXI Conference on Design of Circuits and Integrated Systems, September 2006, pp (CD).

- [14] T. Frodsham et al, "Apparatus for I/O leakage selftest in an integrated circuit", US Patent 6262585, July 2001.

- [15] S. Sunter "The P1149.4 Mixed Test Bus: Costs and Benefits", Proceedings of the International Test Conference, 1995, pp 444-450.

- [16] S. K. Sunter "Cost/benefits analysis of the P1149.4 mixed-signal test bus", IEE Proc.- Circuits Devices Syst. Vol. 13, nº6, December 1996, pp 393-398.

- [17] I. Duzevik, "Preliminary Results of Passive Component Measurement Methods Using an IEEE 1149.4 Compliant Device", Proceedings of the Board Test Workshop, 2002.

- [18] T. Saikkonen, M. Milanen, "Component Value Calculations for Measurements in 1149.4 Environments", Proceedings of the 12<sup>th</sup> International Mixed Signal Testing Workshop, June 2006, pp 77-82.

- [19] <u>http://www.national.com/ds/ST/STA400EP.pdf</u>

- [20] JTAGer site: http://paginas.fe.up.pt/~jmf/pcsd0304/jtager.htm