FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Reconfigurable peripheral manager for embedded robotic systems

**Filipe Miguel Monteiro Lopes**

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor: José Carlos dos Santos Alves

July 30, 2015

© Filipe Lopes, 2015

# A Dissertação intitulada

"Reconfigurable Peripheral Manager for Embedded Robotic Systems"

foi aprovada em provas realizadas em 13-07-2015

o júri

Artsun Joh Smente Anago

Presidente Professor Doutor António José Duarte Araújo Professor Auxiliar do Departamento de Engenharia Eletrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto

Muntpalim to threen print

Professor Doutor Manuel Gradim de Oliveira Gericota Professor Adjunto do Departamento de Engenharia Eletrotécnica do Instituto Superior de Engenharia do Porto

pur Cal Sut Al.

Professor Doutor José Carlos dos Santos Alves Professor Associado do Departamento de Engenharia Eletrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto

O autor declara que a presente dissertação (ou relatório de projeto) é da sua exclusiva autoria e foi escrita sem qualquer apoio externo não explicitamente autorizado. Os resultados, ideias, parágrafos, ou outros extratos tomados de ou inspirados em trabalhos de outros autores, e demais referências bibliográficas

Autor - Filipe Miguel Monteiro Lopes

Faculdade de Engenharia da Universidade do Porto

ii

# Resumo

Uma preocupação crescente em relação à poupança energética tem permitido o crescimento de sistemas computacionais de baixo consumo no mundo da robótica. Este facto combinado com o aumento da diversidade da robótica no dia a dia, torna essencial que os sistemas robóticos possuam a capacidade de serem facilmente reconfigurados.

No entanto, apesar do crescente interesse em volta do desenvolvimento de hardware por parte da comunidade tecnológica juntamente com ferramentas cada vez mais user-friendly ainda existe pouco interesse e conhecimento em relação nesta área.

Este trabalho aproxima o utilizador comum do desenvolvimento de hardware e reconfigurabilidade usando um computador de baixo consumo, BeagleBone Black, Logi-Bone uma placa com FPGA, e uma ferramenta capaz de facilmente e sem necessidade de conhecimentos adicionais gerar um projecto de hardware completo.

A ferramenta desenvolvida e explicada em detalhe neste documento permite gerar um projeto de hardware completo para a Logi-Bone contendo os periféricos mais comuns da robótica, usando uma linguagem simples e intuitiva. E providência as APIs necessárias para uma fácil integração dos periféricos gerados na FPGA com o software presente na BeagleBone.

Finalmente, para atrair utilizadores com algum conhecimento em desenvolvimento de hardware a ferramenta permite a integração de blocos feitos à medida no projecto. iv

# Abstract

Nowadays there is a huge concern with power consumption, opening the doors to small and low energy consumption computers in the world of robotics. With the advance of electronic technology and attempts to delegate further tasks to robots daily, a reconfigurable system is of utmost importance.

However, although the increase in interest regarding digital design and related tools userfriendlier than ever, the adoption of hardware development by the developer community is ratter low.

This work brings digital design and system reconfigurability to the common user, using the low energy consumption, powerful and small computer, BeagleBone Black, the Logi-Bone, a device that contains a FPGA, attached to it and a software tool used to easily generate the full hardware project for the FPGA, without needing any particular hardware design knowledge.

This tool, developed and explored in detail through the length of the document, is capable of generating full hardware design containing most of the common peripherals used in robotics for the Logi-Bone via simple and intuitive language. Furthermore, this tool also provides the APIs necessary to easily interface with the peripherals chosen by the user and implemented in the FPGA.

Finally, in an attempt to captivate hardware designers, the software tool also allows inclusion of one or more custom blocks in a project.

vi

# Agradecimentos

Em primeiro gostaria de agradecer ao meu orientador Professor José Carlos Alves, pelo o apoio, auxilio e conselhos dados ao longo desta dissertação é de louvar o entusiasmo deste professor pelo o seu trabalho que me permitiu continuar a trabalhar entusiasticamente mesmo nas fases menos boas da dissertação. Muitos outros professores também merecem o meu agradecimento pelo todo o apoio prestado durante o meu percurso académico.

Fica aqui um obrigado à minha família por me proporcionar tudo o que necessitei para concluir esta jornada. Ao meu gato, a princesa da minha vida, o meu Bart, por pareceres saber sempre como me sinto e estares à minha beira naqueles dias mais complicados.

Quero deixar um agradecimento também às palavras de apoio dadas pela dona Zeza e à Brigite, incrível como uma rapariga tão nova tem tanta sabedoria.

Ao Sr. Eng. Tiago Souto, deixo um obrigado e um abraço pelos gelados tomados depois do trabalho e por seres aquela pessoa que está comigo desde o inicio.

Ao pessoal do costume, Orelhinhas, Armandalho, Investimento, Cebolinha, Monstro, Mãe Susana, DiMarina, Batares, SraDeArtes, Cláudia, etc um obrigado por os almoços, jogos de cartas, piadas, companhia, etc.

E finalmente, o meu maior agradecimento vai para ti, por teres sido a melhor coisa que me aconteceu, por saber que me apoias apesar de tudo, por me teres levantado do chão, mostrado o mundo e feito sorrir, por seres um orgulho e admiração para mim, por tudo e por nada, pelas palavras e pelos silêncios. Obrigado por tudo, Rainha.

Filipe

viii

"Multiply it by infinity, and take it to the depth of forever, and you will still have barely a glimpse of what I'm talking about."

William Parrish (Meet Joe Black)

х

# Contents

| 1 | Intr       | oduction                           | 1        |

|---|------------|------------------------------------|----------|

|   | 1.1        | Problem definition                 | 2        |

|   | 1.2        | Thesis organization                | 3        |

| 2 | Stat       | e of art                           | 5        |

|   | 2.1        | CPU-FPGA embedded platform         | 5        |

|   |            | 2.1.1 CPU and FPGA in a SoC        | 5        |

|   |            | 2.1.2 FPGA and Softcore CPU        | 13       |

|   |            |                                    | 15       |

|   | 2.2        |                                    | 18       |

|   |            | *                                  | 18       |

|   |            |                                    | 19       |

|   |            |                                    | 19       |

|   | 2.3        |                                    | 20       |

| 3 | Bea        | gleBone Black, Logi-Bone and Tools | 21       |

| U | 3.1        |                                    | 21       |

|   | 3.2        |                                    | 23       |

|   | 5.2        |                                    | 24       |

|   | 3.3        |                                    | 25       |

|   | 3.4        |                                    | 26       |

|   | 3.5        | · ·                                | 28       |

| 4 | Han        | dwove Duriest                      | 29       |

| 4 |            | 5                                  | 29<br>29 |

|   | 4.1<br>4.2 | g                                  | 29<br>30 |

|   |            |                                    |          |

|   | 4.3        | 6                                  | 32       |

|   |            | 6                                  | 33       |

|   |            | 5                                  | 37       |

|   | 4.4        | $\mathbf{I}$                       | 39       |

|   | 4.5        |                                    | 41       |

|   | 4.6        | I                                  | 42       |

|   |            | e                                  | 42       |

|   |            |                                    | 43       |

|   |            |                                    | 43       |

|   |            |                                    | 44       |

|   |            |                                    | 44       |

|   |            | 4.6.6 SPI                          | 45       |

## CONTENTS

|   |      | 4.6.7 Custom blocks                       | 5  |

|---|------|-------------------------------------------|----|

|   | 4.7  | Conclusion                                | 8  |

| 5 | Proj | ect Configuration and implementation 4    | 9  |

|   | 5.1  | Language                                  | 9  |

|   | 5.2  | Tool                                      | 51 |

|   | 5.3  | APIs                                      | 54 |

|   | 5.4  | Work Flow                                 | 55 |

|   |      | 5.4.1 Complete project                    | 55 |

|   |      | 5.4.2 Complete Project with custom blocks | 57 |

|   | 5.5  | Conclusion                                | 59 |

| 6 | Con  | clusion 6                                 | 61 |

|   | 6.1  | Future work                               | 51 |

# **List of Figures**

| 2.2       CoreConnect Block Diagram       7         2.3       Xilinx Zynq-7000 diagram       9         2.4       Altera Cyclone V SoC block diagram       10         2.5       Altera Arria V SoC block diagram       11         2.6       MartFusion block diagram       12         2.7       SmartFusion 2 block diagram       12         2.8       LatticeMico32 block diagram       12         2.8       LatticeMico32 block diagram       14         2.9       Leon 3 block diagram       14         2.9       Leon 3 block diagram       16         2.10       Armadeus APF51 memory bus       16         2.11       Logi Bone board       17         2.12       Logi Pi board       17         2.13       Logi Stack Overview       18         2.14       Skeleton editor       19         3.1       BeagleBone Black board       22         3.2       Logi Bone board       23         3.3       Skeleton interface with a simple project configuration       24         3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27 <t< th=""><th>2.1</th><th>Virtex-II Pro Generic Architecture Overview</th></t<> | 2.1  | Virtex-II Pro Generic Architecture Overview                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------|

| 2.4       Altera Cyclone V SoC block diagram       10         2.5       Altera Arria V SoC block diagram       11         2.6       SmartFusion block diagram       12         2.7       SmartFusion 2 block diagram       12         2.8       LatticeMico32 block diagram       12         2.8       LatticeMico32 block diagram       14         2.9       Leon 3 block diagram       15         2.10       Armadeus APF51 memory bus       16         2.11       Logi Bone board       17         2.12       Logi Pi board       17         2.13       Logi Stack Overview       18         2.14       Skeleton editor       19         3.1       BeagleBone Black board       22         2.2       Logi Bone board       23         3.3       Skeleton interface with a simple project configuration       24         4.8       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop                                                   | 2.2  | CoreConnect Block Diagram                                            |

| 2.4       Altera Cyclone V SoC block diagram       10         2.5       Altera Arria V SoC block diagram       11         2.6       SmartFusion block diagram       12         2.7       SmartFusion 2 block diagram       12         2.8       LatticeMico32 block diagram       12         2.8       LatticeMico32 block diagram       14         2.9       Leon 3 block diagram       15         2.10       Armadeus APF51 memory bus       16         2.11       Logi Bone board       17         2.12       Logi Pi board       17         2.13       Logi Bone board       17         2.14       Skeleton editor       18         3.1       BeagleBone Black board       22         2.2       Logi Bone board       23         3.3       Skeleton interface with a simple project configuration       24         3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop sync                                                  | 2.3  | Xilinx Zynq-7000 diagram         9                                   |

| 2.5Altera Arria V SoC block diagram112.6SmartFusion block diagram122.7SmartFusion 2 block diagram122.8LatticeMico32 block diagram142.9Leon 3 block diagram152.10Armadeus APF51 memory bus162.11Logi Bone board172.12Logi Pi board172.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration244.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone write signals314.3GPMC and Whisbone block diagram324.5Map of the 16-bit GPMC address space334.6Block RW_RO illustrating the method used to have a parameterizable number of registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port ulknown515.2Error port ulknown525.3Error frequency unknown52<                                                                                                                                                                                              | 2.4  |                                                                      |

| 2.6       SmartFusion block diagram       12         2.7       SmartFusion 2 block diagram       12         2.8       LatticeMico32 block diagram       14         2.9       Leon 3 block diagram       15         2.10       Armadeus APF51 memory bus       16         2.11       Logi Bone board       17         2.12       Logi Pi board       17         2.13       Logi Stack Overview       18         2.14       Skeleton editor       19         3.1       BeagleBone Black board       22         3.2       Logi Bone board       23         3.3       Skeleton interface with a simple project configuration       24         3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone write signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whi                                                  | 2.5  |                                                                      |

| 2.8LatticeMico32 block diagram142.9Leon 3 block diagram152.10Armadeus APF51 memory bus162.11Logi Bone board172.12Logi Pi board172.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration244.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone write signals314.3GPMC to Whisbone block diagram324.5Map of the 16-bit GPMC address space334.6Block W_RO illustrating the method used to have a parameterizable number of registers374.7Block RW_RI with a single register384.8Distribution of the memory address space384.9H-Bridge435.1Error port unknown515.2Error port unknown515.3Error frequency unknown51                                                                                                                                                                                                                                                                                                    | 2.6  |                                                                      |

| 2.8LatticeMico32 block diagram142.9Leon 3 block diagram152.10Armadeus APF51 memory bus162.11Logi Bone board172.12Logi Pi board172.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration244.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone write signals314.3GPMC to Whisbone block diagram324.5Map of the 16-bit GPMC address space334.6Block W_RO illustrating the method used to have a parameterizable number of registers374.7Block RW_RI with a single register384.8Distribution of the memory address space384.9H-Bridge435.1Error port unknown515.2Error port unknown515.3Error frequency unknown51                                                                                                                                                                                                                                                                                                    | 2.7  | SmartFusion 2 block diagram                                          |

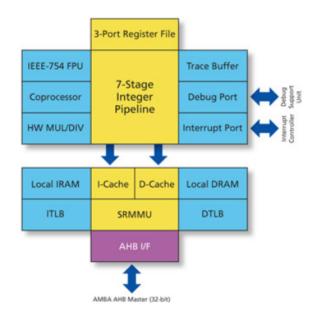

| 2.9Leon 3 block diagram152.10Armadeus APF51 memory bus162.11Logi Bone board172.12Logi Pi board172.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration243.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone read signals314.3GPMC to Whisbone write signals314.4GPMC to Whisbone write signals314.5Map of the 16-bit GPMC address space334.6Block W_RO illustrating the method used to have a parameterizable number of<br>registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                        | 2.8  |                                                                      |

| 2.10Armadeus APF51 memory bus162.11Logi Bone board172.12Logi Pi board172.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration243.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone read signals314.3GPMC to Whisbone write signals314.4GPMC to Whisbone wite signals314.5Map of the 16-bit GPMC dadress space334.6Block W_RO illustrating the method used to have a parameterizable number of<br>registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                  | 2.9  |                                                                      |

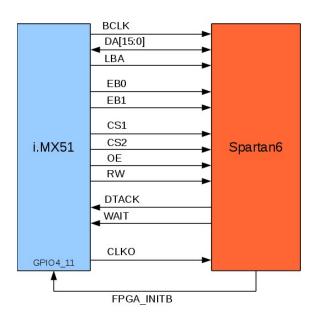

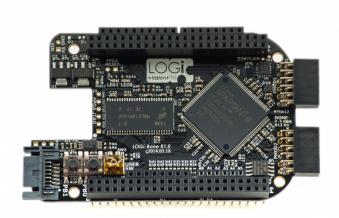

| 2.11Logi Bone board172.12Logi Pi board172.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration243.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone read signals314.3GPMC to Whisbone block diagram324.5Map of the 16-bit GPMC address space334.6Block W_RO illustrating the method used to have a parameterizable number of<br>registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                   | 2.10 |                                                                      |

| 2.12Logi Pi board172.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration243.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone read signals314.3GPMC to Whisbone block diagram324.5Map of the 16-bit GPMC address space334.6Block W_RO illustrating the method used to have a parameterizable number of registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                           | 2.11 |                                                                      |

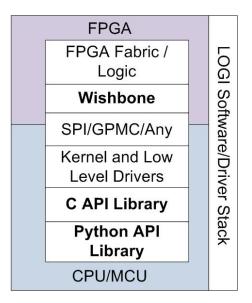

| 2.13Logi Stack Overview182.14Skeleton editor193.1BeagleBone Black board223.2Logi Bone board233.3Skeleton interface with a simple project configuration243.4Blocks and parameters generated253.5Xilinx ISE program263.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone read signals314.3GPMC to Whisbone block diagram324.5Map of the 16-bit GPMC address space334.6Block W_RO illustrating the method used to have a parameterizable number of registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                                                      |

| 3.1       BeagleBone Black board       22         3.2       Logi Bone board       23         3.3       Skeleton interface with a simple project configuration       24         3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC to Whisbone block diagram       32         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3             |      |                                                                      |

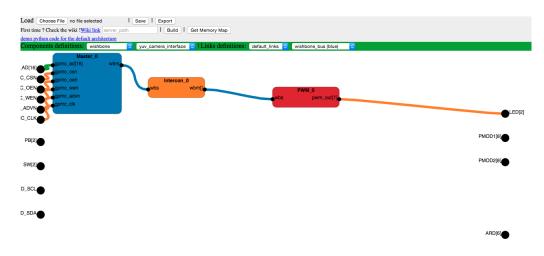

| 3.2       Logi Bone board       23         3.3       Skeleton interface with a simple project configuration       24         3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                       | 2.14 | Skeleton editor                                                      |

| 3.2       Logi Bone board       23         3.3       Skeleton interface with a simple project configuration       24         3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                       |      |                                                                      |

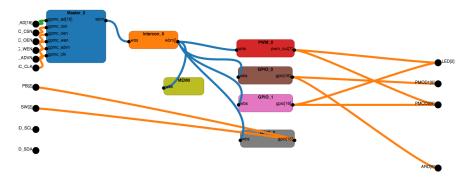

| 3.3       Skeleton interface with a simple project configuration       24         3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                  |      |                                                                      |

| 3.4       Blocks and parameters generated       25         3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error frequency unknown       52         5.3       Error frequency unknown       52                                                                                                                                                      |      |                                                                      |

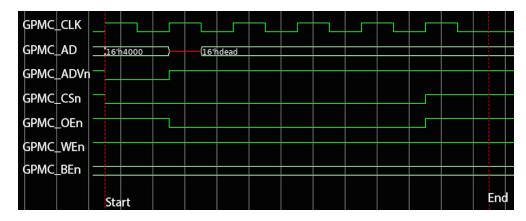

| 3.5       Xilinx ISE program       26         3.6       Read operation in GPMC bus       27         3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                               |      |                                                                      |

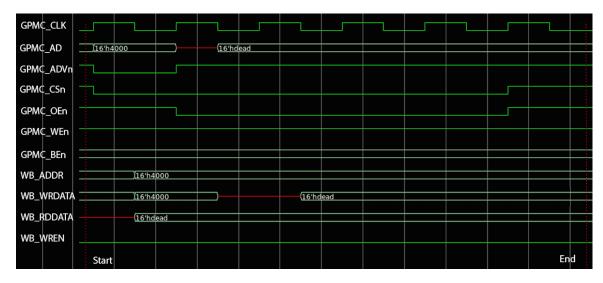

| 3.6Read operation in GPMC bus273.7Write operation in GPMC bus273.8Layers of communication between the BeagleBone Black and the FPGA284.1Two flip-flop synchronizer diagram294.2GPMC and Whisbone read signals314.3GPMC and Whisbone write signals314.4GPMC to Whisbone block diagram324.5Map of the 16-bit GPMC address space334.6Block W_RO illustrating the method used to have a parameterizable number of registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                                      |

| 3.7       Write operation in GPMC bus       27         3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       31         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                                                                                                                                   |      |                                                                      |

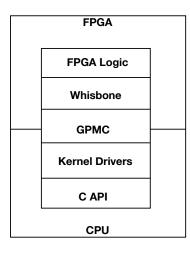

| 3.8       Layers of communication between the BeagleBone Black and the FPGA       28         4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                      |

| 4.1       Two flip-flop synchronizer diagram       29         4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.7  |                                                                      |

| 4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.8  | Layers of communication between the BeagleBone Black and the FPGA 28 |

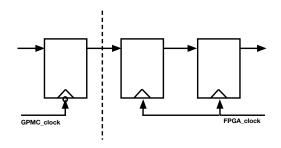

| 4.2       GPMC and Whisbone read signals       31         4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11   | Two flip flop synchronizer diagram                                   |

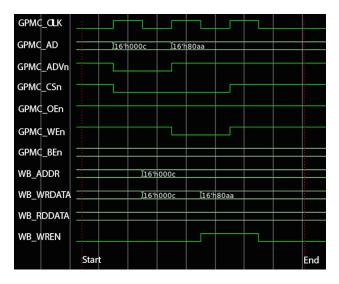

| 4.3       GPMC and Whisbone write signals       31         4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                                                      |

| 4.4       GPMC to Whisbone block diagram       32         4.5       Map of the 16-bit GPMC address space       33         4.6       Block W_RO illustrating the method used to have a parameterizable number of registers       37         4.7       Block RW_RI with a single register       38         4.8       Distribution of the memory address space       39         4.9       H-Bridge       43         5.1       Error port unknown       51         5.2       Error port already in use       52         5.3       Error frequency unknown       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                      |

| <ul> <li>4.5 Map of the 16-bit GPMC address space</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                                      |

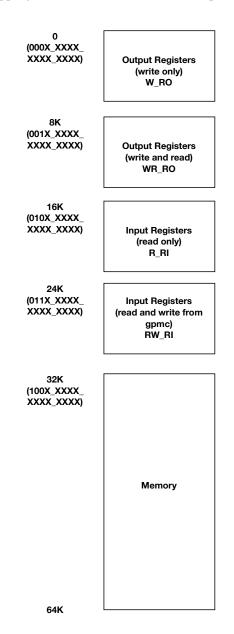

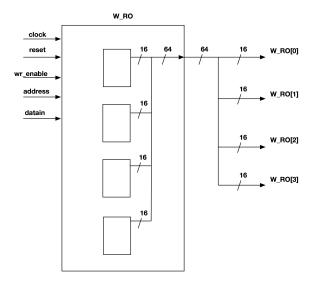

| <ul> <li>4.6 Block W_RO illustrating the method used to have a parameterizable number of registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                                                                      |

| registers374.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                                                      |

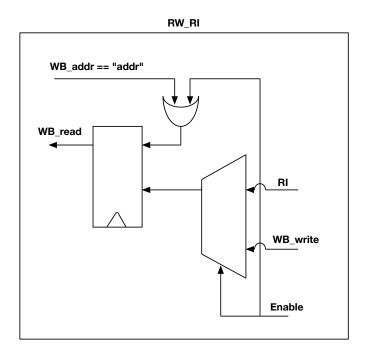

| 4.7Block RW_RI with a single register384.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.0  | - 6 1                                                                |

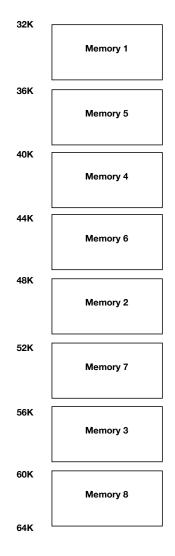

| 4.8Distribution of the memory address space394.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47   |                                                                      |

| 4.9H-Bridge435.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                      |

| 5.1Error port unknown515.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                                                      |

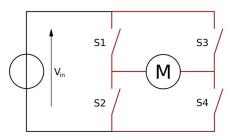

| 5.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.9  | H-Bridge                                                             |

| 5.2Error port already in use525.3Error frequency unknown52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.1  | Error port unknown                                                   |

| 5.3 Error frequency unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | *                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 1 5                                                                  |

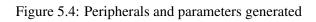

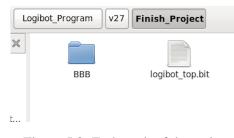

| 3.4 Peripherals and parameters generated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.4  | Peripherals and parameters generated                                 |

| 5.5  | Include file, used to interact with the peripherals | 54 |

|------|-----------------------------------------------------|----|

| 5.6  | Block.txt file with the peripherals written         | 55 |

| 5.7  | ./start script running in terminal                  | 56 |

| 5.8  | End result of the script                            | 56 |

| 5.9  | Files in the BeagleBone Black                       | 56 |

| 5.10 | Application for running in the BeagleBone Black     | 57 |

|      | Blocks.txt file, with custom block                  | 57 |

| 5.12 | ./start_custom script running in terminal           | 58 |

| 5.13 | Adding the template to the logibot_top.v file       | 58 |

| 5.14 | Generating the programming file                     | 59 |

# **List of Tables**

| 2.1  | Characteristics of high end Virtex boards with PowerPC                       |

|------|------------------------------------------------------------------------------|

| 2.2  | Characteristics of low and high end SoC's of Zynq family                     |

| 2.3  | Features for the AXI4                                                        |

| 2.4  | Principal characteristics of Altera Cyclone V and Arriva V high-end SoCs 10  |

| 2.5  | Principal characteristics of Microsemi SmartFusion and SmartFusion2 high-end |

|      | SoCs                                                                         |

| 2.6  | Principal characteristics of Armadeus boards                                 |

| 2.7  | Principal characteristics of Xilinx Spartan 6 LX9                            |

| 2.8  | Principal characteristics of Beaglebone Black and Raspberry Pi               |

| 4.1  | Distribution and size of memories depending on his quantity                  |

| 4.2  | Parameters and compiler directives for registers and memories                |

| 4.3  | Digital I/O FPGA occupation                                                  |

| 4.4  | PWM Unidirectional FPGA occupation    43                                     |

| 4.5  | PWM H-Bridge FPGA occupation    44                                           |

| 4.6  | UART FPGA occupation                                                         |

| 4.7  | Servo FPGA occupation                                                        |

| 4.8  | SPI FPGA occupation                                                          |

| 4.9  | Parameters for custom_r blocks                                               |

| 4.10 | Parameters for custom_m blocks                                               |

| 5.1  | Language and parameters for generate peripheralas c                          |

# Abbreviations

| AMBA  | Advanced Microcontroller Bus Architecture   |

|-------|---------------------------------------------|

| API   | Application Programming Interface           |

| APU   | Auxiliary Processor Unit                    |

| ARM   | Advanced RISC Machine                       |

| ASIC  | Application-Specific Integrated Circuit     |

| AXI   | Advanced Extensible Interface               |

| BBB   | BeagleBone Black                            |

| CPU   | Central Processing Unit                     |

| FPGA  | Field-Programmable Gate Array               |

| GPIO  | General Purpose Input/Output                |

| GPMC  | General Purpose Memory Controller           |

| HDL   | Hardware Description Language               |

| I/O   | Input/Output                                |

| I2C   | Inter-Integrated Circuit                    |

| IP    | Intellectual Property                       |

| LUT   | Look Up Table                               |

| RISC  | Reduced Instruction Set Computer            |

| SDRAM | Synchronous dynamic random access memory    |

| SoC   | System on Chip                              |

| SPI   | Serial Peripheral Interface                 |

| UART  | Universal Asynchronous Receiver/Transmitter |

# **Chapter 1**

# Introduction

The high rate of advances in the embedded computing, electronics, communications and battery technologies has been a great motivation for the growth of small, affordable but powerful and so-phisticated robotic systems. This has been noticed mostly in the field of low cost remote controlled autonomous flying drones increasingly used in several fields like photography, filmmaking, deliveries, surveillance and pure entertainment. The needs for highly integrated sensors for providing the vehicle position (GPS, IMU's and magnetometers), the integration of this with the system computer and control and, at the same time, maintaining low energy consumption is of utmost importance.

Other domain were autonomous robotics systems are gaining importance is in the access to marine environment, both underwater and at the surface. This increase of importance results from the need to exploit a diversity of valuable ocean resources and monitor the state of the planet, promoting the development of several projects concerning autonomous and remotely operated marine vehicles and its equipment like sensors, mechanical manipulators and sampling devices.

The marine environment presents several difficulties to developers. For instance, the radio waves suffer a drastic attenuation in water and in practice the communication underwater through radio frequency signals is only use for very short ranges. The best way to exchange information underwater is using sound waves. However the slow speed of propagation and the complex mechanisms associated to the underwater acoustic channel presents a series of difficulties for the development of autonomous robotics systems for underwater environment.

Besides, the problems previously mentioned to the communication and navigation in the underwater environment, the tasks that can be accomplished in marine applications have fostered the development and invention of a diversity of underwater and surface marine vehicles.

Usually marine robots have a conventional CPU running software on some kind of operating system that performs the control, navigation tasks and communication. To deal with the electronic part like sensors, communication or actuators, the computing system has to implement appropriate interfaces. These interfaces depend on the actual vehicle configuration and mission to accomplish, and in order to provide adaptability the electronics and the computing system should be capable of providing flexibility and easy reconfiguration capability.

Although todays embedded computers and microcontrollers already include the most common interfaces (e.g. I2C, SPI, UART, PWM) this mixed interface is fixed and cannot be easily expanded to fulfil the system needs. As consequence of this, for adding new interfaces there is a need usually requires attaching physical boards, that naturally impact on time of development and debug, system size and power consumption.

Attaching a FPGA (Field-Programmable Gate Array)[1] to a conventional CPU is an effective solution to overcome the problems referred above. In fact, all of the electronics related to the interfacing with the outside world can be moved into the FPGA, taking advantage of the reconfigurability of these devices to implement customized interface mechanisms, including specialized pre-processors for data acquired from external devices to alleviate the load of the main processor (e.g. digital filters, FFT calculators, etc.) and also implement custom computing blocks to accelerate critical parts of the software applications running in the main processor.

This solution has been adopted in various products including FPGA-based devices and singleboard embedded computers as presented in chapter 2.

## **1.1 Problem definition**

Although FPGA devices have many advantages for the type of work described above most of the developers don't use it because this approach requires digital design skills and detailed knowledge of FPGA technology. In fact, system developers are more proficient on software programming than in digital hardware design, in spite of the more and more user friendly and easy to use FPGA design tools.

The objective of this work is to develop an easy to use reconfigurable system, based on an embedded computer and a FPGA to implement highly customized interfaces with external devices, including dedicated pre-processors to alleviate the load of the main processor (e.g. digital filters or FFT calculators) and also specialized computing modules to accelerate critical parts of the software applications running on main processor.

From the FPGA point of view, this work will develop a software tool to automatically generate a complete HDL design for the FPGA device, based on a high-level description of the set of interfacing blocks and protocols configured for the project, from a library of commonly used interfaces in robotic systems (e.g. UART, PWM, SPI, etc). The objective is to hide as most as possible from the system developer all the details of the digital system that implements the external hardware interface. The tool will also allow the integration of other custom designed blocks developed by the user and support the inclusion of new modules in the FPGA design framework.

In addition, the tool will also create the software application programming interfaces (API) to facilitate the software development and the communication with the interfacing resources implemented in the FPGA.

The hardware system to be used is a commercial popular low cost embedded computer (the BeagleBone Black) and an FPGA-based daughter board (Logi-Bone) built on the XILINX Spartan6 FPGA.

## 1.2 Thesis organization

This report is divided in 6 chapters. Chapter 1 address the thesis problem, context and motivation. Chapter 2 presents the state of art divided in 2 parts, first the CPU and FPGA interaction products and second the tools provided to make a project in those platforms. Chapter 3 describes the hardware used, as well as the tools used in this project. Chapter 4 and 5 talk about this thesis work, the first the hardware development part and the second the software developed. Finally, chapter 6 presents the conclusions and future work for this project.

Introduction

# **Chapter 2**

# State of art

This chapter presents technologies and tools for hardware design. The chapter is divided in two main parts. Section 2.1 presents the products that involve a FPGA and a CPU organized in three different categories: CPU and FPGA in a SoC, FPGA integrating one or more softcore CPU and boards with a discrete CPU and FPGA chips. Section 2.2 presents the development tools used to implement and to work with some of the products mentioned in the first section.

## 2.1 CPU-FPGA embedded platform

As mentioned in chapter 1 this works aims to interface a FPGA and a CPU or embedded processor. This section presents some technologies that fit in this category. The section is divided in three parts:

- CPU and FPGA in a SoC

- FPGA and Softcore CPU

- Discrete CPU and discrete FPGA

## 2.1.1 CPU and FPGA in a SoC

Semiconductor devices with hardened CPU subsystem integrated in FPGA offer a whole world of options for system designs. This type of devices came to help and optimize the integration of hard CPUs and FPGAs, making a single SoC with powerful performance and low power consumption.

Some of the best known SoCs with hard CPU and FPGA are the Xilinx Virtex II, 4 and 5 resulting in a partnership between Xilinx and IBM, more recent Xilinx change their CPUs to ARM processors in the Zynq family. Altera also provide their own SoCs, the Cyclone V and Arria V integrating an ARM just like the Zynq, Microsemi also enter the race for SoCs with hard CPU and FPGA launching the Smartfusion series.

## 2.1.1.1 Xilinx Virtex with PowerPC

Introduced in 2002[2], the Xilinx Virtex-II Pro was the first FPGA SoC developed by Xilinx to include a physical processor core, in this case an IBM PowerPC 405[3, 4, 5] running at 300MHz. All 700 I/O ports of the processor can be accessed by the FPGA[2]. This is done by immersing the processor in the first four layers of metal and having 5 layers of routing above, allowing to access the entire CPU from the FPGA fabric.

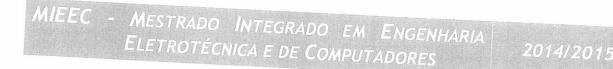

Figure 2.1: Virtex-II Pro Generic Architecture Overview[6]

Figure 2.1 presents an overview of the Virtex-II Pro architecture. As seen in the figure, the CPU is embedded in the FPGA fabric (CLB), and the connection to the FPGA is done through an IBM Core-Connect on-chip bus capable of running at 133MHz. This bus can be seen in detail in figure 2.2.

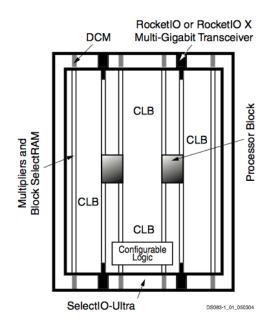

The CoreConnect bus is composed by:

1. Processor Local Bus (PLB)

- 2. On-Chip Peripheral Bus (OPB)

- 3. Device Control Register (DCR)

Figure 2.2: CoreConnect Block Diagram[6]

The high-performance peripherals are connected to the high-bandwidth and low-latency PLB while slower peripheral connect to OPB to reduce the traffic on the PLB, and improve the overall performance[6].

Later, in 2005, Xilinx began to ship its new hybrid CPU and FPGA SoC, the Xilinx Virtex-4 FX[7] with a new PowerPC 405 running up to 450MHz. In this case the interface between the CPU and FPGA is through APU (Auxiliary Processor Unit) capable of: [8]

- Running at different clock rates

- Supporting autonomous instructions: no pipeline stalls

- 32-bit instruction and 64-bit data

- 4-cycle cache line transfer

Virtex-5 FXT launched in 2008[9] with a new PowerPC 440 at 550MHz[10], was the last FPGA with a PowerPC CPU launched by Xilinx. The communication between the FPGA and CPU like in the Virtex-4 FX is done through an APU with the difference of 128-bit wide pipelined APU load/store capability[10].

Table 2.1 presents the characteristics of high-end Virtex devices mentioned above.

Table 2.1: Characteristics of high end Virtex boards with PowerPC [6, 8, 10]

| Xilinx Virtex Pro         | Virtex-II Pro     | Virtex-4 FX   | Virtex-5 FXT             |

|---------------------------|-------------------|---------------|--------------------------|

| PowerPC Processor Blocks  | 2                 | 2             | 2                        |

| Maximum Frequency         | 300MHz            | 450MHz        | 550MHz                   |

| L1 Cache                  | 16 KB Instruction |               | 32 KB Instruction        |

|                           | 16 KB Data j      | per processor | 32 KB Data per processor |

| Programmable Logic Cells  | 99,216            | 142,128       | $30,720^{1}$             |

| Extensible Block RAM (KB) | 7,992             | 9,936         | 16,416                   |

<sup>1</sup>Virtex-5 FPGA slices are organized differently from previous generations. Each Virtex-5 FPGA slice

contains four LUTs and four flip-flops (previously it was two LUTs and two flip-flops.)

## 2.1.1.2 Xilinx Zynq family

Xilinx Zynq[11] is the new generation of hybrid CPU and FPGA developed by Xilinx. The products in this family use an ARM[12] instead of a PowerPC, the ARM power and low consumption make it a better choice. The FPGA is equivalent to a Xilinx Artix-7[13] or a Xilinx Kintex-7[14], depending of the models, becoming an excellent example of a FPGA and CPU SoC integration. Announced in 2011[15, 16] Zynq become the first FPGA and Dual ARM CPU on a single SoC[17, 15] with the first versions launched in 2012[18] in a 28nm technology.

The Zynq family SoC's has a Dual CPU ARM A9 running from 667Mhz to 1GHz and a considerable number of fixed peripherals like, 2xUART, 2xCAN, 2xI2C, 2xSPI, 2xEthernet ports, 2xUSB ports and 2xSD card port. Unlike the CPU that only has one version running with different clock speeds, there are two versions of the FPGA, Artix-7 and Kintex-7. Table 2.2 resumes the characteristics of the low and high model of Zynq family.

| Xilinx Zynq                 | Z-7010                    | Z-7100                |  |

|-----------------------------|---------------------------|-----------------------|--|

| Processor Core              | Dual ARM Cortex-A9 MPCore |                       |  |

| Maximum Frequency           | 866 MHz                   | Up to 1 GHz           |  |

| L1 Cache                    | 32 KB Instruction, 32     | KB Data per processor |  |

| FPGA                        | Artix-7 FPGA              | Kintex-7 FPGA         |  |

| Programmable Logic Cells    | 28K Logic Cells           | 444K Logic Cells      |  |

| Look-Up Tables              | 17,600                    | 277,400               |  |

| Flip-Flops                  | 35,200                    | 554,800               |  |

| Extensible Block RAM        | 240 KB                    | 3,020 KB              |  |

| Programmable DSP Slices     | 80                        | 2,020                 |  |

| Peak DSP Performance        | 100 GMACs                 | 2,622 GMACs           |  |

| Processing System User I/Os | 32                        | 54                    |  |

Table 2.2: Characteristics of low and high end SoC's of Zynq family

One of the advantages of this device, besides its superior characteristics is the possibility of being utilized without the need to program the FPGA part allowing using only the CPU, unlike older families with embedded CPU[16].

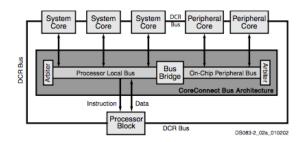

Figure 2.3: Xilinx Zynq-7000 diagram[11]

Figure 2.3 shows the main blocks of Zynq, one of the interesting parts for this work is the connection between the FPGA and CPU, done through a high performance AXI4 and a general purpose AXI4 connection[19]. The AXI connection is part of AMBA protocol, a open standard for functional blocks in a SoC developed by ARM. AXI4 is divided in 3 parts, the AXI4 memory map, AXI4 stream and AXI4 lite with the features presented in table 2.3.

Table 2.3: Features for the AXI4[20]

| Interface       | Features                                                       |

|-----------------|----------------------------------------------------------------|

| AXI4 Memory Map | Traditional Address/Data Burst (single address, multiple data) |

| AXI4 Streaming  | Data-Only, Burst                                               |

| AXI4 Lite       | Traditional Address (single address, single data)              |

Although the AXI4 lite supports 32-bit and 64-bit data, the Xilinx IP only supports 32-bit. The AXI4 memory map and AXI4 streaming supports burst data being that the first is capable of burst up to 256 data beats<sup>1</sup> and the second don't have a burst limit but only works from master to slave.

<sup>&</sup>lt;sup>1</sup>A 'beat' is an individual data transfer within an AXI burst[20]

### 2.1.1.3 Altera Cyclone V and Arria V

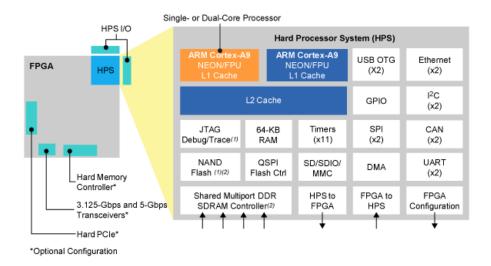

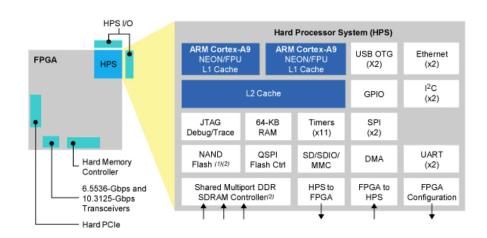

In the race for the hybrid CPU and FPGA SoC market, Altera[21], another FPGA manufacture, release the Cyclone V[22] and Arria V[23]. Launched in second half of 2012, using a technology of 28nm they were the Altera response to the Xilinx Zynq family. Both Cyclone V and Arria V have a Dual ARM Cortex-9 running at 925MHz and 1.05GHz respectively, 64KB of scratch RAM, 2xEthernet port, 2xUSB, 4xI2C controllers, 2xUART and 2xSPI.

Table 2.4 presents the principal characteristics of these two Altera SoCs and figure 2.4 and 2.5 shows an overview of the SoC's typology.

| Altera            | Cyclone V 5CSTD6                            | Arriva V 5ASTD5 |

|-------------------|---------------------------------------------|-----------------|

| Processor Core    | Dual ARM Cortex-A9                          |                 |

| Maximum Frequency | 915MHz                                      | 1.05GHz         |

| L1 Cache          | 32 KB Instruction, 32 KB Data per processor |                 |

| Logic Elements    | 110K                                        | 462K            |

| M10K memory       | 5,570Kb                                     | 22,820Kb        |

| Maximum FPGA I/Os | 288                                         | 504             |

| Maximum CPU I/Os  | 181                                         | 208             |

Table 2.4: Principal characteristics of Altera Cyclone V and Arriva V high-end SoCs [24, 25]

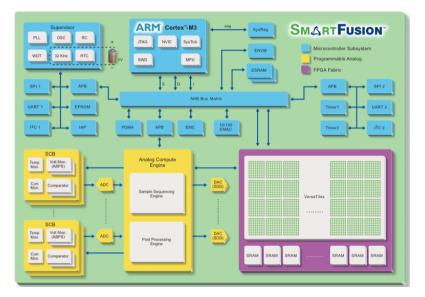

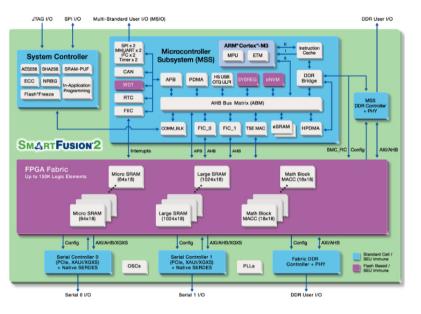

Figure 2.4: Altera Cyclone V SoC block diagram[22]