FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Development of a Dynamically Extensible SpiNNaker Chip Computing Module

Rui Emanuel Gonçalves Calado Araújo

Master in Electrical and Computers Engineering

Supervisor: Jörg Conradt Co-Supervisor: Diamantino Freitas

January 27, 2014

# Resumo

O projeto SpiNNaker desenvolveu uma arquitetura que é capaz de criar um sistema com mais de um milhão de núcleos, com o objetivo de simular mais de um bilhão de neurónios em tempo real biológico. O núcleo deste sistema é o "chip" SpiNNaker, um multiprocessador System-on-Chip com um elevado nível de interligação entre as suas unidades de processamento. Apesar de ser uma plataforma de computação com muito potencial, até para aplicações genéricas, atualmente é apenas disponibilizada em configurações fixas e requer uma estação de trabalho, como uma máquina tipo "desktop" ou "laptop" conectada através de uma conexão Ethernet, para a sua inicialização e receber o programa e os dados a processar.

No sentido de tirar proveito das capacidades do "chip" SpiNNaker noutras áreas, como por exemplo, na área da robótica, nomeadamente no caso de robots voadores ou de tamanho pequeno, uma nova solução de hardware com software configurável tem de ser projetada de forma a poder selecionar granularmente a quantidade do poder de processamento. Estas novas capacidades permitem que a arquitetura SpiNNaker possa ser utilizada em mais aplicações para além daquelas para que foi originalmente projetada.

Esta dissertação apresenta um módulo de computação dinamicamente extensível baseado em "chips" SpiNNaker com a finalidade de ultrapassar as limitações supracitadas das máquinas SpiN-Naker atualmente disponíveis. Esta solução consiste numa única placa com um microcontrolador, que emula um "chip" SpiNNaker com uma ligação Ethernet, acessível através de uma porta série e com um "chip" SpiNNaker. Além disso, um programa de computador multi-plataforma baseado em Java disfarça esta solução personalizada permitindo que este novo sistema seja retrocompatível com todas as ferramentas existentes para as máquinas convencionais.

Para desenvolver esta nova solução foi necessário um estudo profundo e detalhado da arquitetura e do funcionamento interno do "chip" SpiNNaker. Com o conhecimento adquirido a partir desta análise aprofundada, foi possível construir uma placa com um microcontrolador e um "chip" SpiNNaker conectados através dum protocolo interno da arquitetura SpiNNaker. Após a criação da placa, desenvolveu-se o software para controlar o microcontrolador e uma aplicação para manter a retrocompatibilidade com sistemas padrão. Para demonstrar as novas capacidades desta plataforma noutras aplicações para além de redes neuronais, desenvolveu-se uma simulação do movimento dum bando de pássaros.

A solução apresentada permite a utilização de dezenas de núcleos ARM eficientes num pacote de reduzida dimensão, sendo desta forma adequada para ser utilizada em pequenos robots e assim implementar algoritmos avançados que exijam poder computacional paralelo.

ii

# Abstract

The SpiNNaker project has created an architecture that is capable of scaling up to a system with more than a million embedded cores in order to simulate more than one billion spiking neurons in biological real time. The heart of this system is the SpiNNaker chip, a Multi-Processor System-on-Chip with a high level of interconnectivity between its processing units. Although it is a very powerful computing platform, even for non-neural application, it is currently only available in fixed configurations and it requires a workstation, usually a desktop or a laptop connected through an Ethernet connection, to be initialised and to receive the data to be processed.

Therefore if one wishes to take advantage of the capabilities of the SpiNNaker chip in other fields, as for example the robotics field specially in the case of small or flying robots, a new hardware solution with custom software must be built where the amount of processing power can be granularly selected. This new capability allows the SpiNNaker architecture to be used in more applications than it was originally designed for.

This thesis presents a Dynamically Extensible SpiNNaker Chip Computing Module to improve on the limitations of the currently available SpiNNaker machines. This approach is a single board with a microcontroller which emulates an Ethernet connected SpiNNaker chip accessible through a serial port and a single SpiNNaker chip placed together. Additionally it features a cross-platform Java based computer program that disguises this custom solution allowing this new system to be backwards compatible with all the existing tools for the standard machines.

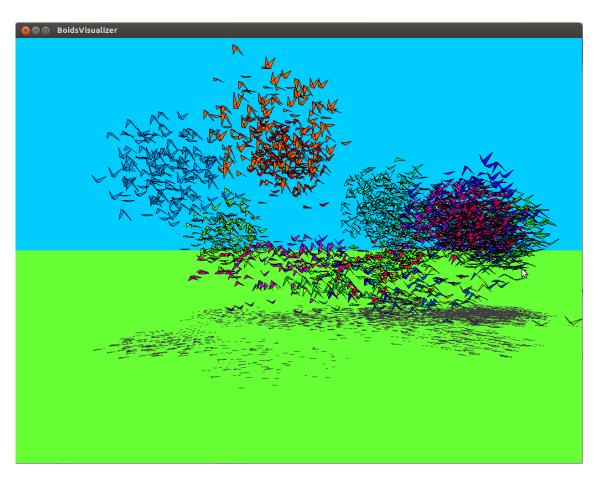

In order to develop this new solution, a very deep and detailed study of the inner workings of the SpiNNaker chip was required. With the acquired knowledge from this thorough analysis, it was then possible to build a custom board with a microcontroller and the SpiNNaker connected through a internal protocol from the SpiNNaker architecture and develop the software to drive the microcontroller and an application to emulate a standard system for the SpiNNaker tools. A non-neural application, the simulation of the movement of a flock of birds, was developed to demonstrate the general purpose capabilities that this new platform has.

The presented solution allows the deployment of dozens of power efficient ARM cores available in a very small package suitable to be used in small robots which makes it possible to implement advanced algorithms that require truly parallel computational power. iv

# Acknowledgments

I wish to thank, first and foremost, to Professor Jörg Conradt who continuously supported and encouraged me, besides the technical advice essential for the development of this work. I am also thankful to my co-supervisor Professor Diamantino Freitas for his availability, support and criticism. Besides my supervisors, I would like to thank Nicolai Waniek and Christian Denk for their precious suggestions and feedback.

This thesis would not have been possible without the precious help from Steve Temple, Luis Plana and Francesco Gallupi from the University of Manchester who provided essential guidance while studying the SpiNNaker system.

I thank my fellow student, Tobias Brennich, whose help in the assembly of the multiple testing and final boards proved to be invaluable.

I owe my deepest gratitude to my family, especially my parents, Rui and Manuela, and my siblings, Mónica, Beatriz and Francisco, for their unconditional love and support.

I reserve a special thank you, to my soul mate, Ângela Igreja for all your love, affection, encouragement, motivation, support and availability, along this path. I would also like to thank all of my friends, especially to Ricardo Castro, for all their encouragement and support.

Rui Araújo

vi

"If you are thinking of the brain as a computer, the neuron is the transistor."

Carl Schoonover

viii

# Contents

| 1 | Intro | oduction 1                                            |

|---|-------|-------------------------------------------------------|

|   | 1.1   | Context                                               |

|   | 1.2   | Motivation                                            |

|   | 1.3   | Goals                                                 |

|   | 1.4   | Methodology                                           |

|   | 1.5   | Main Results                                          |

|   | 1.6   | Related Works   4                                     |

|   | 1.7   | Document Structure   6                                |

| 2 | The   | SpiNNaker System 7                                    |

|   | 2.1   | Architecture                                          |

|   |       | 2.1.1 Inter-chip communication                        |

|   |       | 2.1.2 SDP packets                                     |

|   |       | 2.1.3 SpiNNaker machines                              |

|   | 2.2   | Application Loading                                   |

|   |       | 2.2.1 Boot sequence                                   |

|   |       | 2.2.2 Application Load and Execute (APLX) File Format |

|   |       | 2.2.3 SpiNNaker Control & Monitor Program (SC&MP)     |

|   |       | 2.2.4 SpiNNaker Application Runtime Kernel (SARK)     |

|   |       | 2.2.5 Toolchain                                       |

|   | 2.3   | Summary                                               |

| 3 | SpiN  | Naker Chip Computing Module 41                        |

|   | 3.1   | General Architecture                                  |

|   | 3.2   | Hardware                                              |

|   |       | 3.2.1 Components Selection                            |

|   |       | 3.2.2 Power Dissipation                               |

|   |       | 3.2.3 Layout Concerns                                 |

|   |       | 3.2.4 PCB Test Board                                  |

|   |       | 3.2.5 PCB Final Board                                 |

|   |       | 3.2.6 SpiNNaker Extension Board                       |

|   | 3.3   | Microcontroller Firmware                              |

|   |       | 3.3.1 M0 Core                                         |

|   |       | 3.3.2 M4 Core                                         |

|   | 3.4   | Workstation Application   57                          |

|   | 2.1   | 3.4.1 User Interface                                  |

|   |       | 3.4.2         Wrapper Protocol         60             |

|   | 3.5   | Evaluation 62                                         |

|    | 3.6         | Summary 63                            |

|----|-------------|---------------------------------------|

| 4  | Case        | e Study 65                            |

|    | 4.1         | Boids Model                           |

|    | 4.2         | General architecture                  |

|    |             | 4.2.1 SpiNNaker implementation        |

|    |             | 4.2.2 Computer Visualiser             |

|    | 4.3         | Evaluation                            |

|    | 4.4         | Summary                               |

| 5  | Con         | clusions and Future Work 71           |

|    | 5.1         | Summary 71                            |

|    | 5.2         | Difficulties                          |

|    | 5.3         | Future Work                           |

|    |             | 5.3.1 PCB Layout                      |

|    |             | 5.3.2 Full Workstation Independence   |

| A  | Deve        | eloped Hardware 73                    |

|    | A.1         | Test Board                            |

|    | A.2         | Final Board                           |

|    | A.3         | SpiNNaker Extension Board    73       |

| B  | SDP         | over P2P Packets 89                   |

|    | <b>B</b> .1 | Payload of the different packets used |

| С  | Sour        | rce code 93                           |

|    | C.1         | Microcontroller Firmware 93           |

|    | C.2         | Workstation application               |

|    | C.3         | Boids Simulation                      |

| D  | SAR         | K Source code and API 95              |

|    | D.1         | SARK API                              |

| Re | feren       | ces 99                                |

Х

# **List of Figures**

| 1.1  | Work Methodology: phases and respective research methods                        |

|------|---------------------------------------------------------------------------------|

| 2.1  | Block diagram of the SpiNNaker chip                                             |

| 2.2  | Block diagram of the ARM928 core                                                |

| 2.3  | Emergency routing                                                               |

| 2.4  | The 4 different SpiNNaker Packets                                               |

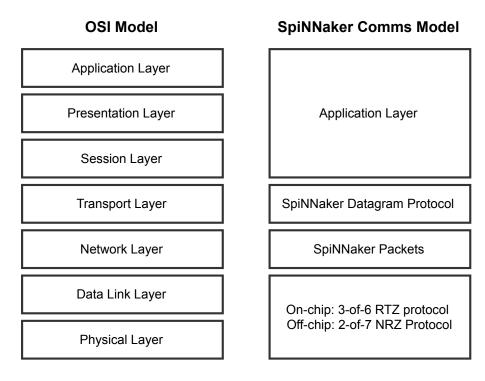

| 2.5  | SpiNNaker Communications model                                                  |

| 2.6  | SDP packet header                                                               |

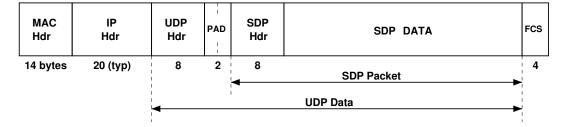

| 2.7  | SDP packet embedded within a UDP packet                                         |

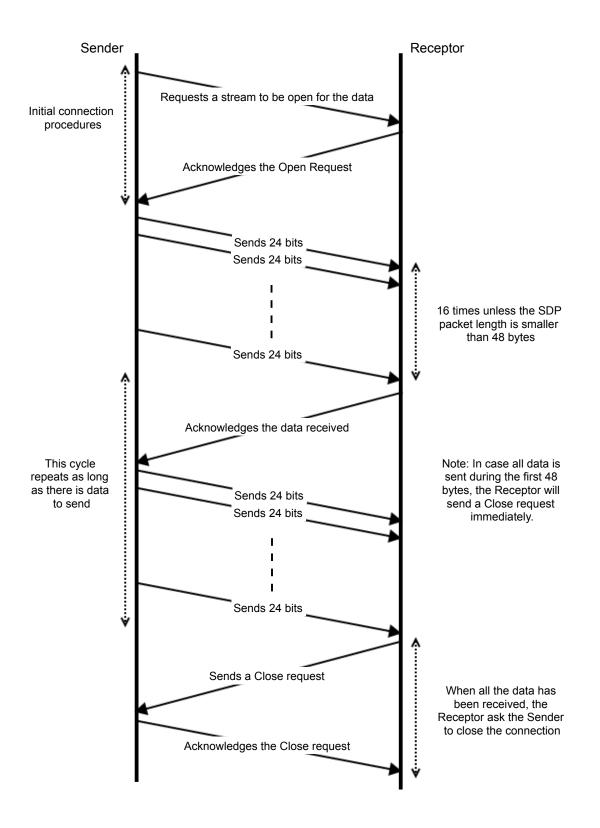

| 2.8  | SDP over P2P protocol                                                           |

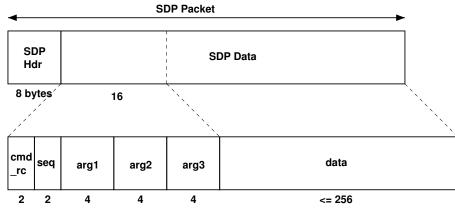

| 2.9  | SCP packet                                                                      |

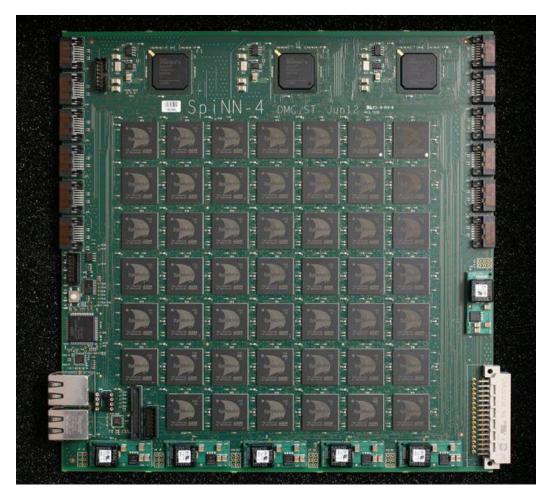

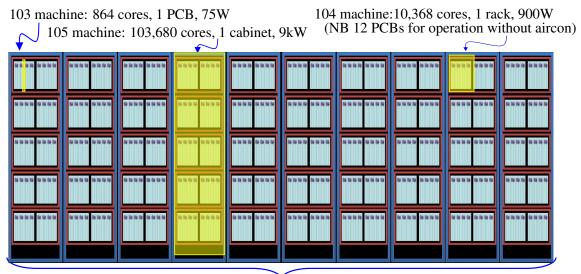

| 2.10 | 102 Machine                                                                     |

| 2.11 | 103 Machine                                                                     |

| 2.12 | SpiNNaker Machines                                                              |

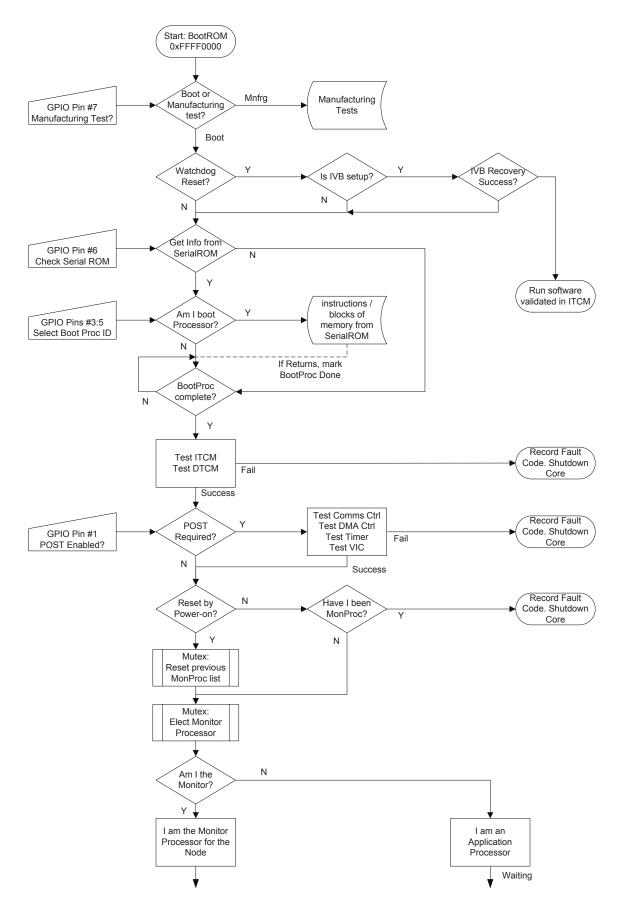

| 2.13 | Node-Boot process until the selection of the Monitor processor                  |

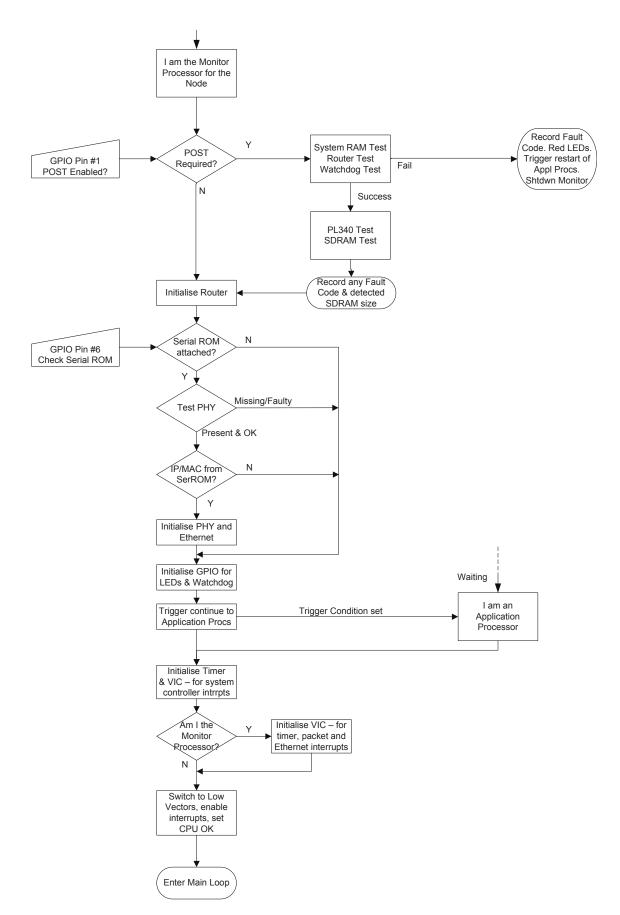

| 2.12 | Node-Boot process after the selection of the Monitor processor                  |

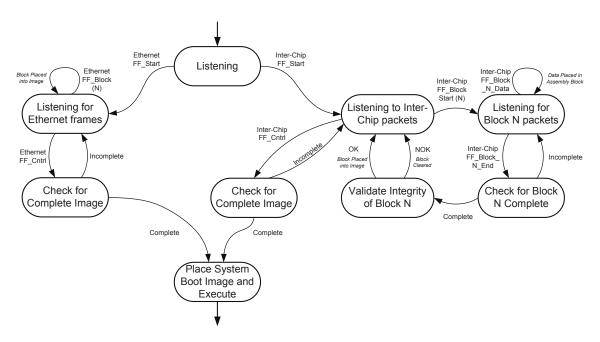

| 2.13 | State machine for the reception of the System-Boot image                        |

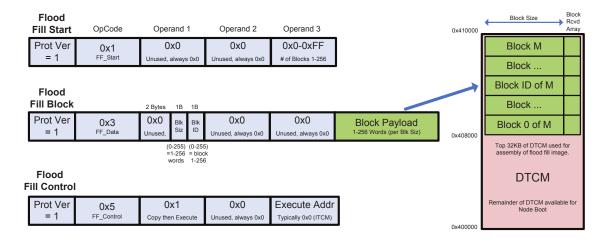

| 2.14 | Packet scheme used by the Host System to push the second stage image to a SpiN- |

|      | Naker chip                                                                      |

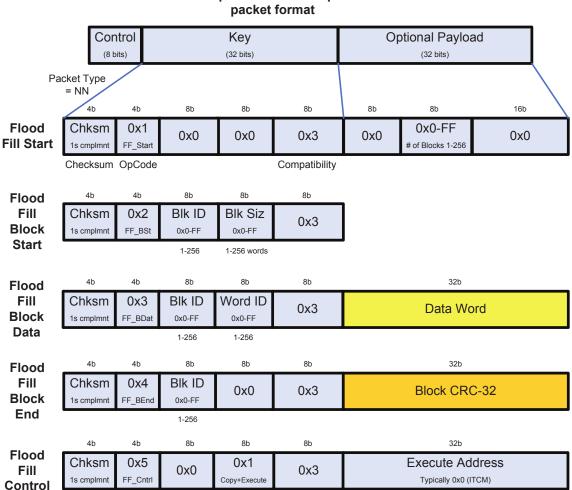

| 2.15 | Packet scheme used by the SpiNNaker chip to push the second stage image to a    |

|      | neighbour chip                                                                  |

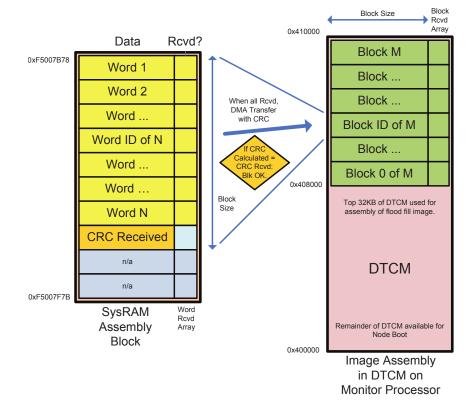

| 2.16 | Word array for a Flood-Fill Block.    33                                        |

| 2.17 | Typical APLX file structure                                                     |

|      | SpiNNaker programming framework                                                 |

| 2.19 | SpiNNaker neural networks simulation development route                          |

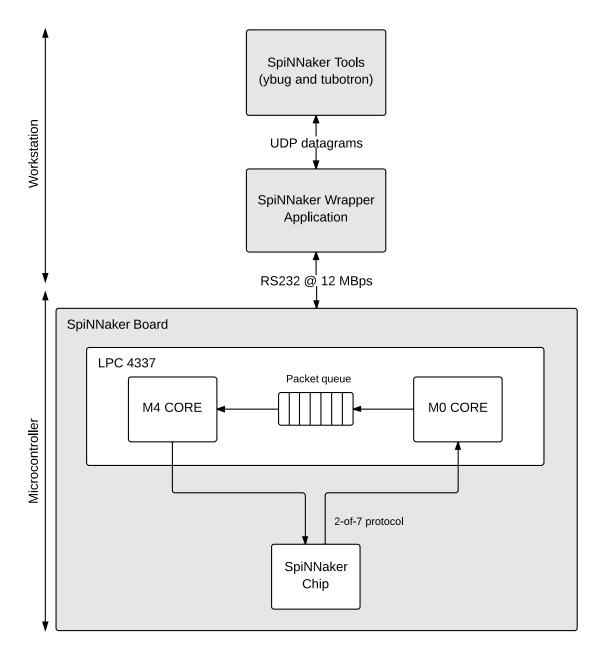

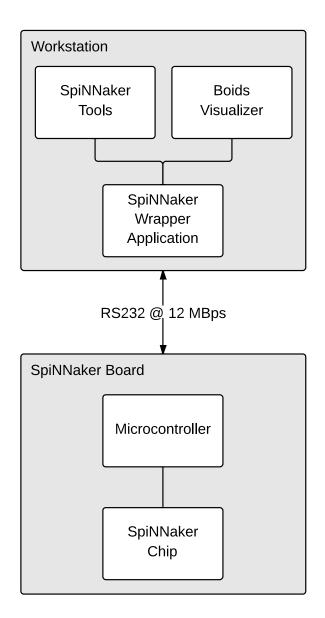

| 3.1  | General Architecture of the developed solution                                  |

| 3.2  | Possible connection between the microcontroller and the SpiNNaker chip 43       |

| 3.3  | AutoBGA user interface for the parameter configuration.                         |

| 3.4  | PCB Test Board                                                                  |

| 3.5  | The SpiNNaker Computing Module.   49                                            |

| 3.6  | Microcontroller Firmware Architecture                                           |

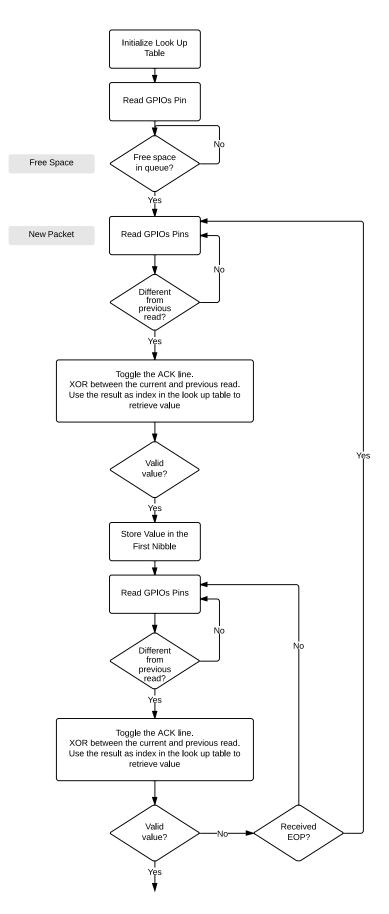

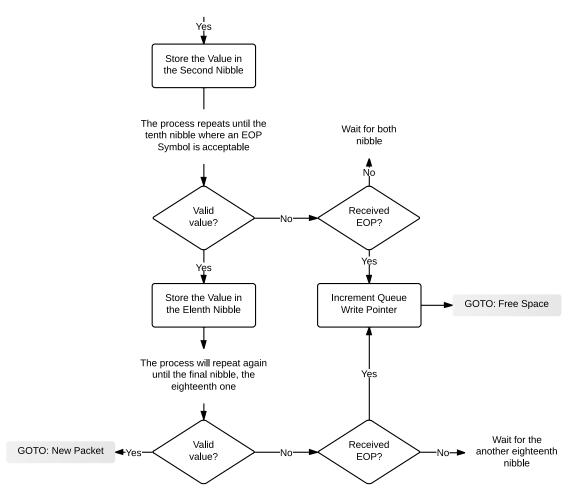

| 3.7  | Packet Input Reading Algorithm                                                  |

| 3.6  | Packet Input Reading Algorithm                                                  |

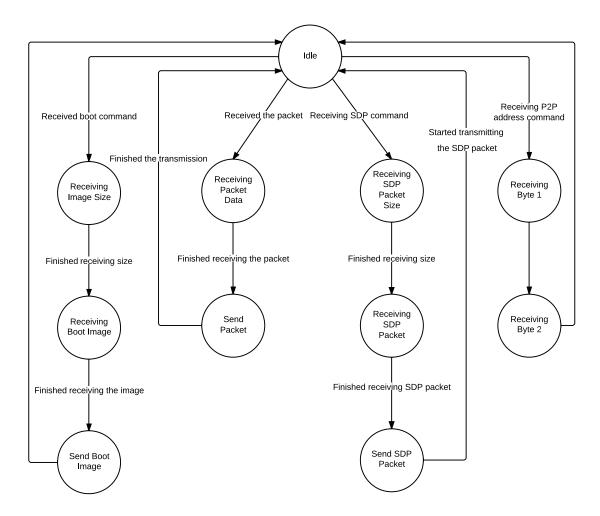

| 3.7  | Host communication task state machine                                           |

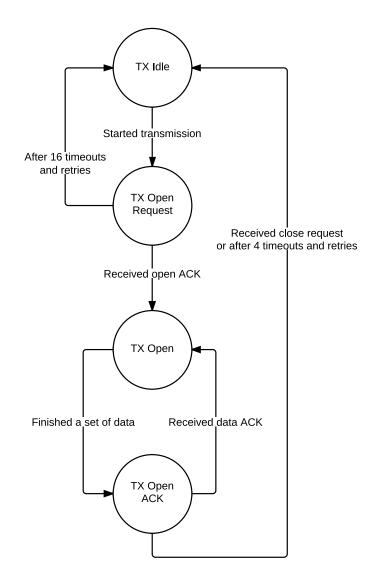

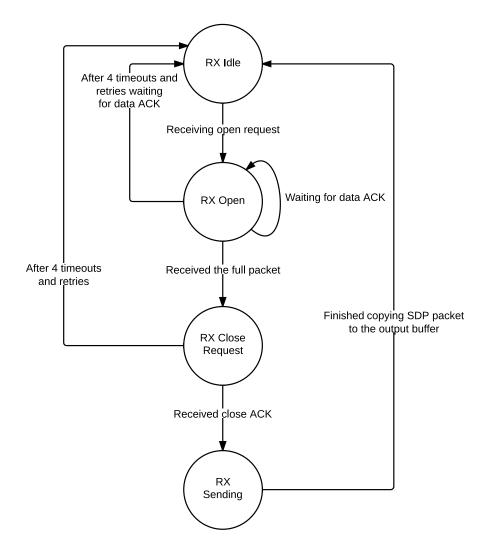

| 3.8  | SDP Packet Transmission State Machine                                           |

| 3.9  | SDP Packet Reception State Machine                                              |

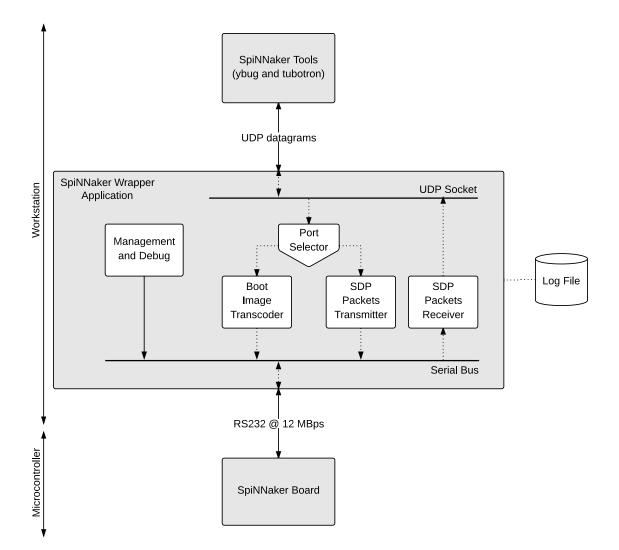

| 3.10 | SpiNNaker Wrapper Application Architecture                                      |

| 5.10 |                                                                                 |

| 3.11        | User Interface of the Workstation Application.              | 61 |

|-------------|-------------------------------------------------------------|----|

| 4.1         | Architecture for the Boids simulation.                      | 67 |

| 4.2         | A frame of the Boids Visualiser with 2176 birds.            | 70 |

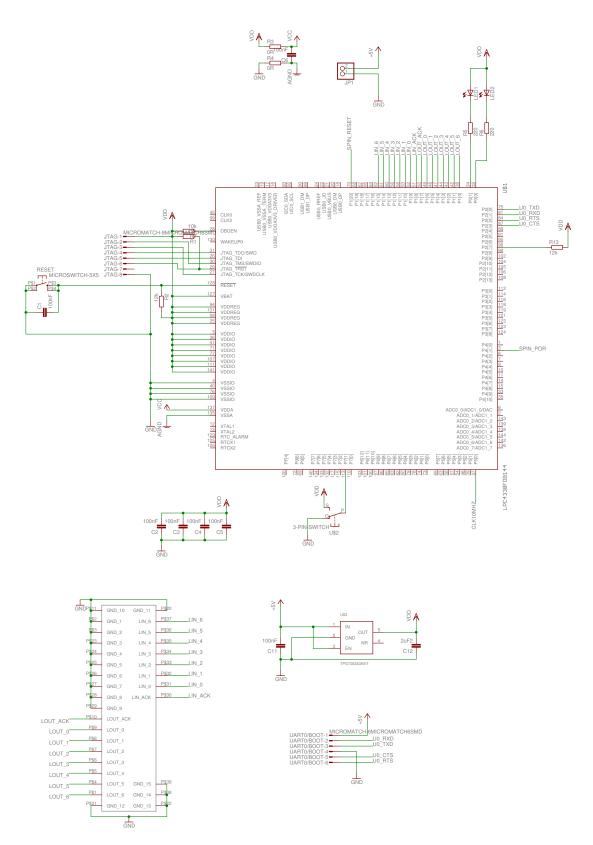

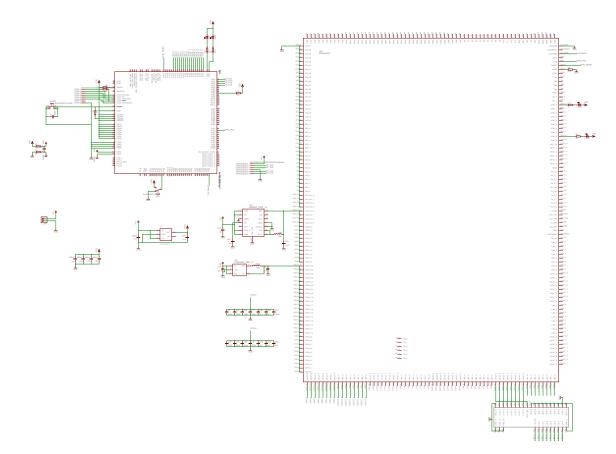

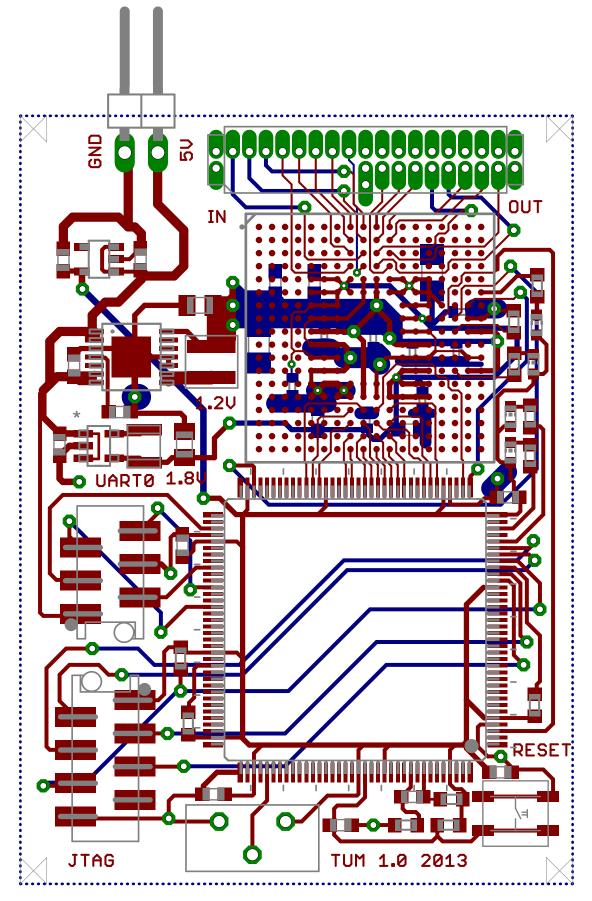

| A.1         | Schematic of the initial testing board.                     | 75 |

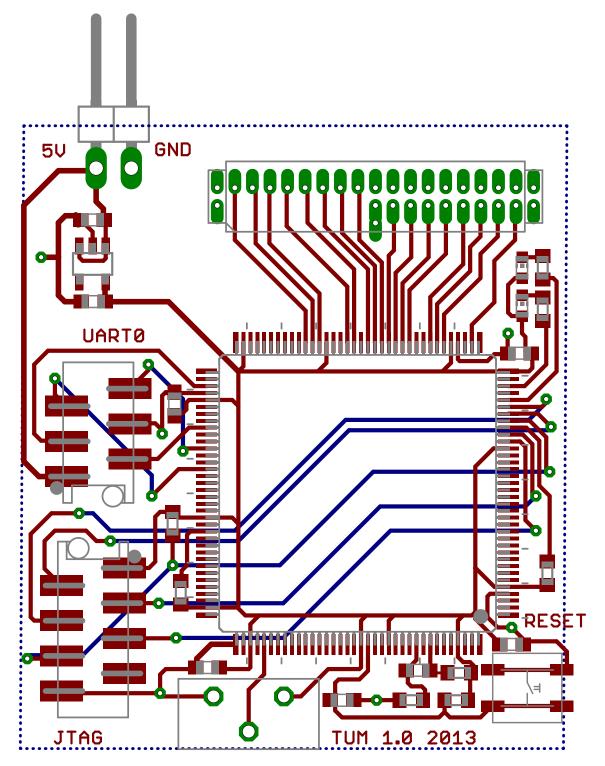

| A.2         | Developed PCB layout for the initial testing board.         | 77 |

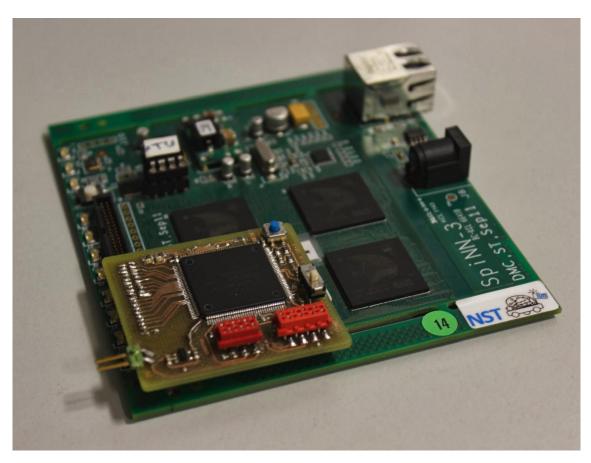

| A.3         | SpiNNaker 102 machine with the test board                   | 79 |

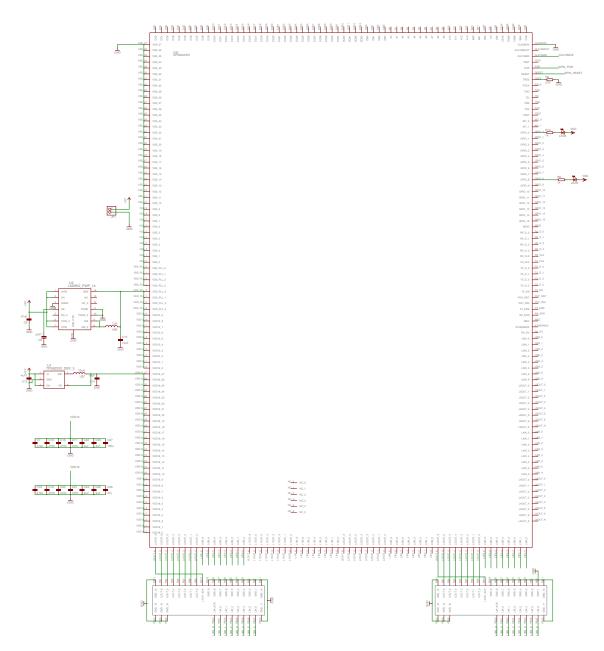

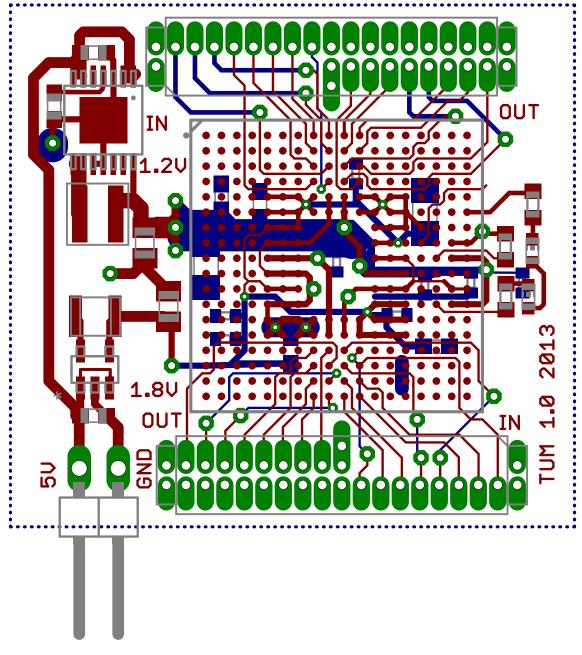

| A.4         | Schematic of the final design.                              | 81 |

| A.5         | Final PCB layout with the SpiNNaker chip and power supplies | 83 |

| A.6         | Schematic of the SpiNNaker extension board.                 | 85 |

| A.7         | SpiNNaker chip extension board                              | 87 |

| <b>B</b> .1 | The different payload packets.                              | 92 |

# **List of Tables**

| 2.1  | Multicast Output Vector Assignment.                                            | 14 |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | P2P Table Entry behavior.                                                      | 14 |

| 2.3  | 2-of-7 Symbol coding.                                                          | 16 |

| 2.4  | IPTag timeout values                                                           | 18 |

| 2.5  | Timeout values for SDP over P2P                                                | 19 |

| 2.6  | Retries count for SDP over P2P                                                 | 21 |

| 2.7  | 5 SCP commands that both SC&MP and SARK implement                              | 21 |

| 2.8  | Ordered list of power-on self-tests performed during Node-Boot                 | 25 |

| 2.9  | APLX header and APLX Command structure                                         | 35 |

| 2.10 | Event Callbacks Arguments.                                                     | 37 |

| 3.1  | Power dissipation for the various regulators.                                  | 47 |

| 3.2  | Commands send by the Application to the Microcontroller                        | 61 |

| 3.3  | Commands send by the Microcontroller to the Application                        | 62 |

| 3.4  | Performance Measurements for the transmission and reception of SpiNNaker pack- |    |

|      | ets                                                                            | 63 |

| 4.1  | Frames per second for the simulation with and without the SpiNNaker Computing  |    |

|      | Module                                                                         | 69 |

# **Abbreviations and Acronyms**

| API    | Application Programmable Interface                  |

|--------|-----------------------------------------------------|

| APLX   | Application Load and Execute                        |

| APT    | Advanced Processor Technologies                     |

| ASCII  | American Standard Code for Information Interchange  |

| BGA    | Ball Grid Array                                     |

| BSD    | Berkeley Software Distribution                      |

| CCR    | Cyclic redundancy check                             |

| CPU    | Central Processing Unit                             |

| DDR    | Double Data Rate                                    |

| DMA    | Direct Memory Access                                |

| DMIPS  | Dhrystone Millions Instructions per Second          |

| DTCM   | Data Tightly-Coupled Memory                         |

| EAGLE  | Easily Applicable Graphical Layout Editor           |

| EDA    | Electronic Design Automation                        |

| ELF    | Executable and Linkable Format                      |

| EEPROM | Electrically Erasable Programmable Read-Only Memory |

| FIQ    | Fast Interrupt Request                              |

| FLOPS  | Floating-point Operations Per Second                |

| FPGA   | Field Programmable Gate Array                       |

| FPS    | Frames Per Second                                   |

| FR     | Fixed Route                                         |

| GALS   | Globally Asynchronous Locally Synchronous           |

| GPIO   | General Purpose Input Output                        |

| GPL    | General Public License                              |

| IRQ    | Interrupt Request                                   |

| JAR    | Java Archive                                        |

| LED    | Light-emitting diode                                |

| IPC    | Interprocessor Communication                        |

| ITCM   | Instruction Tightly-Coupled Memory                  |

| MAC    | Media Access Control                                |

| MC     | Multicast                                           |

| MIPS   | Millions Instructions per Second                    |

| MPSoC  | Multi-Processor System-on-Chip                      |

| NN     | Nearest-neighbour                                   |

| NoC    | Network on Chip                                     |

| NRZ    | Non-Return-To-Zero                                  |

| OSI    | Open Systems Interconnection                        |

| P2P    | Point to Point                                      |

|        |                                                     |

| PCB       | Printed Circuit Board                    |

|-----------|------------------------------------------|

| RAM       | Random Access Memory                     |

| ROM       | Read Only Memory                         |

| RTZ       | Return To Zero                           |

| SARK      | SpiNNaker Application Runtime Kernel     |

| SATA      | Serial Advanced Technology Attachment    |

| SCP       | SpiNNaker Command Protocol               |

| SC&MP     | SpiNNaker Control & Monitor Program      |

| SDP       | SpiNNaker Datagram Protocol              |

| SDRAM     | Synchronous dynamic random access memory |

| SoC       | System on Chip                           |

| SpiNNaker | SPIKING Neural Network Architecture      |

| SRAM      | Static Random Access Memory              |

| TCAM      | Ternary Content-addressable Memory       |

| UDP       | User Datagram Protocol                   |

| VIC       | Vector Interrupt Controller              |

| VLSI      | Very-large-scale integration             |

|           |                                          |

# **Chapter 1**

# Introduction

The inner workings of the biological brain is still one of the great challenges for computational neuroscience despite an increasing amount of experimental data and deeper scientific understanding of individual components such as neurons.

There is a general consensus that the human brain has roughly about 85 to 100 billion neurons total [Ngu10] where each neuron can have up to 15000 connections to other neurons via synapses [Bro09]. Using techniques such as magnetic resonance imaging it is possible to observe large-scale brain activity. However, this knowledge is insufficient to truly understand how thoughts are constructed and how information is generally processed. It is believed that these functions probably lie in the intermediate levels of the brain [FB09]. In order to understand these middle layers, it is necessary to construct very large systems of spiking neurons with structures inspired by the latest findings from the neuroscience field.

General purpose digital architectures are not well suited to simulate these kinds of networks since these networks are characterized by massive processing parallelism and a high level of interconnectivity between the processing units. A possible approach is the usage of neuromorphic systems such as the BrainScales [PGJ<sup>+</sup>12] or the Neuro-grid [CSF<sup>+</sup>12] which *emulate* the neural network with a physical implementation of the individuals neurons. Another possible approach is a massively-parallel computer architecture with a high bandwidth inter-process communication like the SpiNNaker system [FB09].

## 1.1 Context

The SpiNNaker system is a massively-parallel computer architecture based on a Multi-Processor System-on-Chip (MPSoC) technology that can scale up to a million cores and is capable of simulating up to a billion spiking neurons in biological real time with realistic levels of interconnectivity between the neurons.

The SpiNNaker system was designed under the latest paradigm for high-performance computing, highly-parallel systems. However, it is motivated by the attempt to understand and study biological computing structures which achieve high level of parallelism with frugal amounts of energy as opposed to traditional electronics designs which up until the last few years were mostly driven by the serial throughput. The biological approach to the design of this *many-cores* architecture also brings new concerns in terms of fault-tolerance computation and efficiency. The SpiNNaker chip, the basic building block of a SPiNNaker machine, relies on smaller processors than other machines but in greater number, it has 18 highly efficient embedded ARM processors that allows the SpiNNaker system to be competitive according to two metrics, MIPS/mm<sup>2</sup> and MIPS/W.

## **1.2 Motivation**

The currently available machines with SpiNNaker chips are relatively large, the minimum size at this moment is  $105 \times 95$ mm, which limits their deployment on systems with limited size as for example, small mobile robots, specially flying ones due to very strict weight and space constraints. Additionally the SpiNNaker systems currently require a workstation, usually a desktop or a laptop, connected through an Ethernet connection to bootstrap the system every time it powers on and to feed the processing data into the system. This requirement seriously limits the independence and deployment capabilities of systems with embedded SpiNNaker chips. At present, it is necessary to add an wireless router in order to have a mobile system with a SpiNNaker machine [DLBG<sup>+</sup>13]. The drawbacks from this approach are fairly obvious, such as increased power consumption and space requirements since the typical wireless router consumes around 4 to 5 Watt and even though there are fairly small models available at the market it would still take up some space.

Furthermore the amount of extensibility provided by standard SpiNNaker machines is very limited since it only allows increases of computing power in fixed amounts. The current single board SpiNNaker machines are available in two versions, one with four chips and another with forty eight. These are wildly different amounts of processing capability which make it difficult to create intermediate solutions. It would be interesting to have the capability of selecting how many SpiNNaker chips one needs to deploy without having to design new hardware.

The current requirements of the SpiNNaker architecture are not suitable for a lot of applications where its processing power and capabilities would be helpful. It is then necessary to design a new solution that can overcome the limitations of the present options.

## 1.3 Goals

This thesis focused on the detailed study of the SpiNNaker architecture, with special care given to the analysis of the inner workings of the SpiNNaker chips during its bootstrapping procedures and its communications protocols with other chips in the system. The main objective from this study is the identification of the most relevant limitations and possible paths to overcome these.

The primary goal of this research is to bring this advanced and efficient computing platform to new ventures with increased flexibility. Having identified the main flaws and possible solutions to overcome them, the most significant requirements can be determined. These are as follows:

- Small size in order for this system to be available for deployment in as many fields as possible, it must have reduced dimensions or allow for significant reductions in size with future iterations. This requirement makes it feasible to include this new computing platform in many more applications;

- Extensible the basic solution should have only one SpiNNaker chip but it must allow the system to be extended in order to be a compelling option for applications that require greater amounts of computing power;

- Low cost it should strive to use low cost components and only the ones required for the solution;

- **Backwards Compatibility** the new solution must be compatible with tools and frameworks that are currently available for the SpiNNaker machines. The requirement increases the value of the new solution by allowing previous developments based on standard SpiN-Naker machines to be used on the new system with minimal or no work required.

## 1.4 Methodology

The methodology devised for this research to reach the defined goals includes the following phases, as depicted in Figure 1.1.

1. **Information Gathering:** The initial phase of the research was dedicated to gather and synthesize information on the SpiNNaker system and specially on the detailed behaviour of the SpiNNaker chip and on its communication with other chips. The results of this research are presented in chapter 2.

### 2. Development Approach:

The solution development was done in stages. The initial step was the design of a basic hardware version in order to allow the start the development of the software while still iterating on the final hardware design. The second stage was the continued improvement of the software up until the point it could boot SpiNNaker system by itself. The final step was the competition of the software to be feature complete in terms of the various capabilities that the communication subsystem of the SpiNNaker system has. This style of development led to successive improvements on the previous layers when new features or changes of functionality were required.

#### 3. Evaluation Approach:

In order to do a validation of the developed solution, besides the standard test-bench measurements, a case study of a computation-intensive process with special random characteristics was built. The simulation of the movement of a flock of birds [Rey87] was implemented on a desktop computer and on the new system to prove the gains that a SpiNNaker system may bring. This example was tested on the developed solution as well as on a standard SpiNNaker machine to validate the backwards compatibility requirement.

Figure 1.1: Work Methodology: phases and respective research methods

### 1.5 Main Results

The main contribution of the research is a new high performance computing module based on the SpiNNaker chip which is small and cost efficient to be used on mobile platforms such as small robots. The main features of the developed module are:

- Small size Removing the Ethernet jack among other non-essential components allowed significant reductions in total size of the new board even though the current proof of concept is a only one sided. It features also a single SpiNNaker chip and a microcontroller that emulates an Ehternet connected SpiNNaker chip.

- Extensible The developed board has a 34 pin connector that allows the system to be augmented with other SpiNNaker machines or a custom single SpiNNaker board.

- Backwards Compatibility A computer application written in Java was developed that allowed the system to masquerade as a standard SpiNNaker machine, capturing the UDP datagram used by the standard tools.

Another contribution from the developed work during this thesis, is the detailed study presented in chapter 2 on the innards of the SpiNNaker architecture. It is a collection of the knowledge present in the several articles and documents available from the researchers who created this biological inspired computing platform.

## 1.6 Related Works

The SpiNNaker system, although biological inspired and designed to help the study of the behaviour of large neural network of spiking neurons, is still a fairly general purpose architecture since it makes use of small ARM embedded cores which are general purposes processors. There is an alternative named neuromorphic system which are a class of devices that implements particular features of biological neural networks in their physical circuit layout [CSBR10]. One of these type of systems has been designed by the BrainScaleS project, a universal neuromorphic computing substrate [PGJ<sup>+</sup>12], whose central component is the neuromorphic microchip Spikey. This microchip contains analog very-large-scale integration (VLSI) circuits that model the electric behaviour of neurons and synapses. In this type of modelling, measurable quantities in the circuit have biological equivalents as for instance, the membrane potential  $V_m$  of a neuron is modelled by the voltage over a capacitor  $C_m$ . On Spikey, the standard leaky integrate-and-fire (LIF) neuron model with conductance-based synapses, depicted in equation 1.1, is implemented.

$$C_m \frac{dV_M}{dt} = -g_1(V_m - E_1) - \sum_i g_i(V_m - E_i)$$

(1.1)

This neuromorphic system includes a Field Programmable Gate Array (FPGA) to interface the system with a Host computer that is responsible for generating configuration data as well as input stimuli to the network. It was not possible to find the power consumption of this system but depending on the selected FPGA it should be lower than the comparable SpiNNaker system since the power consumption of neuromorphic chips is much lower than equivalent digital designs [ID00].

Another neuromorphic system, although this one is a multi-chip solution, is the *Neurogird*  $[CSF^+12]$  which is capable of simulating a million neurons connected by billions of synapses in real-time. It has sixteen  $12 \times 14$ mm Neurocores where the layers of the neural networks are mapped and SRAMs and a FPGA to relay the packets with the spikes. The power consumption for the entire system is 3.1W which is a very low number for the number of neurons *emulated*. For comparison purposes, a comparable SpiNNaker system would consume 90W.

The biggest advantage from the neuromorphic systems is the low power consumption specially when compared to regular digital circuits. On the other hand, these systems are very tailored to the original models they were designed for and although they have some reconfigurability, it is still very limited when compared with a more general purpose approach like the SpiNNaker architecture.

There are other general purposes solutions which have designed as massively parallel highperformance computing, as for instance, the IBM BlueGene/Q Compute Chip [HOF<sup>+</sup>12] which is the basic unit of computing for the Blue Gene Project [GBC<sup>+</sup>05] which is an IBM project aimed at designing supercomputers that can reach operating speeds in the petaFLOPS (for FLoating-point Operations Per Second) range, with low power consumption. This is the third design generation after BlueGene/L and BlueGene/P. The compute chip design shares some designs decision with the SpiNNaker chip. It features 18 processing units, with one used as spare and another in charge of management tasks, although the cores used are a variant from the PowerPC A2 [IBM12] downclocked to 1.6 GHzfrom the original 2.3 GHz design speed as opposed to the embedded ARM cores used in the SpiNNaker architecture. Nevertheless, the main objective of this chip is to have maximum throughput, as opposed to the SpiNNaker design where the design guidelines lead to some performance sacrifice for increased efficiency. The rated power consumption for the Blue-Gene/Q Compute Chip is 55 W while delivering a peak performance of 204.8 gigaFLOPS. It was not possible to find a Dhrystone performance measurement for this chip in order to compare it with the SpiNNaker architecture which achieves 1.1 DMIPS/MHz.

## **1.7 Document Structure**

This dissertation is organized in four more chapters, besides the current one.

Chapter 2 describes the SpiNNaker chip in detail, starting by the hardware perspective and later analysing the several layers of software that are needed on a standard SpiNNaker machine.

Chapter 3 presents the developed solution, the SpiNNaker Chip Computing Module while the chapter 4 describes the evaluation.

Lastly, chapter 5 reviews the dissertation as a whole, explains results and points questions for future research, that might improve the proposed solution. Appendix A displays the developed hardware, with the schematics and the PCB layouts for all the developed boards, and appendix B has a detailed diagram with the format of the packets used in a SpiNNaker specific protocol. Appendix C has some details on the code organization and on its availability and appendix D has the available API from the kernel that runs on the Application processors.

# Chapter 2

# The SpiNNaker System

The SpiNNaker chip is the basic building block of the SpiNNaker system. This system was designed with the aim of simulating up to a billion spiking neurons in (biological) real-time [NLMA<sup>+</sup>09]. This system is intended to serve as the *brain* of mobile robots to provide real-time stimulus-response behaviour [ES03] and to help improve the understanding of the brain architecture. The system was biologically inspired which allowed it to take advantage of several characteristics such as the lack of memory coherence and the slow pace of biological neurons when compared to artificial ones together with regular neuron losses. In fact, the average human adult loses about a neuron per second without any visible consequences [FB09] meaning that the SpiNNaker machine must be resilient to failures, since the sheer scale of the project will lead to frequent problems from which the system must recover and work around without the need for manual intervention.

This chapter presents the SpiNNaker in detail since it is a state-of-art biologically inspired system that it is not available for sale to the general public.

## 2.1 Architecture

The SpiNNaker machine has massively parallel architecture which can hold up to 65536 nodes, where each node is a SpiNNaker chip, a System on Chip (SoC) device with 18 low power ARM968 processors and a common 128 M byte SDRAM. One of the most important guidelines while the SoC was designed was low energy consumption since it was assumed that the cost of processors can be considered negligible when compared to the cost of the energy for the duration of the system lifetime. These guidelines explain the use of efficient embedded ARM9 cores and Mobile DDR (Double Data Rate ) SDRAM where some performance was sacrificed in exchange of for lower power consumption. For inter-chip communications, self-timed channels were used which require much less power than synchronous links of the same capacity although they are more costly in wiring.

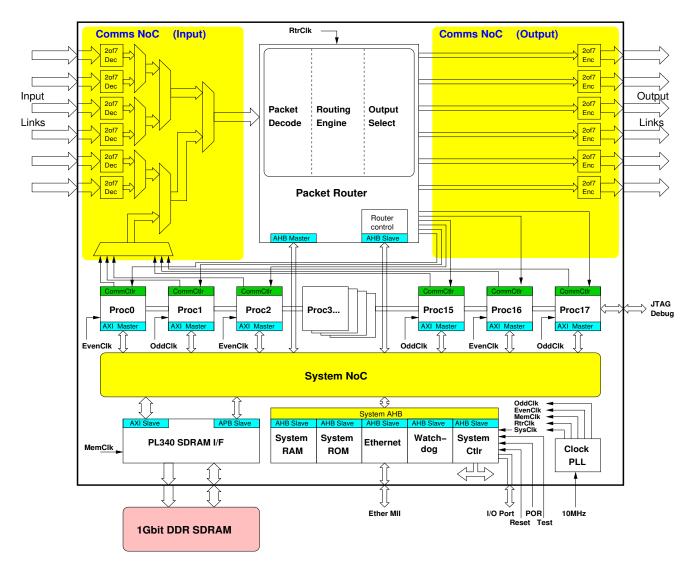

Figure 2.1: Block diagram of the SpiNNaker chip [Gro11b].

The chip itself is a Globally Asynchronous Locally Synchronous (GALS) system with the mentioned 18 low power ARM968 processors nodes connected through an energy-efficient packetswitched asynchronous communications infrastructure. Initial SoC designs used an interconnect paradigm based on a shared bus design [FB05]. However this paradigm is not conveniently upscalable when the complexity of the system increases. In order to solve this problem, SoC designers use a complex hierarchy of buses which allows concurrent communication with the different components partitioned in separate buses. These buses are connected through complex protocols and multiple bridges between them. This increased complexity makes it harder to meet the timing requirements. A solution to this problem is the use of packet-switched networks [DT01] which offer greater flexibility in the topology of the SoC, reduced latency and increased bandwidth through the use of additional area. Networks on Chip (NoC) decouple the timing domains of each block which simplifies the timing closure process. The SpiNNaker chip uses CHAIN, a solution developed at the University of Manchester, which uses self-timed circuits with delay insensitive data encoding combined with a return-to-zero signalling protocol to implement the packet switching network [BF02]. Self-timed circuits ( asynchronous ) are an alternative circuit design which uses acknowledgement to explicitly indicate and validate the data as opposed to synchronous circuits where there is a global clock to indicate the moments of data stability. There are a number of different designs in how to signal data validity, CHAIN uses a delay-insensitive style [Ver88] where the data validity is transmitted implicitly in the data encoding which removes the need for much of the timing analysis since this design operates correctly regardless of the delays involved in the interconnected wires.

Figure 2.1 illustrates the main functional components. The shaded areas indicate the asynchronous interconnect areas. It is clear that each chip has two NoC. The Communications NoC is responsible for transmitting packets between on-chip and off-chip processors while the System NoC replaces the traditional system bus by providing access to an off-chip DDR SDRAM, which is usually available in the same package mounted on top of the SpiNNaker die and stitch-bonded to it, and to other system control peripherals like the Router's configuration registers, the System Controller and the Watchdog Timer.

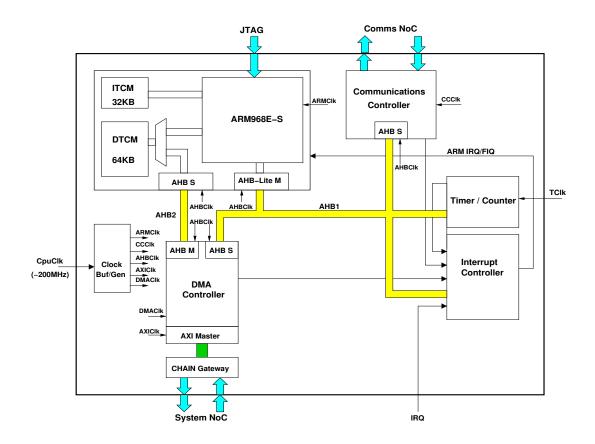

One of the most important components is the ARM928 core which is the main processing resource of the SpiNNaker system and whose block diagram can be seen in Figure 2.2. The ARM698E-S is the smallest, lowest power consuming ARM9 family processor [ARM13]. Each core in the SpiNNaker chip was configured to have 32 Kbyte of instruction tightly-coupled memory (ITCM) and 64 Kbyte of data tightly-coupled memory (DTCM) available. It also has a timer which is used by the kernel to provide time sensitive services, a DMA controller to be used for transfers with the attached SDRAM and to communicate with the system bus, and a Communications Controller. The Communications Controller is the peripheral that allow each core to access the packet switching network present in the SpiNNaker system.

All 18 processors nodes are identical which is the cause of problems during the start-up procedures. One of the processors is chosen as the Monitor Processor through a process which will be described later and it will be responsible for booting the chip, the communication with the Host PC and performing the necessary system management tasks. The other processors are named Application Processors and they will be responsible for modelling a group of neurons with associated inputs and outputs, named neuron fascicle, in neural application since the processor are general purpose in essence. Some Application processors may not be used to serve as spares for faulttolerance purposes. The Monitor processor runs a different kernel, named SpiNNaker Control & Monitor Program (SC&MP), from the Application cores which run the SpiNNaker Application Runtime Kernel (SARK). The Monitor processor is also given access to SystemRAM which is an extra block of 32 Kbyte of on-chip RAM accessible through the System NoC. This memory is not exclusive to the Monitor processor although the latter is its main user to improve its data resources as it will be responsible for the management of the chip and run complex algorithms.

The Router is the hearth of the Communications NoC, taking up 10% of the chip's area [NLMA<sup>+</sup>09], as it is responsible for the routing of packets between on-chip processors and with other SpiNNaker chips. The system supports four basic type of packets which are distinguished

Figure 2.2: Block diagram of the ARM928 core [Gro11b].

through the two most significant bits in the header, the different packet formats are showed in the diagram 2.4. All packets have a 32 bit optional payload whose presence is indicated through bit 1 in the header control byte. The least significant bit indicates if the entire packet has odd parity. For almost all packet types, there is a two bit time stamp present in the control byte. This time stamp is set to the current time phase of the system. There is a global time phase that cycles through 00 -> 01 -> 10 -> 11 -> 00, synchronization should be accurate to within one time phase, which is programmable and dynamically variable. If the Router finds a packet to be two time phases old, easily checked through an XOR operation, then it will drop it to the Monitor Processor. The Router is the one responsible for inserting this time stamp on local packets during normal operation though this behaviour can be overridden through configuration on the Communications Controller.

#### **Emergency Routing**

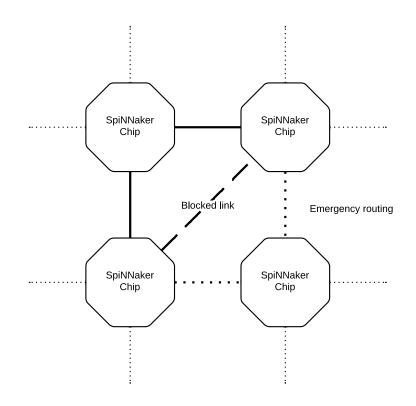

Each chip has six bidirectional links to communicate with other chips. These are numbered from 0 to 5. The recommended connection configuration is a triangular mesh where each chip is connected to six different neighbours. This allows for easy emergency routing in the event of a failing or congested link, the traffic that would be using the congested link is redirected using two adjacent link that form a triangle with the failing link, shown in figure 2.3. Since there are circular

#### 2.1 Architecture

Figure 2.3: Emergency routing.

dependencies between links there are potential deadlock scenarios for which there is a policy in place to prevent them which is "no Router can ever be prevented from issuing its output". In order to enforce this policy, the Router has several mechanisms available, the output has sufficient buffering and capacity detection so that the Router can know whether or not the output can accept another packet. If an output is blocked for any reason then emergency routing is used if possible to avoid overloading the blocked output. In cases where the emergency routing fails the packet is "dropped" to a Router error register and the Monitor Processor notified of this failure. The Monitor Process will then track the problem using a diagnostic counter:

- if the problem was temporary, it will only note it but do nothing further;

- if emergency routing keeps being used for the same route, it will negotiate a new one and divert some traffic to the new link;

- if the problem is permanent, it will establish new routes for all the traffic using this link.

The time taken by the Router to try emergency routing is controllable through its control register, there are two *wait* values, *wait1* is the number of clock cycles that Router waits before trying emergency routing and *wait2* which is the number of cycles that the Router tries to do route the packet through another link before dropping it to the error register and continuing to the next one.

There are 2 bits in the control byte which are used by Multicast and Fixed-route packets to control the emergency routing process. The meaning of each value is as follows:

- 00 normal packet;

- 01 the packet has been redirected by the previous Router through an emergency route along with a normal copy of the packet, the receiving Router should treat this as a combined normal plus emergency packet, meaning it will be routed in two different ways;

- 10 the packet has been redirected by the previous Router through an emergency route which would not be used for a normal packet;

- 11 this emergency packet is reverting to its normal route.

### Multicast Packets ( MC )

Multicast packets carry neural event information to be used during model simulations. Each packet contains an identifier which is used as a routing key as well as a neuron identifier in neural applications [PBF<sup>+</sup>08]. The multicast router behaves like a look-up table with two components, a parallel ternary content-addressable memory (TCAM) and a conventional RAM look-up table. A content-addressable memory is a special kind of memory whose input in a read operation is the data and the output is the address where the data is located as opposed to a read from RAM where the input is a memory location and the output the data stored at that address, the ternary variation include support for a *do not care* bit [PS06]. The router's TCAM has 1024 entries, which must be initialized after reset, each with its own mask and match value. The routing process uses the routing key present in the packet as input for the TCAM, then the TCAM result is used to retrieve from the look-up table the output vector whose value determines where this packet should be sent. In case of multiple matches from the TCAM look-up, the one with the lowest value will be used. The table 2.1 shows how each bit of the output vector, when set to 1, affects the propagation of the multicast packet. When the routing key has no matches then the default routing is employed. The default routing simply outputs the packet on the opposite link of the input link through where it was received. For local packets this routing is not available meaning that if the packet fails to match an entry it will be dropped.

When an output link is blocked, the Router will try to do emergency routing through a link with the next lower number. If the original port becomes unblocked before sending the packet through the emergency port, then the router will retry through the original one. If the Router receives a packet with the emergency packet bits set as diverted, then it will attempt to output it as a *reverting* packet to the output link with the next lower number than the input link number, where it was received. If it is also a normal packet then it will also perform the conventional routing. A received reverting packet is routed normally if it is recognised by the router, otherwise it is *default* routed to the link numbered two greater than the input link.

#### Point to Point Packets (P2P)

Point-to-point packets carry system management and control information. They are also used to implement a higher level packet transmission which it will be described later. These packets

| 8 bits       32 bits       32 bits         control       routing key       optional payload         Control Byte       7       6       5       4       3       2       1       0         0       0       emergency routing       time stamp       payload       parity         Point to Point Packet       8       32 bits       32 bits       32 bits         control       Source ID       destination ID       optional payload       control         Control Byte       7       6       5       4       3       2       1       0         0       1       sequence code       time stamp       payload       parity         Nearest-Neighbour Packet       8       bits       32 bits       32 bits       10         Nearest-Neighbour Packet       8       32 bits       32 bits       10       0         Control Byte       7       6       5       4       3       2       1       0         Fixed-Route Packet       8       32 bits       32 bits       32 bits       32 bits       32 bits         Control Byte       7       6       5       4       3       2       1       0       0 | Multicast Packet   |                       |          |                |                          |                           |                  |            |        |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|----------|----------------|--------------------------|---------------------------|------------------|------------|--------|--|--|

| Control Byte       7       6       5       4       3       2       1       0         0       0       emergency routing       time stamp       payload       parity         Point to Point Packet         8 bits       16 bits       16 bits       32 bits         control       source ID       destination ID       optional payload       parity         Control Byte         7       6       5       4       3       2       1       0         0       1       sequence code       time stamp       payload       parity         Nearest-Neighbour Packet         8 bits       32 bits       32 bits       32 bits         control Byte       7       6       5       4       3       2       1       0         Nearest-Neighbour Packet       solits       32 bits       32 bits       32 bits       0       1       0       debug       route       payload       parity         Fixed-Route Packet         8 bits       32 bits       32 bits       32 bits       32 bits         Solits       32 bits       32 bits         fixed-Route Packet                                             | 8 bits             |                       | 32 b     | its            |                          | 32 bits                   |                  |            |        |  |  |

| 7654321000emergency routingtime stamppayloadparityPoint to Point Packet8 bits16 bits16 bits32 bitscontrolsource IDdestination IDoptional payloadControl Byte76543217654321001sequence codetime stamppayloadparityNearest-Neighbour Packet8 bits32 bits32 bits32 bitscontroladdress/operationoptional payloadcontrol7654321010debugroutepayloadparityFixed-Route Packet8 bits32 bits32 bits32 bitscontrolpayloadroutepayloadparityFixed-Route Packet8 bits32 bits32 bitscontrolpayloadoptional payloadControl Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | control            |                       | routing  | ı key          |                          |                           | option           | al payload |        |  |  |

| 0     0     emergency routing     time stamp     payload     parity       Point to Point Packet     8 bits     16 bits     32 bits     32 bits       control     source ID     destination ID     optional payload     control payload       Control Byte     7     6     5     4     3     2     1     0       0     1     sequence code     time stamp     payload     parity       Nearest-Neighbour Packet     source     source     optional payload     payload     parity       Control Byte     32 bits     32 bits     32 bits     32 bits     32 bits       Control Byte     7     6     5     4     3     2     1     0       7     6     5     4     3     2     1     0       Control Byte     7     6     5     4     3     2     1     0       7     6     5     4     3     2     1     0       1     0     debug     route     payload     parity       Fixed-Route Packet       8 bits     32 bits     32 bits     32 bits       Control     payload     optional payload     optional payload                                                                                  | Control Byte       | 9                     |          |                |                          |                           |                  |            |        |  |  |

| Point to Point Packet         8 bits       16 bits       16 bits       32 bits         control       source ID       destination ID       optional payload         Control Byte       7       6       5       4       3       2       1       0         0       1       sequence code       time stamp       payload       parity         Nearest-Neighbour Packet       8       32 bits       32 bits       32 bits         control       address/operation       optional payload       optional payload         Control Byte       7       6       5       4       3       2       1       0         1       0       debug       route       payload       parity         Fixed-Route Packet         8 bits       32 bits       32 bits       32 bits         fixed-Route Packet       s       32 bits       32 bits       32 bits         fixed-Route Packet       8       bits       32 bits       32 bits       32 bits         control       payload       optional payload       optional payload       optional payload                                                                  | 7                  | 6                     | 5        | 4              |                          | 3                         | 2                | 1          | 0      |  |  |

| 8 bits16 bits32 bitscontrolsource IDdestination IDoptional payloadControl Byte7654321001sequence codetime stamppayloadparityNearest-Neighbour Packet8 bits32 bits32 bits32 bitsControladdress/operationoptional payloadControl Byte7654321010debugroutepayloadparityFixed-Route Packet8 bits32 bits32 bits32 bitsS2 bits32 bits32 bitsControl ByteControl payloadControl payloadControl payloadControl payloadControl payloadControl Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                  | 0                     | emerç    | gency routing  |                          | time                      | stamp            | payload    | parity |  |  |

| 8 bits16 bits32 bitscontrolsource IDdestination IDoptional payloadControl Byte7654321001sequence codetime stamppayloadparityNearest-Neighbour Packet8 bits32 bits32 bits32 bitscontroladdress/operationoptional payloadcontrolControl Byte7654321010debugroutepayloadparityFixed-Route Packet8 bits32 bits32 bits32 bitsStits32 bits32 bitsControl ByteControl payloadpayloadpayloadoptional payloadControl payloadControl Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Point to P         | oint Packe            | t        |                |                          |                           |                  |            |        |  |  |

| Control Byte       7       6       5       4       3       2       1       0         0       1       sequence code       time stamp       payload       parity         Nearest-Neighbour Packet         8 bits       32 bits       32 bits         control       address/operation       optional payload         Control Byte       7       6       5       4       3       2       1       0         1       0       debug       route       payload       parity         Fixed-Route Packet         8 bits       32 bits       32 bits         control       payload       optional payload       optional payload         Control Byte         Control Byte         Control Byte                                                                                                                                                                                                                                                                                                                                                                                                              |                    |                       |          | 16 bits        |                          |                           | 3                | 32 bits    |        |  |  |

| 7       6       5       4       3       2       1       0         0       1       sequence code       time stamp       payload       parity         Nearest-Neighbour Packet       32 bits       32 bits       32 bits         6       32 bits       32 bits       32 bits         control       address/operation       optional payload       optional payload         Control Byte       7       6       5       4       3       2       1       0         1       0       debug       route       payload       parity         Fixed-Route Packet         8 bits       32 bits       32 bits       32 bits         control       payload       optional payload       parity         Fixed-Route Packet       32 bits       32 bits       32 bits         Control       payload       optional payload       optional payload         Control Byte                                                                                                                                                                                                                                            | control            | source I              | D        | destination IE | )                        |                           | optior           | al payload |        |  |  |

| 01sequence codetime stamppayloadparityNearest-Neighbour Packet<br>8 bits8 bits32 bits32 bits32 bitscontroladdress/operationoptional payloadoptional payloadControl Byte<br>7654321010debugroutepayloadparityFixed-Route Packet<br>8 bits32 bits32 bits32 bitscontrolpayloadoptional payloadoptional payloadControl ByteControl Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Control Byte       | e                     |          |                |                          |                           |                  |            |        |  |  |

| Nearest-Neighbour Packet       8 bits     32 bits       control     address/operation       0     address/operation       7     6       5     4       3     2       1     0       0     debug       route     payload       payload     parity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                  | 6                     | 5        | 4              | _                        | 3                         | 2                | 1          | 0      |  |  |

| 8 bits     32 bits       control     address/operation     optional payload       Control Byte     7     6     5     4     3     2     1     0       1     0     debug     route     payload     parity       Fixed-Route Packet       8 bits     32 bits     32 bits       control     payload     optional payload       Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                  | 1                     | seq      | uence code     |                          | time stamp payload parity |                  |            | parity |  |  |

| 8 bits     32 bits       control     address/operation     optional payload       Control Byte     7     6     5     4     3     2     1     0       1     0     debug     route     payload     parity       Fixed-Route Packet       8 bits     32 bits     32 bits       control     payload     optional payload       Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    | -                     | -        |                |                          |                           |                  | -          | _      |  |  |

| controladdress/operationoptional payloadControl Byte7654321010debugroutepayloadparityFixed-Route Packet<br>8 bits32 bits32 bits32 bitsControlpayloadoptional payloadoptional payloadControl Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | leighbour F           |          | vito           |                          |                           |                  | 22 hita    |        |  |  |

| Control Byte         7       6       5       4       3       2       1       0         1       0       debug       route       payload       parity         Fixed-Route Packet         8 bits       32 bits       32 bits         control       payload       optional payload         Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |                       |          |                |                          |                           |                  |            |        |  |  |

| 7     6     5     4     3     2     1     0       1     0     debug     route     payload     parity   Fixed-Route Packet       8 bits     32 bits     32 bits   Control payload optional payload Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | control            | ac                    | ddress/o | peration       |                          |                           | option           | al payload |        |  |  |

| 1     0     debug     route     payload     parity       Fixed-Route Packet<br>8 bits     32 bits     32 bits     32 bits       control     payload     optional payload       Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                  |                       | 5        | 1              |                          | 3                         | 2                | 1          | 0      |  |  |

| Fixed-Route Packet<br>8 bits 32 bits 32 bits<br>control payload optional payload<br>Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | <u> </u>              |          |                | rc                       |                           |                  |            |        |  |  |

| 8 bits     32 bits       control     payload       Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                       |          |                |                          |                           | payload          | panty      |        |  |  |

| controlpayloadoptional payloadControl Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Fixed-Route Packet |                       |          |                |                          |                           |                  |            |        |  |  |

| Control Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |                       |          |                |                          |                           | 3                | 32 bits    |        |  |  |

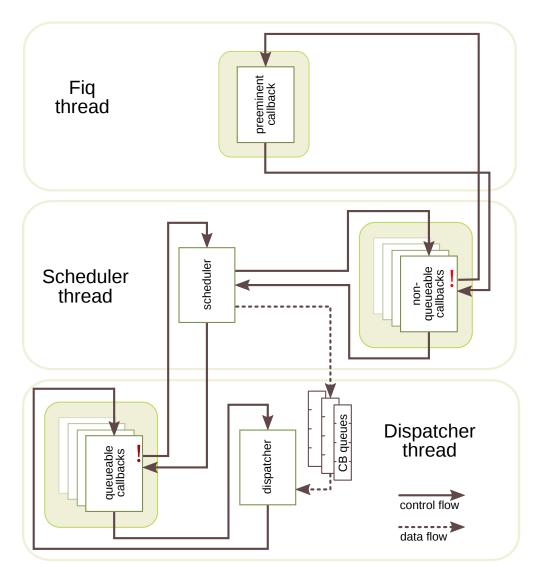

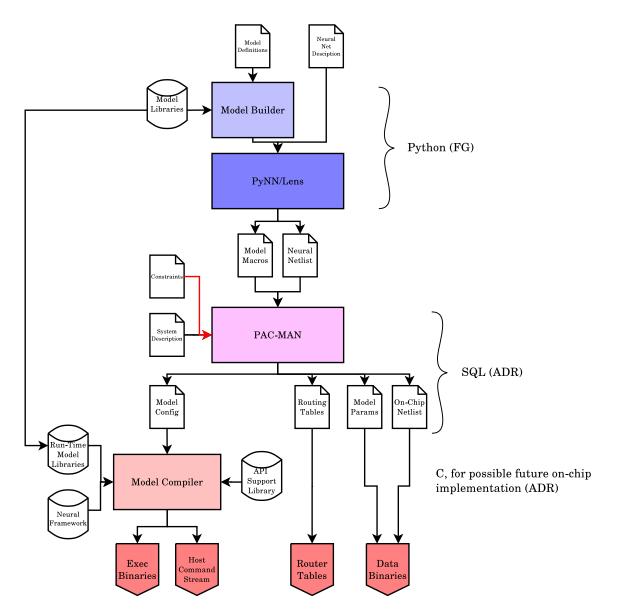

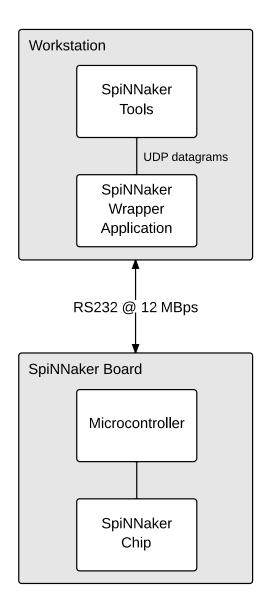

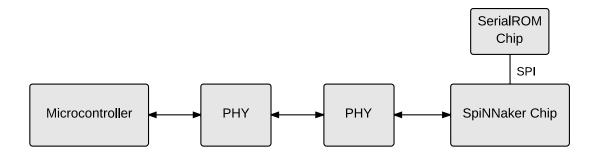

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | control            | control payload       |          |                |                          |                           | optional payload |            |        |  |  |