FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# **CMOS-RF Power Amplifier for Wireless Communications**

Daniel José Azevedo Oliveira

Final report submitted for fulfillment of the Dissertation in the Integrated Master in Electrical and Computers Engineering Telecommunications Major

Supervisor: Vítor Manuel Grade Tavares (PhD)

Co-Supervisor: Manuel Cândido Duarte dos Santos (Eng)

July 2009

© Daniel José Azevedo Oliveira, 2009

## MIEEC - MESTRADO INTEGRADO EM ENGENHARIA ELECTROTÉCNICA E DE COMPUTADORES 2008/2009

### A Dissertação intitulada

### "CMOS-RF Power Amplifier for Wireless Communications"

foi aprovada em provas realizadas em 17/Julho/2009

o júri

No- John Like

Presidente Professor Doutor Mário Jorge Moreira Leitão Professor Associado do Departamento de Engenharia Electrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto

distens funds

Professor Doutor Paulo Mateus Mendes Professor Auxiliar do Departamento de Electrónica Industrial da Escola de Engenharia da Universidade do Minho

Professor Doutor Vitor Manuel Grade Tavares Professor Auxiliar do Departamento de Engenharia Electrotécnica e de Computadores da Faculdade de Engenharia da Universidade do Porto

O autor declara que a presente dissertação (ou relatório de projecto) é da sua exclusiva autoria e foi escrita sem qualquer apoio externo não explicitamente autorizado. Os resultados, ideias, parágrafos, ou outros extractos tomados de ou inspirados em trabalhos de outros autores, e demais referências bibliográficas usadas, são correctamente citados.

Autor - DANIEL JOSÉ AZEVEDO OLIVEIRA

Miniel for Szeredo oligeino

Faculdade de Engenharia da Universidade do Porto

## Abstract

The present work addresses the study and implementation of a radio-frequency (RF) power amplifier (PA). Several classes of amplification are analyzed, from both the linear and the non-linear classes of amplification. From the non-linear class amplifiers, the current-mode class-D (CMCD) amplifier was the chosen, because it is a zero-voltage-switching (ZVS) amplifier but with a lower peak drain voltage than other ZVS amplifiers, like the class-E amplifier. Since CMOS devices have a low breakdown voltage, having a lower peak drain voltage is an important feature. The ZVS characteristic enables the CMCD to work at higher frequencies ideally without energy losses at each RF cycle, in opposition to its dual counterpart, the voltage-mode class-D (VMCD).

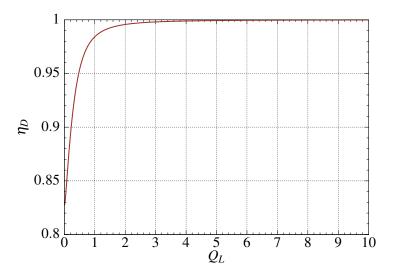

Following the basic operation of the CMCD amplifier, a non-linear analysis is made starting with the impact of the load network quality factor,  $Q_L$ , on the amplifier performance. The second part of the non-linear analysis comprises a study to understand the impact of the inductor unloaded quality factor, along with  $Q_L$ , on the PA efficiency. It is concluded that lowering  $Q_L$  by increasing the RLC network inductor size, and decreasing the filter capacitance by the same factor, greatly improves the PA overall performance.

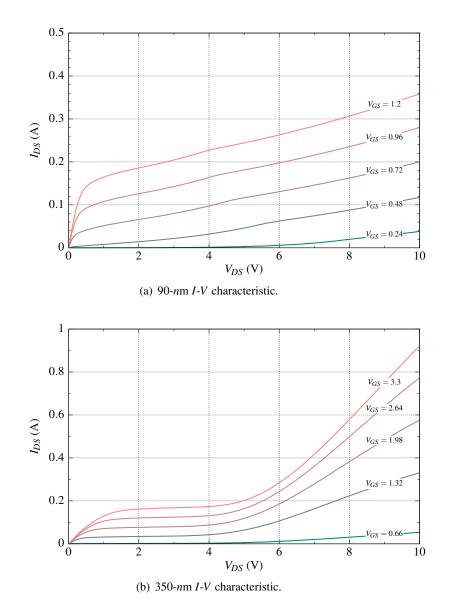

A vast set of simulations is presented in this work. First the low  $Q_L$  approach that improves the PA performance is corroborated, achieving nearly 76% of drain efficiency with 16-dBm of output power. A small comparative study between a 90-*n*m and a 350-*n*m CMOS technology is also performed, showing that the selected 90-*n*m technology is better suited to implement the CMCD PA. The NMOS-RF *I-V* characteristic curves of both technologies are also shown in order to discuss the breakdown voltage of the transistors.

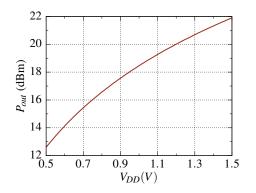

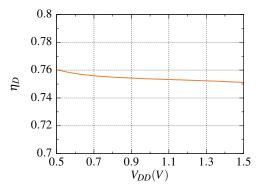

The CMCD cascode topology is presented as a solution to increase the output power, sacrificing only a small percentage of the drain efficiency. Since with the cascode architecture there are two transistors at each branch, it is possible to raise the supply voltage to higher values than with the basic topology.

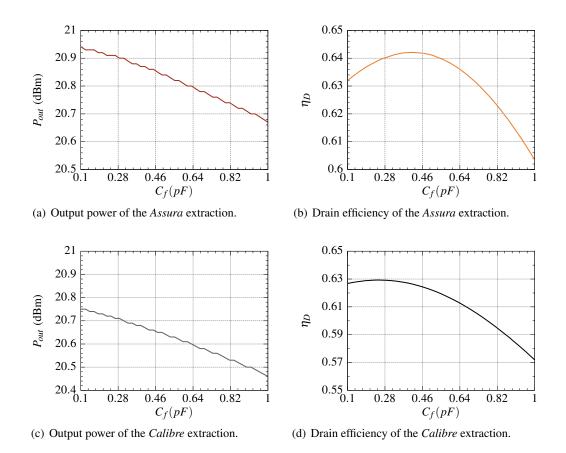

A layout with the selected 90-nm CMOS technology, of the current-mode class-D PA cascode topology is presented. A group of post-layout simulations is performed with *Assura* and *Calibre* parasitic extractions, which leads to the need of a post-layout RLC filter re-tuning. After a correction in the RLC filter capacitance value, new *Assura* and *Calibre* parasitic extractions are performed producing good results. A 64.06% drain efficiency with *Assura* extraction and 62.81% with *Calibre* are achieved against the 66.18% drain efficiency of the ideal case. The output power is approximately 21-dBm with both parasitic extractions and in the ideal case.

ii

## Resumo

O presente trabalho tem como objectivo o estudo e implementação de um amplificador de potência (PA) para rádio-frequência (RF). Várias classes de amplificadores são analisadas e destas, o amplificador de funcionamento classe-D em modo corrente (CMCD) é o seleccionado para implementação. Devido ao amplificador CMCD possuir a característica *zero-voltage-switching* (ZVS) e de ter uma tensão de pico no dreno dos transístores menor que o amplificador classe-E, também ele um amplificador ZVS, fazem dele a melhor opção para um estudo aprofundado e implementação. O facto de não existirem implementações desta classe em CMOS, reportadas até à data também teve influência na decisão.

Após o estudo do funcionamento básico do amplificador classe-D em modo corrente, é efectuada uma análise ao impacto do factor de qualidade da rede de carga,  $Q_L$ , no desempenho do PA. A segunda parte desta análise não linear do comportamento do CMCD, é feita tendo em conta o impacto do factor de qualidade da bobine da rede RLC juntamente com  $Q_L$ . Daqui pode-se concluir que baixar o  $Q_L$ , aumentado o valor da bobine e diminuindo o valor do condensador de carga pelo mesmo factor, traduz-se num aumento de desempenho por parte do amplificador.

Um vasto conjunto de simulações é apresentado neste trabalho. Nestas simulações o método de baixar o factor de qualidade da rede de carga é comprovado com recurso a uma tecnologia CMOS de 90-*n*m, obtendo-se aproximadamente 76% de eficiência de dreno com 16-dBm de potência de saída. Um estudo comparativo entre a tecnologia CMOS de 90-*n*m e outra de 350-*n*m é efectuado, onde se demonstra que a tecnologia de 90-*n*m é mais adequada à implementação do amplificador de potência. As curvas características *I-V* dos transístores de rádio-frequência NMOS, de ambas as tecnologias, são apresentadas para definir as tensões de quebra dos transístores.

A topologia cascode do amplificador classe-D em modo corrente é apresentada como solução para aumentar a potência de saída do amplificador, sacrificando apenas uma pequena percentagem da eficiência de dreno. Este aumento de potência de saída do amplificador é possivel pois, com a topologia cascode temos dois transístores em cada ramo, o que nos permite aumentar a tensão de alimentação do circuito.

Um *layout* do amplificador de potência CMCD desenhado na tecnologia CMOS 90-*n*m é apresentado. Foi necessário efectuar uma re-sintonização do filtro RLC após terem sido efectuadas simulações *post-layout* e os resultado não serem os esperados. Após a correcção na capacidade do filtro RLC, novas extracções parasitas do layout são efectuadas com as ferramentas *Assura* e *Calibre* produzindo bons resultados. Eficiências de dreno de 64.06% com o *Assura* e 62.18% com o *Calibre* foram atingidas contra os 66.18% do caso ideal. A potência de saída atingida é aproximadamente 21-dBm nas extrações parasitas e no caso ideal. iv

## Acknowledgments

First of all I would like to thank my mother, father and brother for making the person I am today. Without you this work was not possible. To my girlfriend who always supported me whenever things went wrong, I would like to show my deepest appreciation.

I would like to show my gratitude to both of my supervisors for all their support and encouragement. To Professor Vítor Grade Tavares for his advises. To the Engineer and future PhD Cândido Duarte for always making me give the best of me, and for the initial idea which made this thesis possible.

The Microelectronic Students' Group at the Faculty of Engineering of the University of Porto, which I am a member since the beginning, also played an important role in this work. My interests in RF grew and were developed thanks to those hard Friday nights spent at the University, but it was worth it. Thanks to all the group members for the good times but mainly to its founders, who keep the group alive since its beginning.

To all my other friends that are with me since the beginning of this course, thank you. For the study hours shared, the fun times spent and also for being there in the bad times.

At last, I would like to show my gratitude to all my other friends that make part of my life and always bring me something positive into it. I hope I also bring something positive into your life.

Daniel José Azevedo Oliveira

vi

"An expert is a man who has made all the mistakes which can be made in a very narrow field."

Niels Bohr

viii

## Contents

| 1 | Intr                                          | oduction                                                                                                            |                                                                                                                                                  | 1                                                                                                 |

|---|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|   | 1.1                                           | Motivat                                                                                                             | ion                                                                                                                                              | . 1                                                                                               |

|   | 1.2                                           | Bluetoo                                                                                                             | th features                                                                                                                                      | . 2                                                                                               |

|   | 1.3                                           | Power a                                                                                                             | mplifiers overview                                                                                                                               | . 4                                                                                               |

|   |                                               |                                                                                                                     | Linear amplifiers                                                                                                                                |                                                                                                   |

|   |                                               |                                                                                                                     | Non-linear amplifiers                                                                                                                            |                                                                                                   |

|   | 1.4                                           |                                                                                                                     | the art                                                                                                                                          |                                                                                                   |

|   |                                               |                                                                                                                     | Amplifiers for Bluetooth                                                                                                                         |                                                                                                   |

|   |                                               |                                                                                                                     | $Class-D^{-1}$ amplifiers                                                                                                                        |                                                                                                   |

| 2 | Clas                                          | s- $\mathbf{D}^{-1}$ Po                                                                                             | ower Amplifier                                                                                                                                   | 17                                                                                                |

|   | 2.1                                           | Current                                                                                                             | -Mode Class-D power amplifier                                                                                                                    | . 17                                                                                              |

|   | 2.2                                           |                                                                                                                     | peration                                                                                                                                         |                                                                                                   |

|   | 2.3                                           | Ideal an                                                                                                            | alysis                                                                                                                                           | . 20                                                                                              |

|   | 2.4                                           | Non-ide                                                                                                             | al analysis                                                                                                                                      | . 25                                                                                              |

|   |                                               | 2.4.1                                                                                                               | Impact of $Q_L$ in the circuit performance                                                                                                       | . 25                                                                                              |

|   |                                               | 2.4.2                                                                                                               | Influence of $Q_u$ in the circuit performance                                                                                                    | . 27                                                                                              |

|   | 2.5                                           | Summar                                                                                                              | ry                                                                                                                                               | . 33                                                                                              |

|   |                                               |                                                                                                                     |                                                                                                                                                  |                                                                                                   |

| 3 | Sim                                           | ulations                                                                                                            |                                                                                                                                                  | 35                                                                                                |

| 3 | <b>Sim</b><br>3.1                             |                                                                                                                     | out simulations                                                                                                                                  | <b>35</b><br>. 35                                                                                 |

| 3 |                                               | Pre-layo                                                                                                            | but simulations $\dots$                                                  | . 35                                                                                              |

| 3 |                                               | Pre-layo<br>3.1.1                                                                                                   |                                                                                                                                                  | . 35<br>. 35                                                                                      |

| 3 |                                               | Pre-layo<br>3.1.1<br>3.1.2                                                                                          | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36                                                                              |

| 3 |                                               | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3                                                                                 | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36<br>. 38                                                                      |

| 3 |                                               | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                        | Lowering the $Q_L$ factorImpact of the transistors size90-nm versus 350-nmCMCD PA cascode configuration                                          | . 35<br>. 35<br>. 36<br>. 38<br>. 40                                                              |

| 3 |                                               | Pre-layc<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                               | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41                                                      |

| 3 |                                               | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                      | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41<br>. 43                                              |

| 3 | 3.1                                           | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Power a                                           | Lowering the $Q_L$ factorImpact of the transistors size90-nm versus 350-nmCMCD PA cascode configurationPower controlPA re-tuningumplifier layout | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41<br>. 43<br>. 44                                      |

| 3 | 3.1                                           | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Power a<br>3.2.1                                  | Lowering the $Q_L$ factorImpact of the transistors size90-nm versus 350-nmCMCD PA cascode configurationPower controlPA re-tuning                 | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41<br>. 43<br>. 44<br>. 45                              |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Power a<br>3.2.1                                  | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41<br>. 43<br>. 44<br>. 45                              |

|   | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Power a<br>3.2.1<br>Summar                        | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41<br>. 43<br>. 44<br>. 45<br>. 47<br><b>49</b>         |

|   | 3.1<br>3.2<br>3.3<br>Con                      | Pre-layc<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Power a<br>3.2.1<br>Summan<br>Achieve             | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41<br>. 43<br>. 44<br>. 45<br>. 47<br><b>49</b><br>. 49 |

| 4 | 3.1<br>3.2<br>3.3<br>Con<br>4.1<br>4.2        | Pre-layo<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Power a<br>3.2.1<br>Summan<br>Achieve<br>Future v | Lowering the $Q_L$ factor                                                                                                                        | . 35<br>. 35<br>. 36<br>. 38<br>. 40<br>. 41<br>. 43<br>. 44<br>. 45<br>. 47<br><b>49</b><br>. 49 |

## CONTENTS

# **List of Figures**

| 1.1        | Bluetooth modulation schemes                                                                                                                                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2        | Power amplifier classes and groups                                                                                                                                                 |

| 1.3        | Linear power amplifier schematic                                                                                                                                                   |

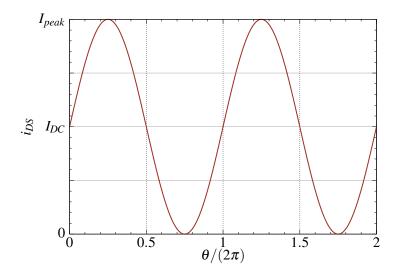

| 1.4        | Class-A amplifier drain current waveform (two RF cycles shown)                                                                                                                     |

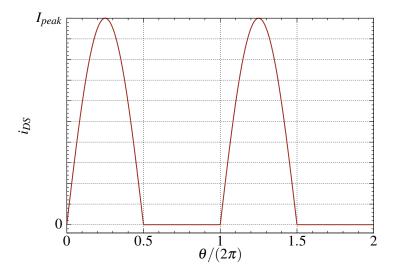

| 1.5        | Class-B amplifier drain current waveform (two RF cycles shown)                                                                                                                     |

| 1.6        | Class-C amplifier drain current waveform (two RF cycles shown)                                                                                                                     |

| 1.7        | Efficiency of linear amplifiers                                                                                                                                                    |

| 1.8        | Class-E power amplifier schematic                                                                                                                                                  |

| 1.9        | Class-E drain current and voltage waveforms                                                                                                                                        |

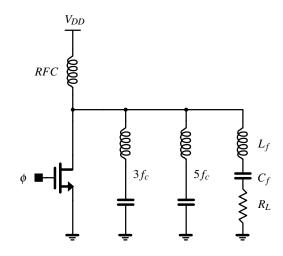

| 1.10       | Class-F power amplifier schematic with $5^{th}$ harmonic peaking                                                                                                                   |

| 1.11       | Class-F drain current and voltage waveforms                                                                                                                                        |

| 1.12       | Class- $F^{-1}$ power amplifier schematic with 5 <sup>th</sup> harmonic peaking                                                                                                    |

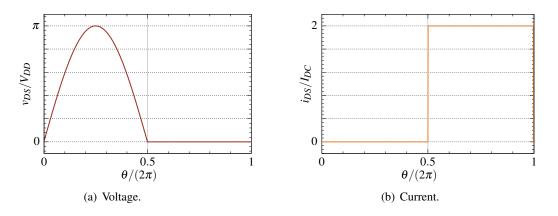

| 1.13       | Class- $F^{-1}$ drain current and voltage waveforms                                                                                                                                |

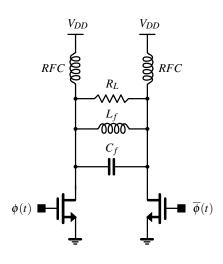

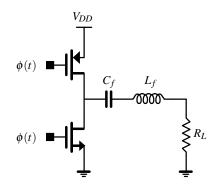

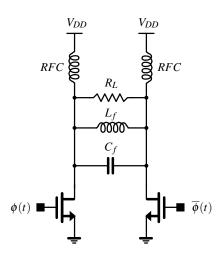

| 2.1        | Circuit of the CMCD power amplifier                                                                                                                                                |

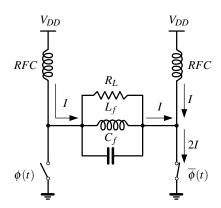

| 2.2        | Current flow in the class- $D^{-1}$ power amplifier                                                                                                                                |

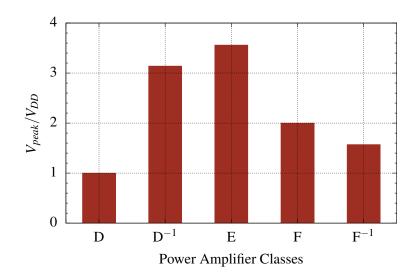

| 2.3        | Drain peak voltage of several SMPA                                                                                                                                                 |

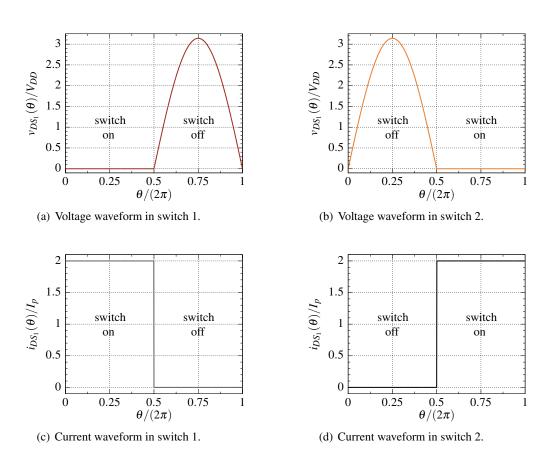

| 2.4        | CMCD power amplifier waveforms                                                                                                                                                     |

| 2.5        | Circuit of the VMCD power amplifier                                                                                                                                                |

| 2.6        | $Class-D^{-1}$ power amplifier with parasitic capacities                                                                                                                           |

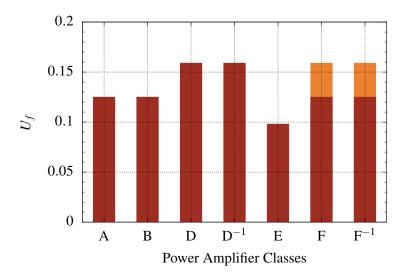

| 2.7        | Utilization factor comparison between several power amplifiers                                                                                                                     |

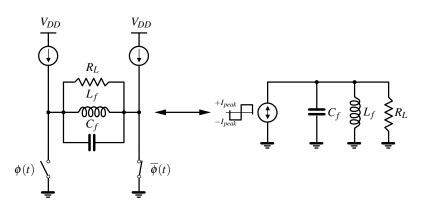

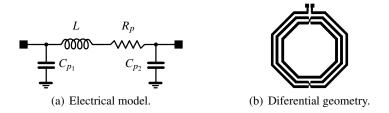

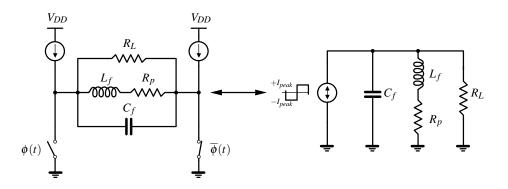

| 2.8        | CMCD ideal architecture and equivalent circuit                                                                                                                                     |

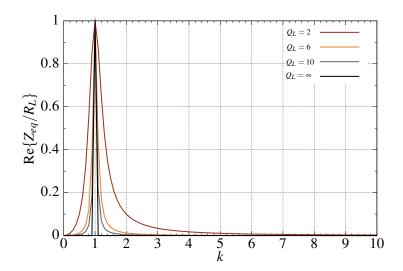

| 2.9        | Value of the RLC network for various harmonics and $Q_L$                                                                                                                           |

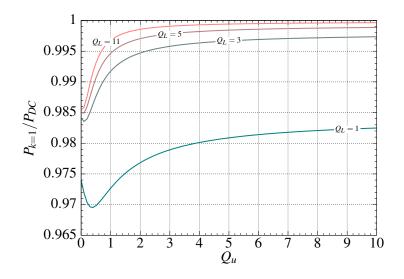

| 2.10       | Efficiency of the CMCD for various values of $Q_L$                                                                                                                                 |

| 2.11       | On-chip inductor                                                                                                                                                                   |

| 2.12       | CMCD architecture with parasitic resistance of the on-chip inductor and equiva-<br>lent circuit                                                                                    |

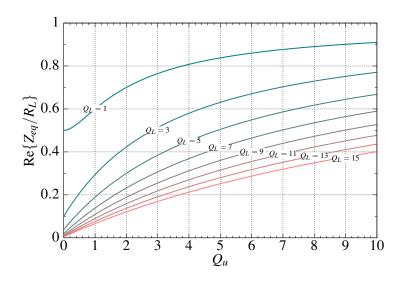

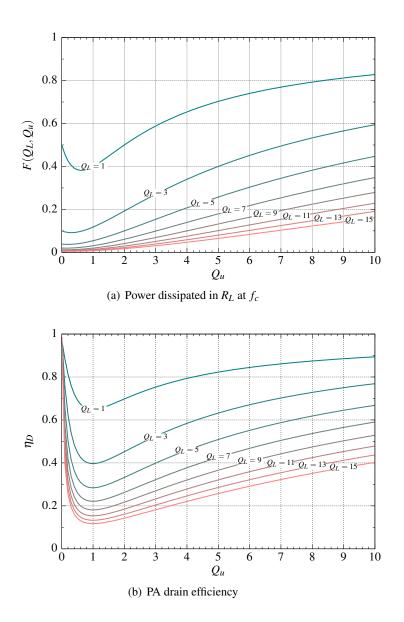

| 2.13       | Value of the RLC network at $f_c$ for several $Q_L$ and $Q_u$                                                                                                                      |

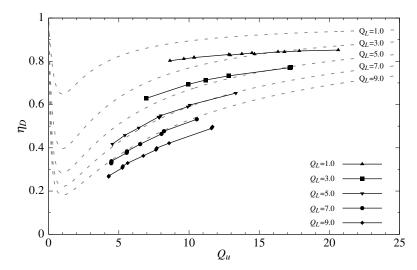

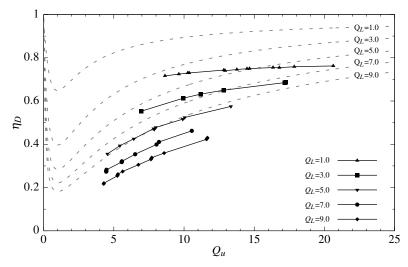

|            | Effect of $Q_L$ and $Q_u$ in the PA performance                                                                                                                                    |

|            | Ratio between the power at $f_c$ and the total power delivered to the load 33                                                                                                      |

| 3.1        | Circuit of the CMCD power amplifier                                                                                                                                                |

| 3.2        | Simulation waveforms for drain-efficiency with the technology models of on-chip inductors (solid lines) and the estimated efficiency from the theoretical analysis (dashed lines). |

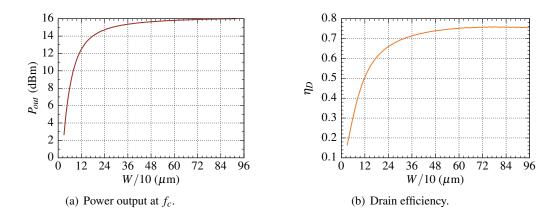

| 3.3        | Impact of the transistors size on the drain efficiency and power outuput of the PA. 38                                                                                             |

| 3.3<br>3.4 | NMOS-RF transistor <i>I-V</i> characteristics.       39                                                                                                                            |

| 5.4        |                                                                                                                                                                                    |

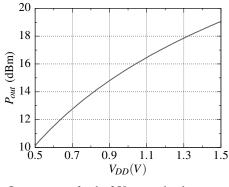

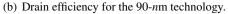

| 3.5         | Output power and drain efficiency for the 90-nm and 350-nm processes, varying                             |    |

|-------------|-----------------------------------------------------------------------------------------------------------|----|

|             | the supply voltage.                                                                                       | 40 |

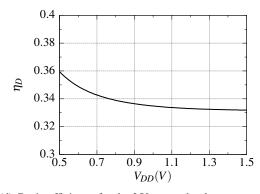

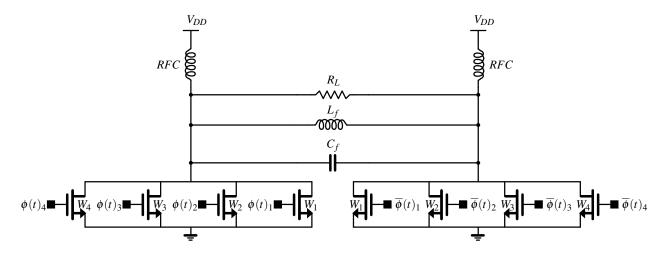

| 3.6         | Cascode configuration of the CMCD power amplifier                                                         | 41 |

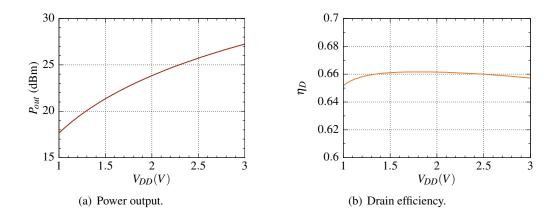

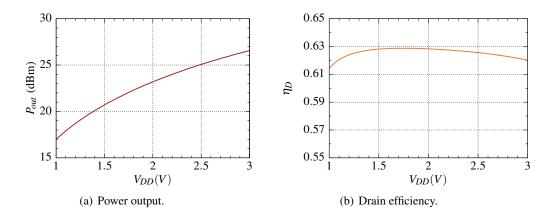

| 3.7         | CMCD PA cascode configuration $P_{out}$ and $\eta_D$ for several values of $V_{DD}$                       | 41 |

| 3.8         | Power control configuration of the CMCD power amplifier                                                   | 42 |

| 3.9         | Cascode power control configuration of the CMCD power amplifier                                           | 43 |

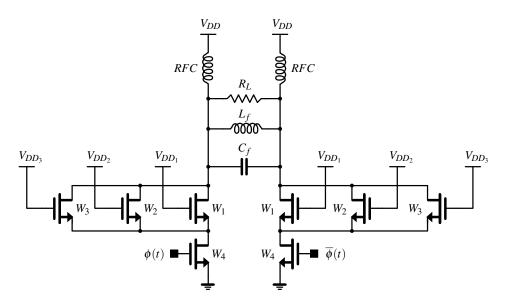

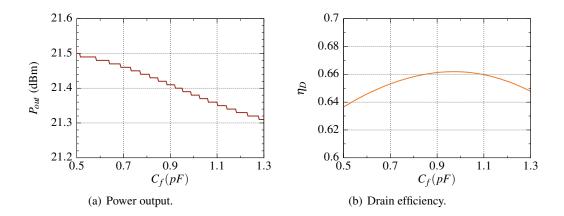

| 3.10        | $P_{out}$ and $\eta_D$ obtained for several values of $C_f$                                               | 44 |

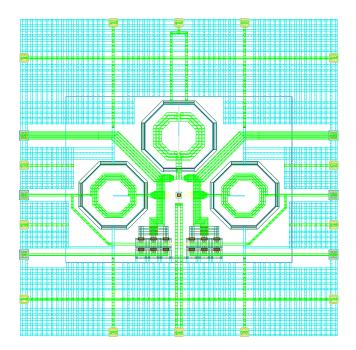

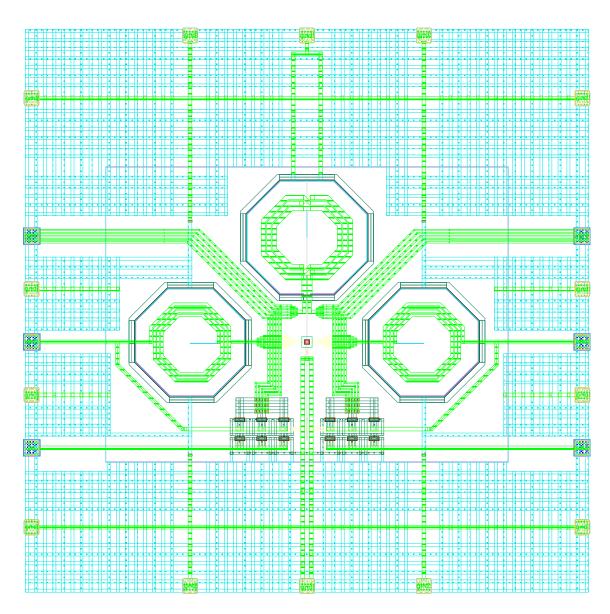

| 3.11        | CMCD power amplifier layout $(1875 \times 1875 - \mu m^2)$                                                | 45 |

| 3.12        | $P_{out}$ and $\eta_D$ of Assura and Calibre extractions, for several values of $C_f$                     | 46 |

| 3.13        | $P_{out}$ and $\eta_D$ obtained with <i>Calibre</i> parasitic extraction for several values of $V_{DD}$ . | 48 |

| Δ 1         | CMCD power amplifier layout $(1875 \times 1875 - \mu m^2)$                                                | 53 |

| <b>A</b> .1 | $e_{\text{MeD}}$ power amplifier rayout (1075x1075- $\mu$ m)                                              | 55 |

## **List of Tables**

| 1.1 | Bluetooth power classes                                      |

|-----|--------------------------------------------------------------|

| 1.2 | Bluetooth ACP requisites                                     |

| 1.3 | Transistor conduction percentage of the RF cycle             |

| 1.4 | State of the art of <i>Bluetooth</i> amplifiers              |

| 1.5 | State of the art of class- $D^{-1}$ amplifiers               |

| 3.1 | Power output and drain efficiency with power control         |

| 3.2 | Power output and drain efficiency with cascode power control |

| 3.3 | Post-layout simulation results                               |

| 3.4 | Post-layout simulation results with re-tuning                |

# **Abbreviations and Symbols**

List of abbreviations

| ACP   | Adjacent Channel Leakage Power             |

|-------|--------------------------------------------|

| BFC   | Big Fat Capacitor                          |

| CMCD  | Current-Mode Class-D                       |

| CMOS  | Complementary Metal-Oxide Semiconductor    |

| DPSK  | Differential Phase-Shift Keying            |

| DQPSK | Differential Quadrature Phase-Shift Keying |

| DRC   | Design Rule Check                          |

| FOM   | Figure Of Merit                            |

| GFSK  | Gaussian Frequency-Shift Keying            |

| HS    | High Speed                                 |

| IC    | Integrated Circuit                         |

| ISM   | Industrial, Scientific and Medical         |

| LVS   | Layout Versus Schematic                    |

| MMSIM | Multi-Mode Simulation                      |

| PA    | Power Amplifier                            |

| PAE   | Power Added Efficiency                     |

| RF    | Radio-Frequency                            |

| RFC   | Radio-Frequency Choke                      |

| SMPA  | Switch-Mode Power Amplifier                |

| VMCD  | Voltage-Mode Class-D                       |

| ZCS   | Zero-Current-Switching                     |

| ZVS   | Zero-Voltage-Switching                     |

|       |                                            |

## List of symbols

| $\eta_D$               | Drain efficiency              |

|------------------------|-------------------------------|

| $f_c$                  | Central frequency             |

| $Q_L$                  | Loaded quality factor         |

| $Q_u$                  | Unloaded quality factor       |

| ω                      | Angular frequency             |

| $\omega_c$             | Central angular frequency     |

| <i>r</i> <sub>on</sub> | Transistor on-resistance      |

| V <sub>break</sub>     | Transistors breakdown voltage |

|                        |                               |

## ABBREVIATIONS AND SYMBOLS

# Chapter 1

## Introduction

Power amplifiers (PA) account for a good part of the power consumption in an RF transceiver. The need for higher efficiencies is putting pressure on the research for new PA architectures, and consequently from it new problems are deriving. Concurrently, low-cost and high integration capabilities are also important factors when considering the hardware support to build the transceiver. These are factors that match with CMOS technologies, and this is one of the reasons for the amount of new work being reported on CMOS transceivers, and also on PA design. However, thin gate transistors operate at very low power voltages, putting a limit on power transmission, especially with the most efficient PAs such as class E. The main goal of this project is to study a class-D based power amplifier (PA) not yet reported in CMOS technology. This is a non-linear amplifier similar to class  $E^1$ , but with the benefit of theoretically more output power capability.

In this chapter a brief introduction to several classes of amplifiers is described, as well as a short survey on the selected communication standard. A state of the art showing published works with results achieved by several classes of amplifiers working on 2.45GHz is then presented. Some implementations of current-mode class-D (CMCD) power amplifiers are also discussed.

## 1.1 Motivation

Communication is essential to society as we know it, thus any evolution that leads to improvement in this field is always important. The continuous growth of interests in mobile communications creates new problems in the integrated circuit (IC) design field, namely in CMOS implementations because of the typical high-frequencies involved in these systems. Power amplifiers are the main block of any wireless transmitter. However, low efficiency can be a strong detriment to its application, because the battery life-time of portable devices gets compromised by power needs. Besides the high-efficiency concern, mobile communication systems also demand for cheap and reliable technologies.

<sup>&</sup>lt;sup>1</sup>In the sense that is also a zero-voltage-switching power amplifier.

The need for higher efficiencies in power amplifiers leads to the research of new classes that are not usually associated with radio-frequency (RF) and CMOS implementations. One example are the class-D architectures, which are normally related with audio applications. Although in theory, class-D power amplifiers can achieve 100% efficiency like other non-linear PAs, RF applications are nearly inexistent. This lack of RF applications using this class of amplifiers is the basis of the present study, which will use the class-D architecture as a starting point for a CMOS IC implementation.

As referred ahead, class-D amplifiers are in fact unsuitable for high-frequency applications, mainly due to the intrinsic parasitic capacitance of the transistors. To overcome this problem a class- $D^{-1}$  PA can be used, owing to its zero-voltage-switching (ZVS) property. Although class-E amplifiers can also overcome the parasitic capacitance problem, the CMCD power amplifier is a good solution because in theory generates lower peak voltages, being more suitable for the low breakdown voltage of CMOS devices. This dual version of the voltage-mode class-D (VMCD) amplifier with a lower drain peak voltage, still manages to get a theoretical efficiency as good as class-E architectures.

### **1.2 Bluetooth features**

In order to choose a communication standard for this project, it is necessary to select one that has proper technical requirements attainable by the proposed amplifier. The main aspects to look into are the output power and the operation frequency of the PA. After the analysis of some mobile communications standards, *Bluetooth* was chosen because it is a low power system. Table 1.1 shows the different levels required in the *Bluetooth* standard [1–3]. It is generally used for short-distance wireless communication between several devices, up to 100 meters distance.

| Class | Power (dBm) | Power (mW) | Distance (m) |

|-------|-------------|------------|--------------|

| 1     | 20          | 100        | 100          |

| 2     | 4           | 2.5        | 10           |

| 3     | 0           | 1          | 1            |

Table 1.1: Bluetooth power classes.

The *Bluetooth* operation frequency was also a favorable factor taken into consideration for our targeted technology. Operates in the industrial, scientific and medical (ISM) 2.4-GHz frequency band. This is important since it is not possible to integrate on-chip inductors and still get good results in sub-GHz CMOS implementations [4]. As referred ahead, an on-chip inductor has great impact on the overall performance of the amplifier. This make inductors critical components for PA design.

*Bluetooth* technology operates in the frequency range of 2400-2483.5-MHz. It is made up of 79 channels<sup>2</sup>, each with a 1-MHz of bandwidth. The first 2-MHz and the last 3.5-MHz are guard bands. This is to comply with out-of-band regulations in each country [3].

<sup>&</sup>lt;sup>2</sup>The 79 channels of the *Bluetooth* standard are numbered from 0 to 78.

An important measure in this standard is the adjacent channel leakage power (ACP). The leakage power interferes with adjacent channels, and a high-leakage value can ruin the system transmission capability. The transmitted power is measured in a 100-KHz bandwidth, at maximum power. Table 1.2 shows the ACP requirements for the *Bluetooth* standard [5].

Table 1.2: Bluetooth ACP requisites.

| Frequency offset | Transmitted power |  |  |

|------------------|-------------------|--|--|

| $\pm 500$        | -20dBc            |  |  |

| 2MHz             | -20dBm            |  |  |

| $\geq$ 3MHz      | -40dBm            |  |  |

The ACP test is performed in the middle channel and 3-MHz inside the upper and lower guard band limits, *i. e.* in the  $3^{rd}$ ,  $39^{th}$  and  $75^{th}$  channels. If the ACP measurement is performed in the  $3^{rd}$  channel the -20-dBm condition (table 1.2) must be checked for channels 1 and 5, and the -40-dBm condition (table 1.2) must be checked for the remaining channels [6].

Since its creation, *Bluetooth* technology has evolved and it is now on version 3.0+HS. Throughout this evolution, *Bluetooth* has improved its modulation scheme and the recent versions make use of non-constant envelope signals. Therefore, linear power amplification is now required, whose efficiency is usually low. There are alternative solutions which uses non-linear amplifiers, such as class-D, with non-constant envelope signals [7]. However, this is not the objective of the present study. We will be using the constant envelope modulation scheme employed in the first versions of *Bluetooth* that is still compatible with the newer versions.

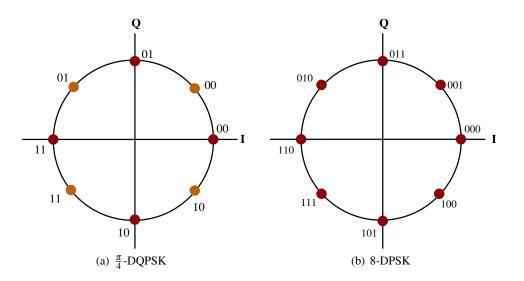

In its first version, *Bluetooth* used the GFSK modulation in which the positive and negative frequency deviations represent the binary 1 and 0, respectively. Although some recent versions use  $\frac{\pi}{4}$ -DQPSK and 8-DPSK (figure 1.1) to achieve 2-Mb/s and 3-Mb/s against the 1-Mb/s from the first version, the symbol rate remains exactly the same, *i.e.* 1-Ms/s [3].

Figure 1.1: Bluetooth modulation schemes.

Figure 1.1(a) shows the  $\frac{\pi}{4}$ -DQPSK modulation. It is composed by two equal constellations, 45 degrees  $\left(\frac{\pi}{4}\right)$  out-of-phase from each other. A jump between two symbols is always made with  $\frac{3\pi}{4}$ ,  $\frac{\pi}{4}$ ,  $-\frac{\pi}{4}$  or  $-\frac{3\pi}{4}$ . Therefore the symbols are always jumping between the two existing constellations.

The 8-DPSK modulation is depicted in figure 1.1(b). With this scheme it is possible to achieve data rates up to 3-Mb/s. This is due to the utilization of 3 bits, instead of the 2 bits used in the  $\frac{\pi}{4}$ -DQPSK modulation scheme, which allows a 2-Mb/s data rate.

### **1.3** Power amplifiers overview

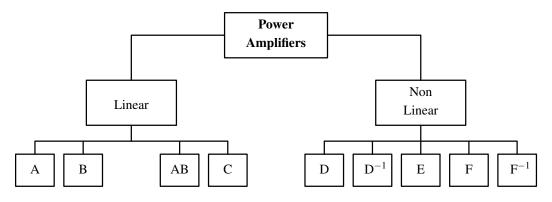

The class of a PA is defined by its operation mode, and classes can be separated onto two major groups, those that work in linear and the non-linear mode<sup>3</sup>. In figure 1.2 some classes are shown separated into the two groups.

Figure 1.2: Power amplifier classes and groups.

#### **1.3.1** Linear amplifiers

On the linear power amplifiers group, we have the classic topologies A, B, AB and C (figure 1.2). As already referred, this group of amplifiers is able to amplify signals with non-constant envelope, *i.e.* modulated amplitude signals. All these classes share a common topology, that is all of them can be implemented using the same circuit, which is depicted in figure 1.3. The amplifier class of operation is distinguished solely by the bias conditions. All these classes are driven with a sinusoidal waveform, or approximately sinusoidal, and the transistor behaves as a controlled current source, at least for a certain portion of the RF cycle [8].

The tuned parallel LC filter, shown in figure 1.3, is not part of the basic schematic circuit for this kind of amplifiers, but its recommended to filter the signal outside the fundamental frequency. This tuned filter improves the efficiency of the amplifier because the device only "sees" the load at the fundamental frequency; at all the other frequencies the filter acts as a short-circuit.

The class of operation, of linear amplifiers, can easily be identified observing the drain current waveform. The percentage of the RF cycle in which the transistor is conducting defines the

$<sup>^{3}</sup>$ We consider linear power amplification in the sense that the output magnitude is somehow linearly correlated with the input voltage.

Figure 1.3: Linear power amplifier schematic.

power amplifier operation class. Table 1.3 shows the differences between the linear classes of amplification [9].

Table 1.3: Transistor conduction percentage of the RF cycle.

| Class | RF cycle conduction (%) |

|-------|-------------------------|

| Α     | 100                     |

| В     | 50                      |

| AB    | > 50 and < 100          |

| C     | < 50                    |

#### 1.3.1.1 Class-A amplifier

To work as a class-A amplifier, the bias levels must be chosen so that the transistor is kept in the active region for all the time. Therefore the drain current waveform has a conduction angle of 360 degrees that is, 100% as shown in figure 1.4.

Figure 1.4: Class-A amplifier drain current waveform (two RF cycles shown).

Although the class-A has the highest conduction angle of all linear amplifiers, its efficiency is the lowest off all, achieving only a theoretical maximum of 50%. The class-A amplifier efficiency can be obtained through:

$$\eta_D = \frac{P_{out}}{P_{DC}} \tag{1.1}$$

$$= \frac{1}{2} \cdot \left(\frac{V_{out}}{V_{DD}}\right)^2 \tag{1.2}$$

where,  $V_{out}$  is the output voltage amplitude. Hence, it can be concluded that the amplifier only achieves its 50% of maximum efficiency, when the maximal output swing occurs. If this amplifier is used with an amplitude modulated signal, the output voltage,  $V_{out}$ , will change according to the envelope signal A(t). If we consider the probability density function of A(t), the efficiency of the amplifier will fluctuate with it, leading to an average efficiency much lower then 50% [2].

#### 1.3.1.2 Class-B amplifier

The class-B amplifiers have their bias levels chosen in a way that the drain current waveform has a conduction angle of 180 degrees. The operation point of the transistor is located exactly at the boundary between the cut-off and the active region [10]. The lower conduction angle, when compared with class-A, increases the efficiency but makes the amplifier less linear. The drain current waveform is depicted in figure 1.5.

Figure 1.5: Class-B amplifier drain current waveform (two RF cycles shown).

The drain efficiency for a class-B amplifier can be calculated as follows:

$$\eta_D = \frac{\pi}{4} \cdot \frac{V_{out}}{V_{DD}} \tag{1.3}$$

Like in the class-A, amplifier the maximum efficiency only occurs when  $V_{out} = V_{DD}$ , which leads to an approximated efficiency of 78.5% [10]. If an amplitude modulated signal is amplified, the average efficiency will also drop according to the envelope signal probability density function A(t).

#### 1.3.1.3 Class-AB and C amplifiers

The class-AB configuration works between the class-A and class-B operation, *i.e.* between 180 and 360 degrees. Therefore, depending on its bias levels this kind of amplifier conducts somewhere between 50% and 100% of an RF cycle. It can also be concluded that its drain efficiency lays somewhere between the 50% maximum of the class-A amplifier or the 78.5% of the class-B [9].

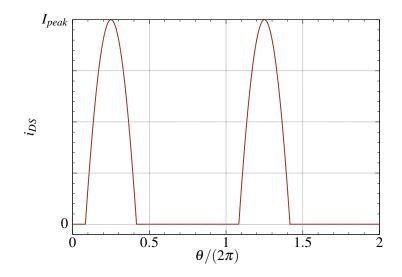

As shown in table 1.3, the class-C amplifier has the lowest conduction angle of all the linear amplifiers. Although the efficiency rises when the conduction angle is lowered, the amplifier becomes less linear because turning off the transistor increases the number of higher harmonics generated [2]. This non-ideal behavior is not considered in the present analysis. The LC resonant tank is considered to have a high-quality factor, which becomes a short circuit to other frequencies besides the central one. The drain current waveform is presented in figure 1.6.

Figure 1.6: Class-C amplifier drain current waveform (two RF cycles shown).

Some authors do not consider the class-C as part of the linear amplifiers group. This is due to its low conduction angle, which greatly reduces the drain current linearity. In fact the amplifier drain efficiency can be arbitrary increased toward 100% by decreasing the conduction angle until zero. This has the drawback of also reducing the utilization factor of the amplifier, toward zero, and increasing the drive power to the infinity [11]. The drain efficiency of a class-C amplifier can be obtained through:

$$\eta_D = \frac{\theta - \sin(\theta)}{4\left[\sin\left(\frac{\theta}{2}\right) - \frac{\theta}{2}\cos\left(\frac{\theta}{2}\right)\right]} \tag{1.4}$$

where  $\theta$  represents the conduction angle [9], which for a class-C can be (0;  $\pi$ ). Equation 1.4 is also valid for classes A, B and AB with their respective conduction angles.

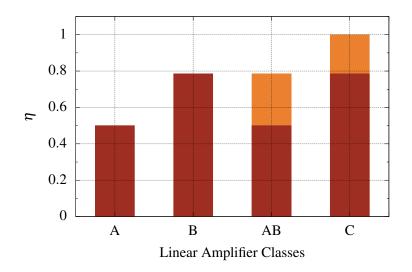

In figure 1.7 it is depicted the drain efficiency of the several linear amplifiers presented. Notice that the class-AB and C amplifiers have a range of possible values that depend on the conduction angle, as previously referred.

Figure 1.7: Efficiency of linear amplifiers.

### 1.3.2 Non-linear amplifiers

The non-linear amplifiers group are also known as switch-mode power amplifiers (SMPA). In the non-linear PAs the transistors act like switches by turning on and off during operation. In this group we have the classes D,  $D^{-1}$ , E, F and  $F^{-1}$  (figure 1.3). An ideal switch dissipates no power, for there is either zero voltage across it or zero current through it. Thus, the resultant product voltage-current is always zero. So, the transistor dissipates no power and the efficiency must be ideally 100% [9], if there are no other losses in the amplifier circuit. This makes this group of amplifiers a good solution to amplify constant envelope signals.

The class- $D^{-1}$  as the main subject of this thesis and will be discussed in detail on chapter 2. A brief analysis on the voltage-mode class-D amplifier is also described on the same chapter.

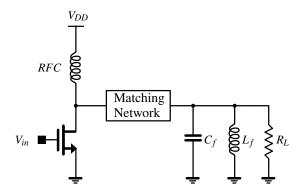

#### 1.3.2.1 Class-E

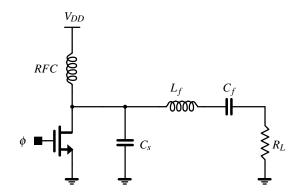

The basic configuration of a class-E power amplifier is depicted in figure 1.8. The output network is made up of a series tuned circuit RLC and a shunt capacitor  $C_s$ . This capacitor includes the inherent parasitic capacitance of NMOS transistors.

The  $C_s$  capacitance value should be carefully designed, because it is the responsible for the soft-switching capability of the class-E amplifier. Hard-switching devices suffer from switching losses. This occurs when the voltage across the transistor drops abruptly from a high value to

Figure 1.8: Class-E power amplifier schematic.

zero. The shunt capacitance  $C_s$  charges and discharges between the ON and OFF state of the transistor. Therefore,  $C_s$  does not allow instant variation in the drain voltage. This guarantees a smooth transition between the ON-OFF states of the transistor [10].

Since the class-E architecture absorbs the parasitic capacitance of the transistor with  $C_s$ , the so-called ZVS state is achieved. This prevents energy loss at each RF cycle, which is critical at high-frequencies, thus increasing the amplifier performance [2]. As further referred, this energy loss is the major drawback in the use of class-D amplifiers at high-frequencies.

Another switch characteristic responsible for efficiency drop in power amplifiers is the onresistance,  $r_{on}$ , associated with MOS transistors. This parasitic component can be diminished by increasing the transistor size, but this also increases the parasitic  $C_{DS}$  capacitor and  $C_{GS}$ , increasing driving requirements.

The voltage and current drain waveforms of the device are represented in figure 1.9.

Figure 1.9: Class-E drain current and voltage waveforms.

#### 1.3.2.2 Class-F

Class-F amplifiers present an elegant solution in order to achieve high-efficiency. This class of amplifiers is characterized by a load network with resonance frequencies at one or more harmonic

frequencies as well as at the carrier frequency (figure 1.10).

The tank resonators depicted in figure 1.10 are tuned to odd-harmonics, which maintain a square voltage waveform at the transistor drain and simultaneously provides a half-sinusoidal current waveform [12]. An infinite number of tanks must be used to set the ideal waveform shaping, figure 1.11.

Figure 1.10: Class-F power amplifier schematic with 5<sup>th</sup> harmonic peaking.

Ideally, all parallel resonant circuits have infinite impedance at the corresponding harmonic resonant frequency and zero impedance at other harmonics [12]. Consequently, the load impedance of the transistor is  $R_L$  at fundamental frequency, infinite at the tank resonators frequencies and zero otherwise [8].

From figure 1.11, we can see that ideally there is no overlap between voltage and current due to the harmonic filtering of the tank resonators. Thus, no power dissipation is produced, leading to 100% of theoretical efficiency. In practice, the infinite harmonic tuning is not achievable. Most of the times the load network is setup by harmonic filtering tuned up to the  $3^{rd}$  or  $5^{th}$  harmonic only (commonly called harmonic peaking). This lowers the attainable efficiency well below 100%.

Figure 1.11: Class-F drain current and voltage waveforms.

#### 1.3.2.3 Class-F<sup>-1</sup>

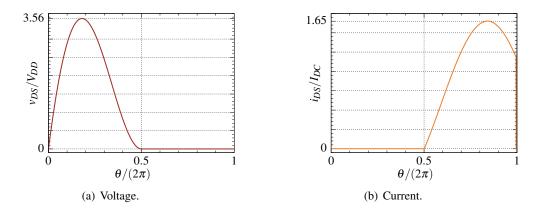

The inverse class-F power amplifier can be implemented using the circuit presented in figure 1.12. The circuit shown in figure 1.10 can also be used, but now the tank resonators need to be tuned to even-harmonic resonant frequencies. This duality in the configuration can be applied also to the inverse class-F amplifier represented in figure 1.12. Thereby, it is necessary, in this case, to perform the tuning only with even-harmonics [12].

Figure 1.12: Class- $F^{-1}$  power amplifier schematic with 5<sup>th</sup> harmonic peaking.

Analyzing the schematic represented in figure 1.12 one realizes that at the fundamental frequency and odd-harmonics, each resonant circuit has zero impedance but infinite impedance at even-harmonics. This produces the idealized square current and the half-sinusoidal voltage waveforms at the drain terminal, as shown in figure 1.13. As a result, the active device "sees" the load resistance  $R_L$  at the fundamental frequency, while the odd-harmonics are shorted by the series resonant circuits [12].

Figure 1.13: Class- $F^{-1}$  drain current and voltage waveforms.

Introduction

## 1.4 State of the art

This section presents a state of the art of reported implementations showing results achieved by several classes of amplifiers working at 2.45GHz. A comparison between some published implementations of CMCD power amplifiers is also covered.

#### **1.4.1** Amplifiers for Bluetooth

*Bluetooth* technology, in an early version, was operated with a modulation scheme that produces constant envelope signals. More recent versions uses modulation methodologies that combines two types of modulations to send data packages. The constant envelope signal of the early version is lost with the more recent modulations. In [7] is reported an implementation of a simple polar-loop transmitter with a class-E PA that is capable of working with the early version of *Bluetooth*, as well as the medium-rate non-constant envelope signal version.

A very important power amplifier figure of merit (FOM) is the power added efficiency (PAE), which can be calculated by:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}}$$

(1.5)

The PAE can be improved by applying a sliding bias technique like the one described in [13]. This technique is applied to a two stage self-biased cascode PA. PAE is in fact increased, but at the cost of a decrease in power gain.

The peak drain voltage, a problem in class-E due to the low breakdown voltage of transistors, was reduced in [14], thus lowering the chances of damaging the device due to the high drain voltages characteristic of the PAs. The power amplifier is referred as a class BE.

Interesting enough, when all losses are taken into account and for certain component values, a better performance is achievable by diverging from class-E to C [14, 15]. Combinations of distinct classes of amplifiers try to take advantage of the positive aspects of each one to produce better results than the originals. Classes BE and CE are examples of PAs that are able to reduce the peak voltage problem. Class CE has been reported in [16], but presents very low performance (PAE of 25.8%) when compared with class-AB in [1], both fabricated with  $0.25\mu$ m CMOS technologies.

The switching nonlinear amplifiers families share a common practical difficulty, the input square wave needed to achieve high amplifier efficiency. Typically, when the switching amplifiers are driven with non-square waveforms the efficiency diminishes. This is due to the fact that the amplifier momentarily operates as a current source (linear amplifier). A way to deal with this problem is to apply a solution like the one presented in paper [17], where it is described a latch-structured pre-amplifier followed by a class-E PA. The pre-amplifier enables a more ideal switching waveform for the PA, reducing the rise and fall times of the driving signals. The procedure effectively reduces the voltage-current overlap on the switch, optimizing the efficiency of the system. Excellent results are obtained with PAE in the order of 66% [17].

Another work that shows a solution to solve the square wave driving issue is presented in [18]. Here a classical class-E PA is driven by a class-F amplifier to provide a better switching behavior, hence improving the efficiency of the amplifier.

Although the early version of *Bluetooth* was based on constant envelope modulation schemes, linear PA classes have been extensively used. A single-ended two-stage common-source topology biased in class-AB operation is presented in [1]. It uses MOS transistor models developed specifically by *Philips* for high-frequencies with low supply voltage. A maximum PAE of 48% is attained for 24dBm of output power. The referred study also addresses the hot carrier effect as a reliability measurement of the amplifier. This effect happens when high-electric fields, near the drain, damage the crystalline structure of the transistor, increasing threshold voltage and also degrading the overall performance of the device. The hot carrier effect is also responsible for inducing noise into the circuit [19].

A class-AB amplifier is also implemented in [20]. The proposed configuration uses two parallel output stages that can provide different levels of output power. With only one active output stage, the impedance seen by the device is different from the case when the two stages are on, by then controlling delivered output power. A PAE of 22% is achieved with 22.7dBm for output power.

Another configuration that allows different levels of output power is presented in [14]. A set of four amplifiers are implemented on-chip within a differential topology, thus producing two differential power amplifiers. The amplifiers are combined with an on-chip LC balun structure, which also performs impedance transformation that increases the amplifiers output power capability. However the PAE is still very low, 29%. The power control feature is done by turning on or off the circuit amplifiers. When a set of amplifiers is off, the LC balun section becomes a high-impedance parallel tank, connected in parallel with the load.

Table 1.4 shows a short compilation of results obtained in the previously discussed works and others. This gives us a perspective on how the research is currently being performed in this field. All the class-E implementations have more than 30% in PAE. Most of the works have an output power of about 20dBm. One can also note that drain efficiency values are quite higher for switching PAs. On the other hand, due to the need for square wave drive,  $P_{in}$  can be higher when compared to linear PAs. The dissipated power value turns out to be lower in switching PAs, thus justifying the higher PAE achieved in switching PA classes.

Note that not a single class-D amplifier is reported in table 1.4 since it cannot be found in literature for 2.45GHz. This somehow indicates its inability to produce good results at RF frequencies.

### **1.4.2** Class-D<sup>-1</sup> amplifiers

A straightforward comparison between the VMCD and CMCD architectures is performed in [26]. The inability of VMCD to work at high-frequencies is presented. The main responsible is, as already referred, the inexistent ZVS condition. The CMCD is presented as a solution. A

Introduction

| Class | Technology ( $\mu$ m) | Max. power (dBm) | PAE (%) | $\eta_D$ (%) | Ref. | Year |

|-------|-----------------------|------------------|---------|--------------|------|------|

| AB    | CMOS 0.25             | 24               | 48      | -            | [1]  | 2001 |

| AB    | CMOS 0.35             | 19               | 33.7    | -            | [21] | 2006 |

| AB    | CMOS 0.18             | 3.5              | -       | 16           | [22] | 2003 |

| AB    | CMOS 0.25             | 22.7             | 22      | -            | [20] | 2003 |

| В     | CMOS 0.24             | 23               | 39      | 45           | [23] | 2000 |

| BE    | CMOS 0.13             | 23               | 29      | 35           | [14] | 2007 |

| CE    | CMOS 0.25             | 21.4             | 25.8    | 38           | [16] | 2002 |

| E     | CMOS 0.25             | 20               | 65.8    | 66.4         | [17] | 2005 |

| E     | CMOS 0.35             | 13               | 30.7    | -            | [7]  | 2005 |

| E     | CMOS 0.35             | 20               | 59      | 64           | [18] | 2003 |

| E     | CMOS 0.35             | 20               | 35      | -            | [24] | 2003 |

| F     | BiCMOS 0.24           | 20               | 34.2    | -            | [25] | 2006 |

| -     | CMOS 0.18             | 23               | 42      | -            | [13] | 2003 |

Table 1.4: State of the art of *Bluetooth* amplifiers

theoretical analysis of a class- $D^{-1}$  is also described in [26] as well the circuit implementation and its results.

In [27] the characteristics of both VMCD and CMCD power amplifiers are also described. Several design considerations are discussed, like the high-order odd harmonic effects, as well as the parasitic resistance of the LC resonator. This parasitic resistance might be of great importance, because it is pointed out as a critical part of the overall system. Two different amplifiers were fabricated, one with a bond-wire and the other with an on-chip spiral inductor. Better results were achieved with the bond-wire implementation due to the high-quality factor that this solution provides. Also in work [27], input and output baluns are used in order to get unbalanced input and output, while the PA works in differential mode.

Works [28–31] present CMCD power amplifiers manufactured in various technologies. Different implementation methodologies applied in the design process of these PAs are exposed in each work. A direct explanation about the advantage of ZVS amplifiers over the non-ZVS is made in [28]. Work [29] reports the highest output power of all CMCD power amplifiers presented, and the second best drain efficiency. Another comparison between the the voltage-mode and currentmode class-D power amplifiers is made in [30]. The class-D<sup>-1</sup> basic principles of operation are also discussed in [31].

Table 1.5 shows the results obtained for the discussed CMCD amplifiers. However, none of these works operate at our frequency of interest, 2.45GHz, neither are implemented in Si-CMOS.

Technology Frequency (GHz) Max. power (dBm)  $\eta_D$  (%) Ref. Year 76.3 GaAs FET 0.9 [26] 24.6 2001 GaAs HBT 0.7 29.5 78.5 [27] 2005 GaN HEMT 1 36 64.4 [28] 2007 0.9 GaN MESFET 43.2/47.1 75/78 [29] 2007 LDMOS 1 41.1 60 [30] 2002 1 71 LDMOS 43.1 [31] 2006

Table 1.5: State of the art of class- $D^{-1}$  amplifiers

Introduction

### Chapter 2

## **Class-D**<sup>-1</sup> **Power Amplifier**

This chapter presents a group of analysis on the class- $D^{-1}$  power amplifier behavior. First the basic operation of the amplifier is demonstrated. Next, an ideal analysis comprising the key features of the CMCD power amplifier, like the ZVS state and its low peak drain voltage, is presented. The main FOM are also analyzed.

The last study focuses on the non-ideal behavior of the CMCD power amplifier. A study on the impact of the load network quality factor in the circuit performance is first presented. Afterward, a study is made to understand the influence of the inductor unloaded quality factor, along with QL, has on amplifier efficiency.

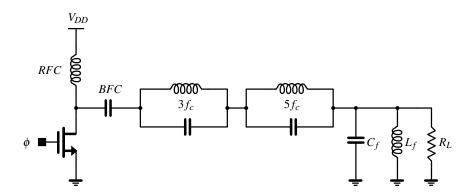

#### 2.1 Current-Mode Class-D power amplifier

The current-mode class-D power amplifier is the dual version of the voltage-mode class-D power amplifier. Its architecture is shown in figure 2.1. As presented, the CMCD is constituted by two branches, each with a radio-frequency choke (RFC) and an NMOS transistor. A RLC differential network, tuned to the central frequency, connects the two branches of the circuit.

Like any other SMPA, the class- $D^{-1}$  power amplifier can achieve 100% of theoretical efficiency since the transistors act like switches, maximizing this way the amplifier performance. This high theoretical efficiency is achieved because ideal switches only have voltage across them or current flowing through<sup>1</sup>, never both at the same time. This non-overlapping of voltage and current means that no power dissipation is produced, thus the PA manages to achieve 100% of theoretical efficiency. However, available transistors are not ideal switches, because they have parasitic capacities and inductors as well as finite on resistance  $r_{on}$ , which degrades the overall performance of the amplifier [26].

<sup>&</sup>lt;sup>1</sup>An open ideal switch has only a voltage drop across him, while a closed one only has current flowing through.

Figure 2.1: Circuit of the CMCD power amplifier.

#### 2.2 Basic operation

In this current-mode class-D amplifier configuration, the transistors are driven by two square waves, in opposite phase. Then only one transistor will be switched on at a time. Since the RFCs act like DC current sources, the current is always switching from one branch of the circuit to the other, passing through the RLC network. From here, we can say that the current is a square waveform with 50% of duty-cycle in each side of the circuit, and with 180 degrees out-of-phase. This operation is depicted in figure 2.2.

Figure 2.2: Current flow in the class- $D^{-1}$  power amplifier.

One can then say that a zero centred square current waveform is applied to the RLC network. This waveform can be derived through the Fourier series,

$$i_{RLC}(\theta) = \sum_{-\infty}^{0} i_{-k} e^{jk\theta} + \sum_{0}^{\infty} i_{k} e^{-jk\theta}$$

(2.1)

#### 2.2 Basic operation

$$= i_0 + \sum_{k=1}^{\infty} i_k (e^{jk\theta} + e^{-jk\theta})$$

(2.2)

where  $\theta = \omega_0 t$  and  $i_k = i_{-k}$  because  $i_{RLC}(\theta)$  its an even function.

The first member of equation 2.2 can be obtained through,

$$i_{0} = \frac{1}{\pi} \int_{-\pi}^{\frac{-\pi}{2}} \frac{-I_{peak}}{\omega_{0}} e^{0} d\theta + \frac{1}{2\pi} \int_{\frac{-\pi}{2}}^{\frac{\pi}{2}} \frac{I_{peak}}{\omega_{0}} e^{0} d\theta$$

(2.3)

which leads to  $i_0 = 0$ . We can also calculate  $i_k$  as follows:

$$i_{k} = \frac{1}{\pi} \int_{-\pi}^{\frac{-\pi}{2}} \frac{-I_{peak}}{\omega_{0}} e^{-jk\theta} d\theta + \frac{1}{2\pi} \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{I_{peak}}{\omega_{0}} e^{-jk\theta} d\theta$$

(2.4)

$$= \frac{8I_{peak}}{k\pi} \sin\left(\frac{k\pi}{4}\right)^3 \cos\left(\frac{k\pi}{4}\right)$$

(2.5)

Combining equations 2.2 and 2.5, gives us the square waveform formula,

$$i_{RLC}(\theta) = \sum_{k=1}^{\infty} \frac{16I_{peak}}{k\pi} \sin\left(\frac{k\pi}{4}\right)^3 \cos\left(\frac{k\pi}{4}\right) \cos(k\theta)$$

(2.6)

which can be simplified to look like,

$$i_{RLC}(\theta) = \sum_{k_{odd}}^{\infty} \frac{4I_{peak}}{k\pi} \sin\left(\frac{k\pi}{2}\right) \cos(k\theta)$$

(2.7)

$$= \frac{4I_{peak}}{\pi} \sum_{k_{odd}}^{\infty} \frac{1}{k} \cos(k\theta + \varphi_k)$$

(2.8)

where  $\varphi_k$  assumes the following values:

$$\begin{cases} 0 & k = 1, 5, 9, \dots \\ \pi rad & k = 3, 7, 11, \dots \end{cases}$$

(2.9)

Since the RLC parallel network is tuned at the fundamental frequency  $f_c$ , at all the other frequencies it acts like a short-circuit. This way, there is only current flowing through  $R_L$  at the frequency of interest, *i.e.* a sinusoidal current waveform<sup>2</sup>. Therefore, a sinusoidal voltage waveform is also present at the  $R_L$  load, which means a semi-sinusoidal waveform at each branch of the circuit. Thus, the voltage at the load network can be expressed as follows:

<sup>&</sup>lt;sup>2</sup>Assuming that we have an infinite quality factor  $Q_L$ .

$$v_{RLC}(\theta) = |I_1| R_L \cos(\theta + \varphi_1)$$

(2.10)

$$= \frac{4}{\pi} I_p R_L \cos(\theta) \tag{2.11}$$

Because there is no voltage drop across the RFCs, and having a semi-sinusoidal waveform with a mean value  $V_{DD}$  at each branch the peak drain voltage is  $\pi V_{DD}$  [26]. This can be obtained through:

$$V_{DD} = \frac{1}{2\pi} \int_{0}^{\pi} \frac{v_{DS}(\theta)}{\omega} d\theta \qquad (2.12)$$

$$= \frac{1}{2\pi} \int_{0}^{\pi} \frac{V_{peak} \sin(\theta)}{\omega} d\theta \qquad (2.13)$$

$$= \frac{V_{peak}}{\pi} \tag{2.14}$$

In figure 2.3 a comparison between the drain peak values of several SMPA is made. It can be noticed that there are classes with a lower peak drain voltage than the CMCD, namely the class-D, the class-F and its inverse architecture. As further referred ahead, the VMCD power amplifier, with a peak drain voltage value equal to  $V_{DD}$  [10], is unable to work at high frequencies due to the intrinsic parasitic capacitance of the active devices. The class-F amplifier and its dual version, with a peak voltage of  $2V_{DD}$  and  $\frac{\pi V_{DD}}{2}$  respectively [12], depend on the number of attainable harmonic tuning, which in practice lowers the overall efficiency.

We can now represent the ideal waveforms for the class- $D^{-1}$  PA. To perform this, we also need to calculate the value of the peak drain current. Having  $V_{peak}$ , the peak current value can be obtained through:

$$I_{peak} = \frac{\pi^2}{4} \cdot \frac{V_{DD}}{R_L} \tag{2.15}$$

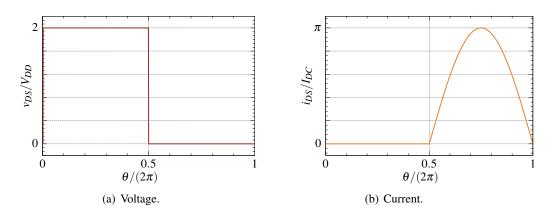

With the peak values of the drain voltage and current and considering a infinite quality factor  $Q_L$  for the load network, we have a half-sinusoidal wave and a 50% duty-cycle square waveform for the drain voltage and current respectively, at each branch of the circuit depicted in figure 2.1. The ideal waveforms for the CMCD power amplifier can be represented as in figure 2.4.

#### 2.3 Ideal analysis

As already said before, transistors are not ideal switches with their inherent parasitic components such as the intrinsic capacity  $C_{DS}$ , the finite on-resistance  $r_{on}$  and an associated parasitic

Figure 2.3: Drain peak voltage of several SMPA.

inductor. In fact, the key issue related to the inability of applying the VMCD power amplifier at RF frequencies is the  $C_{DS}$  parasitic capacitance, that exists in all transistors. In figure 2.5 the basic schematic for a class-D power amplifier is presented.

The  $C_{DS}$  parasitic capacitance of the transistors will charge during turn on to  $V_{DD}$ , so the instant non-null overlapping of voltage and current cannot be avoided. This causes an energy accumulation:

$$E_C = \frac{1}{2} C_{DS} V^2 \tag{2.16}$$

in  $C_{DS}$  that is dissipated in  $r_{on}$  and reduces the overall efficiency of the amplifier [27]. The power dissipation can be described by:

$$P_{diss} = \frac{1}{2} f C_{DS} V^2 \tag{2.17}$$

The power dissipation increases with the frequency of operation of the devices, making the class-D architecture not good solution for RF applications [2].

A possible solution to solve the voltage and current overlap problem is to apply a ZVS amplifier architecture. This can be accomplished using the class- $D^{-1}$  PA (figure 2.1). If the RLC load network has an infinite quality factor  $Q_L$ , which can be expressed by:

$$Q_L = \frac{R_L}{\omega_c L} \tag{2.18}$$

the load acts like a short circuit at all frequencies except at the fundamental. This guarantees that there is no voltage across the transistors at the switching time, and the so-called ZVS is achieved. Therefore, the VMCD problem is apparently solved. Other PA architectures can also achieve ZVS, like the class-E and the class-F. While the class-E PA has a higher peak drain voltage than

Figure 2.4: CMCD power amplifier waveforms.

Figure 2.5: Circuit of the VMCD power amplifier.

the CMCD<sup>3</sup> [2, 10, 12], which is important due to the low breakdown voltage of CMOS devices, the class-F is limited to the finite harmonic tuning that lowers his overall performance.

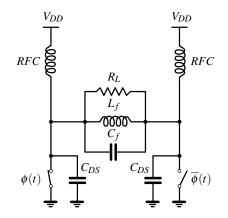

In the class-D<sup>-1</sup> architecture, even the  $C_{DS}$  parasitic capacitances are absorbed and become part of the parallel filter. In figure 2.6,  $\phi(t)$  is on with its parasitic capacity shorted to GND while the  $C_{DS}$  capacitance of the other switch is in parallel with  $C_f$ . The same occurs when  $\overline{\phi}(t)$  is on due to the circuit symmetry. The ZVS state along with a lower drain peak voltage are the key features of the CMCD power amplifier.

Figure 2.6: Class- $D^{-1}$  power amplifier with parasitic capacities.

Another important feature to take into account in a power amplifier is the zero-current-switching (ZCS), which avoids inductance losses by making the current zero at the switching instant. This energy loss can be obtained through:

$$E_I = \frac{1}{2}LI^2$$

(2.19)

Although this feature is not present in the the class- $D^{-1}$  power amplifier, it is less important than the ZVS, because the way transistors are modeled [26]. However it is important to diminish its value in order to improve the amplifier efficiency.

<sup>&</sup>lt;sup>3</sup>The class-E power amplifier has a peak drain voltage of approximately 3.56 $V_{DD}$ , while the CMCD peak voltage value is  $\pi V_{DD}$ .

Another relevant FOM of a power amplifier is the output power it can deliver, *i. e.* the power dissipated in  $R_L$  at  $f_c$ . This can be easily obtained through:

$$P_{out} = \frac{1}{2} \operatorname{Re}\{V_{RLC}I_{RLC}^*\}$$

(2.20)

$$= \frac{8}{\pi^2} R_L I_{peak}^2 \tag{2.21}$$

$$= \frac{\pi^2}{2} \cdot \frac{V_{DD}^2}{R_L} \tag{2.22}$$

Calculating the supplied power to the circuit leads to:

$$P_{DC} = V_{RLC} I_{RLC} \tag{2.23}$$

$$= \frac{\pi^2}{2} \cdot \frac{V_{DD}^2}{R_L} \tag{2.24}$$

With  $P_{out}$  and  $P_{DC}$  its possible to evaluate another important FOM in the power amplifiers domain, the drain efficiency  $\eta_D$ . This quality measure of a PA can be obtained with,

$$\eta_D = \frac{P_{out}}{P_{DC}} \tag{2.25}$$

which in a class- $D^{-1}$ , like in other SMPA architectures considering all the components lossless, achieves a theoretical efficiency of 100%.

The different classes of power amplifiers do not differ solely in the method of operation and in the efficiency capability. The transistor utilization factor is also an important FOM of a power amplifier [11]. This relevant measure is expressed by:

$$U_f = \frac{1}{n} \cdot \frac{P_{out}}{V_{peak}I_{peak}}$$

(2.26)

Applying the equation to the CMCD power amplifier we obtain a  $\frac{1}{2\pi}$  utilization factor. A comparison between the  $U_f$  of several classes of power amplifiers is made in figure 2.7. Here we can see that the CMCD power amplifier and its voltage mode dual architecture, the class-D PA, have the highest utilization factor of all [11]. This indicates a good exploitation of the circuit resources.

The  $U_f$  for the class-F, and its inverse version, assumes different values according to the number of harmonic tuning that is applied. The lowest value, with just one harmonic tuning, is the same as the one obtained in power amplifier classes A an B, *i*.  $e \frac{1}{8}$ , while the highest equals the classes D and D<sup>-1</sup> [11]. Opposing to this attainable high utilization factor is the class-E PA, which has the lowest  $U_f$  from all the compared classes in the chart [11, 12].

Figure 2.7: Utilization factor comparison between several power amplifiers.

#### 2.4 Non-ideal analysis

In this section of the class- $D^{-1}$  power amplifier analysis, the parasitic components that cause a non-ideal behavior will be taken into account. The first study is the impact of the RLC network quality factor in the performance of the amplifier. Next the inductor unloaded quality factor  $Q_u$ influence is also studied, along with the  $Q_L$  quality factor.

#### **2.4.1** Impact of *Q<sub>L</sub>* in the circuit performance

To study the effect of the RLC network quality factor, we consider the transistors as ideal switches that is, with zero  $r_{on}$  and free of any other parasitic components. The RFCs are also considered to be ideal current sources, providing in both sides of the circuit an equal current. Having this in mind, to better perform an analysis on the RLC network we can transform the CMCD basic architecture into an equivalent electric circuit, depicted in figure 2.8.

Figure 2.8: CMCD ideal architecture and equivalent circuit.

The equation of the load network is given by:

$$Z_{eq} = \frac{j\omega R_L L_f}{R_L - R_L L_f C_f \omega^2 + j\omega L_f}$$

(2.27)

$$= R_L \cdot \frac{k^2 + jkQ_L(1-k^2)}{k^2 + Q_L^2(1-k^2)^2}$$

(2.28)

where for every harmonic,

$$\boldsymbol{\omega} = k\boldsymbol{\omega}_c \tag{2.29}$$