Theses & Dissertations

http://open.bu.edu

Boston University Theses & Dissertations

### 2016

# Fluigi: an end-to-end software workflow for microfluidic design

https://hdl.handle.net/2144/14628 Boston University

# BOSTON UNIVERSITY COLLEGE OF ENGINEERING

Dissertation

# FLUIGI: AN END-TO-END SOFTWARE WORKFLOW FOR MICROFLUIDIC DESIGN

by

## HAIYAO HUANG

M.Eng., Massachusetts Institute of Technology, 2007

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2016

## © 2016 by

HAIYAO HUANG

All rights reserved except for Chapter 2 which is ©2014 by The Royal Society of Chemistry and Section 3.3 which ©2014 ACM, Inc. Reprinted with permission.

## Approved by

First Reader

Douglas Densmore, PhD Associate Professor of Electrical and Computer Engineering

Second Reader

Ayse Coskun, PhD Associate Professor of Electrical and Computer Engineering

Third Reader

Ahmad S. Khalil, PhD Assistant Professor of Biomedical Engineering

Fourth Reader

Martin Herbordt, PhD Professor of Electrical and Computer Engineering

## Acknowledgments

I would like thank my advisor Douglas Densmore for giving me the chance to continue working in synthetic biology after I had a minor crisis of conscience working in industry. The last four years have been a wonderful experience.

I would like to thank Professor Ahmad Khalil for letting me borrow his lab space and equipment for making and testing microfluidics, and for the initial ideas of exploring the space of automating microfluidic design; and his graduate students Ali Beyzavi and Brandon Wong for teaching me how to fabricate molds in the clean room.

I'd like to thank Professor Ayse Coskun and Professor Martin Herbordt for being on my committee and providing valuable feedback during the prospectus.

I'd like to thank Swapnil Bhatia for his assistance with the early ideas on using biological circuits in microfluidics and Ernst Oberortner for his assistance working with ANTLR. I'd also like to thank Traci Haddock for keeping peace in the lab and during lab meetings and preventing the members of the computational side of things from damaging themselves and their experiments in the wet lab.

I'd like to thank my labmates in the CIDAR lab, most notably Ryan Silva, Sonya Iverson, and Aaron Heuckroth, for getting the Fluigi project off the ground, and for some unforgettable memories of white elephant gift swaps and that one trip to Maine.

Finally, I'd like to thank my husband Jim Waldrop for his continued moral support during my time as a graduate student and the household felines for keeping me company while I coded.

# FLUIGI: AN END-TO-END SOFTWARE WORKFLOW FOR MICROFLUIDIC DESIGN

## HAIYAO HUANG

Boston University, College of Engineering, 2016

Major Professor: Douglas M. Densmore, PhD Associate Professor of Electrical and Computer Engineering

### ABSTRACT

One goal of synthetic biology is to design and build genetic circuits in living cells for a range of applications with implications in health, materials, and sensing. Computational design methodologies allow for increased performance and reliability of these circuits. Major challenges that remain include increasing the scalability and robustness of engineered biological systems and streamlining and automating the synthetic biology workflow of specify-design-build-test.

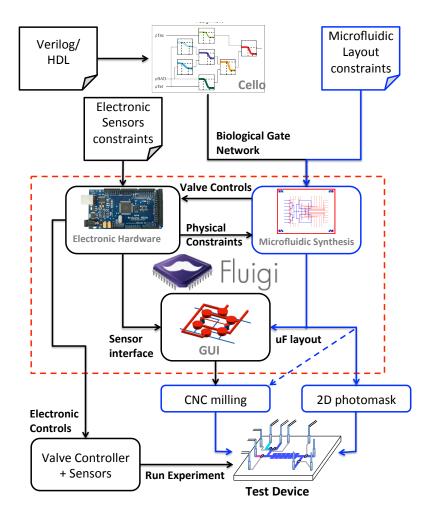

I summarize the advances in microfluidic technology, particularly microfluidic large scale integration, that can be used to address the challenges facing each step of the synthetic biology workflow for genetic circuits. Microfluidic technologies allow precise control over the flow of biological content within microscale devices, and thus may provide more reliable and scalable construction of synthetic biological systems. However, adoption of microfluidics for synthetic biology has been slow due to the expert knowledge and equipment needed to fabricate and control devices. I present an end-to-end workflow for a computer-aided-design (CAD) tool, Fluigi, for designing microfluidic devices and for integrating biological Boolean genetic circuits with microfluidics. The workflow starts with a "netlist" input describing the connectivity of microfluidic device to be designed, and proceeds through placement, routing, and design rule checking in a process analogous to electronic computer aided design (CAD). The output is an image of the device for printing as a mask for photolithography or for computer numerical control (CNC) machining. I also introduced a second workflow to allocate biological circuits to microfluidic devices and to generate the valve control scheme to enable biological computation on the device.

I used the CAD workflow to generate 15 designs including gradient generators, rotary pumps, and devices for housing biological circuits. I fabricated two designs, a gradient generator with CNC machining and a device for computing a biological XOR function with multilayer soft lithography, and verified their functions with dye. My efforts here show a first end-to-end demonstration of an extensible and foundational microfluidic CAD tool from design concept to fabricated device. This work provides a platform that when completed will automatically synthesize high level functional and performance specifications into fully realized microfluidic hardware, control software, and synthetic biological wetware.

# Contents

| 1        | Intr | oducti  | ion                                                              | 1  |

|----------|------|---------|------------------------------------------------------------------|----|

| <b>2</b> | Bac  | kgrou   | nd                                                               | 5  |

|          | 2.1  | Engin   | eering biology                                                   | 6  |

|          |      | 2.1.1   | Boolean logic in biological devices                              | 8  |

|          |      | 2.1.2   | Memory and state in biological devices                           | 9  |

|          |      | 2.1.3   | Specify-Design-Assemble-Verify workflow                          | 9  |

|          | 2.2  | Micro   | fluidics                                                         | 11 |

|          |      | 2.2.1   | Device physics                                                   | 12 |

|          |      | 2.2.2   | Design and fabrication                                           | 13 |

|          |      | 2.2.3   | Microfluidic large scale integration                             | 15 |

|          | 2.3  | Using   | microfluidics to solve challenges in synthetic biology           | 16 |

|          |      | 2.3.1   | Specification                                                    | 19 |

|          |      | 2.3.2   | Design                                                           | 24 |

|          |      | 2.3.3   | Assembly                                                         | 29 |

|          |      | 2.3.4   | Verification                                                     | 33 |

|          | 2.4  | Haster  | ning adoption of microfluidics                                   | 35 |

|          |      | 2.4.1   | Design automation in microfluidics                               | 36 |

|          |      | 2.4.2   | An end-to-end automated workflow for microfluidic design $\ .$ . | 38 |

| 3        | Firs | t foray | ys into microfluidic CAD                                         | 40 |

|          | 3.1  | Motiv   | ation                                                            | 40 |

|          | 3.2  | First i | teration                                                         | 44 |

|   |                | 3.2.1   | Architecture               | 44  |

|---|----------------|---------|----------------------------|-----|

|   |                | 3.2.2   | Workflow                   | 46  |

|   |                | 3.2.3   | Results                    | 50  |

|   |                | 3.2.4   | Flaws                      | 55  |

|   | 3.3            | Second  | d iteration                | 55  |

|   |                | 3.3.1   | Architecture               | 55  |

|   |                | 3.3.2   | Workflow                   | 57  |

|   |                | 3.3.3   | Results                    | 64  |

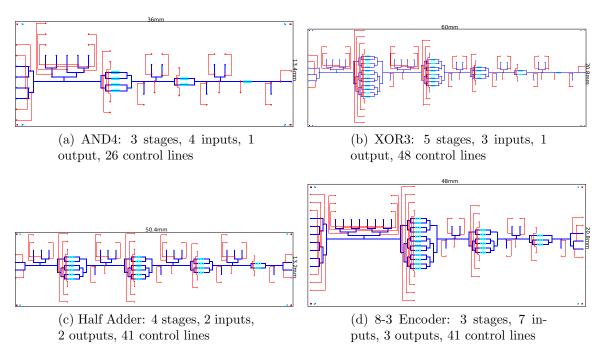

|   |                | 3.3.4   | Benchmark circuits         | 64  |

|   |                | 3.3.5   | Example circuits           | 66  |

|   |                | 3.3.6   | Flaws                      | 68  |

| 4 | $\mathbf{Des}$ | ign are | chitecture                 | 70  |

|   | 4.1            | Device  | e model                    | 70  |

|   | 4.2            | Impler  | mentation                  | 71  |

|   | 4.3            | Netlist | t rules                    | 72  |

|   |                | 4.3.1   | Device declaration         | 73  |

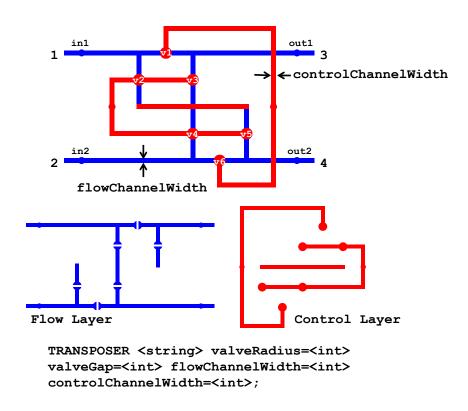

|   |                | 4.3.2   | Primitives                 | 75  |

|   |                | 4.3.3   | Channel                    | 80  |

|   |                | 4.3.4   | Modules                    | 82  |

|   |                | 4.3.5   | 3D structures              | 91  |

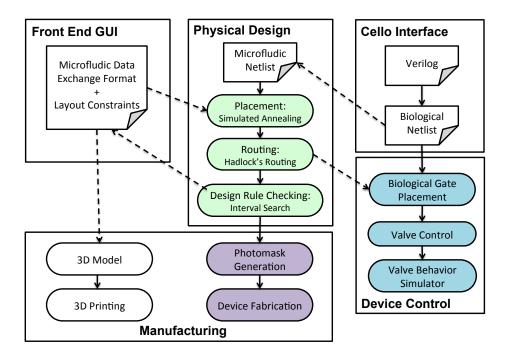

| 5 | Soft           | ware v  | workflow                   | 94  |

|   | 5.1            | Initial | ization                    | 95  |

|   | 5.2            | Parsin  | g the netlist file         | 97  |

|   | 5.3            | Placer  | nent $\ldots$              | 98  |

|   |                | 5.3.1   | Simulated annealing        | 98  |

|   |                | 5.3.2   | Pre-routing layout cleanup | 102 |

|              | 5.4  | Routin  | ng                                                                               | 102 |

|--------------|------|---------|----------------------------------------------------------------------------------|-----|

|              |      | 5.4.1   | Channel routing                                                                  | 103 |

|              |      | 5.4.2   | Net routing                                                                      | 105 |

|              | 5.5  | Design  | rule checking                                                                    | 105 |

|              |      | 5.5.1   | Channel intersection checking $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 106 |

|              |      | 5.5.2   | Space constraint checking                                                        | 108 |

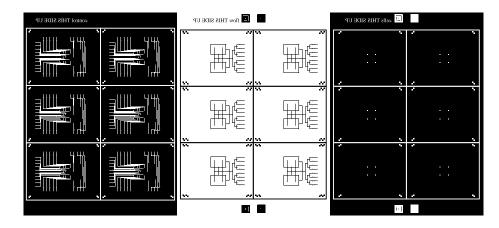

|              | 5.6  | Photon  | mask generation                                                                  | 110 |

|              |      | 5.6.1   | Masks for photolithography                                                       | 111 |

|              |      | 5.6.2   | Designs for CNC milling                                                          | 111 |

|              | 5.7  | Adding  | g biology                                                                        | 112 |

|              |      | 5.7.1   | Generating controls                                                              | 114 |

| 6            | Res  | ults    |                                                                                  | 116 |

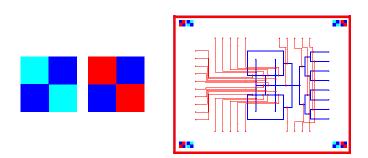

|              | 6.1  | Examp   | ole designs                                                                      | 116 |

|              |      | 6.1.1   | Designs for multilayer soft lithography                                          | 116 |

|              |      | 6.1.2   | Designs for CNC machining                                                        | 121 |

|              | 6.2  | Algorit | thm runtimes                                                                     | 121 |

|              | 6.3  | Demor   | nstration of workflow                                                            | 123 |

|              | 6.4  | Replic  | ation of XOR experiment                                                          | 124 |

|              |      | 6.4.1   | Fabrication process                                                              | 125 |

|              |      | 6.4.2   | Device controls                                                                  | 126 |

|              |      | 6.4.3   | Device testing                                                                   | 127 |

| 7            | Con  | clusior | n and future works                                                               | 132 |

| $\mathbf{A}$ | Java | librar  | ies                                                                              | 136 |

| в            | Dev  | ice Ne  | tlists                                                                           | 137 |

|              | B.1  | Device  | Α                                                                                | 137 |

| Ι                    | B.2 Device B                 | 37 |

|----------------------|------------------------------|----|

| Ι                    | 3.3 Device C                 | 38 |

| Ι                    | 3.4 Device D                 | 39 |

| Ι                    | 3.5 Device E                 | 40 |

| Ι                    | 3.6 Device F                 | 41 |

| Ι                    | 3.7 Device G                 | 42 |

| Ι                    | 3.8 Device H                 | 44 |

| Ι                    | 3.9 Device I                 | 46 |

| I                    | 3.10 Device J                | 48 |

| I                    | 3.11 Device K                | 51 |

| I                    | 3.12 Device txtl             | 62 |

| I                    | 3.13 Device transposer-cells | 63 |

| I                    | 3.14 Device transposer-web   | 64 |

| I                    | 3.15 Device mixer-3d         | 64 |

| CI                   | Photolithography procedure 1 | 66 |

| (                    | C.1 Setup                    | 66 |

| (                    | C.2 Control layer            | 66 |

| (                    | C.3 Flow layer               | 67 |

| DI                   | PDMS molding 1               | 69 |

| Ι                    | D.1 Control layer            | 69 |

| Ι                    | D.2 Flow layer               | 69 |

| Ι                    | D.3 Bonding to glass         | 70 |

| $\operatorname{Ref}$ | erences 1                    | 71 |

| Cur                  | riculum Vitae 1              | 86 |

|                      |                              |    |

# List of Tables

| 2.1 | Key microfluidic technologies for investigation of challenges present in |     |

|-----|--------------------------------------------------------------------------|-----|

|     | the synthetic biology workflow                                           | 18  |

| 2.2 | Comparison of current CAD tools for microfluidics                        | 38  |

| 3.1 | Results of Fluigi for two-input benchmark circuits                       | 51  |

| 3.2 | Results of Fluigi for three-input benchmark circuits                     | 51  |

| 3.3 | Results of Fluigi for example circuits                                   | 51  |

| 3.4 | Definition of terms                                                      | 57  |

| 3.5 | Flow layer and control layer layout parameters                           | 58  |

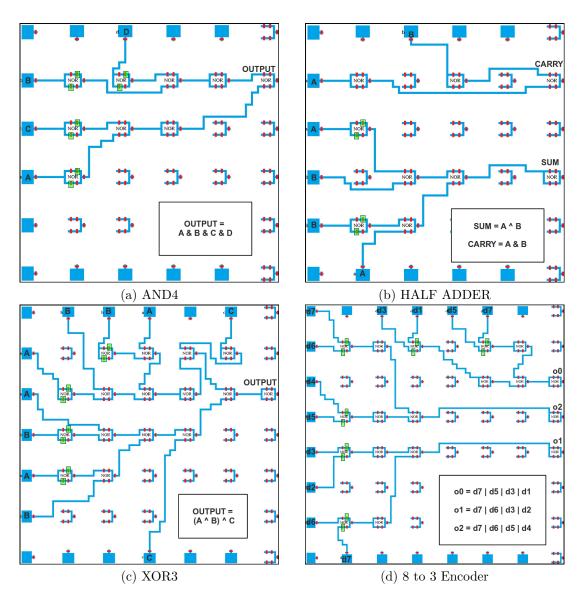

| 3.6 | Three-input Boolean logic functions                                      | 65  |

| 3.7 | Example circuits                                                         | 67  |

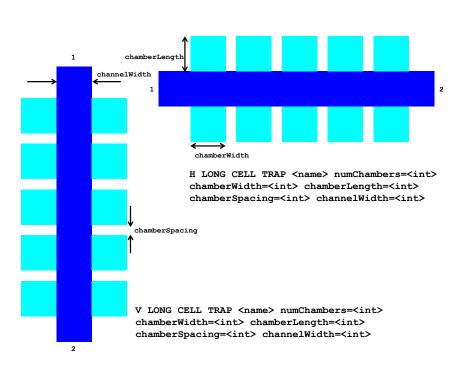

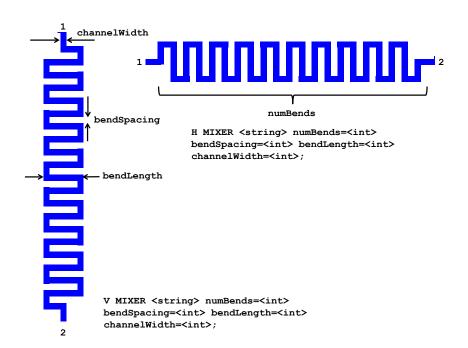

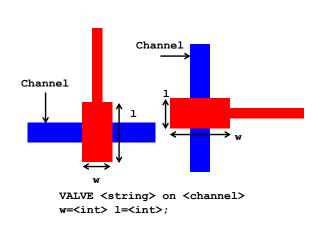

| 4.1 | Syntax for statements declaring primitives                               | 76  |

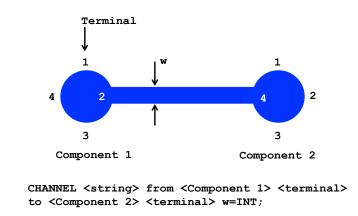

| 4.2 | Syntax for statements declaring channels and nets                        | 81  |

| 4.3 | Syntax for statements declaring modules                                  | 83  |

| 4.4 | Syntax for statements declaring 3D structures                            | 91  |

| 5.1 | Default design rule parameters                                           | 96  |

| 5.2 | Default place-and-route parameters                                       | 97  |

| 5.3 | Channel length penalty calculations                                      | 100 |

| 5.4 | Control pattern operations                                               | 114 |

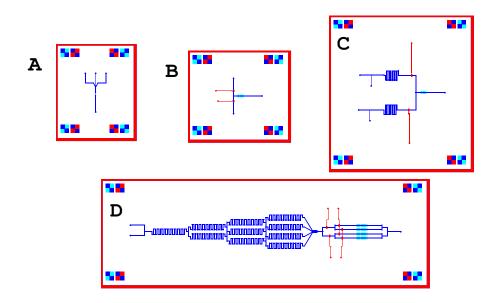

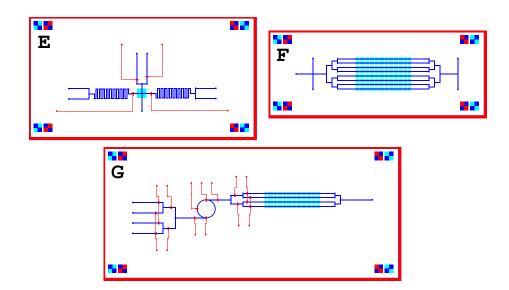

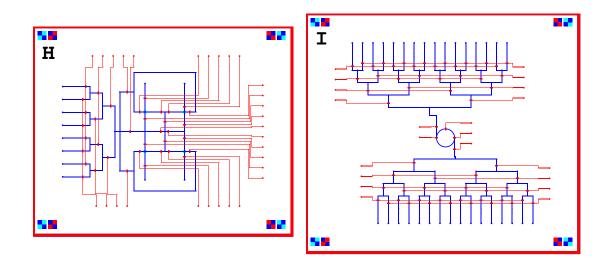

| 6.1 | Examples of devices for multilayer soft lithography                      | 117 |

| 6.2 | Examples of devices for CNC machining                                    | 121 |

| 6.3 | Algorithm runtimes for devices                | 124 |

|-----|-----------------------------------------------|-----|

| 6.4 | Valve states for fluid paths between chambers | 129 |

| A.1 | Additional Java libraries                     | 136 |

# List of Figures

| $2 \cdot 1$ | Biological NOR gate                              | 6  |

|-------------|--------------------------------------------------|----|

| $2 \cdot 2$ | Multilayer soft lithography                      | 13 |

| $2 \cdot 3$ | Synthetic biology workflow                       | 17 |

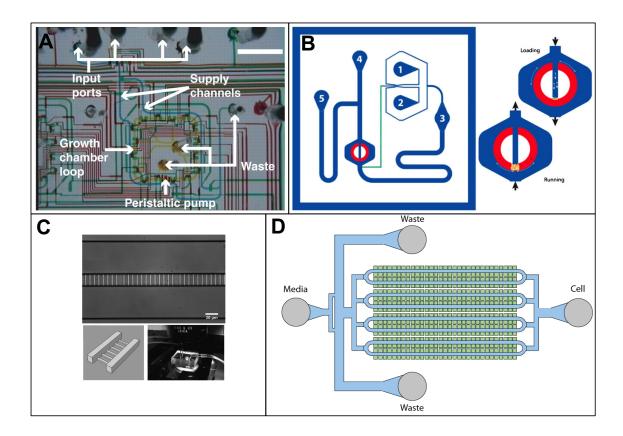

| $2 \cdot 4$ | Microfluidic devices for specification           | 20 |

| $2 \cdot 5$ | Microfluidic devices for design                  | 27 |

| $2 \cdot 6$ | Microfluidic devices for synthesis               | 29 |

| 2.7         | Microfluidic devices for verification            | 32 |

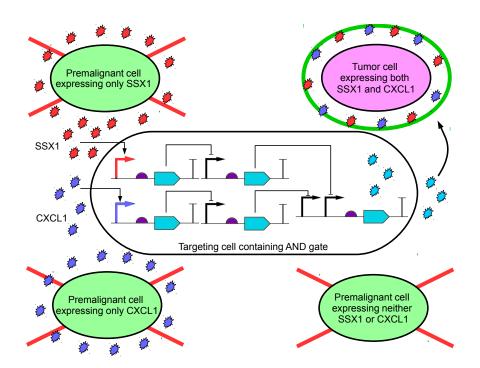

| 3.1         | Uses for biological Boolean logic                | 42 |

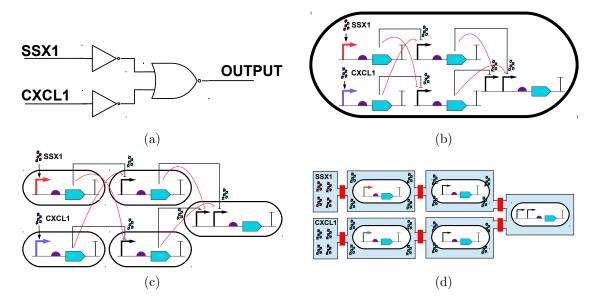

| $3 \cdot 2$ | Uses for microfluidics in biological computation | 45 |

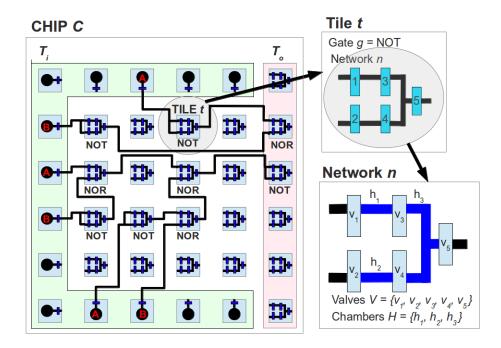

| $3 \cdot 3$ | Hypothetical chip structure                      | 47 |

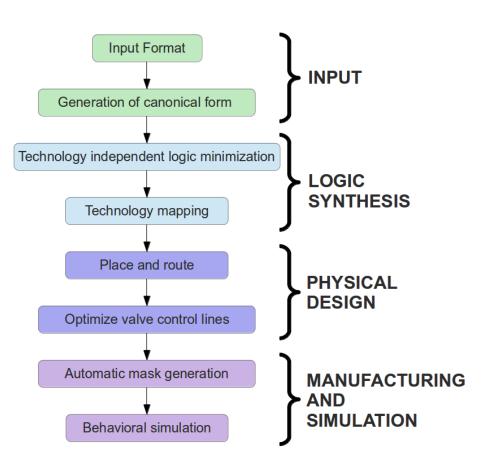

| $3 \cdot 4$ | First iteration of workflow                      | 48 |

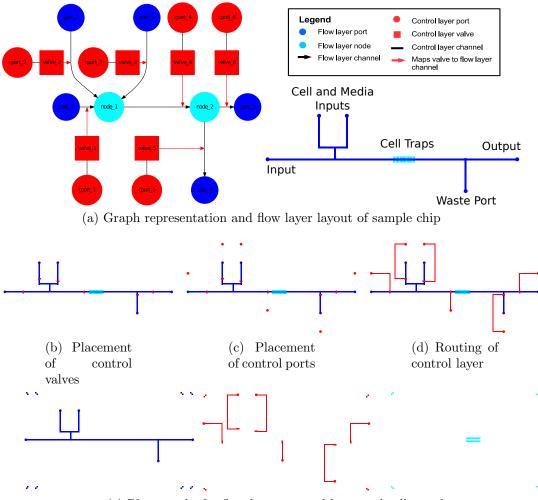

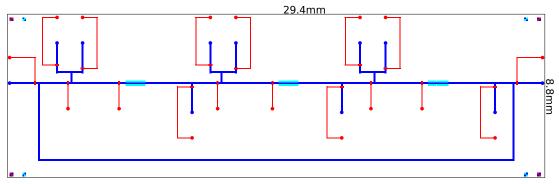

| 3.5         | Sample devices with tile architecture            | 52 |

| $3 \cdot 6$ | Second iteration of workflow                     | 59 |

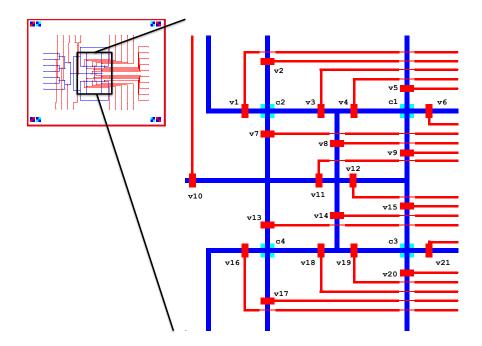

| 3.7         | Negotiated congestion routing                    | 62 |

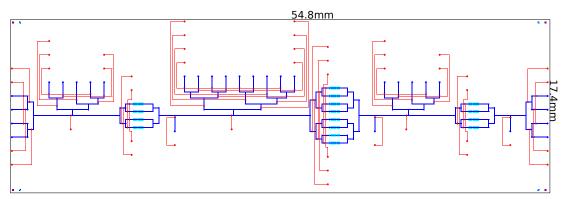

| $3 \cdot 8$ | Layout of selected combinatorial logic circuits  | 66 |

| 3.9         | Layout of selected non-combinatorial circuits    | 69 |

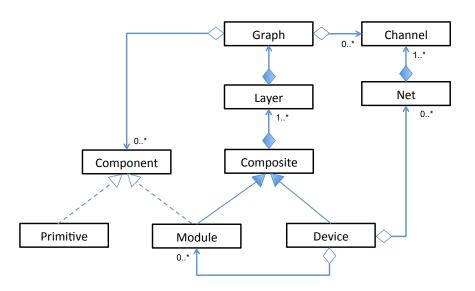

| 4.1         | Class diagram of architecture model              | 71 |

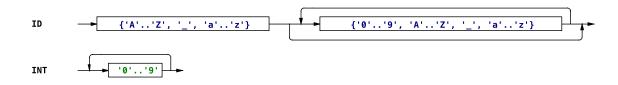

| $4 \cdot 2$ | Lexical rules for the netlist grammar            | 72 |

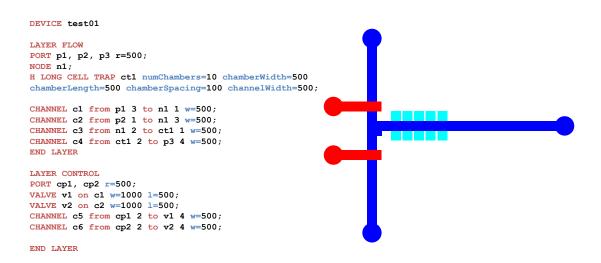

| $4 \cdot 3$ | Netlist example                                  | 73 |

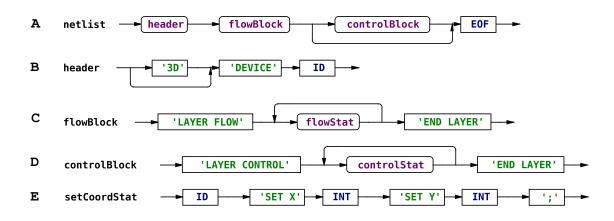

| $4 \cdot 4$ | Syntax for netlist grammar                       | 74 |

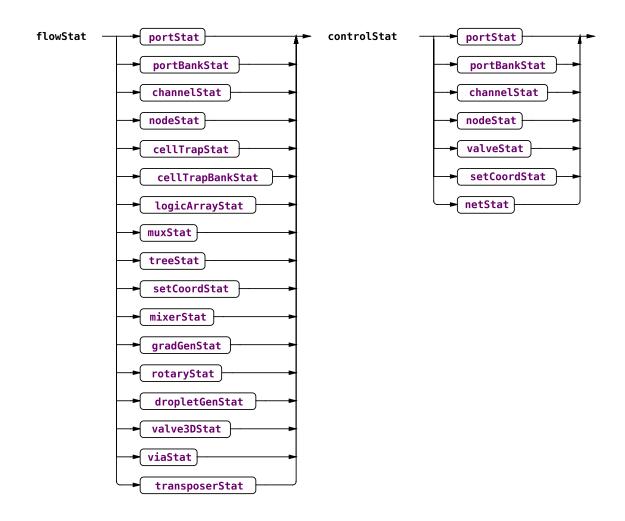

| 4.5         | Syntax for layer declarations                    | 75 |

| $4 \cdot 6$       | Port and Node                  | 76                |

|-------------------|--------------------------------|-------------------|

| 4.7               | CellTrapL                      | 78                |

| $4 \cdot 8$       | CellTrapS                      | 78                |

| $4 \cdot 9$       | Mixer                          | 79                |

| $4 \cdot 10$      | Valve                          | 80                |

| 4.11              | Channel                        | 81                |

| 4.12              | Net                            | 82                |

| 4.13              | Bank                           | 84                |

| $4 \cdot 14$      | CellTrapBank                   | 85                |

| 4.15              | Mux                            | 86                |

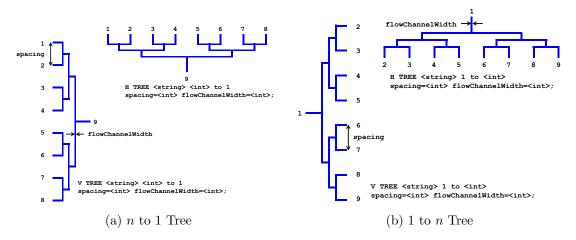

| 4.16              | Tree                           | 86                |

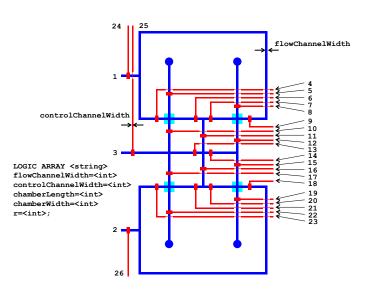

| 4.17              | LogicArray                     | 87                |

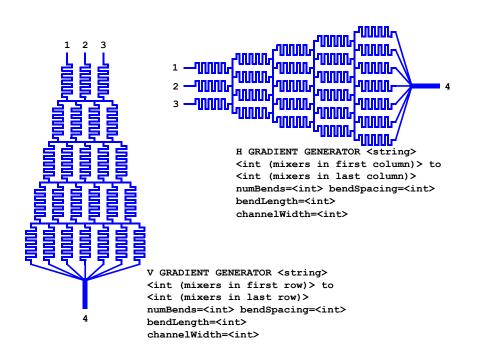

| 4.18              | GradientGenerator              | 88                |

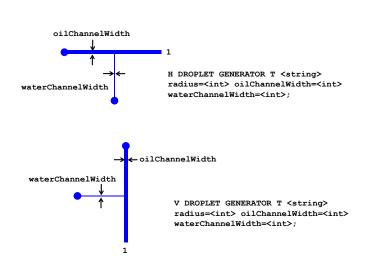

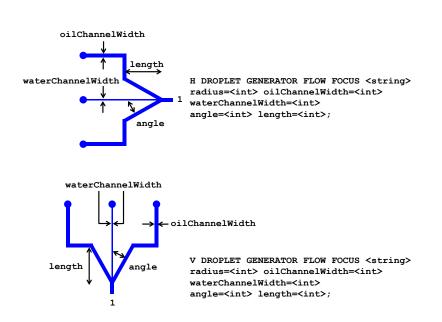

| 4.19              | TDroplet                       | 89                |

| 4.20              | FFDroplet                      | 90                |

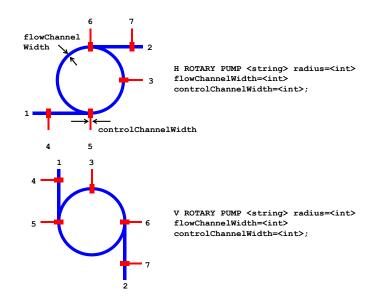

| 4.21              | Rotary                         | 90                |

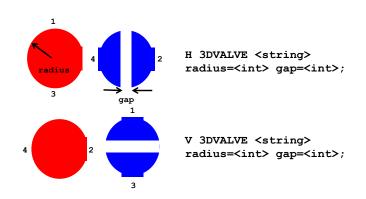

| $4 \cdot 22$      | 3DValve                        | 91                |

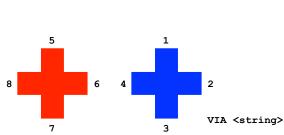

| 4.23              | Via                            | 92                |

| 4.24              | Transposer                     | 93                |

| 5.1               | Software workflow              | 95                |

| $5 \cdot 2$       | Simulated annealing pseudocode | 99                |

| $5 \cdot 3$       |                                | 104               |

| $5 \cdot 4$       | Intersection search            | 107               |

| 5.5               | Interval search                | 108               |

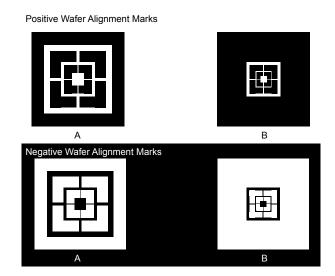

| 5.6               | Photomasks                     | 110               |

| 5.7               | Small alignment marks          | 112               |

| 5.3<br>5.4<br>5.5 | Intersection search            | 104<br>107<br>108 |

| $5 \cdot 8$ | Large alignment marks              | 112 |

|-------------|------------------------------------|-----|

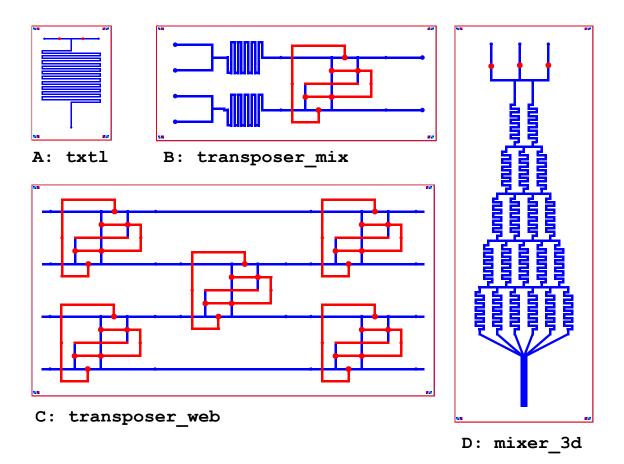

| $6 \cdot 1$ | Device designs A-D                 | 118 |

| $6 \cdot 2$ | Device designs E-G                 | 119 |

| $6 \cdot 3$ | Device designs H and I             | 120 |

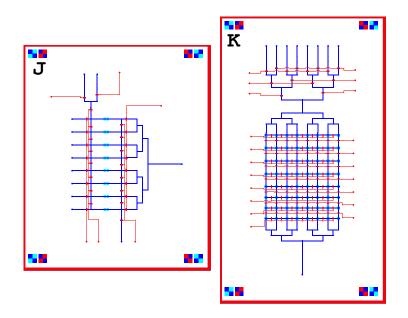

| $6 \cdot 4$ | Device designs $J$ and $K$         | 120 |

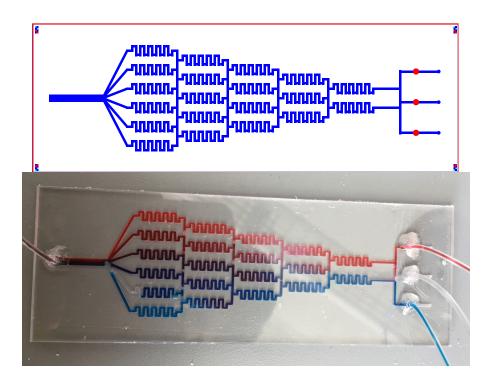

| 6.5         | Device designs for CNC machining   | 122 |

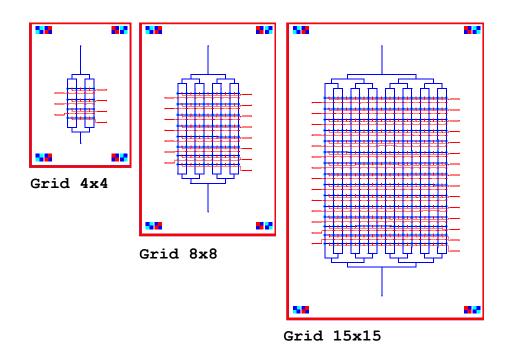

| $6 \cdot 6$ | Device designs to test runtime     | 123 |

| 6.7         | CNC milled mixer                   | 125 |

| $6 \cdot 8$ | Photomask for fabrication          | 126 |

| 6.9         | PDMS device                        | 127 |

| 6·10        | Microfluidic multiplexor in action | 128 |

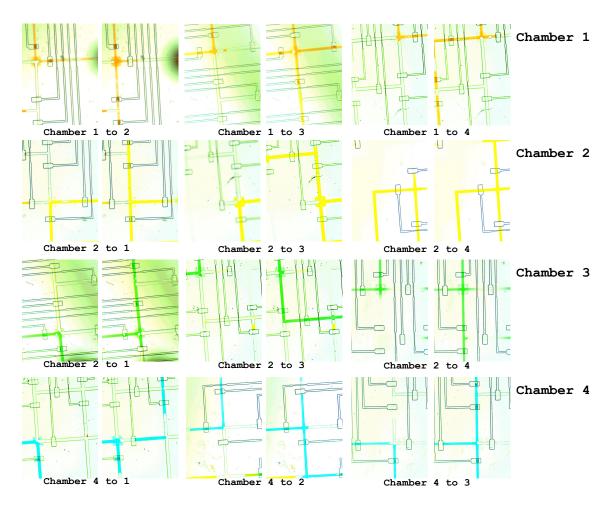

| 6.11        | Valve and chamber numbering        | 129 |

| 6.12        | Fluid paths                        | 130 |

| $7 \cdot 1$ | Long-term workflow                 | 134 |

# List of Abbreviations

| BST  | <br>Binary Search Tree                     |

|------|--------------------------------------------|

| CAD  | <br>Computer-Aided Design                  |

| CNC  | <br>Computer Numerical Control             |

| DNA  | <br>Deoxyribonucleic Acid                  |

| FPGA | <br>Field Programmable Gate Array          |

| GFP  | <br>Green Fluorescent Protein              |

| MAGE | <br>Multiplex Automated Genome Engineering |

| mLSI | <br>Microfluidic Large Scale Integration   |

| mRNA | <br>Messenger Ribonucleic Acid             |

| PDMS | <br>Polydimethylsiloxane                   |

| ORF  | <br>Open Reading Frame                     |

| SBOL | <br>Synthetic Biology Open Language        |

| TLFM | <br>Time-Lapse Fluorescent Microscopy      |

| VLSI | <br>Very Large Scale Integration           |

# Chapter 1 Introduction

Synthetic biology as a field has the potential to offer game-changing breakthroughs in the fields of alternative energy, drug discovery, customized medicine, and alternative computing. The main challenges facing scientists, particularly those working in micro-organisms such as  $E.\ coli$  or yeast, are scaling up the number of experiments and the ability to quickly and accurately reproduce previous experiments. Microfluidics, particularly continuous flow based systems and microfluidic large scale integration, provides a technology platform for chemical and biological experiments that can greatly benefit the synthetic biology community. Specific details and examples of using microfluidics in the synthetic biology workflow of specify-design-assemble-verify are described in Chapter 2.

Currently, the majority of synthetic biology labs do not adopt microfluidics for the simple reason that microfluidics are hard to both design and manufacture. Few synthetic biology labs have personnel with detailed knowledge of fluid dynamics. The process to design a microfluidic device involves drawing every device feature and channel by hand in a graphics program such as Adobe Illustrator or AutoCAD. The designer also has to keep track of and adjust all the required spacing between elements and between layers of the device. The design process can take from several days for a simple device to several weeks for a complex device. Small changes such as altering the size of elements or spacing between elements may mean redrawing large sections of the design to account for the overall design requirements. For microfluidic large scale integration, devices can contain thousands of elements, making layout by hand increasingly time-consuming and error-prone. In addition, the equipment and cleanroom space needed for device manufacturing is beyond the purview for many labs. With the current manufacturing process of multi-layer soft lithography, it takes approximately 7-10 days to make a device once a design has been finalized and a photomask printed. Repeated iterations of device designs would take weeks or months with current technologies, making it vital that the device designs are error-free before fabrication.

The goal now is to reduce the difficulty of designing and fabricating microfluidic devices so more synthetic biology labs will take advantage of the technology for their experiments. This thesis focuses on removing some of the barriers to microfluidic design by introducing a CAD tool for an end-to-end workflow from a textual description of a microfluidic device to the generation of a photomask. The scope of the project is limited to continuous flow based systems as those systems are the most amenable to the cell growth and monitoring experiments commonly used in synthetic biology. The workflow captures and formalizes the design parameters that would otherwise be derived from trial and error and allows lab-specific design choices to be easily shared in the form of initialization files. This ensures that expert knowledge is retained and reduces the learning curve of new designers.

The end-to-end workflow begins with a new netlist format for describing the features on microfluidic devices and the connections between the features. The netlist format contains commonly used microfluidic design elements such as ports, mixers, cell chambers, and multiplexers, and can be easily extended to describe additional features. The full specification for the netlist format is in Chapter 4.

The netlist is converted to a graph representation of the microfluidic device, and the device undergoes automated layout and design rule checking. Algorithms for placement and routing from electronic design automation were adapted to work with the design constraints of microfluidic devices. Simulated annealing is used for placement, and Hadlock's variation of maze routing is used for routing. Design rule checking is performed with a search of intersections between device features that reduces to a 1-D interval search. These processes are described in detail in Chapter 5. The result of this is a vector graphics file of the design for manufacturing.

This workflow was used to build and test a prototype device for solving one of the challenges facing synthetic biology: the lack of non-interferring genetic parts in large genetic networks. Microfluidics could allow reuse of existing genetic parts by separating the parts both spatially and temporally. Previous attempts at solving this challenge are described in Chapter 3. A four chamber device that allowed fluid routing between any two chambers was designed with this workflow. The photomask generated by this workflow was used to fabricate the device through multilayer soft lithography, and the device was tested with dye. An alternative method of fabrication with a desktop computer numerical controlled (CNC) mill was also explored. Where it would take a week to fabricated a device with multilayer soft lithography, a CNC mill can be used to fabricated devices in less than an hour. The workflow was used to generate the design for a gradient generator, and the final device was fabricated with the CNC mill and tested with dye. The results of these two experiments are described in Chapter 6.

The contributions of this work to the fields of synthetic biology, microfluidics, and design automation are two-fold. First, I provide the first end-to-end workflow for microfluidic design automation that includes a new netlist format for describing microfluidic devices, automated layout through place-and-route, and design rule checking. Second, I provide a prototype device built with the workflow for directing communications between different cell populations that may increase the scalability of biological computation. This work has to potential to unlock a paradigm shift in both microfluidic design and synthetic biology by harnessing the capabilities of design automation.

## Chapter 2

# Background

(This chapter was originally published as Huang, H. and Densmore, D. (2014). Integration of microfluidics into the synthetic biology design flow. Lab Chip, 14:3459 - 3474. (Huang and Densmore, 2014b).)

Over the last decade, synthetic biology has emerged as a field with potential applications in diverse fields including pharmaceuticals, biofuels, and materials. The engineering of a microbial production pathway for artemisinic acid (a precursor for antimalarial drugs) (Ro et al., 2006) has lowered the production costs of those drugs from \$2.40 to \$0.40 per dose, expanding the number of patients who can afford the treatment for a disease that kills millions (Densmore and Hassoun, 2012). Several companies from around the world (Gevo in Englewood, Colorado, Butamax in Wilmington, Delaware, and Butalco in Fuerigen, Switzerland) have all developed methods to increase the yield of isobutanol or butanol for commercial biofuels using various strains of yeast (Peralta-Yahya et al., 2012), while Amyris has adapted the mevalonate and deoxyxyulose phosphate metabolic pathways in yeast to ferment farnesene (Westfall and Gardner, 2011). Engineered bacteriophages (viruses targeting bacteria) have been used to destroy biofilms (Lu and Collins, 2007) and resensitize otherwise antibiotic-resistant strains of bacteria (Lu and Collins, 2009), which could extend the effectiveness of current drug therapies in the face of rising antibiotic resistance. However, despite these success stories, the field of synthetic biology faces challenges in workflow acceleration and automation as it seeks to scale from single prototypes

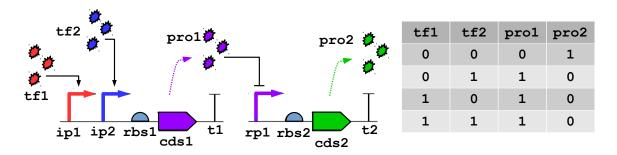

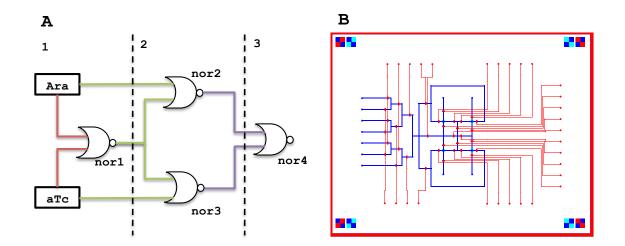

Figure 2.1: A genetic NOR gate, and accompanying truth table. The presence of transcription factors tf1 or tf2 activate the inducible promoters ip1 and ip2 respectively and allow for production of pro1, coded for by cds1. The protein pro1 acts as a transcription factor on repressible promoter rp1 and blocks production of pro2, coded for by cds1. The final output, pro2 is only produced when both transcriptional factors tf1 or tf2 are absent.

to commercial enterprises. The field of microfluidics has proved successful in a wide range of applications in biology and has the potential to address these challenges.

## 2.1 Engineering biology

Synthetic biology seeks to manipulate the structure and functions of deoxyribonucleic acid (DNA) to create new biological systems according to engineering principles. The primary paradigm in the field is to identify biological primitives involved in the transformation of DNA to a protein and encapsulate these individual DNA sequences as "parts" (Voigt, 2006). Synthetic biology has taken advantage of the modularity in the structure of bacterial open reading frames (ORFs) to abstract portions of the sequence as "parts". These "parts" include sequences for promoters, ribosome binding sites, coding regions, and terminators, and can be combined to create functional "devices" which can be introduced into living organisms such as bacteria, yeast, or mammalian cells (Canton et al., 2008; Khalil et al., 2012; Carr and Church, 2009). As logical frameworks such as repressible systems exhibiting the behavior of inverters already exist in gene expression systems, synthetic biology seeks to harness and reengineer these natural logic systems for other applications.

A genetic device that implements the Boolean NOR function and the corresponding truth table are shown in Figure 2.1. This device is designed to function in prokaryotic systems. In this circuit, the inputs are the transcription factors tf1 and tf2, which control the inducible promoters ip1 and ip2 such that transcription only takes place when one or both of the transcription factors are present. Transcription continues until terminator t1, and the resulting messenger RNA (mRNA) is translated into the protein pro1 (coded for by the coding region cds1). The protein pro1 acts as a transcription factor for the repressible promoter rp1, preventing transcription starting at rp1 if it is present. The output of this system is the protein pro2 (coded for by the coding region cds2), which is only expressed if neither tf1 or tf2 are present. In the absence of tf1 and tf2, pro1 is not expressed. Transcription starts at rp1 and continues through t2, allowing pro2 to be expressed. This behavior of this device emulates that of the Boolean NOR function, in which the output is true if and only if both inputs are false. NOR and NAND functions are functionally complete and can be used to build all other Boolean logic functions, thus allowing these devices to be the basis for biological computation. As such, many different implementations of these functions exist in synthetic biology (Goñi-Moreno and Amos, 2012; Wang et al., 2011; Bonnet et al., 2013).

While many different classes of biological devices such as oscillators (Purcell et al., 2010), filters (Sohka et al., 2009), noise generators (Lu et al., 2008), and the beginnings of analog computation (Daniel et al., 2013) exist, I focus here instead on the biological devices implementing Boolean logic (Brophy and Voigt, 2014) and other extensions of the digital abstraction found in electronics. I use the digital abstraction not to replicate silicon-based computing, but as a method for designing robust biological circuits that are insensitive to noise and can be tuned to specific input conditions.

Additionally, the digital abstraction is well understood, and numerous techniques have been developed for its description, synthesis, and verification. The introduction of Boolean logic and memory devices into biological systems leads to new applications and potential methods of computation for solving otherwise computationally intensive and complex problems (Haynes et al., 2008; Baumgardner et al., 2009).

#### 2.1.1 Boolean logic in biological devices

Biological logic devices can be used to detect specific combinations of chemical or environmental triggers for targeted pharmaceutical and biotechnology applications (Tamsir et al., 2011; Gupta et al., 2013). One application for biological logic circuits is in the field of cancer research (Ruder et al., 2011; Shankar and Pillai, 2011), where the use of digital logic provides the necessary specificity for targeting strains of cancer cells while leaving other cells unharmed (Anderson et al., 2006; Xie et al., 2011). Nissim et al. (Nissim and Bar-Ziv, 2010) introduce a tunable dual promoter system that implements the Boolean function AND to target cancer cells while ignoring premalignant cells.

While devices implementing two-input Boolean logic functions are useful in synthetic biology, more complex computation would allow for applications such as the biological sensing of multiple chemical species in the same device, the identification of specific genetic markers, and environmentally tailored drug dosage responses (Purnick and Weiss, 2009). One way of constructing more complex functions is to increase the layers of logic in the genetic device. This method was used by Moon et al. to create a four input transcriptional AND gate (Moon et al., 2012) with eleven orthogonal (non-interfering) regulatory proteins made from two layers of two-input AND gates. Another tactic is to separate the larger function into smaller functions and place devices implementing the smaller functions into different cells. These cells then communicate with each other through intercellular signaling pathways. All sixteen two-input functions have been built from E. coli cells containing NOR gates that communicate through the quorum sensing pathway (Tamsir et al., 2011). Distributed computing (Macía et al., 2012) has also been implemented in yeast with the development of both a 2-to-1 multiplexer and a basic addition circuit (Regot et al., 2011).

### 2.1.2 Memory and state in biological devices

The next step in increasing complexity of computation is to generate the concept of memory or "state", such that the cell remembers what has previously happened and takes that into account in new calculations. One approach is to use recombinases, enzymes used by bacteriophages to manipulate their host's genome, to turn specific DNA sequences on and off by switching the orientation of the DNA (Khalil and Collins, 2010). Memory devices and counters have been integrated into cells through the use of recombinase-based circuits (Ham et al., 2008; Friedland et al., 2009). The use of recombinase has also provided synthetic biologists with a form of rewrite-able and addressable data storage capable of information storage through over 100 cell divisions and through repeated switching without losing performance (Bonnet et al., 2012). More recently, Siuti et al. have used recombinase-based circuits to implement all 16 two-input Boolean logic functions with stable DNA-encoded memory of events in *E. coli* without requiring cascades of multiple gates (Siuti et al., 2013).

#### 2.1.3 Specify-Design-Assemble-Verify workflow

The practice of synthetic biology typically follows an iterative process of specification, design, assembly, and verification. The process begins with the specification of the function of the novel genetic device either by hand or with one of the new description languages such as Eugene (Bilitchenko et al., 2011a; Bilitchenko et al., 2011b), GEC (Pedersen and Phillips, 2009), or Proto (Beal et al., 2011). In the design phase, biological parts are selected from repositories to implement the specified function. Tools such as GenoCAD (Cai et al., 2010), j5 (Hillson et al., 2012), or Clotho (Xia et al., 2011) may aid the design process. Assembly of a novel genetic device starts with obtaining the parts of interest either by isolating segments of DNA from natural sources or by *de novo* synthesis through companies such as DNA2.0, GeneArt (Densmore and Hassoun, 2012), or Gen9 (Goldberg, 2013). Parts are assembled into devices by joining the segments of DNA together using restriction enzymes (proteins that cut DNA at certain sequences) and ligases (proteins that create new bonds between DNA bases). Common assembly techniques, including BioBrick (Shetty et al., 2008), BglBrick (Anderson et al., 2010), Gibson (Gibson et al., 2009), GoldenGate (Engler et al., 2008), the Modular Overlap-Directed Assembly with Linkers (MODAL) (Casini et al., 2014), and modular cloning (MoClo) (Weber et al., 2011), are reviewed in detail elsewhere (Ellis et al., 2011). Software tools are being developed to automate and optimize the assembly process (Densmore et al., 2010; Appleton et al., 2014).

The completed device is then inserted into a host organism, commonly  $E. \ coli$  for prokaryotic systems and yeast (*Saccharomyces cerevisiae*, a model organism for eukaryotic studies) for eukaryotic systems, and the organism is grown under a variety of conditions to test the function of the device as compared to the original specifications. For verification purposes, fluorescent proteins are often used as a substitute for the gene of interest as their expression is more easily measured through flow cytometry to determine the efficiency of the device under test. The fluorescent protein is replaced by the protein of interest in the final application. At this stage, the genetic device may be further refined based on the gathered data, or the host cells may be grown for harvesting more copies of the device.

As new techniques in synthetic biology generate large libraries of thousands of part variations and combinatoric devices, increased throughput and automation are needed to test and characterize these constructs to allow the acceleration of the specifydesign-assemble-verify development cycle for synthetic biology. To lower the barrier of entry into the field, synthetic biology needs to take advantage of the improvement in automation and computer-aided design tools. Software tools for synthetic biology have grown in the past years to encompass a variety from rules-based constraint languages to gene designers to basic simulators. Standards such as the Synthetic Biology Open Language (SBOL) (Galdzicki et al., 2012) are being developed to facilitate information exchange between various tools in the toolchain and will be vital in building end-to-end workflows (Beal et al., 2012) in synthetic biology from high level languages to compilation from the language to biological parts to DNA assembly. While the available tools are still lagging behind the current state of the art of biological research, the development of these tools helps with refining the rules of genetic design for future applications (Lux et al., 2012).

## 2.2 Microfluidics

Microfluidics is comprised of the analytical systems and tools for the study and manipulation of small volumes of liquids, typically at micro and nano liter scales. The advantages of microfluidics come from the decrease in scale, which allows for more predictable fluid flow, decreasing the amount of reagents needed for reactions, and smaller devices and experiment setups. Microfluidics have been used for chemical analysis (Whitesides, 2006) and PCR (Zhang et al., 2006) as well as a variety of applications in molecular biology (Hamon and Hong, 2013), systems biology (Breslauer et al., 2006), stem cell studies (Gupta et al., 2010; Zhang and Austin, 2012), tissue engineering (Inamdar and Borenstein, 2011), point-of-care diagnostics (Lei, 2012), pathogen detection (Foudeh et al., 2012), and systematic toxicity studies (Sung and Shuler, 2010). Recently, synthetic biologists have been developing and using microfluidics to study synthetic gene networks and network dynamics (Bennett and Hasty, 2009). Due to the potential in microfluidic systems for the precise control over input stimuli (Wang et al., 2012; Dertinger et al., 2001) and the ability to track single cells (Ferry et al., 2011), there has been an increased interest in microfluidic platforms to further synthetic biology (Lin and Levchenko, 2012). I present the list of challenges facing synthetic biology as the field matures and describe how microfluidics could be used to find solutions to those challenges as well as potential future applications for systems and workflows integrating both synthetic biology and microfluidics.

The field of microfluidics covers a wide range of technologies such as lateral flow tests, linear actuated devices, pressure driven laminar flow, microfluidic large scale integration, segmented flow microfluidics, centrifugal microfluidics, electrokinetics, electrowetting, surface acoustic waves, and dedicated systems for massively parallel analysis (Haeberle and Zengerle, 2007; Mark et al., 2010). For the purposes of this project, I will focus on the subset of microfluidics that offer the most relevance to current problems in the synthetic biology workflow, particularly in spatial and temporal gradient generation, microfluidic large scale integration (mLSI) high-throughput screening, DNA synthesis, and cell culture.

### 2.2.1 Device physics

In pressure-driven systems, the reduced scale of microfluidic devices results in deterministic fluid flow. The low Reynolds number (a comparison of the forces acting on the flow) of the flow means that the nonlinear and chaotic effects due to turbulence caused by inertial forces are removed, and the flow is restricted to the laminar region. In this flow regime, the behavior of the fluids can be predicted by the size of the fluid channel and the viscosity of the fluid in a manner analogous to Ohm's Law in electrical engineering (Oh et al., 2012), making it easier to simulate and verify the

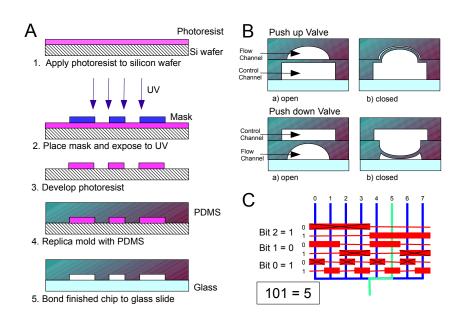

Figure 2.2: (A) Fabrication process for soft lithography (adapted from (Zhang and Austin, 2012)). (B) Two possible structures (push-up or push-down) for valves in multilayer soft lithography (adapted from (Melin and Quake, 2007)). (C) Multiplexer for selection of 8 possible fluid lines, using 6 control lines to represent the 3-bit binary number of the selected line (adapted from Ref. (Thorsen et al., 2002)).

function of the device. The mixing of parallel flows is dominated by diffusion instead of convection, so that the flows only interact at their boundary. This effect can be exploited to generate spatial gradients of chemicals of interest (Dertinger et al., 2001). Mixers (Chou et al., 2001; Stroock et al., 2002) can be used to speed up integration of flows. A detailed synopsis of the physics and fluid mechanics specific to microfluidic devices may be found elsewhere (Squires and Quake, 2005; Kirby, 2010).

### 2.2.2 Design and fabrication

A widely used fabrication material for microfluidic devices is polydimethylsiloxane (PDMS). The properties of PDMS make it well suited for use in biological applications as it offers flexibility for fabrication, scalability, and potential for long-term growth and monitoring of cells (Balaban et al., 2004). PDMS is optically transparent, chemically inert, impermeable to water but permeable to gases, and non-toxic

13

to cells (Sia and Whitesides, 2003). The cost of the raw material is around \$0.05 per  $cm^3$  (Unger et al., 2000; Sollier et al., 2011), making it suitable for rapid prototyping and quick design iteration. PDMS-based microfluidics have been used for a variety of purposes in recent years, including as an alternative platform for computation (Thies et al., 2008). Development of the microchemostat (Balagaddé et al., 2005) has allowed for cells to be grown in microfluidic chips for long periods of time, thus allowing for more complex, long-term experiments. However, the low elastic modulus of PDMS makes it unsuitable for high pressure applications as high pressure causes channel deformation in PDMS-based devices (Sollier et al., 2011).

Microfluidic chips are fabricated from PDMS through soft lithography. As many detailed reviews of the process exist (Duffy et al., 1998; Sia and Whitesides, 2003; Weibel et al., 2007), I will only provide a brief description. Photoresist (typically SU-8) is spun out over a substrate of silicon, and a transparency with the chip design is placed over it as a mask. The sandwich of mask, photoresist, and substrate is then exposed to UV light. The mask is removed, and the photoresist washed in developing agent to obtain the master mold. PDMS layers are cast from the master through replica molding. The channels are then sealed against a substrate suitable for imaging and connected to input and control structures. A summary of the process is shown in Figure 2.2A. The entire fabrication process, from the creation of the photomask to the molding of the chip, takes no more than a few days including the turnaround time for printing the photomask. This process does require the experimenter to have access to a high quality cleanroom and purchase specialized fabrication equipment for soft lithography (Elveflow, 2015), or else contract out the fabrication process to a dedicated microfluidic foundry.

### 2.2.3 Microfluidic large scale integration

An extension of soft lithography, multilayer soft lithography, allows devices to be built of multiple layers of PDMS, typically with one layer as a fluid flow layer and another layer as a control layer with channels pressurized by external actuators (Unger et al., 2000). Fluid flow is controlled by strategic placement of valves in the control layer, which restrict fluid flow when pressurized by causing the PDMS to deform and create a seal across the channel to impede fluid flow (Amin et al., 2009). Two types of valves described by Melin and Quake (Melin and Quake, 2007), push up and push down, are shown in Figure 2.2B. For work with cells, push down valves are preferred as they allow for easier cleaning of the flow channels and chip reuse (Cheong et al., 2009b). Multiple valves may be be controlled by the same pressurized control line, and the optimization problem lies in minimizing the number of control lines needed to operate a chip.

The interaction of the control and flow layer through valves form the basic building block of microfluidic large scale integration (mLSI). As devices made from multilayer soft lithography grow more complicated, an increased number of external pressure lines are needed to control fluid flow. Microfluidic multiplexers, developed by Quake and colleagues (Thorsen et al., 2002), contain combinatorial arrays of binary valve patterns and allow increased fluid manipulation with a minimal number of control inputs such that only  $2 \log_2 n$  control lines are needed to access the valves to select from one of n fluid channels. This makes them very suitable for high-throughput applications that require manipulation of hundreds or thousands of fluid elements. The multiplexer shown in Figure 2.2 uses 6 control lines to represent the 3-bit binary number for selecting the fluid channel. Recent advancements in mLSI architecture focus on increasing the number of control elements on the chip through component miniaturization or additional layers, decreasing the reliance on external pneumatic lines through on-chip logic, and increasing reusability through programmable chips (Araci and Brisk, 2014). Work has also been done on reducing contamination and back flow through the use of a microfluidic serial digital-to-analog pressure converter (Yu et al., 2013).

While CAD and automation have been primarily focused on droplet based digital microfluidics (Su and Chakrabarty, 2005; Su et al., 2006; Chakrabarty and Zeng, 2005; Chakrabarty, 2010) rather than mLSI, a new subset of tools are being developed for layout and optimization of mLSI devices. Earlier tools for mLSI include Biostream, a tool for designing GUIs and control valves for multilayer devices (Thies et al., 2008; Urbanski et al., 2006) (freely available at (Thies et al., 2009)) and Micado (Amin et al., 2009), which automate control valve placement and routing for a given flow layer. Extensions of that work have led to developments in a microfluidic description language similar to hardware description languages used in electronics (McDaniel et al., 2013), algorithms for laying out the flow layer based on a high level description of chip function (Minhass et al., 2012), and better algorithms for valve placement and control routing (Minhass et al., 2013; Tseng et al., 2013).

## 2.3 Using microfluidics to solve challenges in synthetic biology

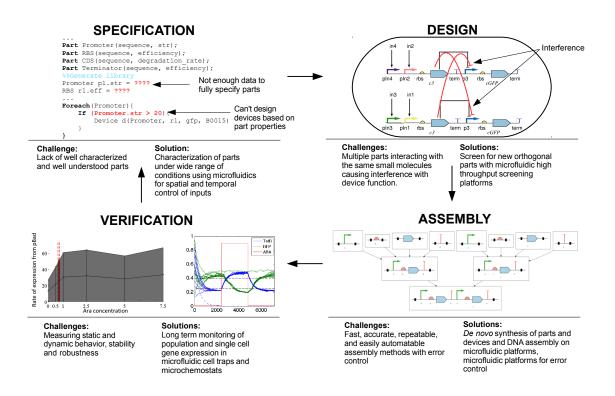

Introducing complex engineered systems into cells presents numerous challenges at different levels of the synthetic biology workflow. I present in Figure 2.3 a sampling of the current challenges in synthetic biology and the microfluidic technologies most applicable to solving those challenges. I begin with the problems facing accurate specification of the function of novel genetic devices as the specification is only as useful as the understanding of the underlying biological behavior. A major challenge when designing new biological devices is that synthetic biology still suffers from a lack of well-characterized parts that do not interfere with each other when used to-

Figure 2.3: The synthetic biology workflow of specification-design-assemblyverification, and the challenges at each step in the workflow. The use of microfluidics in environmental control, high throughput screening, DNA synthesis, and cell culture may be used to augment current work in synthetic biology and address these challenges.

gether to construct larger systems. Important factors in the assembly of a device include potential unintended changes in function introduced when joining two segments of DNA and the time and cost efficiency of the currently available assembly methods. Verification of device function and stability requires accurate monitoring and measurement of protein expression at both the population and single cell level for extended periods of time. Microfluidics technologies in environmental control, high throughput assays, DNA synthesis, and cell culture can be used to augment and supplement existing work in synthetic biology to address these challenges. I present in Table 2.1 a summary of the current challenges facing synthetic biology as it matures

| Workflow                     | Challenge                                                                                                                                                                                          | Potential                                                                                                                                                                 | Applicable                                                                                                                                                                   | References                                                                                                                                                                          |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Domain                       |                                                                                                                                                                                                    | Solution                                                                                                                                                                  | Microfluidic<br>Technology                                                                                                                                                   |                                                                                                                                                                                     |

| Specification         Design | Accurate and<br>standardized<br>models of parts<br>needed for<br>composition<br>of devices and<br>prediction of<br>device behavior<br>in simulations<br>Small number<br>of available<br>orthogonal | Characterization<br>of parts and de-<br>vices over wide<br>range of en-<br>vironments<br>and operating<br>conditions<br>Engineering<br>large libraries<br>of new parts or | Large scale<br>spatial and<br>temporal fine-<br>grained control<br>over chemi-<br>cal inputs in<br>microfluidic<br>devices<br>Microfluidic<br>large scale<br>integration for | (Dertinger<br>et al., 2001;<br>Lin et al., 2004;<br>Bennett et al.,<br>2008; Wang<br>et al., 2012;<br>Cooksey et al.,<br>2009)<br>(Thorsen et al.,<br>2002; Taylor<br>et al., 2009; |

|                              | parts result<br>in unwanted<br>molecular inter-<br>actions in large<br>devices                                                                                                                     | reuse of existing parts                                                                                                                                                   | high throughput<br>screening assays<br>for new parts<br>and controlling<br>intercellular<br>signaling for<br>distributed<br>biological com-<br>puting                        | Dénervaud<br>et al., 2013;<br>Gómez-Sjöberg<br>et al., 2007;<br>Cheong et al.,<br>2009b; Liu<br>et al., 2010;<br>Fidalgo and<br>Maerkl, 2011)                                       |

| Assembly                     | Fast, accurate,<br>repeatable con-<br>struction of<br>large genetic<br>devices with<br>minimal in-<br>terference of<br>part/device<br>function                                                     | De novo syn-<br>thesis of genetic<br>parts and de-<br>vices                                                                                                               | Microfluidic<br>DNA synthesis<br>and assembly                                                                                                                                | (Carr and<br>Church, 2009;<br>Kong et al.,<br>2007; Lee et al.,<br>2010; Huang<br>et al., 2009;<br>Kosuri et al.,<br>2010; Kersaudy-<br>Kerhoas et al.,<br>2014)                    |

| Verification                 | Accurate mea-<br>surements of<br>gene expression<br>at population<br>and single cell<br>level for multi-<br>ple generations                                                                        | Long term<br>monitoring of<br>single cells for<br>part/device<br>stability                                                                                                | Microchemostats<br>and cell traps<br>supporting long<br>term cell growth<br>and single cell<br>monitoring                                                                    | (Balagaddé<br>et al., 2005;<br>Ferry et al.,<br>2011; Long<br>et al., 2013;<br>Danino et al.,<br>2010; Locke and<br>Elowitz, 2009)                                                  |

| Table 2.1: Key microfluidic | technologies for | investigation | of challenges | present in the |

|-----------------------------|------------------|---------------|---------------|----------------|

| synthetic biology workflow  |                  |               |               |                |

as an engineering field and the most applicable microfluidic technologies that may be used to address those challenges.

#### 2.3.1 Specification

Accurate specification of biological device function requires prediction of future behavior of combinations of biological parts and a standardized input/output model to share behavioral data across different designs. However, with the exception of some well studied systems such as the quorum sensing system (Collins et al., 2006), not all biological behavior in synthetic biological parts is well understood or predictable. In many cases, a device that performs well in one host system fails to perform when transplanted into a different host. In addition, different parts are characterized with different experimental methods such that there is no one standard of input/output measurement to specify interfaces between devices. As a result, many new devices fail to function without extensive trial-and-error, which is costly in both time and materials. To build more predictable systems, better characterization of part behavior over a wide range of environmental conditions is required to achieve the necessary understanding to build the correct models.

### Challenges

In electrical engineering, simulation is used to predict device behavior and debug potential design flaws without spending time and resources in the lab. Whereas there is a solid understanding of semiconductor device physics and the ability to create accurate models for electronic parts for simulations, similar knowledge needed to create models of biological parts is still being developed. Chen et al. characterized terminator efficiency for 582 natural and synthetic transcriptional terminators and from that data generated a predictive model of terminator behavior given the sequence (Chen et al., 2013). Similar models have been generated for ribosome binding sites (Salis et al., 2009), but these sequence based models alone cannot predict the behavior of combinations of parts in a biological system. Likewise, new software tools developed

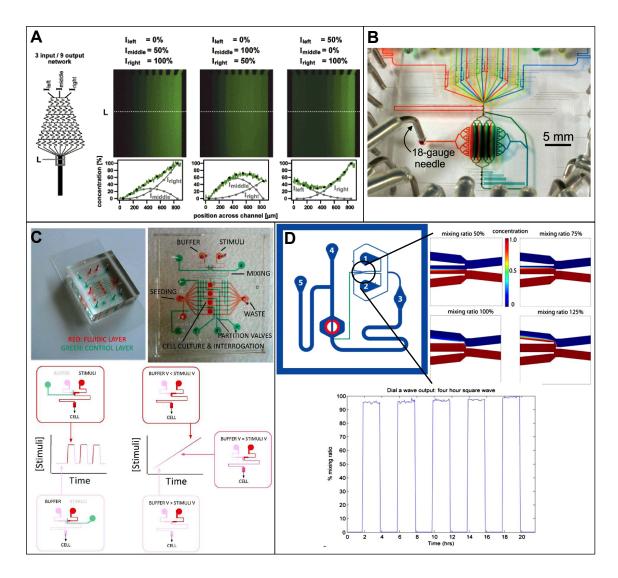

Figure 2.4: (A) Resistance network used to generate complex spatial gradients in fluid channels. (Reprinted with permission from S.K.Dertinger, D.T.Chiu, N.L.Jeon and G.M.Whitesides, Analytical Chemistry, 2001, 73, 1240–1246. Copyright (2001) American Chemical Society."). (B) Microfluidic chip for multipurpose testing using a combination of 16 inputs and outputs to generate spatial gradients in the central test chamber. (Reproduced from Ref. (Cooksey et al., 2009) with permission from The Royal Society of Chemistry.) (C) Dial-a-Wave device for generation of temporal stimuli via adjustment of flow interface for study of synthetic oscillators. (Used with permission from (Baumgartner et al., 2011). Copyright 2011 Buamgartner et al..) (D) Microfluidic function generator using valves to control flow through a T junction. (Used with permission from (Wang et al., 2012).)

for simulating synthetic biological systems (Jang et al., 2012; Madsen et al., 2012) are based on models of the biological processes of cell growth, diffusion, and protein interactions and degradation but may not take into account the details of part function based on DNA sequence.

Datasheets for electronic parts contain the information needed to create accurate behavioral models of those parts for use in simulations, including the valid input and output ranges, the switching characteristics, and frequency response for noise analysis. Canton et al. (Canton et al., 2008) postulated the creation of similar datasheets for biological parts and produced a datasheet for BioBrick BBa<sub>-</sub>F2620, a device that produces the transcription factor LuxR and is controlled by a regulated operator. Datasheets for biological parts must include different information than their electrical engineering counterparts due to issues such as host context and degradation rate of inputs and outputs that have no electronic parallels. Biological parts need to be characterized for orthogonality and multi-component behavior as well as the more usual single-component behavior. The long-term behavior of a part depends on such factors as the strain and growth stage of the host cell, the mutation rate, and environmental conditions such as temperature, pH, and culture media. For example, degradation rate of acylhomoserine lactone (AHL), the key signaling molecule in the popular and commonly used bacterial quorum sensing system, varies with both pH and temperature, making devices using this system sensitive to environmental changes (Kittleson et al., 2012). The addition of biological parts and devices into the host cell introduces large amounts of foreign DNA that may impact host cell metabolism (Klumpp et al., 2009). To produce useful datasheets and models for simulation would require massive amounts of characterization data. The spatial and temporal environmental control that microfluidics provides, combined with high-throughput cell culture assays (described in Section 2.3.2 could be used to develop characterization and test platforms for synthetic biology devices.

#### **Current** solutions

Static analysis of biological devices involves determining the valid input and output ranges and generating the input-output curve that shows the range of outputs for any given input. Inputs to a biological device are transcription factors at various concentrations, and outputs are often fluorescent reporter proteins (Canton et al., 2008). A wide range of inputs is applied to the device under test to generate the full range of outputs. Additional characterization includes testing for interactions with other similar transcription factors and testing the effects of simultaneously applied multiple inputs.

Microfluidic resistance networks for generating complex spatial and temporal gradients (Figure 2.4A) (Dertinger et al., 2001; Lin et al., 2004) are well suited to generating the input ranges needed to characterize basic device behavior. Combining these networks with the ability to select multiple inputs through multiplexing allows for testing interoperatibility and orthogonality (Lu, 2010). This technique has been used for combinatorial drug screening (Kim et al., 2012). The microfluidics chip by Cooksey et al. (Figure 2.4B) provides the ability to generate complex spatial gradients in a central chamber from combinations of up to 16 unique inputs by using segments of high fluid resistance and outlets to control flow (Cooksey et al., 2009).

Dynamic characterization requires the ability to trigger inputs on and off at a given frequency and measure the delay between the change in input and change in output as both valid and invalid inputs require time to propagate through the system. Faults may occur in a system when inputs are changed before the output is stable, when unstable outputs are used in a downstream function, or when the outputs of unstable inputs are used. Determining these timing characteristics of a biological part requires precise temporal control over the inputs to that system.

Wang et al. used values to control inputs through a T junction to create square waves and ramp functions (Figure 2.4C) to characterize the dynamic signaling behavior of the social amoeba *Dictyostelium discoideum* as it transitions from a single-celled to a multicellular form during its life cycle (Wang et al., 2012). A different method of function generation uses laminar interface guidance to direct the laminar interface between input flows by adjusting the ratio of input flows (Bennett et al., 2008). Further refinement of this method led to the development of the 'Dial-a-Wave' device (Figure 2.4D) used to study the dynamics of environmental effects on the galactose metabolism network in yeast (Baumgartner et al., 2011). These microfluidic function generators can be also used for frequency domain analysis, which allows for applications of control theory techniques (Lu, 2010) such as block modeling and provides additional insights on noise and stability in biological devices (Cox et al., 2006; Simpson et al., 2003). Advances in microfluidic fabrication means that on-chip microfluidic oscillators (Mosadegh et al., 2010; Duncan et al., 2013) could also be used to generate complex input stimuli waveforms for device characterization while relying less on external hardware.

# **Future work**

Currently, part characterization experiments for static and dynamic behavior are carried out individually, and as such, are costly in both time and reagents. The expense of these experiments no doubt contributes to the lack of available characterization data. As a next step in the progression of designs useful for part characterization, I suggest a microfluidics platform for multi-dimensional characterization of biological parts. Such a device would allow for simultaneous experiments and data collection of the input/output dose-response behavior, timing characteristics, and noise analysis through measuring single cell gene expression (Lu, 2010).

A starting point for such a platform could begin with a design similar to the

gradient generator by Cooksey et al. (shown in Figure 2·4B). A number of cell traps or microchemostats could be placed in the central chamber for monitoring cell growth and gene expression at the single cell level. A full discussion of single cell analysis in microfluidics is provided elsewhere (Yin and Marshall, 2012), while some of the key microfluidic devices in single cell trapping and cell culture are described in Section 2.3.4. The input to the central chamber could then be switched between a gradient generator and a waveform generator to allow for multiple types of experiments on the same device. Ideally, multiple experiments could be run on the same biological part simultaneously with the same microfluidics setup on this device.

For example, the biological part in this microfluidics device could be subjected to a gradient of inputs to measure the dose response. The inputs could be turned on and off at will to generate the temporal waveforms needed to measure the timing characteristics. Finally, as the cell traps could support single cell analysis, noise analysis could be performed on the part. Being able to perform many different experiments using one setup could allow for rapid characterization of new biological parts and devices.

#### 2.3.2 Design

The nature of biology and evolution results in many homologous biological parts and pathways. Using homologous parts in a device leads to unwanted molecular interactions in the cell and interferes with the intended function of the device. These unwanted interactions are referred to as biological crosstalk. The likelihood of crosstalk increases as biological devices grow more complex and involve more regulatory networks (Voigt, 2006). The use of orthogonal parts (parts that do not interfere with each other) reduces crosstalk, but there is a lack of these parts in the current repertoire of synthetic biology. To increase the scalability of biological devices, new orthogonal parts and regulatory systems (Stanton et al., 2014) must be found or the currently available parts and systems (Tamsir et al., 2011) must be reused.

### Challenges

New orthogonal parts can be discovered by surveying known genomes for novel regulatory networks. By mining the genomic database at the European Bioinformatics Institute, Stanton et al. curated a collection of 73 homologs to TetR (a commonly used gene comprising of a repressible promoter and the repressor protein), and from those homologs, screened and isolated 16 orthogonal promoter-repressor pairs for use in new genetic devices (Stanton et al., 2014). The limiting step in this process is the final screening of pairwise interactions as over 5000 individual experiments were required to screen the homolog library. Microfluidic high throughput screening platforms would allow for hundreds, if not thousands, of parallel experiments and reduce the time needed to discover novel orthogonal parts.

New parts may also be obtained through directed evolution, a method of applying selective pressure to a library of variants to engineer for specific functions without prior knowledge of the system (Cobb et al., 2012). Conventional methods for cycles of mutation, cell growth, and selection require frequent human intervention and several days per cycle, but new automation techniques such as Multiplex Automated Genome Engineering (MAGE) (Wang et al., 2009) reduce both time and human attention required to generate large libraries. Using MAGE to optimize the pathway in *E. coli* that produced isoprenoid lycopene required screening approximately  $10^5$  colonies after 5-35 evolution cycles. The scale of microfluidic devices is too small to screen for the level of diversity produced by MAGE, but perhaps may be used as a secondary screening platform on a subset of the optimized colonies.

One method of part reuse, as demonstrated by Tamsir et al., is to separate large circuits into smaller circuits, each in a different cell colony, which communicate with each other through intercellular signaling chemicals. Using this technique, they built all possible two-input Boolean functions from biological NOR gates. The colonies are spatially separated on a plate by hand, with the intercellular signaling chemicals spreading through diffusion. However, the diffusion of these signals is not directed towards specific colonies and may reach unintended targets to cause crosstalk between circuits. Microfluidics could be used to physically isolate each colony and restrict intercellular signaling to specific colonies by controlling media flow to reduce crosstalk.

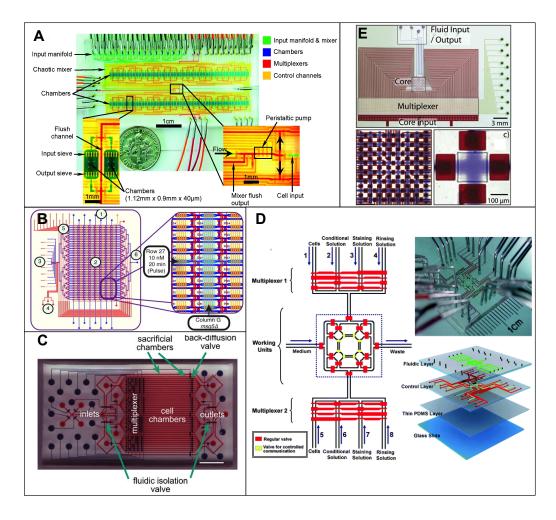

## Current solutions

An early device by Gómez-Sjöberg et al. contained 96 cell culture chambers, each with the capability for unique culture conditions, for automated screening and assays (Figure 2.5A). This device was used to study the effects of transient stimulation on human stem cells (Gómez-Sjöberg et al., 2007). Increased miniaturization of components and a focus on single cell imaging have led to higher density screening platforms. A device by Cheong et al. (Figure 2.5C) allows high throughput analysis of single cell signaling dynamics in 32 cultures (Cheong et al., 2009b; Cheong et al., 2009a). Taylor et al. developed a device with 2048 cell culture chambers capable of conducting 256 simultaneous screening experiments (Figure 2.5B) for studying mating hormone responses in yeast (Taylor et al., 2009) while Denervaud et al. developed a parallel microchemostat array for growing and observing 1152 strains of yeast-GFP strains (Dénervaud et al., 2013). These devices could be adapted for the screening and observation of part libraries developed through genomic mining and directed evolution.

An example of using microfluidics to control intercellular signaling is described by Liu et al. (Liu et al., 2010) with a four chamber network connected by thin channels for communications which could be opened or closed with valves (Figure 2.5D) used to study the response of NIH 3T3 fibroblasts to soluble signals from

Figure 2.5: (A) 96 chamber cell culture device that allows for individual conditions in each chamber. ("Reprinted with permission from R. Gómez-Sjöberg, A. A. Leyrat, D. M. Pirone, C. S. Chen and S. R. Quake, Analytical chemistry, 2007, 79, 8557– 8563. Copyright 2007 American Chemical Society.") (B) High throughput screening device capable of 256 simultaneous screening experiments. (Used with permission from (Taylor et al., 2009). Copyright 2009 Taylor et al.) (C) High content cell screening device used to study cell signaling. (Used with permission from (Cheong et al., 2009a). Copyright 2009 Cheong et al..) (D) Device for control and monitoring of intercellular communications. (Reproduced from Ref. (Liu et al., 2010) with permission from The Royal Society of Chemistry.) (E) Programmable general purpose microfluidic architecture with 64 nodes for reactions and liquid storage. Insets show the array of nodes and the valves surrounding each node. (Reproduced from Ref. (Fidalgo and Maerkl, 2011) with permission from The Royal Society of Chemistry.)

hepatocellular carcinoma cells. A network similar to this could be used to isolate cells and control signaling in biological distributed computing. A general purpose software-programmable architecture of an array of nodes surrounded by individually addressable valves similar to the one developed by Fidalgo et al. (Figure 2.5E) could be used to increase the size of circuits used in distributed biological computation. Incorporating basic Boolean logic directly into the chip through the use of pressure gain valves (Nguyen et al., 2012; Weaver et al., 2010; Devaraju and Unger, 2012) could allow further scaling of the microfluidic architecture by reducing the number of external control lines needed for larger experimental setups. Preliminary work has also been done on integrating microfluidic devices with liquid handling robots to increase automation and decrease the reliance on external control lines (Waldbaur et al., 2013).

### **Future work**

The idea of distributed biological computing (Tamsir et al., 2011; Regot et al., 2011; Macía et al., 2012) can be expanded upon with high-throughput arrays and control of intercellular signaling through valves to produce a hypothetical platform for biological computing. This platform might leverage technologies already present in electrical engineering and digital design to further biological circuit design in synthetic biology. The architecture for this platform may contain both the microfluidic architecture and the software for integrating biological circuit design with microfluidic valve controls.

The microfluidics architecture for this hypothetical platform could contain banks of ports for inputs and outputs and an array of microchemostats to house the cells used for computing. Each port and microchemostat could be individually accessible through the use of multiplexing, and each microchemostat could house a cell colony containing a biological device for the basic unit of computation in the larger biological circuit. Chemical signals could be passed from one stage of computation to the next

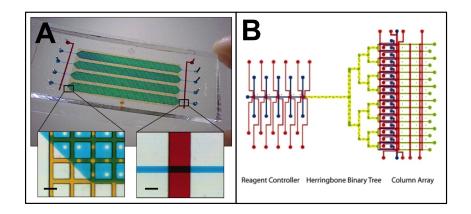

Figure 2.6: (A) Microfluidic chip capable of 4 parallel 500nL synthesis reactions, with the gene synthesis chamber shown on the left in yellow and green and the fluid channel and valve overlay on the right in blue and red. (Kong, David S, Carr, Peter A, Chen, Lu, Zhang, Shuguang and Jacobson, Joseph M, "Parallel gene synthesis in a microfluidic device", Nucleic acids research, 2007, 35, 8, e61, by permission of Oxford University Press) (B) 16 column microfluidic DNA synthesizer comprising of the reagent controller, a herringbone mixer, and a reaction column array. (Lee, Cheng-Chung, Snyder, Thomas M, and Quake, Stephen R, "A microfluidic oligonucleotide synthesizer", Nucleic acids research, 2010, 38, 8, 2514-21, by permission of Oxford University Press).

through the opening and closing of specific valves. An extra isolated microchemostat housing a biological oscillator circuit could be used to synchronize the other biological devices on the chip if the quorum sensing system is used for intercellular communications (Prindle et al., 2012). Synchronization could prevent logic faults caused by timing such as incorrect inputs being used in calculations or incorrect outputs being read.

# 2.3.3 Assembly

A vital part of synthetic biology is the technology used to assemble individual DNA parts into complex devices. The ideal DNA assembly method would allow for arrangement of parts in a specific sequence without scarring that would interfere with device function, easy generation of combinatorial libraries of constructs, and automation of the process (Cheng and Lu, 2012). However, modern assembly methods still fall short of the ideal.

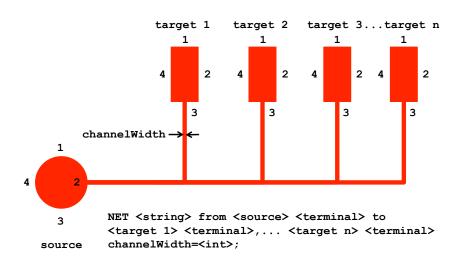

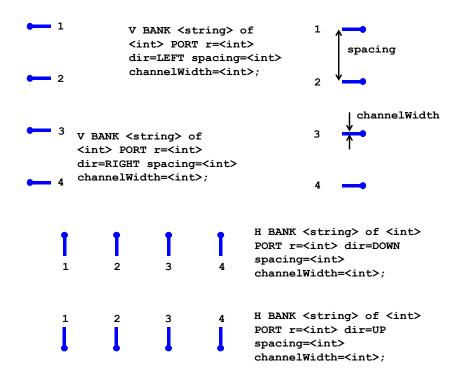

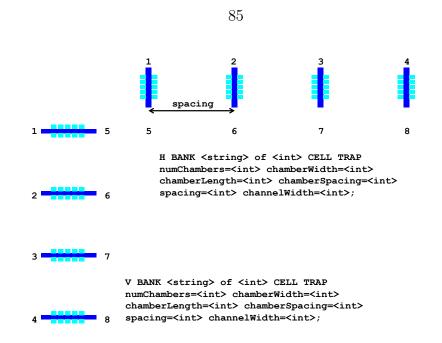

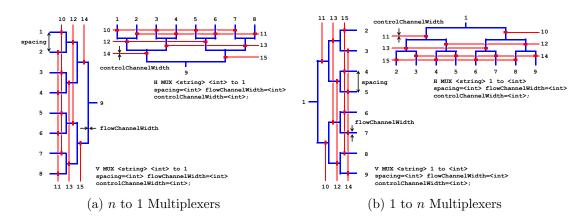

## Challenges