# Negative Bias Temperature Instability (NBTI) Monitoring and Mitigation Technique for MOSFET

#### 13801498 BISWAS SUMIT KUMAR

Supervisor: Dr. Takai Nobukazu

#### **GUNMA UNIVERSITY**

Graduate School of Science and Technology

Education program of Electronics and Informatics, Mathematics and Physics

A thesis submitted for the degree of

Master of Science in Engineering

March 2015

- 1. Reviewer: Prof. Dr Haruao Kobayashi

- 2. Reviewer: Associate Prof. Dr. Ito Tadashi

- 3. Reviewer: Associate Prof. Dr. Takai Nobukazu

Day of the defense:  $20 \mathrm{th}$  February, 2015

#### Abstract

SEMICONDUCTOR reliability is a growing issue as device-critical dimensions shrink and transistor integration continues to roughly double every 24 months. Aggressive oxide thickness scaling has led to large vertical electric fields in MOSFET devices in which oxide breakdown is a critical issue. These high fields also lead to significant threshold voltage shift over time due to the negative bias temperature instability (NBTI) effect, creating additional uncertainty in device behaviour. In the presence of these degradation mechanisms, it is increasingly difficult to ensure the reliability of ICs over their lifetimes. Since the sensitivity of device lifetime to operating conditions has increased, dynamic control schemes that modulate the voltage, sleep state, and workload of processing elements and circuitry in large systems have been pro- posed. Dynamic control further complicates a priori reliability qualification and makes a case for on-chip structures to be used for real-time estimation of device and circuit degradation.

Although many physical details are still under investigation, it has been widely accepted[2][4] that the electrical field across the oxide causes continuous trap generation in Si-SiO2 interface of transistor. These traps usually originate from Si-H bonds in gate oxide layer [1][4]. These bonds can easily break with time and generate positive interfacial traps (donor-like state). This understanding is described by Reaction-diffusion (R-D) analytical models[1] [2][4]. Amongst of all consequences of generated traps, transistors threshold voltage shift has been most dominant. During the time transistor is under the stress Vth increases, while in the recovery time this Vth shift shrinks, but is never nullified. Due to these Vth shift, circuit operation faces

a significant operational delay for any analog circuits.

In this paper, we explain the influence of Negative Bias Temperature Instability (NBTI) in circuit operation and propose a method for detecting NBTI degradation of circuit in order to design a robust system. NBTI takes place when transistor is negative-biased, which is a usual biasing for PMOS. Due to the sever functional hazard caused by NBTI in an analog circuit operational state, it has become eminent to find a permanent solution for NBTI degradation. However so far the most widely used technology for NBTI degradation mitigation is guard banding, which is overly costly and highly power consuming for analog circuit. As new degeneration of electronic circuits needs to be costflective and at the same time reliable in performance, guard banding can no longer satisfy the demand of a stable and cost-effective circuit based solution for NBTI mitigation. Therefore, our research is based on finding the best possible solution for NBTI degradation. Here, we have proposed an new on chip detection method for NBTI degradation, and using the yield of the detecting circuit we tend to mitigate the NBTI dynamically using DVS (Dynamic voltage Scaling) Technology.

### To ...

All my lab mates who sincerely supported my research throughout the whole time.

#### Acknowledgements

This work was supported by the STARC (Semiconductor Technology Academic Research Centre). It was conducted during my studentship from April, 2012 until March,2015 at Takai-kobayashi Laboratory at Gunma University.

First and foremost I would like to thank my supervisor Prof. Takai Nobukazu for providing me this opportunity of carrying out research in the field of my interest at his laboratory. He provided continuous support, feedback and guidance which enabled me to move forward in my thesis in the right direction. He always offered the freedom and encouragement to try different things which made this entire journey an amazing experience. His deep knowledge and vast experience in the field of Analog circuit devices added great value to my research. I thank him for the understanding, patience and trust he vested on me.

Next, I would like to thank Dr. Kobayashi Haruo. He's constant support and guidance has always been the light of this research. His encouragement and support made me come this far in this research. I has always been a great pleaser to close to such a noble professor and receive his guidance. His deep knowledge of circuitry system and analog circuit devices was aways been a great value to this research. I would also like to thank Dr. Ito Tadashi for his supervision.

I would like to thank my senior Mr. Kamiyama Touru for his support and help. His hard work at this project has always been a great value to my research work. I would like to thank my Lab mates Mr. Takayuki Negishi, Mr. Shunsuke Takanaka, Mr. Koutaro Kaneya, Mr. Daichi Motojima for there support and help. I would also like to

convey my gratitude to my lab senior Dr Zach Nosker, who's constant help and courage has always been a guidance through out this project.

## Contents

| Li | st of                  | Figures                                                                        | V          |  |  |  |  |  |  |  |

|----|------------------------|--------------------------------------------------------------------------------|------------|--|--|--|--|--|--|--|

| Li | $\operatorname{st}$ of | Tables                                                                         | vii        |  |  |  |  |  |  |  |

| 1  | Intr                   | oduction                                                                       | 1          |  |  |  |  |  |  |  |

|    | 1.1                    | Motivation                                                                     | 1          |  |  |  |  |  |  |  |

|    | 1.2                    | Aging in Deep-submicrometer MOSFET Technology                                  | 3          |  |  |  |  |  |  |  |

|    | 1.3                    | Impact of Aging on Analog and Mixed Signal Circuits                            | 4          |  |  |  |  |  |  |  |

|    | 1.4                    | State-of-the-Art in Circuit Reliability Research                               | 6          |  |  |  |  |  |  |  |

|    | 1.5                    | NBTI degradation                                                               | 10         |  |  |  |  |  |  |  |

|    | 1.6                    | Contribution of this work                                                      | 13         |  |  |  |  |  |  |  |

| 2  | Aging Physics          |                                                                                |            |  |  |  |  |  |  |  |

|    | 2.1                    | MOSFET Device Wearout                                                          | 17         |  |  |  |  |  |  |  |

|    | 2.2                    | Impact on Device Parameters                                                    | 18         |  |  |  |  |  |  |  |

|    | 2.3                    | Bias Temperature Instability (BTI)                                             | 20         |  |  |  |  |  |  |  |

|    |                        | 2.3.1 NBTI in pMOSFETs                                                         | 21         |  |  |  |  |  |  |  |

|    |                        | 2.3.2 PBTI in nMOSFETs                                                         | 25         |  |  |  |  |  |  |  |

|    |                        | 2.3.3 BTI degradation trend in MOSFETs                                         | 27         |  |  |  |  |  |  |  |

| 3  | Neg                    | ative Bias Temperature Instability (NBTI) Model                                | <b>2</b> 9 |  |  |  |  |  |  |  |

|    | 3.1                    | Negative Bias Temperature Instability (NBTI) Effect                            | 29         |  |  |  |  |  |  |  |

|    | 3.2                    | Overview of Existing NBTI Model                                                | 30         |  |  |  |  |  |  |  |

|    |                        | 3.2.1 Classical Reaction-Diffusion Model $\ \ldots \ \ldots \ \ldots \ \ldots$ | 32         |  |  |  |  |  |  |  |

|    |                        | 3.2.2 Improved RD Model                                                        | 36         |  |  |  |  |  |  |  |

|    | 3.3                    | NBTI Model with Temperature Variation                                          | 40         |  |  |  |  |  |  |  |

| 4                         | MO    | SFET Degradation Due to NBTI                                                                                                  | <b>42</b>  |

|---------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|------------|

|                           | 4.1   | Threshold Voltage degradation                                                                                                 | 42         |

|                           | 4.2   | Drain current decrement due to NBTI degradation                                                                               | 45         |

|                           | 4.3   | Transistor Delay Model                                                                                                        | 45         |

|                           | 4.4   | NBTI Induced Delay                                                                                                            | 47         |

|                           |       | 4.4.1 NBTI Induced Delay                                                                                                      | 47         |

| 5                         | Effe  | ect of NBTI degradation on Analog circuit                                                                                     | 49         |

|                           | 5.1   | Transition time increment of circuit due to NBTI                                                                              | 49         |

|                           | 5.2   | Delay degradation due to Transition time increment of circuit                                                                 | 51         |

|                           | 5.3   | slew rate degradation of comparator circuit                                                                                   | 52         |

| 6                         | NB    | TI Monitoring Technique                                                                                                       | <b>55</b>  |

|                           | 6.1   | NBTI detection method                                                                                                         | 55         |

|                           |       | 6.1.1 Conventional method and its limitations                                                                                 | 55         |

|                           |       | 6.1.2 NBTI New Monitoring Concept                                                                                             | 56         |

|                           |       | 6.1.3 NBTI Monitoring Scheme                                                                                                  | 58         |

|                           | 6.2   | Transition Time Comparator (TTC)                                                                                              | 59         |

|                           | 6.3   | Time-to-Voltage Converter (TVC)                                                                                               | 61         |

|                           | 6.4   | Control Circuit)                                                                                                              | 62         |

|                           | 6.5   | Simulation result                                                                                                             | 62         |

| 7                         | NB    | TI Mitigation Technique                                                                                                       | 64         |

|                           | 7.1   | Limitations Conventional NBTI mitigation method                                                                               | 64         |

|                           | 7.2   | Proposed NBTI mitigation method : DVS (Dynamic Voltage Scall-                                                                 |            |

|                           |       | $\mathrm{ing})  \dots $ | 65         |

|                           |       | 7.2.1 Self Adjusting Threshold Voltage (SATV)                                                                                 | 66         |

|                           | 7.3   | Circuit diagram and Simulation of SATV                                                                                        | 67         |

| 8                         | Dis   | cussion                                                                                                                       | <b>7</b> 0 |

| $\mathbf{R}_{\mathbf{c}}$ | efere | nce                                                                                                                           | 71         |

## List of Figures

| Matching sensitive analog and mixed signal circuits                    | 5                                                                             |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| IEEE publications in the field of analog and mixed signal circuit      |                                                                               |

| reliability                                                            | 9                                                                             |

| Aim of this work                                                       | 15                                                                            |

| nMOS: threshold voltage virgin device                                  | 18                                                                            |

| nMOS: threshold voltage degraded device                                | 19                                                                            |

| pMOS in triode operation                                               | 22                                                                            |

| pMOS in saturation operation:                                          | 23                                                                            |

| High- $\kappa$ nMOS in triode operation:                               | 25                                                                            |

| High- $\kappa$ nMOS in saturation operation:                           | 26                                                                            |

| BTI aging behavior for selected MOSFET                                 | 28                                                                            |

| Bias conditions during circuit operation of a CMOS inverter            | 30                                                                            |

| The degradation of Id-Vg and gm-Vg curves of p-MOSFET                  | 31                                                                            |

| Schematic view of the RD model under stress and recovery conditions $$ | 32                                                                            |

| Typical time dependence of NBTI                                        | 34                                                                            |

| Fitting delVth (measured by ultra-fast On-The-Fly technology           | 34                                                                            |

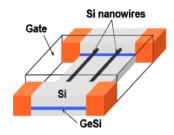

| The 3-D schematic view of the Twin Silicon Nanowire MOSFET .           | 36                                                                            |

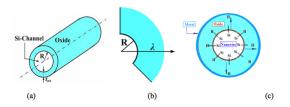

| Cylindrical MOSFET with channel radius R $\dots$                       | 36                                                                            |

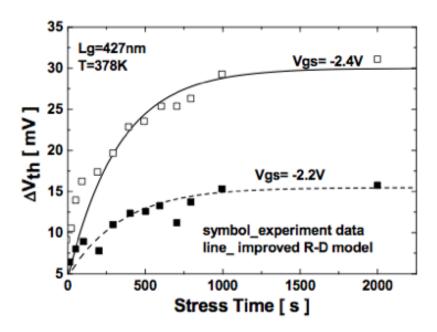

| Comparison between modeling result and the measured data under         |                                                                               |

| stress bias of Vgs=-2.4V and -2.2V $\dots$                             | 38                                                                            |

| Comparison of the experiment data (solid symbol) with both Stan-       |                                                                               |

| dard RD model (open symbol) and improved RD model (line)[38 .          | 39                                                                            |

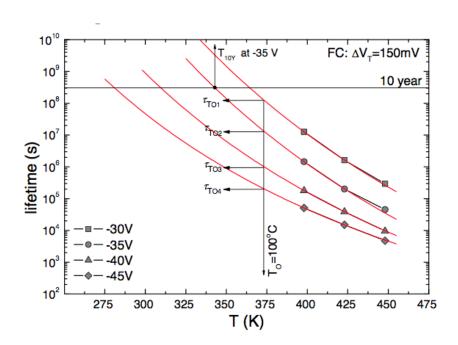

| ${\it MOSFET}$ lifetime decrement due to temperature increament        | 41                                                                            |

|                                                                        | IEEE publications in the field of analog and mixed signal circuit reliability |

#### LIST OF FIGURES

| 4.1 | Threshold voltage shift due to NBTI considering RD model                | 43 |

|-----|-------------------------------------------------------------------------|----|

| 4.2 | shifted threshold voltage of a 32 nm pMOS transistor versus timel       | 44 |

| 4.3 | Shift in Id (drain current) due to shifted threshold voltage $\dots$ .  | 45 |

| 4.4 | ID-VGS characteristics of p-channel MOSFETs during NBTI stress-         |    |

|     | ing                                                                     | 46 |

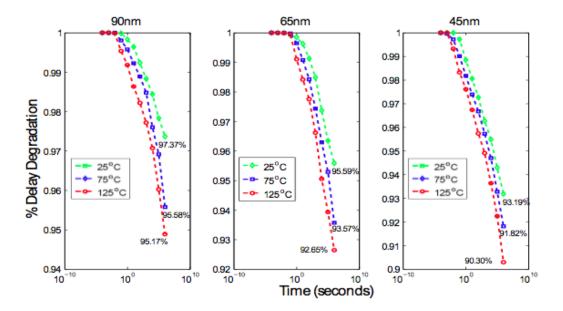

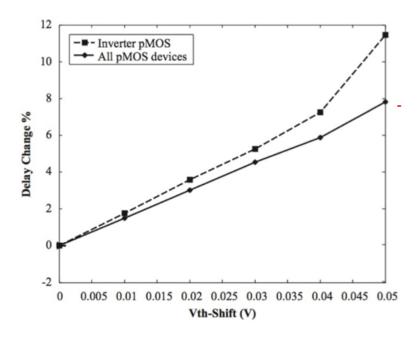

| 4.5 | Percent delay degradation due to threshold voltage shift                | 48 |

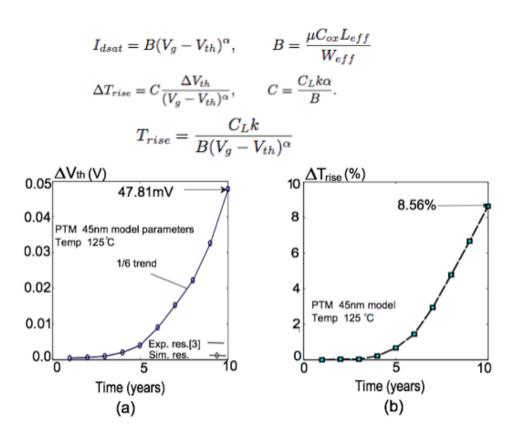

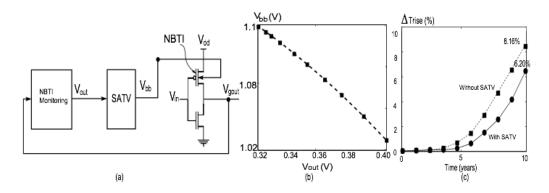

| 5.1 | (a)<br>NBTI induced $V_{th}$ increment of PMOSFET as a function of time |    |

|     | (b) inverter output $\delta T_{rise}$ increment as a function of time   | 50 |

| 5.2 | Delay degradation of Inverter circuit due to Vth shift caused by        |    |

|     | NBTI degradation                                                        | 51 |

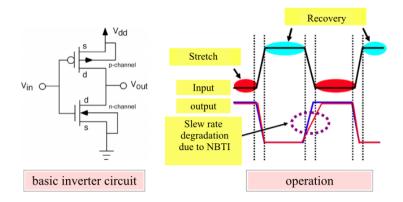

| 5.3 | slew rate degradation of Inverter circuit (operational state)           | 52 |

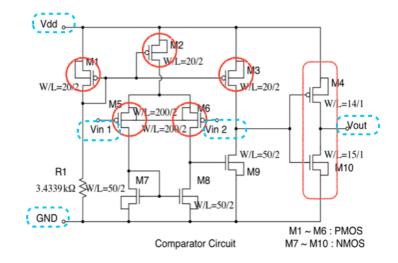

| 5.4 | comparator circuit)                                                     | 53 |

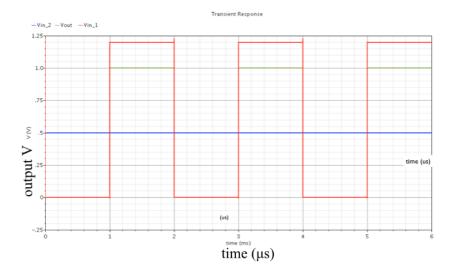

| 5.5 | comparator circuit output simulation)                                   | 53 |

| 5.6 | comparator circuit output simulation: NBTI degradation                  | 54 |

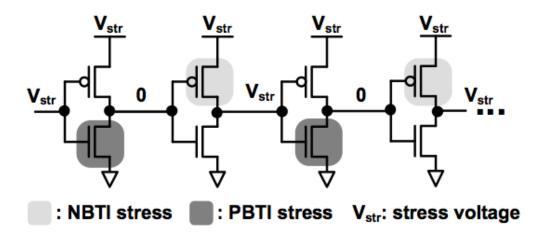

| 6.1 | Conventional ring oscillator based NBTI monitor)                        | 57 |

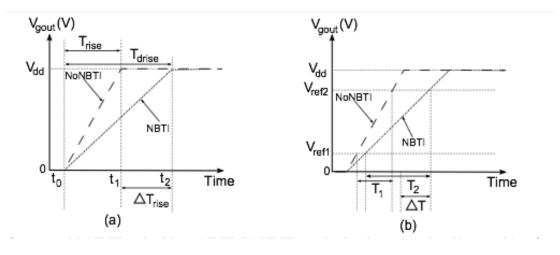

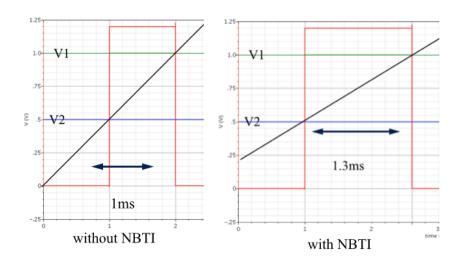

| 6.2 | (a) Trise of a gate with NBTI and without NBTI (b) NBTI mon-            |    |

|     | itoring by comparing Vgout with reference voltages Vref1 and            |    |

|     | Vref2)                                                                  | 57 |

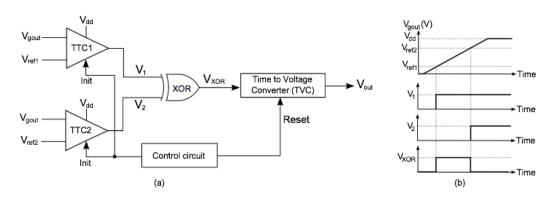

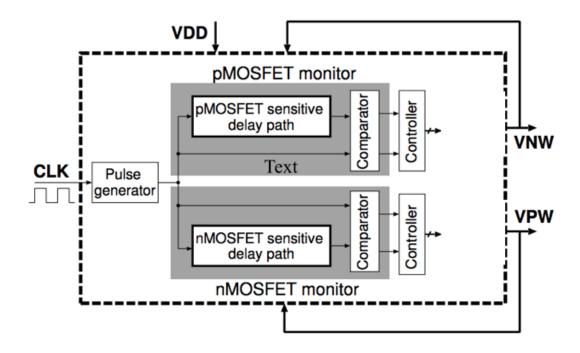

| 6.3 | (a) (a) Block diagram of the proposed NBTI monitoring scheme            |    |

|     | that compares gate output with two reference voltages (b) Timing        |    |

|     | diagram of NBTI monitor)                                                | 58 |

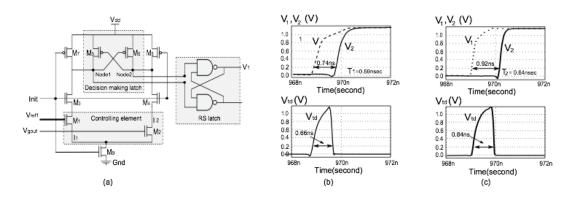

| 6.4 | (a) Schematic of transition time comparator (b) Low-to-high tran-       |    |

|     | sitions of TTC1 and TTC2; Active high duration of XOR without           |    |

|     | and (c) with NBTI)                                                      | 60 |

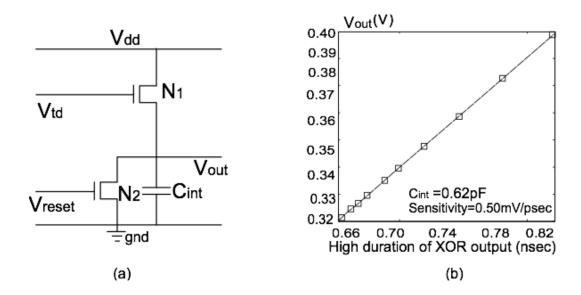

| 6.5 | (a) Schematics of TVC, (b) Output characteristics of TVC                | 62 |

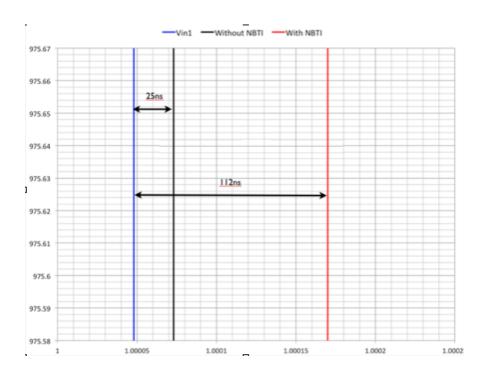

| 6.6 | Simulation result of TTC circuit sung TSMC90nm process                  | 63 |

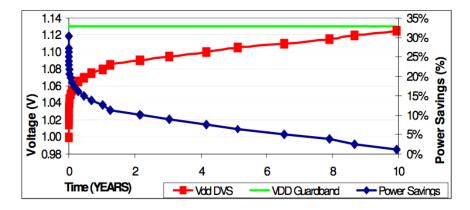

| 7.1 | Significance in operation of DVS compared to Guardbanding)              | 65 |

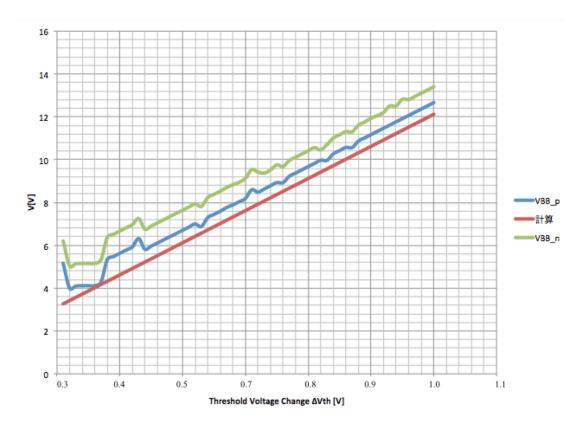

| 7.2 | (a) Schematic of the self adadjusting threshold voltage scheme (b)      |    |

|     | The modified Vbb due to the TVC output (Vout) variation (c)             |    |

|     | Trise increment due to NBTI with and with our SATV)                     | 67 |

#### LIST OF FIGURES

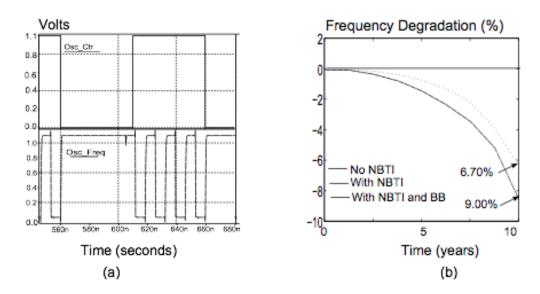

| 7.3 | (a) Samples of Osc Ctr and Osc Freq waveforms (b) Frequency    |    |  |  |  |  |  |  |  |

|-----|----------------------------------------------------------------|----|--|--|--|--|--|--|--|

|     | degradation due to NBTI with and without body biasing) $\dots$ | 68 |  |  |  |  |  |  |  |

| 7.4 | Block diagram of SATV (DVS) system)                            | 68 |  |  |  |  |  |  |  |

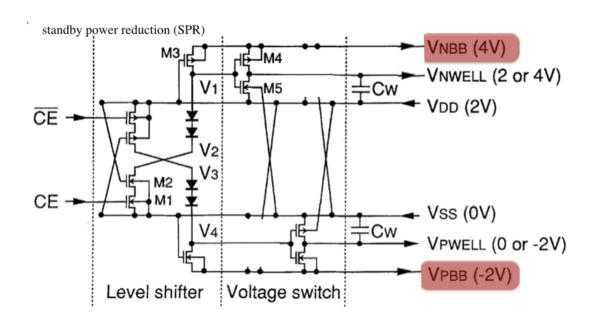

| 7.5 | Circuit diagram of SATV (DVS) system)                          | 69 |  |  |  |  |  |  |  |

| 7.6 | simulation result of SATV (DVS) system)                        | 69 |  |  |  |  |  |  |  |

## List of Tables

| $\circ$    | 1 . | Application  | 1 . 4 . 1 | ·     |      |       |   |   |   |   |   |   |   |  |   |   |   |   |   |   | 6 | <b>&gt;</b> - |

|------------|-----|--------------|-----------|-------|------|-------|---|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---------------|

| '/         |     | a nniication | related   | aono  | 1190 | Cases |   |   |   |   |   |   |   |  |   |   |   |   |   |   |   | , ,           |

| <i>4</i> . | L 1 | TDDIICautoii | rciacca   | aging | ubc  | Cabcb | • | • | • | • | • | • | • |  | • | • | • | • | • | • |   |               |

## 1

## Introduction

#### 1.1 Motivation

Since the early days of microelectronics, integrated MOSFET (Metal Oxide Semiconductor Field Effect Transistor) technology has been continuously advanced by dimension shrink. Via the equivalent scaling of relevant processing parameters channel area, oxide thick- ness and supply voltage - the fundamental device characteristic keeps the same with less area and power consumption. This general feature forms the basis of today 's triumph of microelectronics and the initiation of the information era.

But MOSFET (Complementary Metal Oxide Semiconductor) - the processing of n- and p- type MOSFETS on one chip - technology scaling has to face some inheritable problems like device noise and process fluctuations, that are given by semiconductor physics, processing imperfections and its atomic limitations. For example, the circuit relevant SNR (Signal to Noise Ratio) reduces for every technology step as voltage headroom is reduced with decreased supply voltage, but device noise contributions remain constant. Since the 0.1 um regime, MOSFET processing migrates to the non-constant field scaling approach, by keeping the supply voltage at higher levels than would be required by the scaling factor, while all other parameters are scaled in the usual way. Here, raised electric fields in MOS devices are accepted at the cost of increased wear out, thus worsening device reliability but maintaining sufficient SNR. At the same time, higher integration rates with increased chip complexity demand for an enhanced device reliability

to maintain a stable and reliable system, which has to be further provided by the MOSFET processing. In the past, this was achieved by the continuing optimization of the chip processing, but the gap between the optimization window and limiting semiconductor physics reduces and device aging mechanisms come to the fore.

Condensed operation of MOSFET devices at only slightly reduced supply voltages further leads to increased on-chip operation temperatures, that even worsen device wear out. On the other hand, reduction in voltage headroom increases circuit sensitivity towards device aging. Advanced MOSFET processing options like the inclusion of novel high-  $\kappa$  materials into the MOS gate stack lowers gate leakage, but further debuts device aging effects that were nonexistent in classic SiO2 or SiON based MOSFET technologies. The general shrink of channel length further induces novel aging effects, that even occur for switched off de- vices. Increased circuit sensitivity and growing appearance of aging effects in magnitude and number involve the reliability topic as an emerging concern in today 's and future MOSFET microelectronics [1, 2].

The impact of device wear out on circuit level was only rudimentary studied in the past, as occurring minor device parameter drifts were covered by design techniques like guard banding or mitigated by the operation in safe operation area. Contrary to the inherently robust digital circuits, where device wear out mainly leads to an increase of switching delay, analog circuitry is more sensitive towards a change of device characteristics like drive current, transconductance or noise behaviour. The requested compliance of numerous circuit performance specifications to maintain proper system functionality makes reliability proofs for analog circuits more challenging. With the increased appearance of device aging effects in advanced MOSFET technologies, their impact on circuit level demands for future research effort [3]. But also circuit level reliability measurement proofs arise as a challenging task, as an accelerated stress methodology to exactly reproduce equivalent end-of-lifetime states is still missing.

## 1.2 Aging in Deep-submicrometer MOSFET Technology

Integrated electronic systems with AMS circuits fabricated using MOS technology find a wide range of applications ranging from life critical field; aircraft, pacemaker and automotive, consumer electronics field; television systems, mobile, camera and gaming station, to non-critical field; toys and electronic greeting cards. MOS transistors used in these circuits are expected to degrade (age) with time. This causes the circuit performance to deviate from its specifications measured post fabrication. [3,6]So device and circuit reliability evaluation is of prime practical importance. The recent MOSFET technologies have witnessed slowing down or stopping of supply voltage  $(V_{DD})$  and threshold voltage  $(V_{th})$  scaling because of the non-scalability of sub-threshold slope whereas the transistor gate length (L) and thickness of gate oxide (tox) is continuing to scale down. This results into a net increase in lateral electric field, effective channel field and the vertical oxide field. Moreover, with scaling of device geometry and the increase in device number, power consumption rises resulting into rise in the operating temperature which produces another big issue with respect to device reliability. The introduction of first nitrogen and then high-  $\kappa$  in the gate oxide stack has lead to enhancement of oxide degradation in both pMOSFET and nMOSFET devices. This leads to enhancement of different aging degradation mechanisms in the integrated circuits fabricated using state-of-the-art deep sub-micrometer MOSFET technology.

Aging degradation mechanisms can be classified into destructive and non-destructive categories, depending on if it leads to transistor hard failure (e.g. gate-oxide breakdown) or wearout (e.g. bias temperature instability (BTI), conducting, non-conducting hot car- rier injection (CHCI, NCHCI)). Hard failures due to destructive stress are completely unacceptable since it can partially or completely disrupt the functionality of the circuit.[14]

Aging degradation mechanisms can be classified into destructive and non-destructive categories, depending on if it leads to transistor hard failure (e.g. gate-oxide breakdown) or wearout (e.g. bias temperature instability (BTI), conducting,

non-conducting hot carrier injection (CHCI, NCHCI)). Hard failures due to destructive stress are completely unacceptable since it can partially or completely disrupt the functionality of the circuit.[12]

On the other hand wearout mechanisms due to the non-destructive stress are acceptable unto a limit which is defined by the desired circuit accuracy and precision. So to pre-dict if the circuit meets the target lifetime expectation, performance degradation over lifetime under non-destructive stress effects must be analyzed by the designer. Accurate prediction of aging degradation is important to avoid expensive re-spins, for gaining the consumers trust and to correctly define the warranty period and cost of the product. In order to perform quick practical aging predictions to evaluate the lifetime reliability of an integrated circuit, it is necessary to map the end-of-life use case condition of the product (e.g. mobile phone use case of 4 Years, 85C, 105% of worst case VDD) to an meaningful and accurately mapped accelerated stress condition (e.g. 103s, 125C, 120\% of worst case VDD). For these evaluations the AMS circuit is assumed to be well designed and functioning perfectly at time zero. This acceleration allows the stress conditions to shrink the 4 year product life to a 103s period so the reliability of the circuit can be studied in laboratory and guaranteed. The shrinking in lifetime of a MOSFET device is possible by elevating the stress temperature, bias voltages and time [3,9,28].

## 1.3 Impact of Aging on Analog and Mixed Signal Circuits

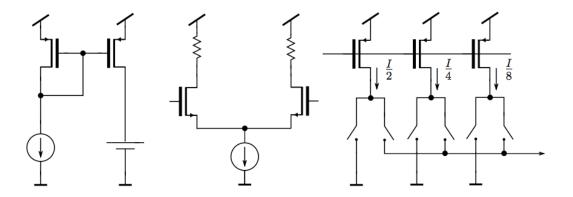

Current mirror, operational amplifier and bandgap reference circuits are some of the very basic building blocks of AMS systems. The precision and accuracy of these basic building blocks is linked to the matching of the transistor pairs as illustrated in figure 1.2. The reliability performance of all such matched pair circuits depends closely on their aging differential. Analog circuits always witness DC voltages for biasing purposes irrespective of the input signal unlike digital circuits. Further in addition to the applied DC bias voltages, a high temperature may also exist on the chip because of the high transistor density. Thus the failure rate varies as a function of stress voltage, temperature and time. Further the maximum allowed margins of process and aging degradation induced parameter drifts and variations are lower for analog applications and high resolution mixed signal circuits [2].

The transistors in typical AMS circuit are operated either in active mode or power down mode. Operation in either of these modes can induce aging degradation in the transistors depending on the surrounding bias conditions [3]. In the circuit active mode, the transistors are usually operated in saturation region with gate to source overdrive voltage  $V_{od} = |V_{gs} - V_{th}|$  of around several 100mV and drain to source voltages  $|V_{ds}| > |V_{od}|$ . Diode connected transistors are less prone to aging degradation due to their low biasing values with  $|V_{gs}| = |V_{ds}|$ . Other transistors can see high voltage conditions enough to induce aging degradation due to BTI and/or HCI depending on the input signals and the circuit configuration (closed loop, open loop, feedback, etc.). Asymmetrical input signals lead to aging degradation induced offset voltages in matched differential pairs [4].

Figure 1.1: Matching sensitive analog and mixed signal circuits -

In a typical power down mode the bias currents are switched off to avoid power consumption of the inactive circuit, but the supply voltages are not driven down in order to allow for fast reactivation of the circuit. In this case the potentials of the internal nodes are determined by the input signals and the sub-threshold or off state leakage currents of the transistors. All the transistors connected in

the current mirror configuration are not prone to aging degradation in this case because the diode connected transistors lead to low gate voltages. The remaining transistors can be affected by BTI stress depending on the input signals.

In case of specific circuits like ring oscillator the transistors see high gate to source voltages ( $|V_{gs}|$ ), being switched between VDD and VSS leading to BTI and NCHCI degra- dation. Also the transistor here experience high drain to source voltage ( $|V_{ds}|$ ) during signal transition phase resulting into degradation due to CHCI. CMOS transistor switches with bi-directional current flow typically used in switched capacitor circuits experience similar stress conditions like the transistors in the ring oscillator circuit but with lower  $|V_{ds}|$  values resulting into low CHCI and NCHCI degradation.

Thus accurate evaluation of aging degradation is required on circuit level to obtain realistic risk evaluation for precise reliability qualification. Simply sizing up devices, such as is done to reduce process variation and HCI effects offers little relief to NBTI and PBTI degradation effects on circuits. The AMS circuit designers need to move one step further to include device aging impact into consideration, so that the circuit can meet the specifications at end-of-life ( $E_{oL}$ ). Special circuit techniques are needed as countermeasure for these aging degradation effects [5].

# 1.4 State-of-the-Art in Circuit Reliability Research

Previous circuit design mostly treated device aging as a side effect, that is covered by design margins applied for balancing PVT (Process Voltage Temperature) variations. Nowadays, device aging obtained an individual status as growing source of device variability in the extension to PVTA (Process Voltage Temperature Aging) variations. Grow- ing interest on device degradation lead to several studies on the impact of device aging on circuit level. For digital logic circuits the general aging induced weakening of the de- vice characteristic increases logic gates' switching delay and so induces a time dependent degradation of the data evaluation. This increase of propagation delay can lead to a time dependent violation of timing constraints in the critical path and so to failure of the circuitry [4, 5,

6]. Several detection and sensing approaches, for example using replica circuits to provide a kind of aging odometer [7], are developed and countermeasures are proposed [8]. A general approach to detect and compensate for PVTA variation induced logic errors is treated in [9]. Another relevant field of research is the digital SRAM (Static Random Access Memory), as reliable data storage has to be guaranteed with minimum feature size devices for millions of cells. Reliability investigations revealed, that device degradation in the asymmetric storage state varies SRAM cell stability [10, 11]. Due to the minimum feature size devices, process variations and variations in the degradation effect as well play an important role for the reliability of the storage system. Transient components in device degradations additionally include a time dependent component for the cell stability [12]. For analog and mixed-signal circuits, performance characteristics and thus device aging impacts are more complex [13].

In the study on selected amplifiers of Martin-Martinez, variability is identified as the major concern for advanced MOSFET technologies, which is accompanied by aging induced drift contributions. Variability in the aging effect itself was found to be of minor concern. The study further reveals that aging impacts amplifier gain and GBW (Gain Band Width) dependent on the circuit topology [19]. A detailed investigation on the effect variability for the used devices as well as a general statement on aging sensitive topologies is still missing. In the fundamental work of Thaws, a state-of-the-art differential amplifier is used to study analog circuit reliability according to numerous aging effects. From the point of view of distinct circuit operation states, occurring device stress and resulting aging effects are determined. Aging effects are again expected to degrade circuit performance in offset, gain, noise and linearity. Here, BTI (Bias Temperature Instability) effects, induced by high oxide fields, are expected to arise as the most prominent challenges in future robust circuit design [10]. HCI (Hot-Carrier Injection) is beneficially used to perform calibration of an SRAM sense amplifier [11]. With an automated reliability simulator, an ADC (Analog to Digital Converter) circuit is studied with respect to the impact of device aging by Yan [2]. Several countermeasures like device sizing for improved HCI degradation or a reduction of power consumption to reduce NBTI (Negative Bias Temperature Instability)

aging are evaluated. Nevertheless, a deep understanding of the interaction between device degradation and circuit behaviour is still missing.

In [13], Jha investigated the impact of NBTI on selected basic analog circuit blocks like current mirrors, amplifiers and a current-steering DAC (Digital to Analog Converter). The study showed that device aging impact strongly depends on the circuit topology. For the current mirror circuits for example, huge differences in general aging sensitivity can be seen. Investigations on amplifier circuits reveal large aging induced offset generation for open-loop comparator operation. Due to stable current biasing, transconductance of the circuit remains stable and further impact on performance parameters like gain or GBW are small. For the current-steering DAC, NBTI degradation is expected to induce considerable gain errors, but only minor impact on its linearity. This study shows that sensitivity of the analog circuit strongly depends on its configuration. However, universal rules for aging robust circuitry are not provided.

Further analog circuit types, that are in the focus of reliability investigations, are LC based VCO (Voltage Controlled Oscillator) circuits. This is mainly due to the high volt- age swings during circuit operation [4, 5]. In his study, Lin revealed considerable VCO performance degradations related to HCI device degradation [6]. Sadat showed in [7] that degradation of active bridge devices impacts oscillation amplitude and thus the effective value of the tank capacitance, that further modifies oscillator Phase Noise and startup behaviour. Current-reusing MOSFET VCO designs are determined to be the most reliable oscillator topologies due to amplitude limitation by the voltage supply. In [8], Reedy reported a significant VCO Phase Noise degradation in the close-in region related to a NCHCI (Non-Conductive Hot-Carrier Injection) induced worsening in device flicker noise - a device characteristic, that is typically not considered in todays aging prediction models.

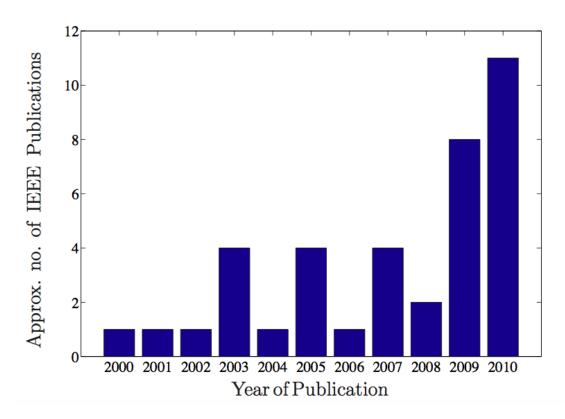

Several studies in the past years showed the increasing impact of device aging on analog circuit blocks and further brought up the most critical analog circuit types. Nevertheless, a throughout and universal study performed on state-of-theart analog circuit designs, providing insight into the mechanisms of the circuit related impact of device aging, is still missing. Analog circuit related device aging taking into consideration typical device dimensions and operation states has to be

Figure 1.2: IEEE publications in the field of analog and mixed signal circuit reliability -

investigated in detail for advanced MOSFET technologies, to reveal analog related degradation behaviour as well as expected variations of the aging mechanisms. Selected circuit designs have to be investigated with respect to their general aging sensitivity to establish approaches for future robust circuit designs. Novel circuit aging modelling approaches, expanding results from circuit reliability simulations, will provide deep understanding of device aging and circuit interaction and will break new ground for aging countermeasures and circuit stress testing as well.

#### 1.5 NBTI degradation

As the device dimensions in metal-oxide-silicon (MOS) technologies have been continuously scaled down, a phenomenon called negative bias temperature instability (NBTI), which refers to the generation of positive oxide charge and interface traps in MOS structures under negative gate bias at elevated temperature, has been gaining in importance as one of the most critical mechanisms of MOS field effect transistor (MOSFET) degradation. NBTI effects are manifested as the changes in device threshold voltage  $(V_T)$ , transconductance (gm) and drain current (ID), and have been observed mostly in p-channel MOSFETs operated under negative gate oxide fields in the range 2 - 6 MV/cm at temperatures around 100 ° C or higherThe phenomenon itself had been known for many years, but only recently has been recognised as a serious reliability issue in state-of-the-art MOS integrated circuits. Several factors associated with device scaling have been found to enhance NBTI: i) operating voltages have not been reduced as aggressively as gate oxide thickness, leading to higher oxide electric fields and increased chip temperatures; ii) threshold voltage scaling has not kept pace with operating voltage, resulting in larger degradation of drain current for the same shift in threshold voltage; and iii) addition of nitrogen during the oxidation process has helped to reduce the thin gate oxide leakage, but the side effect was to increase NBTI. Considering the effects of NBTI related degradation on device electrical parameters, NBT stress-induced threshold voltage shift ( $\Delta V_T$ ) seems to be the most critical one, and a couple of basic questions, which are to be addressed now, are why the NBTI appears to be of great concern only in p-channel devices, and why the negative bias causes more considerable degradation than positive bias.

The bias temperature stress-induced  $V_T$  shifts are generally known to be the consequence of underlying buildup of interface traps and oxide-trapped charge due to stress-initiated electrochemical processes involving oxide and interface defects, holes and/or electrons, and variety of species associated with presence of hydrogen as the most common impurity in MOS devices. An interface trap is an interfacial trivalent silicon atom with an unsaturated (unpaired) valence electron at the SiO2/Si interface. Unsaturated Si atoms are additionally found in SiO2 itself, along with other oxide defects, the most important being the oxygen vacancies.

Si atoms in the oxide are concentrated mostly near the interface and they both act as the trapping centres responsible for buildup of oxide-trapped charge. Interface traps readily exchange charge, either electrons or holes, with the substrate and they introduce either positive or negative net charge at interface, which depends on gate bias: the net charge in interface traps is negative in n-channel devices, which are normally biased with positive gate voltage, but is positive in p-channel devices as they require negative gate bias to be turned on. On the other hand, charge found trapped in the centres in the oxide is generally positive in both n- and p-channel MOS transistors and cannot be quickly removed by altering the gate bias polarity. The absolute values of threshold voltage shifts due to stress-induced oxide-trapped charge and interface traps in n- and p-channel MOS transistors, respectively, can be expressed as:

$$\Delta V_{Tn} = \frac{q\Delta N_{at}}{C_{ox}} - \frac{q\Delta N_{it}}{C_{ax}} \tag{1.1}$$

$$\Delta V_{Tp} = \frac{q\Delta N_{at}}{C_{ox}} - \frac{q\Delta N_{it}}{C_{ax}} \tag{1.2}$$

where q denotes elementary charge, Cox is gate oxide capacitance per unit area, while  $\Delta N_{to}$  and  $\Delta N_{ti}$  are stress-induced changes in the area densities of oxide-trapped charge and interface traps, respectively. The amounts of NBT stress-induced oxide-trapped charge and interface traps in n- and p-channel devices are generally similar[2], but above consideration clearly shows that the net effect on threshold voltage,  $\Delta V_T$ , must be greater for p-channel devices, because in this case the positive oxide charge and positive interface charge are additive.

As for the question on the role of stress bias polarity, it seems well established that holes are necessary to initiate and/or enhance the bias temperature stress degradation[4], which provides straight answer since only negative gate bias can provide holes at the SiO2/Si interface. Moreover, this is an additional reason why the greatest impact of NBTI occurs in p-channel transistors since only those devices experience a uniform negative gate bias condition during typical MOSFET circuit operation.

Several models of microscopic mechanisms responsible for the observed degradation have been proposed, but in spite of very extensive studies in recent years, the mechanisms of NBTI phenomenon are still not fully understood, so technology optimisation to minimise NBTI is still far from being achieved. With reduction in gate oxide thickness, NBT stress-induced threshold voltage shifts are getting more critical and can put serious limit to a lifetime of p-channel devices having gate oxide thinner than 3.5 nm, so accurate models and well established procedure for lifetime estimation are needed to make good prediction of device reliable operation.

Though the gate oxide in nanometre scale technologies is continuously being thinned down, there is still high interest in ultra-thick oxides owing to widespread use of MOS technologies for the realisation of power devices. Vertical double-diffused MOSFET is an attractive device for application in high-frequency switching power supplies owing to its superior switching characteristics which enable operation in a megahertz frequency range.

High-frequency operation allows the use of small-size passive components (transformers, coils, capacitors) and thus enables the reduction of overall weight and volume, making the power MOSFETs especially suited for application in power supply units for communication satellites, but they are also widely used as the fast switching devices in home appliances and automotive, industrial and military electronics. Degradation of power MOSFETs under various stresses (irradiation, high field, and hot carriers) has been subject of extensive research (, but very few authors seem to have addressed the NBTI in these devices [3]. However, power devices are routinely operated at high current and voltage levels, which lead to both self heating and increased gate oxide fields, and thus favour NBTI. Accordingly, NBTI could be critical for normal operation of power MOSFETs though

they have very thick gate oxides.

Given the above considerations, this chapter is to cover the NBTI implications on reliability of commercially available power MOSFETs. In the next section, we will describe the experimental procedure for accelerated NBT stressing applied in our study and analyse typical results for the threshold voltage shifts observed in stressed devices. Applicability of some empirical expressions for fitting the dependences of stress-induced threshold voltage shifts on stress conditions (voltage, temperature, time) to our experimental data will be discussed as well. Third section is to describe in details the results of the procedure applied to fit the experimental data and estimate the device lifetime by means of several fitting and extrapolation models. Impacts of stress conditions, failure criteria, models used for fitting and extrapolation, and intermittent annealing on lifetime projection will be discussed as well. The extrapolation models available in the literature offer only extrapolation along the voltage (or electric field) axis and provide lifetime estimates only for the temperatures applied during the accelerated stressing, so in the next section we propose a new approach, which requires double extrapolation along both voltage and temperature axes, but can estimate the device lifetime for any reasonable combination of operating voltages and temperatures, including those falling within the ranges normally found in usual device applications. Finally, most important findings presented in the chapter will be summarised in the conclusion section.

#### 1.6 Contribution of this work

In this work a detailed overview over major device NBTI aging effects, leading to parametric drifts of device characteristics, but not to a hard destruction of the device is provided. Most recent findings on distinct effect physics and resulting aging prediction model approaches are discussed. Options for consideration of device degradation in classic circuit simulations are reviewed with respect to analog circuit simulation suitability.

Device NBTI degradation for typical analog operation scenarios for an advanced MOSFET process technology is studied by simulation and stress measurements. In doing so, analog related device NBTI ageing degradation not entirely covered

by state-of-the-art modelling is investigated in detail, taking into consideration typical operation states, device dimensions and analog relevant effect properties. Operation modes like accumulation, which are not considered so far and potentially occur during circuit standby, are shown to be another significant reliability issue. Further investigations on aging effect variability as well as transient recovery re- veal the need for novel aging models, that are close to the basing physics. Additionally, it is shown that degradation effects can be beneficially used also for passive reliability improvement.

Throughout investigations on device aging impact on a wide area of analog circuit build- ing blocks are the foundation for a general overview of major circuit aging monitors and the behaviour dependent on the operation state. For instance, current mirror circuits experience current mismatch, amplifiers offset and oscillators power degradation. Further case studies on distinct device and circuit types like varactors and reference generation circuits showed a minor impact of device wearout.

Circuit level aging is very complex, due to the simultaneous interaction of distinct device degradation effects and distinct dominant effects are not per se detectable. A general methodology to accurately predict aging on circuit level is performed via fully analytic modeling of circuit behaviour, that further provides a deep insight into major effect contributions. This approach allows to derive further aging related design concepts and to easily account for circuit level degradation in future MOSFET process technologies.

Via circuit degradation models, a methodology to accurately determine end-of-lifetime equivalent circuit states for accelerated stress test is developed and validated via meaurement for selected circuit types. Furthermore, customized circuit type specific stress testbenches are developed and described providing the ability to stress and measure circuit performance in one test setup. This novel approach allows to use analog circuits' signal sensitivity for further aging effect characterisation, like device flicker noise degradation in oscillator Phase Noise behavior or short-time recovery in fast amplifier circuits. Design related aging countermeasures for reliable analog circuit operation are proposed and evaluated. Furthermore, a novel method to suppress device aging and simultaneously use the induced device parameter drift for circuit calibration is proposed and verified

via measurements. From the overall findings and circuit investigations, guidelines for design of reliable analog circuits are established.

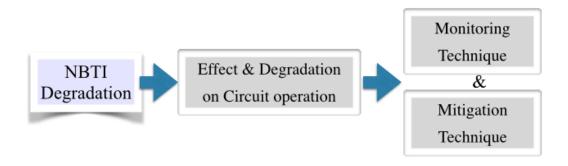

Figure 1.3: Aim of this work - flow of research

In this research we have emphasise on NBTI degradation model and its effect on circuit (analog circuit) operation. As it is obvious that NBTI degradation have a sever effect on circuit operation and parameters, i derives that operational mismatch can certainly be the target criteria to measure NBTI circuit degradation. In this research we have come to the conclusion that the most mentionable NBTi degradation effect an anolog circuit have on its operation is the slew rate degradation and by measuring the rate of slew rate degradation, we can not only determine the existence of NBTI but also the rate of the degradation. As rate of NBTI degradation differs from chip to chip, it can never be predicted accurately while designing the circuit, Therefore an on-chip detection circuit is necessary, which we have proposed using TTC (Time Transient Circuit) monitoring circuit. As shown in fig 1.3, we have stretched our research from on chip monitoring to mitigation technique as well. As we will describe the process in the later part of this paper, we have used DVS (dynamic Voltage Scaling) System to compensate the effect of NBTI degradation on chip. As a system we proposed a new NBTI robust system for analog circuit in this research.

## **Aging Physics**

#### 2.1 MOSFET Device Wearout

As most technical products, also integrated MOS (Metal Oxide Semiconductor) devices suffer from wearout due to their usage in electronic devices. High integration in today's ICs (Integrated Circuits), with billions of MOS transistors on one die, demands MOS (Metal Oxide Semiconductor) insulator thickness of a few nanometers between the controlling gate and the channel. Electric fields across the oxide reach MV/cm although operating in the 1V regime. Those lead to a time dependent wearout of insulators' properties inducing changes in the device characteristics or in worst case to its breakdown. As mentioned in 1.3, technology scaling by inducing non-constant field scaling and inclusion of new materials in the gate stack worsens this wearout from technology node to node.

Aging mechanisms can be separated in two groups: mechanisms leading to drift of device characteristics, but not to an immediate malfunction of the transistor the so called non- destructive aging mechanisms, including BTI and HCI effects. And the destructive mechanisms like TDDB (Time Dependent Dielectric Breakdown)[29, 30] leading to a permanent malfunction of the device. Precursors to the TDDB are the SBD (Soft Breakdown) effects inducing a temporary breakdown of the device. After stress removal, device is working again.

Our investigation on analog circuit aging addresses the non-destructive aging mechanisms, as those are able to change circuit behaviour during lifetime operation. In advance to a dielectric breakdown a huge amount of parameter drift occurs, also acting as a precursor to the hard breakdown. From the system point of view it is not only the hard break- down of an incorporated device leading to malfunction, but also drifts in performance specifications of the analog circuit can lead to failure of the overall system.

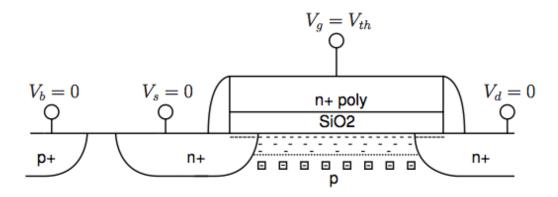

#### 2.2 Impact on Device Parameters

All non-destructive aging mechanisms have in common that insulator wearout is due to inclusion of charge into the insulator region. This additional charge changes device characteristic in several ways. As derived in lots of semiconductor textbooks, threshold voltage  $V_{th}$  of an exemplary nMOS (see fig. ) with zero Bulk-Source voltage  $V_{BS} = 0$  is defined as the inversion mode Gate voltage where electron (minority carrier) density in the inversion region is equal to hole (majority carrier) density of the bulk in thermal equilibrium [31, 32].

Figure 2.1: nMOS: threshold voltage virgin device -

The physical representation of the threshold voltage condition is given by:

$$V_{th} = V_{FB} + 2\Phi_F + \gamma_n \sqrt{2\Phi_F}$$

(2.1)

with VF B the flatband voltage,  $\Phi$  F the Fermi level from intrinsic Fermi level and  $\gamma$  n the Body factor for a nMOSFET, that is dependent on the bulk doping and the dielectric constant of the insulator. A uniformly distributed charge Qdeg

Figure 2.2: nMOS: threshold voltage degraded device -

in the interface to the insulator, as depicted in fig.2.2 would shift the flatband voltage to

$$V_{FB} = \Phi_{MS} + \frac{Q_{deg}}{C_{cride}} \tag{2.2}$$

with  $\Phi_{MS}$  the workfunction difference between gate material and bulk and  $C_{oxide}$  the gate oxide capacitance. Depending on the amount of generated charge,  $V_{FB}$  and so  $V_{th}$  is shifted by

$$V_{th,n} = \Delta V_{FB} = -\frac{Q_{deg}}{C_{oxide}} \tag{2.3}$$

Equation (2.3) also shows that the direction of the  $V_{th}$  shift depends on the polarity of the generated charge. Furthermore, induced oxide charges also impact field dependent effective channel mobility  $\mu_{eft}$ . Equation(2.4) shows there lation of  $\mu_{eff}$  with respect to device operation condition.

$$\mu_{eff} = \frac{\mu_0}{1 + \Theta(V_g - V_{th,n})} \tag{2.4}$$

with  $\mu_0$  the low field surface mobility,  $\Theta$  the mobility degradation coefficient and  $V_g$  the gate voltage. Equation (2.4) reveals a direct relation of  $\mu$  eff to a drift in threshold voltage [33]. But also  $\mu_0$  can be affected by oxide charges at the Si — SiO2 interface acting as Coulomb scattering centers and changing the interface roughness and hence  $\mu_0$  and  $\Theta$  [34]. The often discussed degradation of further device parameters as drain current ID, transconductance gm, subthreshold

swing SS or MOS C - V characteristic can be related to the drift of basic MOS parameters  $V_{th}$  and  $\mu_0$ . These general impacts of device wearout were derived for an exemplary nMOS device, but are also valid for the pMOS counterpart.

#### 2.3 Bias Temperature Instability (BTI)

NBTI for pMOS as well as PBTI (Positive Bias Temperature Instability) for nMOS transistors are derived from the typical inversion mode operation of CMOS devices and their degradation behavior under elevated temperatures. Both effects lead to a general weakening of the transistor characteristic. BTI degradation is strongly dependent on the oxide field given by eq. (2.5) for strong inversion,

$$F_{el,ox} = \frac{V_g - V_{FB} - 2\Phi_F}{t_{ox}} \tag{2.5}$$

with  $V_{FB}$  the flat band voltage,  $\Phi$  F the Fermi Potential defined by the well doping and the lattice temperature and tox the insulator thickness. As shown by eq. (2.5), Vg and tox are key parameters for the BTI degradation.

BTI effects, especially the NBTI in pMOS transistors, were already observed in the early days of MOSFET development [35]. In this decade NBTI was not concerned as a major reliability issue as impact on the formerly buried channel with n+ poly gate for the pMOS was small. Due to constant field scaling in CMOS technology development, that means a similar scaling of Vg and tox, NBTI was well controlled. Changeover to surface channel p+ poly gate pMOSFET increased the NBTI sensitivity. Particularly, the introduction of non-constant field scaling in sub-0.1  $\mu$  CMOS technologies, typically keeping or slightly decreasing Vg but scaling tox in the classic manner, enhanced NBTI as one major degradation mechanism. A corresponding PBTI for nMOS transistor was negligibly small for SiO2 based oxides, but emerged with the introduction of high- $\kappa$  materials in advanced CMOS technologies also for the nMOS transistor [36].

#### 2.3.1 NBTI in pMOSFETs

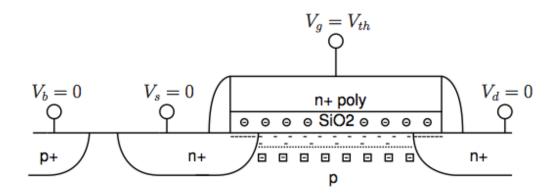

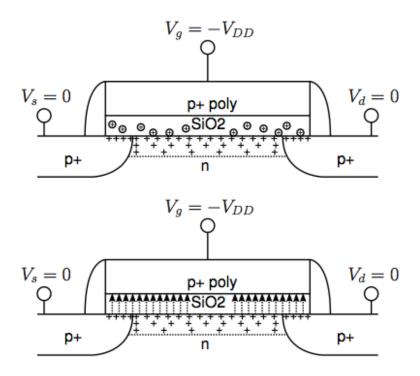

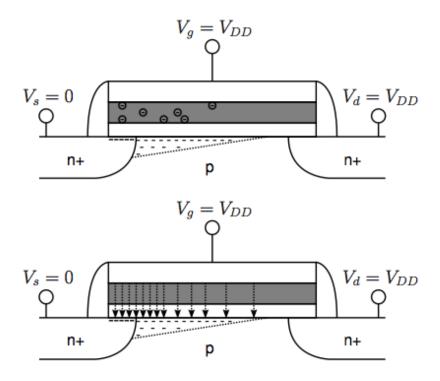

Figure 2.3 shows the inversion mode NBTI stress condition and the resulting oxide degradation for an exemplary pMOSFET - the transistor's deep triode region with zero voltage drop over the channel. Source, Drain and Substrate are connected to ground and Vg is set to a high negative value inducing an inversion layer in the n-well and an accumulation layer in the Source and Drain overlap regions. The electric field in the insulator on the inverted channel is given by eq. (2.5). Under high  $F_{el,ox}$ , oxide quality degrades by the trapping of charge. Insulator degradation also happens in the Source/Drain overlap regions, but with minor impact due to the distance to the controlled inversion channel. Fig. 2.4 shows the situation for a pMOS device in saturation region. Also in this operation mode NBTI degradation occurs, but due to the decreasing electric field from the Source to the Drain region with smaller total degradation [34].

Lots of literature on NBTI and its involved mechanisms for differing CMOS gate stacks is available. Due to strong sensitivity towards processing and included materials, lots of differing degradation numbers and effect explanations exist. The general accepted mech- anisms are the generation of interface states at the substrate oxide interface and the electric activation of oxide charges, that is due to the activation of pre-existing defects or generation of new defects in the insulator [37]. According to one theory, an interface state is created by the release of hydrogen saturating an open Si bond at the substrate oxide interface. The remaining dangling bond is an electrically active defect with an energy distribution throughout the Si bandgap. It can be occupied by an electron or hole, but for pMOS in inversion mode it is positively charged [38]. The electric field induces a diffusion of the remaining hydrogen through the insulator. As this interface state gen- eration process was believed to be the dominant NBTI contributor, the widely-used RD (Reaction Diffusion) model was developed for NBTI prediction [39]. More recently, oxidecharges were believed to be dominant to NBTI. These traps are neutral when discharged and are positively charged when occupied by holes. Former modeling explained positive oxide charge is due to trapping of H+ from the RD process, but recent findings revealed that hole

Figure 2.3: pMOS in triode operation - : NBTI stress generated defects and arising electric field under NBTI stress

traps and their precursors already exist in the oxide before stress is applied [40].

**Figure 2.4: pMOS in saturation operation:** - NBTI stress generated defects and arising electric field under NBTI stress

NBTI recovery was controversially discussed for long times, but its investigations revealed a deeper understanding of NBTI degradation mechanisms. As recovery immediately sets in when stress is removed, the time delay between stress and aging monitor measurement is very important. This undefined delay in published NBTI data is also one origin of the lack in NBTI understanding. In recent years a lot of effort was performed measuring degradation during stress to find the whole amount of contributing effects [41, 42, 43, 44]. Early understandings divided NBTI characteristic into two components, a recovering one and a permanent part. Controversial results assigned effect recovery to passivation of interface traps [45] or hole detrapping [42]. Also investigations for enhanced recovery under accumulation mode did not reveal a distinct recovery origin [46, 47]. Reisinger 's ultra-fast Vth measurement method to monitor recovery after

stress, revealed for small dimension devices a stepwise recovery curve indicating the discharge of single defects with differing contributions in step size, which can be related to the random position of channel dopants and insulator defects. In a large area device this single defect recovery is masked by the huge number of defects and the small impact of each defect recovery to the overall device Vth, leading to the classic log(t) NBTI recovery behavior, which is in-compatible with the RD model [48]. Defect relaxation behavior was related to the model of low frequency noise/flicker noise or its manifestation as RTN (Random Telegraph Noise) and extended to the BTI timing range with individual capture and emission times for each defect [49, 50, 48]. With the adapted RTN characterisation technique TDDS (Time Dependend Defect Spectrocopy) from Grasser, it was shown that general BTI isdue to a thermally activated capture and emission of holes and electrons in oxide traps - called SOT (Switching Oxide Traps) [40, 51]. Capture and emission time constants are vastly distributed from nanoseconds to months or even longer. Investigations revealed that metastable states of these defects contribute an additional noise portion and scaling to nanometer devices can lead to very large induced variations due to high defect step sizes of a very small number of defects per device.

Changing the insulator materials from SiO2 to SiON or high- $\kappa$  stacks also changes the NBTI degradation. For SiON devices nitrogen portions should be located rather to the Gate/insulator than to the substrate/insulator interface for improved NBTI degradation [38]. High-k based gate stacks also show similar NBTI degradations compared to SiO2 and SiON data [52]. Fernandez showed that NBTI is strongly DF (Duty Factor) dependent, but shows a flat AC degradation behavior up to the GHz range [53], which is in line with SOT model from Grasser. From recent findings, Kaczer proposes to migrate to SiGe buried channel pMOSFETs to guarantee limited NBTI/pMOS degradation in future CMOS technology nodes [37].

#### 2.3.2 PBTI in nMOSFETs

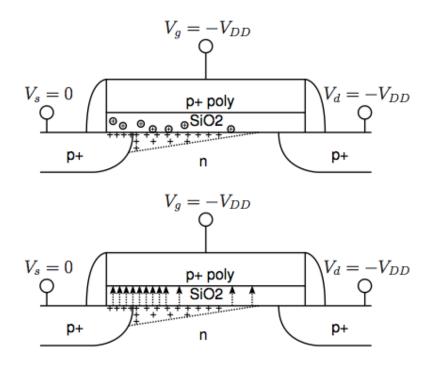

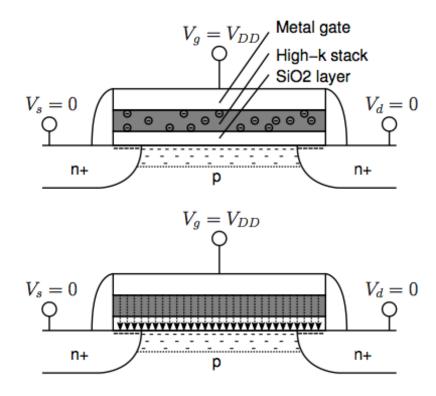

Corresponding to pMOSFET 's NBTI, a PBTI arise in nMOSFETs in inversion operation. PBTI degradation was negligibly small in SiO2 and SiON technologies, but arises with similar orders of magnitudes in high-k technologies. Fig. 2.5 shows the inversion

Figure 2.5: High- $\kappa$  nMOS in triode operation: - PBTI stress generated defects and arising electric field under PBTI stress

mode stress condition and its degraded insulator in deep triode region for an exemplary high- $\kappa$  nMOS. Contrary to classic pMOS/NBTI, oxide degradation occurs in the high- $\kappa$  portion of the Gate stack [36]. Due to intermediate SiO2 layers at the substrate insulator interface, nMOS/PBTI degradation is located in a certain distance from the inversion channel, thus mainly impacting threshold voltage  $V_{th}$  with almost no effect on channel mobility  $\mu_0$  [24]. Similarly to NBTI/pMOS degradation, also PBTI/nMOS shows a concentrated degradation near the Source in saturation operation resulting in a reduced total degradation

compared to the deep triode region operation (see fig. 3.6).

Figure 2.6: High- $\kappa$  nMOS in saturation operation: - PBTI stress generated defects and arising electric field under PBTI stress

As nMOS/PBTI in high- $\kappa$  processes compared to pMOS/NBTI is a very new type of degradation mechanism and due to the controversial discussion and explanation for the classic pMOS/NBTI, most BTI related investigations concentrate on a deeper under- standing of pMOS/NBTI. Nevertheless, there is a general consensus that nMOS/PBTI degradation is due to charge trapping in the high- $\kappa$  or related capping layers [25, 26, 27, 26]. High- $\kappa$  CMOS processing especially the gate stack with its specific arrangement of interface and capping layers - is a very confidential matter of semiconductor companies. Due to specific processing, differing nMOS/PBTI degradation results are available. Some investigations report a PBTI turnover phenomenon - an enhancement or weakening of the nMOS characteristic as a function on time depending on the bias and temperature stress condition. This observation indicates a multiple polarity defect trapping [38, 39]. Recent results for HfO2 based high-κ processes linked the major parts of PBTI degradation to electron trapping at oxygen vacancies [37]. Early investigations on nMOS/PBTI tried to model PBTI degradation with an adapted RD explanation from NBTI modeling, but neglected PBTI relaxation phenomena [58]. nMOS/PBTI relaxation is similar to pMOS/NBTI behavior, showing defect relaxation in a vast timescale from sub-microseconds to months. The promising SOT approach also fits well for PBTI degra- dation, its relaxation behavior and AC voltage stress degradation dependency [40, 25]. A possible option to reduce nMOS/PBTI degradation in HfO2 based processes is the inclusion of group III elements to passivate oxygen vacancies [30].

#### 2.3.3 BTI degradation trend in MOSFETs

Aging investigations in this work restrict to some application relevant EOL (End-of-Lifetime) use cases. Thereby operation conditions representing a typical use case or worst case scenario according to the intended application are assumed and circuit performance is evaluated in the corresponding end-of-lifetime state. For simplicity, only few use cases are used in this work, given in tab. 2.1. A good overview of commonly used ones for industrial applications are given in the JEDEC standard [29].

| EOL Use Case      | V             | T                | t   |

|-------------------|---------------|------------------|-----|

| General           | VDD           | 125 ° C - 85 ° C | 10y |

| MP (Mobile Phone) | VDD,WC $+5\%$ | 85 ° C           | 4y  |

| Combined          | VDD,WC $+5\%$ | 85 ° C           | 10y |

Table 2.1: Application related aging use cases

A reason for the accomplishment of this work can be determined from the following evaluation of aging effects 'evolution. Here, major degradation mechanisms and their behavior towards selected stress parameters are depicted and compared for the most recent CMOS technology nodes.

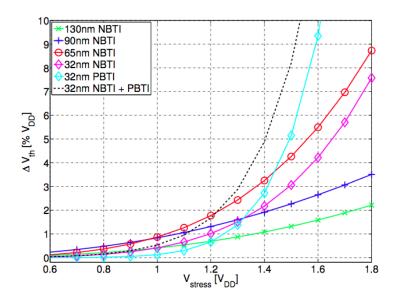

Figure 2.7: BTI aging behavior for selected MOSFET - technology nodes for mobile phone

Fig.2.7 depicts BTI aging behavior for the mobile phone end-of-lifetime use case and of the stress voltage. For comparison reasons, stress voltages and Vth degradations are given with respect to the corresponding supply voltage given in [2]. Especially for voltages much higher than nominal supply, the effect of the non-constant field scaling transistor design from 130nm CMOS down to 32nm appears in an increased voltage sensitivity: for each technology step, degradation values increase and the slopes of the curves are getting more steep. In the region of nominal supply, process optimization dominates and limits absolute drift values to certain margins. Nevertheless, the 32nm node bases on a high- $\kappa$ , metal gate process and besides the classic NBTI in pMOS, an additional PBTI in the nMOS device occurs. In fact, in the allowed supply region, single NBTI and PBTI degradations for the 32nm process are smaller than the 65nm NBTI. But from the circuit point of view, NBTI and PBTI drifts have to be summed up aspMOS and nMOS devices are typically stacked and both contribute to the proper circuit operation.

## Negative Bias Temperature Instability (NBTI) Model

# 3.1 Negative Bias Temperature Instability (NBTI) Effect

The aggressive scaling down of the MOSFETs results in an increase of the internal electric field both in the channel and the gate oxide. Moreover, in order to reduce the gate leakage and enhance the carrier mobility, high-K dielectrics, strain engineering and high mobility channel materials are applied. However, they are accompanied with inevitable high concentration of defects within the materials as well as at the interface [1.2-1.9]. It has been reported that, when the gate of p-MOSFET is negatively biased (Fig. 3.1), the NBTI effect is caused by positive charged oxide traps and interface states. This increases the delay time of the circuit critical path with increased operation time, which reduces the circuit speed and lifetime. In long term operation conditions, p-MOSFETs suffer from continuous stress and recovery cycle, and 20% delay increase during 5-10 years' operation is expected [1.10]. In order to avoid the impact of degradation to logic functions, the design tolerance may increase to 30% under the worst case. However, the increased design tolerance inevitably results in higher complexity and area of the circuit design. Therefore, analysing the NBTI sensitive partof the circuit and developing accurate predictive model is the key for approach cost

saving and optimisation design.

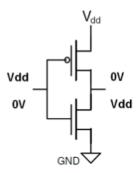

Figure 3.1: Bias conditions during circuit operation of a CMOS inverter - With input is 0V, output is high and the p-MOS device (top) is under uniform negative gate bias, which causes NBTI degradation.

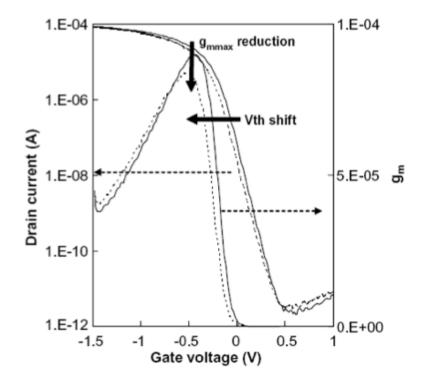

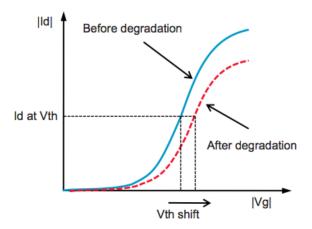

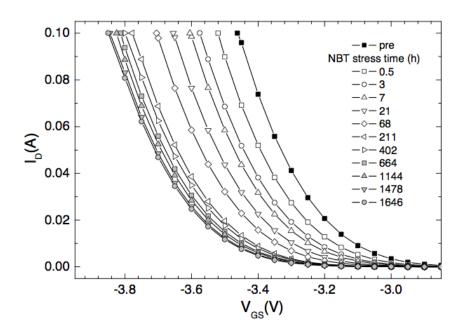

During circuit operations, carriers have great opportunity to be captured by such defects or generate new traps under high electric field. The charged traps are quite possible to degrade the threshold voltage, subthreshold slope, current, and transconductance. The degradation of current characteristics induced by the NBTI effect is shown in Fig. 3.2 [11]. After 10000s stress, the threshold voltage, On-state current and transconductance exhibit evidentdegradation. The above degradation deteriorates the lifetime and speed of the circuit and system [1.12], and even leads to logic failure.

#### 3.2 Overview of Existing NBTI Model

At present, numerous NBTI predictive models based on different concepts have been developed, including the hydrogen reaction-diffusion theory, hole-trapping theory and the energy transfer based theory. However, none of them are able to balance both the consistency of the theory as well as the practical application. An efficient NBTI model must be able to accurately predict the following features:

1) Long term degradation under DC stress conditions. 2) AC degradation with various frequencies and duty cycle. 3) The recovery characteristic in short term and long term regions. 4) Temperature dependence. In the following part, the

Figure 3.2: The degradation of Id-Vg and gm-Vg curves of p-MOSFET - before and after 10000s NBTI stress. The gate oxide thickness is 2nm,and temperature is  $125\,^\circ$  C. Solid and dashed lines indicate the characteristic before and after stress, respectively.

significant published NBTI predictive models, such as the reaction-diffusion (RD) model, the hole-trapping model, the interface-state generation model and energy transfer hole-trapping model, are simply reviewed from principle, verification, advantage and drawback.

#### 3.2.1 Classical Reaction-Diffusion Model

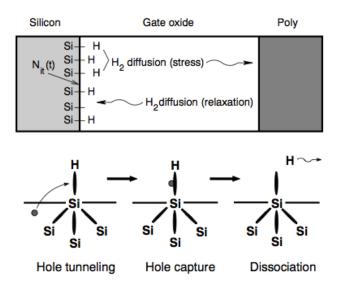

Principle of the reaction-diffusion (RD) model is simply described as follows: when a negative bias is applied to the gate of p-MOSFET, high density holes are injected into the gate oxide from the substrate. Holes with high energy possibly react with the Si-H bonds located at the Si/SiO2 interface, generating a Si dangling bonds and hydrogen atoms. When the Si dangling bonds are occupied by holes, such positively charged states will act as interface-states and results in the threshold voltage shift (delta $V_{th}$ ). At the same time, H atoms released from the Si-H bonds diffuse towards gate electrode [2.1]. The diffusion concentration determines the reaction rate of the Si-H bonds. The schematic view of Si-H bond reaction and hydrogen diffusion is shown in Fig. 3.3. The generation of interface state is determined by both Si-H bond reaction rate.

Figure 3.3: Schematic view of the RD model under stress and recovery conditions -

Eq. (3.1) describes the process of interface generation [2.1]. Here kF and kR are forward and reverse reaction rate respectively, N0 is the initial trap density at the interface, NH is the hydrogen concentration, and Nit is the interface-state density. Eq. (3.2) indicates the diffusion process, where DH is the hydrogen atom diffusion constant.

$$\frac{dN_{it}}{dt} = k_F(N_0 - N_{it}) - k_R N_H N_{it}$$

(3.1)

$$\frac{dN_H}{dt} = -D_H \frac{d^2 N_H}{dx^2} \tag{3.2}$$

During the initial period of the reaction process, the generated interface-state density is much lower than the total density of Si-H bonds. Therefore,  $dN_{it}0$ , and  $N_{0\dot{i}\dot{i}\dot{i}}N_{it}$ . Eq. (3.1) is simplified as

$$\frac{k_F N_0}{k_R N_{it}} = N_H \tag{3.3}$$

According to the diffusion equation (3.2), the hydrogen diffusion front  $x_D$  is solved as

$$x_D = \sqrt{(D_H t)} \tag{3.4}$$

As mentioned in Fig. 2.2. hydrogen atoms diffused into the gate oxide is supposed forming a triangle distribution. Thus the generated interface-state density is concentration is calculated by integrating the hydrogen within the gate oxide.

$$N_{it} = \frac{1}{2} N_{it0} x_D = \frac{1}{2} N_H x_D = \frac{1}{2} \frac{k_F N_0}{k_r N_{it}} \sqrt{(D_H t)}$$

(3.5)

The final expression of the interface-state density is

$$N_{it} = \left(\frac{1}{2} \frac{k_F N_0}{k_r}\right)^{(1/2)} (D_H t)^{(1/4)} \tag{3.6}$$

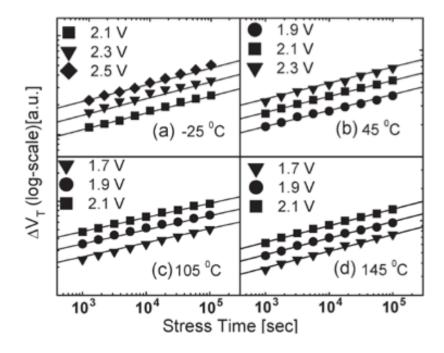

The traditional RD model was validated by comparing with the measurement result, as shown in Fig. 3.4. The Vth shifts following a power-law relationship with the stress time, and the time exponent is about 0.25 0.3, which is consistent with the model result [23, 24].

Figure 3.4: Typical time dependence of NBTI - The log-log Vth shift versus stress time shows 0.25 time exponent. Data is from (a) [23] and (b) [24]

Figure 3.5: Fitting delVth (measured by ultra-fast On-The-Fly technology -  $\,$

The time exponent of 1/4 is obtained based on numerous hypotheses, for example, slow reaction in the initial period, infinite gate oxide thickness and hydrogen atom diffusion process. However, soon after the proposed classical RD model, many measurement results obtained using advantage technologies showed that the time exponent featured 1/6 [25, 26], as shown in Fig. 3-5 [27].

Such phenomenon indicated that H atom diffusion is not the only element responsible for the NBTI degradation. In order to make a correct explanation to such phenomenon, A. Alam et al improved the classical RD model and assumed that part of the hydrogen atoms are possible to transfer into H2 molecule during the diffusion procedure [28].

In Eq. (3.1), the H atom concentration is supposed as NH. If the diffusion of H2 is considered, the transfer between H2 molecule and H atom is described as

$$N_H^{(0)} \propto \sqrt{(N_{H_2}^{(0)})}$$

(3.7)

The diffusion process of H2 molecule is

$$\frac{dN_{H_2}}{dt} = D_{H_2} \frac{d^2 N_{H_2}}{dy^2} \tag{3.8}$$

Similar to the classical RD model, the H2 molecule diffusing in the gate oxide still follows the triangle distribution. Note that one H2 molecule results in two Si dangling bonds, the interface state density (NIT) is written as

$$N_{IT} = 2\frac{1}{2}N_{H_2}^{(0)}\sqrt{(D_H t)} = N_{H_2}^{(0)}\sqrt{(D_H t)}$$

(3.9)

Substituting Eq. (3.3) into Eq. (3.7) and Eq. (3.9), the interface-state associated to the H2 diffusion is derived as

$$N_{IT} \propto \left[\frac{k_F N_0}{k_P}\right]^{\frac{2}{3}} (D_{H_2} t)^{\frac{1}{6}}$$

(3.10)

The relationship between Vth shift and stress time is described using powerlaw equation in the RD model. The time exponent is insensitive to neither electric field nor temperature, but only determined by the diffusion series. If the diffusion series is H atom, the time exponent is 1/4. Otherwise, the time exponent is 1/6

#### 3.2.2 Improved RD Model