# Towards Efficient 100 Gb/s Serial Rate Optical Interconnects: a Duobinary Way

X. Yin<sup>1</sup>, M. Verplaetse<sup>1</sup>, L. Breyne<sup>1</sup>, J. Van Kerrebrouck<sup>1</sup>, T. De Keulenaer<sup>1,2</sup>, A. Vyncke<sup>1,2</sup>, R. Pierco<sup>1,2</sup>, R. Vaernewyck<sup>1,2</sup>, S. Spiga<sup>3</sup>, M.-C. Amann<sup>3</sup>, J. Chen<sup>4</sup>, G. Van Steenberge<sup>5</sup>, G. Torfs<sup>1</sup>, J. Bauwelinck<sup>1</sup>

<sup>1</sup>IDLab Design, INTEC, Ghent University - imec, 9052 Ghent, Belgium

<sup>2</sup>BiFast, Spin-off of Ghent University-imec, IDLab, 9052 Ghent, Belgium

<sup>3</sup>TUM, Germany, <sup>4</sup>KTH, Sweden, <sup>5</sup>CMST, Ghent-University-imec, 9052 Ghent, Belgium

\*xin.yin @ugent.be

**Abstract:** Recent advances in integrated opto-electronic devices and frontend circuits have made it possible to efficiently transmit very high data rates over optical links for HPC/datacenter applications. This paper reviews our current progress towards serial 100-Gb/s optical interconnects, with emphasis on electrical duobinary (EDB) modulation.

#### 1. Introduction

Upgrading high-speed optical interconnects to serial line rates of 100 Gb/s is currently gaining a lot of interest for 400 Gb/s and future Terabit Ethernet applications. Experiments of different schemes, such as NRZ, PAM-4, DMT or EDB transmissions at 100 Gb/s serial rate were reported [1-7]. However, most [1-5] required considerable digital signal processing (DSP), which is not power efficient and often undertaken offline. Among those formats, EDB is considered to be an attractive approach. EDB is convenient to generate, is free from skewed transition issues, and shows a unique bandwidth-SNR compromise between NRZ and PAM-4 [8]. This paper gives an overview of our recent progresses on real-time EDB optical links using high-speed EDB transmitter (TX) and receiver (RX) ICs.

## 2. 100 Gb/s EDB Transmitter and Receiver Chipset

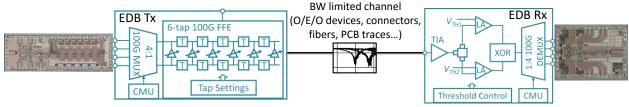

Figure 1. Block diagram and die photograph of SiGe BiCMOS EDB TX and RX chipset

Figure 1 shows the block diagram and photograph of our 100 Gb/s EDB TX and RX chipset. Both EDB TX and RX chips were designed in-house and fabricated in a 0.13um SiGe BiCMOS technology [9]. The TX IC consists of a 4-to-1 MUX and a 6-tap feedforward equalizer (FFE). The 4-to-1 MUX is capable of multiplexing 4 signal streams up to 25 Gb/s into a serial 100 Gb/s NRZ signal. Inside the TX the high-speed master-slave flip-flops are custom designed and clocked at half the serial data rate, i.e. 50 GHz for a 100 Gb/s serial rate. The 6-tap FFE is designed as a tapped delay line (~10 ps delay spacing) where each gain cell can be independently tuned with a resolution of 8 bit. Ideally a baseband cosine filter with ¼-rate 3dB bandwidth (BW) is needed for duobinary signaling [10]. As shown in Fig. 1, this cosine filter can be approximated by the BW-limited channel, along with an appropriately adapted TX FFE response. As such, the real-time FFE in the TX is employed to create an equivalent overall channel response that transforms the NRZ from the MUX output into 3-level duobinary at the RX input. The required equalization was chosen to be implemented in the TX. Without the need of complex DSP, the EDB RX IC demodulates the 3-level eyes with two separate threshold levels. The demodulated signal is then deserialized on-chip into 4x25 Gb/s NRZ outputs for real-time error detection. The TX IC occupies ~1.6mm x 4.6mm including IOs and consumes about 1 W, and the RX occupies ~1.9mm x 2.6mm including IOs and uses less than 1.2 W. A new design of the transceiver chips with lower power consumption and added functionality (e.g. CDR) is currently being tested.

#### 3. 100 Gb/s EDB Transmission with EAM

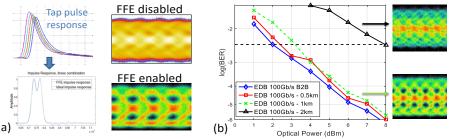

In [6] we presented, for the first time, a real-time 100 Gb/s EDB transmission over 2 km SSMF, employing a travelling-wave electro-absorption modulator (EAM) with an integrated DFB laser. The integrated DFB laser emitted at 1548.7nm in the experiment. The measured tap pulse responses are shown in Fig. 2(a). Those pulse responses can be used for tap coefficient optimization by fitting the FFE response to the ideal duobinary impulse response, taking the channel response into account. For fair comparison, the TX FFE is always enabled in the experiment and separately

optimized for each rate. As seen in Fig. 2(a), by enabling the 6-tap FFE in the EDB TX IC, we can shape the closed receiver optical eye into 3-level duobinary with two separate open eyes. At 100 Gb/s the resulting BER and eyediagrams for B2B, 500m, 1km, and 2km SSMFs are depicted in Fig. 2(b). For 500m applications, no noticeable penalty was observed. Over 2km SSMF, the 100Gbit/s EDB signal can still be received with a BER below 7% HD-FEC threshold. In a follow-up experiment, the TX and RX ICs were used with a lumped SiGe EAM in imec's 200 mm silicon photonics platform for a 100 Gb/s NRZ link [11]. Further measurements of 100 Gb/s EDB with such lumped SiGe EAM may be discussed during the presentation. Compared to the travelling-wave EAM, the lumped EAM removes the required 50-ohm termination and can further improve the power efficiency of the link.

**Figure 2**. (a) Tap coefficient optimization and captured eye-diagrams with FFE and without FFE (b) real-time BER curves for B2B, 500m, 1km and 2km SSMF at 100 Gb/s

## 4. 80 Gb/s Single-Mode VCSEL EDB Link

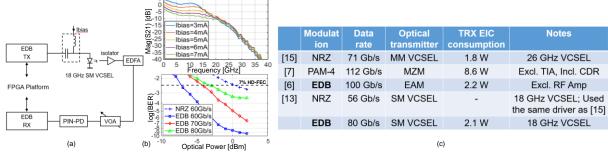

Another interesting optical transmitter for future HPC/datacenters is long-wavelength (LW) single-mode (SM) VCSEL. It offers potentially an energy-efficient and future-proof solution for >500 m applications, and operating at LW facilitates using wavelength division multiplexing to reduce fiber counts. So far, the reported highest data rate for real-time SM VCSEL links is ~56 Gb/s NRZ [12-13], which is still lower than the multimode (MM) counterpart (e.g. 71 Gb/s NRZ [14]). This is also confirmed by the measured small-signal bandwidth of such long-wavelength SM VCSELs, i.e., max. 22 GHz [12] versus 30 GHz for MM VCSELs [14]. To study the effectiveness of the proposed TX FFE and EDB modulation, we have evaluated our EDB transceiver chipset with an 18 GHz SM VCSEL (1544 nm). The test setup is shown in Fig. 3. The measured frequency response showed that the link BW is limited by the VCSEL and the real-time BER with PRBS7 at 80 Gb/s was below 7% HD-FEC threshold. This is the highest data rate demonstrated for a SM LW VCSEL without complex offline DSP. The comparison table in Fig. 3(c) summarizes recent real-time short-reach optical link experiments for different schemes: the low power consumption of the proposed EDB EICs makes it an attractive alternative as it enables a higher data rate compared to the typical NRZ format.

Figure 3. (a) Experimental setup of the VCSEL link (b) measured frequency response and BER (c) comparison of real-time short-reach optical links with custom front-end transceiver ICs

#### Acknowledgement

The authors would like to thank the support from UGent IOF/BOF, the FWO, and the European Commission for OI related projects such as FP7 ICT MIRAGE, PhoxTrot, H2020 ICT STREAMS, and Teraboard.

### 5. References

- [1] Katopodis et al. in OFC, Anaheim, CA, 2016, Tu2A3.

- [2] C. Caillaud et al., in ECOC, Valencia, 2015, PDP.

- [3] P. Dong et al., in OFC, Los Angeles, 2015, PDP Th5B.4

- [4] J. Lee et al., in OFC, 2014, PDP Th2.A.4.

- [5] W. Bo et al., "Single-Lane ...," in ECOC, 2016, pp. 1148-1150.

- [6] X. Yin et al., in ECOC, Dusseldorf, 2016, PDP Th.3.B.5.

- [7] J. Lee et al, in ECOC, ID:0604, Valencia, 2015.

- [8] X. Yin et al., in OECC/PS, Dusseldorf, 2016, invited ThE1-1.

- [9] M. Verplaetse et al., Journ. Of Lightw. Techn., 2017.

- [10] B. Moeneclaey et al., Journ. Of Lightw. Techn., 2017.

- [11] J. Verbist et al., submitted to OFC PDP, 2017.

- [12] S. Spiga et al., Journ. of Lightw. Techn., 2017.

- [13] D. M. Kuchta et al., Journ. of Lightw. Techn., 2016.

- [14] E. Haglund et al., Journ. of Lightw. Techn., 2016.

- [15] D.M. Kuchta et al., in CSICS, Austin, TX, 2016.