# CHARACTERIZATION OF 28 NM FDSOI MOS AND APPLICATION TO THE DESIGN OF A LOW-POWER 2.4 GHZ LNA

A Master's Thesis

Submitted to the Faculty of the

Escola Tècnica d'Enginyeria de Telecomunicació de

Barcelona

Universitat Politècnica de Catalunya

by

Jaume del Rio Jimenez

In partial fulfilment

of the requirements for the degree of

MASTER IN ELECTRONICS ENGINEERING

**Advisor: Xavier Aragonés Cervera**

Barcelona, May 2017

#### Title of the thesis:

# Characterization of 28 nm FDSOI MOS and application to the design of a low-power 2.4 GHz LNA

#### **Author:**

Jaume del Río Jiménez

#### Advisor:

Xavier Aragonés Cervera

#### **Abstract**

IoT is expected to connect billions of devices all over world in the next years, and in a near future, it is expected to use LR-WPAN in a wide variety of applications. Not all the devices will require of high performance but will require of low power hungry systems since most of them will be powered with a battery.

Conventional CMOS technologies cannot cover these needs even scaling it to very small regimes, which appear other problems. Hence, new technologies are emerging to cover the needs of this devices. One promising technology is the UTBB FDSOI, which achieves good performance with very good energy efficiency.

This project characterizes this technology to obtain a set of parameters of interest for analog/RF design. Finally, with the help of a low-power design methodology (gm/ld approach), a design of an ULP ULV LNA is performed to check the suitability of this technology for IoT.

### Keywords

IoT, UTBB FDSOI, LNA, ULP, ULV, gm/ld, IC

# **Acknowledgements**

I want to thank my supervisor, Xavier Aragonés, for all the help and given support during this thesis.

# **Revision history and approval record**

| Revision | Date       | Purpose           |

|----------|------------|-------------------|

| 0        | 19/05/2017 | Document creation |

| 1        | 22/05/2017 | Document revision |

|          |            |                   |

|          |            |                   |

| Written by: |                       | Reviewed and approved by: |                         |

|-------------|-----------------------|---------------------------|-------------------------|

| Date        | 23/05/2017            | Date                      | 23/05/2017              |

| Name        | Jaume del Rio Jimenez | Name                      | Xavier Aragonés Cervera |

| Position    | Project Author        | Position                  | Project Supervisor      |

### **Table of contents**

| Αt  | stract   |        |                                                                        | 1    |

|-----|----------|--------|------------------------------------------------------------------------|------|

| Ac  | knowl    | edge   | ments                                                                  | 2    |

| Re  | evision  | histo  | ory and approval record                                                | 3    |

| Ta  | able of  | cont   | ents                                                                   | 4    |

| Lis | st of Fi | gure   | s                                                                      | 6    |

| Lis | st of Ta | ables  |                                                                        | 10   |

| 1.  | Intro    | oduct  | ion and objectives                                                     | 11   |

|     | 1.1.     | Moti   | vation                                                                 | 11   |

|     | 1.2.     | loT -  | - CMOS nanometer technology as enabler                                 | 12   |

|     | 1.3.     | Des    | ign challenges for CMOS RF                                             | 15   |

|     | 1.4.     | MOS    | S scaling limitations and trends                                       | 16   |

|     | 1.5.     | FDS    | OI as a technology candidate for IOT                                   | 17   |

|     | 1.6.     | Obje   | ectives                                                                | 17   |

|     | 1.7.     | The    | sis organization                                                       | 18   |

| 2.  | Stat     | e of t | the art on low-power low-voltage LNA design and gm/ld methodology      | 19   |

|     | 2.1.     | Cas    | e reviews                                                              | 19   |

|     | 2.2.     | Gm/    | Id approach for low-power analog circuit optimization                  | 26   |

|     | 2.2.     | 1.     | Introduction to the gm/ld approach                                     | 26   |

|     | 2.2.     | 2.     | Determining the specific current                                       | 28   |

|     | 2.2.     | 3.     | Gm/ld design methodology                                               | 30   |

| 3.  | UTE      | BB FE  | DSOI CHARACTERIZATION                                                  | 32   |

|     | 3.1.     | UTB    | BB FDSOI 28 nm technology                                              | 32   |

|     | 3.1.     | 1.     | Body Bias                                                              | 33   |

|     | 3.2.     | UTB    | BB FDSOI 28 nm technology transistors characteristics                  | 36   |

|     | 3.2.     | 1.     | Id- V <sub>gate</sub> characteristics <b>¡Error! Marcador no defin</b> | ido. |

|     | 3.2.     | 2.     | Width dependence                                                       | 38   |

|     | 3.2.     | 3.     | Fingers dependence                                                     | 39   |

|     | 3.3.     | LVT    | transistor characterization as function of its inversion degree        | 40   |

|     | 3.3.     | 1.     | Transconductance efficiency                                            | 41   |

|     | 3.3.     | 2.     | Transconductance                                                       | 42   |

|     | 3.3.     | 3.     | Output conductance                                                     | 43   |

|     | 3.3.     | 4.     | Effective gate-source voltage                                          | 43   |

|     | 3.3.     | 5.     | Drain-source saturation voltage                                        | 44   |

| 3.3.6.        | Threshold voltage                                | 45 |

|---------------|--------------------------------------------------|----|

| 3.3.7.        | Intrinsic voltage gain                           | 45 |

| 3.3.8.        | Gate capacitances                                | 46 |

| 3.3.9.        | Transition frequency                             | 47 |

| 3.3.10.       | Low power RF FoM                                 | 47 |

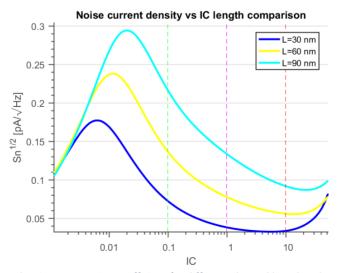

| 3.3.11.       | Noise                                            | 48 |

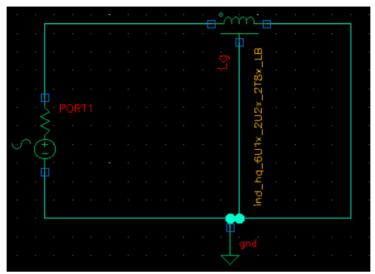

| 3.4. Pas      | ssive devices performance – Inductors at 2.4 GHz | 49 |

| 3.5. Bad      | ck gate Bias effect                              | 50 |

| 4. LNA des    | sign                                             | 55 |

| 4.1. Spe      | ecifications                                     | 55 |

| 4.1.1.        | NF specification                                 | 56 |

| 4.1.2.        | Gain specification                               | 57 |

| 4.1.3.        | IIP3 specification                               | 58 |

| 4.1.4.        | Receiver specifications                          | 59 |

| 4.1.5.        | LNA specifications                               | 59 |

| 4.2. LN/      | A design methodology                             | 60 |

| 4.2.1.        | LNA design for 1 V                               | 61 |

| 4.2.2.        | LNA design for sub-1 V                           | 69 |

| 5. Conclus    | sions and future works                           | 76 |

| 5.1. Cor      | nclusions                                        | 76 |

| 5.2. Fut      | ture works                                       | 77 |

| Bibliography  | /                                                | 78 |

| Appendix 1 .  |                                                  | 87 |

| Appendix 2 .  |                                                  | 88 |

| List of Terms | s and Abbreviations                              | 90 |

|               |                                                  |    |

# **List of Figures**

| Figure 1 - Estimated number (in billions) of smart connected things in use worldwide, by category [2]11                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 - Overview example of an IoT environment [9]13                                                                                                                                                                                                          |

| Figure 3 - IoT applications: power needs [11]14                                                                                                                                                                                                                  |

| Figure 4 - RF Disciplines and Design hexagon [23]16                                                                                                                                                                                                              |

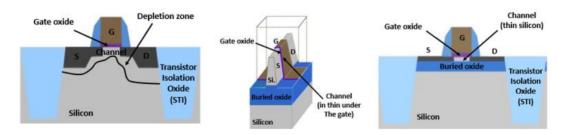

| Figure 5 - Cross section of conventional bulk MOS transistor (left), FinFET on SOI (center) and planar fully-depleted (FDSOI) transistor (right) [30]16                                                                                                          |

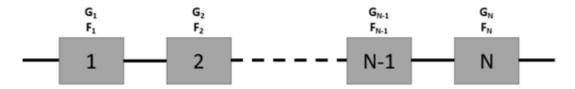

| Figure 6 - Typical chain of cascaded components19                                                                                                                                                                                                                |

| Figure 7 - Important features in LNA design20                                                                                                                                                                                                                    |

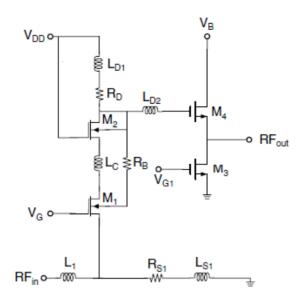

| Figure 8 - Schematic of a low power LNA from [54]21                                                                                                                                                                                                              |

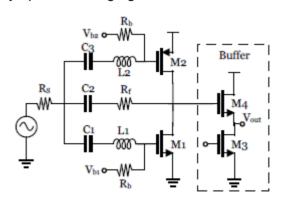

| Figure 9 - Schematic of an ultra-low power, ultra-low voltage LNA with buffer for measurement purposes from [57]21                                                                                                                                               |

| Figure 10 - Schematic of the proposed ULV and ULP LNA along with a buffer stage for measurement purposes from [61]                                                                                                                                               |

| Figure 11 - Simplified schematic of a ULP LNA along with a buffer stage for measurement purposes from [63]24                                                                                                                                                     |

| Figure 12 - Schematic of the proposed ultra-low power LNA with inductive feedback and C <sub>GD</sub> neutralization from [64]25                                                                                                                                 |

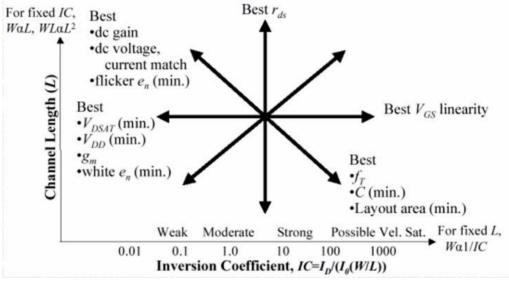

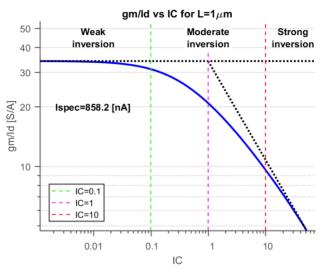

| Figure 13 - Transconductance efficiency vs. inversion coefficient (IC)28                                                                                                                                                                                         |

| Figure 14 - Technology Current (I <sub>0</sub> ) Determination Flowchart [78]29                                                                                                                                                                                  |

| Figure 15 - MOSFET operating plane [8]30                                                                                                                                                                                                                         |

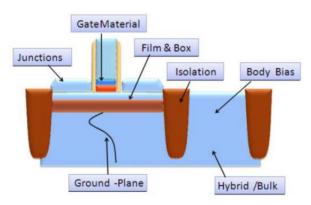

| Figure 16 - 28 nm UTBB device structure [84]32                                                                                                                                                                                                                   |

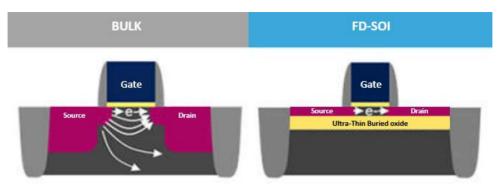

| Figure 17 - Architectural difference between bulk and FDSOI transistor [40]33                                                                                                                                                                                    |

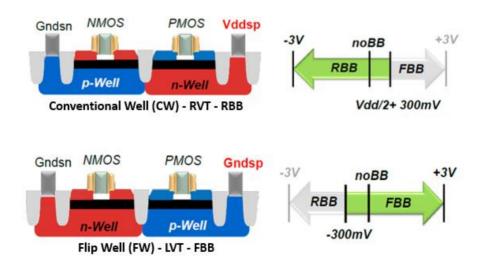

| Figure 18 - Cross-sectional view of UTBB FDSOI NMOS and PMOS devices with different wells [96]                                                                                                                                                                   |

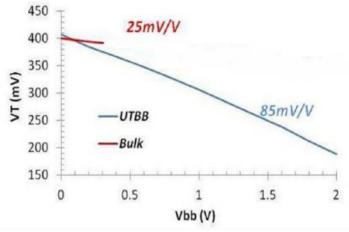

| Figure 19 - Body bias efficiency of 28 nm UTBB FDSOI vs. Bulk [96]35                                                                                                                                                                                             |

| Figure 20 - Speed leakage benefits of FDSOI over Bulk technology [96]35                                                                                                                                                                                          |

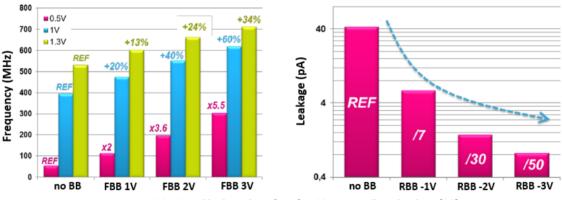

| Figure 21 - Test circuit for LVT NMOS characteristics characterization36                                                                                                                                                                                         |

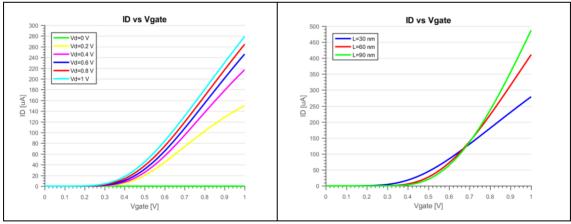

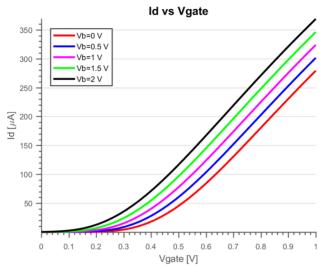

| Figure 22 - Id vs Vgate characteristic of a LVT NMOS with W/L=1036                                                                                                                                                                                               |

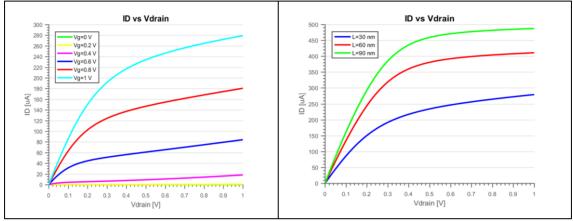

| Figure 23 - Id vs Vdrain characteristic of a LVT NMOS with W/L=1037                                                                                                                                                                                              |

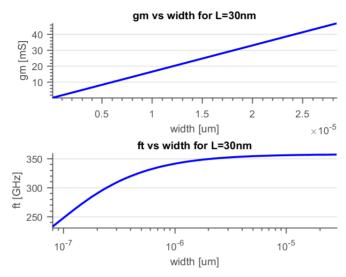

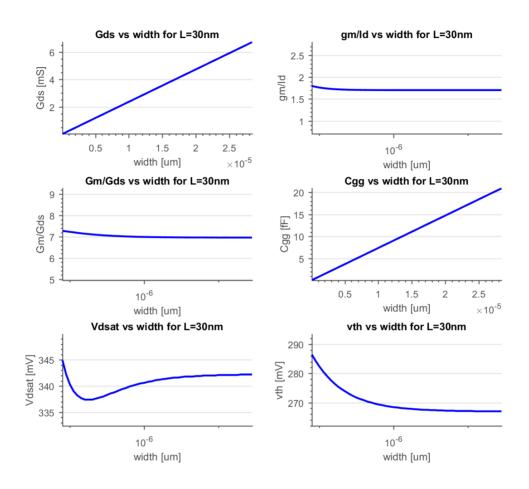

| Figure 24 - NMOS LVT gm and $f_T$ vs. Total width for a 30 nm gate length transistor. The measurements correspond to a RF DUT having an aspect ratio of 10, gate length of 30 nm, Vgate = 1 V and Vdrain = 1 V39                                                 |

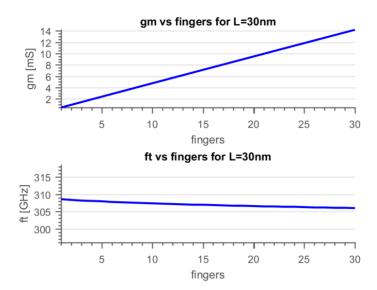

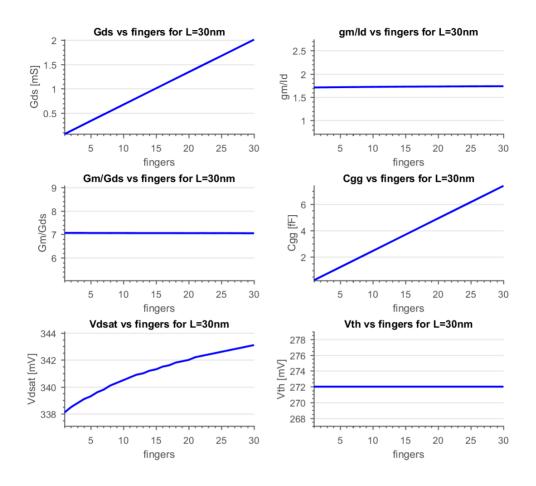

| Figure 25 - NMOS LVT gm and $f_T$ vs. Number of fingers for a 30 nm gate length transistor and 300 nm of finger width. The measurements correspond to a RF DUT having an aspect ratio of 10 and gate lengths of 30 nm and finger width of 300 nm, at Vdd = 1 V40 |

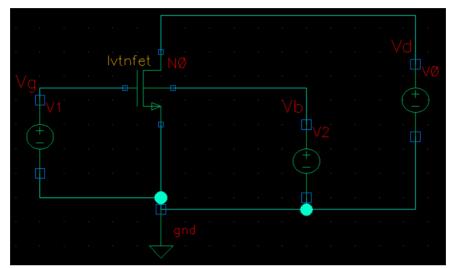

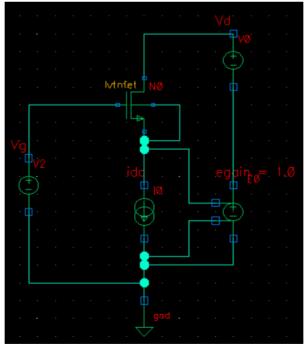

| Figure 26 - Lest circuit for IC characterization of the LVT NMOSFET40                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 27 - Extraction of the specific current Ispec, which corresponds to the value of Id at which the SI asymptote is equal to gm/Id in WI. The measurement corresponds to an RF DUT having W=1 $\mu$ m and L= 1 $\mu$ m, at Vdd = 1 V41                                                                                                                                                                                                               |

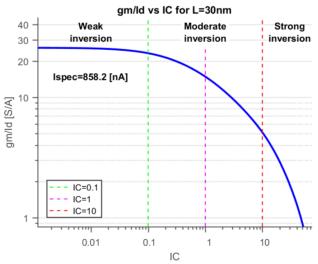

| Figure 28 - Transconductance efficiency vs. inversion coefficient for a short-channel device The measurement corresponds to an RF DUT having W=300 nm and L= 30 nm, at Vdd = 1 V41                                                                                                                                                                                                                                                                       |

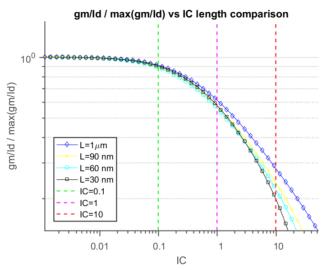

| Figure 29 - Normalized transconductance efficiency vs. inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (1 $\mu$ m, 90 nm, 60 nm and 30 nm), at V <sub>dd</sub> = 1 V. We can observe how the transconductance efficiency for a short-channel device degrades much faster in SI compared to a long-channel device, due to the velocity saturation effect42 |

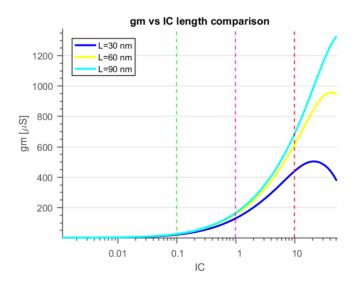

| Figure 30 - Transconductance vs. inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at $V_{dd} = 1$ V. We can observe how gm increases along with the channel length and IC42                                                                                                                                                      |

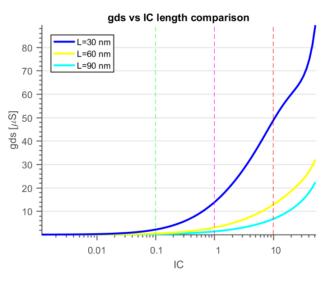

| Figure 31 - Output conductance vs. inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V                                                                                                                                                                                                                                 |

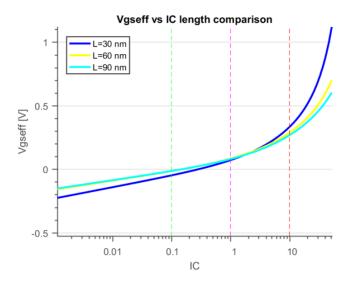

| Figure 32 - Effective gate-source voltage vs. inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V44                                                                                                                                                                                                                    |

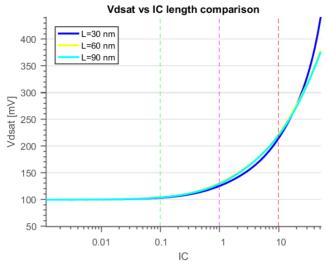

| Figure 33 - Drain-source saturation voltage vs. inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V45                                                                                                                                                                                                                  |

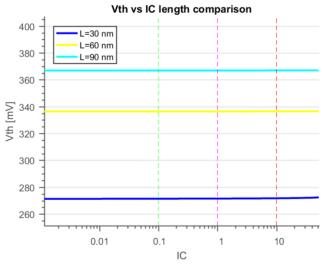

| Figure 34 - Threshold voltage vs. inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V                                                                                                                                                                                                                                  |

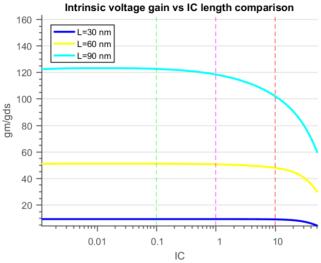

| Figure 35 - Intrinsic voltage gain vs. Inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V                                                                                                                                                                                                                             |

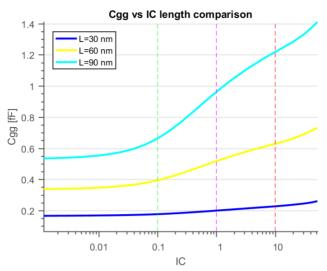

| Figure 36 - Gate capacitances vs. Inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V47                                                                                                                                                                                                                                |

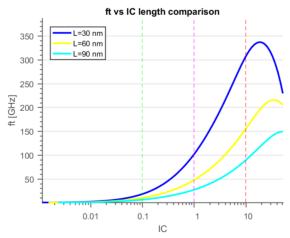

| Figure 37 - Transition frequency vs. Inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V47                                                                                                                                                                                                                             |

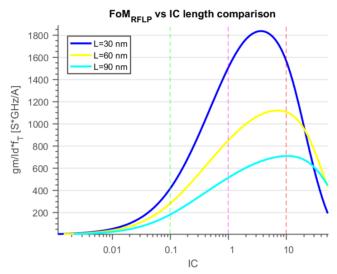

| Figure 38 - FoMRFLP vs. Inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V48                                                                                                                                                                                                                                          |

| Figure 39 - Noise current density vs. Inversion coefficient for different channel lengths. The measurements correspond to RF DUTs having an aspect ratio of 10 and different lengths (90 nm, 60 nm and 30 nm), at Vdd = 1 V48                                                                                                                                                                                                                            |

| Figure 40 - Test circuit for inductance characteristics                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 41 - Quality factor vs. Inductor values for various number of turns of the inductor. The measurements have been performed with the same model of the inductor but for the different number of turns (n) that the design kit allows, from 2 to 6 turns |

| Figure 42 - Transfer characteristics of LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at Vds=1V                                                                            |

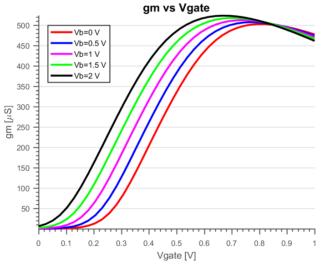

| Figure 43 - transconductance of LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at $Vds=1V51$                                                                                |

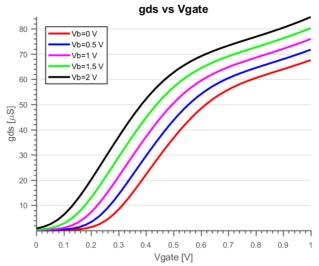

| Figure 44 - Output conductance of a LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at Vds=1V.                                                                               |

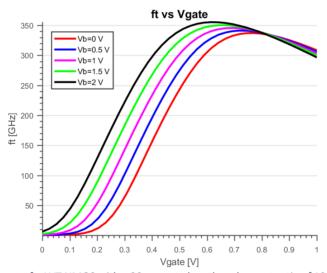

| Figure 45 - Transit frequency of a LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at Vds=1V52                                                                               |

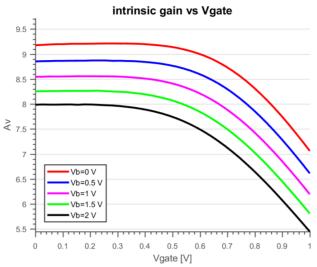

| Figure 46 - Intrinsic gain of a LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at Vds=1V53                                                                                  |

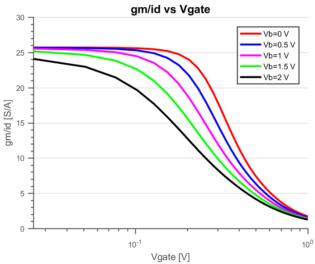

| Figure 47 - Transconductance efficiency of a LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at Vds=1V                                                                       |

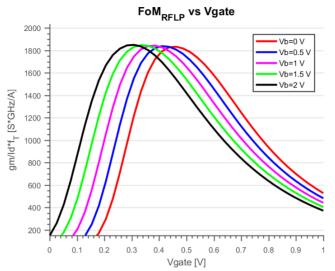

| Figure 48 - Low power RF FoM of a LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at $V_{ds}$ =1V.                                                                           |

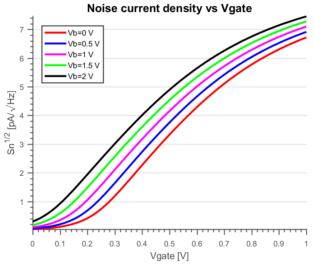

| Figure 49 - Noise current density at 2.4 GHz of a LVT NMOS with a 30 nm gate length and aspect ratio of 10 as a function of gate-source voltage and back-gate voltage (0 V to 2V) at Vds =1V                                                                 |

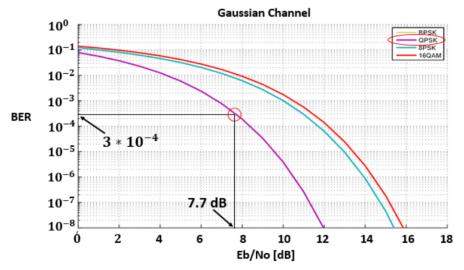

| Figure 50 - BER over AWGN channel for BPSK, QPSK, 8PSK and 16QAM [110]57                                                                                                                                                                                     |

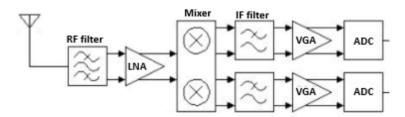

| Figure 51 - low-IF topology [112]59                                                                                                                                                                                                                          |

| Figure 52 - Level plan for the low-IF receiver60                                                                                                                                                                                                             |

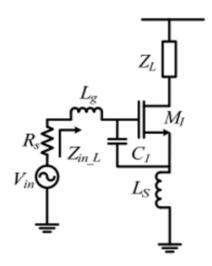

| Figure 53 - Inductive source-degeneration CSLNA [115]61                                                                                                                                                                                                      |

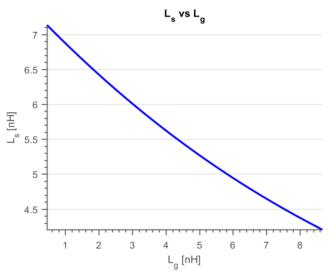

| Figure 54 - Source inductor vs. gate inductor64                                                                                                                                                                                                              |

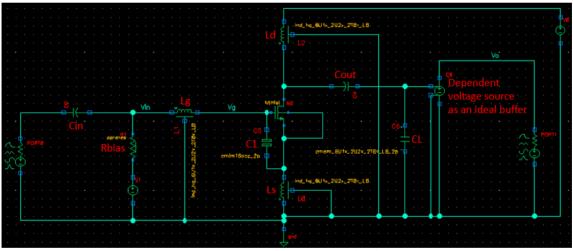

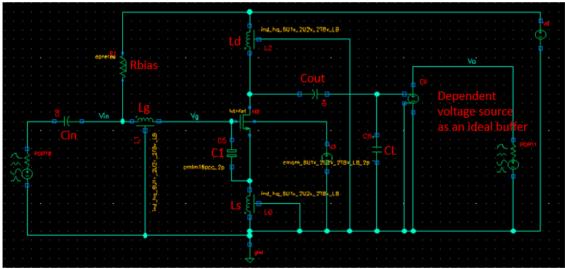

| Figure 55 - LNA schematic supplied with 1 V65                                                                                                                                                                                                                |

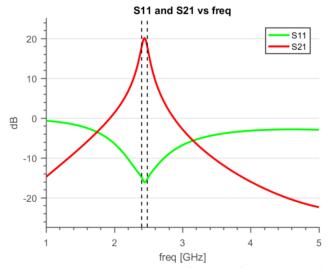

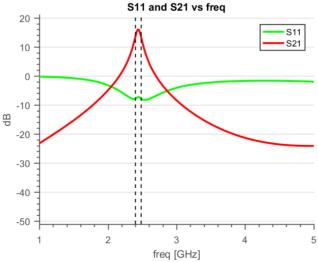

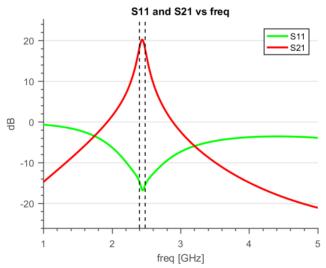

| Figure $56-S_{21}$ and $S_{11}$ parameters over the frequency for the LNA supplied with 1 V $66$                                                                                                                                                             |

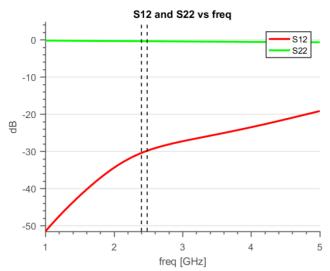

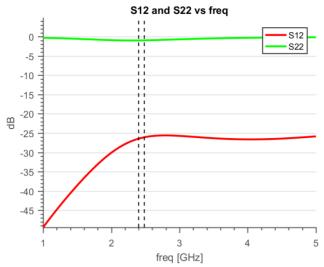

| Figure 57 - $S_{\rm 12}$ and $S_{\rm 22}$ parameters over the frequency for the LNA supplied with 1 V 67                                                                                                                                                     |

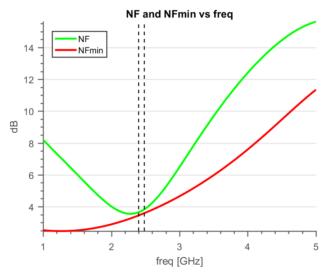

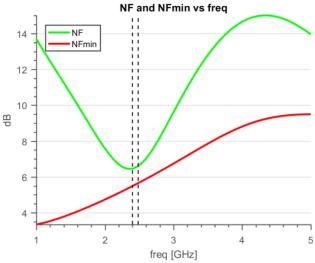

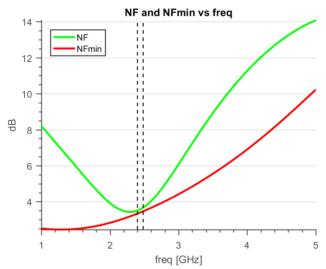

| Figure 58 - NF and minimum NF over the frequency for the LNA supplied with 1 V67                                                                                                                                                                             |

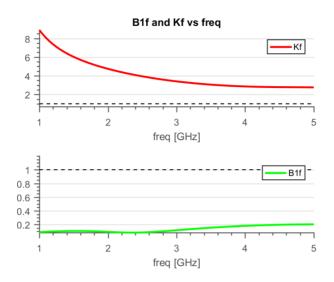

| Figure 59 - Stability parameters over the frequency for the LNA supplied with 1 V68                                                                                                                                                                          |

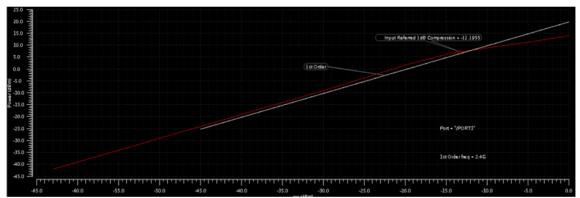

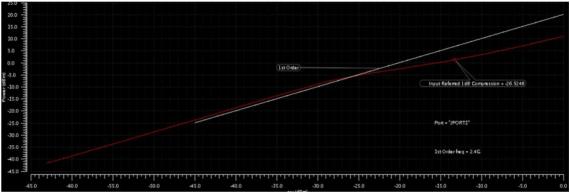

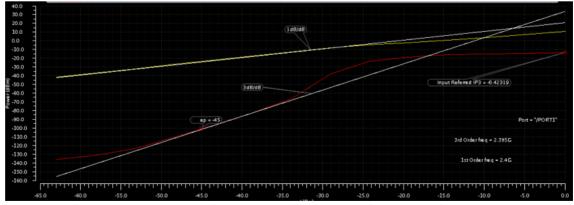

| Figure 60 - P1dB of the fundamental tone (2.4 GHz) for the LNA supplied with 1 V68                                                                                                                                                                           |

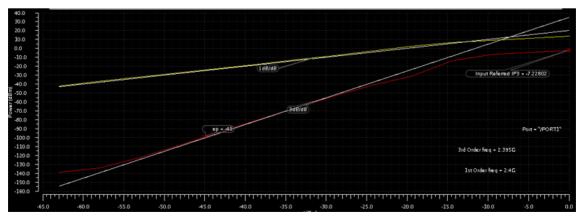

| Figure 61 – IIP3 for the test with one tone at fo=2.4GHz and a second tone at f1= 2.405 GHz for the LNA supplied with 1 V                                                                                                                                    |

| Figure 62 - S21 and S11 parameters over the frequency for the LNA supplied with 250 mV without FBB69                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 63 - NF and minimum NF over the frequency for the LNA supplied with 250 mV without FBB70                                                                                                                                                                       |

| Figure 64 - LNA schematic supplied with 250 mV70                                                                                                                                                                                                                      |

| Figure 65 - S <sub>21</sub> and S <sub>11</sub> parameters over the frequency for the LNA supplied with 250 mV with FBB71                                                                                                                                             |

| Figure 66 - $S_{12}$ and $S_{22}$ parameters over the frequency for the LNA supplied with 250 mV with FBB72                                                                                                                                                           |

| Figure 67 - NF and minimum NF over the frequency for the LNA supplied with 250 mV with FBB72                                                                                                                                                                          |

| Figure 68 - Stability parameters over the frequency for the LNA supplied with 250 mV73                                                                                                                                                                                |

| Figure 69 - P1dB of the fundamental tone (2.4 GHz) for the LNA supplied with 250 mV.73                                                                                                                                                                                |

| Figure 70 - IIP3 for the test with one tone at fo=2.4GHz and a second tone at f1= 2.405 GHz for the LNA supplied with 250 mV73                                                                                                                                        |

| Figure 71 - NMOS LVT parameters vs. Total width for a 30 nm gate length transistor. The measurements correspond to a RF DUT having an aspect ratio of 10, gate lengths of 30 nm, Vgate = 1 V and Vdd = 1 V88                                                          |

| Figure 72 - NMOS LVT parameters vs. number of fingers for a 30 nm gate length transistor and 300 nm of finger width. The measurements correspond to a RF DUT having an aspect ratio of 10, gate lengths of 30 nm, finger width of 300 nm, Vgate = 1 V and Vdd = 1 V89 |

# **List of Tables**

| Table 1 - Comparison of different harvesting methods [17]                                                                  | .14         |

|----------------------------------------------------------------------------------------------------------------------------|-------------|

| Table 2 - Main characteristics of LNA from [54]                                                                            | .21         |

| Table 3 - Main characteristics of LNA from [57]                                                                            | .22         |

| Table 4 - Main characteristics of LNA from [61]                                                                            | .24         |

| Table 5 - Main characteristics of LNA from [63]                                                                            | .25         |

| Table 6 - Main characteristics of LNA from [64]                                                                            | .26         |

| Table 7 - MOSFET characteristics values in saturation region for the 4 types of transist                                   | tors<br>.38 |

| Table 8 - IEEE 802.15.4 RF bands [109]                                                                                     | .55         |

| Table 9 - IEEE 802.15.4 RF specifications [109]                                                                            | .56         |

| Table 10 - Receiver specifications                                                                                         | .59         |

| Table 11 – LNA design specifications                                                                                       | .60         |

| Table 12 - Main parameters of the transistor when $f_{\text{T}}$ is 30 GHz                                                 | .62         |

| Table 13 - LNA design parameters when supplied with 1 V                                                                    | .66         |

| Table 14 – Detailed values of the parameters at the frequency points of the 2400 MHz bate for the LNA supplied with 1 V    |             |

| Table 15 - LNA design parameters when supplied with 250 mV                                                                 | .71         |

| Table 16 - Detailed values of the parameters at the frequency points of the 2400 MHz bate for the LNA supplied with 250 mV |             |

| Table 17 - Performance summary and comparison with state-of-the-art LNAs                                                   | .75         |

#### 1. <u>Introduction and objectives</u>

An introduction on the IoT paradigm and a definition of the main objectives of the thesis as well as the thesis organization are commented in this chapter.

#### 1.1. Motivation

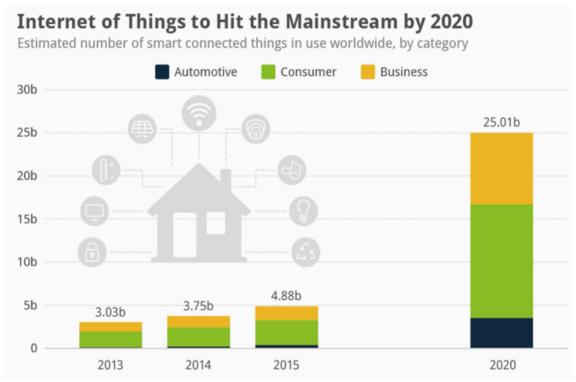

The Internet of Things (IoT) has emerged in the recent years as the new paradigm that will revolutionize a wide range of sectors. Although some IoT applications are already present today, forecasts predict a fast grow in the near future, thus increasing exponentially the number of connected devices in the next years. According to [1, 2], companies are going to make an economic effort spending over \$5 trillion on these technologies in the next five years, and an increase from the 6.6 million devices existing in 2016 to almost 22 billion in 2021. The estimation of the worldwide growth of the usage of these devices by category is shown in Figure 1.

Figure 1 - Estimated number (in billions) of smart connected things in use worldwide, by category [2]

For this trend to be accomplished, a fundamental need is to make use of new technologies that enable connectivity between such a huge amounts of devices while keeping a low cost, small volume and reduced power consumption. Although bulk Complementary Metal-Oxide-Semiconductor (CMOS) technology is the predominant one for integrated circuits (IC) due to its high integration capability and affordable among other properties, a transition to other "unconventional" MOS-based technologies is being produced these years. The evolution towards down-scaled sizes of transistors gates has reached its limits with the conventional bulk CMOS, and a promising technology for overcoming its drawbacks is the Ultra-Thin Body and Buried-oxide Fully Depleted Silicon-On-Insulator (UTBB FDSOI) technology, developed by STMicroelectronics.

Small nodes suffer from small-geometry effects and the UTBB FDSOI technology minimizes many of them and comes with improvements providing a boost to speed

performance and power-efficiency compared with the regular bulk CMOS technology. Its flexibility to adapt to different operation modes such as high performance, low power or low leakage makes it the perfect replacement for current technologies. In addition, it offers many advantages for the low power Radio Frequency (RF) design [3, 4] becoming a well suited technology for IoT applications.

#### 1.2. <u>IoT – CMOS nanometer technology as enabler</u>

The term "IoT" refers to the idea where the capability of computing and the access to network connectivity is extended to objects which are not normally considered computers but can have the ability to communicate between each other without or with minimal human interaction. A "thing", on IoT context, could be literally anything such as any type of sensor implanted on a human body or a car, or any human created object with the ability to generate, exchange and consume data over a network without human intervention [5].

IoT technologies allow each one of these devices to work as an "intelligent node" in the network, acting smartly and making collaborative decisions in order to benefit certain applications. These nodes collect information and also can process/adapt low level signals received by them, so they can retransmit these signals creating a communication network between nodes. The nodes should establish a secured communication link with a centralized "cloud" in order to protect, process and store the data and then be able to offer this data to users/applications who require it.

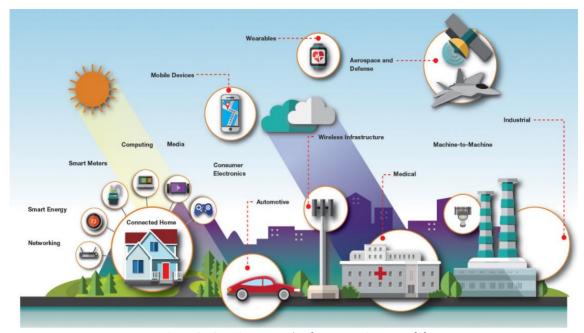

Nowadays, some market applications based on the IoT concept can be found in [6], but in a quite near future, it is expected that Low Rate Wireless Personal Area Networks (LR-WPAN) will be used in a wide different embedded applications, including smart home systems automations, industrial sensing and control, environmental monitoring and sensing, which will connect thousands of millions of devices and services anytime and anywhere. A small picture of an overview example of an IoT environment can be found in Figure 2.

Within the wide variety of devices inside the IoT concept not all of them need complex operating systems compared with smartphones or computers. Most of them are only deployed to one specific purpose such as physical magnitude sensing in a remote area, which turns out in basic needs of coverage or minimum power consumption. Based on this principle, IoT applications can be divided into two main categories, Critical and Massive IoT deployments [7].

Critical IoT deployments require more complex systems with different properties depending on its usage, such as high reliability, low latency, low delay or a high date rate. On the other hand, Massive IoT deployments, referred as massive since billions of theses sensors will be deployed globally, typically don't need high complexity with less power-hungry systems extending the battery life, specifications of data rate or latency much more relaxed and being very cost effective devices. New machine communication standards for massive Low Power Wide Area (LPWA) devices were released recently, allowing for example the launch of the ICT industry's first complete cellular LPWA offering of Ericsson in 2016 in collaboration with AT&T [8].

Figure 2 - Overview example of an IoT environment [9]

There's a coexistence of a multitude of wireless standards because of the different requirements of the environment or the big variety of use cases. On one side, the sensors networks work over relatively short distances (i.e. tens of meters) with low data rates and with a low power consumption protocols (i.e. ZigBee, Bluetooth, RFID...), which has driven a significant interest in investigation of low power wireless technologies. On the contrary, the connection between these networks and other systems has the need to cover long distances with high throughput which normally means higher consumptions and using other types of standards (i.e. GPRS, LTE, WiMAX...) with other requirements. The choice of the correct standard among the big variety available on the market is a challenging task since many things have to be taken into account (application, software used, type of network, security...).

Nowadays, devices like IoT nodes, mobiles, wearables... require of certain capabilities at limited power. The reduction of voltages, associated with each new generation of advanced CMOS to move towards ultra-low power and ultra-low voltage requirements of some systems, has degraded the performance of many analog/RF circuits in a way of lower noise margins, lower linearity and reduced output power among others. As deeply scaled CMOS technologies have become available, circuit design has required more innovative approaches to make the most of their scaling benefits in power and performance while keeping the reduction in price of the product.

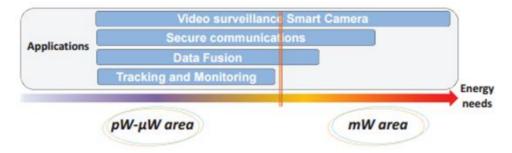

The need of low power energy efficient technologies, which is a key requirement in the market, is because many of IoT devices must survive on a single battery and they typically require long lifetimes. To extend the battery life without decreasing the receiver's performance, the reduction of the current consumption in active or idle state of the device is challenging. Figure 3 shows an example of the power levels needed by autonomous Wireless Sensor Node (WSN), which typically range from the pW to mW area depending on the type of the application, e.g. a simple tracking and monitoring application will require less energy than a full system of video surveillance smart cameras. Some more information about maximum average power consumption as function of battery size can be found in [10].

Figure 3 - IoT applications: power needs [11]

Besides the batteries, alternative sources of energy must be considered to avoid problems with powering the device and minimize the device maintenance. A key solution to allow the spread of these technologies is acquiring the energy from the environment close to the sensor, instead of a battery with finite charge capacity. This is known as energy harvesting, the process which captures this energy, and converts it into electrical current, being able to accumulate the charge in order to use it when needed. This enables self-powered IoT devices using this energy on demand, removing their dependence on batteries. Some examples and extended information about energy harvesting systems can be found in [12 - 16]. These energy harvesting systems will not generate either high power or high voltages, and given the scenario, the interest of evolution towards very low voltage and very low power consumption devices makes great sense. Table 1 lists various energy harvesting methods and their power generation capabilities.

| Energy source             | Power density                 | Advantages                                            | Disadvantages                                        |

|---------------------------|-------------------------------|-------------------------------------------------------|------------------------------------------------------|

| Solar                     | 15 <u>mW</u> /cm <sup>3</sup> | Sufficient energy in the daytime, high output voltage | Disappear at night                                   |

| Vibration (piezoelectric) | 200 μW/cm <sup>3</sup>        | Without voltage source                                | fragile materials                                    |

| Thermoelectric            | 40 μW/cm <sup>2</sup>         | Long life, reliable with low maintenance              | Low energy conversion<br>efficiency                  |

| Acoustic noise            | 960 <u>nW</u> /cm³            | High energy conversion efficiency                     | Rare environments with high<br>acoustic noise levels |

| Airflow                   | 1 mW/cm²                      | Sufficient in certain place and time                  | Big size                                             |

| Radio<br>frequency        | 1 μW/cm²                      | Sufficient in urban areas                             | Few in suburbs                                       |

Table 1 - Comparison of different harvesting methods [17]

Energy harvesting raises more challenges to the power supply of the circuit. In fact, the autonomous wireless sensor nodes that get their energy from the environment (solar, thermic, vibration...) will probably suffer from changing energetic environments. This fact implies that the energy level available for the receiver will change along the device life, what entails that the energy supply system will require any type of adaptive scheme. These systems will need to be functional to different supply voltages, which can possibly reach energies around transistors' threshold levels. The presumption of performance at very low speed for low voltage supplies can compromise the correct functioning of the application,

and for this reason, a solution that increases the performance of the circuit for a determined task becomes mandatory.

Although IoT applications may differ from one another, the various requirements demanded in the devices to be extremely small, low cost, and efficient and to have low energy consumption will remain basically the same with certain commitments. Because of this, IoT devices have become highly integrated devices, often including all devices within a module or chip.

In the VLSI era, CMOS became the prevailing technology for manufacturing billions of chips. Nowadays, the electronic systems are adapted to the customers' expectations of better and increasing features with smaller sizes at reduced cost. The continuous advance in CMOS technology has allowed this fact for the last years with the shrinking trend of the transistors achieving better properties with smaller transistors at the cost of power. Besides the feature size reduction, other innovations such as new transistor architectures and the use of new materials have opened new opportunities and challenges for circuit designers. Scaling the technology is no longer just a matter of a geometrical issue but the implementation of these innovations in architectures and materials.

Under the premise that a great number of highly energy efficient small electronic devices are needed for the IoT era, nanometer CMOS technology is the best candidate for these applications because of its low cost, availability and highly integration capability developing new strategies to integrate all the functions (RF, analog, digital...) on a single chip. All this evolution has resulted in different technologies depending on the strategy used such as the already commercially available 22 nm FDSOI technology [18] maintaining the planar structure reaching the 12 nm node by 2019 [19] or going to non-planar structures like the 14 nm FinFET technology [20].

This work will focus on the RF part of the connectivity affected by the physical layer (PHY) of the protocol. As a reference for targeted performance, this work uses the IEEE 802.15.4 standard, which suits the basis of a low power consumption communication between sensors with low data rates for IoT applications. This standard only defines the physical and medium access control (MAC) layers of LR-WPAN. The others layers can be implemented by others standards compatible with this one such as ZigBee, ISA100.11a, WirelessHART, MiWi, SNAP, and Thread [21, 22].

#### 1.3. <u>Design challenges for CMOS RF</u>

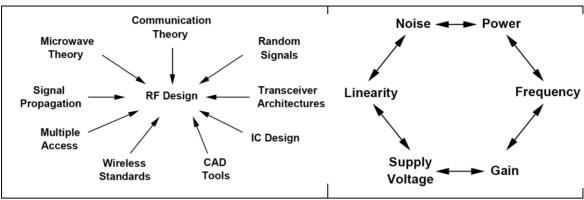

RF design is linked to a multitude of disciplines, and it has become a very challenging task to coordinate all these subjects. Figure 4, on the left part, shows and overview of different fields integrated in the RF design.

When the time to design comes there are some trade-offs to take into account in order to obtain the best suited system for your requirements. It is impossible to design a system adapted to be the best in every environment. Figure 4, on the right part, shows a basic idea how the figures of merit of the RF designs are linked and the trade-offs they involve. As an example, if you need a low power consumption design, the noise or frequency attributes will have to be sacrificed to obtain the desired consumption.

Figure 4 - RF Disciplines and Design hexagon [23]

#### 1.4. MOS scaling limitations and trends

The technology scaling following the Moore's law is getting harder to keep on. In deeply scaled MOSFETs, as they have very narrow channels, small-geometry effects start to affect their behavior. All this phenomena are collective referred to as Short Channel Effects (SCE) and tend to increase standby leakage currents, e.g., the potential of the drain starts to impact the electrostatics of the channel, which makes the gate to lose the adequate control over it. As a consequence, the gate cannot completely shut down the transistor and big sub-threshold leakage currents appear between the drain and the source [24-26]. To alleviate this issue, the use of thinner oxide layers and high-k materials have helped so far but the required gate oxide thickness in current technology nodes is so thin that it is not able to ensure the necessary isolation, implying too big gate and Gate-Induced Drain Leakages (GIDL) [27-29].

Among others evolutions strategies to overcome such problems, one is based on the implementation of a fully depleted channel. Big companies like Intel and STMicroelectronics are already manufacturing these devices and even though both use technologies with the channel fully depleted, they have a different philosophy. While Intel prefers to evolve towards a 3D technology like the Fin Field Effect Transistor (FinFET), STMicroelectronics has kept the planar concept, which makes it simpler to manufacture than FinFETs, with the FDSOI FET technology. The comparison of a cross-section of the different transistors is shown in Figure 5.

Figure 5 - Cross section of conventional bulk MOS transistor (left), FinFET on SOI (center) and planar fully-depleted (FDSOI) transistor (right) [30]

The basic principle of FinFETs is that the channel is formed on a thin semiconductor fin, which has to be thin enough to obtain a fully depleted channel, perpendicular to the substrate surface. They have a gate that wraps around the channel not only by one surface, which improves the electric characteristics. The substrate can be the conventional one or SOI, which entails some improvements on the performance [31], and they can have more

than one fin to reduce the total parasitic resistance and have more current flowing through it. These devices has already been widely studied for the last decade and a large amount of papers have been published demonstrating the enhancements in SCE behavior compared to bulk MOSFETs [32-35, 36-38].

On the other hand, STMicroelectronics' device consist in an ultra-thin layer, in order to have the channel fully depleted, above an extremely thin oxide isolation layer, so no current can circumvent the channel. This guaranties no floating body effect [39, 40] and the fact that the channel is undoped brings less manufacturing process variations. This technology is simpler to manufacture than the FinFETs and provides better yield at lower cost [11].

The performance at high speed, power consumption and the low cost are very important requirements for RF circuits in which bulk MOS technology is lagging behind. FDSOI CMOS technology seems to satisfy the need of the low power devices, combining high performance and low energy consumption, and at the same time shows good behavior at low supply voltages [30], which makes this technology a good candidate for the RF environment.

#### 1.5. FDSOI as a technology candidate for IOT

Prior to choose any technology, some analysis on the IoT application requirements have to be performed. As commented before, there is a wide range of energy levels needed depending on the applications, so an efficient energy flexibility is a key requirement.

Another issue is where this energy comes from because a lot of this devices will work autonomously in a distributed network harvesting the energy to perform their tasks within a changing energetic environment. This involves a very wide scenario of working conditions over the time for each node of the network, so an adaptive scheme that allows proper function at different voltage supplies, even at very low voltages around threshold levels, is needed. FDSOI has this flexibility to work with proper performance from normal voltage operation mode to low voltage levels.

Moreover, is known that IoT devices will not be continuously sending data and will remain in idle state most of the time. During the idle phases is interesting to have a very low consumption in order to extend the battery life or increase their autonomy, which is achieved by very low leakage systems. The application of a back biasing voltage in FDSOI allows to have a compromise between very low leakage and high speed, changing the operating conditions depending on the phase of the device as demonstrated in [43].

Finally, IoT devices are generally microsystems with a combination of digital and analog mixed signals and RF (RF transceivers, sensors, voltage converters...), and to make them profitable there is the need of having everything fully integrated in a single System on Chip (SoC). FDSOI allows this full integration, as demonstrated in [44], of digital and analog submodules maintaining the digital performance and an efficient analog design thanks to the property of threshold voltage (Vth) modulation, besides it is less sensitive to noise [45].

Therefore, taking into account all the flexibility needs for the IoT, the properties of the FDSOI technology cover all these points making this technology the most appropriate one for a wide range of IoT applications.

#### 1.6. Objectives

This thesis tries to verify the suitability of the 28 nm UTBB FDSOI technology developed by STMicroelectronics for designing IoT RF blocks. The main points are listed below:

- Get familiar with UTBB FDSOI technology.

- Characterization of 28 nm UTBB FDSOI transistors, with the compact models provided by ST Microelectronics.

- Design of a simple CS LNA with 1V supply fulfilling IEEE 802.15.4 requirements, making use of the capabilities of the UTBB FDSOI technology.

- Design of a simple CS LNA with sub-1V supply fulfilling IEEE 802.15.4 requirements, making use of the capabilities of the UTBB FDSOI technology.

#### 1.7. Thesis organization

To fulfill these objectives the thesis is divided in 5 chapters:

- Chapter 1: This is the introduction chapter where the motivation for this project is explained. There is an explanation of what the IoT is and which are some of the basic requirements of the devices that allow this concept. Additionally, the limitations of regular bulk CMOS for this purpose are commented and how other technologies are suitable for IoT. Finally, the main objectives and the thesis structure are included in this chapter.

- Chapter 2: This chapter reviews the state of the art in low power and low voltage RF designs. Some examples of papers of RF blocks already published are revised and an introduction to the gm/ld methodology for low power analog circuit optimization is included in this chapter.

- Chapter 3: This chapter starts with an overview of the UTBB FDSOI 28 nm developed by STMicroelectronics with its main properties covered. The simulation performed to characterize this technology is presented in form of some representative graphics and tables with the most relevant parameters, comparing some of the different transistors available in this technology that can be part of IoT systems. Finally, the characterization of a transistor in accordance with its inversion degree is presented.

- Chapter 4: This chapter presents two CS-LNA designs with this technology in different operating conditions. The first design is supplied by 1 V, the other design is supplied by 250 mV and tries to recover the specifications from the first one using the back bias technique. All these designs come with their proper simulations of the main figures of merit of an LNA.

- Chapter 5: In this last chapter the conclusions of the thesis are presented and the

possible future work lines to keep on checking the suitability of this technology are

mentioned.

# 2. State of the art on low-power low-voltage LNA design and gm/ld methodology

This section reviews some low power and low voltage Low Noise Amplifiers (LNA) designs extracted from the literature and a brief analysis of the gm/ld approach for low-power analog circuit optimization is performed.

#### 2.1. Case reviews

In the receiving path, the RF signal received is often very small and surrounded by interferers so the Signal to Noise Ratio (SNR) is easily degraded impacting negatively in the receiver performance. Hence, the first stages of an RF receiver should amplify the received weak signal with minimal noise added to the system in order to increase the sensitivity of the receiver. The Noise Figure (NF), or its lineal form noise factor (F), is a metric used to quantify this noise contribution, which describes the amount of noise a component or entire radio receive chain adds to the RF signal received. Therefore, the NF is a key measurement of the performance of an RF receiver and have to be kept as low as possible.

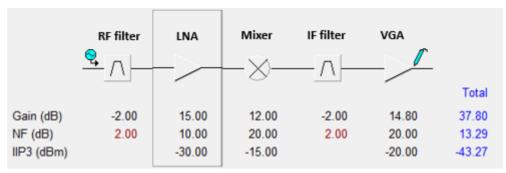

The cascaded values for the overall receiver NF for the system budget of the typical chain of the Figure 6 can be calculated by the Friis's formula (2.1) [46].

$$F_{TOTAL} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \dots + \frac{F_n - 1}{G_1 G_2 \dots G_{n-1}}$$

(2.1)

Where  $F_n$  is the noise factor and  $G_n$  is the gain of the n-th stage in the receive chain.

Figure 6 - Typical chain of cascaded components

As the equation shows, the stages closest to the input of the system are the ones that affects the most to the total noise. Consequently, the noise factor of the first stage should be minimum and its gain should be large enough to decrease the total noise contribution of the following stages, but it should be small enough not to saturate the following stages and jeopardize the receiver's linearity. For this reason, normally, the first active stage in a receiver after the antenna is a low noise amplifier (LNA), which have a moderate gain and a low noise figure.

Besides the NF and gain are the main candidates to ensure a receiver performance, other important characteristics involved in a LNA design are shown in Figure 7 [47-52].

Normally, good performance in terms of noise, gain, linearity... of a LNA entails a high power consumption. As a consequence, a lot of effort has been put in low power consumption LNAs design research (<1mW) [53 - 55]. The trade-offs between all this parameters can be taken into account through the FoM commonly used for benchmarking the low power LNA, which consists on the ratio of power gain to the Direct Current (DC)

power consumption (Gain/P<sub>DC</sub>). Furthermore, it can be extended including the effect of noise figure, linearity (IIP3) and the operation frequency (f<sub>c</sub>) with equation (2.2) [56].

$$FoM_{LNA} = \frac{Gain[abs]IIP3[mW]f_c[GHz]}{(F-1)[abs]P_{DC}[mW]}$$

(2.2)

Figure 7 - Important features in LNA design

As a first example of LNA designed for very low power consumption, the Figure 8 shows a low-power Ultra Wide Band (UWB) common-gate (CG) LNA implemented in a standard 1P6M 0.18 µm CMOS process presented in [54]. This LNA consists of a cascode CG stage followed by a buffer stage. This LNA has an operating bandwidth from 3 GHz to 10 GHz.

The drawbacks of the traditional input matching network (i.e.  $L_{S1}$  only) of CG LNAs include poor input impedance matching at low frequencies and non-flat NF over the frequencies of interest. A wideband input impedance matching is achieved thanks to a T-match input network composed of series resistances and inductances, which improve the matching at low frequencies ( $S_{11}$ ). The peaking inductor  $L_C$  resonates in parallel at the lower corner frequency 3 GHz with the parasitic capacitances at the drain from  $M_1$  and at the source of  $M_2$ , while the peaking inductor  $L_{D2}$  resonates in series at the upper corner frequency (10 GHz) with the parasitic gate capacitance of  $M_4$ . This peaking inductor helps to have a flat and high response of  $S_{21}$  and a flat and low response of NF.

In addition, to achieve the low power consumption it uses the self-body-bias technique, which consists on connecting body terminals of  $M_1$  and  $M_2$  by a resistor ( $R_B$ ), to reduce the threshold voltage of  $M_1$  and  $M_2$ . This  $V_{th}$  reduction results in a smaller supply voltage, 1.1 V in this case, for a fixed bias current.

Figure 8 - Schematic of a low power LNA from [54]

The overall performance summary of this LNA can be found in Table 2.

| Technology       | 180 nm |

|------------------|--------|

| Consumption [µW] | 990    |

| Supply [V]       | 1.1    |

| S11 [dB]         | <-10.3 |

| IIP3 [dBm]       | NA     |

| Gain [dB]        | 7.9    |

| NF [dB]          | 6      |

Table 2 - Main characteristics of LNA from [54]

A second example is presented in [57]. Figure 9 shows this Ultra-Low-Power (ULP) Ultra-Low-Voltage (ULV) UWB resistive-shunt feedback LNA implemented in a 90 nm CMOS technology. Its frequency operation range goes from 100 MHz to 7 GHz.

Figure 9 - Schematic of an ultra-low power, ultra-low voltage LNA with buffer for measurement purposes from [57]

This LNA circuit uses the current-reuse technique to improve the overall RF performance for a given power consumption. Current-reuse is an important technique in the

implementation of ultra-low power circuits. The basic idea is to share the DC current between two or more transistors while each transistor contributes to the total gain, thereby reducing the overall power and increasing the current efficiency. This technique has been widely used to reduce the power consumption [58 - 60]. Moreover, the complementary characteristics of transistors  $M_1$  and  $M_2$  (NMOS and PMOS) gives an advantage to ULP designs with additional benefits, such as better distortion and noise cancellation.

Another characteristic of this work is the presence of the gm/ld approach for designing a low-power amplifier. It introduces an extended ULP ULV biasing metric, which takes into account the current efficiency, the intrinsic gain and the transit frequency, to optimize transistor performance. Finally, the biasing metric shows that the transistor working on the MI region maximizes it. This metric also shows the impact of lowering the supply voltage. Lower supply voltages degrades the overall performance but continues showing the MI region as the optimum region to work in.

The input matching is achieved using a shunt-feedback resistor, which provides of wideband matching. However, some restrictions on the design have been taken into account due to the low voltage and low power requirements. In addition, the use of series peaking inductors ( $L_1$  and  $L_2$ ) in the feedback loop alleviate the gate-source capacitance ( $C_{gs}$ ) and the miller effect due to the gate-drain capacitance ( $C_{gd}$ ) extending the input matching and bandwidth. The use of this inductor is a conventional technique to resonate with the parasitic capacitances of the transistors increasing the bandwidth without burning extra power.

Regarding the stability, the presence of a feedback network and boosting inductors rise the instability problem but, in this case, the simulations demonstrated its unconditionally stability.

The performance summary of this LNA can be found in Table 3.

| Technology       | 90 nm     |

|------------------|-----------|

| Consumption [µW] | 750       |

| Supply [V]       | 0.5       |

| S11 [dB]         | <-10      |

| IIP3 [dBm]       | >-9       |

| Gain [dB]        | 12.6      |

| NF [dB]          | 5.5 – 6.5 |

Table 3 - Main characteristics of LNA from [57]

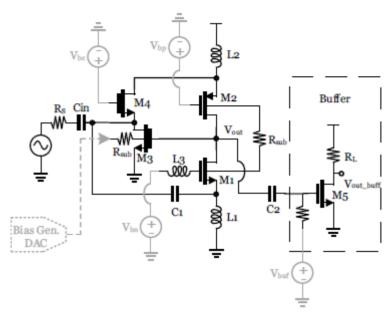

Figure 10 shows the ULP ULV CG LNA implemented in an IBM 0.13 µm 1P8M CMOS technology presented in [61] with a frequency range from 600 MHz to 4.2 GHz.

This work also uses the current-reuse technique. A complementary current-reuse structure can be seen where the input stage transistor M<sub>1</sub> and M<sub>4</sub> share DC current with the cascoded devices M<sub>2</sub> and M<sub>3</sub>, respectively, leading to an improvement on the DC current efficiency.

Inductor  $L_3$  at the gate of M1 provides inductive gm-boost [53] increasing the effective gm of the device at the resonant frequency of the inductor with the  $C_{gs}$  of  $M_1$  enhancing the bandwidth, gain and input matching without additional power consumption.

Figure 10 - Schematic of the proposed ULV and ULP LNA along with a buffer stage for measurement purposes from [61]

This LNA uses the forward body bias (FBB) technique which is attractive for ULP ULV circuit designs. The use of ULV supplies limits the choice of biasing voltages and achievable performances such as gain, linearity, operating frequency... The increment of the bulk-to-source voltage ( $V_{bs}$ ) have a direct impact on  $V_{th}$ , reducing it so a lower bias voltage is required to work on the desired region of operation. This work also shows how the use of FBB improves the intrinsic characteristics by mitigating some SCE; as the body potential increases, the drain depletion region decreases, so the control that the drain has over the channel is reduced reducing the drain- induced barrier lowering (DIBL). The FBB is implemented by adding  $R_{sub}$  between bodies of  $M_1$  and  $M_2$  [62]. This connection, which includes the source-to-body diodes, creates an ULP self-bias loop.  $R_{sub}$  controls the current in this loop, which is in the order of a few  $\mu A$ . Summarizing, this technique improves the output resistance of the transistors increasing the intrinsic gain of the transistor and lower the  $V_{th}$  allowing a reduction in the voltages needed.

The same previously commented biasing metric is used in this design, but introducing the effect of the FBB on this metric. It shows that the FBB improves the performance providing further validation of the suitability of this technique for ULV circuits without additional power consumption. It should be noted that transistors  $M_1$  and  $M_2$  are biased in the middle of the MI region and  $M_3$  and  $M_4$  are biased in the WI region.

A folded-cascode structure is used with  $M_4$  and  $M_2$  providing ULV isolation between the feedback node and the output. This isolation is necessary to have a flat gain and good input matching.

The broadband input matching is also obtained with the active shunt-feedback techniques. The transistor M<sub>3</sub> reduces the current needed for this matching paying the price of slightly reduced overall gain and higher NF. Hence, this technique plays a crucial role in the low power LNAs design.

The performance summary of this LNA can be found in Table 4.

| Technology       | 130 nm    |

|------------------|-----------|

| Consumption [µW] | 250 / 160 |

| Supply [V]       | 0.5 / 0.4 |

| S11 [dB]         | <-9       |

| IIP3 [dBm]       | -10 / -12 |

| Gain [dB]        | 14 / 13   |

| NF [dB]          | 4 / 4.5   |

Table 4 - Main characteristics of LNA from [61]

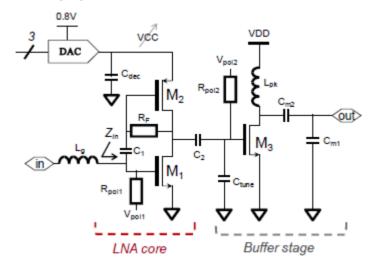

Figure 11 shows the single stage ULP LNA implemented in a standard 0.13 µm CMOS technology presented in [63] dedicated to the 2.4 GHz ISM band.

Figure 11 - Simplified schematic of a ULP LNA along with a buffer stage for measurement purposes from [63]

The starting point of this LNA design is based on the FoM  $\frac{gm*f_T}{I_D}$ . This figure takes into account the current efficiency (gm/ld) and the effect of parasitic such the capacitances, which impact negatively in the RF performance and are represented by  $f_T$ . This figure represents a trade-off between them and shows an optimum point when the transistor is biased in the MI region.

The not so high gm performed in this region requires of active topologies, such as a self-biased inverter topology, to compensate the gain. The core of the LNA is based in a self-biased inverter whose supply voltage is controlled by a 3-bit Digital to Analog Converter (DAC). This digital tuning allows maximizing the FoM of the LNA. An additional decoupling capacitor ( $C_1$ ) is placed between gates of  $M_1$  and  $M_2$  to further decrease the supply voltage.

The buffer stage provides the matching at the output (50  $\Omega$ ) through L<sub>pk</sub>, C<sub>m1</sub> and C<sub>m2</sub>. It holds on the LNA gain and is only used for measurement purposes.

The performance summary of this LNA can be found in Table 5.

| Technology       | 130 nm                |

|------------------|-----------------------|

| Consumption [µW] | 60 / 90 / 130         |

| Supply [V]       | 0.4 / 0.5 / 0.6       |

| S11 [dB]*        | <-10/<-10/<-10        |

| IIP3 [dBm]       | -12.2 / -12.6 / -13.1 |

| Gain [dB]        | 13.1 / 15.2 / 15.7    |

| Min NF [dB]      | 5.3 / 4.9 / 4.6       |

Table 5 - Main characteristics of LNA from [63]

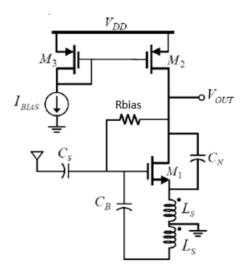

The last LNA reviewed in this section is shown in Figure 12. It is an ULP LNA with inductive feedback fabricated in a standard  $0.18 \mu m$  CMOS technology operating at 1 GHz presented in [64].

Figure 12 - Schematic of the proposed ultra-low power LNA with inductive feedback and  $C_{GD}$  neutralization from [64]

It uses the same FoM as the previous LNA to bias the  $M_1$  transistor, which is biased in MI region to achieve maximum FoM.

A gm-boosting inductive feedback [65] technique is used. The differential inductor feedback the signals at the gate and at the source to follow each other by  $180^{\circ}$  phase shift. This doubles the gm of the input transistor and provides the input impedance matching to  $50~\Omega$ . This technique along with an active load configuration increases the gain at very low bias currents.

The neutralization of  $C_{gd}$  is critical in LNA without a cascode structure [66] to maintain the input-output stability. The neutralization capacitance ( $C_N$ ) is implemented with a dummy NMOS device identical to  $M_1$ . Taking into account that the voltages at the gate and at the source are  $180^a$  phase shifted, making  $C_N$  equal to  $C_{gd}$  cancels out the currents that passes through them to the output node, therefore, neutralizing the feed-forward path through  $C_{gd}$ .

$R_{bias}$  connected between the gate and drain of  $M_1$  bias the circuit. This resistor has to be high enough so to not impact on the NF and gain of the proposed LNA. In this case, the designer has taken a value of 100 K $\Omega$ .

<sup>\*</sup>Estimated from the curves.

The performance summary of this LNA can be found in Table 6.

| Technology        | 180 nm |

|-------------------|--------|

| Consumption [µW]  | 100    |

| Supply [V]        | 1      |

| S11 [dB]          | -25    |

| IIP3 [dBm]        | -11.2  |

| Voltage gain [dB] | 16.28  |

| Min NF [dB]       | 3.9    |

Table 6 - Main characteristics of LNA from [64]

#### 2.2. Gm/ld approach for low-power analog circuit optimization

The electronics development toward smaller technology sizes has been pushed mostly by the digital electronics to have a high density transistors packed. At the same time, the analogue design has suffered this evolution with smaller headroom voltages, dynamic range, gains among other characteristics.

At these technologies dimensions the well-known long channel equations describing the transistors behavior are not accurate anymore. The short channel effects and the need of developing more agile and intuitive new design methodologies imply of a whole technology characterization.

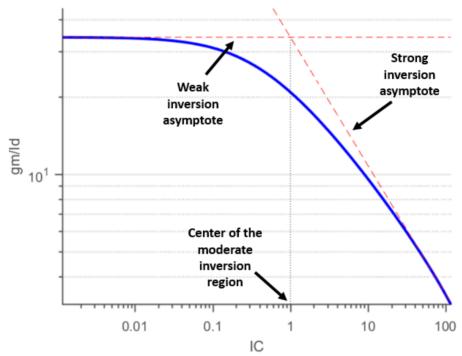

The gm/ld methodology is based on the universal shape of the technology transconductance efficiency (gm/ld) in function of the inversion degree in which the device is [67, 68], and this ratio is obtained by the whole characterization of the transistor process. This methodology is attractive because integrates the operating region of the MOSFET in the design (i.e. from weak through strong inversion) [69, 70] and is currently used for the modern analogue design [71, 72].

#### 2.2.1. Introduction to the gm/ld approach

The DC response of a transistor in saturation can take place in 3 different regions; weak inversion, moderate inversion and strong inversion region.

The weak inversion region appears when the MOSFET works with sufficiently low values of effective voltage. The channel is considered weakly inverted and the drain current is dominated by the carrier's diffusion current. This saturation current, which is expressed in equation (2.1), grows exponentially with the gate-to-source effective voltage ( $V_{qs}$ - $V_{th}$ ).

$$I_D(WI) = 2n\mu C_{ox} U_T^2 \left(\frac{W}{L}\right) \left(e^{\frac{V_{gs} - V_{th}}{nU_T}}\right)$$

(2.1)

The strong inversion region appears when the MOSFET works with sufficiently high effective voltage values. The channel is strongly inverted and the drain current is mostly related with the drift current. This saturation current is proportional to the squared gate-to-

source effective voltage and excluding geometrical effects, such as the saturation velocity, can be expressed with equation (2.2).

$$I_D(SI) = \frac{1}{2} \left( \frac{\mu C_{ox}}{n} \right) \left( \frac{W}{L} \right) (V_{GS} - V_{TH})^2$$

(2.2)

The region between these two is called the moderate inversion region and have no defined current expression or is too complex to calculate. For this reason, to design in an efficient and intuitive way is necessary an all-regions unified model like the EKV Model [73]. This model proposes an inversion coefficient (IC) which is an inversion degree's metric which defines the region where the transistor is operating in quantifying the inversion degree. This coefficient is determined by equation (2.3) [68].

$$IC = \frac{I_D}{I_o \frac{W}{I}} \tag{2.3}$$

Where  $I_D$  is the drain current, W is the width, L is the length and  $I_O$  is the normalization current named the technology's specific current defined in equation (2.4).

$$I_o = 2n\beta U_T^2 \tag{2.4}$$

Where n is the substrate factor,  $\beta = \mu C_{ox}$  is the transfer parameter,  $U_T = KT/q$  is the thermal voltage,  $\mu$  is the carriers' mobility factor and  $C_{ox}$  is the oxide capacitance per unit area. In this way, normalizing the drain current removes any size or technology dependence of the inversion coefficient.

The center of the moderate inversion region, assuming long channel behavior, is defined where the drain current is exactly the same to the technology's current and is equivalent to IC=1 [70]. From this point, the boundaries of the regions are defined as follows [74]:

- Weak inversion region IC < 0.1</li>

- Strong inversion region IC > 10

- Moderate inversion region 0.1 < IC < 10</li>

The gm/ld Figure of Merit (FoM) is one of the most important figures for low power applications. This FoM, which is very useful for the transistors sizing [75, 76], basically measures how much transconductance can be obtained for a fixed bias current and is closely linked with the IC. A simple expression of gm/ld is given by the equation (2.5) [74, 77]:

$$\frac{gm}{Id} = \frac{1}{nU_T} \frac{1}{(0.5 + \sqrt{IC + 0.25})} \tag{2.5}$$

The transconductance efficiency has two clearly recognizable regions; the weak inversion region and the strong inversion region. The weak inversion region behavior boundary is defined by a close to the thermal level flat asymptote, and the strong inversion region boundary is defined by an asymptote which is approaching in a square law relation to the gm/ld response [70]. As previously commented, as long as the short channel effects are neglected, the strong inversion current follows a squared law dependence, therefore, the asymptote has a -1/2 slope; on the other hand the weak inversion asymptote is simply a flat line with slope 0. The point where both asymptotes cross matches the middle of the moderate inversion region as Figure 13 shows.

Figure 13 - Transconductance efficiency vs. inversion coefficient (IC)

#### 2.2.2. Determining the specific current

Looking the equation (2.3), the extraction of the technology current to calculate the inversion coefficient is needed. An easy direct method to obtain it through simulations is explained in [78], which is based on the properties of gm/ld commented before.

The weak inversion asymptote is a horizontal line where the transconductance efficiency approaches the thermal limit. The strong inversion asymptote, assuming saturation and long channel conditions, is a line with -1/2 slope on a logarithmic scale. The reason why it has to be performed in a long channel transistor is because in short channel devices, its strong inversion response is degraded much faster due to the velocity saturation effect, so the asymptote in those cases have a steeper slope [79]. Therefore, this method must be performed in a long channel transistor and biased in saturation region.

Figure 14 shows the flowchart of the method to obtain the specific current of a transistor, which has been implemented with MATLAB after the extraction of the gm/ld vs. ld/W/L data from CADENCE simulations using the Process Design Kit (PDK) of this STMicroelectronics technology. The MATLAB code can be found in appendix 1. This algorithm basically plots

these two asymptotes and moves the strong asymptote horizontally until it coincides with the gm/ld curve. The point where the two asymptotes coincides determines the specific current ( $I_{o}=Id/W/L$ ).

Figure 14 - Technology Current (I<sub>0</sub>) Determination Flowchart [78]

#### The steps are the following:

- First the curves of gm/ld in terms of current density have to been extracted from the model.

- Then, an initial guess of the technology current have to be determined. In this thesis

case, it is determined as a current in the strong region behavior.

- The next step is to calculate the square law gm/ld line and calculate the distance between the line and the gm/ld curve. The gm/ld<sub>max</sub> is obtained in the weak inversion region.

- If the distance is zero or close to zero the I<sub>o</sub> used to calculate the SQL is the correct one. In other case it is slightly modified and the process is repeated. In the case of this thesis it is decreased in steps of 10 nA.