Lightweight Protocols and Applications for Memory-Based Intrinsic Physically Unclonable Functions Found on Commercial Off-The-Shelf Devices

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) genehmigte Dissertation von M.Sc. André Schaller aus Zeitz Tag der Einreichung: 18.10.2017, Tag der Prüfung: 29.11.2017 Darmstadt 2017 — D 17

- 1. Gutachten: Prof. Dr. Stefan Katzenbeisser

- 2. Gutachten: Prof. Dr. Jakub Szefer

Security Engineering Group Fachbereich Informatik Computer Science Department

## Lightweight Protocols and Applications for Memory-Based Intrinsic Physically Unclonable Functions Found on Commercial Off-The-Shelf Devices

Genehmigte Dissertation von M.Sc. André Schaller aus Zeitz

1. Gutachten: Prof. Dr. Stefan Katzenbeisser

2. Gutachten: Prof. Dr. Jakub Szefer

Tag der Einreichung: 18.10.2017 Tag der Prüfung: 29.11.2017

$\rm Darmstadt - D~17$

## Erklärung zur Dissertation

Hiermit versichere ich, die vorliegende Dissertation ohne Hilfe Dritter nur mit den angegebenen Quellen und Hilfsmitteln angefertigt zu haben. Alle Stellen, die aus Quellen entnommen wurden, sind als solche kenntlich gemacht. Diese Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

Darmstadt, den 18.10.2017

(M.Sc. André Schaller)

### Zusammenfassung

Derzeit erleben wir die Ära, in der durch die zunehmende Verbreitung von miteinander verbundenen, eingebetteten Geräten sich das sogenannte "Internet of Things" (IoT) manifestiert. Obwohl derartige Endgeräte oft als "smarte Objekte" bezeichnet und ihnen somit eine gewisse Intelligenz unterstellt wird, ist aus Perspektive der IT-Sicherheit oftmals das Gegenteil der Fall. Die Einwirkung der Märkte im Bereich kommerzieller IoT-Geräte führt zur Minimierung der Herstellungskosten sowie der Produkteinführungszeiten. Dieser weit verbreitete Trend hat einen direkten, desaströsen Einfluss auf die Sicherheitseigenschaften der Geräte. Eine Großzahl aktuell genutzter und zukünftig produzierter Plattformen implementieren keinerlei oder nur unzureichende Sicherheitsmechanismen. Vor allem das Fehlen sicherer Hardware-Komponenten, unterbinden oftmals die Implementierung sicherer Protokolle und Anwendungen.

Diese Arbeit widmet sich einem grundsätzlichen Lösungsansatz, welcher es erlaubt, kommerzielle, eingebettete Geräte, die durch das Fehlen sicherer Hardware-Komponenten verschiedensten Angriffen ausgesetzt sind, nachträglich absichern kann. Im speziellen, nutzen wir das Konzept der Physikalisch Unkopierbaren Funktionen (PUFs), um Hardware-basierte Sicherheitsanker in Standard-Hardware-Komponenten zu erstellen. Wir setzen dabei auf die Varianz von Static Random-Access Memory (SRAM) und Dynamic Random-Access Memory (DRAM) Modulen, welche während der Herstellungsprozesse induziert werden, um intrinsische, speicherbasierte PUF Instanzen zu extrahieren und darauf aufbauend, sichere und leichtgewichtige Protokolle und Anwendungen zu entwickeln.

In einem ersten Schritt führen wir zu diesem Zwecke eine empirische Evaluation ausgewählter und repräsentativer Gerätetypen bezüglich ihrer PUF-Eigenschaften durch. Als nächstes nutzen wir die Gerätetypen, welche sich durch die Existenz guter PUF-Instanzen für die darauf folgende Entwicklung leichtgewichtiger Sicherheitsanwendungen und -protokolle qualifizieren. Im zweiten Teil der Arbeit stellen wir verschiedene Software-basierte Sicherheitslösungen vor, die speziell für die charakteristischen Eigenschaften von eingebetteten Geräte konzipiert sind. Im speziellen umfassen diese Lösungen eine Secure Boot Architektur sowie einen Ansatz, die Integrität von Firmware durch Bindung an die zugrundeliegende Hardware zu schützen. Weiterhin wird ein leichtgewichtiges Authentifizierungsprotokoll vorgestellt, welches die Charakteristiken eines neuartigen DRAM-basierten PUF-Typs ausnutzt. Als letztes wird ein Protokoll vorgestellt, welches erlaubt, die Sicherheit des Software-Zustandes von entfernten, eingebetteten Geräten sicher zu attestieren.

## Abstract

We are currently living in the era in which through the ever-increasing dissemination of interconnected embedded devices, the Internet-of-Things manifests. Although such end-point devices are commonly labeled as "smart gadgets" and hence they suggest to implement some sort of intelligence, from a cyber-security point of view, more then often the opposite holds. The market force in the branch of commercial embedded devices leads to minimizing production costs and time-to-market. This widespread trend has a direct, disastrous impact on the security properties of such devices. The majority of currently used devices or those that will be produced in the future do not implement any or insufficient security mechanisms. Foremost the lack of secure hardware components often mitigates the application of secure protocols and applications.

This work is dedicated to a fundamental solution statement, which allows to retroactively secure commercial off-the-shelf devices, which otherwise are exposed to various attacks due to the lack of secure hardware components. In particular, we leverage the concept of Physically Unclonable Functions (PUFs), to create hardware-based security anchors in standard hardware components. For this purpose, we exploit manufacturing variations in Static Random-Access Memory (SRAM) and Dynamic Random-Access Memory modules to extract intrinsic memory-based PUF instances and building on that, to develop secure and lightweight protocols and applications.

For this purpose, we empirically evaluate selected and representative device types towards their PUF characteristics. In a further step, we use those device types, which qualify due to the existence of desired PUF instances for subsequent development of security applications and protocols. Subsequently, we present various software-based security solutions which are specially tailored towards to the characteristic properties of embedded devices. More precisely, the proposed solutions comprise a secure boot architecture as well as an approach to protect the integrity of the firmware by binding it to the underlying hardware. Furthermore, we present a lightweight authentication protocol which leverages a novel DRAM-based PUF type. Finally, we propose a protocol, which allows to securely verify the software state of remote embedded devices.

### Acknowledgements

First and foremost, I am deeply indebted to my supervisor professor Stefan Katzenbeisser. His profound expertise, his supervision and his unrestricted support contributed greatly to the successful results of my research and eventually to the compilation of this doctoral thesis. In fact, his supervision did not just shape the process of my scientific work but also me as a person. Thus, I want to state explicitly that without him the successful writing of this thesis would not have been possible. In addition, I would like to thank professor Jakub Szefer, who enabled me to spent two months researching at the Computer Architecture Laboratory Lab (CAS Lab) at Yale University. This visit allowed me to work on exciting research projects and to exchange inspiring ideas with his group, which eventually resulted in several publications. Moreover, I express my thanks to my colleagues of our research group, the Security Engineering group. Our longtime collaboration did not just open up new vistas and led to innovative solutions but also led to friendships. My special thanks go to my family: my parents Ingrid and Gerhardt Schaller, my sister Katja and my brother-in-law Finley. Their continuous support, trust and positivity provided me with the energy necessary to successfully handle this challenge. Finally, I would like to thank my many friends for their permanent support.

### Danksagung

In erster Linie gilt mein Dank meinem Betreuer Professor Stefan Katzenbeisser. Sein profundes Fachwissen, seine Betreuung und seine uneingeschränkte Unterstützung trugen maßgeblich zu den erfolgreichen Resultaten meiner Forschung und schließlich zur Erstellung dieser Doktorarbeit bei. Tatsächlich hatte seine Betreuung nicht nur Einfluss auf den Prozess meiner wissenschaftlichen Arbeit, sondern auch auf mich als Person. Daher möchte ich ausdrücklich festhalten, dass ohne ihn, die erfolgreiche Erstellung dieser Arbeit nicht möglich gewesen wäre. Mein Dank gilt weiterhin Professor Jakub Szefer, welcher mir ermöglichte, für zwei Monate am Computer Architecture Laboratory (CAS Lab) der Yale Universität zu forschen. Durch diesen Besuch konnte ich an spannenden Forschungsthemen arbeiten, trat in einen inspirierenden Austausch mit seiner Forschungsgruppe, woraus letztendlich mehrere Publikationen resultierten. Darüber hinaus möchte ich mich bei meinen Kollegen unserer Forschungsgruppe — der Security Engineering Group — bedanken. Die langjährige Zusammenarbeit mit ihnen eröffnete nicht nur neue fachliche Perspektiven, führte zu innovativen Lösungsansätzen, sondern brachte auch Freundschaften hervor. Mein besonderer Dank gilt meiner Familie: meinen Eltern Ingrid und Gerhardt Schaller, meiner Schwester Katja und meinem Schwager Finley. Ihre kontinuierliche Unterstützung, ihr Vertrauen und Positivität gaben mir die Energie, welche notwendig war, diese Herausforderung erfolgreich zu meistern. Nichtzuletzt bedanke ich mich bei meinen vielen Freunden, für deren ständige Unterstützung.

Denn indem ein Mensch mit den ihm von Natur gegebenen Gaben sich zu verwirklichen sucht, tut er das Höchste und einzig Sinnvolle, was er kann.

Hermann Hesse

Gewidmet meinem Großvater Horst Künzel.

VII

## Contents

| 1. | Introduction                                               | 1        |

|----|------------------------------------------------------------|----------|

|    | 1.1. Research Goal and Research Question                   | 4        |

|    | 1.2. Methodology                                           | 5        |

|    | 1.3. Thesis Outline                                        | 5        |

| 2. | Preliminaries                                              | 7        |

|    | 2.1. Notations                                             | 7        |

|    | 2.1.1. Functions and Mappings                              | 8        |

|    | 2.1.2. Distance and Similarity Metrics                     | 8        |

|    | 2.1.3. Entropy                                             | 8        |

|    | 2.2. Common Capabilities of Low-Cost Devices               | 9        |

|    | 2.2.1. Hardware                                            | 9        |

|    |                                                            | 12       |

|    | 2.2.3. Security Issues                                     | 13       |

|    | •                                                          | 14       |

|    |                                                            | 14       |

|    | ·                                                          | 15       |

| 3  | Physically Unclonable Functions found in Commodity Devices | 16       |

| 0. |                                                            | 17       |

|    |                                                            | 17       |

|    | 1                                                          | 20       |

|    |                                                            | 20       |

|    |                                                            | 21<br>24 |

|    |                                                            | 26       |

|    |                                                            | 20<br>27 |

|    | 5                                                          | 27<br>29 |

|    |                                                            | 31       |

| 4  | Empirical Analysis of DIJE Instances                       | 32       |

| 4. | r J                                                        | 32<br>33 |

|    |                                                            |          |

|    |                                                            | 34       |

|    |                                                            | 35       |

|    |                                                            | 36       |

|    |                                                            | 36       |

|    |                                                            | 37       |

|    |                                                            | 37       |

|    | 8                                                          | 38       |

|    |                                                            | 38       |

|    | 4.4.3. Metrics Used for Entropy Estimation                 | 39       |

|    | 4.5.       |                                                      | 40 |

|----|------------|------------------------------------------------------|----|

|    |            | 4.5.1. SRAM-based PUF Results                        | 40 |

|    |            | 4.5.2. Decay-Based DRAM PUF Results                  | 46 |

|    |            | 4.5.3. Rowhammer PUF Results                         | 53 |

|    |            |                                                      |    |

|    | 4.6.       | Chapter Summary                                      | 59 |

|    |            |                                                      |    |

| 5. | Secu       | re Boot                                              | 61 |

|    | 5.1.       | Threat Model                                         | 62 |

|    |            |                                                      | 63 |

|    |            |                                                      |    |

|    | 5.3.       | 6                                                    | 64 |

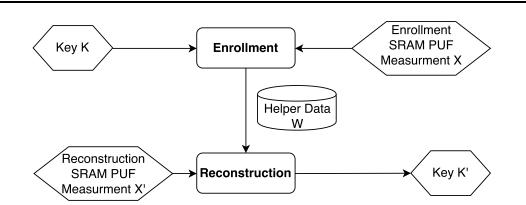

|    |            | 5.3.1. Enrollment                                    | 65 |

|    |            | 5.3.2. Reconstruction                                | 65 |

|    | 5.4.       | Proof of Concept                                     | 65 |

|    |            | 5.4.1. Enrollment                                    | 66 |

|    |            | 5.4.2. Reconstruction                                | 66 |

|    |            |                                                      |    |

|    |            | 5.4.3. Fuzzy Extractor Design                        | 66 |

|    |            | 5.4.4. Evaluation                                    | 67 |

|    |            | 5.4.5. Memory                                        | 68 |

|    |            | 5.4.6. Runtime                                       | 68 |

|    | 55         |                                                      | 69 |

|    | 5.5.       |                                                      | 09 |

| 0  | <b>T</b> T |                                                      |    |

| 6. |            | lware-Software Binding                               | 70 |

|    | 6.1.       | Architecture                                         | 71 |

|    | 6.2.       | Code Integrity Checks                                | 72 |

|    |            | Device Authenticity Check                            | 73 |

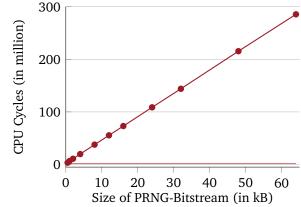

|    | 0.01       | 6.3.1. PRNG Bitstream Generation                     | 73 |

|    | <i>C</i> 1 |                                                      |    |

|    | 0.4.       | Response Functions                                   | 74 |

|    |            | 6.4.1. Indirect Branch Response                      | 74 |

|    |            | 6.4.2. Stack Manipulation Response                   | 75 |

|    | 6.5.       | Mutually Checking Code Regions                       | 75 |

|    |            | On the Solvability of Mutually Checking Code Regions | 76 |

|    | 0.0.       |                                                      | 77 |

|    |            | 6.6.1. Assumptions                                   |    |

|    |            | 6.6.2. Proof Sketch                                  | 77 |

|    | 6.7.       | Security Evaluation                                  | 78 |

|    |            | 6.7.1. Static Attacker Model                         | 78 |

|    |            | 6.7.2. Dynamic Attacker Model                        | 79 |

|    | 68         | Proof of Concept                                     | 81 |

|    | 0.0.       |                                                      |    |

|    |            | 6.8.1. Implemented Protection Mechanisms             | 81 |

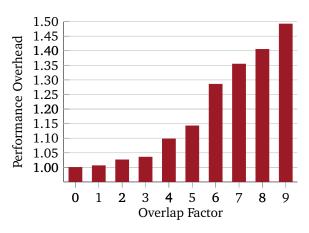

|    |            | 6.8.2. Performance Evaluation                        | 82 |

|    | 6.9.       | Chapter Summary                                      | 84 |

|    |            |                                                      |    |

| 7. | Aut        | hentication                                          | 85 |

|    | 7.1.       | Existing Authentication Solutions                    | 86 |

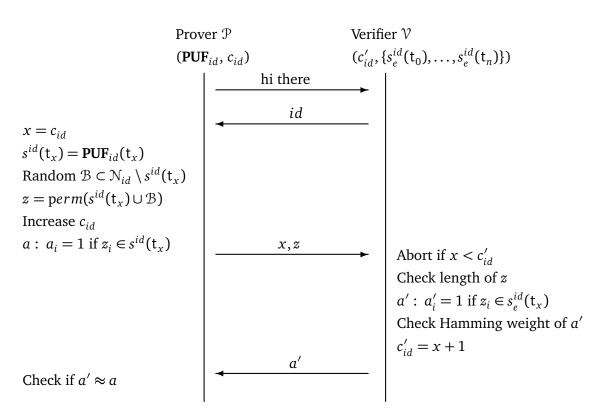

|    |            | Mutual Authentication Protocol                       | 87 |

|    | /.4.       |                                                      |    |

|    |            | 7.2.1. Threat Model                                  | 88 |

|    |            | 7.2.2. System Setup                                  | 88 |

|    |            | 7.2.3. Enrollment Phase                              | 88 |

|    |            | 7.2.4. Authentication Phase                          | 88 |

|    | 73         | Experimental Validation                              | 90 |

|    | /.0.       | Experimental valuation                               | /0 |

|    | 7.4. Chapter Summary                 | . 92  |

|----|--------------------------------------|-------|

| 8. | Remote Attestation                   | 93    |

|    | 8.1. Existing Attestation Solutions  | . 93  |

|    | 8.2. System Model and Goals          | . 94  |

|    | 8.2.1. System Model                  | . 94  |

|    | 8.2.2. Threat Model                  | . 95  |

|    | 8.2.3. Remote Attestation Game       | . 95  |

|    | 8.3. Boot Attestation                | . 96  |

|    | 8.3.1. Implicit Chain of Trust       | . 96  |

|    | 8.3.2. Remote Attestation Protocol   | . 96  |

|    | 8.3.3. Security Evaluation           | . 98  |

|    | 8.4. Hardware Requirements           | . 99  |

|    | 8.5. Proof-of-Concept Implementation | . 101 |

|    | 8.6. Performance Evaluation          |       |

|    | 8.7. Chapter Summary                 |       |

| 9. | Conclusion                           | 105   |

| Bi | bliography                           | 108   |

| Α. | List of Publications                 | 124   |

# List of Figures

|      | Typical hardware configuration of an embedded Microcontroller Unit (MCU)<br>An SRAM array (a) that consists of SRAM cells that form two cross-coupled inverters (b). The structure of a 6T-Static Random-Access Memory (SRAM) cell in | 11       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 23   | detail (c) and the threshold voltage $V_{th}$ of the corresponding transistor (d)<br>Schematic of Dynamic Random-Access Memory (DRAM) cells (a). DRAM cell                                                                            | 14       |

| 2.0. | organization (b).                                                                                                                                                                                                                     | 15       |

|      | Illustration of the enrollment and reconstruction phases of a Fuzzy Extractor<br>Bitmap of 32 kB SRAM start-up values extracted from a Texas Instruments                                                                              | 23       |

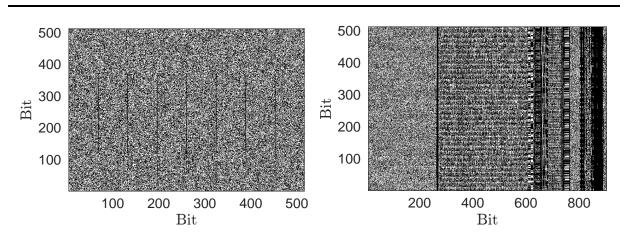

| 3.3. | LM4F120H5QR development platform                                                                                                                                                                                                      | 26       |

| 3.4. | Memory (ROM) code                                                                                                                                                                                                                     | 26       |

| 3.5. | for dissipation of charges that lead to PUF behavior                                                                                                                                                                                  | 27<br>27 |

| 3.6. | Process of querying a decay-based DRAM PUF instance.                                                                                                                                                                                  | 27<br>28 |

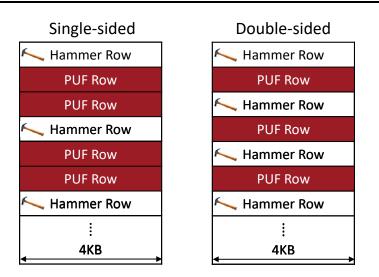

|      | Layout of hammer rows and PUF rows due to the RH type parameter. Left: single-<br>sided (SSRH). Right: double-sided (DSRH). A row size of 4 kB is assumed                                                                             | 30       |

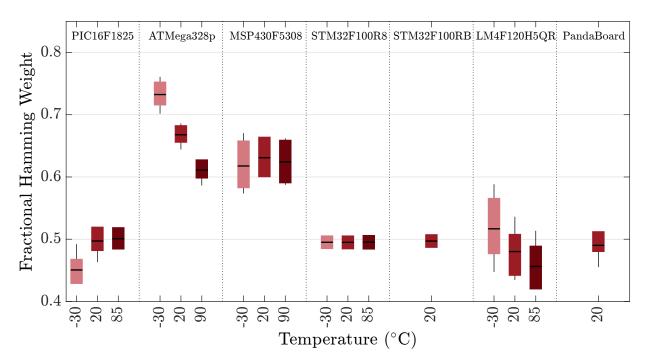

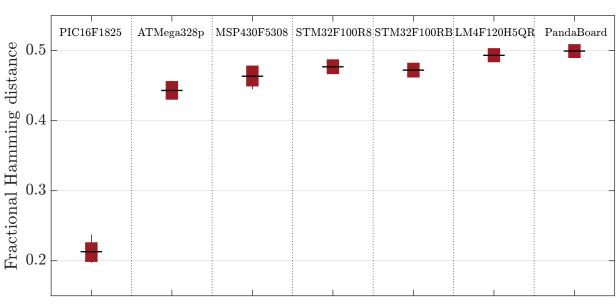

| 4.1. | Hamming weight ( <b>HW</b> ) values of SRAM start-up measurements obtained from device types at different ambient temperatures (optimum: 0.5).                                                                                        | 41       |

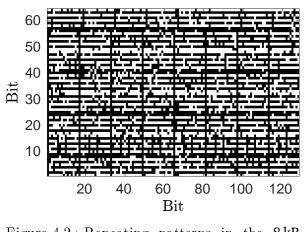

|      | Repeating patterns in the 8 kB SRAM start-up values from an PIC16F721 MCU                                                                                                                                                             | 42       |

|      | Uniqueness values (HD <sub>inter</sub> ) of SRAM start-up measurements obtained from device types at different ambient temperatures (optimum: 0.5)                                                                                    | 43       |

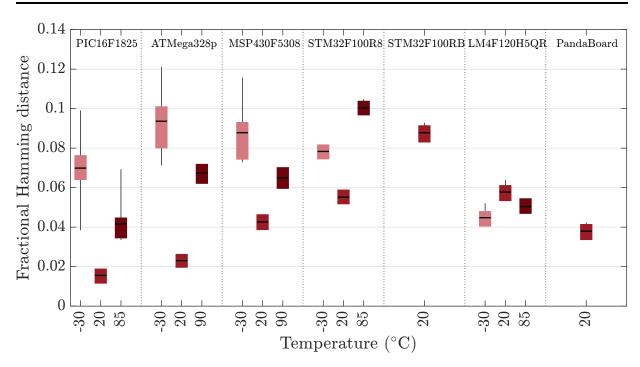

| 4.4. | Robustness values (HD <sub>intra</sub> ) of SRAM start-up measurements obtained from device types at different ambient temperatures (theoretical optimum: 0)                                                                          | 44       |

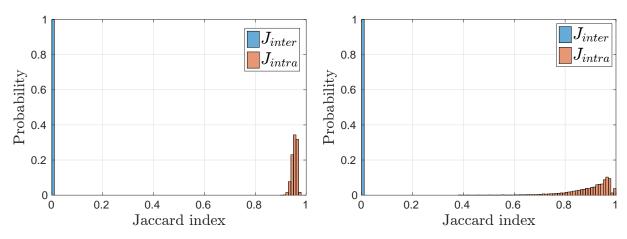

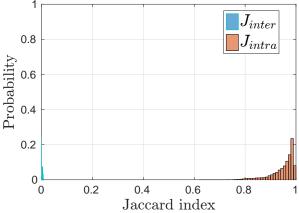

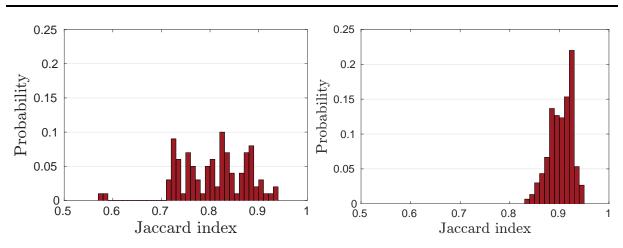

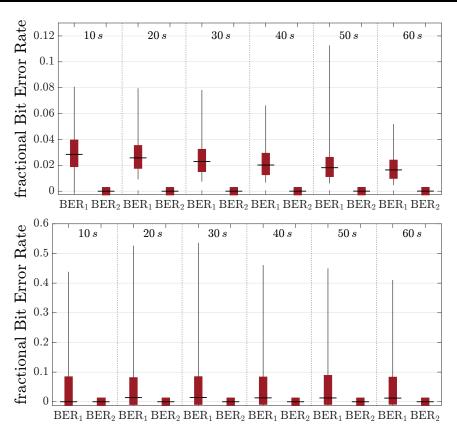

| 4.5. | Histograms of $\mathbf{J}_{intra}$ and $\mathbf{J}_{inter}$ values for the PandaBoard and the Intel Galileo,<br>with $\mathcal{T}_1 = \{10s, 20s, 30s, 40s, 50s, 60s\}$ and $\mathcal{T}_2 = \{120s, 180s, 240s, 300s, 360s\}$        | 40       |

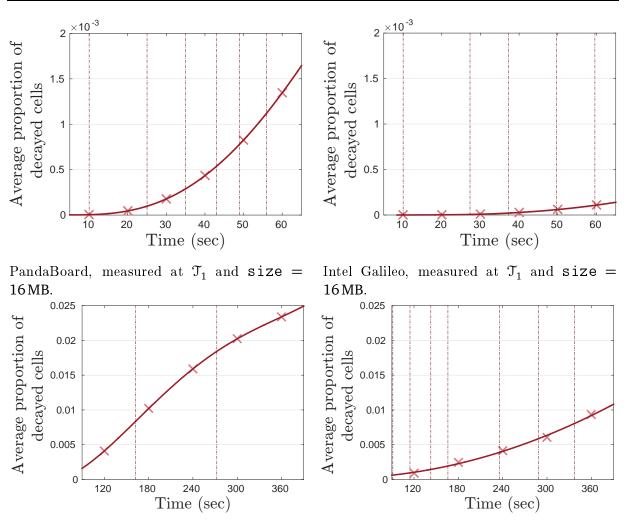

| 4.6. | and two different PUF sizes<br>Time-dependency of the decay DRAM cells on the PandaBoard and the Intel<br>Galileo for $\mathcal{T}_1$ and $\mathcal{T}_2$ , as well as size = 16MB and 32kB. Possible challenges are                  | 48       |

| 4.7. | indicated by vertical lines                                                                                                                                                                                                           | 50       |

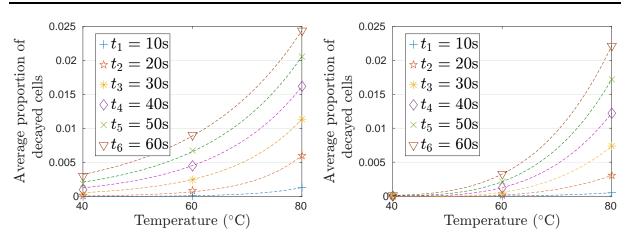

|      | Board and the Intel Galileo for different decay times $\mathcal{T}_1$ and $\mathcal{T}_2$ and values of PUF size parameter                                                                                                            | 51       |

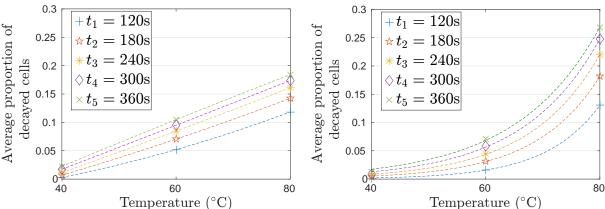

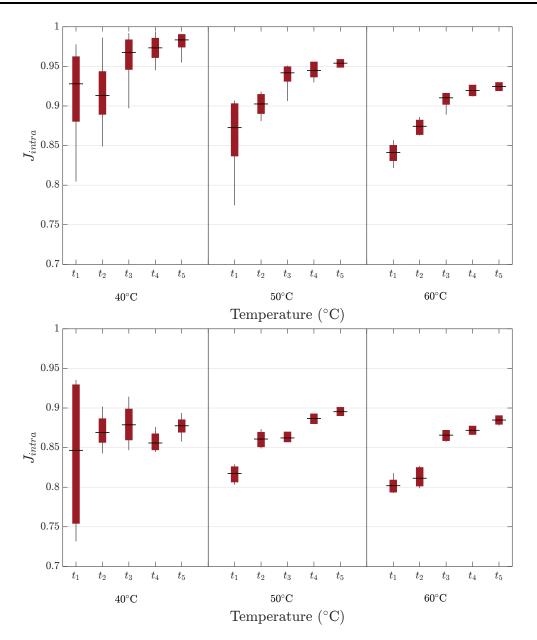

| 4.8. | $J_{intra}$ values (i.e., similarity) of enrollment measurements taken at room temper-<br>ature and measurements at higher temperatures $T' = \{40 \text{ °C}, 50 \text{ °C}, 60 \text{ °C}\}$ , with<br>adjusted decay times $t'$ for the PandaBoard (top) and Intel Galileo (bottom) | 52       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.9. | Distribution of $J_{intra}$ values computed between measurements pairs, taken at en-<br>rollment and reconstruction from the same logical PUF instances, roughly 16                                                                                                                    |          |

| 1 10 | months apart. Values are shown for the PandaBoard (left) and Intel Galileo (right).                                                                                                                                                                                                    | 53       |

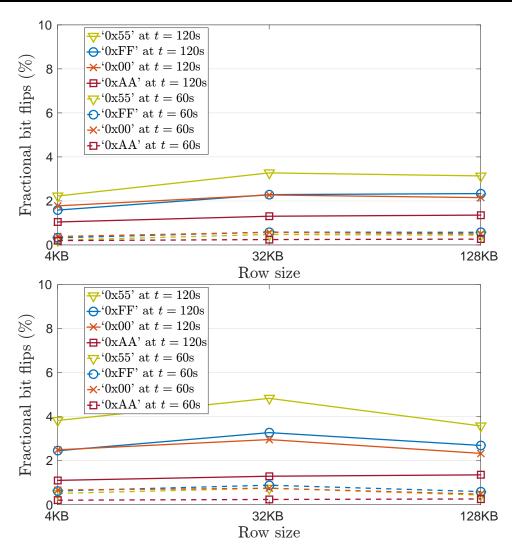

|      | .Fractional number of bit flips, given in percent relative to RH size, using PUF row<br>iv ='0xAA'. Number of bit flips using SSRH (top) and using DSRH (bottom)                                                                                                                       | 55       |

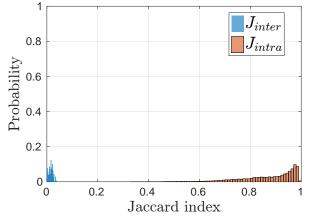

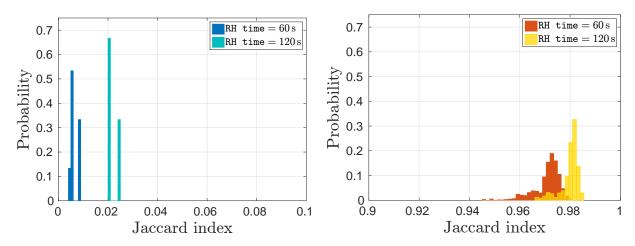

| 4.11 | .Histograms of $J_{inter}$ (left) and $J_{intra}$ (right) values for three PUF instances using 20 measurements with PUF row iv =' $0xAA'$ , Hammer row iv =' $0x55'$ , RH size =                                                                                                       |          |

|      | 128  kB and RH type set to SSRH                                                                                                                                                                                                                                                        | 57       |

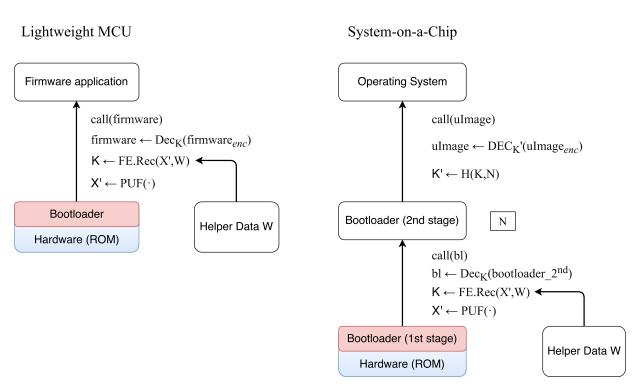

| 5.1. | Secure boot architecture for low-end MCU- and more complex SoC-based device                                                                                                                                                                                                            |          |

|      | types                                                                                                                                                                                                                                                                                  | 64       |

|      | Relative runtime performance with different overlap factor settings                                                                                                                                                                                                                    | 83<br>83 |

|      | The lightweight mutual authentication protocol                                                                                                                                                                                                                                         | 90<br>92 |

| 8.1. | Schematic overview of one possible instantiation of our Boot Attestation scheme as part of a remote attestation protocol.                                                                                                                                                              | 97       |

# List of Tables

| 2.1. | The three classes of embedded devices evaluated in this thesis                                                                                                                                                                                                                                                                                      | 10  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Device types used for evaluating characteristics of different PUF types Evaluation results of bias, uniqueness and robustness for SRAM-based PUF in-                                                                                                                                                                                                | 34  |

|      | stances extracted from various device types under different ambient temperatures.                                                                                                                                                                                                                                                                   | 41  |

| 4.3. | Entropy results of SRAM-based PUF measurements extracted from various device types under different ambient temperatures.                                                                                                                                                                                                                            | 45  |

| 4.4. | Evaluation results for logical decay-based DRAM PUF instances measured at different decay times $\mathcal{T}_1$ and $\mathcal{T}_2$ as well as for different PUF sizes. Top: results for decay times $\mathcal{T}_1 = \{10 \text{ s}, 20 \text{ s}, 30 \text{ s}, 40 \text{ s}, 50 \text{ s}, 60 \text{ s}\}$ and size = 16 MB. Bottom: results for | чJ  |

|      | decay times $T_2 = \{120 \text{ s}, 180 \text{ s}, 240 \text{ s}, 300 \text{ s}, 360 \text{ s}\}$ and size = 32 kB                                                                                                                                                                                                                                  | 47  |

| 4.5. | Parameters used during evaluation of the Rowhammer PUF characteristics and                                                                                                                                                                                                                                                                          |     |

| 16   | their corresponding set of values                                                                                                                                                                                                                                                                                                                   | 54  |

| 4.0. | tions of Hammer row iv and PUF row iv. Configuration used: RH size = 128KB and RH time = 120s (SSRH/DSRH)                                                                                                                                                                                                                                           | 56  |

| 4.7. |                                                                                                                                                                                                                                                                                                                                                     | 00  |

| 4.8. | {60 s, 120 s}, RH size = {4 kB, 32 kB, 128 kB}, and both variants of RH type<br>Comparison of the average number of bit flips and minimum $J_{intra}$ values at oper-                                                                                                                                                                               | 57  |

|      | ating temperatures of 40 °C, 50 °C and 60 °C using the optimal parameter configu-<br>ration.                                                                                                                                                                                                                                                        | 58  |

| 5.1. | Implementation overhead with respect to runtime in milliseconds (left) and mem-<br>ory overhead in Bytes (right) for the PandaBoard.                                                                                                                                                                                                                | 68  |

| 8.1. | Implementation overhead with respect to runtime in milliseconds (left) and memory overhead in Bytes (right) for the TI Stellaris (ARM), with compiler optimizations for size ( <b>-0s</b> ) and runtime ( <b>-01</b> ).                                                                                                                             | 103 |

## Acronyms

- AES Advanced Encryption Standard. 39, 66

- ASIC Application-Specific Integrated Circuit. 3, 21, 31, 45

- COTS Commercial Off-The-Shelf. 2–6, 10, 13, 14, 19, 26, 31–34, 40, 42, 53, 60, 69, 100, 101, 103, 105

- CPU Central Processing Unit. 2, 4, 11, 12, 26

- CTW Context Tree Weighting. 33, 39, 40, 46

- DRAM Dynamic Random-Access Memory. XI, XIII, 2–7, 9, 11–15, 17–21, 23, 26–31, 33–39, 46–51, 53–56, 58–60, 62, 64, 66, 78, 87–92, 105, 106

- ECC Error-Correcting Code. 22, 29, 31

- EEPROM Electrically Erasable Programmable Read-only Memory. 10–12, 14, 34, 35, 62, 102

- FE Fuzzy Extractor. 22, 73, 74, 82

- FPGA Field-Programmable Gate Array. 3, 21, 26, 31, 45

- HCI Hot Carrier Injection. 18, 19

- HMAC Keyed-Hash Message Authentication Code. 96–98, 101–103

- IoT Internet-of-Things. 1, 5, 10, 24, 93, 95, 96, 99

- JTAG Joint Test Action Group. 12, 61, 95, 101, 102

- KDF Key Derivation Function. 96, 103

- MCU Microcontroller Unit. XI, XII, 1, 2, 4, 9–12, 14, 19, 23, 25, 31–36, 41, 42, 44–46, 59–65, 69, 95, 97, 99–101, 103

- MITM Man In The Middle. 86–88

- NVM Non-Volatile Memory. 12, 22, 61-64, 67, 68, 88

- OS Operating System. 27, 36

- PCB Printed Circuit Board. 4, 35

PoP Package-on-Package. 11, 26, 35, 107

PRNG Pseudo-Random Number Generator. 73, 74, 76, 77, 79, 80, 82-84

- PUF Physically Unclonable Function. VIII, IX, XI–XIII, 3–7, 9, 14–60, 62–65, 67, 69, 71, 73, 74, 79–84, 87–92, 101–103, 105–107

- RFID Radio-Frequency Identification. 10, 86, 87

- ROM Read-Only Memory. XI, 22, 26, 62, 63

- RoT Root of Trust. 4, 12, 13, 95, 97, 98, 100–102

- SGX Software Guard Extensions. 2, 13, 22

- SoC System on Chip. XI, XII, 1, 10, 11, 13, 25, 26, 33–35, 62–65, 92, 95, 98, 100, 101, 107

- SRAM Static Random-Access Memory. XI, XIII, 2–7, 9, 11–15, 17–19, 22–26, 31–46, 50, 53, 56, 59, 60, 62–65, 67–69, 71, 73, 74, 81, 82, 84, 98, 101–103, 105

- TEE Trusted Execution Environment. 2, 13, 61, 96

- TPM Trusted Platform Module. 2, 13, 22, 70, 93, 96, 98, 99

- UART Univeral Asynchronous Receiver Transmitter. 25, 36, 40, 82

## Chapter 1

## Introduction

n the Internet-of-Things (IoT) [LTL16] embedded devices, particularly low-cost and resource-constrained platforms are becoming the fundamental building blocks for many facets of life. Innovation in this space is not only fueled by making devices ever more powerful, but also by a steady stream of even smaller, cheaper, and less energy-consuming "smart things" that enable new features and greater automation at home, in transportation [Sye+12], smart factories [Zue08; Zue10] and cities [Zan+14]. Primarily, miniaturization and cost reduction of Microcontroller Unit (MCU) and System on Chip (SoC) designs have enabled the creation of almost ubiquitous smart devices, from smart thermostats and appliances to smart phones and embedded car entertainment systems. Besides private applications of embedded platforms, they are employed to enhance the degree of industrial automation and in particular, to realize "Industry 4.0" [Jaz14]. Generally in the industrial domain, embedded devices are increasingly used as integral part of more complex Cyber-Physical Systems (CPS) [LS16]. CPS are commonly leveraged in production systems, for the purpose of process monitoring and controlling or to realize responsive quality management [LCK16]. Substituting traditional components in this domain such as programmable logic controllers (PLC) and remote terminal units (RTU), embedded systems are employed to sense and control physical processes as well as communication interfaces for (existing) industrial automation systems to the Internet or an internal network [Jaz14].

Unfortunately, the novelty of this field combined with dominating market forces to minimize cost and time-to-market also has a devastating impact on security. In particular, one major concern is that these devices often lack hardware as well as software implementations of sufficient security mechanisms [Sch14b; VT12]. As a result, the proliferation of such "smart" devices leads to a constant discovery of new security vulnerabilities [Her+14; Cos+14; Def15; Gre15; Fos+15]. Moreover, constraints on the available memory and computational power have an impact on the security of these devices. Means to provide robust identification and authentication of involved devices and mechanisms to securely store long-term cryptographic keys, while minimizing the chances of their illegitimate extraction or access, are particularly demanding tasks for this device class. Besides interconnected platforms, the ability to recognize and establish trust in embedded devices is even becoming relevant for ultra low-cost storage devices, including SD-cards and USB sticks that are exchanged with third parties and hence can be infected or replaced by malicious hardware in order to attack the host [b313; NL14]. Moreover, Bluetooth devices may offer an even larger attack surface since typically employed security mechanisms were shown to be insufficient [Rya13; SW05].

In order to establish trust in these resource-constrained devices, respective security solutions must be based on realistic assumptions concerning the specific hardware capabilities of these devices. Hence, a meaningful approach of designing security protocols and applications towards the peculiarities of low- cost and embedded devices begins with defining requirements

of such solutions, taking into account the limitations imposed by the underlying platforms. A first requirement is imposed by the device class considered in this thesis, namely Commercial Off-The-Shelf (COTS) embedded devices, which usually do not implement secure hardware such as Trusted Platform Module (TPM), Intel Software Guard Extensions (SGX) or ARM TrustZone for economic reasons. Hence, secure protocols and applications cannot rely on dedicated secure hardware, such as TPM or a Trusted Execution Environment (TEE). Instead, they are usually restricted to standard hardware components. Hereafter we denote standard hardware as such components that are produced for general-purpose usage and which are not application specific. Common examples for standard hardware components comprise Static Random-Access Memory (SRAM), Dynamic Random-Access Memory (DRAM), Central Processing Units (CPUs) and Graphics Processing Unit. A second important requirement derives from the very limited computational resources and memory-related capabilities of such devices. In particular, a security solution only qualifies if it exhibits a small memory footprint and if it relies on building blocks that are computationally efficient. Cryptographic protocols that are specifically optimized towards such constrained devices, are commonly denoted as lightweight security protocols [EK07]. Hence, the adoption of classical yet more heavyweight approaches, such as most asymmetric cryptographic systems, is not a viable option for many MCUs-based device types (cf. Chapter 2.2). In particular, for ultra low-cost 8 bit microcontrollers, that are found in smart cards or RFID chips, efficient implementation of traditional cryptographic solutions is a non-trivial task. From the perspective of the memory domain (8 bit MCUs are usually limited to 256 B to 1 kB RAM), implementations of public-key cryptographic systems are indeed feasible, especially when leveraging ECC that uses smaller key sizes compared to RSA, to achieve equivalent security levels [Bro09]. However, the time required for decryption, encryption, signing or verifying a signature can be tremendous. As shown in [Pie00], RSA suffers from computing expensive decryption, which can take up to several hundreds of seconds using a 2048 bit key on an 8 MHz platform. Leveraging ECC, the decryption process was shown to be inefficient on a similar platform, requiring up to 8s using a 193 bit key, with both key sizes of RSA and ECC providing comparable security levels. Further approaches towards efficient implementations of public-key cryptographic systems and signature schemes show similar runtime results, which are in the same order of magnitude [PLP06; LGK10]. In many applications these performance characteristics are not acceptable. Moreover, such devices do not allow for hardware customization after their acquisition "off- the-shelf" and obviously not after their deployment to their field of operation. Thus, a third vital requirement to any security solution applicable to such devices is to be a purely software-based solution, i.e., to not require any hardware modifications. Instead, solutions must build on existing hardware capabilities a well as features provided by the firmware drivers and libraries. In order to establish better understanding of the hardware capabilities of the targeted device class, we provide a detailed description of the device class considered in this thesis in Chapter 2.2. At last, a fourth requirement for successfully addressing the challenge of establishing trust in commercially available embedded devices is to consider the major phases of utilization of such devices firmware<sup>1</sup> and its interaction with remote entities in its entirety. In particular, major distinct execution phases of firmware on embedded devices comprise i) the boot phase conducted by the boot loader, ii) execution phase of the firmware application and iii) authentication towards external interconnected entities. Furthermore, especially in the case of low-end embedded devices, the possibility to attest the level of trust and to re-establish trust in case of being compromised by malware (i.e., "device recoverability") is becoming an increasingly vital requirement. We argue that only a holistic approach that considers all these aspects

<sup>&</sup>lt;sup>1</sup> In this work, we will use the terms software and firmware interchangeably.

that emerge during the interaction with COTS embedded platforms suffices in order to establish trust in said platforms.

With those identified requirements at hand, providing strong security guarantees becomes a challenging task. In this thesis we propose to address these challenges by leveraging the concept of *memory-based intrinsic Physically Unclonable Functions (PUFs)* to provide a hardware-enforced security anchor on low-cost devices, which can be established efficiently and by software-only means. PUFs exploit device-unique physical characteristics of the underlying hardware, that can be used to derive "fingerprints" of hardware components. Based on these device-unique fingerprints, cryptographic keys can be extracted that allow for the subsequent employment of lightweight security protocols and applications on the targeted devices.

Although PUFs have been made a subject of discussion in previous works in the literature, up to now the majority of research has considered PUFs to be a security building block, which has to be added explicitly during the design phase of the chip (i.e., either as part of an Application-Specific Integrated Circuit (ASIC) or Field-Programmable Gate Array (FPGA)) before it can be utilized, in turn requiring a priori design decisions. As a result, most low-cost devices, which are usually optimized towards cost-efficient manufacturing and hence do not allow for modifications of the production process, have not been addressed in existing research.

However, many commercially available devices already contain standard components that can be leveraged for PUF use. In particular, some memory modules already present in COTS devices – specifically SRAM and DRAM – exhibit good PUF behavior, even though such modules were not designed for the purpose of using them as PUFs in the first place. In the first part of this thesis, we investigate whether it is possible to find and utilize existing PUF instances in commercially available low-cost embedded devices. Having found usable PUF instances, the second part of this thesis is dedicated to the development of lightweight security protocols that leverage those PUF instances in order to eventually establish trust in those otherwise unprotected low-cost devices. In particular, we present the following PUF-enabled applications and protocols that provide security for the phases of interaction with embedded low-end devices:

1. Secure boot of the device firmware application.

The presented solution provides a software-only mechanism to guarantee *boot time integrity* of firmware application. For this purpose we leverage the intrinsic SRAM PUF instance, in order to derive a device-unique key, which is subsequently used to decrypt the firmware application by an immutable boot loader. Hence, this solution effectively protects against firmware replacement or extraction on low-end embedded devices.

- 2. Integrity protection during execution. Having secured the loading of the firmware application, a next step is to protect the *execution time integrity* of the application, i.e. to prevent against analysis and modification at runtime. TO this end, we combine the technique of self-checksumming codes with SRAM-based PUFs to protect against modification of the firmware execution and binding of the same to the underlying platform.

- 3. Lightweight mutual device authentication.

We present a very lightweight protocol that allows for *mutual authentication* of heavily resource-constrained devices with an external verifier. While we leverage a novel DRAM-based PUF construction, we avoid computational expensive error-correction, which is traditionally required to derive a robust key from PUF instances and hence would otherwise render PUF usage impractical on very resource-constrained devices. Instead, we leverage

the characteristics of the underlying DRAM-based PUF to realize a more lightweight and robust mutual authentication scheme.

4. Remote attestation and device recovery.

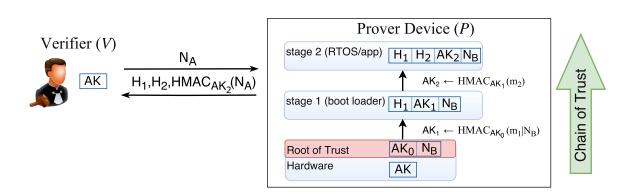

We propose a novel attestation scheme entitled "Boot Attestation", which is the first *remote attestation protocol* that is optimized towards highly resource-constrained off-the-shelf devices. It supports a variety of standard hardware components, intrinsic PUFs amongst others, which are used as a Root of Trust (RoT). From this RoT and based on a symmetric attestation key, software integrity of the individual firmware stages is measured and committed immediately, resulting in a so-called "Chain of Trust". The scheme allows for device recovery after runtime compromise and can be extended to support various read-world use cases, such as third party verification or key provisioning.

## 1.1. Research Goal and Research Question

Addressing the class of commercial embedded devices that lack dedicated secure hardware mechanisms, the research goal of this work is to establish trust in such platforms by leveraging existing on-board memory components as PUF instances, with particular focus on SRAM and DRAM modules. For this purpose, this thesis tries to answer the following research question:

#### Do standard memory components, implemented on commercial off-the-shelf microcontrollers, show physical variations that exhibit PUF-like behavior, such that these components can be exploited as hardware-based security anchors in lightweight security protocols?

Hence, the focus of this thesis lies on the physical variations of said memory components found on COTS embedded devices, which will be analyzed with regards to their PUF characteristics and which subsequently serve as a basis for constitutive security protocols and applications. By focusing on the physical layer, i.e., considering standard hardware components, which are intrinsically part of commercial low-cost platforms as security primitives, we achieve manifold desired properties:

- 1. By focusing on the physical level of standard hardware components, i.e., SRAM and DRAM modules, which can be found on the majority of COTS devices, we achieve a high degree of independence from vendor-specific implementation decisions, including individual layouts of the Printed Circuit Board (PCB), on- or off-chip organization or interaction of functional elements of the MCU that resides at the core of all the considered device classes (cf. Chapter 2.2). Functional elements typically comprise the CPU, memory components, timers and external peripheral components.

- 2. By relying on standard hardware components, we allow for developing secure protocols and applications that help to maintain trust in COTS embedded devices, despite the absence of secure hardware components, which are otherwise required in traditional security solutions [Tru11].

- 3. By carefully designing secure protocols and applications solutions to require software-only modifications, any changes to the hardware are avoided entirely. Hence, implementation of PUF-based security solutions is simplified tremendously, immediately providing support of a broad range of COTS devices.

4. Lastly, we allow for retro-fitting hardware-based security anchors to legacy devices, which are already in-field, in order to deploy supplementary security features.

## 1.2. Methodology

In order to answer the research question and to efficiently realize the research goal, the first part of this work deals with the identification, extraction and evaluation of PUF instances extracted from standard hardware found on COTS embedded devices. The second part of this thesis presents secure software solutions, i.e. secure boot, code integrity protection, mutual authentication and remote attestation, that are based on the PUF instances previously identified. Moreover, the underlying device types are leveraged as evaluation platforms to prove the feasibility and efficiency of the implementations. From this methodical approach a gradual process results as follows:

- 1. In a first step, commercial embedded platforms are identified, which have a large scope of application among typical use cases of IoT and thus are qualified representatives for the targeted device class.

- 2. After identifying wide-spread embedded platforms, means to extract PUF instances from each device's SRAM and DRAM modules are identified. This step involves physically measuring the targeted hardware components in order to extract a significant number of PUF measurements. The extraction process must be software-only, i.e., without requiring any hardware modifications that are usually infeasible on COTS platforms.

- 3. The measurements obtained in the previous step serve as the data set for subsequent evaluation of the identified PUF instances towards various PUF characteristics. Evaluation is done in order to be able to quantify PUF characteristics that have an influence on the security of the overlying protocols.

- 4. Finally, based on those PUF instances that yield positive evaluation results with respect to their PUF characteristics, security protocols and applications were developed in order to show how to establish trust in these devices.

## 1.3. Thesis Outline

Given the research methodology introduced in this chapter, the remainder of this thesis is structured as follows.

Chapter 2 introduces fundamental notations used throughout the remainder of this work. Furthermore, the targeted device class is discussed, focusing on common memory technologies found on such devices, SRAM and DRAM in particular.

The concept of Physically Unclonable Functions is introduced and defined in Chapter 3. Moreover, central properties that are used to assess and quantify PUF characteristics are discussed. Furthermore, basic principles of the three PUF types built from SRAM and DRAM modules are explained. In Chapter 4 we identify a set of device types which are representatives of COTS embedded devices and which serve as evaluation and implementation platforms throughout this thesis. Furthermore, a common software-only approach to extract memory-based intrinsic PUF instance from these devices is presented. Finally, this chapter details the evaluation process of the extracted PUF instances and discusses its results.

After showing the existence of favorable memory-based intrinsic PUF instances on COTS platforms, Chapter 5 presents a first application which builds on these PUF instances. In particular, a lightweight secure boot solution is proposed, that protects against firmware extraction on embedded devices by exploiting SRAM-based PUFs.

Subsequently, Chapter 6 extends the secure boot application by introducing a PUF-based solution that focuses on the protection of the firmware integrity. Again, SRAM-based PUF instances are used as a hardware-based trust anchor, which are combined with the technique of self-checksumming code in order to protect from firmware modifications.

Chapter 7 is dedicated to the task of authenticating a given low-cost device towards a remote server. As there are numerous existing approaches to device authentication for SRAM-based PUFs, this section presents the first lightweight authentication protocol that uses the decay-based DRAM PUF, which was previously introduced in this work.

In Chapter 8 a novel and ultra lightweight remote attestation scheme is presented. As the scheme relies on memory-based intrinsic PUFs, amongst other hardware primitives, it allows for adoption to a wide-spread spectrum of COTS and legacy devices.

Finally, this thesis is concluded in Chapter 9, summarizing the contributions and discussing potential future work.

## Chapter 2

## Preliminaries

n this chapter we discuss important concepts, which will be used frequently throughout this thesis. On the one hand, these concepts will serve as a basis for the evaluation of Physically Unclonable Function (PUF) instances and are used to infer properties of the PUF-enabled protocols. On the other hand, concepts introduced in this chapter illustrate the technical properties of the involved device types and the memory components considered in this work. Since knowledge of these underlying concepts greatly contributes to the understanding of the remainder of this thesis, they are discussed in detail.

In particular, we will first introduce basic mathematical and information- theoretic notations, which will be used extensively during evaluation of the PUF instances in Chapter 4. Next, we model the targeted device class by identifying common hardware capabilities and general properties. Lastly, we detail the physical structure of the investigated memory components, namely Static Random-Access Memory (SRAM) and Dynamic Random-Access Memory (DRAM), in order to provide an understanding of the involved physical effects that result in PUF behavior.

### 2.1. Notations

Throughout this thesis the following notation and definitions are used frequently, mainly to model the characteristics of a PUF or to infer information-theoretical statements about the privacy or security of PUF-enabled applications.

#### Variables, Distributions and Sets

Random variables are written in capital letters, such as *X*. A particular instance of the variable is written in lowercase, i.e., *x*. The set of possible instances of *X* and sets in general are denoted with a calligraphic symbol  $\mathcal{X} = \{x_1, x_2, \dots, x_n\}$ . The probability function of a random, discrete variable *X* is defined as

$$p(x) = Pr(X = x). \tag{2.1}$$

We denote the process of uniformly randomly sampling from a distribution *X* as  $x \stackrel{\$}{\leftarrow} X$ .

#### 2.1.1. Functions and Mappings

We denote a function f that maps elements from X to values of Y as  $f : X \mapsto Y$ . In cases where we expect X to consist of bitstrings of length m and elements of Y to be bitstrings of length n, we write  $f : X^m \mapsto Y^n$ .

#### 2.1.2. Distance and Similarity Metrics

#### Hamming weight

The Hamming weight **HW** is a metric that defines the number of non-zero symbols in a sequence of symbols  $a = \{a_1, a_2, ..., a_n\}$ . In the classical case and in the context of this thesis, *a* is assumed to be a bitstring, such that **HW** depicts the number of non-zero elements of *a*:

$$\mathbf{HW}(a) \stackrel{\text{def}}{=} |\{i \in \{1, 2, \dots, n\} | a_i \neq 0|.$$

(2.2)

#### **Hamming Distance**

The Hamming distance **HD** between two symbol sequences  $a = \{a_1, a_2, ..., a_n\}$  and  $b = \{b_1, b_2, ..., b_n\}$  of same length *n* and generated from the alphabet  $\Sigma$ , denotes the number of positions at which both symbol sequences differ:

$$HD(a,b) \stackrel{\text{def}}{=} |\{i \in \{1,2,\dots,n\} | a_i \neq b_i|.$$

(2.3)

#### Jaccard index

The Jaccard index  $J(\cdot, \cdot)$  is a metric that reflects the similarity of two sample sets A and B. Here, the sample sets can be of unequal size. It is computed as:

$$\mathbf{J}(\mathcal{A},\mathcal{B}) \stackrel{\text{def}}{=} \frac{|\mathcal{A} \cap \mathcal{B}|}{|\mathcal{A} \cup \mathcal{B}|}, \text{ with } 0 \le J(\mathcal{A},\mathcal{B}) \le 1.$$

(2.4)

The Jaccard index is '1' if the sets A and B are identical. Likewise, the index is '0' if both sets share no common elements.

#### 2.1.3. Entropy

In order to make statements about the information content, i.e., entropy of a PUF, we introduce the following notations. The notation 'log' refers to the base-2 logarithm.

#### Shannon entropy

The Shannon entropy [Sha48] H(X) of a discrete, random variable X is denoted as

$$\mathbf{H}(X) = -\sum_{x \in X} p(x) \log p(x).$$

(2.5)

#### **Binary entropy**

Suppose that *X* is a binary random variable, i.e.,

$$X = \begin{cases} Pr(X=1) = p \\ Pr(X=0) = 1 - p. \end{cases}$$

(2.6)

The binary entropy function  $H_b(X)$  is written as

$$\mathbf{H}_{\mathbf{b}}(p) \stackrel{\text{def}}{=} -p \log p - (1-p) \log(1-p). \tag{2.7}$$

#### **Min-entropy**

Furthermore, for a binary source X, we define the min-entropy [Rén+61]  $\mathbf{H}_{\infty}(X)$  as

$$\mathbf{H}_{\infty}(X) = -\log(\max((p(0), p(1)))), \tag{2.8}$$

where p(0) and p(1) are the probabilities of P(X = 0) and P(X = 1), respectively. Note that the min-entropy denotes the greatest lower bound on the entropy for *X*.

#### **Mutual information**

The mutual information [CT12] I(X, X') between two discrete variables X and Y is denoted by

$$\mathbf{I}(X;Y) = \sum_{y \in Y} \sum_{x \in X} p(x,y) \log\left(\frac{p(x,y)}{p(x)p(y)}\right).$$

(2.9)

Informally, it defines the amount of information that can be obtained about a variable *X* through a second variable *Y*. Here, p(x, y) denotes the joint probability function of *X* and *Y*.

## 2.2. Common Capabilities of Low-Cost Devices

#### 2.2.1. Hardware

In the following section, we will define the classes of devices considered throughout this thesis, as selected device types of this class will serve as a basis for evaluation of PUF instances. Furthermore, they will be used as proof-of- concept platforms for the implementation of PUFenabled security applications. For this purpose we first outline the capabilities of respective device types, regarding their computational and memory faculties and subsequently identify hardware components that are common to devices of this class. At last, we detail the principles of SRAM and DRAM, as two widely-used memory technologies on Microcontroller Unit (MCU)-based platforms.

| Device<br>Class | Processing Power  | Volatile Memory<br>(SRAM) | Non-Volatile Memory<br>(Flash / EEPROM) | Usage Scenario                                                            |

|-----------------|-------------------|---------------------------|-----------------------------------------|---------------------------------------------------------------------------|

| Class-0         | $\leq$ 32 MHz     | $\leq 6  \text{kB}$       | $\leq$ 32 kB                            | home automation, sensor<br>networks, smart objects                        |

| Class-1         | 32 MHz to 120 MHz | 8 kB to 32 kB             | 32 kB to 256 kB                         | home automation, indus-<br>trial environments, net-<br>working appliances |

| Class-2         | ≫32 MHz           | 32 kB to 512 kB           | ≫1 MB                                   | smart car infotainment,<br>wearable devices, indus-<br>trial environments |

Table 2.1.: The three classes of embedded devices evaluated in this thesis.

We consider the space of so-called *Commercial Off-The-Shelf (COTS) embedded devices*, which are increasingly deployed as important building blocks of the Internet-of-Things (IoT).

The predicate *COTS* mainly refers to the property that such devices are manufactured in mass production to yield large quantities. Hence, they are commercially available and are comparably cheap to obtain. Furthermore, they tend to be adaptable to various applications that share similar performance requirements.<sup>1</sup> Their cost-efficiency as well as their versatility commonly lead to their high dissemination.

The term *embedded devices* lacks a rigorous definition and incorporates various device classes which observe different hardware facilities. The main common characteristic of the device types considered as embedded devices is the much higher restriction of their (hardware) capabilities, compared to desktop PCs, laptops, servers and alike. Hence, the embedded attribute suggests that these devices tend to be single-purpose devices with often the minimum memory required to meet their intended application, in order to minimize manufacturing cost and power consumption. While these restrictions manifest in constraints on processing resources, available memory, electrical energy consumption and interconnectivity, the main characteristic of embedded devices from a security point of view lies in the unavailability of dedicated secure hardware. However, there are classes of embedded devices that have quite diverse characteristics, i.e., varying processing power (i.e., MCUs with up to 32 MHz vs. System on Chips (SoCs) running at 1 GHz) or which implement different architectures (4 bit vs. 32 bit).

In order to introduce some structure to this rather undifferentiated pool of embedded devices and to provide a way of relating the evaluated device types to a set of common hardware capabilities, we introduce three device classes. For this purpose we follow the categorization of [BEK14] which introduced the notion of *constrained* devices. The spectrum of embedded devices extends from the class of ultra low-cost MCU-based class-0 devices (e.g., used in Radio-Frequency Identification (RFID) tokens) through to conventional MCUs (often deployed in industrial environments) that belong to class-1, to class-2 devices that resemble sophisticated, complex SoC platforms (i.e., as part of in-car infotainment systems). Table 2.1 provides an overview of the characteristics and hardware capabilities associated with each device class. Given the vast variety of device types that observe numerous configurations of processing power, volatile memory, non-volatile memory (i.e., flash end Electrically Erasable Programmable Read-only Memory (EEPROM)), the presented numbers do not act as sharp class boundaries but are rather used as orientation values indicating the capabilities of the corresponding hardware characteristic.

<sup>&</sup>lt;sup>1</sup> In contrast to high-priced hardware, which is made for general purpose usage, most embedded devices are restricted to a subset of applications, due to their limited hardware capabilities.

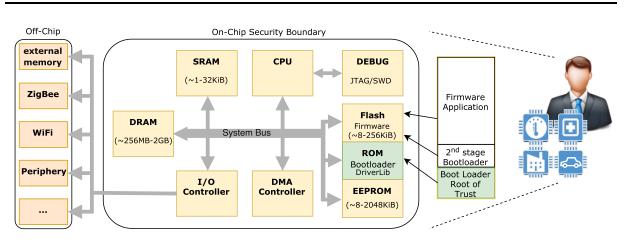

Figure 2.1.: Typical hardware configuration of an embedded MCU.

Although SoC-based device types are more complex in their structure and have better hardware capabilities compared to class-0 devices, at the core of all embedded devices resides an MCU, featuring the Central Processing Unit (CPU), memory components, I/O controllers and a debugging interface on a single integrated circuit. Ultimately, the most basic device types belonging to class-0 entirely consist of a single MCU. In contrast, class-2 device types are usually made up of several MCUs. The MCU is highly-integrated, implementing SRAM, flash and sometimes EEP-ROM as part of a single die package, i.e., such components are usually "on-chip" (cf. Figure 2.1). Although DRAM is currently implemented as an external component, i.e. "off-chip", we foresee that due to the fast maturation of embedded DRAM technology, future embedded devices will also feature DRAM as an on-chip component (cf. Section 2.3). The high level of integration of key components within a single chip creates an effective protection against attempts to physically probe, modify or entirely replace such components. Compared to a system which implements key components as isolated packaged modules (i.e., a laptop or server), an invasive attacker who wants to tamper with on-chip components of an MCU will be required to put in much more effort in terms of time and hardware equipment. One of the attacker's challenges is to de-package the core chip, keeping the highly interconnected components functional, in order to get access to the components in the first place. This task is becoming even more challenging if state of the art circuit packaging technologies such as Package-on-Package (PoP) are used [Yos+06]. In this case, functional components such as the CPU, SRAM and other on-chip components are vertically organized in a stacked fashion. Hence, the underlying design principle of MCUs and SoCs of high integration establishes an innate security boundary against basic physical adversaries.

The majority of MCUs follow the Reduced Instruction Set Computer (RISC) design principle that allows for less cycles per instruction by using fewer but more general-purpose instructions instead of a higher number of more complex instructions as in the Complex Instruction Set Computer (CISC) architecture. <sup>2</sup> More sophisticated class-2 SoC platforms, such as the OMAP4460 (cf. Chapter 4.2), even implement multi-core architectures. However, even the simplest class-0 MCUs implement some form of parallelism as most microcontrollers follow a pipelined architecture.

<sup>&</sup>lt;sup>2</sup> Note however, that due the steadily increasing complexity of MCUs, a strict discrimination between both architectures is not always possible. For example, ARM processors, being RISC processors, allow for different instruction sizes by using the ARM Thumb mode, which is a feature of CISC processors.

### 2.2.2. Firmware

On the software side, MCUs are often programmed bare-metal, with the Software Development Kit (SDK) building necessary drivers and libraries into a single application binary (firmware image). The term firmware usually refers to a fixed piece of software, usually not intended to be changed by the user [AGS12]. The firmware image consists of a *boot loader* part and the application itself, denoted as *firmware application*.

The boot loader part initializes basic hardware components, i.e., it configures the clock, initializes the main memory and sets up key peripherals. Class-0 and class-1 devices usually rely on a very compact single-staged boot loader that (after hardware initialization) merely sets up the stack and calls the firmware application, which usually consists of a main function and a loop that continuously executes the application logic at its core. In contrast, class-2 device types often implement a much more complex multi-staged boot loader. Here, the first stage boot loader is small enough to reside in the on- chip SRAM and, amongst others, sets up the CPU, configures the main memory subsystem, initializes and synchronizes various timers and finally sets up external peripherals before invoking the second-stage boot loader. This part is too big to fit into SRAM in its entirety and hence is executed from external DRAM. It is in charge of configuring higher-level functionalities of the embedded device and configuration of the residual peripherals (USB subsystem, networking etc.). One of the most popular multi-staged open source boot loaders is u-boot [Eng02], which is also the standard boot loader implementation of some of the evaluated class-2 device types, including the PandaBoard and the Intel Galileo (cf. Section 4.2). U-boot consists of a first- and a second-stage boot loader. Whilst the first stage initializes core functionalities, the second stage boot loader configures DRAM and external components and eventually executes the application part of the firmware.

The application part implements the main functionality and algorithms of the firmware. The firmware image is stored in Non-Volatile Memory (NVM), usually flash memory or EEPROM. Conventionally, there are two distinct sections of NVM that are dedicated to either the boot loader or the application part of the firmware. While the memory range dedicated to the boot loader is very limited in terms of memory (usually not more then 6 kB to 10 kB on class-1 device types), the entire remaining NVM address space can be used to store the firmware application. On most device types both sections can be configured individually regarding their memory access controls. This is because the boot loader is usually regarded as the Root of Trust (RoT), i.e., the trust anchor in order to boot strap the platform from an integer initial state. Accordingly, the boot loader is usually "locked-down" once it is written to the respective memory region by disabling write-access to it. The firmware application is therefore typically initialized by such an immutable firmware boot loader, which additionally reduces the risk of permanently disabling a device ("bricking"). In order to allow for modification of the boot loader (usually after exceptional events, such as device recovery), most platforms allow for programming via low-level interfaces such as Joint Test Action Group (JTAG). Hence, many device types provide customization of these early stage(s) of boot.

Depending on the underlying platform and application scenario, there are different approaches regarding the firmware's architecture. Especially in scenarios that focus on low-power (i.e., sensor networks or home automation) or low-cost (i.e., wearables or smart gadgets) mostly MCU-based class-0 device types are employed. Such devices traditionally implement a single-threaded firmware application that continuously executes its functionality within a loop. Systems that operate in time-critical environments (mostly class-1 device types, i.e., as part of industrial control systems or avionics) often implement more complex kernel-based Real-Time

Operating System (RTOS), which allow multitasking by means of event-driven scheduling of multiple tasks [Edi16]. Class-2 SoC-based device types are able to implement an entire rich operating system.

### 2.2.3. Security Issues

While embedded COTS devices are significantly restricted regarding their hardware facilities, which manifest itself in constraints on processing resources, available memory, electrical energy consumption and interconnectivity, the main characteristic of embedded devices from a security point of view lies in the unavailability of dedicated secure hardware. More powerful computing platforms, such as up-to-date tablets, laptops, desktop PCs and servers traditionally rely on Trusted Platform Modules (TPMs) [Tru11] in order to establish a hardware-based RoT and to provide a foundation for secure protocols and applications. TPM is based on a trust anchor in hardware, the TPM-chip, and provides a set of cryptographic functionalities and protocols. Alternatively, current Intel processors implement the company's own approach towards a Trusted Execution Environment (TEE), called Intel Software Guard Extensions (SGX) [Int16b]. Leveraging an extended instruction set, SGX implements so-called enclaves that act as secure "compartments" used to execute applications in a secure manner. SGX protects the integrity and confidentiality of code and related data run within the enclave from a potentially malicious operating system and further. For this purpose SGX allows to remotely attest the state of an enclave, supports key provisioning and sealing of data communicated with external parties. However, currently only the most powerful processor types implement Intel SGX, omitting Intel's embedded product line. Furthermore, as discussed by Costan and Devadas [CD16], Intel's licensing model, which is integrated in the SGX architecture by means of the Launch enclave and associated patents, suggests that the SGX technology can only be used by a party which maintains some sort of business relationship with Intel. Furthermore, a series of vulnerabilities that can lead to key compromises were discovered recently [Sch+17b]. In the mobile world, the prevailing approach of providing a TEE world is ARM's TrustZone technology [ARM17]. TrustZone leverages an extended bit line in order to create and distinguish between a normal and a secure "world". Using hardware resources, TrustZone provides individual sets of memory, peripheral components and software states for applications running in both worlds. Secure context switching guarantees that no data from the secure world is leaked to the normal world's processes. However, currently only ARM's non-lightweight application processors (ARM Cortex) support TrustZone technology.<sup>3</sup>

Hence, available embedded devices fail to implement dedicated hardware-based RoTs. Furthermore, already deployed devices cannot be retro-fitted with possible future security mechanisms once they are available to the market. Given the high dissemination of such devices and the market force of minimizing costs, their replacement by more secure platforms is highly unlikely. In order to fill this security gap, we propose to use standard hardware components, existing in virtually all computing platforms to realize a hardware-based RoT. In particular, we leverage the manufacturing variabilities of SRAM and DRAM components. Next, we present the principles of both technologies.

<sup>&</sup>lt;sup>3</sup> ARM recently announced support for a future generation of low-cost architectures, the Cortex-M23 and M33

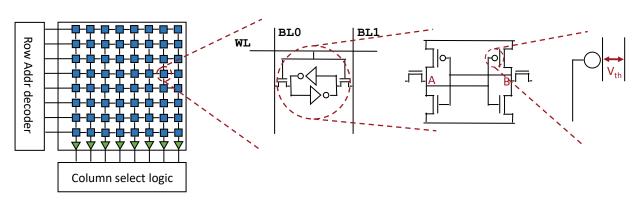

Figure 2.2.: An SRAM array (a) that consists of SRAM cells that form two cross-coupled inverters (b). The structure of a 6T-SRAM cell in detail (c) and the threshold voltage  $V_{th}$  of the corresponding transistor (d).

## 2.3. Memory Technologies Found on Low-Cost Devices

Common on-die memory components that can be found on the majority of low-cost MCUs comprise local instruction and data caches, SRAM<sup>4</sup>, flash memory and EEPROM. Recently, embedded on-chip DRAM (eDRAM) technology has become part of newer embedded devices generations. Due to its promising technology and fast improvement [Bar+10; Fre+15; Iye+05; Kal+10; Pei+14; PTT17], we anticipate that DRAM will most likely become a standard on-die element of future low-cost MCUs generations.

Below we will provide background information on the physical structure of SRAM and DRAM technologies, which is necessary to understand the functionality of the PUF types extracted from both technologies, as introduced in Chapter 3. Although common memory components of low-cost COTS MCUs also comprise flash memory and EEPROM – both which have been shown to exhibit PUF-like behavior [Pra+11; Roa+15; Wan+12] – the focus of this work lies on SRAM and DRAM modules.

### 2.3.1. Static Random Access Memory

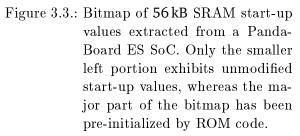

Static Random-Access Memory (SRAM) is a standard volatile memory technology that stores information for as long as operational voltage is applied. Although SRAM can be constructed in different ways, the prevailing construction uses six transistors in order to construct a single SRAM cell (6T-SRAM-cell), based on Complementary Metal–Oxide–Semiconductor (CMOS) technology. In this design, four transistors are used to store a single bit, whereas two additional transistors are used to control access to the SRAM cell for reading or writing purposes.

The four storage transistors form two cross-couples inverters (A and B in Figure 2.2), that reinforce each other, effectively creating a positive feedback loop. Once the threshold voltage  $V_{th}$ is attained, the respective transistor starts to conduct. Due to manufacturing variations, usually there exists a mismatch between the threshold voltages of both cross-coupled inverters. The inverter with the smaller  $V_{th}$  conducts first and initiates the feedback loop. There exist two stable states, used to store a logic zero or one. A third metastable state exists only for a very short

<sup>&</sup>lt;sup>4</sup> On many embedded platforms, CPU caches are implemented using SRAM technology.

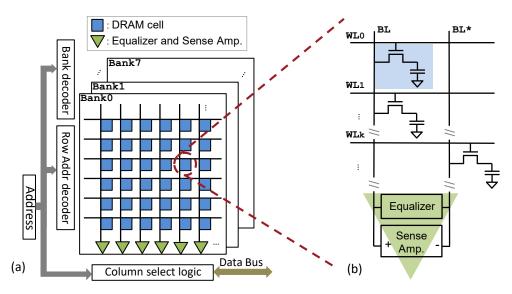

Figure 2.3.: Schematic of DRAM cells (a). DRAM cell organization (b).

time, after supply voltage is applied (i.e., at start-up of the SRAM module). Minuscule deviations from the metastable state are amplified by the feedback loop, pulling the cell to one of the stable states, a process also referred to as "ramp-up". A schematic description of a 6T-SRAM cell is given in Figure 2.2.

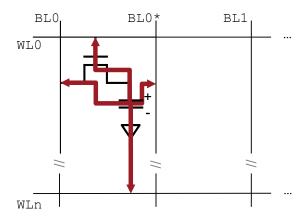

### 2.3.2. Dynamic Random Access Memory

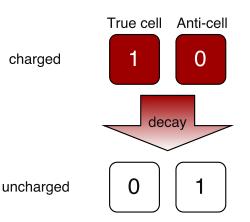

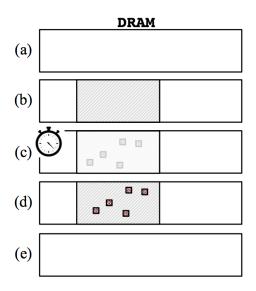

A single DRAM cell stores a bit charge in a capacitor that can be accessed through a transistor. DRAM cells are grouped into cell arrays, where each row of the array is connected to a horizontal word-line and DRAM cells in the same column are connected to the same bit-line. All bit-lines are coupled to equalizers and sense-amplifiers that amplify voltages on bit-lines to such level that can be interpreted as logical zeros or ones. The structures of a DRAM cell array and a single DRAM cell are depicted in Figure 2.3.