JOURNAL OF NANO- AND ELECTRONIC PHYSICS Vol. 5 No 1, 01021(5pp) (2013) Журнал нано- та електронної фізики Том **5** № 1, 01021(5сс) (2013)

# Electrical Characterization of TiO<sub>2</sub> Insulator Based Pd / TiO<sub>2</sub> / Si MIS Structure Deposited by Sol-Gel Process

Kumar Shubham\*, R.U. Khan

Department of Electronics Engineering, Indian Institute of Technology (Banaras Hindu University), 221005 Varanasi, India

(Received 01 January 2013; published online 28 March 2013)

Electrical characterization of a Pd / TiO<sub>2</sub> / Si MIS structure has been reported in this paper. The TiO<sub>2</sub> layer has been deposited on *n*-Si substrate by spin coating sol-gel process using Titanium Tetraisopropoxide [Ti(OC<sub>3</sub>H<sub>7</sub>)<sub>4</sub>]. The current-voltage and capacitance-voltage characteristics were studied at room temperature (300 K) by applying the dc bias gate voltage swept from -3 to 3 V for the frequency range of 50 kHz to 1 MHz. The study reveals that the capacitance in the accumulation region has frequency dispersion in high frequencies (> 10 kHz) which is attributed to leakage behavior of TiO<sub>2</sub> insulating layer, interface states and oxide defects. Different models of current conduction mechanism have been applied to study the measured data. It is found that Schottky-Richardson (SR) emission model is applicable at low bias voltage, Frenkel-Poole (FP) emission model at moderate bias voltages while Fowler-Nordheim (FN) tunneling dominates at higher bias voltages. TiO<sub>2</sub> based MIS devices having high dielectric constant and good interface quality with Si substrate are expected to play a major role in microelectronic applications.

Keywords: TiO<sub>2</sub>, Thin film, Sol-Gel, MIS structure.

PACS numbers: 68.35. bt, 68,55. aj, 73.61. Ng

#### 1. INTRODUCTION

Titanium dioxide (TiO<sub>2</sub>) films are being sought as a competent alternative dielectric to silicon dioxide (SiO<sub>2</sub>) films in ultra large-scale integration (in sub 100 nm silicon technology) because of its much higher dielectric constant and higher breakdown strength than those of SiO<sub>2</sub> [1]. At such a low dimension, SiO<sub>2</sub> becomes vulnerable to direct tunneling which dramatically increases the leakage current [2]. A number of attempts have been made to find alternative oxides with high dielectric constant (ĸ) such as HfO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> allowing to increase gate capacitance thereby negating the associated leakage effects. Among these high-k dielectric materials, TiO<sub>2</sub> is being seen as an attractive candidate in order to replace the conventional oxide material SiO<sub>2</sub>. Because TiO<sub>2</sub> possesses higher dielectric constant approximately ranging from 10 to 80 depending on the deposition techniques, annealing temperature and annealing ambiance [3, 4] of the former. The electrical properties of the insulator (TiO<sub>2</sub>) layer have been found to be affected by the growth technique owing to the reactions at the insulator / Si substrate interface and metal / TiO2 interface. Furthermore, TiO2 based MIS structures exhibit relatively large leakage currents. This may be attributed to relatively small bandgap of ~ 3.5 eV of TiO<sub>2</sub>, low electron affinity ~ 4 eVand low band offset with silicon [1, 3-4].

A number of thin film deposition techniques are employed in the formation of  $TiO_2$  thin film, including RF- sputtering [5], Metal-organic chemical vapor deposition (MOCVD) [6], E-Beam Evaporation [7], Chemical Vapor Deposition [8] and Sol-Gel process. The Sol-Gel process is becoming popular to prepare thin films coating using simple equipment. The interest in application of Sol-Gel method is due to several advantages including homogenous layers on various substrates at low cost, ease of composition control, large area coatings and tailoring of refractive index. The thickness and the porosity of the film can be easily controlled by changing the concentration of the Sol-Gel. Large surface areas can be coated by spin or dip coating. The Sol-Gel processes are particularly efficient in producing thin, uniform and multicomponent oxide layers of many compositions on various substrates, including Si substrate [9].

The electrical properties of gate dielectrics are usually characterized by capacitance-voltage (C-V) and current-voltage (I-V) measurements in MIS devices. The oxide / semiconductor interface and current transport mechanisms are the factors that determine the effect of interface states on MIS based devices. The performance, reliability and compatibility of the MIS devices depend mainly on the formation of the insulating layer, natives at the MIS interface, interface states  $(N_{SS})$  at insulator / semiconductor interface and series resistance  $(R_S)$ . Besides, the frequency factor also affects the electrical properties of these devices [10].

In this paper we have studied electrical properties of  $TiO_2$  based Pd/TiO<sub>2</sub>/*n*-Si MIS structures by conducting capacitance-voltage (C-V) and conductance-voltage (G-V) measurements for different high frequencies at room temperature. Charge flow mechanisms were determined from current-voltage (I-V) measurements on MIS structures.

### 2. EXPERIMENTAL

TiO<sub>2</sub> thin film based MIS capacitor was fabricated on <100> *n*-type Si (1-6  $\Omega$ ·cm) substrate at room temperature. The Si wafer was cleaned by using standard procedures and then loaded in spinner system to deposit TiO<sub>2</sub> thin film through spin coating process [11]. The procedure for the preparation of TiO<sub>2</sub> thin film, involved the dissolution of 12 cc Titanium Tetrai-

2077-6772/2013/5(1)01021(5)

kshubham.rs.ece@itbhu.ac.in

sopropoxide [Ti (OC<sub>3</sub>H<sub>7</sub>)<sub>4</sub>, ex. Ti  $\ge$  98 % Merck] in 170 cc Isopropyl alcohol [CH<sub>3</sub>CH(OH)CH<sub>3</sub>, 99.7 % Merck]. The solution was kept on a magnetic stirrer for 1 h. As a final step, a few drops of Hydrochloric acid [HCl, 2M35 % Merck] were slowly added in the solution and after each additive component is added, the final solution was subjected to the magnetic stirrer for 3 h. The solution was aged at room temperature for one day before deposition. The films were inserted into a furnace and post annealed at 500 °C temperatures in O2 atmosphere for 30 minutes after deposition. The thickness of the deposited films were determined using an ellipsometer ( $\lambda = 633$  nm). The Pd / TiO<sub>2</sub> / Si MIS structure was developed by metalizing with palladium (~ 70 nm) using mask with circular holes of 1 mm diameter on top of the TiO<sub>2</sub> thin film by the vacuum vapor deposition technique using vacuum coating unit (model No.12A4D Hind VAC, India). Later on, whole back side of the Si substrate was first metalized with titanium (~ 40 nm) and then with aluminum (~ 600 nm) for the ohmic contact. Final annealing of Pd / TiO<sub>2</sub> / Si MIS structure had been done in the furnace at 450 °C for 7 minute in nitrogen ambiance to achieve proper front and back contacts. The Hewlett Packard, LCR meter (model No. HP-4284, USA) was used to measure (C-V) and (G-V) characteristics at room temperature with a 100 mV ac sweeping signal. DC leakage current through the structure was measured as a function of the bias voltage using semiconductor device analyzer (Agilent Technology, B-1500 A).

#### 3. RESULTS AND DISSCUSSION

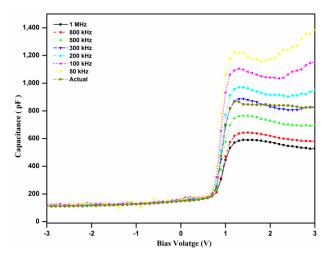

The electrical properties of the thin film type capacitor depend upon the crystalline structure and defects of the films. Note that the defects of the films depend on the post-deposition annealing temperature and ambiance. The thickness of TiO<sub>2</sub> thin films were measured by the ellipsometric technique using a visible laser beam at  $\lambda = 633$  nm at an incident angle of 70 °. The thickness was found  $22 \pm 2$  nm. The surface, optical and morphological properties of TiO<sub>2</sub> thin films have already been reported in our previous work [11]. The deposited structure of TiO<sub>2</sub> thin film was found porous in nature with anatase crystalline state. The capacitance-voltage (C-V) and conductance-voltage (G-V) characteristics of Pd / TiO<sub>2</sub> / n-Si MIS diode structure measured at different values of high frequencies (50, 100, 200, 300, 500, 800 kHz and 1 MHz) are shown in Fig. 1 and Fig. 2, respectively. All the capacitancevoltage curves contain three distinct regimes: accumulation, depletion and inversion as shown in Fig. 1. The accumulation and depletion regions show dispersion at different high frequencies. In accumulation and depletion regions, the measured capacitances decrease with increasing frequency whereas the changes are negligible in inversion region. Such dispersion in the MIS system may be due to oxide charges at the interface and in the insulator. The main cause for the frequency dispersion in accumulation region of (C-V) characteristics is the formation of an inhomogeneous layer at insulator/semiconductor interface. The (C-V) characteristics were found to be stretched along the voltage axis revealing the presence of both acceptor and donor like

interface traps distributed in semiconductor bandgap [12, 13]. This frequency dispersion of the capacitance in accumulation region is attributed to leaky behavior of the TiO<sub>2</sub> thin film because inhomogeneous layer acts in series capacitance with insulator capacitance.

**Fig.** 1 - C-V characteristic of Pd / TiO<sub>2</sub> / *n*-Si MIS structure at different high frequencies as well as actual frequency

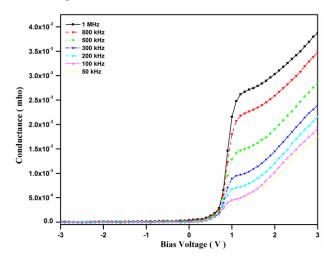

The conductance as a function of gate bias voltage for different high frequencies is shown in Fig. 2. The value of conductance increases with increasing frequency because of insulator capacitance in series with the interface trap resistance-capacitance network. The small peak behavior in the (G-V) characteristics indicates the presence of interface states.

Fig. 2 – G-V characteristic of Pd /  $\text{TiO}_2$  / *n*-Si MIS structure at different high frequencies

The frequency error can be minimized by measuring the series resistance ( $R_s$ ) and applying a correction in measured values of (C-V) and (G-V) characteristics for desired information. When the MIS structure is biased into accumulation region the frequency-dependent properties of MIS devices can be described via the complex impedance as given by [14]

$$Z_m = \frac{1}{G_m + j\omega C_m} \tag{1}$$

ELECTRICAL CHARACTERIZATION OF TIO2 INSULATOR...

The series resistance is the real part of the complex impedance which is given as

$$R_S = \frac{G_m}{G_m^2 + (\omega C_m)^2} \tag{2}$$

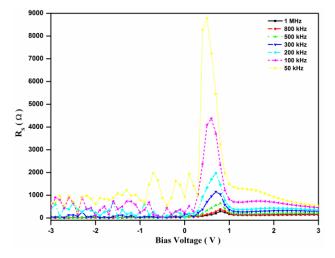

where  $C_m$  and  $G_m$  are the measured capacitance and conductance in the accumulation region. The values of  $R_S$  were calculated as a function of gate bias voltage for the frequency range 50 kHz to 1 MHz at room temperature using Eq. 2 (Fig. 3). It is seen that there is a clear peak of  $R_S$  in each curve shown in Fig. 3. The peak of  $R_S$  increases as the frequency decreases and peak almost disappears at sufficiently high frequencies. Such behavior of  $R_S$  is attributed to the particular distribution of interface states ( $N_{SS}$ ) and localized trap charges at Si / TiO<sub>2</sub> interface states and the interfacial insulator layer at the metal-semiconductor interface.

**Fig. 3** – The variation of the series resistance of the Pd /  $TiO_2$  / *n*-Si MIS structure as a function of the bias voltage for various high frequencies

The theory proposed by Yang et al. [15] for frequency-independent capacitance was calculated from the measured capacitance at two different measuring frequencies with quantum mechanical correction accordingly. The value of true frequency-independent capacitance ( $C_{actual}$ ) of TiO<sub>2</sub> thin film is obtained as [15]

$$C_{actual} = \frac{f_i^2 C_i (1 + D_i^2) - f_j^2 C_j (1 + D_j^2)}{f_i^2 - f_j^2}$$

(3)

where  $C_i$  is the capacitance and  $D_i = 1 / \omega_i C_i R_i$  is the measured at a  $f_i$  frequency,  $i \neq j$  and  $R_i$  is the equivalent resistance. The frequency-independent capacitance is found to be compatible to the frequency at 300 kHz and it is also shown in Fig. 1. The interface trap density ( $D_{ii}$ ) has been calculated using Hill's method [16] by considering single frequency (300 kHz) capacitance-voltage (C-V) and conductance-voltage (G-V) characteristics. The interface trap density ( $D_{ii}$ ), fixed oxide charge density ( $Q_i$ ), flat-band voltage ( $V_{Fb}$ ), dielectric constant ( $G_i$ ) and effective oxide thickness (EOT) are  $3.11 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$ ,  $-1.9 \times 10^9 \text{ cm}^{-2}$ , 0.98 V, 17 and 3.98 nm respectively. TiO<sub>2</sub> thin film based MIS structures generally show high leakage current, hence their applications are limJ. NANO- ELECTRON. PHYS. 5, 01021 (2013)

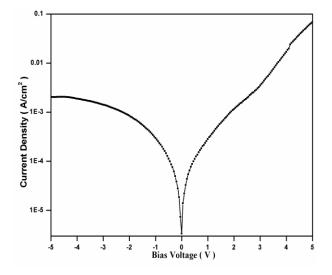

Fig. 4 – Forward and reverse bias J-V characteristic of Pd /  $TiO_2$  / *n*-Si MIS structure

ited to ultralarge-scale integrated circuits. Thus it becomes important to study the various conduction mechanisms in leakage current and causes of breakdown in devices. Fig. 4 shows the (J-V) characteristics of Pd / TiO<sub>2</sub> / n-Si based MIS structure at room temperature. The measurement has been carried out by sweeping the bias voltage from negative side to positive side. The maximum current density is found to be of 0.068 A/cm<sup>2</sup> at 5 V. There are several carrier conduction mechanisms involved simultaneously in transport process in high-k dielectric material such as Schottky-Richardson (SR) emission, Poole-Frenkel (PF) emission and Fowler-Nordheim tunneling. The current conduction mechanism is mainly dependent on the insulating material composition, gate material, film thickness, voltage dependent insulator property and insulating film growth processing. So, it becomes necessary to check the dominancy of current conduction mechanism for TiO<sub>2</sub> thin films grow by sol-gel process. A number of authors have employed these mechanisms with different biasing voltages. It was found that SR emission conduction mechanism involves at lower bias voltages while at higher bias voltages other two conduction mechanisms generally dominate [17-21]. We have put current density-voltage data as per the trends suggested by previous authors. The closely observed results have been mentioned below.

SR emission is dependent on the quality of the metal insulator interface and the insulating film which results from lowering of the barrier due to bias voltage and image forces. The current density owing to SR emission can be expressed as [13, 17, 20-21]

$$J = A^* T^2 \exp\left[-\frac{q}{kT} \left(\Phi_T - \sqrt{\frac{qV}{4\pi\varepsilon_{dyn}\varepsilon_o d_{ox}}}\right)\right]$$

(4)

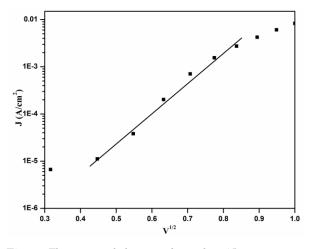

where  $A^*$  is the Richardson constant, k is the Boltzmann constant, q is the electronic charge, T is the temperature,  $\Phi_T$  is the barrier height,  $\varepsilon_{dyn}$  is the dynamic dielectric constant of the oxide,  $\varepsilon_0$  is the permittivity of free space,  $d_{ox}$  is the oxide thickness and V is the applied bias. SR emission has been illustrated in terms of ln(J) versus the square root of the applied voltage  $(V^{1/2})$  using the experimental J-V curve measured at room temperature (Fig. 5). The straight line characteristics at relatively low bias voltage confirm that the conduction of current follows SR emission model.

**Fig. 5** – The curve of the semi logarithm (*J*) versus square root of the positive applied voltage ( $V^{1/2}$ ) TiO<sub>2</sub> film to describe SR emission

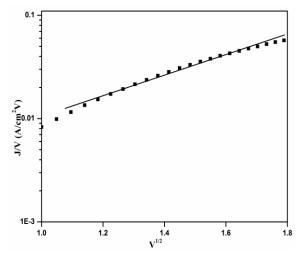

At moderate bias voltage the J-V characteristics of MIS structure is the best fitted by FP emission model. FP emission is associated with field enhanced thermal excitation of charge carriers from traps. So mechanism of FP emission is bulk limited and depends on traps within the insulator. The expression for the FP current density is given as [13, 17-21]

$$J = A_{Pf} V \exp\left[-\frac{q}{kT} \left(\Phi_T - \sqrt{\frac{qV}{\pi\varepsilon_{dyn}\varepsilon_o d_{ox}}}\right)\right].$$

(5)

The  $\ln(J/V)$  versus the square root of the applied voltage  $(V^{1/2})$  obtained from the experimental J-V curve is shown in Fig. 6. The straight line characteristics at moderate bias voltage confirm the validity of FP emission model. Other researchers reported that the self-consistent dynamic dielectric constant  $\varepsilon_{opt} < \varepsilon_{dyn} < \varepsilon_{static}$  can ensure the type of current conduction mechanism [22-23]. The optical dielectric constant ( $\varepsilon_{opt}$  is determined from refrac- $TiO_2$ tive index (n)of thin film.  $\varepsilon_{opt} = n^2 = 2.23 \times 2.23 = 4.97$ , measured by ellipsometer (Gaertner scientific corporation, Chicago) with a wavelength of 633 nm.  $\varepsilon_{dyn}$  can be determined from the slope of a linear portion of curves of SR and FP emission mo-dels. The static dielectric constant ( $\varepsilon_{static}$ ) is obtained from C-V characteristics of the MIS structure. The dynamic dielectric constant extracted from the slop of plot  $\ln(J)$  versus  $V^{1/2}$  for SR mechanism and slop of plot  $\ln(J/V)$  versus  $V^{1/2}$ is used in the case of the FP mechanism. FP analysis was found to be 68.7 which is higher than static dielectric constant while for SR analysis the value was found to be 15.5 consistent with the expected range of values. The linearity observed in the slopes suggests that current conduction takes place by both the emission processes but SR emission is dominated at room temperature.

**Fig. 6** – The curve of the semi logarithm (J/V) versus square root of the positive applied voltage  $(V^{1/2})$  for the TiO<sub>2</sub> film to describe FP emission

At high bias voltage role of tunneling process in the conduction of current cann't be ruled out. FN tunneling model is used to verify the tunneling through the insulator. The expression for FN tunneling is given as [13, 17-19]

$$J = V^2 \exp\left[-\frac{b}{V}\right],\tag{6}$$

where b is a constant given by

$$b = \frac{8\pi \sqrt{2m^* m_o (q\Phi_T)^3}}{3qh} d_{ox}$$

(7)

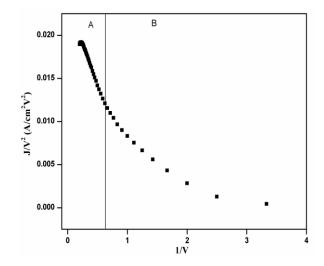

$m^*$  is the tunneling effective mass of the charge carrier in the tunnel barrier,  $m_0$  is the free electron rest mass, his the Planck's constant and  $\Phi_T$  is the barrier height of oxide. The FN model based on tunneling mechanism is applied to  $\ln(J/V^2)$  versus the reciprocal of the applied voltage (1/V) curve as shown in Fig. 7. The straight line

**Fig.** 7 – The curve of the semi logarithm  $(J/V^2)$  versus reciprocal of the positive applied voltage (1/V) for TiO<sub>2</sub> film to describe FN tunneling

Electrical Characterization of  $TiO_2\ Insulator\ldots$

nature of the variation confirms (regime A) the applicability of FN model at larger bias voltage more than 3 V. The current behavior for lower bias voltages (regime B) shows trap-assisted tunneling and quasi-saturation stages.

#### 4. CONCLUSION

The interfacial and electrical properties of Pd /  $\text{TiO}_2$  / *n*-Si based MIS structure were characterized using *C*-*V* and *G*-*V* techniques. The *C*-*V* and *G*-*V* characteristics exhibit frequency dependence due to traps in the insulating layer and at interface. TiO<sub>2</sub> thin films

## REFERENCES

- S.A. Campbell, D.C. Gilmer, X.-C. Wang, M.-T. Hsieh, H.-S. Kim, W.L. Gladfelter, J. Yan, *IEEE T. Electron. Dev.* 44, 104 (1997).

- 2. X. Gou, T.P. Ma, IEEE Electr. Device L. 19, 207 (1998).

- J.C. Tinoco, M. Estrada, B. Iñiguez, A. Cerdeira, *Microelectron. Reliab.* 48, 370 (2008).

- J.C. Tinoco, M. Estrada, G. Romero, *Microelectron. Reliab.* 43, 895 (2003).

- C.-W. Wang, S.-F. Chen, G.-T. Chen, J. Appl. Phys. 91, 9198 (2002).

- N. Rausch, E.P. Burte, *Microelectronic Engineering* 19, 725 (1992).

- M. Lottiaux, C. Boulesteix, G. Nihoul, F. Vernier, F. Flory, R. Galindo, E. Pelletier, *Thin Solid Films* 170, 107 (1989).

- Z. Ding, X. Hu, P.L. Yue, G.Q. Lu, P.F. Greenfield, *Catal. Today* 68, 173 (2001).

- M. Kumar, M. Kumar, D. Kumar, *Microelectron. Eng.* 87, 447 (2010).

- O. Pakma, N. Serin, T. Serin, S. Altındal, J. Phys. D: Appl. Phys. 41, 215103 (2008).

- 11. K. Shubham, P. Chakrabarti, Adv. Sci, Eng. Med. 5, 156 (2013).

### J. NANO- ELECTRON. PHYS. 5, 01021 (2013)

have high dielectric constant with good interface quality with Si. The leakage current conduction is checked with different conduction model and was found to be consistent with previous reported results. In the low bias range SR emission model is found to dominate followed by FP emission model at moderate bias voltage. The effect of tunneling at high voltage is also confirmed by application of FN model. Leakage current is acceptable for most of the electronics circuits. So high quality TiO<sub>2</sub> films deposited by Sol-Gel process can be used to develop a variety of thin film devices for electronic applications.

- 12. R. Razouk, E. Deal, J. Electrochem. Soc. 126, 1573 (1979).

- S.M. Sze, *Physics of Semiconductor Devices* (second ed.) (New York: Wiley: 1981).

- E.H. Nicollian, J.R. Brews, Metal-Oxide Semiconductor (MOS) Physics and Technology (New York: Wiley: 1982).

- 15. K.J. Yang, C. Hu, *IEEE T. Electron. Dev.* 46, 1500 (1999).

- W.A. Hill, C.C. Coleman, Solid State Electron. 23, 987 (1980).

- W. Yang, J. Marino, A. Monson, C.A. Wolden, *Semicond. Sci. Technol.* 21, 1573 (2006).

- L.H. Chong, K. Mallik, C.H. de Groot, R. Kersting, J. Phys.: Condens. Mat. 18, 645 (2006).

- K. Murakami, M. Rommel, V. Yanev, T. Erlbacher, A.J. Bauer, L. Frey, *J. Appl. Phys.* **110**, 054104 (2011).

- 20. S.-F. Chen, C.-W. Wang, J. Vac. Sci. Technol. B 20, 263 (2002).

- M.-K. Lee, J.-J. Huang, T.-S. Wu, Semicond. Sci. Technol. 20, 519 (2005).

- 22. J.J. O'Dwyer, J. Appl. Phys. 37, 599 (1966).

- 23. G.S. Oehrlein, J. Appl. Phys. 59, 1587 (1986).