J. Nano- Electron. Phys. 3 (2011) No1, P. 937-941

© 2011 SumDU (Sumy State University)

PACS numbers: 85.30.Tv, 83.10.Rs

# ROLE OF INTERFACE CHARGES ON HIGH-K BASED POLY-SI AND METAL GATE NANO-SCALE MOSFETS

## N. Shashank, Vikram Singh, W.R. Taube, R.K. Nahar

Central Electronics Engineering Research Institute Council of Scientific and Industrial Research, Pilani-333031, Rajasthan, India

E-mail: Shashank@ceeri.ernet.in

The characteristics of typical sub-100 nm high K gate dielectrics MOSFET with different gate materials are simulated by two dimensional device simulators (ATLAS and ATHENA). The impact of interface charges on the characteristics of Poly-Si and TiN metal gate MOSFETs are investigated. The simulation results shows that, at high interface charge densities, the devices with Poly-Si gate degrade much compared to metal gate MOSFET structures. Emphasis is given to study the mobility degradation which stands as a major hurdle with the implementation of high-k dielectrics in nano-scale devices. The advantages of using Watt model over other models for the extraction of channel mobility is also clearly explained. The performance of the high-k MOSFET with metal electrode and poly-silicon electrode is also compared for various interface state charges.

Keywords: MOSFET, HIGH-K, INTERFACE CHARGES, MOBILITY, METAL GATES.

(Received 04 February 2011)

#### 1. INTRODUCTION

The need for high drivability with low standby power consumption has made the high-k dielectrics indispensable in advanced Complementary Metal Oxide Semiconductor (CMOS) devices. In devices with a channel length of 100 nm or below, the oxide thickness reduces to below 3 nm as per scaling laws. Dielectric thicknesses lower than 3 nm result in quantum mechanical tunneling through the device. This results in tunneling of charge carriers through the gate oxide into the channel and increase in leakage current through the device [1]. Passage of charge carriers through the thin oxide layer may result in creation of traps which further results in oxide degradation and breakdown [2, 3]. For this reason high-k materials are used to physically increase the thickness of the gate dielectric without reducing the effective gate capacitance. However, the use of high K dielectric on MOSFET does not just simply increase the thickness of high K dielectric layer but also affects the characteristics of MOSFETs which needs to be studied in detail. As-deposited HfO<sub>2</sub> layer have a number of defects which results in increased fixed oxide and interface charges [4-5]. These charges are formed during the high-k deposition and/or post deposition processing which affect the device performance. Another unresolved issue that still affects high-k MOSFETs is the reduction of channel effective carrier mobility. Various sources of this degradation like Remote Coulomb Scattering (RCS), Remote soft-optical Phonon Scattering (RPS), interfacial layer thickness, permittivity and 938

roughness have been identified. Yet there has been no consensus on which particular phenomenon dominates [6-7]. Hence, the role of interface charges on mobility and other device figures of merit should be investigated.

#### 2. DESIGN AND SIMULATION

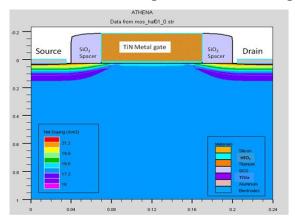

In our study, we have process modeled 0.1 µm n-channel MOSFETs using HfO<sub>2</sub> as gate dielectric material. Two MOSFET structures, one with Poly-Si gate and the other with TiN metal gate electrode were designed using ATHENA 2D simulator of the SILVACO<sup>©</sup> suite. The simulated structures, which are based on fully scaled 100 nm gate length MOSFET's proposed in the International Technology Roadmap for Semiconductors (ITRS) [8], have gate length of 100 nm, with effective oxide thicknesses (EOT) of 3 nm. The dielectric constant of HfO<sub>2</sub> gate dielectric was considered to be 20 [9]. The substrate doping concentration is  $N_{sub} = 3 \times 10^{-17} \, \mathrm{cm}^{-3}$ . The source / drain extensions and deep source/drain junction depths are 45 and 75 nm, respectively. Titanium Silicide is used at source drain contacts to reduce the sheet resistance. The gate work-function for TiN is chosen to be 4.5 and 4.17 for Poly-Si. Once the process modeling is done in ATHENA, the device is simulated in ATLAS to determine the device characteristics. The device parameters were studied for three surface state densities viz.  $5 \times 10^{11}$ Charges/cm<sup>2</sup>,  $1 \times 10^{-12}$  Charges/cm<sup>2</sup>,  $5 \times 10^{-12}$  Charges/cm<sup>2</sup>. The schematic of the design structure with TiN metal gate is as shown in Fig. 1.

Fig. 1 - Simulated structure of TiN gate MOSFET

### 3. RESULTS AND DISCUSSION

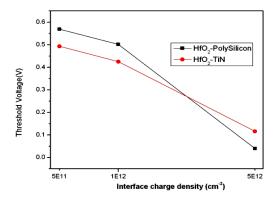

We have investigated the effect of interface charges on the performance of both Poly-Si and metal gated MOSFETs. It is seen from Fig. 2 that threshold voltage of both the design structures decreases with increase in interface charges. The degradation is found to be more in case of Poly-Si gated device structure than device with metal gate at higher interface charge densities. The threshold voltage degradation results in increased current  $(I_D)$  in the devices with increase in interface charge density. The trans-conductance  $(g_m)$ also decreases for the same. Sub-threshold swings (1/S) and drain current  $(I_D)$ increases. On comparison with poly Si electrode, metal gate electrodes seem to

perform better with a more  $I_D$ , transconductance and lower sub-threshold swing. This proves that high-k dielectrics perform better in combination with metal gates. The simulated results are summarized in Table 1.

Fig. 2 - Threshold voltage degradation of Poly-Si and TiN gate MOSFET

**Table 1** – Simulated results of MOSFET structures for various interface charge densities

| Interface                   | Design                    | $V_T$ | $I_D$ | $g_m$ | 1/S         | $R_O$ |

|-----------------------------|---------------------------|-------|-------|-------|-------------|-------|

| Charges (cm <sup>-2</sup> ) |                           | (V)   | _     |       | (mV/decade) | _     |

| 5 × 10 <sup>11</sup>        | HfO <sub>2</sub> -TiN     | 0.49  | 0.73  | 7.12  | 74.48       | 13159 |

|                             | HfO <sub>2</sub> -Poly Si | 0.56  | 0.31  | 5.86  | 85.66       | 20573 |

| 1 × 10 <sup>12</sup>        | HfO <sub>2</sub> -TiN     | 0.42  | 0.79  | 7.15  | 75.59       | 12768 |

|                             | HfO <sub>2</sub> -Poly Si | 0.50  | 0.36  | 5.92  | 85.62       | 19166 |

| $5 	imes 10^{-12}$          | HfO <sub>2</sub> -TiN     | 0.11  | 1.32  | 6.75  | 196.58      | 10488 |

|                             | HfO <sub>2</sub> -Poly Si | 0.04  | 0.81  | 5.59  | 162.5       | 13104 |

Among various challenges presented by high-k gate oxides, mobility degradation has received the utmost attention as it proposes a serious concern when it comes to MOSFET performance. Hence it is very important to accurately model the effective mobility of the carriers in Silicon MOSFET. The total mobility in the inversion layer is given by Matthiessen's rule which is formulated as follows:

$$\frac{1}{\mu_{total}} = \frac{1}{\mu_{ph}} + \frac{1}{\mu_{sr}} + \frac{1}{\mu_{coul}}$$

Where,  $\mu_{total}$  is the total mobility in the inversion region,  $\mu_{ph}$  is mobility due to phonon scattering,  $\mu_{sr}$  is mobility due to surface scattering and  $\mu_{coul}$  is mobility due to coulombic scattering. Numerous models have been included in the ATLAS viz. CVT (Lombardi's model), Watt, modified Watt, SHI (Shirahata's model), CONMOB (concentration dependent low field mobility), FLDMOB (transverse electric field dependent mobility), KLA (Klaassens' low field mobility), modified CVT, YAMAGUCHI and TASCH model. Most of

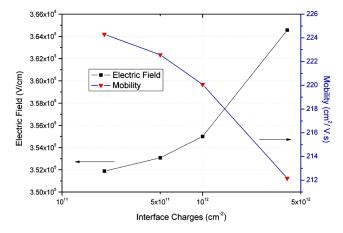

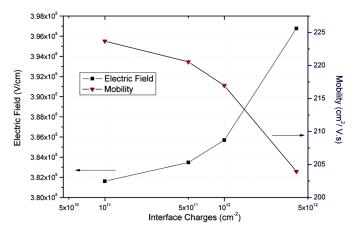

these models have the Matthiessen's rule built within them. However all these models have some trade-off. The Watt [10] model includes all the effects of phonon scattering, surface roughness scattering and charge impurity scattering effects caused by the inversion charge carriers and the ions located in the oxide and interfaces. This was in line with our requirements. Hence this model was selected specifically to show the scattering effects due to interface charges in high-k materials. The role of interface charges on the high field mobility of TiN metal gated and Poly-Si gated MOSFET structures are shown in Fig. 3 and Fig. 4, respectively. It can be observed that the electric field increases with the increase in interface charges while the mobility degrades.

Fig. 3 - Channel mobility of TiN gated MOSFET structure for various interface charge densities

Fig. 4 - Channel mobility of Poly-Si gated MOSFET structure for various interface charge densities

The components affecting the effective mobility of the carriers in the transistor channel are the horizontal electric field, vertical electric field and carrier velocity. As devices are reduced in size, the electric field typically

also increases and the carriers in the channel have an increased velocity. However at high fields there is no longer a linear relation between the electric field and the velocity. When the horizontal electric field is high, the carriers in the transistor channel are accelerated to a maximum velocity. Above a critical field, the velocity is no longer related to electric field and reaches a constant level. This velocity saturation is caused by the increased scattering rate of highly energetic electrons, primarily due to optical phonon emission. This effect increases the transit time of carriers through the channel. When the vertical electric field is high the carriers in an n channel device are strongly attracted to the silicon surface where they rebound. This results in surface scattering causing a reduction in the recombination time and the mobility of the carriers [11]. Surface scattering due to irregularities of the surface near the interface and coulomb scattering due to presence of interface charges very near to the interface can be considered as the main reasons for mobility degradation.

#### 4. CONCLUSION

The role of interface charges on the high-k based MOSFETs have been compared for Poly-Si and metal gate electrodes. At high interface charge densities, the MOSFET with Poly-Si gate are found to degrade more compared to metal gate structures. The replacement of polysilicon with metal gate seems to tackle the mobility degradation issue in high-k based devices to a greater extent. The non-linearity of mobility curves at high electric fields has been studied for various interface trap densities. The Watt model was found to be the most suitable model for mobility extraction, which includes most of the scattering phenomena.

The authors thank the Director, CEERI for his encouragement during the course of this work. Financial support from Council of Scientific and Industrial Research (CSIR), New Delhi, India, under Emeritus Scientist research scheme is greatly acknowledged. The authors would also like to thank members of Sensors and Nanotechnology Group, CEERI, Pilani for their insightful discussions.

#### REFERENCES

- 1. D.S. Jeong, C.S. Hwang, J. Appl. Phys. 98, 113701 (2005).

- 2. T.H. DiStefano, M. Shatzkes, Appl. Phys. Lett. 25, 685 (1974).

- 3. I.C. Chen, S. Holland, C. Hu, *IEEE T. Electron. Dev.*, ED32, 413 (1985).

- E.P. Gusev, E. Cartier, D.A. Buchanan, M. Gribelyuk, M. Copel, H. Okorn-Schmidt, *Microelecton. Eng.* 59, 341 (2001).

- W.J. Zhu, T.P. Ma, S. Zafar, T. Tamagawa, *IEEE Electron Dev. Lett.* 23, 597 (2002).

- 6. O. Weber, F. Andrieu, M. Casse, *IEDM Tech. Dig*, 867 (2004).

- S. Rhee, C.Y. Kang, C.S. Kang, R. Choi, C.H. Choi, M.S. Akbar, J.C. Lee *Appl. Phys. Lett.* 85, 1286 (2004).

- 8. ITRS Roadmap, San Jose, CA: Semiconductor industry association (2007).

- B. Sen, C. Sarkar, H. Wong, M. Chan, C.W. Kok, Solid State Electron 50, 237 (2006).

- 10. J T Watt, Ph.D. Thesis, Stanford University (1989).

- 11. H.J.M. Veendrick, MOS ICs-From Basics to ASICs (Weinheim, New York, Basel, Cambridge, VCH publishers Inc.: 1992).