J. Nano- Electron. Phys. 3 (2011) No1, P. 728-740 © 2011 SumDU (Sumy State University)

PACS number: 85.30.TV

# STRATEGIC REVIEW OF ARSENIDE, PHOSPHIDE AND NITRIDE MOSFETS

# Gourab Dutta, Palash Das, Partha Mukherjee, Dhrubes Biswas

<sup>1</sup> Indian Institute of Technology-Kharagpur Kharagpur, West Bengal 721 302 E-mail: gdutta.iitkgp@gmail.com

Metal oxide semiconductor field effect transistor used as an amplifier and switch uses Si primarily as a channel material for its very stable oxide  $SiO_2$ . In-spite of many advantages there are some restrictions for Si MOS, so the world is approaching towards compound semiconductor for higher frequency and current. The development of compound semiconductor metal oxide semiconductor is also facing critical problems due to the lack of availability of proper gate oxide material. Research is being conducted on arsenide and phosphide metal oxide semiconductor field effect transistor. Nitride channel MOS are in focus due to their high band gap, high current and high temperature uses.

Keywords: REVIEW, ARSENIDE, PHOSPHIDE, NITRIDE, MOSFET, COMPARISON.

(Received 04 February 2011)

# **1. INTRODUCTION**

In present days MOSFETs find their applications in digital circuits as well as in switching. Generally Si-MOS is used due to super quality of  $SiO_2$  as a gate oxide material on silicon. But it has certain limitations like low mobility of electron in Si compared to GaAs due to which Si-MOS has a frequency limitation as well as drain current in case of Si MOS is also low. Thus, in order to remove these limitations we have to go for III-V compound semiconductor MOSFET. Basic research works on compound semiconductor had started as early as in 1960's but even after such a long time compound semiconductor MOSFETs are under-performing as compared to their price and performance. Main constrains for the compound semiconductor MOSFETs are leaky gate oxide with interface, trap charges and low breakdown. The intended properties of a MOS gate oxide are high resistivity, high breakdown field, low trap charge density, chemical stability, good interface property and little or no drift of charge through oxide layer. Different types of oxide like  $Al_2O_3$ ,  $(Ga_2O_3, Gd_2O_3)$  GGO are used in different types of MOS. Work is in progress on three types of MOSFETs like Arsenide, Phosphide and Nitride channel MOSFET. This paper reviews the remarkable progress being made in the development of compound semiconductor MOSFET in the context of material device properties, device structures and DC performances.

### 2. III-V MOSFET

#### 2.1 Arsenide MOSFET

First anodic-oxide arsenide MOS was reported in 1976 by B. Bayraktararoglu et al. [1]. It was GaAs MOS where  $Al_2O_3$  was used as a gate oxide layer.

728

Metal layer of In-Sn-Al was exposed to electrolyte causing the growth of native oxide. Oxide layer thickness was found to be 1000 Å. Breakdown field for this MOS was reported as  $10^7$  V/cm and threshold voltage as 0.2 V [1]. But  $Al_2O_3$  creates some trap at interface due to which  $Ga_2O_3$  and  $Gd_2O_3$  (GGO) [2,3,11] which is native oxide and having dielectric coefficient (k) 14.2, much higher than that of  $SiO_2$  (3.9) [2] could also be considered as an option. Hafnium oxide which is another rare earth oxide proves itself as a good gate oxide material for compound semiconductor MOS [15, 16]. Due to high dielectric constant the breakdown voltage for this MOS will be higher and also leads to increase its current conducting capability. Trap charge density in GGO is also very low in the order of  $2 \times 10^{10}$  cm<sup>-2</sup> eV<sup>-1</sup> [3]. Passlack et al. reports this distribution of surface charge as U-shaped [25]. To deposit GGO on GaAs in MBE at first oxide on GaAs is deposited by heating followed by depositing the oxide using electron beam evaporation at a temperature of 350-550 °C. P-channel MOS with an oxide thickness of 400 Å, extrinsic transconductance was found as 0.3 mS/mm and breakdown field as  $3.6\times 10^6~{\rm V/cm}$  [2, 3]. In GGO (band gap 4.4 eV) the ratio of  $Ga_2O_3$  and  $Gd_2O_3$  is nearly constant (55:45) [3]. For GaAs depletion MOSFET transconductance was found as 210 ms/mm [3] and maximum frequency of oscillation as 36 GHz [3]. Introduction of Indium in GaAs results increase in mobility and higher saturation voltage. For In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS with GGO as gate oxide showed maximum oscillating frequency as 10 GHz. Reduction in the frequency might have been due to higher interface charge density  $(D_{it})$ . If GGO was grown on ultrahigh vacuum (<  $10^{-9}$  Torr) then leakage current would have been as low as  $10^{-9}$  A/cm<sup>2</sup> and breakdown voltage  $10^{7}$  V/cm [5]. If novel oxide GGO was grown on As free environment then interfacial state density would have been comparable with that of  $SiO_2$  (10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup>) [6]. To increase the high current density P.Parikh et al [4] reported Al<sub>2</sub>O<sub>3</sub> as an oxide layer on GaAs. 200 Å epitaxial layer of  $Al_{0.98}Ga_{0.02}As$  is oxidized with steam at 85 °C forming Al<sub>2</sub>O<sub>3</sub> layer. Current level for this MOS was reported 330 mA/mm and breakdown voltage as 30V [4]. Transconductance  $(g_m)$

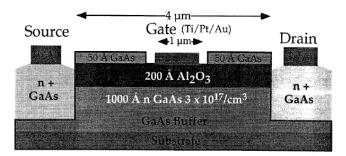

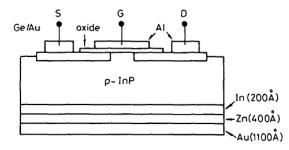

Fig. 1 – Cross-section schematic of D-mode MOSFET (From Ref. 4)

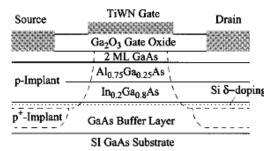

was 110 mS/mm where RF parameter i.e. maximum oscillating frequency was reported as 21 GHz [4]. J.Y.Wu et al introduce the concept of 'selective liquid phase oxide gate' [7] where GaAs is immersed into Ga-ion containing nitric acid solution to make a stable oxide which is composed by  $Ga_2O_3$ , As and  $As_2O_3$ . This liquid phase oxide gate MOS has breakdown voltage of  $4.5 \times 10^6$  V/cm, leakage current as  $10^{-8}$  A/cm<sup>2</sup>. Reported value of the dielectric constant is low (3.1) [7]. The only advantage of this oxide layer is that it is formed in room temperature. SiO<sub>2</sub> as a gate oxide layer on GaAs for a MOS reported higher density of interface state  $(10^{14} \text{ cm}^{-2} \text{ eV}^{-1})$  [8]. Though low temperature LPD grown SiO<sub>2</sub> on GaAs, shows much lower interface state [9]. For InAlAs MOSFET where the oxide layer was formed by thermal oxidation of InAlAs (Al = 48 %) showed transconductance of 6 ms/mm for gate length of 8 µm [10]. Breakdown field for this type of oxide layer was found lower than that of MOS using Al<sub>2</sub>O<sub>3</sub> as oxide layer [10]. In<sub>0.2</sub>Ga<sub>0.8</sub>As channel p-type enhancement mode MOSFET [11] where AlGaAs layer acts as spacer layer and Ga<sub>2</sub>O<sub>3</sub> as a gate oxide showed interface charge density of  $3 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ . With Si-delta doped region below the channel this MOS (Fig. 2) shows a good transconductance value of 51 mS/mm [11]. Be-doped n-type InGaAs n-channel MOS where GGO was used as a gate oxide material shows excellent c-v characteristics and surface

Fig. 2 – Cross section view of self-alligned enhancement mode InGaAs MOSFET [11]

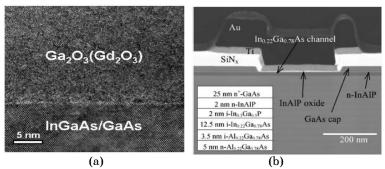

trap density was in the order of  $10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> [12]. With gate length of 4 µm this device shows maximum drain current of 30 mA/mm and transconductance of 1.7 mS/mm [12]. Threshold voltage was found moderate (1.8 V) [12]. Very good surface state between InGaAs and GGO makes the surface charge density comparable with Si. TEM of the interface between InGaAs/GaAs and GGO is shown in Fig. 3(a). Drain current and transconductance of In<sub>0.2</sub>Ga<sub>0.8</sub>As channel can be increased by growing a layer of  $Al_2O_3$  on GGO gate oxide layer [13]. This device gave a transconductance value of 48 mS/mm and maximum drain current value of 135 mA/mm [13]. Metal gate last shows large traps at oxide-semiconductor interface compared to metal gate first process due to higher chance of contamination in first case [13]. To achieve higher current and low threshold voltage form In<sub>0.22</sub>Ga<sub>0.78</sub>As-channel MOS native oxide of InAlP is currently taken as a gate oxide material [14]. The cross section of the MOS is shown in Fig. 3(b). Top most InAlP layer is oxidized with steam at a temperature of 440 °C for 9.5 minute to grow a oxide of thickness 3.5 nm. Low threshold voltage (0.25V) was found for this MOS [14]. For gate length of 0.25  $\mu$ m transconductance was found as 245 ms/mm and saturation drain current as 165 mA/mm. RF characteristics of this type of MOS are also found very promising. The reported value of maximum oscillation frequency for this MOSFET was 80 GHz [14]. TEM image of the interface of  $HfO_2/P_xN_u/In0._{70}Ga_{0.47}As$ is shown in Fig. 4a. Recently In rich In<sub>0.57</sub>Ga0<sub>.47</sub>As receives considerable attention as increasing In amount increases mobility of electron in the channel. For n-channel In<sub>0.57</sub>Ga<sub>0.47</sub>As MOS with Al<sub>2</sub>O<sub>3</sub> as gate oxide repots maximum drain current of 200 mA/mm [17].

Fig. 3 - HR-TEM of GGO and InGaAs/GaAs interface (a) [12] and cross section of InGaAs channel enhancement MOS with native oxide of InAlP (b) [14]

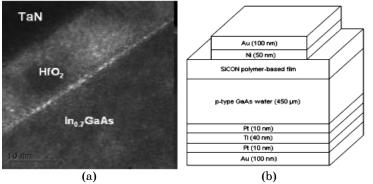

Here gate is fabricated at first which increases contamination at the oxide semiconductor interface [17]. InGaAs (In = 57 %) channel E-mode MOSFET where Al<sub>2</sub>O<sub>3</sub> was grown by ALD as a gate oxide reports much higher drain current (360 mA/mm) [18]. Possible reason for this high current might be the formation of gate at last; as a result it suffers less from contamination at the oxide semiconductor interface. Threshold voltage for these MOS was found as 0.25 V and surface charge density as  $1.4 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> by HF-LF method [18]. At the same time ZrO<sub>2</sub> grown on InGaAs had surface charge density of  $10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> [20]. Plasma based PH<sub>3</sub> passivation technique is one of the best way to passivate the open surface. H.J. Ho et al. reported a technique to passivate InGaAs of a n-MOSFET [19]. After plasma-PH<sub>3</sub> treatment using MOCVD, HfO<sub>2</sub> and HfAlO were deposited. Plasma-PH3 passivation improves the thermal stability between oxide-semiconductor interface upto 750 °C [19]. Metal contact was given by TiN. Interface between plasma-PH3 treated InGaAs-HfO<sub>2</sub>-TiN is shown in the Fig. 4b. Transconductance

**Fig.** 4 – TEM of interface of  $HfO_2/P_xN_y/In_{0.70}Ga_{0.47}As S/D$  formed at 700 °C [14] (a) and GaAs MOS capacitor with SiCON polymer layer as gate dielectric [22] (b)

for this MOS was reported high (378 mS/mm at  $V_d = 1$  V) and the effective mobility of electron was found as 2557 cm<sup>2</sup>/V s [19], which was higher than that of enhancement mode MOSFET [18]. ZrO<sub>2</sub> as gate oxide material on InGaAs grown on p-type InAlAs shows interface charge density in the range of 10<sup>13</sup> cm<sup>-2</sup> eV<sup>-1</sup> [20]. CVD grown polymer based thin film 'SiCON', grown on GaAs showed very good result [22]. Process of growing this polymer layer is described in detail in Ref. 23, 24. This MOS (shown in Fig. 4b) reported density of interface charge as  $9.7 \times 10^9$  cm<sup>-2</sup>eV<sup>-1</sup>[22]. Dielectric leakage current reported in the range of nA/cm<sup>2</sup> and breakdown field 2.05 MV/cm [22].

### 2.2 Phosphide MOSFET

InP due to its high electron mobility, has been used as a MOSFET channel material. Compared to GaAs, InP has higher saturation velocity which goes in favor of InP MOSFET. Thermal oxidization of InP produces oxide on it but it shows a departure from stoichiometry [26, 27] which causes degradation of properties at the interface of InP-oxide. Oxide grown on InP using plasma oxidation system is stable both thermally and chemically and does not react with organic solvents [26]. Though  $P_2O_5$  has strong affinity to water but due to different chemical composition does not react even with boiling water [26]. No accumulation of phosphorous at the interface was reported [26]. This InP channel MOSFET showed channel conductance of

Fig. 5 - Cross section view of self-alligned enhancement mode InP MOSFET [26]

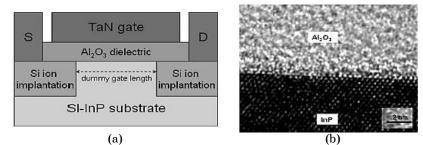

1.2 mA/V at  $V_g = 13$  V [26]. Electron surface mobility at the interface was reported much lower (400 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup>) than the bulk mobility [26]. SiO<sub>2</sub> was also tried as a gate oxide for InP MOS [28,32]. Using plasma enhanced decomposition of tetraethoxysilane in oxygen plasma, a layer of  $SiO_2$  was deposited at 300 °C [28]. Oxide layer quality was found to be dependent on deposition condition. Fe-doped InP MOS with SiO<sub>2</sub> as oxide showed electron surface mobility in between 250-750 cm<sup>2</sup> V<sup>-1</sup> S<sup>-1</sup> but X-ray study shows dislocation densities in the order of  $10^4 \cdot 10^5$  cm<sup>-2</sup> [28]. Kawakami et al. reported interface between InP and  $Al_2O_3$  [29] and unpinned Fermi level [33]. Using anodic oxide as gate insulator promising surface charge density was observed.  $D_{it}$  of the order of  $8 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> was achieved in midband if the oxide was annealed at 200 °C [30]. Enhancement mode n-channel In P metal oxide semiconductor field effect transistor with ALD grown  $Al_2O_3$ as gate oxide (30 nm) showed maximum drain current of 70 mA/mm for a gate length of  $0.75 \ \mu m$  [33]. Gate oxide was grown at substrate temperature of 300 °C using  $Al(CH_3)_3$  and water vapor at nitrogen environment [33]. Source and drain was done using ion-implantation of Si and then RTA at 720 °C for a period of 10 second. Leakage current for this MOS was reported as 10  $\mu$ A/mm at maximum gate voltage of 8V [33]. Interface charge density was comparatively high and in the order of  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>. Electron mobility at the interface was reported as  $650 \text{ cm}^2 \text{ V}^{-1} \text{ S}^{-1}$  and transconductance as 10mS/mm [33]. Inversion type InP MOS (Fig. 6a) with ALD grown

$Al_2O_3$  as oxide layer having effective oxide thickness of 21 Å shows improvement in transconductance [34]. Fig. 6b shows sharp interface between  $Al_2O_3$ and InP without any sign of interfacial reaction. For this MOS possessing gate length of 50 µm, drain current was reported as 50mA/mm [34]. High electron mobility of 745 cm<sup>2</sup>/V s was also reported at the interface [34]. Another way

**Fig. 6** – Schematic cross-section of InP MOSFET (a) and TEM of  $Al_2O_3$ -InP interface (b) [34]

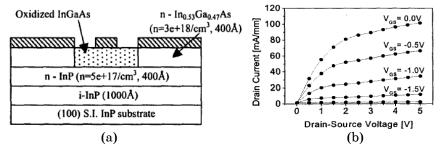

to passivate InP-MOS is by using liquid phase oxidized InGaAs [35]. This oxide layer was formed by using a solution of Ga-ion contained nitric acid with oxygen plasma treatment. Peak transconductance of the depletion mode MOS (Fig. 7a) was found as 60 mS/mm [35]. In this case, normalized drain saturation current was reported as 78 mA/mm and maximum operation frequency ( $f_{Max}$ ) as 70 GHz [35]. Drain current vs drain-source voltage curve for the device was shown in Fig. 7b. Maximum drain current drift from its saturation level was reported as 7.1% due to the interface trap charge [35].

Fig. 7 – Schematic cross-section of InP MOSFET with InGaAs liquid oxide (a) and drain current-voltage characteristics InP channel MOSFET (b) [35]

# 2.3 Nitrite MOSFET

Gallium Nitride is also being an important material choice for MOSFET researches. Although it has a lower mobility than GaAs and InP based III-V compound semiconductors, but it has other advantages like very high saturation current, high temperature stability, higher breakdown voltage due to its high bandgap. The inherent piezoelectric charge property makes the material a very good choice for high current, high voltage and high power devices. Gallium nitride is also experimented in different magnetic field conditions and found to be very reliable. So, GaN MOSFET can extensively be used for the space application purpose. In search of proper oxide for gate oxide, at first gallium oxide was tried. But both dry [39, 40]

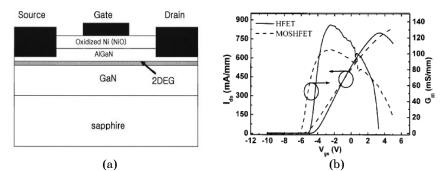

and wet [41] oxidation shows improper interface of Ga<sub>2</sub>O<sub>3</sub>/GaN [38]. SiO<sub>2</sub> was also tested as a gate dielectric [46, 47, 49]. Then AlN was also tried but it was suffered from defects and grain boundaries [38]. Rear earth oxide  $HfO_2$  has also been tried as gate dielectric [57,58,59,60]. Using SiO<sub>2</sub> as gate dielectric GaN MOSFET was formed in LP-MOCVD on sapphire substrate [49]. PECVD was used to grow an oxide layer of 10-15 nm. Reported values of maximum current and transcondutance were 300 mA/mm and 60 ms/mm respectively for a gate length of 2 µm [49]. Cut-off frequency and gate length product of this GaN MOS was reported as 11.6 GHz-micron which is comparable to the same value of AlGaN/GaN MOSFET grown on same substrate [49]. Crystalline gadolinium oxides  $(Gd_2O_3)$  have been investigated as a gate oxide material for GaN MOS. Deposition of Gd<sub>2</sub>O<sub>3</sub> on GaN was done in MBE using Gd and oxygen plasma at a temperature of 650 °C [38]. Though crystalline structure of the oxide but it shows low breakdown field (0.5 MV/cm), which proves the presence of large no. of defects at the interface [38]. Thermal stability experiment at a temperature of 1000 °C showed less than 10% increase in RMS roughness of  $Gd_2O_3$  interface [38]. If a layer of SiO<sub>2</sub> (300 Å) was deposited then it shows very low leakage current in the order of pA [38]. Leakage current in the order of 10-11 A was reported for wet oxidized nitride MOS [55]. Among all these tests for the search of gate oxide, amorphous GGO proves itself better in almost all the way [42, 43, 44, 45]. GGO layer was deposited by electron beam evaporation from a single crystal GGO in MBE [38]. GGO/GaN MOS showed leakage current in the order of mA to nA [38]. Dielectric constant of GGO is found very high (14). GGO/GaN allows modulation at forward voltage of 3 V, where as SiO<sub>2</sub> layer added Gd<sub>2</sub>O<sub>3</sub>/GaN MOS shows the value as 7V [38]. High temperature silicon-di-oxide (HTO, 900°C) deposited GaN MOS showed interface trap density as  $3 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> near the conduction band edge [46]. Gate leakage current for this RESURF (Reduced SURface Field) GaN MOS was reported very low and in order of pA, where as field electron mobility reported as 110 cm<sup>2</sup>/Vs [46]. High doping in GaN may cause degradation of mobility in the channel as a result AlGaN/GaN heterostructure is being used to generate 2DEG. AlGaN/GaN heretostructure MOS with  $SiO_2$  as oxide layer repots mobility of 1180  $\text{cm}^2/\text{Vs}$  [37]. Sheet carrier concentration at the interface was found as  $1.15 \times 10^{13}$  cm<sup>-3</sup> and maximum drain current as 600 mA/mm [37]. Gate oxide for this MOS was fabricated by PECVD. Gate leakage current found four times lower than that of AlGaN/GaN HEMT [37]. Maximum transconductance for this MOS was reported as 75 mS/mm [37]. AlGaN/GaN heterostructure MOSFET with nickel oxide as dielectric is reported by C.S. Oh et al. [48]. NiO as dielectric has band-gap energy of 4 eV and dielectric constant of 11.9. Ni oxidation was performed in air ambient at  $300^\circ\!\mathrm{C}$  to  $600^\circ\!\mathrm{C}$  for 5 minutes [48]. Ohmic contact was done by thermal deposition of Ti/Al/Ni/Au. Maximum drain current of the AlGaN/GaN MOS (Fig. 8a) was reported as 800 mA [48]. At high gate voltage the device showed negative resistance (Fig. 8b) due to self-heating but pinch-off was observed for gate voltage about -5.9 V [48]. Maximum value of  $g_m$  value of AlGaN/GaN MOS was reported as 105 ms/mm [48]. In 2006, D. Alexandrov et al. reported a strange type of GaN/InN MOSFET which can behave both n and p-channel MOS. While making the MOS, GaN layer is grown on InN layer where at the interface a layer of  $In_xGa_{1-x}N$  is formed which can act as an exciton layer [50]. This layer can behave as a source of both electron and

Fig. 8 – Schematic cross-section of AlGaN/GaN MOSFET (a) and  $I_d$  vs  $V_{gs}$  curve for AlGaN/GaN HFET and MOSFET (b) [48]

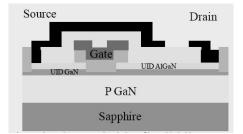

hole depending upon the applied voltage to the heterojunction. If positive voltage with respect is applied to the gate then exciton layer act as a source of electron and generated electrons moves to the higher band gap material i.e. GaN in this case. So GaN/InN MOSFET will become n-channel for positive gate voltage. For negative gate voltage In<sub>x</sub>Ga<sub>1-x</sub>N layer breaks and acts a source of holes, making the MOS as p-channel [50].  $SiO_2$  was used as gate oxide material for the MOS [50]. GaN MOS with  $SiO_2$ -Ga<sub>2</sub>O<sub>3</sub> as oxide dielectric reports low leakage current in the order of pA [51]. To grow the oxide layer of  $Ga_2O_3$  on GaN, oxidization was done with the help of nitric acid (pH 3.5) with He-Cd laser [51]. Then a layer of  $SiO_2$  was grown. Forward and reverse breakdown fields were found as 2.92 and 11.5 MV/cm respectively, where as leakage currents were 91 and 10 pA [51]. Interface state density was stated as  $2 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> [51]. Use of GaN as a channel material increases the breakdown voltage which is dependent on the doping of GaN layer. K.Tang et al. [52] shows this phenomenon in their E-mode MOS which has also the advantage of 2DEG at AlGaN/GaN interface. This hybrid MOS-HEMT was built on p-GaN by growing unintentionally doped GaN/AlGaN layer (Fig. 9) [52]. Gate oxide thickness was 100 nm. A reported value of 2DEG at AlGaN/GaN interface was  $8 \times 10^{12}$  cm<sup>-3</sup> [52]. Maximum breakdown voltage for this hybrid MOS was 1300V, which depends on the doping concentration in the p-GaN layer [52]. With increasing doping in lower GaN region the breakdown voltage for this MOSFET was found reducing [52].

Fig. 9 – Schematic cross-section of hybrid MOS-HEMT [52]

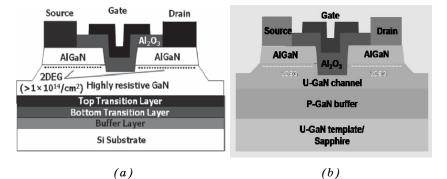

By using special technique GaN can be grown on silicon. AlGaN/GaN MOSFET grown on Si was described by K-S. Im et al. [54]. The device was grown on silicon by growing multiple transition layers on them. Bottom

transition layer was made by five stacks of low temperature grown AlN (20 nm) and high temperature grown GaN (150 nm). Upper transition layer was made up of multiple stacks of AlN/GaN superlattice [54]. Upon this a high resistive GaN layer of thickness 0.7  $\mu$ m and Al<sub>0.3</sub>Ga<sub>0.7</sub>N layer (25 nm) was grown. After etching  $Al_{0.3}Ga_{0.7}N$  in the gate region 30 nm thick high qualities  $Al_2O_3$  layer was grown using ALD. Source and drains are made up of Ta/Ti/Al/Ni/Au using electron beam evaporator [54]. Reported value of 2DEG at the AlGaN/GaN interface is very high and in the order of  $10^{14}$  cm<sup>-2</sup>. This high value is due to the strong tensile stress in the growth of AlGaN/GaN which increases both types of polarizations. This density of 2DEG is greater than that for normal AlGaN/GaN heterostructure. Mobility of 2DEG was found as  $120 \text{ cm}^2/\text{ v}$  s from Hall measurement. Due to higher value of 2DEG drain current was also high (353mA/mm) [54]. Maximum transconductance for this MOS was reported as 98 mS/mm whereas gate leackage current was in the order of  $10^{-7}$  A/mm at gate voltage of 6 V [54]. Field effect mobility for this case was reported as  $225 \text{ cm}^2/\text{V}$  s (highest reported mobility in GaN MOSFET) [54]. For this normally off GaN MOS off-state breakdown voltage was reported as 40 V with a gate length of 0.25 µm [54]. AlGaN/GaN MOSFET grown on sapphire [53] with p-GaN buffer layer showed less promise compared to the previous case [54].

Fig. 10 – Schematic cross-section of GaN MOSFET grown on Si-substrate [54] (a) and schematic cross section of MOSFET grown on sapphire [53] (b)

For this normally-off MOSFET (fig. 10b) maximum drain current was reported as 109 mA/mm at  $V_g = 7$  V and extribuic transconductance in the order of 30 ms/mm [53]. Sheet carrier (2DEG) density for this was reported in the order of  $10^{12}$  cm<sup>-2</sup> [53], two order lower than that reported for AlGaN/GaN MOS grown on Si [54]. With increasing channel thickness, density of 2DEG increases due to lower effect of p-GaN buffer on the 2DEG at interface of AlGaN/GaN [53]. H. Kambayashi et al. recently reports AlGaN/GaN hybrid MOS-HFET with maximum drain current of 100 A for a channel length of 2 µm [56].

# 3. COMPARISON

Arsenide MOSFET is the one subject of maximum interest among researcher in the domain of field effect technology. From Table 1 it is clear that GaAs MOS with GGO as gate oxide material has performed well. From GaAs, MOS technology is shifting towards InGaAs to achieve higher breakdown and

transconductance but at the same time lower threshold voltage and leakage current. Table 2 shows the development of arsenide MOS and their performances improving year after year. For phosphide MOS cost is higher and performance is inferior as compared to Arsenide MOS. So less number of research has been done on phosphide MOS. One of the main disadvantage of this type of device is higher leakage current instead of higher electron mobility in phosphide metal oxide semiconductor field effect transistor. Among all types of MOS technology nitride channel is the new one and most discussed. For nitride MOS breakdown voltage is higher compared with other MOS, so this MOS can be used as to make low frequency high power devices. Nitride MOS with  $Al_2O_3$  as oxide layer shows higher leakage current due to the presence of leaky oxide at the interface. Instead of using only gallium nitride if we use AlGaN/GaN heterostructure then 2DEG formed at the interface that can supply lots of carrier without decreasing the electron mobility caused by high doping. Further Drain current increases This type of device is called as hybrid MOS-HEMT structure as both the advantage of HEMT and MOSFET are available there. GGO as gate oxide reports lowest interface charge density for nitride technology. Nitride MOS with NiO as gate dielectric reports highest drain current.

| Year<br>[Ref] | MOSFET                            | Oxide<br>material                                                      | ${D_{it} m cm^{-2}eV^{-1}}$ | Breakdown<br>field<br>(V/cm) | Saturated<br>drain<br>current<br>mA/mm | g <sub>m</sub><br>mS/mm | Reverse-<br>Leakage<br>current               | $_{\rm V}^{V_{Th}}$ |

|---------------|-----------------------------------|------------------------------------------------------------------------|-----------------------------|------------------------------|----------------------------------------|-------------------------|----------------------------------------------|---------------------|

| 1996<br>[2]   | E-mode P-channel<br>GaAs          | GGO                                                                    | -                           | $3.6 \times 10^{6}$          | -                                      | 0.3                     | -                                            | -                   |

| 1997<br>[3]   | D-Mode n-channel<br>GaAs          | GGO                                                                    | -                           | $3.6 \times 10^{6}$          | -                                      | -                       | -                                            | -                   |

| 1998<br>[4]   | D-Mode n-channel<br>GaAs          | Al <sub>2</sub> O <sub>3</sub>                                         | -                           | -                            | 330                                    | 30                      | 50 µA                                        | -                   |

| 2001<br>[7]   | D-mode n-channel<br>GaAS          | Ga <sub>2</sub> O <sub>3</sub> ,<br>As, As <sub>2</sub> O <sub>3</sub> | $5 \times 10^{11}$          | $4.5 \times 10^{6}$          | 380                                    | 80                      | 10 nA                                        | -                   |

| 2002<br>[11]  | E-mode p-channel<br>GaAs          | $\mathrm{Ga}_2\mathrm{O}_3$                                            | 3×10 <sup>11</sup>          | -                            | 0.55                                   | 51                      | -                                            | -0.93               |

| 2007<br>[18]  | E-mode n-channel<br>InGaAs        | $Al_2O_3$                                                              | $1.4 \times 10^{12}$        | -                            | 360                                    | -                       | -                                            | 0.25                |

| 2008<br>[12]  | Inversion-mode n-<br>channel GaAs | GGO                                                                    | 2-6×10 <sup>11</sup>        | -                            | 30                                     | 1.7                     | $\begin{array}{c} 110\\ nA/cm^2 \end{array}$ | 1.8                 |

| 2009<br>[13]  | D-mode n-channel<br>InGaAs/GaAs   | Al <sub>2</sub> O <sub>3</sub> /<br>GGO                                | $10^{11}$                   | -                            | 135                                    | 48                      | -                                            | -                   |

| 2010<br>[14]  | E-mode InGaAs                     | Native<br>oxide of<br>InAlP                                            | $5 \times 10^{12}$          | 14.7×10 <sup>6</sup>         | 165                                    | 168                     | 5.5 nA                                       | 0.25                |

| Table 1 – Compa | ison of Ars | senide MOSFET |

|-----------------|-------------|---------------|

|-----------------|-------------|---------------|

| Year | MOSFET                    | Gate-Oxide<br>material          | Transconductance<br>( mS/mm) | Reverse Leackage<br>Current | Surface<br>Mobility<br>(Cm <sup>2</sup> / V s) | Ref.<br>No. |

|------|---------------------------|---------------------------------|------------------------------|-----------------------------|------------------------------------------------|-------------|

| 1998 | D-mode GaN                | GGO                             | 5                            | -                           | -                                              | 35          |

| 2000 | GaN                       | $Gd_2O_3$ , $SiO_2$             | 15                           | 10 μA <sup>-1</sup> nA      | -                                              | 38          |

| 2002 | GaN                       | $SiO_2$                         | 60                           | -                           | -                                              | 49          |

| 2003 | GaN MOS on<br>AlGaN       | $SiO_2$                         | -                            | 50 pA                       | 110                                            | 46          |

| 2003 | GaN                       | ${ m SiO_2}	ext{-}{ m Ga_2O_3}$ | -                            | 10 pA                       | 350                                            | 51          |

| 2010 | AlGaN/GaN<br>MOS on Si    | $Al_2O_3$                       | 98                           | 0.1 μΑ                      | 225                                            | 54          |

| 2010 | AlGaN/GaN<br>MOS on p-GaN | $Al_2O_3$                       | 30                           | 4 μΑ                        | 850                                            | 53          |

Table 2 – Comparison of Nitride MOSFET

# 4. CONCLUSION

In this paper we have studied the properties of different types of MOS in terms of their structure, characteristics and performance. Further arsenide, phosphide and nitride MOS were compared for electrical performances on the basis of some common parameters like threshold voltage,  $D_{it}$ , transconductance, gate oxide materials etc. Nitride Hybrid MOS was found to be the most useful transistor for making high power devices. The year wise studies of different III-V MOSFETs demonstrate that various electrical parameters are rapidly transforming into better situations.

#### REFERENCES

- 1. B. Bayraktaroglu, E. Kohn, H.L. Hartnagel, *IEEE Electr. Device L.* 53, 12 (1976).

- F. Ren, M.W. Hong, W.S. Hobson, J.M. Kuo, J.R. Lothian, J.P. Mannaerts, J. Kwo, Y.K. Chen, and A.Y. Cho, *International Elec. Device Meeting IEDM'96*, 943 (1996).

- F. Ren, M. Hong, J.M. Kuo, W.S. Hobson, J.R. Lothian, H.S. Tsai, J. Lin, J.P. Mannaerts, J. Kwo, S.N.G. Chu, Y.K. Chen, A.Y. Cho, *GaAs IC* Symposium, 18 (1997).

- 4. P. Parikh, P. Chavarkar, B. Keller, U. Mishra, *IEEE High Speed Semi. Device* and Ckt., 389 (1997).

- 5. M. Hong, IEEE Solid-state IC Tech., 685 (1998).

- M. Hong, F. Ren, W.S. Hobson, J.M. Kuo, J. Kwo, J.P. Mannaerts, J.R. Lothian, M.A. Marcus, C.T. Liu, A.M. Sergent, T.S. Lay, Y.K. Chen, *International Symposium on Compound Semiconductor*, 319 (1997).

- 7. J.Y. Wu, H.H. Wang, Y. H. Wang, M.P. Houng, *IEEE T. Electron. Dev.* 48, 634 (2001).

- 8. Y. Mochizuki and M. Mizuta, Appl. Phys. Lett. 69, 3051 (1996).

- M.P. Houng, C.J. Huang, Y.H. Wang, N.F. Wang, W.J. Chang, J. Appl. Phys. 82, 5788 (1997).

- 10. P.A. Grudowski, R.V. Chelakara, R.D. Dupuisa, Appl. Phys. Lett. 69, 388 (1996).

- M. Passlack, J.K. Abrokwah, R. Droopad, Z. Yu, C. Overgaard, S. In. Yi, M. Hale, J. Sexton, A.C. Kummel, *IEEE Electr. Device L.* 23, 508 (2002).

- 12. C.P. Chen, T.D. Lin, Y.J. Lee, Y.C. Chang, M. Hong, J. Kwo, *Solid State Electron.* 52, 1615 (2008).

- C.A. Lin, T.D. Lin, T.H. Chiang, H.C. Chiu, P. Chang, M. Hong, J. Kwo, J. Cryst. Growth 311, 1954 (2009).

- 14. X. Xing, P.J. Fay, IEEE Electr. Device L. 31, 1214 (2010).

- G.K. Dalapati, Y. Tong, W.Y. Loh, H.K. Mun, B.J. Cho, *Appl. Phys. Lett.* 90, 183510 (2009).

- I. Ok, H.Kim, M. Zhang, F. Zhu, S. Park et al., J. Vac. Sci. Technol. B 25, 1491 (2007).

- 17. A. Olivier, N. Wichmann, J.J. Mo, et al., *IEEE IPRM 2010*, 1 (2010).

- Y. Xuan, Y.Q. Wu, C.Lin, T. Shen, P.D. Ye, *IEEE Device Research Conf.*'07, 207 (2007).

- H.j. Oh, J.Q. Lin, S.A.B. Suleiman, G.Q. Lo, D.L. Kwong, D.Z. Chi and S.J. Lee, *IEEE International Electron Device Meeting (IEDM 2009)*, 1 (2009).

- L. Morassi, G. Verzellesi, A. Padovani, L. Larcher et al., *IEEE International Reliability Physics Symposium (IRPS'10)*, 532 (2010).

- 21. T. Mimura, M. Fukuta, IEEE T. Electron. Dev. 27, 1147 (1980).

- 22. E.H. Oulachgar, C. Aktik, M. Scarlete, IEEE T. Electron. Dev. 57, 1942 (2010).

- E. Oulachgar, C. Aktik, S. Dostie, R. Sowerby, et al., J. Appl. Phys. 101, 084107 (2007).

- E. Oulachgar, C. Aktik, S. Dostie, R. Sowerby et al., J. Electrochem. Soc. 153, F255 (2006).

- 25. M. Passlack, R. Droopad, G. Brammertz, IEEE T. Electron. Dev. 57, 2944 (2010).

- 26. S.N. Al-Refaie, J.E. Carroll, IEEE Solid State Electron Devices 128, 207 (1981).

- 27. J.P. Wager, C.W. Wilmsen, J. Appl. Phys. 51, 812 (1980).

- J. Woodward, G.T. Brown, B. Cockayne, D.C. Cameron, *Electron. Lett.* 18, 415 (1982).

- 29. T. Kawakami, M. Okamura, Electron. Lett. 15, 502 (1979).

- 30. A. Yamamoto, C. Uemura, Electron. Lett. 18, 63 (1982).

- O. Sri, R.E. Owens, C.W. Wilmsen, S.M. Goodnick, J.E. Lary, 2nd International Conference- Indium Phosphide and related material (ICIPRM-1990), 320 (1990).

- 32. T. Yamagata, T. Sakai, K. Sakata, K. Shimomura, International Topical Meeting on Microwave Photonics (MWP'96), 173 (1996).

- 33. Y.Q. Wu, Y. Xuan, T. Shen, P.D. Ye, *Appl. Phys. Lett.* **91**, 022108 (2007).

- H. Zhao, D. Shahrjerdi, F. Zhu, H.S. Kim, I. OK, M. Zhang, J.H. Yum, S.K. Banerjee, J.C. Lee, *Electrochem. Solid St.* 11, H233 (2008).

- 35. S.J. Kang, J.C. Han, J.H. Kim, S.J. Jo, S.W. Park, J.I. Song, Indium Phosphide and Releted Material Conference (IPRM '02), 193 (2002).

- F. Chen, M. Hong, S.N.G. Chu, M.A. Marcus, M.J. Schurman, A. Baca, S.J. Pearton, C.R. Abernathy, *Appl. Phys. Lett.* 73, 3893 (1998).

- 37. M.A. Khan, X. Hu, G. Sumin, A. Lunev, J. Yang, R. Gaska, M.S. Shur, *IEEE Electr Device L.* 21, 63 (2000).

- B.P. Gila, K.N. Lee, W. Johnson, F. Ren, C.R. Abernathy, S.J. Pearton, M. Hong, J. Kwo, J.P. Mannaerts, K.A. Anselm, *High Performance Device Proceedings 2000*, 182 (2000).

- S.D. Wolter, B.P. Luther, D.L. Waltemyer, C. Onneby, S.E. Mohney, R.J. Molnar, *Appl. Phys. Lett.* **70**, 2156 (1997).

- S.D. Wolter, S.E. Mohney, H. Venugopalan, A.E. Wickenden, D.D. Koleske, J. Electrochem. So.c 145,629 (1998).

- E.D. Readinger, S.D. Wolter D.L. Waltemyer, J.M. Delucca, S.E. Mohney, B.I. Prenitzer, L.A. Gainnuzzi, R.J. Molnar, J. Electron. Mater. 28, 257 (1999).

- M. Hong, J.P. Mannaerts, J.E. Bower, J. Kwo, M. Passlack, W-Y. Hwang, L.W. Tu, *J Cryst. Growth* 175/176, 422 (1997).

- Y.C. Wang, M. Hong, J.M. Kuo, J.P. Mannaerts, J. Kwo, H.S. Tsai, J.J. Krajewski, J.S. Weiner, Y.K. Chen, A.Y. Cho, *Materials Research Society* Symposium Proceedings '99 573, 219 (1999).

- 44. J. Kwo, M. Hong, A.R. Kortan, D.W. Murphy, J.P. Mannaerts, A.M. Sergent, Y.C. Wang, K.C. Hsieh, *Materials Research Society Symposium Proceedings*, 573, 57 (1999).

- A.R. Mortan, M. Hong, J. Kwo, J.P. Mannaerts, N. Kopylov, Materials Research Society Symposium Proceedings 573, 21 (1999).

- 46. K. Matocha, T.P. Chow, R.J. Gutmann, Power Semiconductors International Symposium on Power Semiconductor Devices and ICs Proceedings (ISPSD'03), 54 (2003).

- 47. N. Pala, S.L. Rumyantsev, M.S. Shur, X. Hu, A. Tarakji, R. Gaska, M. Asif Khan, G. Simin, and J. Yang, *Solid-State Electron.* 46, 711 (2002).

- C.S. Oh, C.J. Youn, G.M. Yang, K.Y. Lim, J.W. Yang, *Appl. Phys. Lett.* 85, 4214 (2004).

- 49. R. Gaska, M.A. Khan, X. Hu, G. Simin, J. Yang, J. Deng, S. Rumyantsev, M.S. Shur, *Device Research Conf. (DRC'00)*, 43 (2000).

- 50. D. Alexandrova, R. Dimitrrova, K.S. Butcher, M. Wintrebert-Fouquet, R. Perks, Canadian Conf. on Electrical and Comp. Eng. (CCECE'06), 537 (2006).

- 51. C.T. Lee, H.Y. Lee, H.W. Chen, *IEEE Electr. Device L.* 24, 54 (2003).

- 52. K. Tang, Z. Li, T.P. Chow, Y. Niiyama, T. Nomura, S. Yoshida, 21<sup>st</sup> International Symposium on Power Semiconductor Device & IC (ISPSD'09), 279 (2009).

- 53. D.S. Kim, J.B. Ha, S.N. Kim, E.H. Kwak, S.G. Lee, H.S. Kang, J.S. Lee, K.S. Im, K.W. Kim, J.H. Lee, 22<sup>nd</sup> International Symposium on Power. Semi. Device & IC (ISPSD'10), 229 (2010).

- 54. K.S. Im, J.B. Ha, K.W. Kim, J.S. Lee, D.S. Kim, S.H. Hahm, J.H. Lee, *IEEE Electr. Device L.* **31**, 192 (2010).

- M.K. Mazumder, K. Kobayashi, T. Ogata, J.I. Mitsuhashi, Y. Mashiko, S. Kawazu, M. Sekine, H. Koyama, A. Yasuoka, *Solid-State Electron.* 41, 749 (1997).

- H. Kambayashi, Y. Satoh, S. Ootomo, T. Kokawa, T. Nomura, S. Kato, T.P. Chow, *Solid-State Electron.* 54, 660 (2010).

- S. Abermann, G. Pozzovivo, J. Kuzmik, G. Strasser, D. Pogany, J-F. Carlin, N. Grandjean and E. Bertagnolli, *Semicond. Sci. Technol.* 22, 1272 (2007).

- C.F. Shiha, K.T. Hunga, C.Y. Hsiaoa, S.C. Shua, W.M. Li, J. Alloy Compd. 480, 541 (2009).

- Y. Hayashi, S. Sugiura, S. Kishimoto, T. Mizutani, *Solid-State Electron.* 54 1367 (2010).

- D.J. As, H. Pottgen, E. Tschumak, K. Lischka, phys. status solidi c 7, 1988 (2010).