examined devices submitted to HBM pulses, with a 10 ns rise time and a 150 ns time constant. These pulses are applied on the collector of the simulated devices, while their emitter and substrate are grounded. The thermal boundary condition is considered to be a constant temperature of 300K at the bottom of the simulation domain which corresponds to the substrate electrode.

Fig. 2 shows the calculated transient voltage responses of the two transistors submitted to a low stress level (peak current  $I_p$  =  $8\text{mA/\mu m}$ ) and to a high stress level ( $I_p = 15\text{mA/\mu m}$ ). This figure shows that initially the voltage across the device increases up to the triggering level (points A and A', Fig. 2). The simulated values of the triggering voltage of the two devices are in good agreement with the experimentally measured values (Table 1). In fact, the triggering voltages under transient conditions are lower than under static conditions owing to capacitive effects and the existence of displacements currents. Accordingly, the devices enter in snap-back and the voltage decreases up to the sustaining level (points B and B', Fig. 2). When this occurs, the greatest part of the discharge current flows laterally from the collector to the emitter under the field oxide (PBL, see Fig. 1a), while the conductivity of the base region is significantly modulated [6], which leads to a decrease in the resistance of the discharge path. However, the applied current still increases, since its maximum value is attained at 10ns (points C and C', Fig. 2), also causing the terminal voltage to increase. Subsequently, the current decays exponentially and when it reaches the value for which the snap-back condition is not satisfied anymore, the terminal voltage goes back to the triggering voltage of the device (points E and E', Fig. 2).

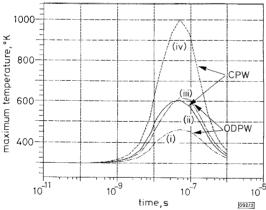

Fig. 2 also shows that at high stress level the terminal voltage of the CPW device increases after the current has reached each peak value, and that it decreases in the case of the ODPW device (points D and D', Fig. 2). This is a thermal effect and can be attributed to the decrease of the mobility as well as to the increase of the avalanche voltage at high temperatures. The calculated maximum temperature transients for the different stress levels of the examined devices (Fig. 3) show that at high stress level the maximum temperature in the CPW device is considerably higher than in the ODPW device. This fact is probably the cause of the observed different failure levels of the tested transistors.

Fig. 3 Calculated maximum temperature transients

Low stress level: (i) and (ii) High stress level: (iii) and (iv)

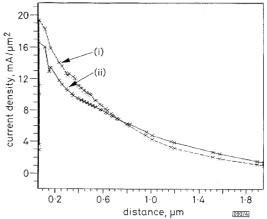

The increase in the lattice temperature is proportional to the product of the electric field by the current density. The electric field is lower in the ODPW device owing to the lower sustaining voltage in comparison with the CPW device. Conversely, Fig. 4 shows that, in the case of the ODPW device, the current density under the field oxide, when the discharge current reaches its peak value (i.e. 15mA/µm), is lower and spreads deeper in the base region, than in the case of the CPW device. This effect can be attributed to the additional implantation existing in the ODPW devices.

Conclusion: A simple process modification (over-doped P-well) can lead to a faster activation of a classical field oxide transistor and to a significant increase of the failure level. The higher

Fig. 4 Calculated current density under PBL for high stress conditions (i) CPW, (ii) ODPW

performance of these devices is caused by the lower heat dissipation provoked by the lower electric field and by the spreading of the discharge current deeper in the device.

© IEE 1996 16 February 1996 Electronics Letters Online No: 19960541

T. Nikolaidis (SGS-Thomson Microelectronics, 850, rue Jean Monnet, BP 16, F-38921 Crolles Cedex, France)

## References

- 1 CLARK, N., PARAT, K., MALONEY, T., and KIM, Y.: 'Melt filaments in n+pn+ lateral bipolar ESD protection devices'. EOS/ESD Symp. Proc., 1995, Vol. EOS-17, pp. 295–303

- 2 DUVVURY, C., ROUNTREE, R., and WHITE, L.: 'A summary of most effective electrostatic discharge protection circuits for MOS memories and their observed failure modes'. EOS/ESD Symp. Proc., 1983, Vol. EOS-5, pp. 181–184

- 3 NIKOLAIDIS, T., PAPADAS, C., VARROT, M., MORTINI, P., and PANANAKAKIS, G.: 'Impact of I/O buffer configuration on the ESD performance of a 0.5 \mu CMOS process'. EOS/ESD Symp. Proc., 1995, Vol. EOS-17, pp. 34-42

- 4 HASHIMOTO, C., OKUYAMA, K., KUBOTA, K., and ISHIZUKA, H.: 'Degradation of I/O devices due to ESD-Induced dislocations'. IEDM, 1994, pp. 459–462

- 5 AMERASEKERA, A., VAN ROOZENDAAL, L., ABDERHALDEN, J., BRUINES, J., and SEVAT, L.: 'An analysis of low voltage ESD damage in advanced CMOS processes'. EOS/ESD Symp. Proc., 1990, Vol. EOS-12, pp. 143-150

- 6 HSU, F., MULLER, R., and HU, C.: 'A simplified model of short-channel MOSFET characteristics in the breakdown mode', IEEE Trans. Electron Devices, 1983, ED-30, (6), pp. 571-576

## Gate recess engineering of pseudomorphic In<sub>0.30</sub>GaAs/GaAs HEMTs

N.I. Cameron, S. Murad, H. McLelland, A. Asenov, M.R.S. Taylor, M.C. Holland and S.P. Beaumont

Indexing terms: High electron mobility transistors, Semiconductor

The authors report how the performance of  $0.12\mu m$  GaAs pHEMTs is improved by controlling both the gate recess width, using selective dry etching; and the gate position in the source drain gap, using electron beam lithography. pHEMTs with a transconductance of 600 mS/mm, off state breakdown voltages >2 V,  $f_T$  of 120 GHz,  $f_{max}$  of 180 GHz and MAG of 13.5 dB at 60 GHz are reported.

Introduction: The Schottky gate contact of a GaAs p HEMT is usually formed in a shallow etched recess. The depth of the recess sets the gate to channel spacing and controls the gate source capacitance, transconductance, pinch off voltage and high frequency current gain; and the extent of the recess towards the drain affects the drain extension of the gate depletion region and controls the feedback elements: gate drain capacitance, output conductance and hence high frequency power gain. The width of the recess also dramatically affects the access resistance of the device [1]. It is desirable to engineer the size and shape of the recess to control device performance. The recess is typically formed either by wet or dry etching, both of which may be either selective or non-selective [2-5]. When a non-selective etch is used the gate recess depth is usually controlled by etching until a desired saturated drain current is achieved [2, 4]. No independent control over the width of the recess is afforded. Where a selective etch is used, tighter control over the etch depth is generally achieved as the depth is accurately set by the epitaxial layer structure [3, 5]. In addition, lateral over etching of the recess can be used to increase the gate recess width provided the selectivity is high enough to prevent further vertical etching. Wet etches do not generally have sufficient selectivity to allow extended overetching, and wetting effects can also degrade lateral etch control. With selective dry etching issues such as ion induced damage, material deposition and etch anisotropy must be addressed. Here we report on the use of a highly selective low damage process employing SiCl<sub>4</sub>/SiF<sub>4</sub>/O<sub>2</sub> to engineer the gate recess of 0.12 µm GaAs p HEMTs.

Fabrication: The GaAs pHEMT layer structure was grown as follows: 600nm GaAs buffer, 10nm In<sub>0.3</sub>Ga<sub>0.7</sub>As channel, 2.5nm  $Al_{0.2}Ga_{0.8}As$  spacer,  $7\times10^{12}cm^{-2}$  Si delta doping layer, 10nm  $Al_{0.2}Ga_{0.8}As$  barrier, 2.5nm GaAs surface buffer, 5nm  $Al_{0.2}Ga_{0.8}As$ etch stop layer and  $30\,\mathrm{nm}~4\times10^{18}\mathrm{cm}^{-3}$  GaAs cap. This layer structure is fairly conventional except that a thin GaAs surface buffer layer is used to prevent deep oxidation of the AlGaAs exposed in the gate recess. In addition the structure is quite aggressively scaled for optimum short gate device performance in terms of In content, doping density and channel depth. After removal of the GaAs cap the layer was found to have  $N_{sh}$  of  $2.4 \times 10^{12}$  cm<sup>-2</sup> and  $\mu_H$ of 4000cm²/Vs. The pHEMT fabrication process has been described in detail by Asenov et al. [6]. and further evidence for low damage etching and details of the SiCl<sub>4</sub>/SiF<sub>4</sub>/O<sub>2</sub> process was reported by Murad et al. [7]. We used SiCl<sub>4</sub>/SiF<sub>4</sub>, which forms a very tight recess and does not etch laterally, to produce pHEMTs in which the gate fills the recess (0nm gate offset). The addition of oxygen enhances the lateral etch rate, and allowed devices with 25 and 50nm gate offsets to be produced. Electron beam lithography allowed the position of the gate to be varied with respect to the source contact. A number of devices with 0, 25 and 50nm gate offsets and 0.5 and 0.75 µm spacing between the edge of the source and centre of the gate were fabricated and characterised at DC. The RF performance was evaluated by on wafer measurement from 0-60GHz for the following four devices: 0nm gate offset devices with 0.5 and 0.75 µm source to gate spacing, a 25 nm gate offset device with 0.75 µm spacing and a 50 nm offset device with 0.5 µm spacing.

Device performance: DC measurements of the off state breakdown voltage were made with a constant drain current of 1mA/mm, following the procedure of Bahl and del Alamo [8]. Devices with 25 and 50nm gate offsets showed an off state breakdown of  $BV_{ds}$  = 2.14V ( $1\sigma = 0.23V$ ) while 0nm offset devices exhibited variable and lower breakdown in the range  $BV_{ds} = 0.5$  to 1.3V. The variation was probably caused by variations in the contact area between the edge of the gate and the highly doped GaAs cap. Similarly the 25 and 50 nm offset devices had  $BV_{dg} = 4.77 \text{V}$  ( $1\sigma =$ 0.70V) and the 0nm devices had  $BV_{dg} = 3.4$  to 4.4V. All the devices exhibited an on state ( $V_{gs} = 0$ V) breakdown voltage of 5V, characterised by a rapid and destructive increase in drain current probably caused by breakdown in the channel. These results agree with those of Geiger et al. [9], who reported an on state breakdown voltage of 5V, independent of the recess size, and recess dependent off state breakdown behaviour. Otherwise we found no variation in the DC parameters against gate source spacing and recess width. Average values from four separate fabrication lots and best standard deviation values were:  $I_{dss} = 630 \text{mA/mm}$  ( $1\sigma =$ 41 mA/mm),  $g_m = 600 \text{ mS/mm} (1\sigma = 41 \text{ mS/mm})$  and  $V_{th} = -0.97 \text{ V}$  $(1\sigma = 16\text{mV}).$

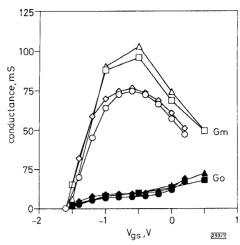

**Fig. 1** pHEMTs with filled gate recess, 0nm, have the highest transconductance, the gate source spacing has less influence, at  $V_{\rm ds}=1.5\,V$  shown, output conductance is similar for all devices

$\bigcirc$  50nm, 0.75µm;  $\diamondsuit$  25nm, 1µm;  $\square$  0nm, 1µm;  $\triangle$  0nm, 0.75µm

Fig. 1 shows the transconductance  $G_m$  and output conductance  $G_o$ , at  $V_{ds}=1.5$ V, extracted by a small signal equivalent circuit fit to the measured s-parameters. Higher  $G_m$  was observed for devices in which the gate was positioned close to the source, but much larger  $G_m$  was obtained for the pHEMTs in which the gate filled the recess compared with devices with significant gate offset. Similar behaviour was observed for  $C_{gs}$  and so an extrinsic  $f_T$  of 120 GHz was obtained for all devices. All of the pHEMTs have

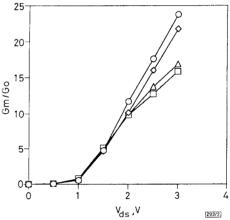

Fig. 2 pHEMTs with largest gate offset have highest  $G_{\rm m}/G_{\rm o}$  ratio, the gate source spacing has a smaller influence

$V_{gs} = 0 \text{ V}$  symbols as for Fig. 1

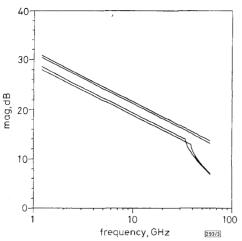

similar threshold voltage and peak  $G_m$  occurred at similar gate bias, suggesting that the gate to channel separation did not vary. Little variation in the output conductance  $(G_o)$  can be observed in Fig. 1. However,  $G_o$  is strongly dependent on the drain bias and, as Fig. 2 shows, variations in the ratio of  $G_m/G_o$  are observed at large  $V_{ds}$ . Similar trends were observed with  $C_{ss}/C_{gd}$ . In all the devices, as the drain field increases the gate depletion region extends toward the drain and  $G_o$  is reduced. The effect is particularly strong for the 25 and 50nm gate offset devices, although there is also a small reduction in  $G_o$  brought about by moving the gate closer to the source. The ratio of  $G_m/G_o$  and  $C_{gs}/C_{gd}$  determine the high frequency power gain, and thus the best gain is found at  $V_{ds}=3V$  as shown in Fig. 3. The 50nm gate offset device has the highest MAG of 13.5dB at 60GHz which gives a cutoff frequency  $(f_{max})$  of 180GHz.

The size of the gate recess and the position of the gate affects the access resistances  $R_s$  and  $R_d$ . To examine the effect of the recess size only, the extracted values of  $R_s$  and  $R_d$  were added: values of 1 to 1.5, 3.5 and 4.3 $\Omega$  were found for the 0, 25 and 50nm

**Fig. 3** pHEMTs with gate offset of 50nm have the best magnitude of 13.5dB at 60GHz and  $f_{mas}$  of 180GHz (at  $V_{ds}=3V$  and  $V_{gs}=0V$ ), gate source spacing has negligible influence

Lower two lines: 0nm Above these: 25nm Top line: 5nm

gate offset devices, respectively. Very little dependence on recess width and gate position was found for the other equivalent circuit elements, except for gate inductance ( $L_{\rm g}$ ) which was strongly dependent on the recess size with values of 1.1 to 1.3, 4.2 and 13.6pH obtained for the 0, 25 and 50nm gate offset *p*HEMTs. This indicates that the recess alters the shape of the magnetic field surrounding the gate.

Conclusions: We have used selective reactive ion etching in SiCl<sub>4</sub>/SiF<sub>4</sub>/O<sub>2</sub> to engineer the gate recess of a 0.12 $\mu$ m pseudomorphic In<sub>0.30</sub>GaAs/GaAs HEMT. Improved off state breakdown voltage, BV<sub>ds</sub> > 2V, MAG = 13.5dB at 60GHz and  $f_{max}$  = 180GHz were achieved. Other parameters such as DC transconductance, saturated drain current density, threshold voltage and  $f_T$  were not dependent on the gate offset. The gate position was also varied and was found to have a much smaller influence than the recess.

© IEE 1996 5 February 1996

Electronics Letters Online No: 19960489

N.J. Cameron, S. Murad, H. McLelland,

N.I. Cameron, S. Murad, H. McLelland, A. Asenov, M.R.S. Taylor, M.C. Holland and S.P. Beaumont (Nanoelectronics Research Centre, Department of Electronics and Electrical Engineering, University of Glasgow, Glasgow, Scotland, G12 8LT, United Kingdom)

## References

- 1 ASENOV, A., CAMERON, N., TAYLOR, M., BEAUMONT, S.P., and BARKER, J.R.: 'Numerical study of the series resistance in deepsubmicrometer recess gate MESFETs'. IEEE Proc. Europ. Gallium Arsenide and Rel. III-V Compounds Applications Symp., 1994, p. 373

- 2 THAYNE, I.G., PAULSEN, A., and BEAUMONT, S.P.: 'A study of wet chemical gate recess etching of pseudomorphic In<sub>0.15</sub>GaAs/GaAs HEMTs', Semicond. Sci. Technol., 1994, 9, pp. 1143–1147

- 3 TONG, M., BALLEGEER, D.G., KETTERSON, A., ROAN, E.J., CHENG, K.Y., and ADESIDA, I.: 'A comparative study of wet and dry selective etching processes for GaAs/AlGaAs/InGaAs pseudomorphic MODFETs', J. Electron. Mater., 1992, 21, (1), pp. 9–15

- 4 CAMERON, N.I., BEAUMONT, S.P., WILKINSON, C.D.W., JOHNSON, N.P., KEAN, A.H., and STANLEY, C.R.: 'An investigation of CH<sub>4</sub>/H<sub>2</sub> reactive ion etching damage to thin heavily doped GaAs metal-semiconductor field effect transistors layers during gate recessing', J. Vac. Sci. Technol., 1990, B8, (6), pp. 1966–1969

- 5 CAMERON, N.I., FERGUSON, S., TAYLOR, M.R.S., BEAUMONT, S.P., HOLLAND, M., TRONCHE, C., SOULARD, M., and LADBROOKE, P.H.: 'Selectively dry gate recessed GaAs MESFETs, HEMTs and MMICs', J. Vac. Sci. Technol., 1993, B11, (6), pp. 2244

- 6 ASENOV, A., BABIKER, S., CAMERON, N., MURAD, S., HOLLAND, M., and BEAUMONT, S.P.: 'Basics of Pseudomorphic HEMTs; technology and numerical simulation' To be published in BALKANSKI, M. (Ed.): 'Devices based on low dimensional semiconductor structures' (Kluwer Academic Publishers, The Netherlands)

- MURAD, S.K., CAMERON, N.I., BEAUMONT, S.P., and WILKINSON, C.D.W.: 'The effects of O<sub>2</sub> addition to SiCl<sub>4</sub>/SiF<sub>4</sub> and the thickness of capping layer on gate recess etching of GaAs-pseudomorphic high electron mobility transistors', Submitted to Electron Ion and Photon Beams and Nanotechnology, 1996

- 8 BAHL, S.R., and DELALAMO, J.A.: 'A new drain-current injection technique for the measurement of off-state breakdown voltage in FETs', IEEE Trans. Electron Devices, 1993, ED-40, (8), pp. 1558

- 9 GEIGER, D., DICKMANN, J., and KOHN, E.: 'Recess dependent breakdown behaviour of GaAs-HFET's', IEEE Electron Device Lett., 1995, EDL-16, (1), pp. 30

## lon-implanted 0.4 µm wide 2-D MESFET for low power electronics

M.J. Hurt, W.C.B. Peatman, R. Tsai, T. Ytterdal, M. Shur and B.J. Moon

Indexing terms: MESFETs, Ion implantation

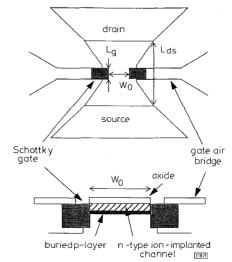

Two-dimensional (2-D) MESFETs with 0.4µm channel widths have been fabricated on ion-implanted *n*-GaAs material. The 2-D MESFET uses sidewall Schottky contacts on either side of an Sidoped channel to laterally modulate the current. The peak drain current is 370mA/mm and the peak transconductance is 295mS/mm at room temperature. The narrow channel effect and channel length modulation have been reduced in this device.

Introduction: Recently, we proposed and fabricated a new transistor called the 2-D metal-semiconductor field effect transistor (2-D MESFET) in which sidewall Schottky contacts on either side of an AlGaAs/InGaAs/GaAs heterostructure laterally deplete the narrow 2-D electron gas (2-DEG) channel [1 - 3]. One of the principal advantages of this device is that the narrow channel effect (NCE) [4], which leads to parasitic currents at the gate edges in a top-gated structure, is eliminated by the unique sidewall gate geometry. Thus, 2-D MESFET device widths may be scaled to deep submicrometre dimensions without degradation of the electrical characteristics [5]. In this Letter, we investigate a new 2-D MESFET fabricated on ion-implanted, bulk n-GaAs material. The ion-implanted 2-D MESFET uses the same geometry as the PHEMT 2-D MESFET and therefore experiences no deterioration from the NCE at submicrometre widths. In addition, the ionimplanted GaAs material is cheaper to fabricate and more compatible with commercial GaAs IĈ fabrication processes than the MBE-grown AlGaAs/InGaAs/GaAs heterostructure devices. Also, despite a lower mobility in the bulk n-GaAs than in the InGaAs structure, preliminary comparisons indicate that the DC electrical characteristics of submicrometre ion-implanted 2-D MESFETs are comparable to those of submicrometre PHEMT 2-D MESFETs

Fig. 1 Top view and cross-section of ion-implanted 2-D MESFET