# Suppression of Random Dopant-Induced Threshold Voltage Fluctuations in Sub-0.1- $\mu$ m MOSFET's with Epitaxial and $\delta$ -Doped Channels

Asen Asenov, Member, IEEE, and Subhash Saini

Abstract—A detailed three-dimensional (3-D) statistical "atomistic" simulation study of fluctuation-resistant sub-0.1-\(\mu\) m MOS-FET architectures with epitaxial channels and delta doping is presented. The need for enhancing the fluctuation resistance of the sub-0.1- $\mu$ m generation transistors is highlighted by presenting summarized results from atomistic simulations of a wide range of conventional devices with uniformly doped channel. According to our atomistic results, the doping concentration dependence of the random dopant-induced threshold voltage fluctuations in conventional devices is stronger than the analytically predicted fourth-root dependence. As a result of this, the scaling of such devices will be restricted by the "intrinsic" random dopant-induced fluctuations earlier than anticipated. Our atomistic simulations confirm that the introduction of a thin epitaxial layer in the MOSFET's channel can efficiently suppress the random dopantinduced threshold voltage fluctuations in sub-0.1- $\mu$ m devices. For the first time, we observe an "anomalous" reduction in the threshold voltage fluctuations with an increase in the doping concentration behind the epitaxial channel, which we attribute to screening effects. Also, for the first time we study the effect of a delta-doping, positioned behind the epitaxial layer, on the intrinsic threshold voltage fluctuations. Above a certain thickness of epitaxial layer, we observe a pronounced anomalous decrease in the threshold voltage fluctuation with the increase of the delta doping. This phenomenon, which is also associated with screening, enhances the importance of the delta doping in the design of properly scaled fluctuation-resistant sub-0.1-µm MOSFET's.

Index Terms—Doping, fluctuations, MOSFET, semiconductor device simulation, silicon devices, threshold.

# I. INTRODUCTION

HEN MOSFET's are scaled down to deep submicrometer dimensions, the "intrinsic" variation in the transistor parameters arising from the small number of discrete dopants and their random position in the channel depletion region starts to become increasingly pronounced. This problem, recognized almost three decades ago [1], [2], is confirmed now experimentally [3]–[8] and in three-dimensional (3-D) continuous charge [9]–[11] and "atomistic" device simulations [12]–[14]. Simple analytical models, describing, for example, the random dopant-induced threshold voltage fluctuations,

Manuscript received January 19, 1999; revised March 31, 1999. This work was supported by NASA-Ames under Grant NAG 2-1241. The review of this paper was arranged by W. Weber.

A. Asenov is with the Device Modeling Group, Department of Electronics and Electrical Engineering, The University of Glasgow, Glasgow G12 8LT, Scotland, U.K. (e-mail: A.Asenov@elec.gla.ac.uk).

S. Saini is with the Numerical Aerospace Simulation (NAS) System Division, NASA Ames Research Centre, Moffett Field, CA 94035-1000 USA. Publisher Item Identifier S 0018-9383(99)06019-0.

have also been developed [3], [11], [15], [16]. At the same time, the integrated circuits are becoming more sensitive to the fluctuation in the MOSFET characteristics due to the reduction in the supply voltage to reduce the power consumption and to sustain the reliability. The intrinsic parameter variations and the corresponding transistor mismatch start to impinge on the performance and functionality of analog [8] and logical [17] circuits and SRAM's [18].

A relatively easy way to reduce the intrinsic parameter fluctuations, without a major change in the MOSFET architecture, is the appropriate tailoring of the channel doping profile. Results of continuous-charge 3-D numerical simulations [9], [11] have shown that the introduction of a thin, low doped layer in the MOSFET channel, immediately below the interface, can efficiently suppress the threshold voltage fluctuations. This approach has been successfully demonstrated experimentally in MOSFET's with low doped epitaxial channels [15]. The introduction of a low doped region in the channel, however, makes the corresponding devices more susceptible to short channel effects. This drawback can be compensated to some extent by introducing a delta doping below the epitaxial channel [19].

In this paper we use an efficient 3-D "atomistic" simulation technique [20] to study the random dopant-induced threshold voltage fluctuations in sub-0.1- $\mu$ m MOSFET's with epitaxial channels and delta doping. For the first time, effects associated with screening of the random dopant charge in the depletion layer behind the epitaxial channel and in the partially depleted delta-doping layer are captured in our simulations. The screening leads to an "anomalous" reduction of the threshold voltage fluctuations with the increase of the delta doping or the uniform doping density below the epitaxial channel. This offers new means for the design of fluctuation-resistant MOSFET's.

In the next section we summarize our atomistic results for the threshold voltage fluctuations in conventional sub-0.1- $\mu$ m MOSFET's, highlighting the need for development of fluctuation-resistant devices. Section III, after a brief review of various fluctuation-resistant FET architectures, introduces the epitaxial and delta-doped devices which are the main subject of this investigation. In Section IV we study in detail the random dopant-induced threshold voltage fluctuations in MOSFET's with low doped epitaxial channels. Finally, Section V investigates the impact of a delta-doped layer, placed behind the epitaxial channel, on the threshold voltage fluctuations.

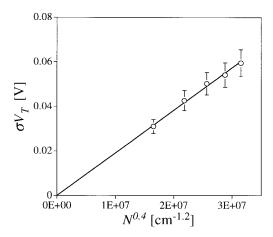

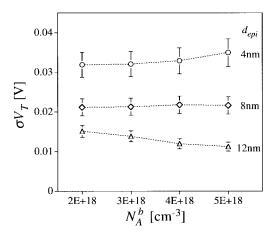

Fig. 1. Threshold voltage standard deviation  $\sigma V_T$  as a function of the doping concentration  $N_A$  for a conventional n-channel MOSFET with uniform doping distribution in the channel depletion region,  $L_{\rm eff}=0.05~\mu{\rm m}$ ,  $W_{\rm eff}=0.05~\mu{\rm m}$ , and  $t_{\rm ox}=3~{\rm nm}$ . Samples of 200 devices.

# II. CONVENTIONAL MOSFET'S

In this section we summarize some important results related to random dopant-induced threshold voltage fluctuations in sub-0.1-µm MOSFET's with conventional architecture. The conventional devices have typically a high doping concentration in the channel region for suppression of short channel effects and threshold voltage control. With a good degree of approximation, the doping concentration in the channel depletion layer can be considered uniform. We investigate the random dopant-induced threshold voltage fluctuations in such devices by using an efficient statistical atomistic simulation approach described in detail elsewhere [20]. The simulations are based on a 3-D solution of the Poisson equation where the doping charge is introduced as discrete, randomly placed, individual dopants. At low drain voltage, the current is calculated by solving a simplified current continuity equation. A current criterion  $10^{-8}W_{\text{eff}}/L_{\text{eff}}$  [A] is used for determining the threshold voltage. The threshold voltage standard deviation  $\sigma V_T$  is extracted from the simulation of samples containing 200 MOSFET's with microscopically different distributions of dopants. The corresponding relative standard deviation of the extracted  $\sigma V_T$  is 5% for all results presented in this paper.

When the channel length is scaled down to dimensions below  $0.1~\mu\mathrm{m}$ , the doping concentration in the channel region has to be increased to levels above  $1\times10^{18}~\mathrm{cm}^{-3}$ . The results of our atomistic simulations show that the doping concentration dependence of the random dopant-induced threshold voltage fluctuations in sub-0.1- $\mu\mathrm{m}$  MOSFET's with conventional architecture is stronger than the  $N^{0.25}$  dependence suggested by most of the analytical models [3], [11], [15], [16]. Fig. 1 illustrates the "atomistically" simulated dependence of  $\sigma V_T$  as a function of the doping concentration  $N_A$  for an n-channel MOSFET's with uniform doping distribution in the channel depletion region, effective channel length  $L_{\rm eff}=0.05~\mu\mathrm{m}$ , effective channel width  $W_{\rm eff}=0.05~\mu\mathrm{m}$ , and oxide thickness  $t_{\rm ox}=3~\mathrm{nm}$ . The data in Fig. 1 can be approximated well with the following expression:

$$\sigma V_T = 1.914 \times 10^{-9} N_A^{0.401} \quad [V]. \tag{1}$$

The discrepancy between the above doping concentration dependence and the analytical predictions is associated with the fact that the refereed analytical models take into account only the fluctuation of the total number of dopants in the channel depletion region but do not include the effects associated with the random position of the individual dopants. The stronger doping concentration dependence suggests that the problems associated with the random dopant-induced parameter fluctuations can be more restrictive to the scaling of the conventional MOSFET than anticipated until now.

Our atomistic simulations have, however, confirmed that the theoretically predicted  $1/\sqrt{L_{\rm eff}W_{\rm eff}}$  dependence of  $\sigma V_T$  and its proportionality to  $t_{\rm ox}$  remain valid in properly scaled sub-0.1- $\mu$ m MOSFET's with uniform channel doping. This observation allows (1) to be transformed into an useful "empirical" expression relating  $\sigma V_T$  to the basic structural MOSFET parameters

$$\sigma V_T = 3.19 \times 10^{-8} \frac{t_{\rm ox} N_A^{0.401}}{\sqrt{L_{\rm eff} W_{\rm eff}}}$$

[V] (2)

where all dimensions are in centimeters. Equation (2) has been obtained by fitting our atomistic results in the range of  $L_{\rm eff}$  from 0.03 to 0.1  $\mu$ m,  $W_{\rm eff}$  from 0.05 to 0.5  $\mu$ m,  $t_{\rm ox}$  from 1 to 6 nm, and  $N_A$  from 1  $\times$  10<sup>18</sup> cm<sup>-3</sup> to 5  $\times$  10<sup>18</sup> cm<sup>-3</sup>.

Let us project the above results toward the end of the Silicon Roadmap, according to which after the year 2010 [21], the effective MOSFET channel length is expected to be below 0.05  $\mu$ m.  $\sigma V_T$  larger than 30 mV can be expected in 0.05  $\times$  0.05  $\mu$ m MOSFET's with conventional architecture. This estimation is based on the assumption that the oxide thickness cannot be scaled bellow 1.5 nm and channel doping concentrations larger than  $4 \times 10^{18}$  cm<sup>-3</sup> will be required to prevent the short channel effects in such devices with conventional architecture. In the corresponding circuits with 0.1 to 10 billion transistors, worst case threshold voltage deviations of  $6\sigma$  must be considered. This translates to 180 mV worst case threshold voltage deviation in the transistors with square topology. It is clear that such levels of intrinsic threshold voltage fluctuations will be unacceptable even for digital applications, bearing in mind that threshold voltages below 0.3 V and supply voltages below 1 V are projected for this generation of devices.

# III. FLUCTUATION-RESISTANT ARCHITECTURES

The radical solution to the problems associated with random dopant-induced fluctuations in small MOSFET's is to remove completely the dopants from the channel region. Undoped channel MOSFET's with double gate [22], surrounding gate [23], and Schottky source and drain [24] have been proposed primarily to suppress short channel effects in devices scaled to decanano dimensions. Simulations predict that such devices will remain operational to channel lengths below 10 nm [24], [25] and hence may provide a solution to the problem of dopant fluctuations once and for all. Building and integration of such devices, however, is a serious technological challenge. Technologically difficult areas are the use of SOI with very thin silicon films (less than 10 nm) and the fabrication and connection of the back gate in the double gate devices; the

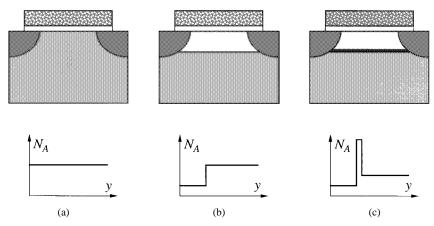

Fig. 2. Schematic structure and doping profile of (a) a conventional MOSFET with uniform doping in the channel region, (b) an epitaxial MOSFET, and (c) an epitaxial MOSFET with a delta-doping layer behind the epitaxial channel.

uniform vertical low damage etching, uniform gate oxidation, and the drain integration in the vertical surrounding gate architectures; and the gate isolation above the Schottky contacts in the aggressively scaled Schottky source/drain FET's.

A less technologically demanding modification of the MOS-FET architecture, which will enhance the dopant fluctuation immunity, is the introduction of a low-doped epitaxial layer in the channel. Low-doped channel MOSFET's fabricated by the epitaxial growth of a thin undoped Si layer were introduced in the early 1990's [26], and their importance for the scaling of the MOSFET's to sub-0.1- $\mu$ m dimensions was further justified in [27]. The initial drive behind the introduction of lowdoped epitaxial channels was the expectation for mobility and transconductance enhancement, together with the introduction of new means for threshold voltage and subthreshold slope control. Later, based on continuous charge numerical simulations [9], [11] and elaborated analytical models [11], [15], [28], it has been realized that the retrograde channel doping profile in the epitaxial devices will also significantly suppress the random dopant-induced threshold voltage fluctuations. These theoretical predictions were also confirmed experimentally [15].

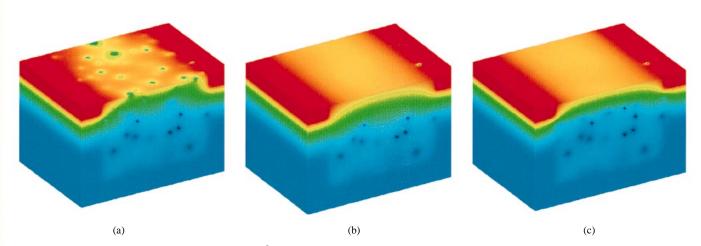

The introduction, however, even of a thin intrinsic epitaxial layer in the channel makes the corresponding MOSFET's more susceptible to short channel effects and will require higher doping concentrations behind the channel compared to the conventional devices. This, in turn, will increase the source and drain capacitances and will reduce the breakdown voltage. A carefully positioned  $\delta$ -doping layer below the epitaxial channel [19] can provide an efficient short channel and threshold voltage control, reducing to some extent the detrimental heavy doping effects. Using our atomistic simulation approach, we study for the first time the effect of such a delta-doped layer on the threshold voltage fluctuations. Fig. 2 illustrates schematically the structure and the doping profiles of the epitaxial and delta-doped devices in comparison with a conventional MOSFET. Idealized abrupt step profiles and a plane delta doping are used in the following simulations. The results in the next two sections are for MOSFET's with  $W_{\rm eff}=L_{\rm eff}=0.05~\mu{\rm m}$ , oxide thickness  $t_{\rm ox}=3~{\rm nm}$ , and junction depth  $x_j = 10$  nm. This choice of device dimensions

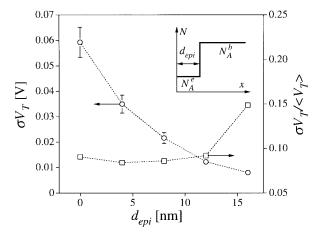

Fig. 3. Standard deviation of the threshold voltage  $\sigma V_T$  as a function of the thickness of the epitaxial channel layer  $d_{\rm epi}$  for a set of MOSFET's with  $L_{\rm eff}=0.05~\mu{\rm m},\,W_{\rm eff}=0.05~\mu{\rm m},\,N_A^e=1\times10^{15}~{\rm cm}^{-3},\,N_A^b=5\times10^{18}~{\rm cm}^{-3},$  and  $t_{\rm ox}=3$  nm. Samples of 200 transistors.

provides a basis for comparison with the wide range of results for MOSFET's with conventional architecture published in our previous paper [14].

# IV. EPITAXIAL CHANNEL MOSFETS

Fig. 3 illustrates the dependence of  $\sigma V_T$  on the thickness  $d_{\mathrm{epi}}$  of the epitaxial channel layer for a 0.05 imes 0.05  $\mu\mathrm{m}^2$ MOSFET with  $t_{\rm ox}=3$  nm. The background doping in the epitaxial layer is assumed to be  $N_A^e=1\times 10^{15}~{\rm cm}^{-3}$ , and the doping behind it is  $N_A^b=5\times 10^{18}~{\rm cm}^{-3}$ .  $\sigma V_T$  decreases very rapidly for the first 10 nm of epitaxial layer and then tends to saturate. An epitaxial layer with thickness 12 nm reduces the threshold voltage fluctuation almost five times. However, the thickness of the epitaxial layer has to be chosen primarily not to compromise the short channel effect immunity of the corresponding MOSFET. The maximum allowable thickness depends on the channel length, oxide thickness, the junction design, and the doping profile behind the channel. Simulations carried out with a standard commercial 2-D simulator indicate that the aspect ratio between the channel length and the thickness of the epitaxial layer  $L_{\rm eff}/d_{\rm epi}$  should be greater than five. This translates to epitaxial layer thicknesses less than

Fig. 4. Standard deviation of the threshold voltage  $\sigma V_T$  as a function of the doping concentration in the epitaxial layer  $N_A^e$  for a 0.05  $\times$  0.05  $\mu \text{m}^2$  MOSFET with  $d_{\rm epi}=12$  nm,  $t_{\rm ox}=3$  nm,  $N_A^b=5\times 10^{18}$  cm $^{-3}$ . Samples of 200 transistors.

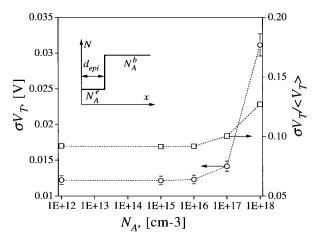

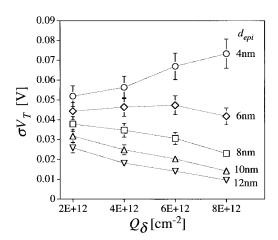

Fig. 5. Standard deviation of the threshold voltage  $\sigma V_T$  as a function of the doping concentration  $N_A^b$  behind the epitaxial layer for a set of  $0.05\times0.05$   $\mu\mathrm{m}^2$  MOSFET's with  $t_\mathrm{ox}=3$  nm,  $N_A^e=1\times10^{15}$  cm $^{-3}$ , and different thickness  $d_\mathrm{epi}$  of the epitaxial layer. Samples of 200 transistors.

Fig. 6. Standard deviation of the threshold voltage  $\sigma V_T$  as a function of the delta-doping dose  $Q_\delta$  for a set of 0.05  $\times$  0.05  $\mu \mathrm{m}$  MOSFET's with  $t_{\mathrm{ox}}=3$  nm,  $N_A^b=1\times 10^{18}$  cm $^{-3}$ ,  $N_A^e=1\times 10^{15}$  cm $^{-3}$ , and different thicknesses  $d_{\mathrm{epi}}$  of the epitaxial layer. Samples of 200 transistors.

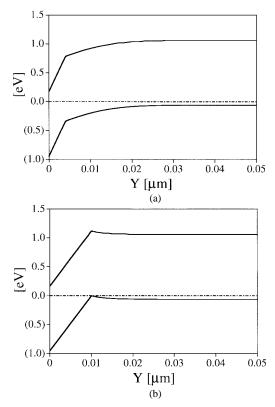

Fig. 7. Band diagrams in the middle of the channel in two epitaxial  $\delta\text{-doped}$  MOSFET's with  $N_A=1\times10^{18}~\mathrm{cm^{-3}}$  and  $t_{\rm ox}=3~\mathrm{nm},\,Q_\delta=8\times10^{12}~\mathrm{cm^{-2}},$  and different thickness of the epitaxial layer: (a)  $d_{\rm epi}=4~\mathrm{nm},$  (b)  $d_{\rm epi}=10~\mathrm{nm}.$

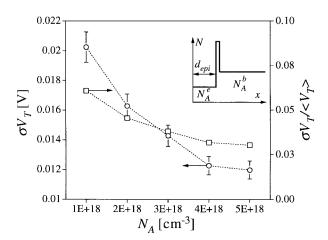

Fig. 8. Standard deviation of the threshold voltage  $\sigma V_T$  as a function of the doping  $N_b^A$  behind the epitaxial layer for a 0.05  $\times$  0.05  $\mu$ m $^2$  MOSFET with  $t_{\rm ox}=3$  nm,  $N_A^e=1\times 10^{15}$  cm $^{-3}$ ,  $d_{\rm epi}=10$  nm, and  $Q_\delta=3\times 10^{12}$  cm $^{-2}$ . Samples of 200 transistors.

20 nm in a 0.1- $\mu$ m MOSFET and less than 10 nm in a 0.05- $\mu$ m MOSFET. We do not present here values for the average threshold voltage obtained from the atomistic simulation, which can be misleading from a device design point of view, since our simulations do not include the quantization in the inversion layer and the poly-depletion effect. However, in order to indicate some of the problems associated with the threshold voltage control in epitaxial MOSFET's in Fig. 3 and

Fig. 9. Potential distributions in three  $0.05 \times 0.05 \ \mu \text{m}^2$  MOSFETs: (a) MOSFET with conventional architecture, (b) MOSFET with epitaxial channel, and (c) MOSFET with epitaxial channel and delta doping.

in some of our next figures, we present the ratio between  $\sigma V_T$  and the average threshold voltage  $\langle V_T \rangle$  calculated from the simulated samples.

To grow an epitaxial layer with low boron concentration on top of the heavily doped substrate may be complicated, because the boron has a tendency to segregate upwards during the epitaxial growth. Diffusion associated with the post epitaxial processing steps may also increase the boron concentration in the epitaxial layer. It is technologically important to have an indication of what the tolerable doping level is in the epitaxial layer from a threshold voltage fluctuation point of view. The dependence of  $\sigma V_T$  on the doping concentration in the epitaxial layer  $N_A^e$  is presented in Fig. 4 for a 0.05  $\times$  0.05  $\mu \rm m^2$  MOSFET with  $d_{\rm epi}=12$  nm,  $t_{\rm ox}=3$  nm, and  $N_A^b=5\times 10^{18}~\rm cm^{-3}$ . Doping levels in the epitaxial layer up to  $10^{16}~\rm cm^{-3}$  do not noticeably affect the threshold voltage fluctuations in the above device. For doping concentrations above  $10^{17}~\rm cm^{-3}$   $\sigma V_T$  increases rapidly.

The dependence of  $\sigma V_T$  on the doping concentration  $N_A^b$ behind the epitaxial layer is illustrated in Fig. 5 for a set of  $0.05\times0.05~\mu\mathrm{m}^2$  MOSFET's with  $t_\mathrm{ox}=3$  nm,  $N_A^e=1\times10^{15}$ cm<sup>-3</sup>, and different thicknesses of epitaxial layer. In contrast to the conventional MOSFET's, in the epitaxial devices we observe for the first time either an increase or decrease of  $\sigma V_T$  as a function of the doping concentration, depending on the thickness of the epitaxial layer. The anomalous reduction of  $\sigma V_T$  with the increase of  $N_A^b$  in the devices with thicker epitaxial layer is associated with screening. When the epitaxial layer is relatively thick, the width of the depletion layer in the heavily doped region beneath the epitaxial layer becomes rather small. The holes in the heavily doped region start to screen the charge of the discrete random acceptors in the thin depletion layer, reducing their effect on the threshold voltage fluctuation. Any further increase in the doping concentration reduces further the width of the depletion layer and enhances the screening. Screening effects from the free carriers in the substrate are not present in the available analytical models and have not been reported in the previous continuous charge 3-D simulations of doping fluctuation effects in epitaxial channel MOSFET's. We believe that the fine resolution of the atomistic simulations, down to an individual dopant level, in conjunction with the large statistical samples in our simulations, are instrumental in capturing the screening effects.

# V. THE EFFECT OF THE DELTA DOPING

The introduction of a boron delta doping behind the epitaxial layer in n-channel MOSFET's will allow the doping concentration  $N_A^b$ , which surrounds the pn-junctions, to be reduced without aggravating the short channel effects. When partially depleted, the delta doping will act as a ground plane efficiently suppressing the short channel effects. The influence of the delta-doping dose  $Q_{\delta}$  on the threshold voltage fluctuations is illustrated in Fig. 6 for a set of 0.05  $\times$  0.05  $\mu\mathrm{m}^2$  MOSFET's with  $t_\mathrm{ox}=3$  nm,  $N_A^b=1\times10^{18}$  cm $^{-3},~N_A^e=1\times10^{15}$ cm<sup>-3</sup>, and different thicknesses of the epitaxial layer. For devices with a thin epitaxial layer (4 nm),  $\sigma V_T$  increases with the increase of  $Q_{\delta}$ . However, the same dependence passes through a maximum for devices with an intermediate thickness (6 nm) of the epitaxial layer and follows a monotone decrease for devices with a thicker epitaxial layer (>8 nm). This behavior, reported here for the first time, is also associated with screening. Its explanation becomes clear in Fig. 7 where the band diagrams in the middle of the channel for two of the MOSFET's from Fig. 6, with 4 nm and 10 nm epitaxial layers, respectively, are plotted for  $V_G = V_T$ . In the device with the thinner epitaxial layer (4 nm), the delta doping is completely depleted and, in addition to this, a depletion layer in the region behind the delta-doping is also present. All randomly placed dopants in the delta-doping layer and in the depletion layer behind it contribute to the threshold voltage fluctuations. In the device with a thicker epitaxial layer (10 nm), the delta doping is only partially depleted. The high residual hole concentration in the delta-doped layer screens the charge of the random discrete dopants in it.

If the delta doping is only partially depleted, any increase in the doping concentration  $N_A^b$  behind the epitaxial channel will result in an anomalous reduction of  $\sigma V_T$ . This is illustrated in Fig. 8 where the dependence of  $\sigma V_T$  as a function of  $N_A^b$  is

plotted for a 0.05  $\times$  0.05  $\mu\mathrm{m}^2$  MOSFET's with  $t_\mathrm{ox}=3$  nm,  $N_A^e=1\times10^{15}~\mathrm{cm}^{-3},$   $d_\mathrm{epi}=10$  nm, and  $Q_\delta=6\times10^{12}~\mathrm{cm}^{-2}.$

Due to the anomalous dependence of  $\sigma V_T$  on  $Q_\delta$ , for a range of thicknesses of the epitaxial layer, transistors with delta doping and a relatively low level of doping behind the epitaxial layer may have threshold voltage fluctuation resistance comparable to this of transistors without delta doping but with a much higher level of doping behind the epitaxial layer. For example, a  $0.05\times0.05~\mu\mathrm{m}^2$  MOSFET's with  $d_{\mathrm{epi}}=10$  nm, no delta doping, and  $N_A^b=5\times10^{18}$  cm<sup>-3</sup> will have the same  $\sigma V_T=0.016$  V as its counterpart with delta doping  $Q_\delta=6.5\times10^{12}$  cm<sup>-2</sup> and  $N_A^e=1\times10^{18}$  cm<sup>-3</sup>. This gives an additional degree of freedom in tailoring the threshold voltage and reducing the short channel effects in the corresponding devices.

Finally, Fig. 9 compares the typical atomistic potential distributions at the Si/SiO $_2$  interface in three 0.05  $\times$  0.05  $\mu m^2$  MOSFETs: one with conventional architecture, the second with epitaxial channel, and the last one with epitaxial channel and delta doping. The reduction of the potential fluctuations at the interface as a result of the low doping in the epitaxial layer is clearly visible in the second device. The introduction of a delta doping in the third device does not have a visible detrimental effect on the smoothness of the surface potential.

# VI. CONCLUSION

In this paper we apply 3-D statistical atomistic simulations to study dopant fluctuation-resistant MOSFET architectures with epitaxial channels and delta doping. The atomistic simulations of conventional sub-0.1- $\mu$ m MOSFET's with uniform doping in the channel depletion region suggest that the doping concentration dependence of the random dopant-induced threshold voltage fluctuations is stronger than the fourth-root dependence present in most of the available analytical models. This may have serious implications to the scaling of such devices to sub-0.1- $\mu$ m dimensions. The atomistic results for a wide range of conventional devices are used to derive a simple empirical expression relating  $\sigma V_T$  to the major MOSFET design parameters.

Our atomistic simulations confirm that the random dopant-induced threshold voltage fluctuations can be significantly suppressed in MOSFET's with low-doped epitaxial channels. A tradeoff, however, has to be made between increasing the fluctuation resistance and reducing the short channel immunity with the increase in epitaxial layer thickness. For the first time, we report an ambiguous dependence of the threshold voltage fluctuations as a function of the doping concentration in such devices. For MOSFET's with thin epitaxial layers, a "normal" increase of  $\sigma V_T$  with the increase of the doping concentration behind the layer is observed. However, in devices with a thicker epitaxial layer,  $\sigma V_T$  anomalously decreases with the doping concentration. We attribute this anomalous behavior to screening of the random dopant charge in the depletion layer by the holes behind it.

The screening effects and the corresponding anomalous reduction in  $\sigma V_T$  become even more pronounced when a delta-doping layer is placed behind the epitaxial channel. As

a result of this, a design window is available in sub-0.1- $\mu$ m MOSFET range where, for the same thickness of epitaxial layer, devices without delta doping but with high doping concentration behind the epitaxial layer will have the same dopant fluctuation immunity as devices with high delta doping but low doping concentration behind the epitaxial layer.

# ACKNOWLEDGMENT

The authors are thankful to A. R. Brown and J. H. Davies for the critical reading of the manuscript and useful discussions.

# REFERENCES

- B. Hoeneisen and C. A. Mad, "Fundamental limitations in microelectronics-I, MOS technology," *Solid-State Electron.*, vol. 15, pp. 819–829, 1972.

- [2] R. W. Keys, "Physical limits in digital electronics," *Proc. IEEE*, vol. 63, pp. 740–766, 1975.

- [3] T. Mizuno, J. Okamura, and A. Toriumi, "Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFET's," *IEEE Trans. Electron Devices*, vol. 41, pp. 2216–2221, 1994.

- [4] T. Mizuno, "Influence of statistical spatial-nonuniformity of dopant atoms on threshold voltage in a system of many MOSFET's," *Jpn. J. Appl. Phys.*, vol. 35, pp. 842–848, 1996.

- [5] M. Steyaert, J. Bastos, R. Roovers, P. Kinget, W. Sansen, B. Grain-dourse, A. Pergot, and E. Janssens, "Threshold voltage mismatch in short-channel MOS transistors," *Electron. Lett.*, vol. 30, pp. 1546–1548, 1994.

- [6] O. R. dit Buisson and G. Morin, "MOSFET matching in deep submicron technology," in *Proc. ESSDERC'96*, G. Bakarani and M. Rudan, Eds., 1996, pp. 731–734.

- [7] J. T. Horstmann, U. Hilleringmann, and K. F. Goser, "Matching analysis of deposition defined 50-nm MOSFET's," *IEEE Trans. Electron Devices*, vol. 45, pp. 299–306, 1997.

- [8] C. G. Linnenbank, W. Weber, U. Kolmer, B. Holzapfl, S. Sauter, U. Achaper, R. Brederlow, S. Cyrusian, S. Kessel, R. Heinrich, E. Hoefig, G. Knobinger, A. Hesener, and R. Thewes, "What do matching results of medium area MOSFET's reveal for large area devices in typical analogue applications," in *Proc. ESSDERC'98*, G. A. Touboul, Y. Danto, J.-P. Klein, and H. Grunbacher, Eds., pp. 104–107.

[9] K. Nishiohara, N. Shiguo, and T. Wada, "Effects of mesoscopic fluc-

- [9] K. Nishiohara, N. Shiguo, and T. Wada, "Effects of mesoscopic fluctuations in dopant distributions on MOSFET threshold voltage," *IEEE Trans. Electron Devices*, vol. 39, pp. 634–639, 1992.

- [10] V. K. De, X. Tang, and D. J. Meindl, "Random MOSFET parameter fluctuation limits to gigascale integration (GSI)," in *Tech. Dig.*, *VLSI Symp*. '96, pp. 198–199.

- [11] P. A. Stolk, F. P. Widdershoven, and D. B. M. Klaassen, "Modeling statistical dopant fluctuations in MOS Transistors," *IEEE Trans. Electron Devices*, vol. 45, pp. 1960–1971, 1998.

- Devices, vol. 45, pp. 1960–1971, 1998.

[12] H.-S. Wong and Y. Taur, "Three dimensional 'atomistic' simulation of discrete random dopant distribution effects in sub-0.1 μm MOSFET's," in *Proc. IEDM'93. Dig. Tech. Papers*, pp. 705–708.

- [13] D. Vasileska, W. J. Gross, and D. K. Ferry, "Modeling of deepsubmicrometer MOSFETs: Random impurity effects, threshold voltage shifts and gate capacitance attenuation," *IEEE Cat. no. 98EX116*, Extended Abstracts IWEC-6, Osaka, pp. 259–262, 1998.

- [14] A. Asenov, "Random dopant induced threshold voltage lowering and fluctuations in sub 0.1 μm MOSFETs: A 3D 'atomistic' simulation study," *IEEE Trans. Electron Devices*, vol. 45, pp. 2505–2513, 1998.

- [15] K. Takeuchi, T. Tatsumi, and A. Furukawa, "Channel engineering for the reduction of random-dopant-placement-induced threshold voltage fluctuations," in *Proc. IEDM'97 Dig. Tech. Papers*.

- [16] K. R. Lakshmikumar, R. A. Hadaway, and M. A. Copeland, "Characterization and modeling of mismatch in MOS transistors for precision analogue design," *IEEE J. Solid-State Circ.*, vol. SC-21, pp. 1057–1066, 1986.

- [17] M. Eisele, J. Berthold, R. Thewes, E. Wohlrabh, D. Schmitt-Landsiedel, and W. Weber, "Intra-die device parameter variations and their impact on digital CMOS gates at low supply voltages," in *IEDM Tech. Dig.*, 1995, pp. 67–70.

- [18] D. Burnett, K. Erington, C. Subramanian, and K. Baker, "Implications of fundamental threshold voltage variations for high density SRAM and logic circuits," in *Tech. Dig. VLSI Symp.* '94, pp. 15–16.

- [19] K. Noda, T. Tatsumi, T. Uchida, K. Nakajima, H. Miyamoto, and C. Hu, "A 0.1-μm delta doped MOSFET fabricated with post-low-energy implanting selective epitaxy," *IEEE Trans. Electron Devices*, vol. 45, pp. 809–813, 1998.

- [20] A. Asenov, "Statistically reliable 'Atomistic' simulation of sub 100 nm MOSFET's," in *Simulation of Semiconductor Devices 1998*, K. De Meyer and S. Biesemans, Eds. Berlin: Springer, pp. 223–226, 1998.

- [21] The National Technology Road-Map for Semiconductors, Semiconductor Industry Association, San Jose, CA, 1997 Revision.

- [22] P. Francis, A. Terao, D. Flandre, and F. Van de Wiele, "Modeling of ultrathin double-gate nNMOS/SOI transistors," *IEEE Trans. Electron Devices*, vol. 41, pp. 715–720, 1994.

- [23] H. Takato, K. Sunouchi, N. Okabe, A. Nitayama, K. Hieda, F. Horiguchi, and F. Masuoka, "Impact of surrounding gate transistor (SGT) for ultra-high-density LSI's," *IEEE Trans. Electron Devices*, vol. 38, pp. 573–578, 1991.

- [24] C.-K. Huang, W. E. Zhang, and C. H. Yang, "Two-dimensional numerical simulation of Schottky Barrier MOSFET with channel length to 10 nm" *IEEE Trans. Electron Devices*, vol. 45, pp. 842–848, 1998.

- nm," *IEEE Trans. Electron Devices*, vol. 45, pp. 842–848, 1998.

[25] T. Shimatani, S. Pidin, and M. Koyanagy, "0.01 μm SOI-MOSFET's with intrinsic channel," *Tech. Rep. IEICE*, vol. SDM-137, pp. 39–44, 1996.

- [26] M. Aoki, T. Ishii, T. Yoshimura, Y. Kiyota, S. Iijima, T. Yamanaka, T. Kure, K. Ohyu, T. Nishida, S. Okazaki, K. Seki, and K. Shimohigashi, "0.1-μm devices using low-impurity-channel transistors (LICT)," in *IEDM Tech. Dig.*, 1990, pp. 939–941.

[27] C. Fienga, H. Iwai, T. Wada, T. Saiti, E. Sangiorgi, and B. Ricco,

- [27] C. Fienga, H. Iwai, T. Wada, T. Saiti, E. Sangiorgi, and B. Ricco, "Application of semiclassical device simulation to trade-off studies for sub-0.1-mm MOSFET's," in *IEDM Tech. Dig.*, 1994, pp. 437–450.

- [28] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S.-H. Lo, A. A. Sai-Hakasz, R. G. Viswanathan, H. J. C. Wann, S. J. Wind, and H.-S. Wong, "CMOS scaling into the nanometer regime," *Proc. IEEE*, vol. 85, pp. 486–504, 1997.

**Asen Asenov** (M'96) received the M.Sc. degree in solid state physics from Sofia University, Bulgaria, in 1979 and the Ph.D. degree in physics from The Bulgarian Academy of Science in 1989.

He had ten years industrial experience as a head of the Process and Device Modeling Group in IME-Sofia, developing one of the first integrated process and device CMOS simulators, IMPEDANCE. In 1989–1991, he was a Visiting Professor at the Physics Department of TU Munich. He is currently a Reader in the Department of Electronics and

Electrical Engineering, Glasgow University, Glasgow, Scotland. As a leader of the Device Modeling Group and academic director of the Process and Device Simulation Centre at The University of Glasgow, he coordinates the development of 2-D and 3-D device simulators and their application in the design of FET's, SiGe MOSFET's, and IGBT's. He has over 120 publications in process and device modeling and simulation, semiconductor device physics, "atomistic" effects in ultrasmall devices and parallel computing.

**Subhash Saini** received the Ph.D. degree from the University of Southern California (USC), Los Angeles.

He has held positions at University of California, Los Angeles (UCLA), University of California, Berkeley (UCB), and Lawrence Livermore National Laboratory (LLNL). He has over ten years experience of teaching physics at the B.S. (Hons.) and M.S. level. His research interest involves performance evaluation and modeling of new-generation of CMOS-based processors and highly parallel computers. He has published over 80 technical papers in nuclear engineering, quantum scattering, nanotechnology, high-temperature materials, operating systems, computer architectures, and performance modeling of high-end computers, and he has presented over 100 technical talks. He joined the Numerical Aerospace Simulation (NAS) System Division of NASA, Moffett Field, CA, in 1989. Currently, he is Manager of a department at NASA Ames Research Center which includes several groups such as Information Systems Performance Modeling; Algorithms, Architectures and Application; Information Power Grid Architectures; Legacy Codes Modernization; Higher Level Languages; Nanotechnology; and Device Modeling.

Dr. Saini has won several awards for "Excellence in Teaching" including one from USC. He was named the NAS-NASA Employee of the Year in 1991