University of Warwick institutional repository: http://go.warwick.ac.uk/wrap

### A Thesis Submitted for the Degree of EngD at the University of Warwick

http://go.warwick.ac.uk/wrap/41852

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

**Engineering Doctorate**

# **Innovation Report**

# Design of In-Vehicle Networked Control System Architectures through the Use of New Design to Cost and Weight Processes

**Christopher Patrick Quigley**

This work has been submitted in partial fulfilment of the requirements for the degree of Doctor of Engineering (EngD)

Warwick Manufacturing Group, University of Warwick

30<sup>th</sup> November 2011

#### Abstract

Over the last forty years, the use of electronic controls within the automotive industry has grown considerably. In-vehicle network technologies such as the Controller Area Network (CAN) and Local Interconnect Network (LIN) are used to connect Electronic Control Units (ECU) together, mainly to reduce the amount of wiring that would be required if hardwired integration were used.

Modern passenger cars contain many networks, which means that for the architecture designer, there is an almost overwhelming number of choices on how to design/partition the system depending on factors such as cost, weight, availability of ECUs, safety, Electro-Magnetic Compatibility (EMC) etc. Despite the increasing role played by in-vehicle networks in automotive electrical architectures, its design could currently be described as a "black art". Not only is there an almost overwhelming number of choices facing the designer, but there is currently a lack of a quantifiable process to aid decision making and there is a dearth of published literature available.

NetGen is a software tool used to design CAN/J1939, LIN and FlexRay networks. For the product to remain competitive, it is desirable to have novel features over the competition. This report describes a body of work, the aim of which was to research in-vehicle network design processes, and to provide an improvement to such processes. The opportunities of customer projects and availability of customer information resulted in the scope of the research focusing on the adoption of LIN technology and whether the adoption of it could reduce the cost and weight of the target architecture. The research can therefore be seen to address two issues: firstly the general problem of network designers needing to design in-vehicle network based architectures balancing the needs of many design targets such as cost, weight etc, and secondly the commercial motivation to find novel features for the design tool,

2

NetGen. The outcome of the research described in this report was the development of design processes that can be used for the selection of low cost and weight automotive electrical architectures using coarse information, such as that which would be easily available at the very beginning of a vehicle design programme. The key benefit of this is that a number of candidate networked architectures can be easily assessed for their ability to reduce cost and weight of the electrical architecture.

#### Acknowledgements

I would like to acknowledge the help from others in the completion of the Engineering Doctorate.

I would like to thank my academic supervisors Peter Jones and Ross McMurran and my industrial mentor Paul Faithfull for their helpful comments and guidance throughout the project.

Finally I would like to thank my partner Libby Hayward for proof reading final drafts of submissions and this report.

#### Declaration

This report is the original work by the author, parts of which have been published elsewhere, as stated in the text.

## Contents

| 1.     | INTRODUCTION                                                            | .13 |

|--------|-------------------------------------------------------------------------|-----|

| 1.1.   | The Sponsoring Company – Rapicore                                       | .14 |

| 1.2.   | The Product – NetGen                                                    |     |

| 1.3.   | Distributed System Development Using NetGen                             | .17 |

| 1.4.   | NetGen – Competitor Analysis                                            |     |

| 1.5.   | NetGen – Current Sales and Distribution Strategy                        |     |

| 1.6.   | NetGen – Requirement for Improvement                                    |     |

| 1.7.   | Aim of Research                                                         |     |

| 1.8.   | Flow of Doctorate Submissions                                           | .28 |

| 1.9.   | Flow of this Report                                                     | .32 |

| 2.     | LITERATURE SURVEY                                                       | .35 |

| 2.1.   | Trends in Automotive Electronic Systems Integration                     | .35 |

| 2.2.   | Automotive In-Vehicle Networking Technologies for Control               |     |

| 2.2.1. | Controller Area Network Based Technologies                              |     |

| 2.2.2. | Local Interconnect Network (LIN)                                        |     |

| 2.2.3. | Emergence of High Speed Time Triggered Automotive Control Networks      | .44 |

| 2.2.4. | Other Emerging Automotive Control Networks                              |     |

| 2.2.5. | Multimedia Automotive Networks                                          |     |

| 2.2.6. | The Future of Automotive Control Networks                               |     |

| 2.3.   | Adoption of Control Networks in Other Vehicle Applications              |     |

| 2.4.   | Processes Used for Designing the Electrical Architecture of Distributed |     |

|        | Automotive Control Systems                                              | .63 |

| 2.4.1. | Design of Network Schedules and Dealing with the Multi-Supplier Problem |     |

| 2.4.2. | Designing an Automotive Electrical Architecture to a Target Cost        |     |

| 2.5.   | Which Network Technology is Most Cost Effective?                        |     |

| 3.     | CAR DOOR SYSTEM LIN BASED HARNESS – CASE STUDY                          |     |

| 3.1.   | Case Study Overview                                                     |     |

| 3.2.   | Case Study – Main Outcomes                                              |     |

| 4.     | PROCESSES FOR ARCHITECTURE SELECTION                                    |     |

| 4.1.   | Architecture Design to Cost Process                                     |     |

| 4.2.   | Architecture Design to Weight Process                                   |     |

| 5.     | MICROCONTROLLER MEMORY CAPABILITY ASSESSMENT AND                        |     |

|        | VARIANT SELECTION                                                       | 105 |

| 5.1.   | ROM and RAM Capability Relationship within a Microcontroller Family1    |     |

| 5.2.   | Estimation of LIN Communications Stack ROM and RAM Requirements1        |     |

| 5.3.   | Microcontroller Family ROM/RAM Capability Assessment Process            |     |

| 5.4.   | Microcontroller Variant Selection By ROM/RAM Requirement Estimation     |     |

| 6.     | SPORTSCAR BODY CONTROL ELECTRICAL ARCHITECTURE                          |     |

|        | DESIGN – CASE STUDY                                                     | 126 |

| 6.1.   | Case Study – Overview                                                   |     |

| 6.2.   | Case Study – Main Outcomes                                              |     |

| 7.     | CONCLUSION AND RECOMMENDATIONS FOR FURTHER WORK .1                      | 147 |

| 7.1.   | Conclusion                                                              |     |

| 7.2.   | Recommendations for Further Work                                        |     |

| 7.2.1. | Potential Future Exploitation of Research Findings1                     |     |

| 7.2.2. | Embedded Software Memory Requirements Modelling                         |     |

| 7.2.3. | Adaptation of Processes to Other Network Technologies and Applications. |     |

| 7.2.4. | Automatic Rule-Based Optimisation of Architecture Design                |     |

|        |                                                                         |     |

| 8. | REFERENCES | .15 | 5 |

|----|------------|-----|---|

|----|------------|-----|---|

## **Table of Figures**

| Figure 1 : Example screen shot of the NetGen LIN tool                                                                                                            | 18  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2 : Example LIN schedule screen shot of the NetGen LIN tool                                                                                               |     |

| Figure 3 : The NetGen code generation interface                                                                                                                  |     |

| Figure 4 : Warwick Control Toolset for ECU development (McLaughlin et al, 2010)                                                                                  |     |

| Figure 5 : Top level process developed during the engineering doctorate                                                                                          |     |

| Figure 6 : Suggested reading order of the Engineering Doctorate submissions and ke outcomes                                                                      | ey  |

| Figure 7: Stand alone ECUs (No Integration)                                                                                                                      |     |

| Figure 8: Hard-wired ECU Integration                                                                                                                             |     |

| Figure 9: Single Bus Integration                                                                                                                                 |     |

| Figure 10: Partitioning of Automotive Electrical Architecture into a Two Bus Syster                                                                              |     |

|                                                                                                                                                                  | 37  |

| Figure 11: Multiple Network Partitioned Automotive Electrical Architecture (e.g. Real Time Control Networks, Sensor/Actuator Sub-buses, One Infotainment Network | rk, |

| One Diagnostic Bus - ideally partitioned by function but more usually by data sharir requirements)                                                               | -   |

| Figure 12 : A typical use of a combination of the LIN sub-bus along with the CAN                                                                                 |     |

| bus in the localised area of car door control.                                                                                                                   |     |

| Figure 13 : Example TDMA time triggered matrix                                                                                                                   | 46  |

| Figure 14 : A plot of bit rate of the data field versus the average bit rate across the                                                                          |     |

| whole CAN frame. CAN Identifier 11 Bit, Data Field 8 Byte, Bit Rate Arbitration.                                                                                 |     |

|                                                                                                                                                                  | 56  |

| Figure 15 : Possible in-vehicle network architecture of the future comprising multiple                                                                           |     |

| networks and network technologies                                                                                                                                | 60  |

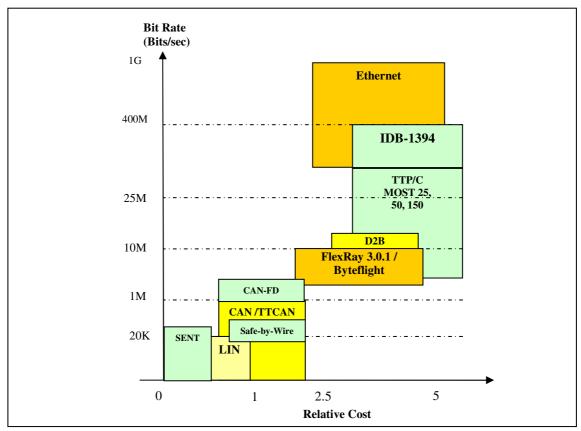

| Figure 16: Current and emerging communications technologies versus price versus                                                                                  |     |

| bandwidth (based on Figure 1 of LIN specification package Revision 1.2 page 2)                                                                                   |     |

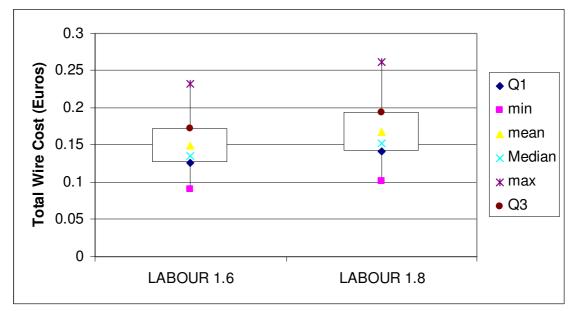

| Figure 17: Two possible distributions for the cost of an intra-door wire                                                                                         |     |

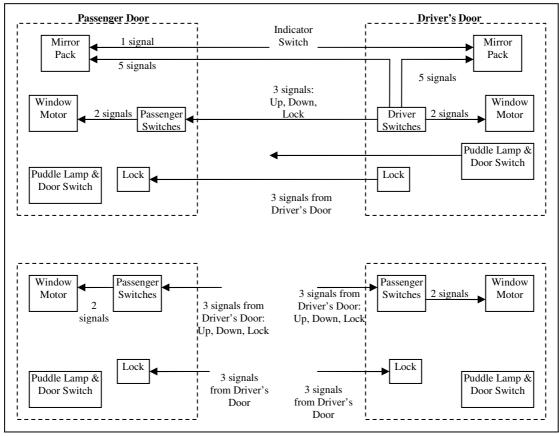

| Figure 18: Hardwired architecture                                                                                                                                |     |

| Figure 19: LIN Bus Based Architecture                                                                                                                            |     |

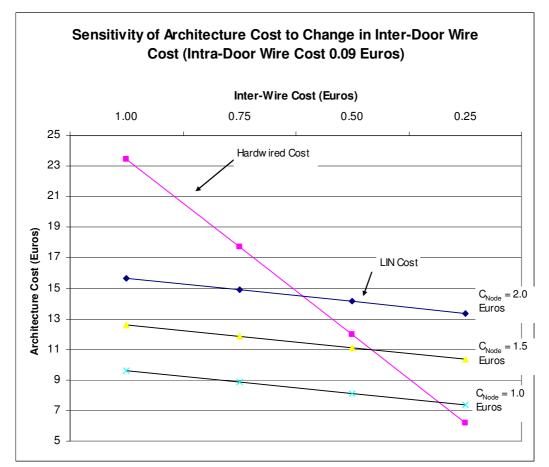

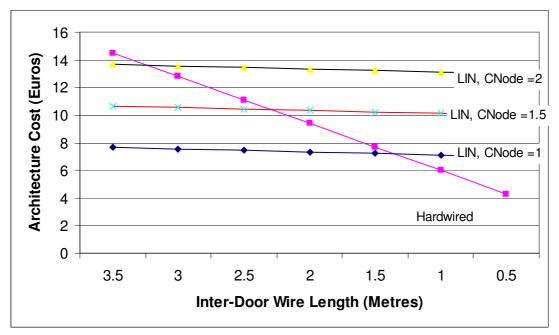

| Figure 20: Sensitivity of both hardwired and LIN bus based architecture cost to both                                                                             | 1   |

| inter-door wire and LIN node cost                                                                                                                                |     |

| Figure 21: Cost of both hardwired and LIN architectures                                                                                                          |     |

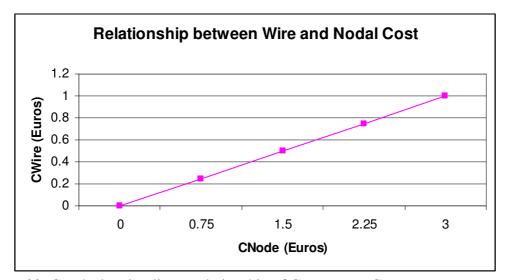

| Figure 22: Graph showing linear relationship of $C_{Wire}$ versus $C_{Node}$                                                                                     |     |

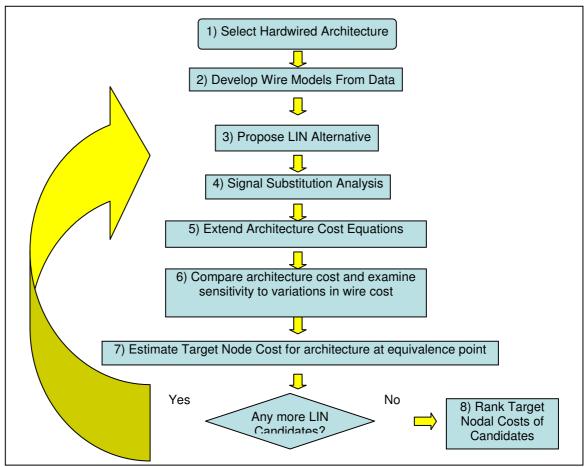

| Figure 23: Process for LIN architecture design to cost                                                                                                           |     |

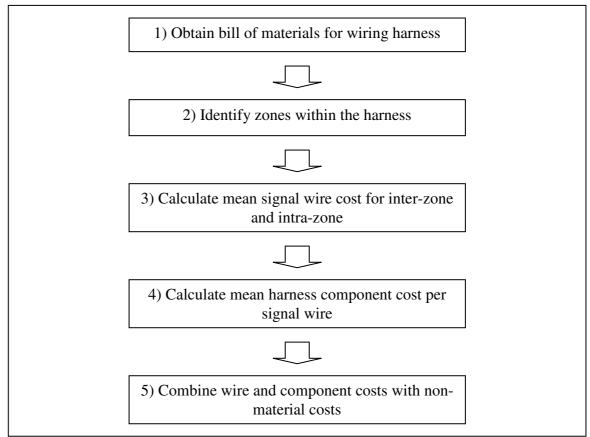

| Figure 24: Process for Signal Wire Model Development                                                                                                             |     |

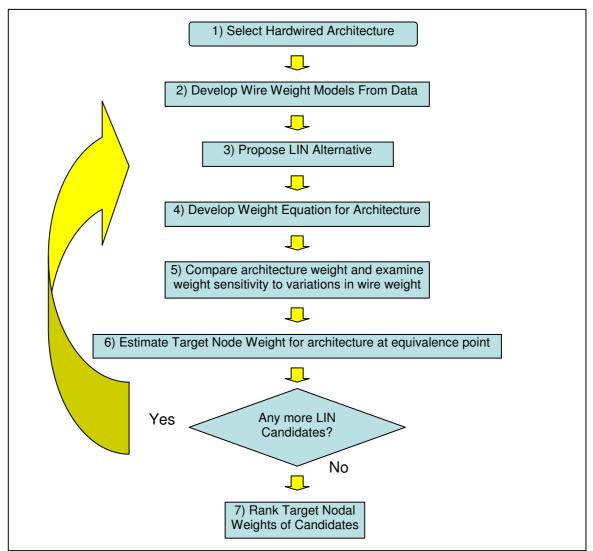

| Figure 25 : Process for design for harness weight1                                                                                                               |     |

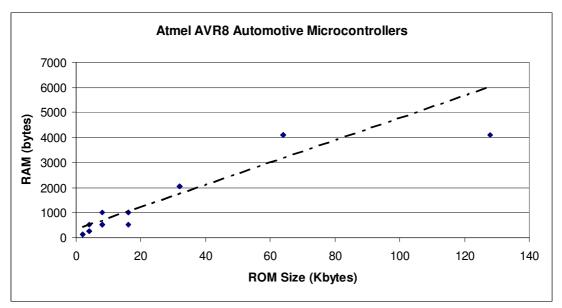

| Figure 26: Plot of RAM Size versus ROM Size for the PIC18 Microcontroller1                                                                                       |     |

| Figure 27: Plot of RAM Size versus ROM Size for the PIC16 Microcontroller1                                                                                       | 08  |

| Figure 28: Plot of RAM Size versus ROM Size for the AVR Automotive                                                                                               |     |

| Microcontrollers1                                                                                                                                                | 08  |

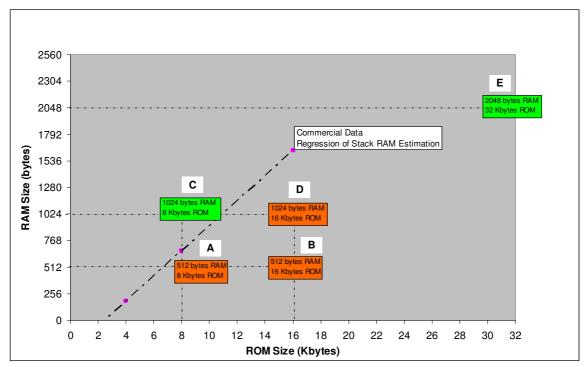

| Figure 29: ROM versus RAM relationship of the Atmel AVR microcontroller and                                                                                      |     |

| LIN communications stack with AVR variants shown. The Atmel AVR                                                                                                  |     |

| microcontroller are the points A, B, C, D and E on the figure1                                                                                                   |     |

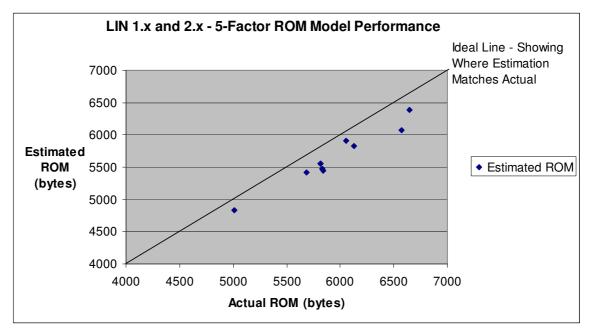

| Figure 30: Performance of 5-factor model with <i>Model Assessment</i> dataset                                                                                    |     |

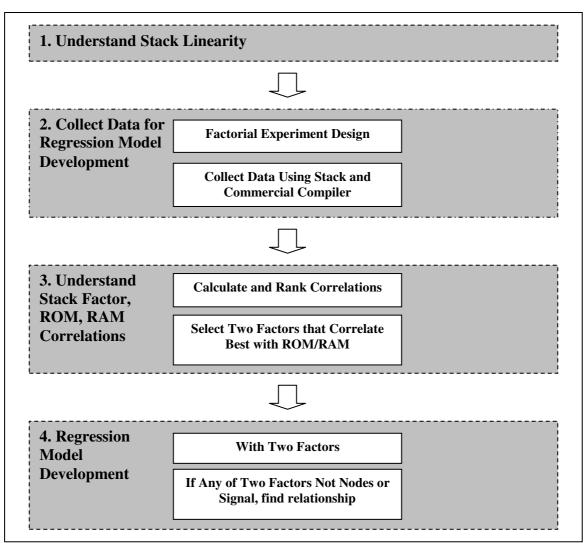

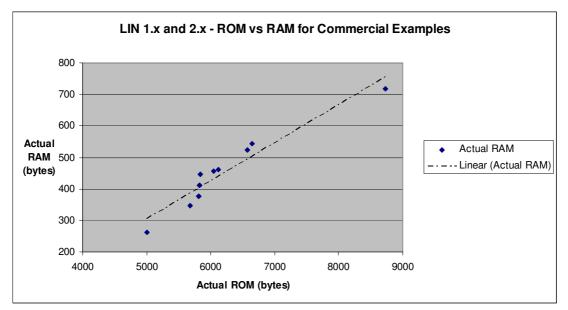

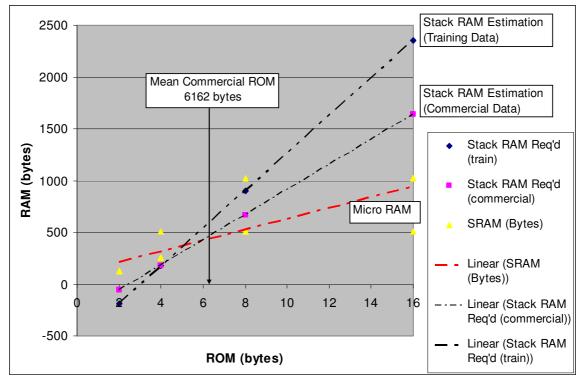

| Figure 31: LIN communications stack ROM, RAM modelling process1                                                                                                  |     |

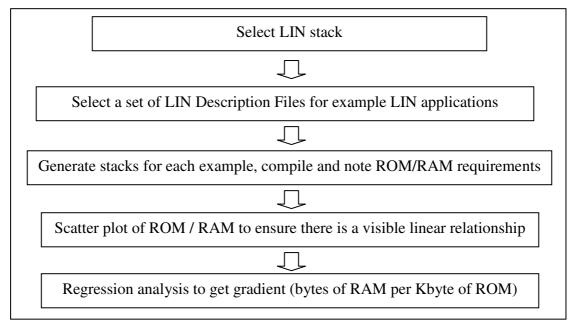

| Figure 32: Process for ascertaining LIN stack ROM/RAM requirements1                                                                                              |     |

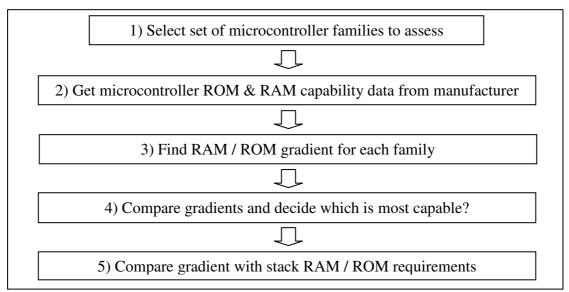

| Figure 33: Process for comparing microcontroller and stack memory capability1                                                                                    | 19  |

| Figure 34: ROM and RAM values of the examples in the Model Assessment datas    | et   |

|--------------------------------------------------------------------------------|------|

| -                                                                              | .120 |

| Figure 35: ROM and RAM relationship of the Atmel AVR and LIN stack             | .121 |

| Figure 36: Process for microcontroller selection and nodal cost estimation     | .123 |

| Figure 37: Three zones of the sportscar body control wiring harness (Westfield |      |

| Sportscars Ltd., 2009).                                                        | .128 |

| Figure 38 : Generic configuration of LIN node considered in all candidate      |      |

| architectures                                                                  | .130 |

| Figure 39 : Example of a LIN linear bus architecture                           | .132 |

| Figure 40: Comparison of Hardwired and Two Node LIN Architecture Cost with     |      |

| Variation of Non-Material Cost Factor                                          | .136 |

| Figure 41: Comparison of Hardwired and Three Node LIN Architecture Weight w    | vith |

| Variation of Wire Weight                                                       | .138 |

| Figure 42: Assessment of design processes and models                           | .140 |

| Figure 43: Dash LIN node actual connections two node architecture              | .141 |

## List of Tables

| Table 1 : Currently available product versions by network technology                    |

|-----------------------------------------------------------------------------------------|

| Table 2: NetGen competitor products as of end of 2009 (Green=NetGen feature             |

| coincidence)                                                                            |

| Table 3: Top level comparison of automotive time triggered protocol candidates45        |

| Table 4: Mean wire cost by using equation (1)74                                         |

| Table 5: Body Control Functions by Door                                                 |

| Table 6 : The signal substitution between hardwired and LIN architectures80             |

| Table 7: Variation in target LIN nodal cost to increases in architecture information.88 |

| Table 8 : Comparison of semiconductor manufacturer, microcontroller family and          |

| RAM / ROM gradient109                                                                   |

| Table 9: Comparison of RMS error of models in context of mean commercial ROM            |

|                                                                                         |

| Table 10: Selection of the RAM model that overestimates with the lowest error114        |

| Table 11: Combined wire and component costs    129                                      |

| Table 12: Comparison of the number of wires, wire types and LIN nodes between           |

| architectures – forms coarse architecture equations                                     |

| Table 13: Comparison of LIN candidate architectures on a cost basis         137         |

| Table 14: Comparison of LIN candidate architectures on a weight basis                   |

| Table 15 : Comparison of original and improved cost estimations142                      |

| Table 16 : Comparison of original and improved weight estimations         143           |

| Table 17 : Comparison of original model mean and actual mean wire lengths 143           |

## Abbreviations

| ABS          | Anti-lock Braking System                                       |

|--------------|----------------------------------------------------------------|

| API          | Application Programming Interface                              |

| ASAM         | Association for Standardisation of Automation and Measuring    |

|              | Systems                                                        |

| ASIC         | Application Specific Integrated Circuit                        |

| ASIL         | Automotive Safety Integrity Level                              |

| AUTOSAR      | <u>AUT</u> omotive <u>Open System Ar</u> chitecture            |

| BEAN         | Body Electronic Area Network (Toyota proprietary technology    |

|              | used for the control of body electronics)                      |

| CAN          | Controller Area Network                                        |

| CD           | Compact Disk                                                   |

| COTS         | Commercial Off The Shelf                                       |

| CPU          | Central Processing Unit                                        |

| CSMA-CD-NDBA | Carrier Sense, Multiple Access, Collision Detection, Non-      |

|              | Destructive Bitwise Arbitration                                |

| DTC          | Diagnostic Trouble Code                                        |

| DVD          | Digital Versatile Disk                                         |

| EASIS        | Electronic Architecture and Systems engineering for Integrated |

|              | Safety Systems                                                 |

| ECU          | Electronic Control Unit                                        |

| EEPROM       | Electrically Erasable Programmable Read Only Memory            |

| EMC          | Electromagnetic Compatibility                                  |

| EPAS         | Electrically Power Assisted Steering                           |

| EPB          | Electric Park Brake                                            |

| ESP      | Electronic Stability Program                          |

|----------|-------------------------------------------------------|

| EUSART   | Enhanced Universal Synchronous Asynchronous Receiver  |

|          | Transmitter                                           |

| FPGA     | Field Programmable Gate Array                         |

| HLP      | Higher Layer Protocol                                 |

| HVAC     | Heating Ventilation Air Conditioning                  |

| ISG      | Integrated Starter Generator                          |

| IVN      | In-Vehicle Network                                    |

| LAN      | Local Area Network                                    |

| LDF      | LIN Description File                                  |

| LIN      | Local Interconnect Network                            |

| LNA      | LIN Network Architect                                 |

| MILCAN   | Military Controller Area Network Protocol             |

| MISRA    | Motor Industry Software Reliability Association       |

| MOST     | Media Oriented Systems Transport                      |

| NM       | Network Management                                    |

| NMEA2000 | National Marine Electronics Association 2000 Protocol |

| NRE      | Non-Recoverable Expenditure                           |

| OEM      | Original Equipment Manufacturer                       |

| РСВ      | Printed Circuit Board                                 |

| PDU      | Protocol Data Unit                                    |

| PLC      | Power Line Carrier                                    |

| RAM      | Random Access Memory                                  |

| RMS      | Root Mean Squared                                     |

| ROM      | Read Only Memory                                      |

| RTOS        | Real Time Operating System                              |

|-------------|---------------------------------------------------------|

| SENT        | Single Edge Nibble Transmission                         |

| SIL         | Safety Integrity Level                                  |

| SME         | Small Medium Enterprise                                 |

| SPC         | Short PWM Code                                          |

| TDMA        | Time Division Media Access                              |

| TTCAN       | Time Triggered CAN                                      |

| TT-Ethernet | Time Triggered Ethernet                                 |

| TTP         | Time Triggered Protocol                                 |

| UART        | Universal Asynchronous Receiver Transmitter             |

| USART       | Universal Synchronous Asynchronous Receiver Transmitter |

#### 1. INTRODUCTION

Prior to the 1970s there were very few electronic systems implemented in passenger cars. By 1974 there were up to twelve electronic systems or sub-systems in a high end vehicle although they were not microcontroller based. These systems included alternator diodes, voltage regulators, electronic fuel injection and electronic controlled ignition (Jurgen, 1999). Electronic system adoption then began to grow as a result of increasingly stringent emissions legislation world wide (initially from the Californian Air Resources Board) and the emergence of cost effective microprocessor technology. By the end of the 1990s, electronic components and systems accounted for over 20% of the cost of a high end passenger car (Leen et al, 1999). A current high-end passenger car can have over fifty Electronic Control Units (ECUs) of varying complexity contained within its electrical architecture. This figure is expected to grow significantly over the coming years with the introduction of increasingly more complex control systems such as drive-by-wire and multimedia systems giving access to the Internet. Forecasts indicate that by 2010, 24% of the total vehicle costs across all types of vehicle will be due to electronic equipment (Robert Bosch GmbH, 2004).

The large number of ECUs that now exist in modern vehicles has led to the adoption of in-vehicle networks in order to share information between each of the ECUs. There have been many example technologies over the years but currently the de-facto standard is the Controller Area Network (CAN). More recently intelligent sensors and actuators, and low speed digital switching have been integrated with a complementary but lower cost and lower performance technology known as the Local Interconnect Network (LIN). Since 2006 a new higher cost but higher performance network technology known as FlexRay has been implemented in cars from BMW,

Audi, Rolls Royce and Bentley. Finally, a technology known as Media Oriented Systems Transport (MOST) is now deployed in many higher-end vehicles for infotainment applications such as camera and navigation systems. MOST is a fast network technology for information transfer and not control and therefore it can be considered as different from the aforementioned network technologies. A typical modern vehicle will now have at least two CAN buses and four to eight LIN buses. A high-end vehicle can have up to six CAN buses and twelve LIN buses and therefore system partitioning can be a significant problem in the design of the electrical architecture.

The designers of a vehicle's electrical architecture must balance the requirements of many different design targets in order to produce the best architecture. These include but are not limited to ensuring that it is the lowest cost to meet the requirement of delivering the maximum value to a customer, achieving the lowest weight possible, which in turn reduces emissions and fuel consumption, ensuring that it is easy to manufacture and assemble and also that it meets legislative requirements in terms of Electro-Magnetic Compatibility (EMC) and safety. Much of this is carried out relying on the judgement and experience of the designers since it is a "black art" rather than using fully quantified design processes.

#### **1.1.** The Sponsoring Company – Rapicore

Rapicore was a spin-off company from Potenza Technology founded in 2004 to commercially exploit and develop products relating to design and automatic code generation of communication software stacks for automotive network systems. Potenza Technology itself is part of a group that now owns niche sportscar manufacturer brands Westfield and GTM. Potenza gave access to some information on the design of these vehicles during the doctorate programme which is contained within this report.

Rapicore products included a CAN bus I/O block for Simulink (called RapidTarget) which was targeted towards the Infineon c16x microcontroller family and also integrated into the Prodrive uProteus product. Another key product was an in-vehicle networking design tool called NetGen. Due to a decline in interest in these products, the company was wound down in 2009. During the five year life of the company it consisted of up to five people and participated in the Eureka project SAPECS (Secured Architectures and Protocols for Enhanced Car Safety).

The Rapid Target product is no longer supported as the high cost of maintenance makes this product commercially unviable. The NetGen product, although not financially viable within Rapicore, is now a part of the product portfolio of a company called Warwick Control Technologies, which is a provider of control systems networking technology products for automotive and industrial automation systems. The NetGen intellectual property is currently jointly owned by Potenza Technology and Warwick Control Technologies.

#### **1.2.** The Product – NetGen

#### Background

NetGen is a PC-based network design and automatic code generation tool for LIN, CAN, SAE J1939 (a version of CAN used in truck and off-highway industries) and FlexRay. The NetGen tool is a rule-based LIN network and node designer that can also be used to automatically generate or configure the MISRA C source code stack for network communications. The stack is compiled and included as part of an automotive application that is embedded within an ECU.

#### NetGen LIN

The first version of NetGen to be released commercially was NetGen LIN. The current versions of NetGen LIN available on the market are for Atmel AVR and Infineon Tricore microcontrollers and have been included in a number of production vehicle programmes. The Infineon Tricore version has been used by a major first tier supplier to generate the communications between a gearbox controller and a gear selector module for a large number of manufacturers. Atmel AVR versions have been used by first tier automotive suppliers in the USA for development of LIN slave devices for  $CO_2$  sensing and Heating Ventilation and Air Conditioning (HVAC).

#### NetGen FlexRay Development

During the SAPECS Project (Secured Architectures and Protocols for Enhanced Car Safety) which was a pan-European Eureka project, the NetGen tool was extended to support the FlexRay protocol. The tool was included as part of the development process for the SAPECS project to design the FlexRay communications of an engine management demonstrator for a first tier European automotive supplier. It was used to automatically generate the C configuration files for an AUTOSAR FlexRay stack targeted to an Atmel AVR32 microcontroller (Laes et al, 2009).

#### NetGen SAE J1939

The SAE J1939 is a CAN higher layer protocol primarily used in bus, truck and offhighway applications. A J1939/CAN version was developed and extended to support the application programming interface of a commercial J1939 stack as the target. Currently NetGen CAN J1939 is not targeted towards a particular microcontroller, but to CAN-specific software stacks provided by two companies. However for the sake of this discussion, the J1939 software stack can be seen to be in the same scope as a microcontroller.

#### Summary of NetGen Product Variants

The different versions of the tool that are currently available are summarised in Table 1. It can be seen that the generic naming convention is *NetGen "Network Technology" "Microcontroller Targeted"*. The list of product versions is not exhaustive, these are just the versions that have been developed specifically to meet customer requests or other market needs that have been determined.

| Technology | Product offering                                                   |  |  |  |  |  |

|------------|--------------------------------------------------------------------|--|--|--|--|--|

| LIN        | <i>NetGen LIN Tricore</i> – automatic code generation tool for LIN |  |  |  |  |  |

|            | targeted at the Tricore microcontroller from Infineon AG and the   |  |  |  |  |  |

|            | AVR microcontroller from the Atmel Corporation                     |  |  |  |  |  |

| CAN        | <i>NetGen CAN LPC</i> – automatic code generation tool for CAN     |  |  |  |  |  |

|            | targeted at the LPC microcontroller from NXP                       |  |  |  |  |  |

| J1939      | NetGen CAN J1939 – automatic code generation tool for CAN          |  |  |  |  |  |

|            | targeted at the J1939 software stacks from two different suppliers |  |  |  |  |  |

| FlexRay    | <i>NetGen FlexRay AVR32</i> – automatic code generation tool for   |  |  |  |  |  |

|            | FlexRay targeted at the AVR32 microcontroller from the Atmel       |  |  |  |  |  |

|            | Corporation.                                                       |  |  |  |  |  |

Table 1 : Currently available product versions by network technology

#### **1.3.** Distributed System Development Using NetGen

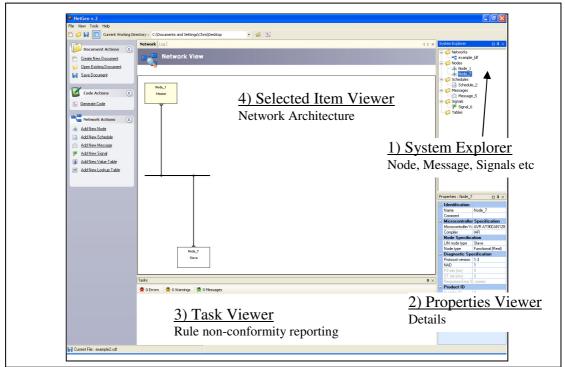

A screen shot of the tool is shown in Figure 1 which shows an example two node network for LIN. The network architecture display shows a network topology. The Node, Message, Signals Tree View shows the number and name of network nodes, messages, signals and also schedules for message transmission. During the development of a network, there are protocol conformity rules that continually check the correctness of the design and provide three priority levels of warnings at the bottom. Figure 2 shows the NetGen view for schedules of message transmission and how they can be designed within the tool.

Figure 1 : Example screen shot of the NetGen LIN tool

| NetGen v.2                                                                                                                                                                                                                                                                    |                                                                                               | - <b>d</b>                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------|

| File View Tools Help                                                                                                                                                                                                                                                          |                                                                                               |                            |

| 睯 🧔 📙 🚺 Current Working Dire                                                                                                                                                                                                                                                  | ectory : C1\Documents and Settings\Chris Quigley\Desktop 🔹 😡 🔀                                |                            |

| Document Actions                                                                                                                                                                                                                                                              | Network   Log Schedule - Operation 4 b x                                                      | System Explorer 4 ×        |

| <u>Create New Document</u> <u>Open Existing Document</u>                                                                                                                                                                                                                      | Operation                                                                                     | Wodes     Schedules        |

|                                                                                                                                                                                                                                                                               | Uhoondtional Sporado Event Triggered Diagnostic                                               | 🖻 🣁 Messages               |

| ↓     Save Document       ✓     Code Actions       >>     Generate Code       ✓     Network Actions       >>     Add New Node       >>     Add New Node       >>     Add New Massage       >>     Add New Massage       >>     Add New Sanad       >>     Add New Value Table | Unconditional         Spondo         Event Triggered         Diagnostic         Time Scaling: | er w Diagnostic Messages   |

| Add New Lookup Table                                                                                                                                                                                                                                                          | Message       Dala         Delay (mc)                                                         | Properties System Explorer |

| 📙 Current File : Tutorial sdf                                                                                                                                                                                                                                                 |                                                                                               |                            |

Figure 2 : Example LIN schedule screen shot of the NetGen LIN tool

Upon opening NetGen and selecting to create a new configuration, the user is presented with a selection of technologies for which they can configure. At present the options include CAN/J1939, LIN and FlexRay. Once the desired network is selected the user is presented with the main configuration environment shown in Figure 1. The interface consists of four main components: the *System Explorer (1)*; the *Properties Viewer (2)*; and the *Task Viewer (3)*; and the *Selected Item Viewer (4)*. For the purposes of this discussion a network has already been entered to show the kind of information that is displayed.

The *System Explorer* (1) shows all of the components within the network, including the network itself, its nodes, schedules of communication, messages, signals and lookup tables. This allows developers to view all of the network's constituents at a glance. The configuration parameters for each item can be viewed and edited in the *Properties Viewer* (2) by selecting the item with the mouse. Items can also be copied and deleted through the System Explorer.

The *Properties Viewer* (2) displays the parameters and settings of the item selected in the *System Explorer*. Through this component the user can modify the item's parameters as required. It also performs checks on the values entered or selected according to rules contained in the schema files. If a parameter is invalid an error or warning message, depending on the nature of the invalidity, is shown in the *Task Viewer* (3). Some errors can also result in a dialog box being displayed, showing the error that has occurred and the action that has been performed e.g. the value is above the permitted bounds and has been reverted back to its original value.

The *Task Viewer* (3) shows any errors, warnings and information concerning the network's current configuration, and offers the user guidance on how to correct the network design. If an error is highlighted in the *Task Viewer*, the user simply has to make the associated correction. Once the item is corrected the error/warning is removed from the viewer. During the NetGen development process the user must work through all errors and warnings that are reported to satisfactorily complete the network design.

The Selected Item Viewer (4) displays a number of items depending on the selection in the System Explorer. The viewer is used for items that require, or can benefit from, the use of visual artefacts, either for simple display purposes or for more complicated configurations that cannot be done through the Properties Viewer. The main items displayed are the Network (currently shown in the figure), the Log (which displays information on the applications events), and the Schedule, (for modifying the network's schedule which is required for LIN and FlexRay, but not CAN). The Schedule view is the most interactive of the displays, allowing users to set up messages within the schedule.

Throughout development the developer can save (and later reopen) the network configuration to file. The file is called a System Description File and uses the 'SDF' extension and is saved as an XML file.

Once the entire network configuration has been entered correctly and all errors/warnings reported in the *Task Viewer* have been dealt with satisfactorily, the developer can then generate the source code for one or more of the nodes present in the network. The code generation interface is shown in Figure 3. The simple code generation interface allows the user to select the nodes for which the code should be generated. It also allows the configuration of a few other items including the generation of OIL (OSEK Implementation Language) and DIL (Data Input Language) files for each node, diagnostics API, and SCI (Serial Communication Interface)/TIM (Timer) Channel selection (for LIN only). Once the required nodes have been selected the developer clicks on the 'Generate Code' button to generate the source code for the selected nodes. These files are saved into a separate directory on the local machine for each node selected.

| Code Generation                                                                                                            |                                                                       |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Code Generation                                                                                                            |                                                                       |

| Output File Formats Generate OIL file for selected nodes. Generate DIL file for selected nodes. Diagnostics API Raw Cooked | Select Nodes to Generate Code For<br>✓ Node_1<br>✓ Node_2<br>✓ Node_3 |

| Channels<br>SCI Channel<br>TIM Channel                                                                                     |                                                                       |

|                                                                                                                            | Generate Code Cancel                                                  |

Figure 3 : The NetGen code generation interface

#### **1.4.** NetGen – Competitor Analysis

The competitors for the NetGen tool vary depending upon the network technology that they are targeted towards. The main competitor products to NetGen network design and code generation tool are shown in Table 2.

| Feature                            | NetGen | Vector<br>(DaVinci) | Intrepid<br>(LIN Tool) | Mentor<br>LNA | TTTech<br>TT-Plan | TZM<br>FlexConfig | E-bit |

|------------------------------------|--------|---------------------|------------------------|---------------|-------------------|-------------------|-------|

| Automatic Scheduling of            | No     | No                  | No                     | Yes           | Yes               | No                | Yes   |

| messages                           |        |                     |                        |               |                   |                   |       |

| Code Generator                     | Yes    | Yes                 | No                     | Yes           | Yes               | No                | Yes   |

| Rule Based Design                  | Yes    | Yes                 | Yes                    | Yes           | Yes               | Yes               | Yes   |

| Design Process Workflow            | Yes    | Yes                 | None                   | Yes           | Yes               | Yes               | Yes   |

| Microcontroller selection          | No     | No                  | No                     | No            | No                | No                | No    |

| (e.g. by stack ROM/RAM estimation) |        |                     |                        |               |                   |                   |       |

| Support of architecture            | No     | No                  | No                     | No            | No                | No                | No    |

| design to a target (e.g.           |        |                     |                        |               |                   |                   |       |

| Cost/weight)                       |        |                     |                        |               |                   |                   |       |

| FIBEX support                      | No     | Yes                 | No                     | No            | Yes               | Yes               | Yes   |

| Pricing Point                      | Medium | High                | Free                   | High          | High              | Medium            | High  |

| CAN Support                        | Yes    | Yes                 | No                     | Yes           | TTCAN             | No                | No    |

| J1939 Support                      | Yes    | Yes                 | No                     | No            | No                | No                | No    |

| LIN Support                        | Yes    | Yes                 | Yes                    | Yes           | Yes               | No                | No    |

| FlexRay Support                    | Yes    | Yes                 | No                     | No            | Yes               | Yes               | Yes   |

Table 2: NetGen competitor products as of end of 2009 (Green=NetGen feature coincidence)

The following can be seen from Table 2:

- Only the product from Vector competes across all network technologies (i.e. CAN, J1939, LIN and FlexRay).

- J1939 versions of the tool only have one competitor, which is Vector.

- For FlexRay the market place is very crowded and there is a lot of competition for the FlexRay version of the NetGen.

- The LIN version of the NetGen product has just two serious competitor products (from Vector and Mentor), as two other competitors do not provide the same level of features such as C code generation.

- None of the tools help with microcontroller selection

• None of the tools helps with the selection of the ideal network architecture that can result in reduced cost or weight.

Therefore there are technological gaps in the market for such products in the area of microcontroller selection and architecture selection based on design targets such as cost or weight.

In general NetGen offers the following benefits in addition to what is shown in this table:

- Network design and code generator available in same package many of NetGen's competitors separate the designer side of the product from the code generator whilst NetGen includes both in the same package.

- 2. Easy-to-use user interface therefore requiring minimal training.

- Customisable rule-base editable XML schema offers an easy to customise rule-base.

- 4. **Competitive pricing** middle end pricing point makes the product ideal for smaller suppliers and niche /low-volume vehicle manufacturers.

- Multiple stack supplier relationships not tied to a single stack supplier, i.e. currently supports FlexRay for Atmel AVR32, two different J1939 stacks, HIS Automotive standard for LIN, Atmel AVR microcontrollers.

- 6. **Integration with the free GNU C compiler –** giving the possibility for the customer to reduce their capital investment cost.

- Free CAN stack signals API-based stack available with CAN version based on early AUTOSAR standards.

#### 1.5. NetGen – Current Sales and Distribution Strategy

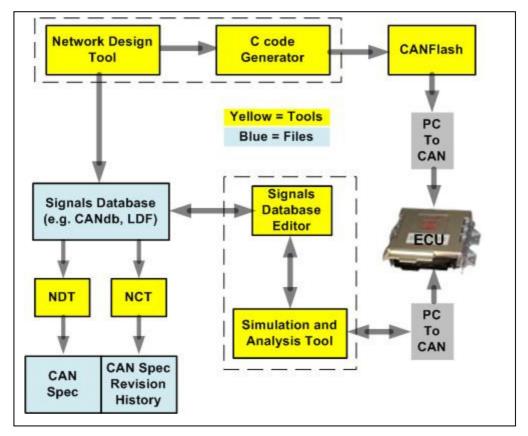

The NetGen product is currently sold world-wide as a part of the Warwick Control in-vehicle network development tool portfolio, primarily via the Warwick Control web-shop, direct sales and distribution partnerships. The product portfolio is shown in Figure 4, and within this portfolio the NetGen product is able to survive commercially as part of a solution that can be supplied to customers.

The product portfolio is a design suite which includes NetGen as a network designer and automatic code generator (i.e. generation of signals API and configuration for the network stack), an automatic J1939 CAN Network Documentation Tool (NDT) for generation of network specifications, Network Comparison Tool (NCT) to help manage the data between different revisions of the vehicle network specification, network analyser and tool for flashing over CAN.

Figure 4 : Warwick Control Toolset for ECU development (McLaughlin et al, 2010)

The tool faces some tough competition from some very large companies. To help improve product exposure, versions of NetGen without any code generation capabilities are given away for free. This is inline with current approaches from competitors. For example, at least two competitors give away a free version of their LIN editor tool. This has the advantage of allowing the customer to try out the product's features before purchase.

FlexRay and CAN versions of the NetGen product are available as custom products, in other words developed specifically as customer projects to their requirements. LIN and J1939 NetGen versions are available as off-the-shelf and also custom products. Custom versions of the tool can be developed for microcontroller manufacturers, first tier tool suppliers, car manufacturers and first tier ECU suppliers.

#### **1.6.** NetGen – Requirement for Improvement

For the NetGen product to survive against market threats, the product needs to be taken in new directions. The higher-end of the market (which is represented by tools with a high level of features and commanding higher pricing) is very crowded. This is especially true for FlexRay tools. Therefore NetGen FlexRay has a large amount of competition. There is the potential for NetGen FlexRay to be a lower cost alternative but the disadvantage of being dominant in the low price sectors is that it can be hard to get large revenues in comparison to the competitors in the high-end pricing sectors. The main reason for this is that the expected number of license sales would not be large enough, even if FlexRay experienced a high level of adoption. Currently the adoption of FlexRay is very low due to company budget limitations and therefore the market is small.

NetGen LIN only has serious competition from two competitors and NetGen J1939 only has serious competition from one competitor. It is desirable to increase revenues by further differentiating the product from the competition and move its market positioning to include higher features and therefore be able to command a higher price. Therefore there is a requirement for the development of novel features to help this product differentiation.

The general market for network stacks is in decline due to the continual emergence of open source projects and an increased perception from customers that free stacks can be successfully integrated into their embedded system products.

#### 1.7. Aim of Research

As has previously been stated, the successful design of automotive electrical architectures involves balancing of the requirements of many different factors. Even

if the number of factors is limited by the design team, the design of an automotive electrical architecture based on in-vehicle networking technology is a very difficult problem to solve. There is very little published literature providing a formalised process for such a design, probably due to the commercial sensitivity. There is also the problem that the amount of information that is required to make design decisions is potentially overwhelming. There is a lack of process for dealing with this information. Therefore the design of an automotive electrical architecture could be described as a black art. The aim of the research described in this report was to ultimately help improve the understanding of the possible decisions involved in the design of an automotive electrical architecture based on in-vehicle networking technology and to formalise the design processes.

The requirements of one of NetGen's customers led the research to initially focus on designing an automotive electrical architecture to a specified target cost. The requirements of a second customer led to the addition of a second factor and therefore the focus was widened to include designing an electrical architecture to a target weight. The requirements of these two customers led to the two case studies that are described in chapters three and six.

The commercial aim was to provide a commercial advantage for the NetGen tool and explore how this could be achieved. To enable further NetGen product differentiation and a move to the higher-end of the market, research was required to ascertain potential new and innovative features. However there was particular emphasis on how much information could be estimated at the very early design stages so that the information required for design decisions could be reduced.

The scope of the research was limited to LIN technology due to the commercial influence of the NetGen LIN product. LIN was the biggest market for

27

the NetGen tool and therefore potential projects and data had the greatest availability in this area.

To achieve the academic and commercial aims, there were the following research objectives. The first was to research the state of the art literature on invehicle networking and the processes used in their design. Secondly to investigate the cost of an automotive door wiring harness which is integrated by hardwiring (in other words not using an in-vehicle networking technology), develop a process for assessing whether a LIN alternative electrical architecture can reduce the cost of the harness and apply the process on the automotive door wiring harness case study. The final research objective was to apply the previously developed cost assessment process on a new case study, a niche sports car manufacturer electrical architecture.

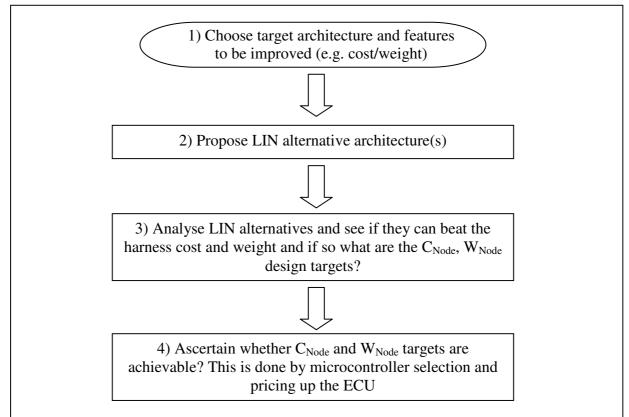

#### **1.8.** Flow of Doctorate Submissions

The outcome of the Engineering Doctorate research was that a number of processes were developed through the case studies. These can be expressed as part of one overall process which is summarised in Figure 5. The overall process consisted of four steps. Step 1 is concerned with the selection of the target architecture for a vehicle which is to be analysed for cost or weight improvement. Step 2 is concerned with the proposal of one or more alternative architectures to be compared. Step 3 is concerned with the analysis of the proposed architectures to see if they can achieve lower cost/weight and determine what nodal cost/weights ( $C_{Node}$  and  $W_{Node}$ ) are required to achieve an equal or lower cost/weight target. Step 4 is concerned with ascertaining whether nodal cost and weight targets ( $C_{Node}$  and  $W_{Node}$ ) are realistically achievable by looking at the communications stack ROM/RAM requirements. The

development of this process is described in the various submissions that were written

throughout the doctorate.

Figure 5 : Top level process developed during the engineering doctorate

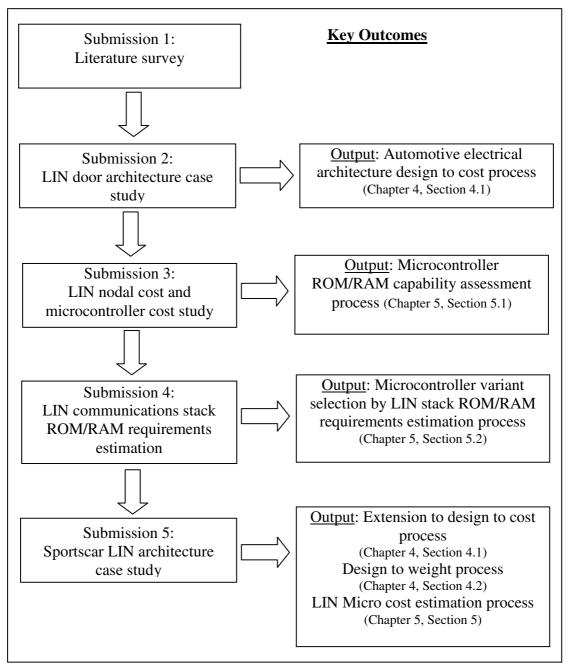

There were five submissions that were submitted to the Engineering Doctorate portfolio:

1. Review of Automotive Electronic Control Systems - Trends, Technologies,

Processes, and Standards

- A Comparison of the Cost of Hardwired and LIN Bus Based Car Door Electrical Architectures

- An Investigation into the Relationship between Microcontroller Monetary Cost and ROM/RAM Capability for Improved Understanding of Automotive Local Interconnect Network Node Cost Issues

- Modelling of Automotive Microcontroller LIN Communications Stack ROM and RAM Requirements for Improved Cost Estimation

A Case Study on the Design to Cost/Low Harness Weight Processes for Local Interconnect Network Based Alternatives to a Niche Sports Car Hardwired Wiring Harness

The suggested reading order is shown in Figure 6. Submission one started the research by looking at the general trends in the adoption of the in-vehicle electronics and in-vehicle networking technologies for the integration of the electronic systems and design process.

The motivation for submission two came from a partnership between a major Japanese wiring harness manufacturer with offices in the UK, and an automotive LIN microcontroller manufacturer with offices in France, both of whom use the NetGen product. The wiring harness manufacturer wanted to see if they could reduce the cost of one of their door system wiring harnesses by the adoption of LIN. Cost data of the bill of materials of the original hardwired driver's door harness was provided by the wiring harness manufacturer. This was analysed and a number of findings came out of this. Firstly it is not very useful to analyse the door harness on its own but best to look at the entire door system. By dividing the entire door system into zones, the harness could be analysed in terms of inter-zone and intra-zone wires (a zone in this case being a vehicle door). The process that was followed is described in chapter four of this report. The study revealed that a very challenging nodal cost target would be needed in order for LIN communications to be added.

Figure 6 : Suggested reading order of the Engineering Doctorate submissions and key outcomes

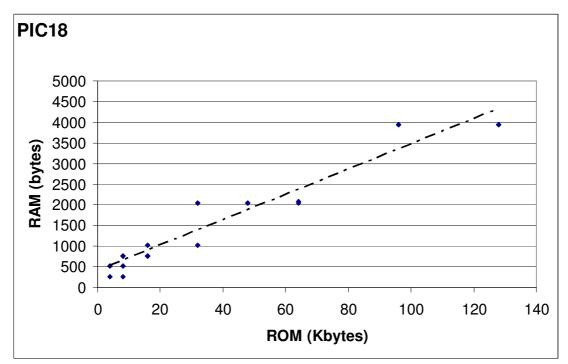

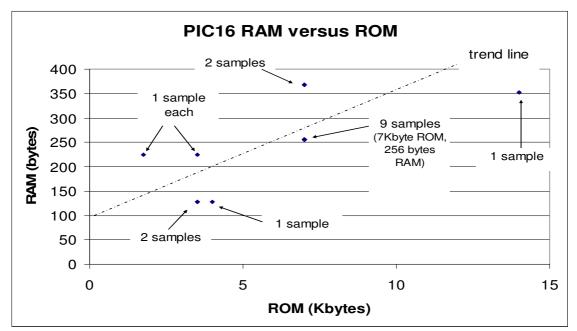

Submission three was motivated by submission two and investigated LIN node cost issues. In particular the relationship between microcontroller unit price and its memory capabilities was investigated for the Microchip 16F and 18F microcontroller families. This was significant as it had the potential to partially quantify the cost of an embedded software component by characterising its ROM and RAM requirements. It was found that the ROM and RAM capabilities did have an effect on unit price but not clearly enough to be able to determine a generic model for microcontroller price estimation. Further investigation showed that there was a linear relationship between the ROM and RAM capability of the microcontroller and that this relationship varied between families (e.g. PIC 16F, 18F and Atmel AVR). This relationship could be used to determine whether a piece of embedded software such as a LIN communications stack could easily be targeted towards a particular microcontroller.

Submission four continued on the subject of the cost of embedded software relating to microcontroller ROM and RAM. This submission investigated whether it was possible to produce models to estimate the ROM and RAM requirements of a LIN communications stack as a function of the number of network nodes, messages and signals. It was found that linear regression modelling did allow estimations to be made.

Submission five applied provided the opportunity to apply the processes developed in the other submissions to a new case study. The aim was to ascertain whether adoption of LIN in body control could be lower cost and lower weight than the hardwired original in a niche sports car. The design-to-cost process that was used in submission two was adapted to form a design-for-low-architecture weight process. It was found that there was likely to be an additional cost rather than a cost saving. However there was potential to reduce the weight with the adoption of LIN.

#### **1.9.** Flow of this Report

Chapter two of this Innovation Report summarises the key points from the literature survey which was outlined in submission one and also makes some updates to the literature based on current developments. Chapter three summarises the case study that was carried out in submission two, which investigated the design-to-cost process of an automotive door electrical architecture based on LIN.

The case study described in chapter three resulted in the development of a process for the design-to-cost of an electrical architecture that allowed an original hardwired architecture to be compared with one or more LIN candidate architectures to ascertain if they can be of lower cost. This resulted in the determination of a target nodal cost that would be required for the LIN architecture to be of lower cost. The process for this is described in chapter four. A design-to-weight process that allows two architectures to be compared in terms of their weight was developed based on the design-to-cost process. This is important since it helps low weight architectures be developed and was required for the second case study that is described in chapter four of this report.

Chapter five outlines the research carried out in submissions three and four that resulted in two processes which are also described in this chapter. The first of these is a process for the assessment of the ROM and RAM capability of a family of microcontrollers so that it can be ascertained how well the family is suited for the design of certain embedded software. The second of these processes is for ROM and RAM requirements estimation of a LIN communications stack so that a microcontroller variant can be selected.

Chapter six describes the case study that was carried out in submission five which investigated the design-to-cost and design-for-low-harness-weight of a sportscar body control electrical architecture. This case study used the design-to-

33

cost/weight processes that are described in chapter four and the microcontroller variant selection process that is described in chapter five.

Chapter seven concludes this Innovation Report and summarises the key innovations from the research carried out. It also outlines recommendations for further research.

#### 2. LITERATURE SURVEY

#### 2.1. Trends in Automotive Electronic Systems Integration

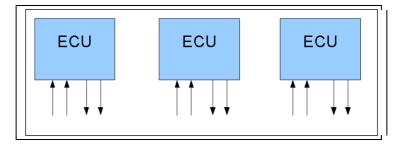

Early microcontroller based automotive control systems had a small number of ECUs with sensors and actuators connected directly to the ECU that used the signal. This often resulted in duplicate sensors being used providing the same information. An example of this method of ECU integration is shown in Figure 7.

Figure 7: Stand alone ECUs (No Integration)

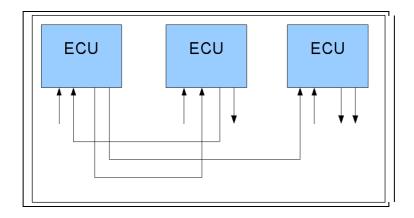

Figure 8: Hard-wired ECU Integration

An improvement to stand alone ECUs was to integrate ECUs with hard-wired signals. Therefore if two ECUs required the same signal, they could share the information from one sensor. This provided the benefit of cost saving by reduction of duplicate sensors. However, as the number of ECUs and sensors grew, this approach

to ECU integration became very complicated and the weight of the wiring harness grew significantly. A large number of connectors within the wiring harness were required, which in turn led to reliability problems. Another significant problem of the hardwired integration method is cross-talk between wires caused by induced electrical interference (Khoh, 1993). An example of this method of integration is shown in Figure 8.

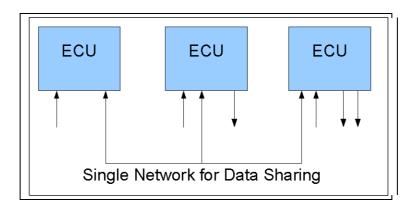

The problems associated with hard-wired integration led to the adoption of digital networks. Networks can have ring, star or bus architectures. The single bus architecture was adopted by the automotive industry for integration of ECUs since it was the most economically viable. This provided a number of benefits such as reduced wiring harness weight, reduction of the number of connectors, increased reliability, simplified assembly and ease of upgradeability for new ECUs and automotive platform customer option ECU management (McLaughlin, 1993). An example of this method of integration is shown in Figure 9.

Figure 9: Single Bus Integration

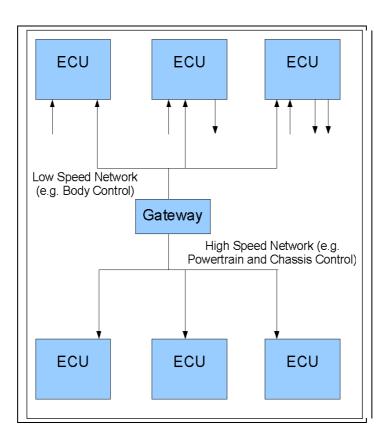

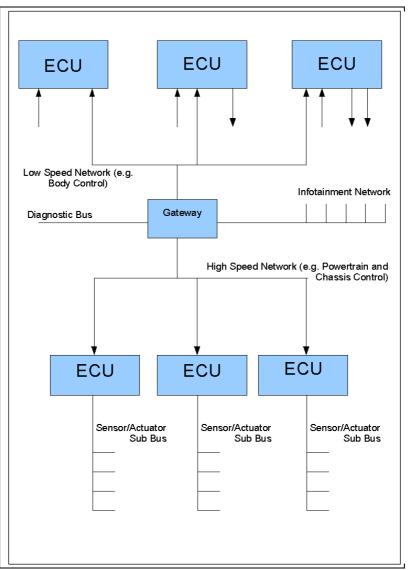

Early data bus systems were based on some kind of message arbitration methodology which resulted in message latency becoming very unpredictable at higher bus loads. Therefore to maintain reasonable message latency, it became appropriate to partition the automotive electrical architecture between hard real time and soft real time functionality. An example of this is shown in Figure 10 in which powertrain (e.g. engine management, gearbox control) or chassis systems (e.g. braking, steering controls) are integrated via the high speed data bus and body control systems (e.g. lighting and door controls) are integrated via the low speed data bus.

Figure 10: Partitioning of Automotive Electrical Architecture into a Two Bus System

The adoption of electronic control systems continued to grow as a result of the integration ability provided by early in-vehicle network systems. This led to two problems, partitioning and optimal cost. A dual network system had limitations when the number of electronic systems (and therefore ECUs) grew beyond the capabilities of a two-network system. Therefore the number of networks required within the vehicle's electrical architecture increased. However, partitioning the system into

similar levels of safety criticality and real-time requirements can lead to a single network technology being sub-optimal. It can be found to be too powerful for some low-end applications (therefore wasting resources and money) or not powerful enough for high end applications. Therefore multiple network partitioned automotive systems have been the state of the art as shown in Figure 11. Infotainment, real-time control, low speed body and sensor/actuator bus systems are shown in Figure 11.

Figure 11: Multiple Network Partitioned Automotive Electrical Architecture (e.g. Real Time Control Networks, Sensor/Actuator Sub-buses, One Infotainment Network, One Diagnostic Bus - ideally partitioned by function but more usually by data sharing requirements)

## 2.2. Automotive In-Vehicle Networking Technologies for Control

Open standard in-vehicle data networks such as SAE J1850, SAE J1597, SAE J2106 and the Vehicle Area Network (VAN; ISO11519 Part 3) have been successfully applied to many mass production motor vehicles over the last twenty years. BEAN (Body Electronics Area Network) has been adopted as a proprietary protocol used specifically in Toyota. Their successful application has been due to their ability to deliver low system cost, lower weight through reduced wiring loom size, increased reliability, maintainability and sensor data sharing. The fact that such protocols have been open-standard is one of the over-riding causes of their lower cost, since suppliers to the automotive OEMs (both systems and semiconductors) can quickly and economically access the technology and supply different OEMs with similar products. Although these open network protocols existed, suppliers had to adapt to whatever protocol was used by their suppliers. This was costly in terms of tools, expertise and software maintenance.

### 2.2.1. Controller Area Network Based Technologies

CAN was developed by Robert Bosch GmbH in the 1990s (CAN Specification Version 2.0; 1991). Of the currently available open standard network protocols, CAN has become the most prominent across the world's automotive industry and is the de-facto standard adopted by most automotive manufacturers. The probable reasons for the significant adoption have been its huge support from major semiconductor manufacturers, tool suppliers and automotive OEMs. Now, nearly all automotive OEMs worldwide have products available with CAN or are intending to develop with CAN in the near future. The Controller Area Network is standardised

under ISO-11898, which itself is split into four parts. The main features of CAN are summarised as:-

- Event based communication

- Standard CAN (11 bit identifiers) and Extended CAN (29 bit identifiers introduced for the US truck and bus industry in SAE J1939)

- Bus access is Carrier Sense Multiple Access Collision Detection (CSMA/CD) with Non-Destructive Bitwise Arbitration (NDBA), the lowest value identifier has highest priority for bus access

- Retransmission of messages that lose arbitration

- Silicon available from most semiconductor manufacturers

There are at least four physical layers available to suit different applications: CAN High Speed up to 1Mbaud (ISO-11898), Low Speed or Fault Tolerant CAN at up to 125Kbaud (ISO-11519-2), truck and bus protocol up to 250Kbaud (ISO-11992 Part 1), and Single Wire CAN up to 33.3Kbaud.

The CAN protocol specifies the method by which data is passed between communicating devices on a CAN bus. It conforms to the ISO Open System Interconnection (OSI) model (ISO7498), which is a seven-layer description of a telecommunications network standard. The OSI model describes a layered system of communication between two network nodes, whereby in theory each layer can only communicate with the layers directly above and below it in the local node, and only with the equivalent layer in a remote node. In fact, the CAN protocol can be described by the lowest two layers of the OSI model – the Data Link Layer and the Physical Layer (layers 2 and 1 respectively). The Application Layer (layer 7) protocols can be proprietary schemes developed by individual CAN users or one of the emerging standards used within particular industries. In the automotive industry most manufacturers use their own proprietary standard.

CAN was originally designed for the automotive industry, but it has many applications elsewhere. Amongst the first applications were in industrial automation type applications using the CAN higher layer protocols DeviceNet and CANopen. CANopen has been applied in more varied applications than DeviceNet. CANopen has specialist profiles for industries such as lifts, marine controls and railways controls (Pfeiffer et al, 2003). This has now allowed it to reach the aerospace industry since CANopen is used in the Airbus A380 for lift control between three floors of the aircraft and the runway (CAN Newsletter 3/2006\_1). DeviceNet is mostly limited to industrial automation applications such as those used in manufacturing lines.

SAE J1939 is the CAN higher layer protocol for the bus, truck and offhighway industries. The passenger car market tends to use proprietary higher layer protocols within vehicle manufacturers with virtually no standardisation. However, this was not possible with the truck industry. Truck cabs are required to connect to a variety of trailers from different manufacturers and therefore standardisation was required. SAE J1939 was specified for this purpose and the result is that certain CAN messages have a specific purpose, e.g. there is a CAN message for engine management information.

CANaerospace is a protocol which was designed for the highly reliable communication of microcomputer-based systems in airborne applications via CAN. The purpose of the protocol is for applications requiring an efficient data flow and easy time-frame synchronisation within redundant systems. The definition is kept widely open to allow implementation of user-defined message types and protocols. It

41

has been applied commercially in applications such as the Airbus A380 and the Eurofighter.

NMEA2000 is a protocol based upon the SAE J1939 standard from the National Marine Electronics Association (http://www.nmea.org) to interconnect various electronic units onboard ships and smaller recreational and commercial vessels. The development of this standard began in 1994 and it was released in 2001. The standard currently operates at 250 Kbit/s.

MILCAN is a specification for a CAN based protocol for military applications and borrows parts from CANopen and SAE J1939. MILCAN has been used commercially by BAe Systems for the communication in an air-transportable armoured combat vehicle Terrier for the British Royal Engineers (CAN Newsletter 3/2006\_2). MILCAN is used for operations such as drive-by-wire using a dual redundant bus and also a variety of functions such as power management.

# 2.2.2. Local Interconnect Network (LIN)

The LIN consortium was set up in 1999 to develop a new low cost bus for intelligent sensor and actuator applications not requiring the sophistication of CAN, referred to as the Local Interconnect Network. Core members include Freescale, BMW, Volvo and DaimlerChrysler. The LIN specification is currently at revision v2.1.

Many body control functions are often simple digital on/off operations, such as activating lights, wipers and windows. These are considered soft requirement real time systems that do not necessarily need the hard real time response that can be provided by CAN. Therefore a lower performance, more economical technology can be used. The LIN protocol development commenced in 1999 and was introduced in 2000 (Wense; 2000). It provides an open market alternative to the proposed TTP/A protocol (Kopetz; 1995) for low cost sub-bus systems to complement CAN in applications such as vehicle roof (rain sensor, light sensor, light control, sun roof), vehicle doors (mirror, central locking, mirror switch, window lift), engine (sensors, small motors, steering wheel, cruise control switches, wiper, turn signal, radio, climate control) and seat (seat position motors, seat heater, occupancy sensor).

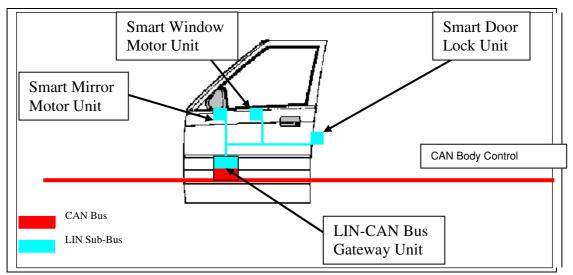

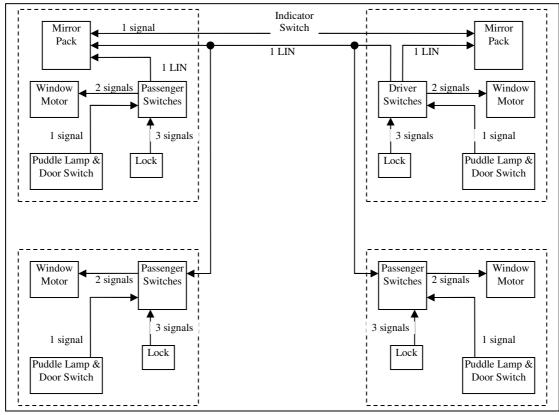

The main features of LIN are that it is UART based and uses a physical layer based on ISO-9141. It is limited to 20Kbaud and allows transfer of up to 8 bytes of information at a time. The application of LIN gives rise to the type of vehicle body control network architecture shown in Figure 12, which shows an example LIN subbus for control of a car door electrical sub-system. It can be seen that the main body control CAN network interfaces with the rest of the door system via a LIN-CAN Bus Gateway Unit. A single LIN signal line is used to connect the LIN-CAN Bus Gateway Unit to the Smart Door Lock Unit, Smart Mirror Motor Unit and Smart Window Motor Unit.

A deviation from the LIN consortium's main LIN protocol is SAE J2602, which is a variant of LIN 2.0. SAE J2602 is fixed to 10.4 Kbit/s to bring it in line with the legacy SAE J1850 protocol used by US automotive manufacturers.

The aim of the LIN 2.0/2.1 protocol is to provide the ability to purchase Commercial Off-The-Shelf (COTS) components, such as intelligent sensor and actuators, which are easily and rapidly integrated into an ECU with the use of LIN. Revision 2.0/2.1 provides diagnostic and plug/play features that are not in versions 1.2/1.3.

Figure 12 : A typical use of a combination of the LIN sub-bus along with the CAN bus in the localised area of car door control.

# 2.2.3. Emergence of High Speed Time Triggered Automotive Control Networks

CAN and LIN technologies enjoy widespread adoption in most vehicles that are currently manufactured. However there has been the emergence of a number of network technologies to address the needs of future high speed automotive control networking which tend to be generically referred to as "time triggered". In general these requirements are to deliver higher bandwidth, determinism and failsafe features. Higher bandwidth provides the ability to transfer more data across the network and therefore a number of lower speed networks such as CAN have the possibility to be replaced by a single higher speed network. Determinism is achieved by rigid scheduling techniques which are generically referred to as "time triggered" in the automotive industry and provide the ability to precisely know when a message is late and synchronise applications over the network. Failsafe features provide support such as backup network channels to provide alternative data routes and bus guardians to prevent babbling idiot failures. Over recent years there have been five main technologies that have emerged as the main contenders for applications beyond the capabilities of CAN, although only one of them currently looks likely to become the de-facto standard. These are Time Triggered CAN (TTCAN), TTP/C, Byteflight and FlexRay. The main protocol features are compared in Table 3.

|            | Bandwidth                         | Scheduling                 | Failsafe Features            |

|------------|-----------------------------------|----------------------------|------------------------------|

| TTCAN      | 1Mbit/s                           | TDMA                       | None                         |

| TTP/C      | 25Mbit/s<br>Unlimited (in theory) | TDMA                       | Dual channel<br>Bus Guardian |

| Byteflight | 10Mbit/s                          | Mini-slotting              | None                         |

| FlexRay    | 10Mbit/s                          | TDMA and mini-<br>slotting | Dual channel<br>Bus Guardian |

Table 3: Top level comparison of automotive time triggered protocol candidates

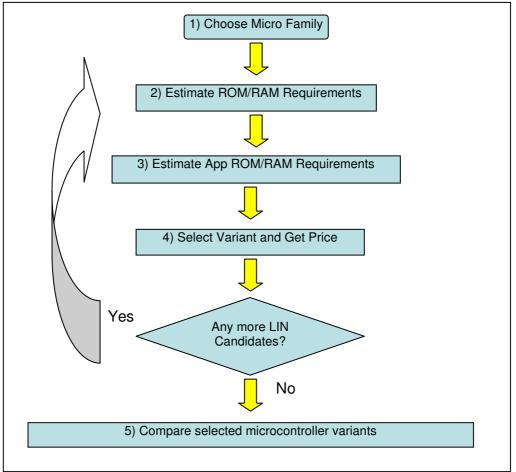

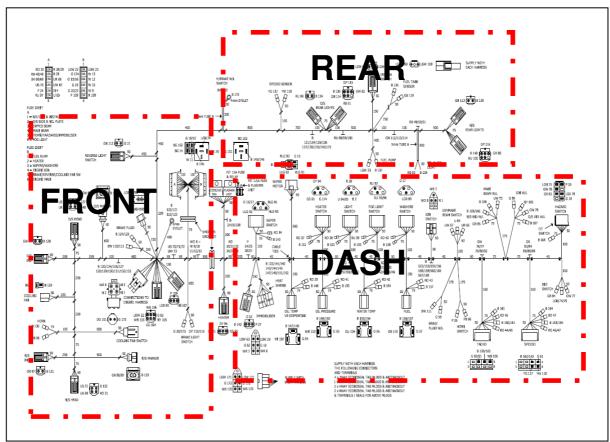

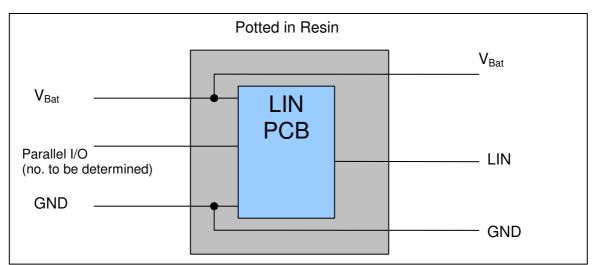

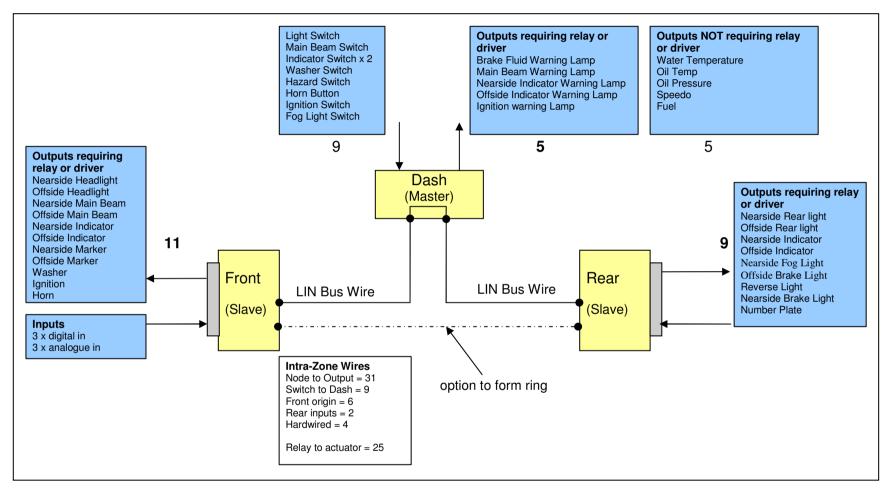

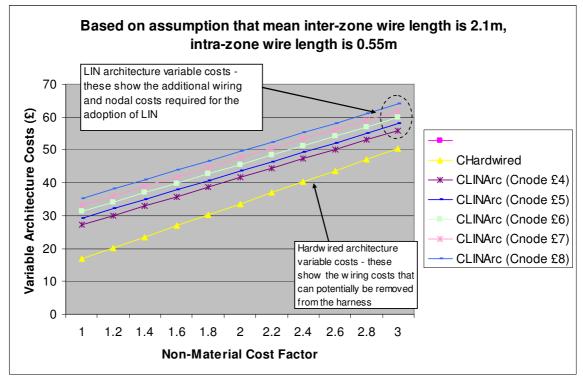

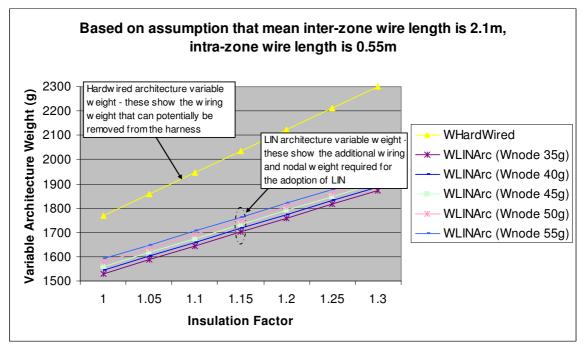

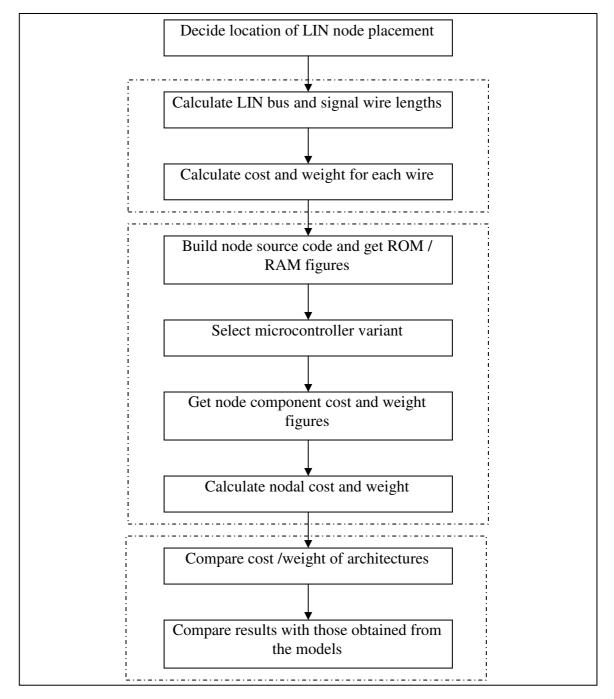

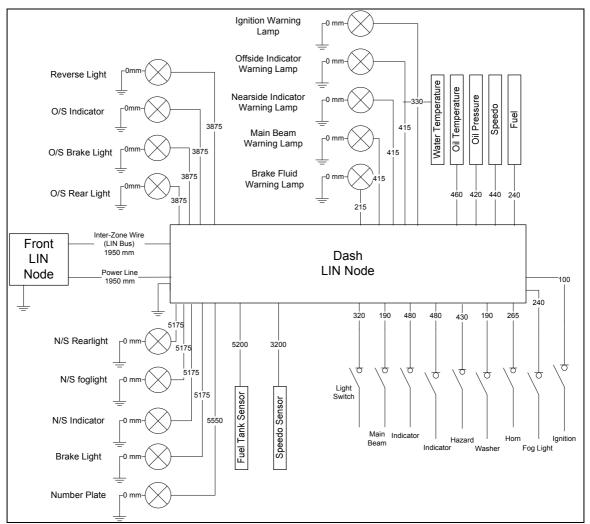

The main feature that is common with the emerging network technologies is that their scheduling mechanism is known as "time triggered". There are two main time triggered scheduling methodologies that are used; Time Division Media Access (TDMA) and mini-slotting.