University of Warwick institutional repository: http://go.warwick.ac.uk/wrap

#### A Thesis Submitted for the Degree of PhD at the University of Warwick

http://go.warwick.ac.uk/wrap/36283

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it. Our policy information is available from the repository home page.

No access Sefore Apr 98

# High Sample-Rate Givens Rotations for Recursive Least Squares

Richard Lewis Walke

A thesis submitted to The University of Warwick for the degree of

**DOCTOR OF PHILOSOPHY**

**Faculty of Science**

**Department of Computer Science**

**July 1997**

To Valerie

# **Summary**

The design of an application-specific integrated circuit of a parallel array processor is considered for recursive least squares by QR decomposition using Givens rotations, applicable in adaptive filtering and beamforming applications. Emphasis is on high sample-rate operation, which, for this recursive algorithm, means that the time to perform arithmetic operations is critical. The algorithm, architecture and arithmetic are considered in a single integrated design procedure to achieve optimum results.

A realisation approach using standard arithmetic operators, add, multiply and divide is adopted. The design of high-throughput operators with low delay is addressed for fixed- and floating-point number formats, and the application of redundant arithmetic considered. New redundant multiplier architectures are presented enabling reductions in area of up to 25%, whilst maintaining low delay. A technique is presented enabling the use of a conventional tree multiplier in recursive applications, allowing savings in area and delay. Two new divider architectures are presented showing benefits compared with the radix-2 modified SRT algorithm.

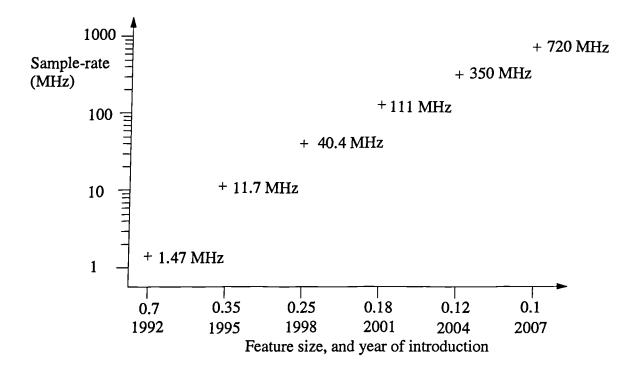

Givens rotation algorithms are examined to determine their suitability for VLSI implementation. A novel algorithm, based on the Squared Givens Rotation (SGR) algorithm, is developed enabling the sample-rate to be increased by a factor of approximately 6 and offering area reductions up to a factor of 2 over previous approaches. An estimated sample-rate of 136 MHz could be achieved using a standard cell approach and 0.35µm CMOS technology.

The enhanced SGR algorithm has been compared with a CORDIC approach and shown to benefit by a factor of 3 in area and over 11 in sample-rate. When compared with a recent implementation on a parallel array of general purpose (GP) DSP chips, it is estimated that a single application specific chip could offer up to 1,500 times the computation obtained from a single GP DSP chip.

# **Contents**

| Chapter | 1 Introduction 1                              |

|---------|-----------------------------------------------|

| 1.1     | Background1                                   |

| 1.2     | Objective of Research                         |

| 1.3     | Adaptive Filtering3                           |

| 1.4     | The QR-Algorithm6                             |

| 1.5     | The QR-Array 8                                |

| 1.6     | Performing Rotations in VLSI9                 |

| 1.7     | VLSI Design Methodology12                     |

| 1.8     | Overview of Thesis                            |

| Chapter | 2 Redundant Arithmetic                        |

| 2.1     | Introduction                                  |

| 2.2     | Redundant Number Systems                      |

| 2.3     | Addition of Redundant Numbers                 |

| 2.4     | Most-Significant-Digit-First Arithmetic       |

| 2.5     | DSP Using Msdf Arithmetic                     |

| Chapter | 3 High-Throughput, Low-Latency Multipliers 31 |

| 3.1     | Introduction                                  |

| 3.2     | Msdf Multipliers                              |

| 3.3     | Tree-Based Multipliers                        |

| 3.4     | Discussion of Multiplier Results62            |

| Chapter | 4 High-Throughput, Low-Latency Dividers 64    |

| 4.1     | Introduction64                                |

| 4.2     | Overview of Division65                        |

| 4.3     | Digit Recurrence Methods                      |

|     | 4.4        | Radix-2 Modified SRT69                                     |

|-----|------------|------------------------------------------------------------|

|     | 4.5        | Speculative SRT                                            |

|     | 4.6        | Multiplier-Based Division Methods                          |

|     | 4.7        | Low-Latency Convergence Divider80                          |

|     | 4.8        | Summary of Divider Results89                               |

| Cha | pter       | 5 Floating-Point Operators 91                              |

|     | 5.1        | Introduction91                                             |

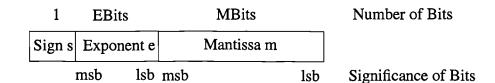

|     | 5.2        | Floating-Point Representation92                            |

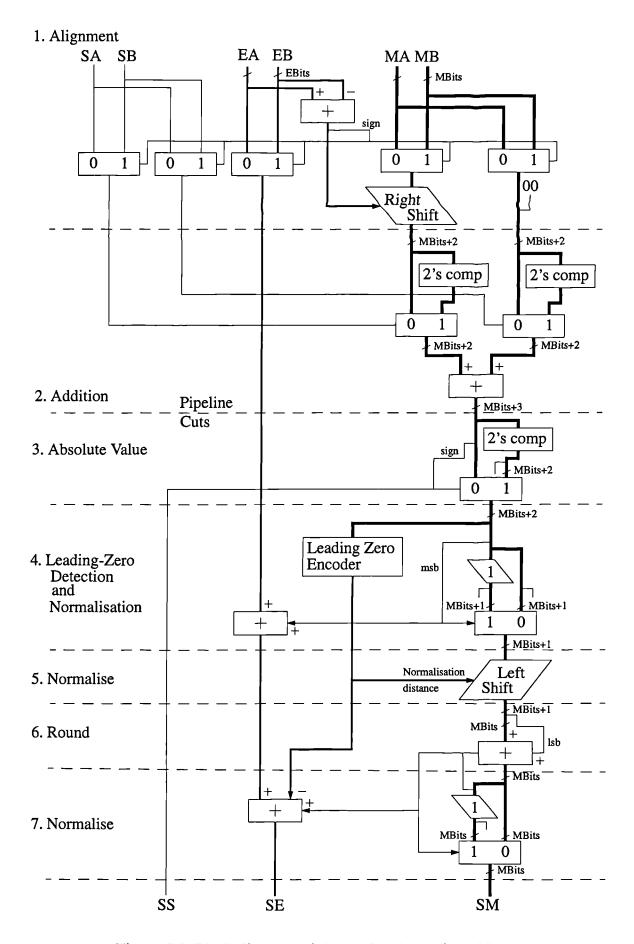

|     | 5.3        | Floating-Point Adder93                                     |

|     | 5.4        | Fixed/Floating Point Adder100                              |

|     | 5.5        | Floating-Point Multiplication                              |

|     | 5.6        | Floating-Point Division                                    |

|     | 5.7        | Other Operators                                            |

|     | 5.8        | Comments on Floating-Point Operator Designs                |

| Cha | pter       | 6 Givens Rotation Algorithm Variants 116                   |

|     | 6.1        | Overview of Givens Rotation Algorithm Variants             |

|     | 6.2        | Square-Root-Free Algorithm121                              |

|     | 6.3        | Divide-and-Square-Root-Free Algorithm                      |

|     | 6.4        | Summary of Givens Rotation Algorithms130                   |

|     | 6.5        | Normalisation of Conventional Givens Rotation Algorithm131 |

| Cha | pter       | 7 Comparison of Givens Rotation Algorithms 138             |

|     | 7.1        | Introduction                                               |

|     | 7.2        | Conventional Givens Rotations141                           |

|     | 7.0        | Normalised Algorithms144                                   |

|     | 7.3        | 1.0111a1130a / 11g011a1113                                 |

|     | 7.3<br>7.4 | Square-Root-Free Algorithms                                |

| 7.6      | Com   | parison Between Algorithms                                   |

|----------|-------|--------------------------------------------------------------|

| Chapter  | 8     | Architecture of Adaptive Filter 167                          |

| 8.1      | Intro | oduction167                                                  |

| 8.2      | Para  | llel Array Processing167                                     |

| 8.3      | Full- | Sized QR-Array Solution170                                   |

| 8.4      | LPG   | S Linear Array Solution171                                   |

| 8.5      | LSG   | P Solution176                                                |

| 8.6      | VLS   | I Implementation of Full-Sized Array                         |

| 8.7      | QR-   | Array Implementation using General Purpose DSP Processors183 |

| 8.8      | Adap  | ptive Beamforming Application186                             |

| 8.9      | Disc  | ussion187                                                    |

| Chapter  | 9     | Conclusions 189                                              |

| 9.1      | Over  | view189                                                      |

| 9.2      | Low   | -Latency Arithmetic189                                       |

| 9.3      | Give  | ns Rotation Algorithm191                                     |

| 9.4      | Appl  | ication Specific Array Processor192                          |

| 9.5      | Futu  | re Work193                                                   |

| Chapter  | 10    | References                                                   |

| Appendi  | x A   | Analysis of Msdf Multiplier-Adders 210                       |

| Appendi  | х В   | Low-Latency, High-Throughput Redundant                       |

|          |       | Squarer                                                      |

| Appendi  | x C   | <b>Summary of Convergence Reciprocal Circuit</b>             |

|          |       | Parameters                                                   |

| Appendi  | x D   | Numerical Effect in Normalised Algorithm 225                 |

| Appendix | хE    | Overview of Channel Equaliser Application 226                |

# **List of Figures**

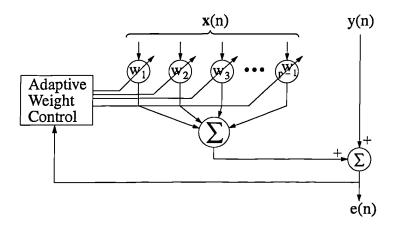

| 1.1  | Adaptive linear combiner                                                   |

|------|----------------------------------------------------------------------------|

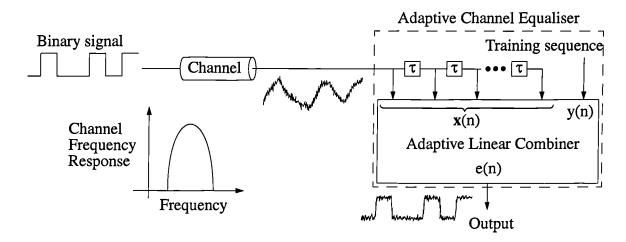

| 1.2  | Channel equalisation using an adaptive filter5                             |

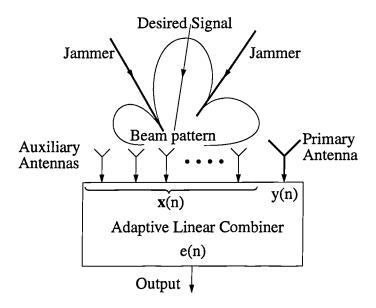

| 1.3  | Diagram of an adaptive sidelobe canceller5                                 |

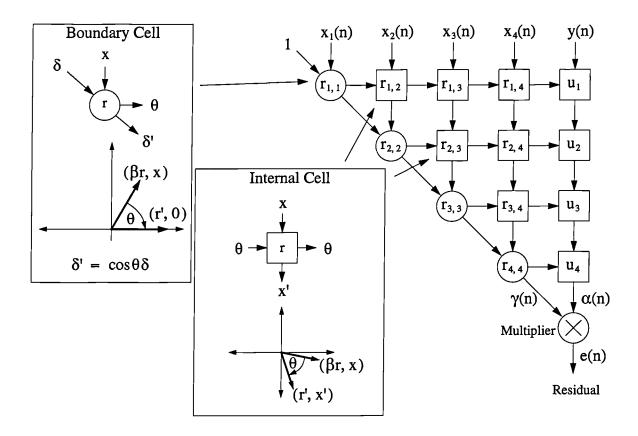

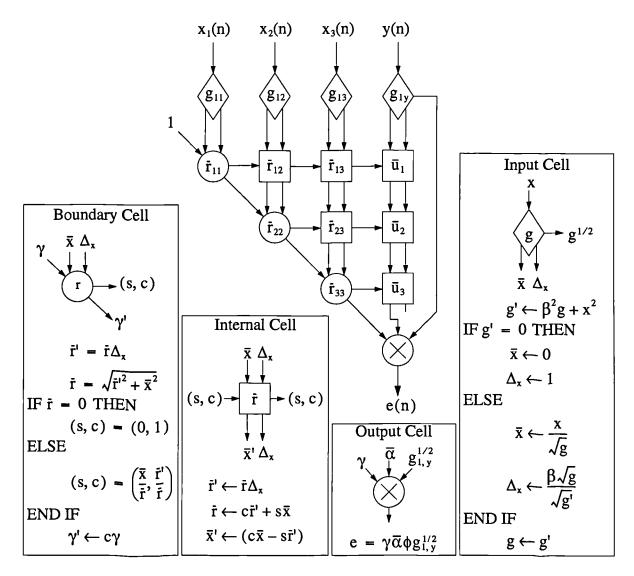

| 1.4  | The QR-array architecture for performing the QR-algorithm 8                |

| 1.5  | Signal flow graph of conventional rotation algorithm                       |

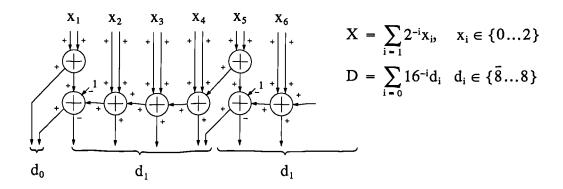

| 2.1  | An example of modified Booth's recoding                                    |

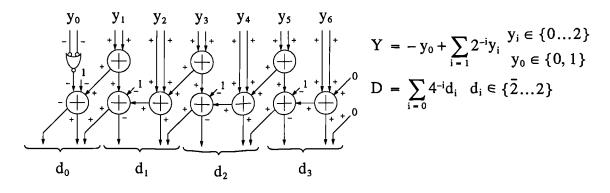

| 2.2  | Redundant number adders                                                    |

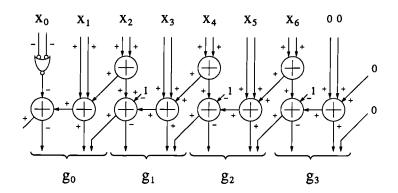

| 2.3  | The generalised full-adder                                                 |

| 2.4  | Using full-adders to add a signed-binary and a binary number               |

| 2.5  | Using full-adders to add two signed-binary numbers                         |

| 2.6  | Using full-adders to add two MinR4 numbers24                               |

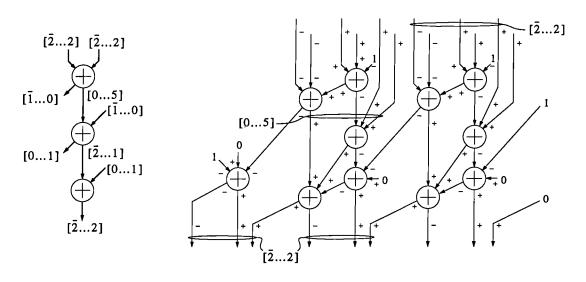

| 2.7  | Digit-serial, on-line computation                                          |

| 2.8  | Msdf arithmetic                                                            |

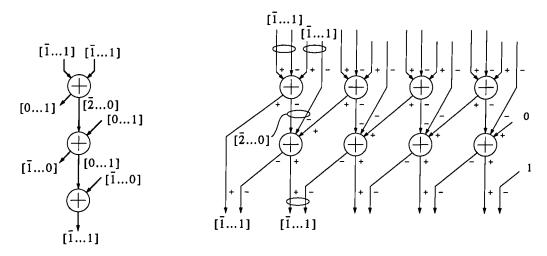

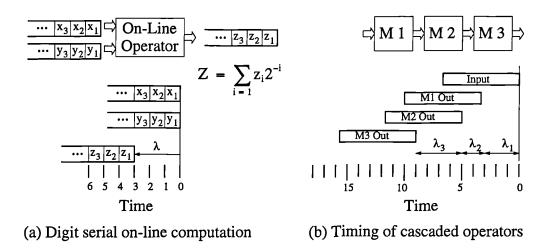

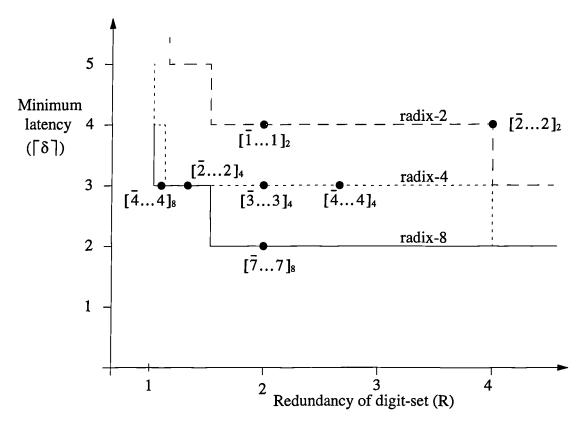

| 3.1  | Minimum latency for a range of digit redundancy and radix                  |

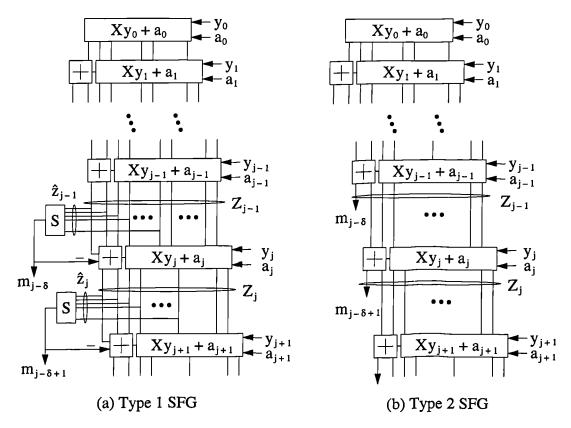

| 3.2  | Msdf multiplier-adder architectures                                        |

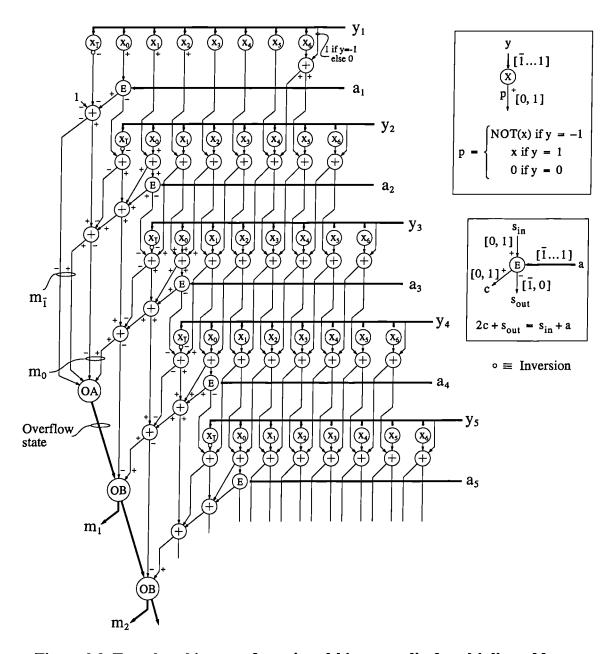

| 3.3  | Type 2 architecture for a signed-binary, radix-2 multiplier-adder 40       |

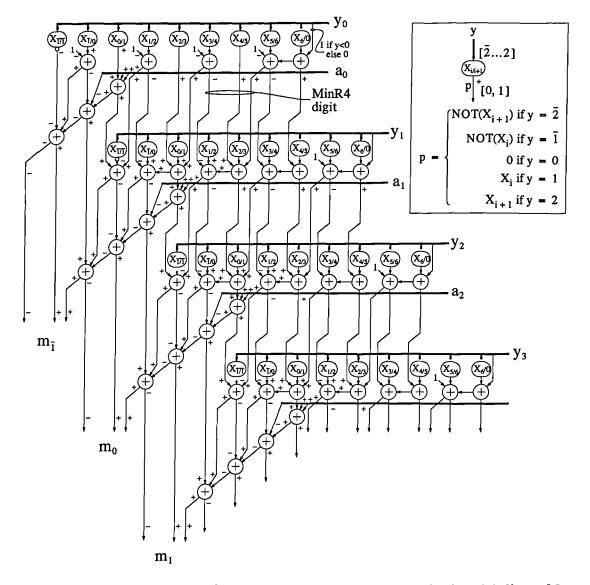

| 3.4  | Type 2 architecture for a minimally-redundant, radix-4 multiplier-adder 41 |

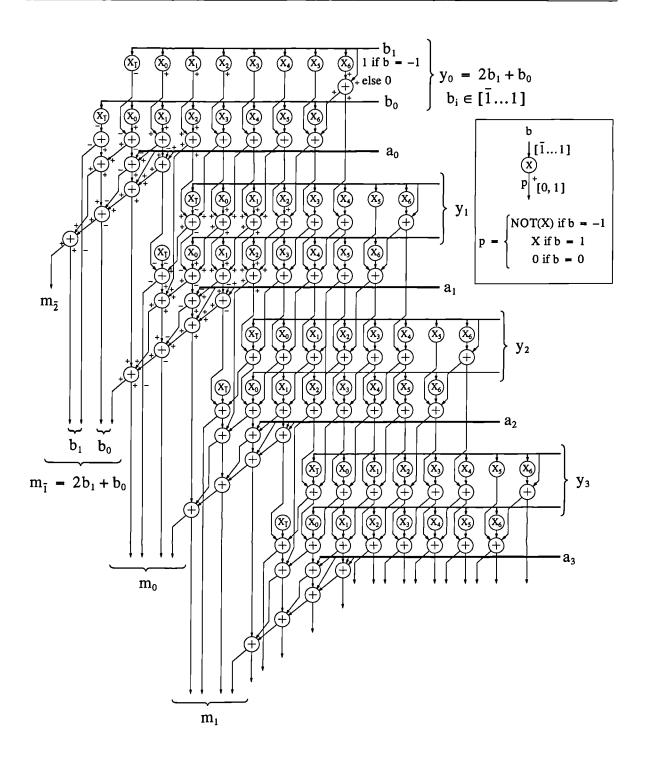

| 3.5  | Type 2 architecture for a maximally redundant radix-4 multiplier-adder 43  |

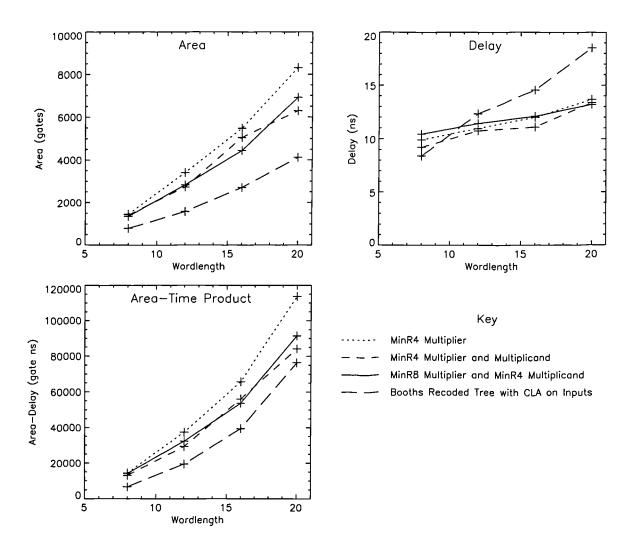

| 3.6  | Delay and area comparison of msdf multipliers                              |

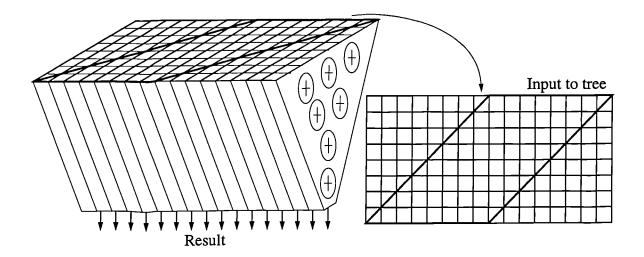

| 3.7  | Tree-based redundant multiplier                                            |

| 3.8  | Simplified adder-tree                                                      |

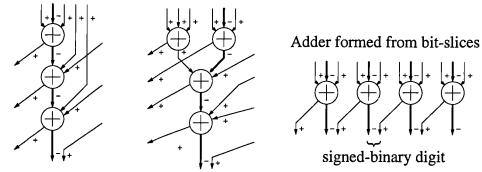

| 3.9  | Obtaining signed-binary output from adders 50                              |

| 3.10 | Obtaining signed-binary from a conventional adder-tree                     |

| 3.11 | Recoding from signed-binary to MinR4                                       |

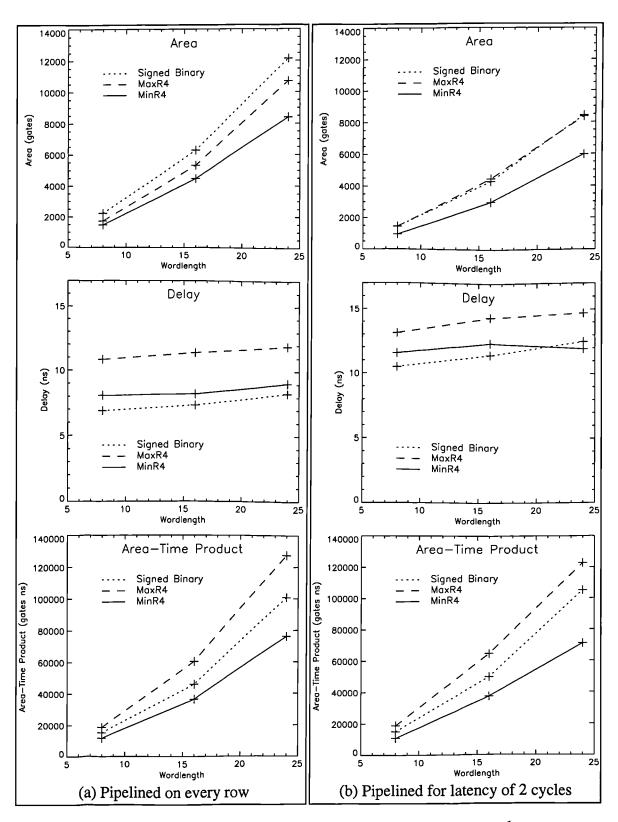

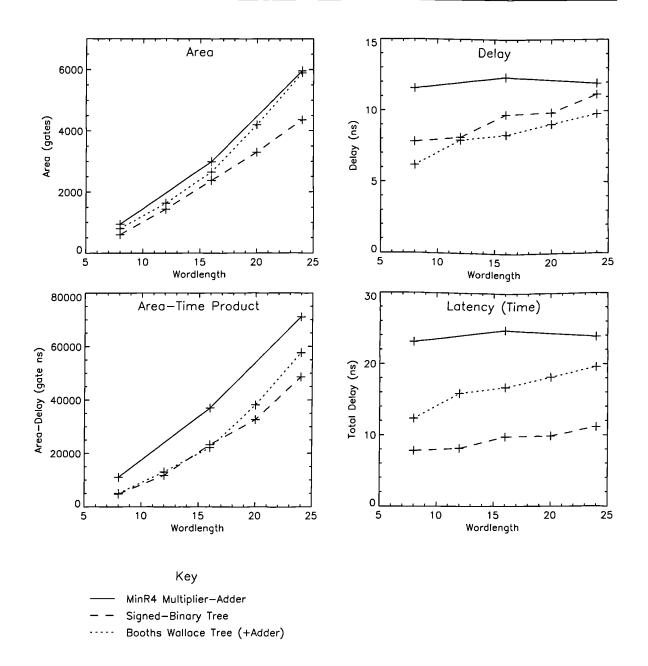

| 3.12 | Speed and area comparison of tree-based, redundant multipliers 53          |

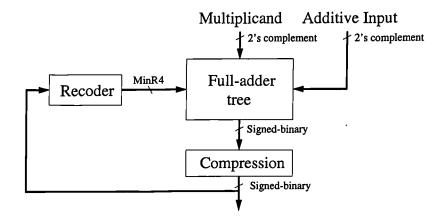

| 3.13 | Block diagram of recoded, redundant multiplier                   |

|------|------------------------------------------------------------------|

| 3.14 | Recoding from carry-save to MinR16                               |

| 3.15 | Recoding from carry-save to MinR4                                |

| 3.16 | Recoding of 2X from carry-save to MinR4                          |

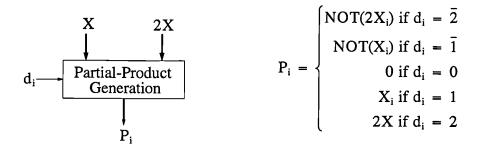

| 3.17 | Partial-product generation                                       |

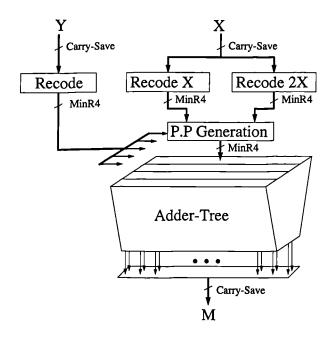

| 3.18 | Speed and area comparison of tree-based redundant multipliers    |

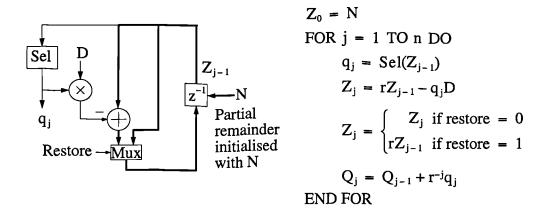

| 4.1  | Division using digit recurrence                                  |

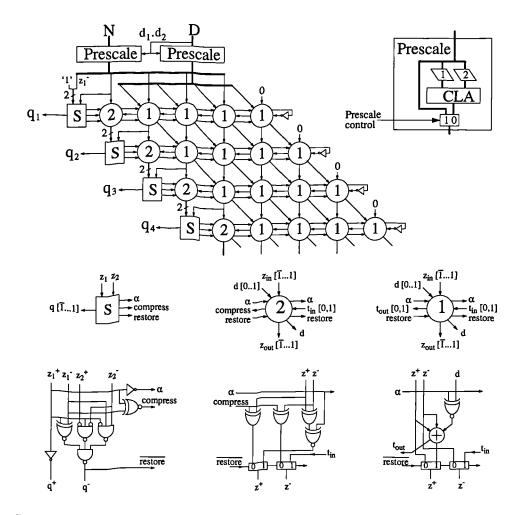

| 4.2  | Radix-2 modified SRT division array with prescaling              |

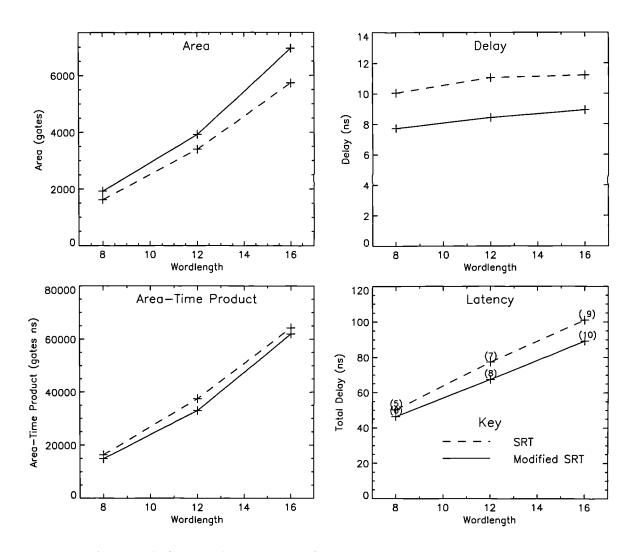

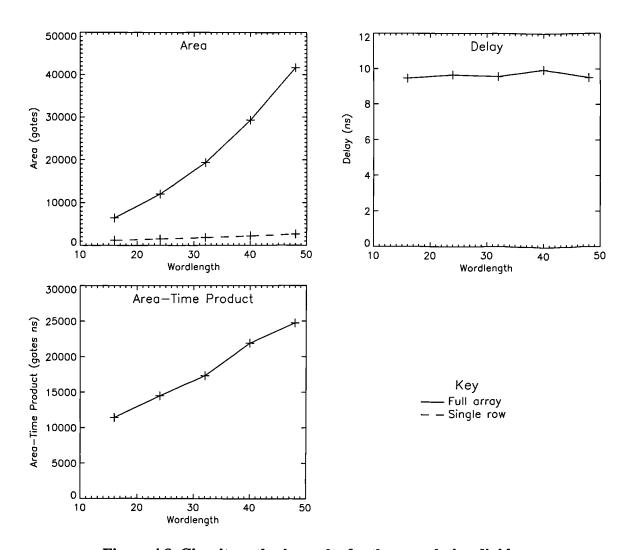

| 4.3  | Area and speed of modified SRT divider71                         |

| 4.4  | Comparison between SRT and modified SRT algorithms               |

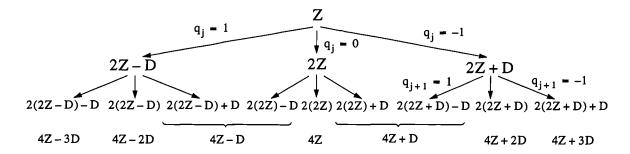

| 4.5  | Speculative calculation of SRT partial remainders                |

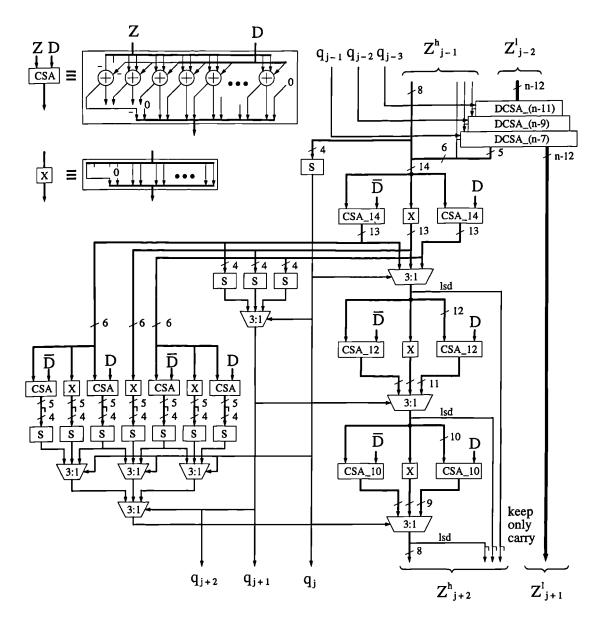

| 4.6  | Block diagram of one row of the radix-8 speculative divider      |

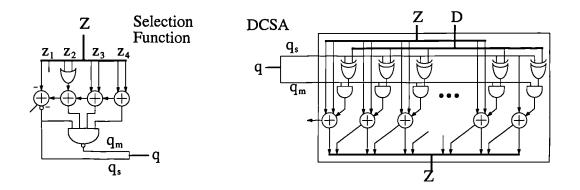

| 4.7  | Logical implementation of selection function and DCSA            |

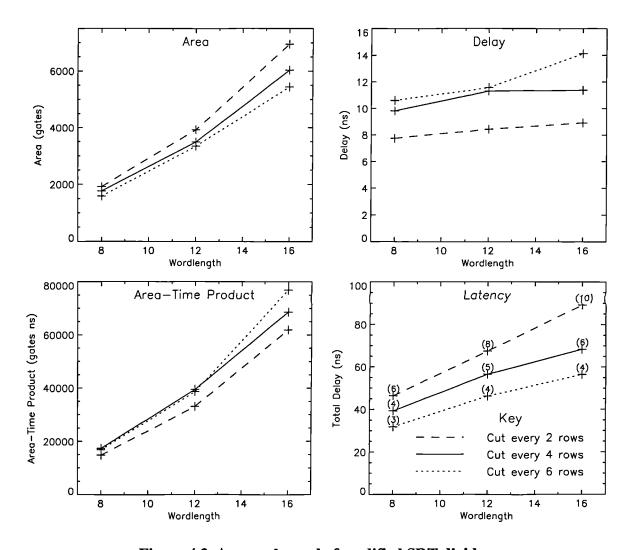

| 4.8  | Circuit synthesis results for the speculative divider            |

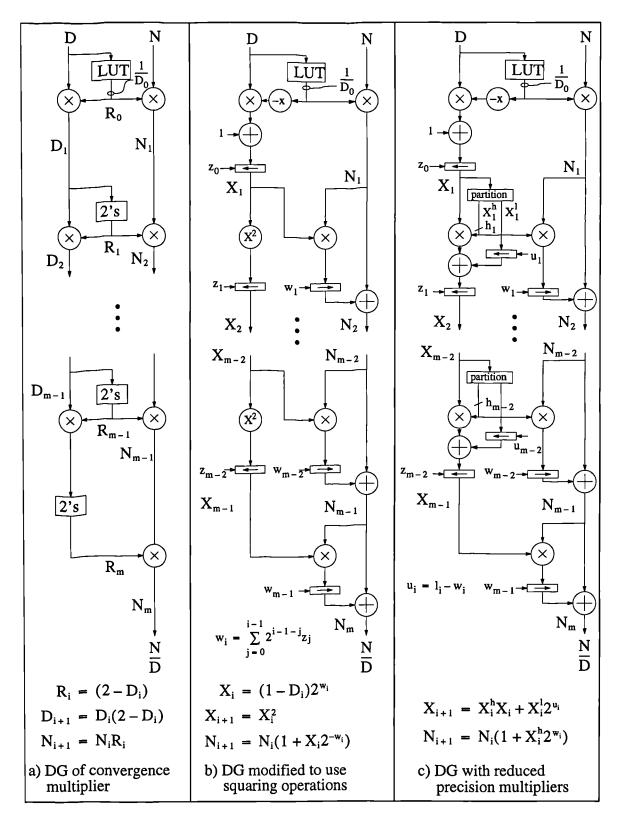

| 4.9  | Dependence graphs for division by multiplicative convergence     |

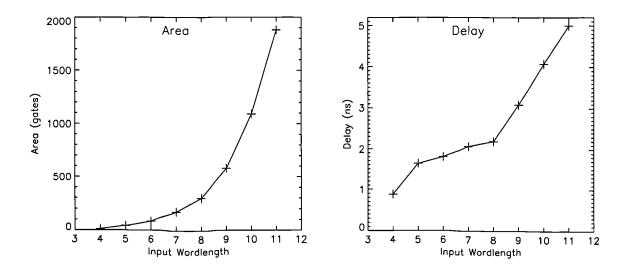

| 4.10 | Circuit synthesis results for reciprocal LUT                     |

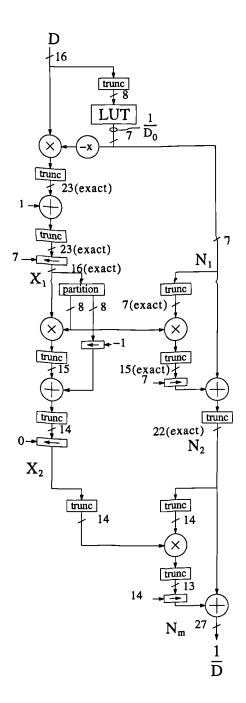

| 4.11 | DG for 16-bit reciprocal                                         |

| 4.12 | Circuit synthesis results of the convergence reciprocal circuits |

| 5.1  | Floating-point number format92                                   |

| 5.2  | Block diagram of simple floating-point adder                     |

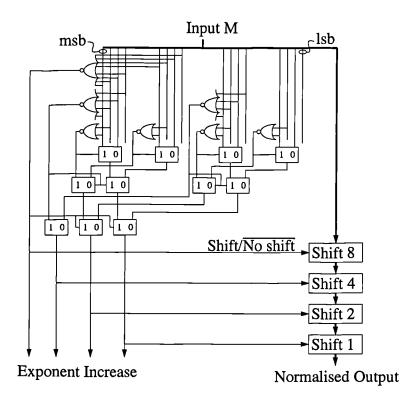

| 5.3  | Normalisation using speculation of leading zeros                 |

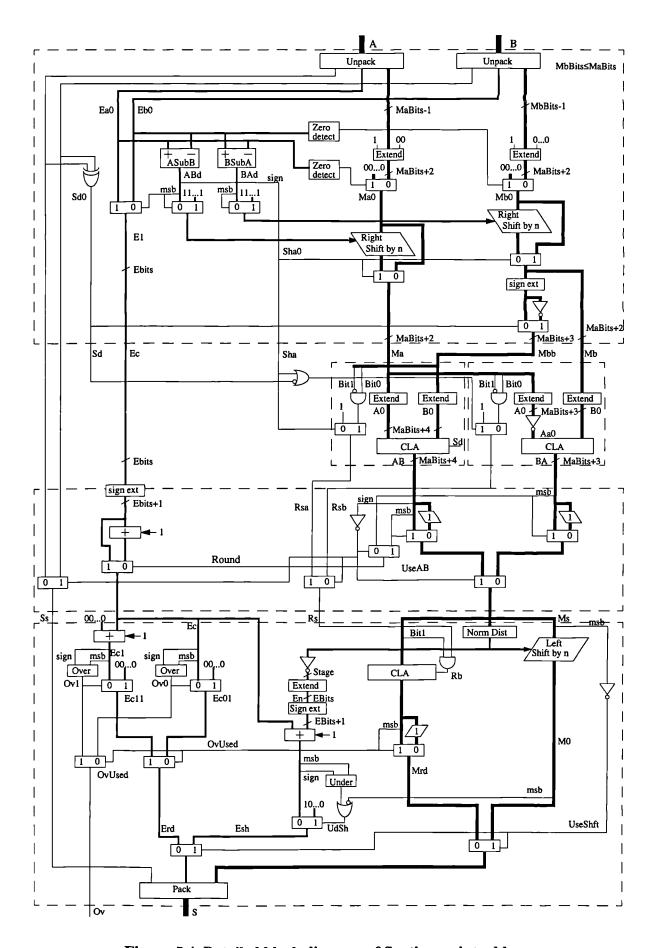

| 5.4  | Detailed block diagram of floating-point adder                   |

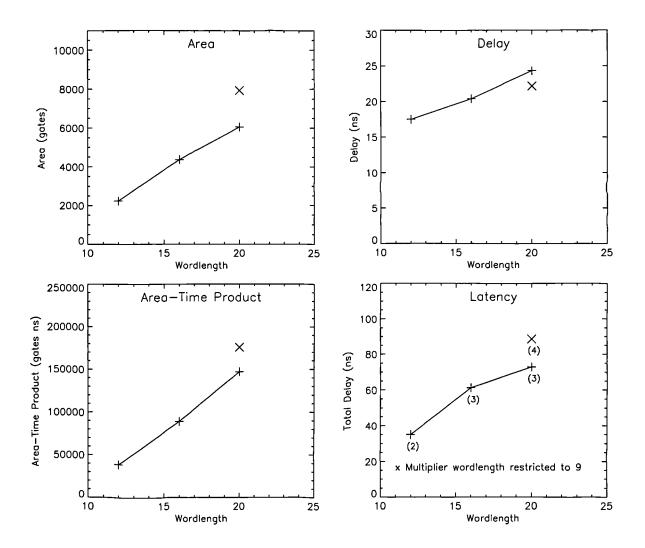

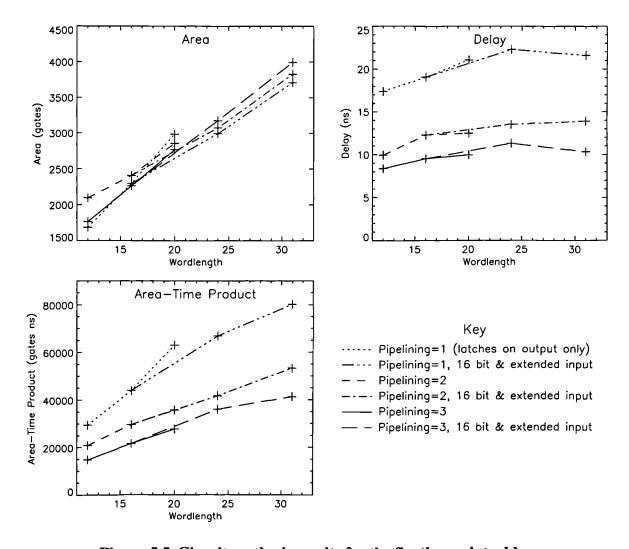

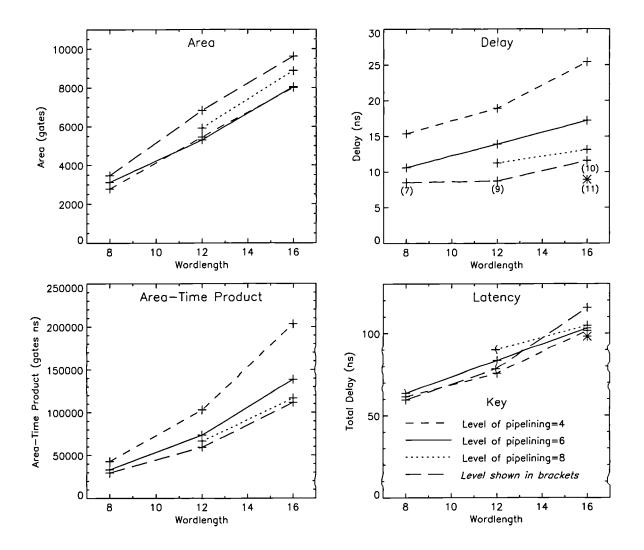

| 5.5  | Circuit synthesis results for the floating-point adder           |

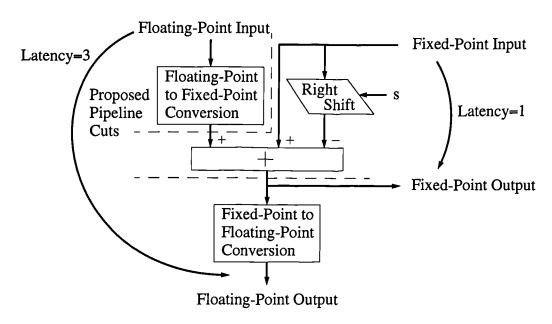

| 5.6  | Fixed/floating-point adder                                       |

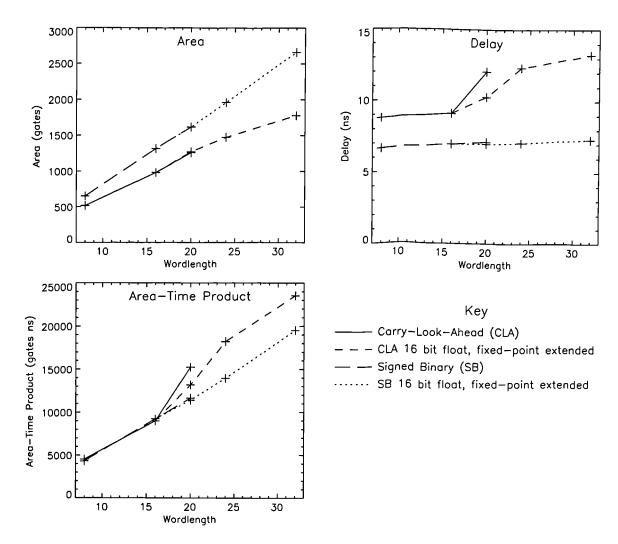

| 5.7  | Circuit synthesis results for fixed/floating-point adder         |

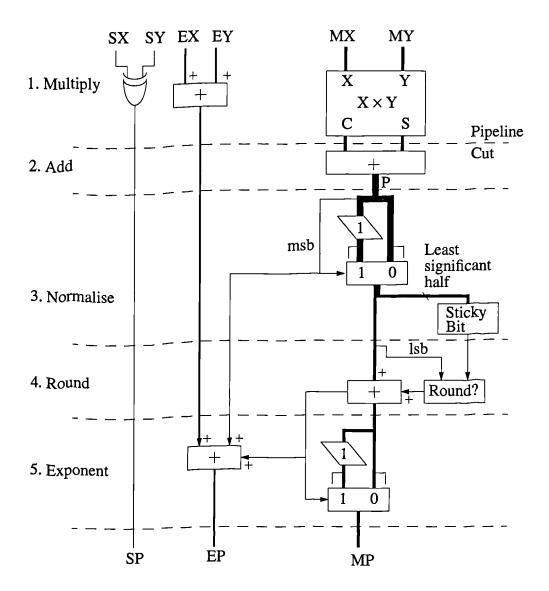

| 5.8  | Block diagram of the basic floating-point multiplier             |

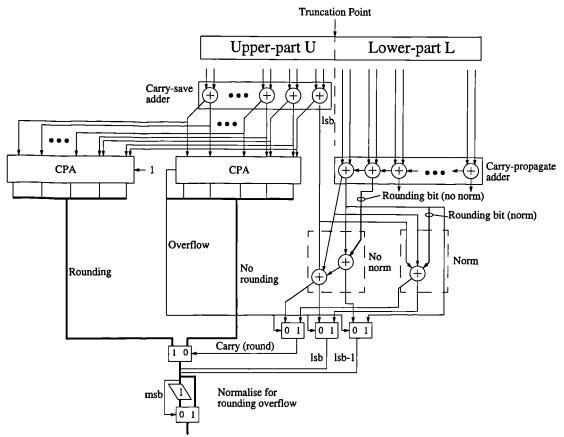

| 5.9  | Performing the addition, rounding and normalisation together     |

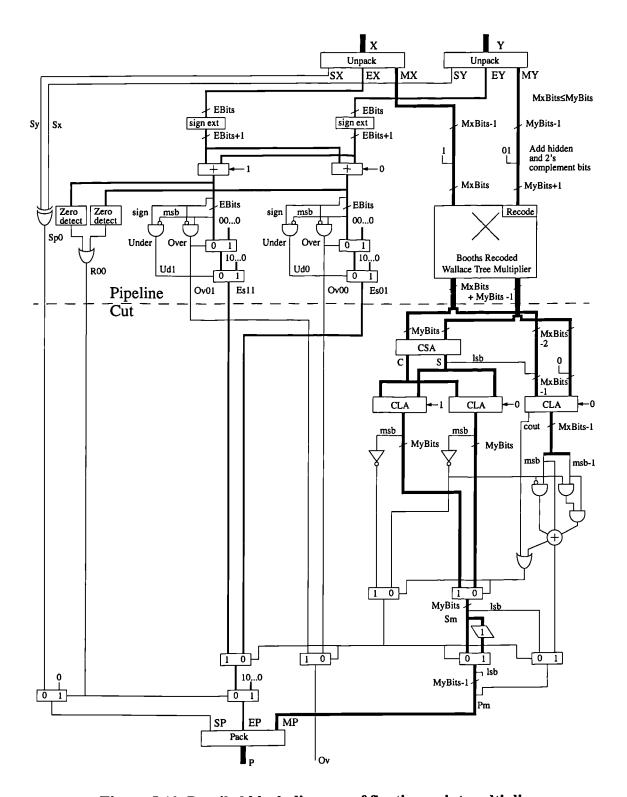

| 5.10 | Detailed block diagram of floating-point multiplier                          |

|------|------------------------------------------------------------------------------|

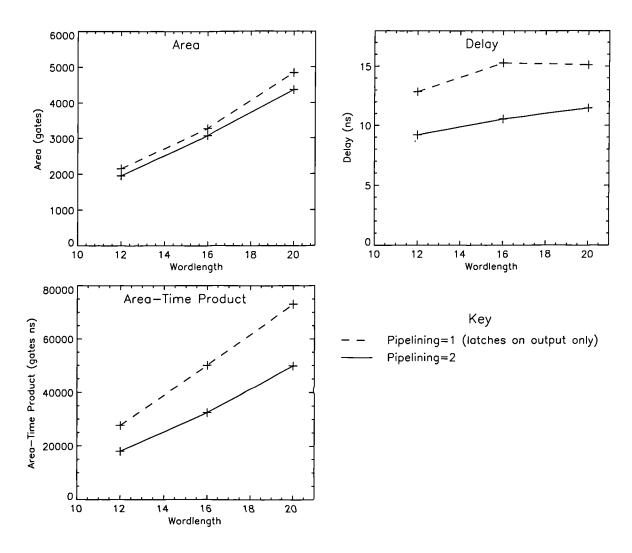

| 5.11 | Circuit synthesis results for the floating-point multiplier                  |

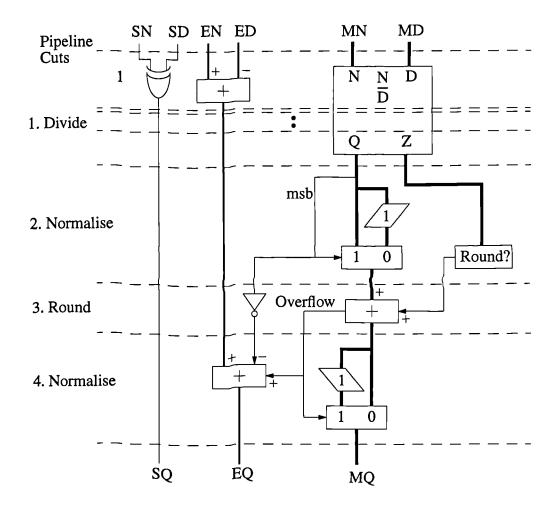

| 5.12 | Block diagram of a basic floating-point divider                              |

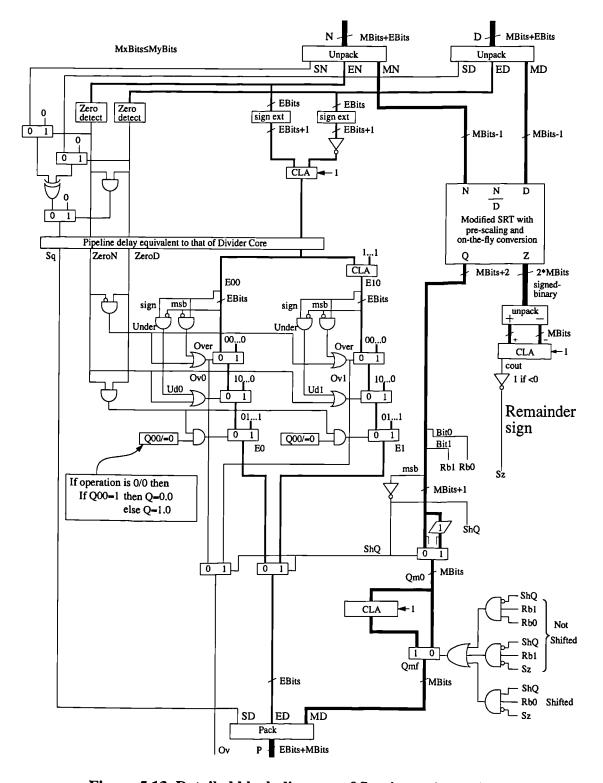

| 5.13 | Detailed block diagram of floating-point divider                             |

| 5.14 | Circuit synthesis results for the floating-point divider                     |

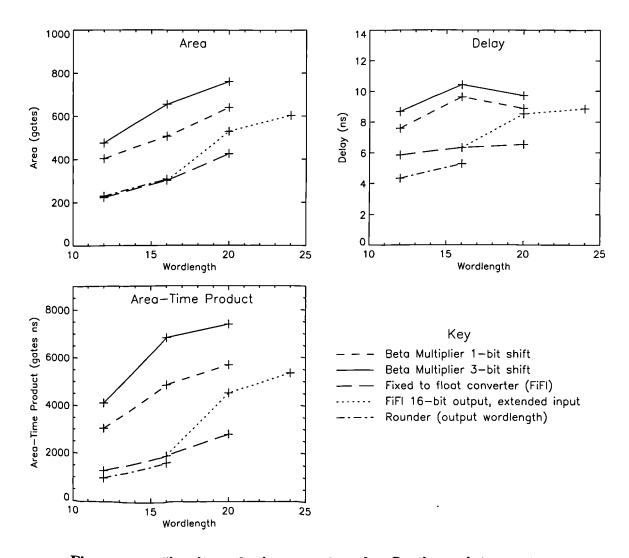

| 5.15 | Circuit synthesis results for other floating-point operators                 |

| 6.1  | Summary of square-root-free algorithm                                        |

| 6.2  | Summary of SGR algorithm                                                     |

| 6.3  | Summary of the DSF algorithm                                                 |

| 6.4  | Summary of the normalised Givens rotation algorithm                          |

| 6.5  | Summary of column normalised Givens rotation algorithm                       |

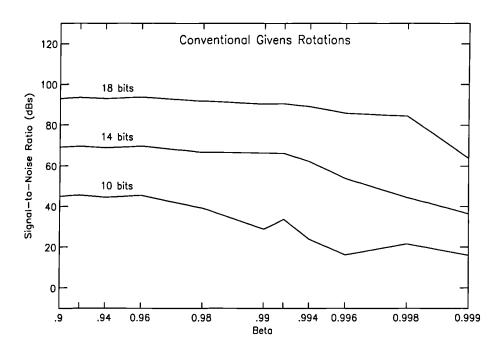

| 7.1  | Numerical performance of conventional algorithm                              |

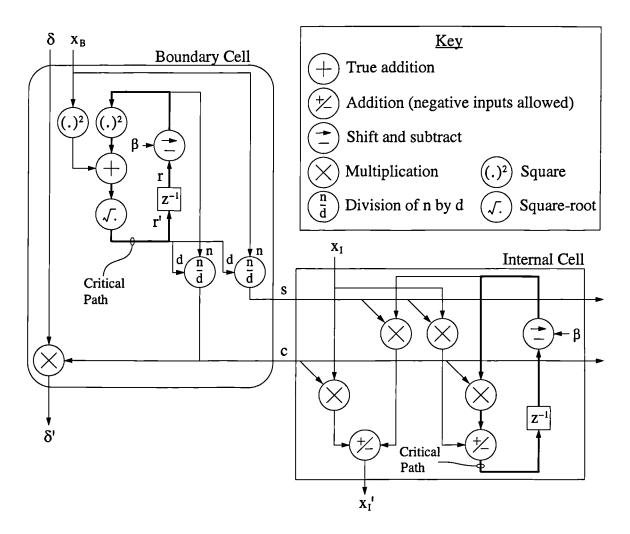

| 7.2  | SFG of boundary and internal cell for the conventional algorithm             |

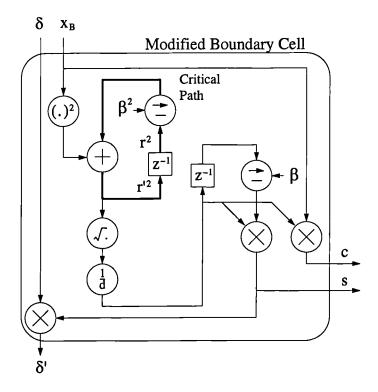

| 7.3  | Modified SFG for the conventional algorithm                                  |

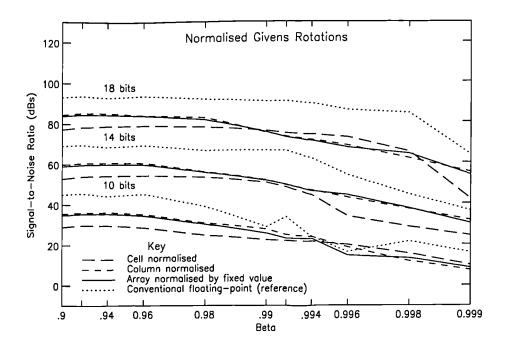

| 7.4  | Numerical performance of the normalised algorithms                           |

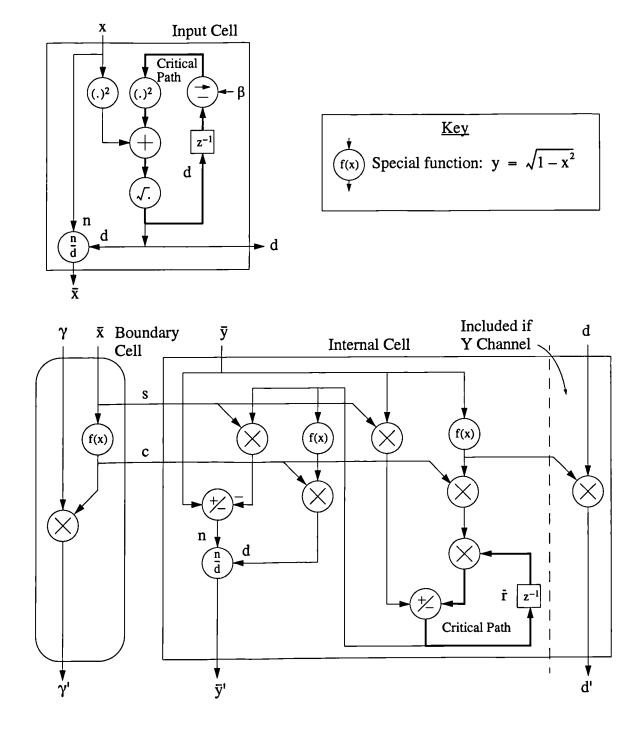

| 7.5  | SFG for the normalised algorithm                                             |

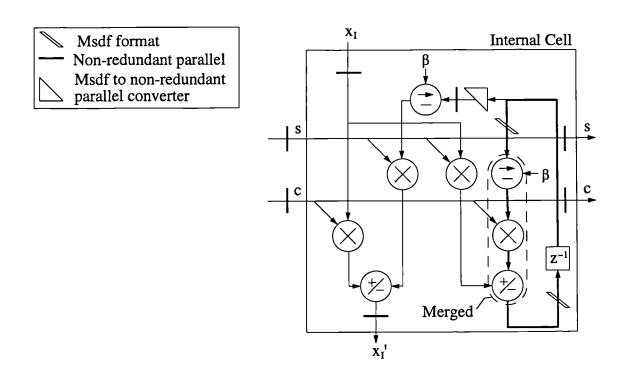

| 7.6  | Fixed-point Msdf implementation of the conventional algorithm 149            |

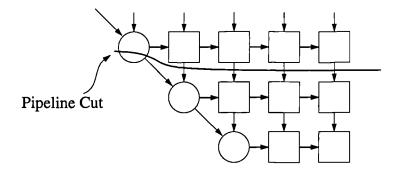

| 7.7  | Section of QR-array showing effect of pipeline cut through boundary cell 150 |

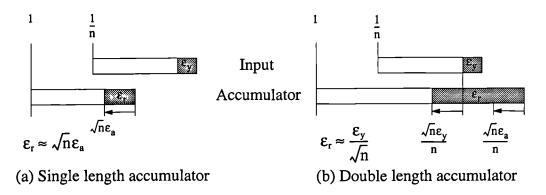

| 7.8  | Effect of accumulator length on errors                                       |

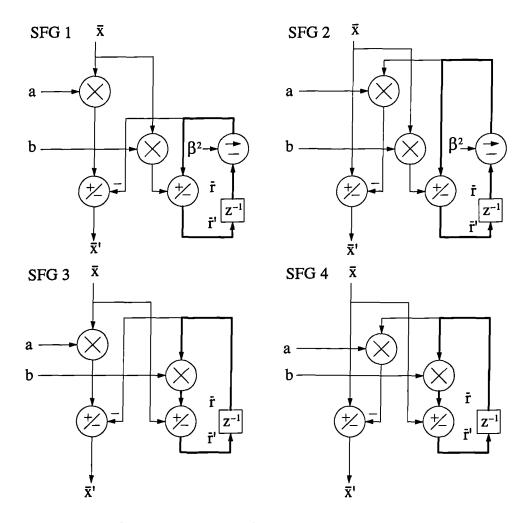

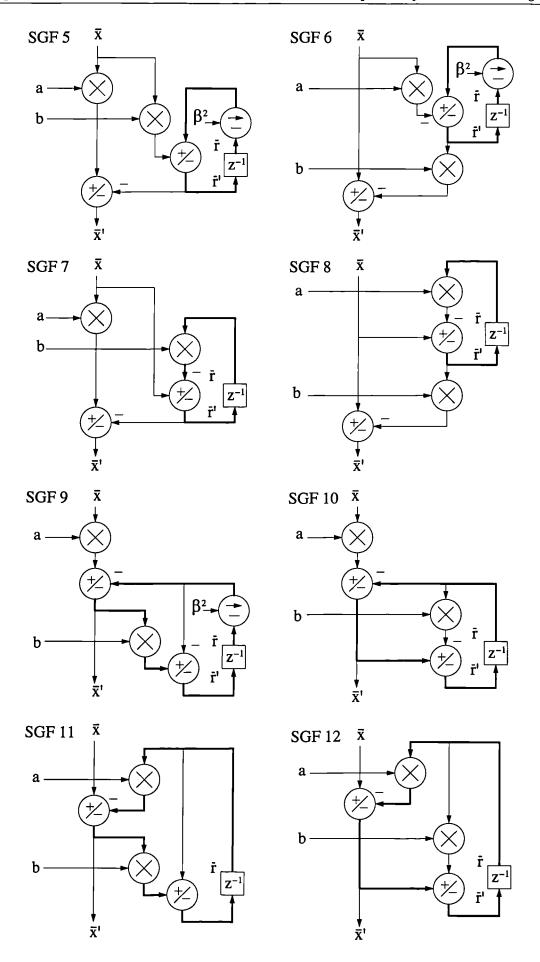

| 7.9  | SFGs of internal cells for two-multiply feed-forward algorithms              |

| 7.10 | SFG for two-multiply feedback algorithms                                     |

| 7.11 | SFG of SGR Algorithm                                                         |

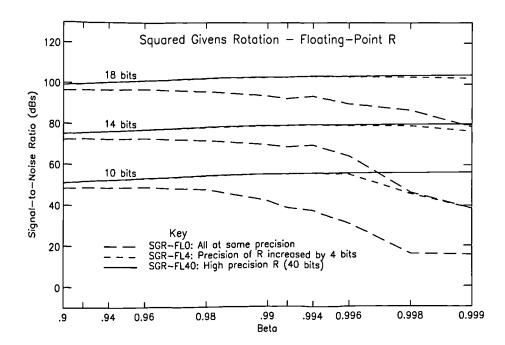

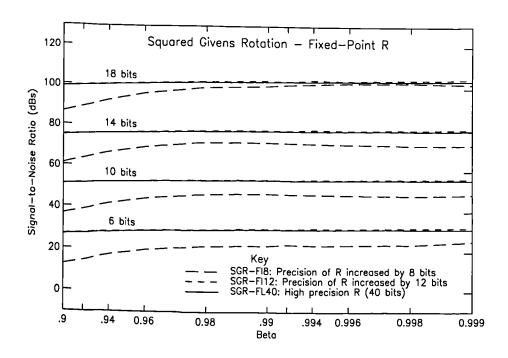

| 7.12 | Performance of SGR algorithm with floating-point loop variable 158           |

| 7.13 | Performance of SGR algorithm with fixed-point loop variable                  |

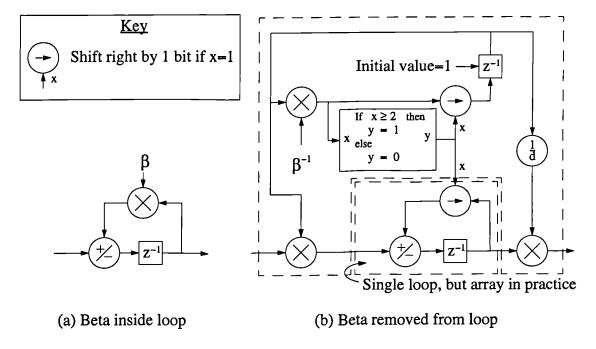

| 7.14 | Removing beta from the loop                                                  |

| 7.15 | SFG of DSF algorithm                                                         |

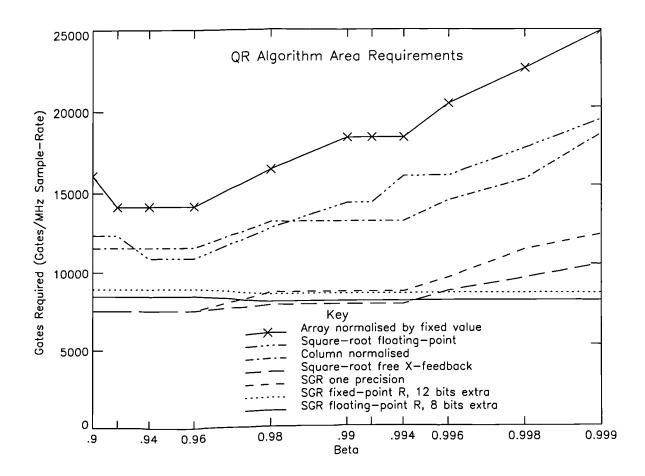

| 7.16 | Number of gates required to meet an SNR of -60dBs                            |

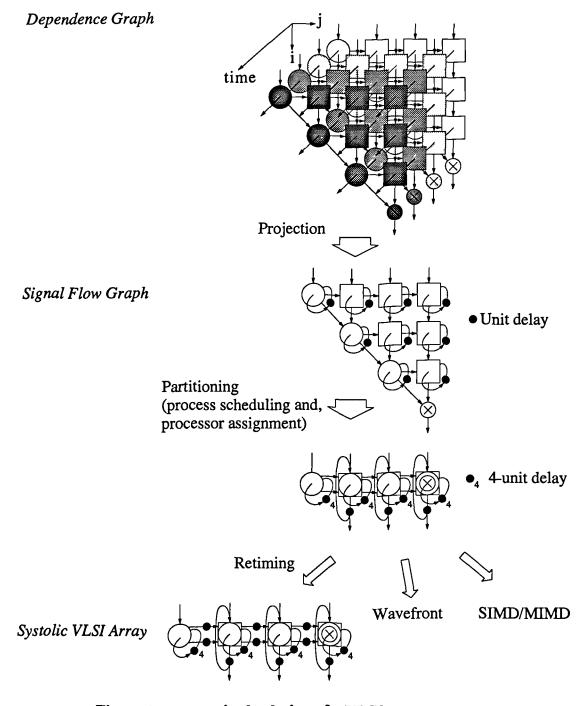

| 8.1  | Stages in the design of a VLSI array processor              |

|------|-------------------------------------------------------------|

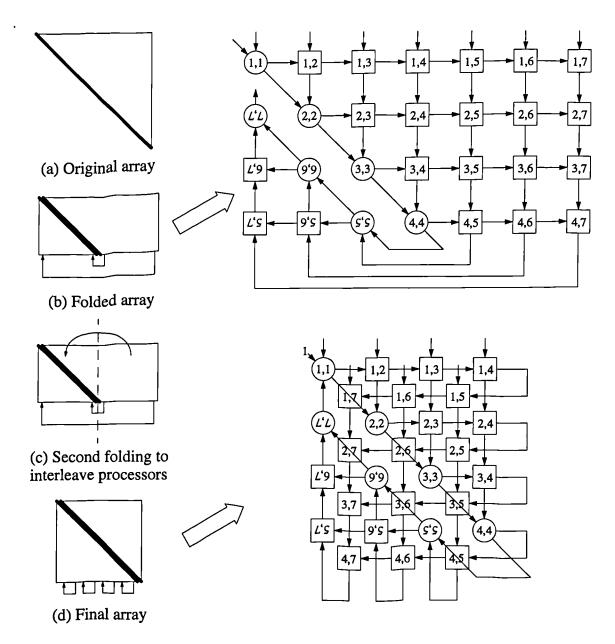

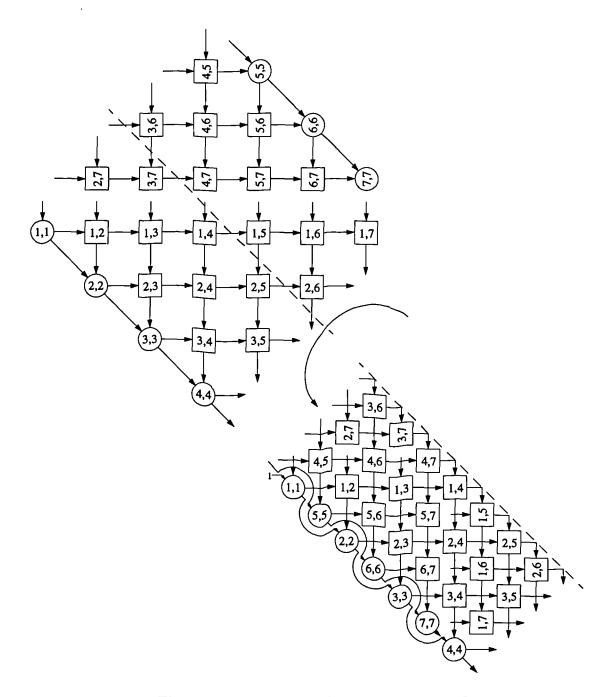

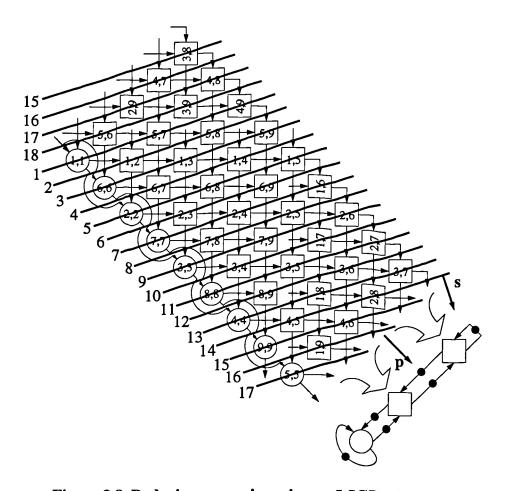

| 8.2  | Rader's folding of the QR-array                             |

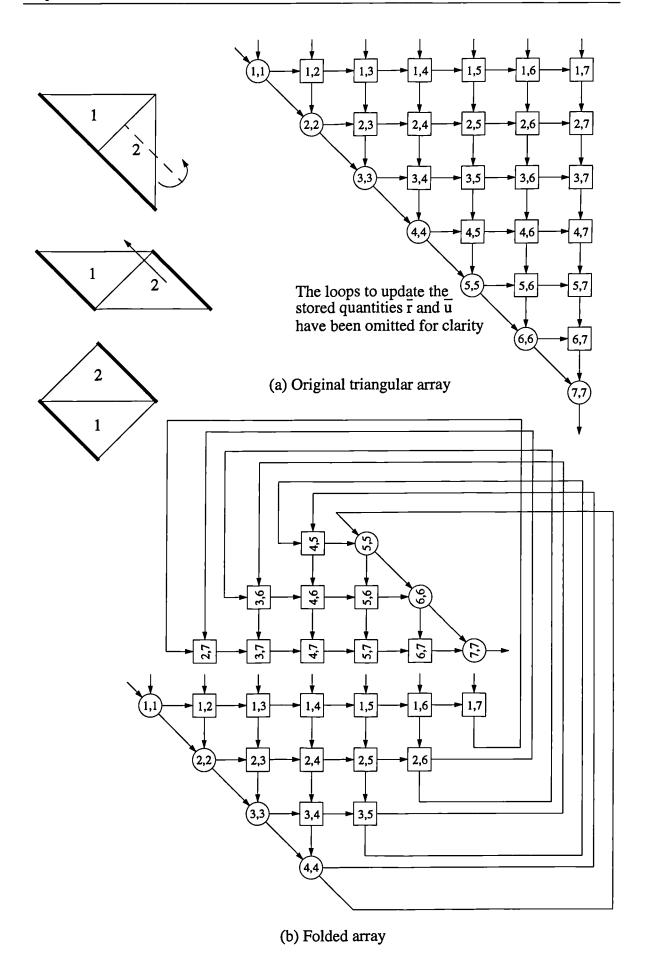

| 8.3  | An alternative folding of the QR-array                      |

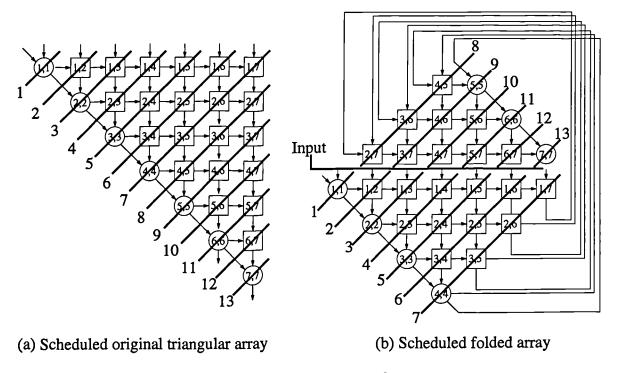

| 8.4  | Array with diagonal fold marked                             |

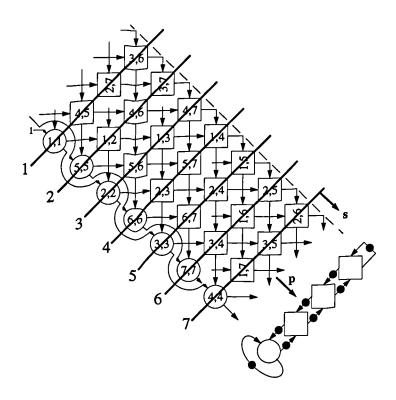

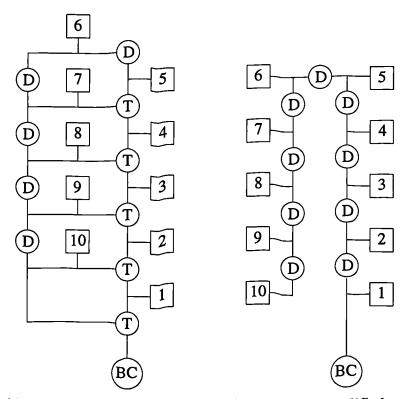

| 8.5  | LPGS projection of the folded QR-array                      |

| 8.6  | Scheduling of the QR-array                                  |

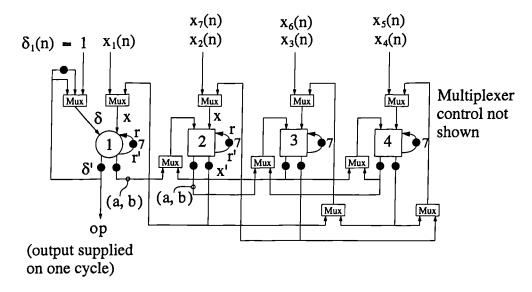

| 8.7  | Linear systolic array for the LPGS schedule                 |

| 8.8  | Reducing array size using an LSGP schedule                  |

| 8.9  | Retimed QR-array                                            |

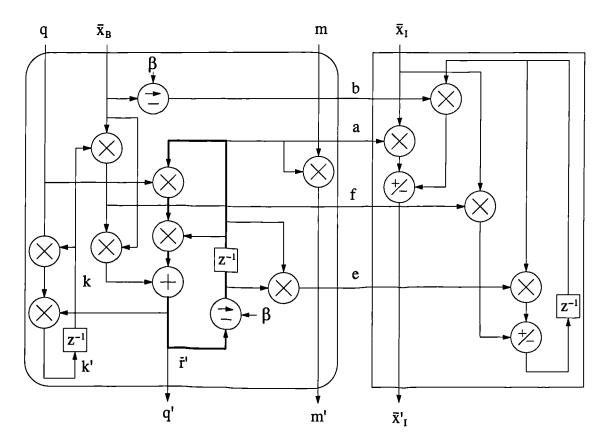

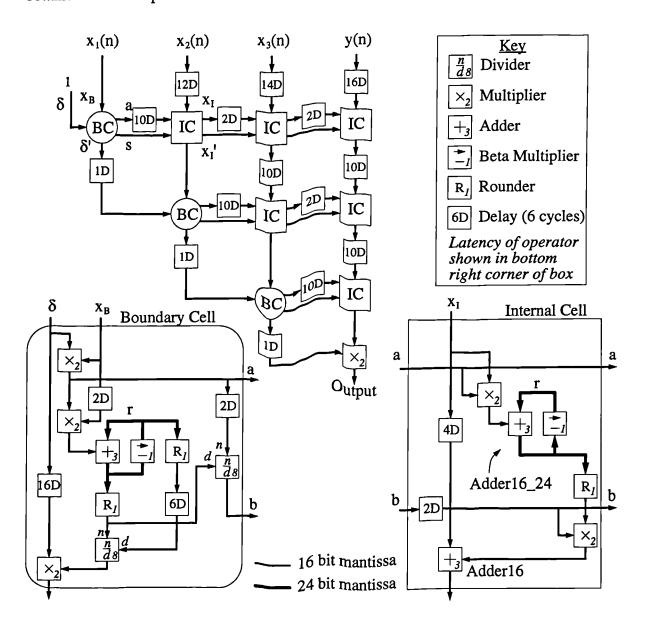

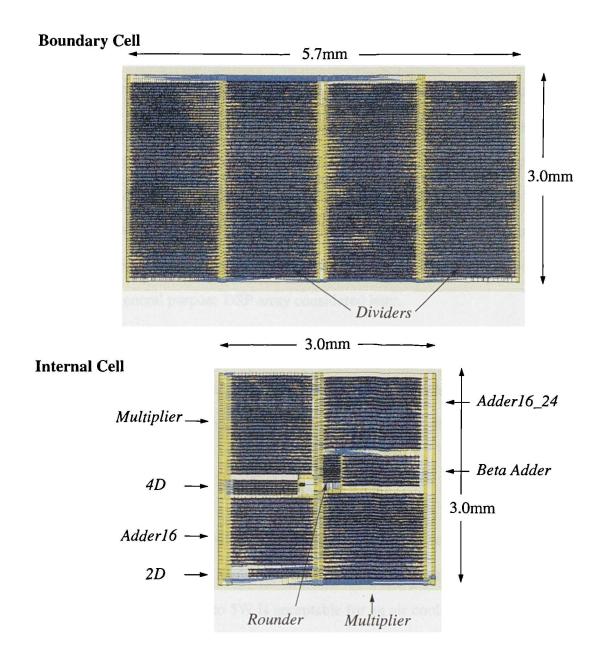

| 8.10 | VLSI layout of the enhanced SGR boundary and internal cells |

| 8.11 | Array processor of DSP chips                                |

| 8.12 | Estimated performance of an adaptive beamforming ASIC       |

| A.1  | Result digit selection regions                              |

| A.2  | Non-overlapping selection regions                           |

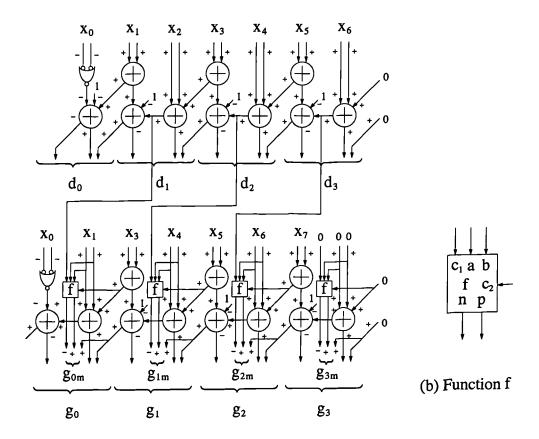

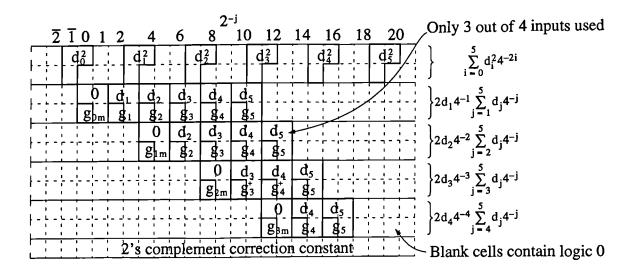

| B.1  | Block diagram of the redundant number squarer               |

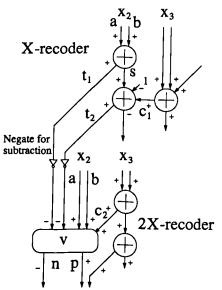

| B.2  | Derivation of function f and its truth-table                |

| B.3  | Modified recoders for correct partitioning of recoded input |

| B.4  | Partial-product array for a small squarer                   |

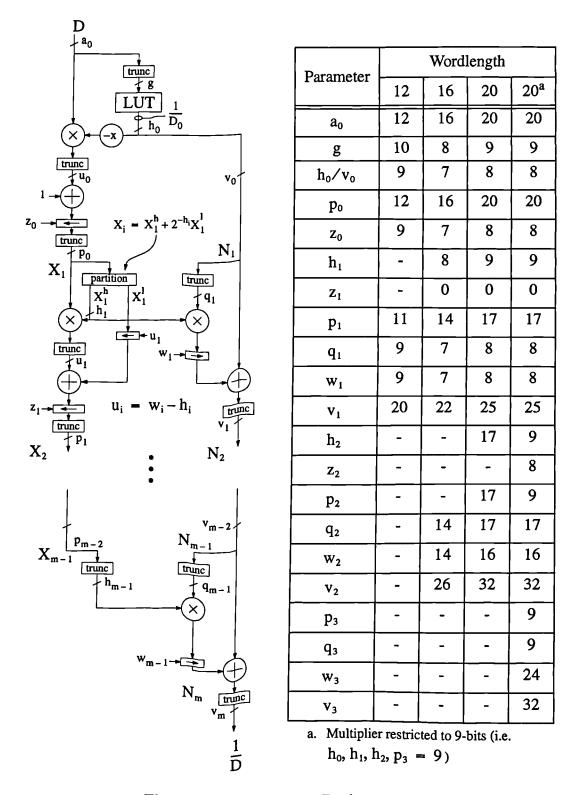

| C.1  | Convergence Reciprocal DG                                   |

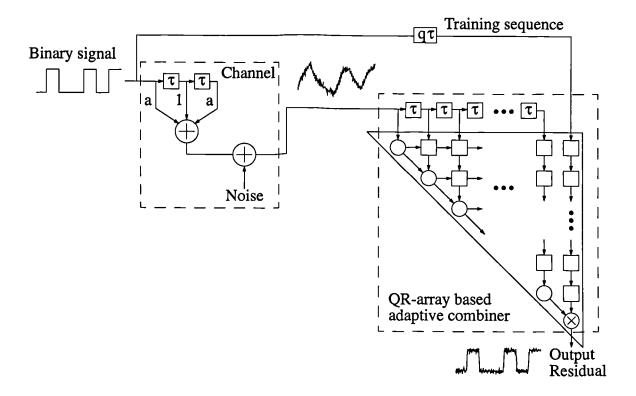

| E.1  | Block diagram of channel equaliser for algorithm evaluation |

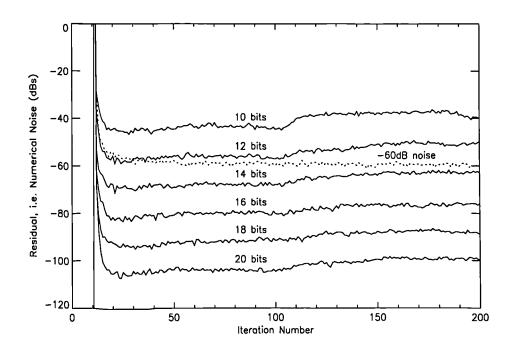

| E.2  | Channel equaliser output during adaption phase              |

# **List of Tables**

| 2.1 | Representations of the number                                 |

|-----|---------------------------------------------------------------|

| 2.2 | Encoding of signed bits                                       |

| 3.1 | Compression and saturation cell functions44                   |

| 3.2 | Minimally redundant radix-r digit-sets                        |

| 3.3 | Coding of partial-product for adder-tree                      |

| 4.1 | Selection function                                            |

| 4.2 | Circuit synthesis results for reciprocal circuit              |

| 5.1 | Obtaining a positive output from adder96                      |

| 5.2 | Divider rounding111                                           |

| 5.3 | Summary of the performance of 16-bit floating-point operators |

| 6.1 | Summary of Givens rotation algorithms                         |

| 6.2 | All two-multiply solutions obtained by feedback               |

| 7.1 | Permissible values of beta                                    |

| 7.2 | Numbers of cells required by QR-array                         |

| 7.3 | Operation count of algorithm variants                         |

| 7.4 | Operator area as a function of wordlength                     |

| 7.5 | Latency of operations in loop and QR-array sample-rate        |

| 8.1 | Properties of floating-point operators                        |

| 8.2 | Area and computation rate of the enhanced-SGR cells           |

| 8.3 | Comparison between SGR and CORDIC approaches                  |

| 8.4 | Comparison between programmable DSP and ASIC approaches       |

| A.1 | Truncation errors                                             |

| B.1 | Truth-table of digit squaring logic                           |

# Acknowledgements

I have been fortunate to receive guidance and supervision from a number of knowledgeable and generous people. In particular, I thank my supervisors Prof. John McWhirter and Prof. Graham Nudd for their encouragement and help. I also thank Dr. Richard Evans for his encouragement, the helpful discussions on arithmetic, his comments on this thesis, and enabling the supporting research to be performed. I am very grateful to Dr. Ian Proudler for his explanations and guidance on the adaptive filtering and numerical simulation aspects of this research.

The results and conclusions of this thesis have relied on circuit synthesis results produced by Integrated Silicon Systems Ltd. An enormous effort has been made by Dr. Yi Hu to code and synthesise these circuits which has been far and beyond the call of duty. I am very grateful for his efforts.

I would also like to thank Prof. John McCanny for allowing me to use the VLSI design tools in August 1995 at The Queen's University of Belfast to produce circuit layout.

My thanks goes to Dr. Robert Hamill for the CORDIC results, Dr. David Trainor for the use of the IRIS tools and help with the other VLSI design tools, and Simon Knowles for discussions on arithmetic and for the information on the power consumption of circuits. My thanks to Dr. Neil Burgess for his helpful comments on the thesis.

This work has been funded by the Ministry of Defence, through the Defence Evaluation and Research Agency, and I thank those who have enabled this to happen.

I thank Rev. Frank Holt for proof reading the thesis.

Lastly, I would like to thank my wife Valerie for being patient and supportive during this challenging period.

# **Declaration**

Unless otherwise stated, the work in this thesis is the author's own original research work.

Some of the work has been published previously:

R. L. Walke and R. A. Evans, "A Minimally Redundant Radix-4 Systolic Array for High Performance IIR Filtering", VLSI Signal Processing, VI, ISBN 0-7803-0996-0, pp. 168-178, 1993.

J. G. McWhirter, R. L. Walke and J. Kadlec, "Normalised Givens Rotations for Recursive Least Squares Processing", VLSI Signal Processing, VIII, ISBN 0-7803-2612-1, pp. 323-332, 1995.

# **Abbreviations**

lsb least significant bit

lsd least significant digit

msb most significant bit

msd most significant digit

msdf most significant digit first

ASIC Application specific integrated circuit

CAD Computer aided design

CLA Carry look ahead (adder)

CMOS Complementary metal oxide semiconductor

CORDIC CoOrdinate Rotation by DIgital Computer

CSA Carry save adder

DFE Decision feedback equaliser

DG Dependence graph

DSF Divide-and-square-root-free (Givens rotation algorithm)

DSP Digital signal processing

GP DSP General purpose digital signal processor

FFT Fast fourier transform

FIR Finite impulse response (filter)

FPU Floating-point unit

IEEE Institute of Electronic and Electrical Engineers

IIR Infinite impulse response (filter)

LPGS Locally parallel globally sequential

LSGP Locally sequential globally parallel

LUT Look-up table

MFLOPS Million floating-point operations per second

MinR4 Minimally redundant radix-4

MaxR4 Maximally redundant radix-4

RAM Random access memory

QR-Algorithm QR decomposition by Givens rotations

QR-Array Triangular array of processors for performing the QR-algorithm

SFG Signal flow graph

SGR Squared Givens rotation

SNDR Signed digit number representation

SNR Signal-to-noise ratio

SQF-XFB Square-root-free X-feedback (Givens rotation algorithm)

SRT Sweeney, Robertson and Tocher (divider algorithm)

VHDL VHSIC hardware description language

VLSI Very large scale integration

# **Chapter 1** Introduction

## 1.1 Background

The rapid evolution of integrated circuit technology into the realms of very large scale integration (VLSI) has enabled the realisation of the complex circuit structures necessary to process real-time signals in a digital manner. Processing a signal in this way offers considerable advantages over the real-world analogue representation, as it simplifies the storage of signals and allows functions to be performed on them that would otherwise be impractical. Consequently, the application of digital signal processing (DSP) has grown, and become an important enabling technology in many new applications of digital electronics. For example, the development of digital audio, multimedia and mobile communications have relied heavily on DSP.

There is now a wide variety of programmable general purpose digital signal processors commercially available with which to implement DSP. These offer a rapid and low cost development route, but currently only achieve computation rates of the order of 50 million floating-point operations per second (MFLOPS) as only one arithmetic unit is generally integrated. Also, for some simple functions they are inefficient, and use large amounts of silicon area and power as a consequence of the generality of their architecture and the overheads of programmability. In some instances, as little as 5% of the chip area may be occupied in useful operations on a signal.

More efficient use of the silicon resource can be achieved using an *application specific inte-grated circuit* (ASIC), as the processor architecture and arithmetic unit may be tailored to the specific requirements of the algorithm. In this way, significant reductions in area and power are possible, which enables either die sizes to be reduced, or higher levels of computation to be achieved by integrating more arithmetic units on a chip.

When adopting an ASIC approach, the optimum design is achieved in a process of developing the algorithm, the processor architecture and arithmetic in a way which accommodates Chapter 1 Introduction

the benefits and limitations of VLSI technology. Parallelism, regularity and local interconnect are features that are sought to achieve high levels of computation from circuits which are easy to realise.

Parallelism is perhaps the most important feature of any algorithm, as it allows results to be produced at a greater rate by using more than one arithmetic unit simultaneously to process a signal. With current technology it is possible to integrate large numbers of arithmetic units on a single chip and so achieve computation rates in excess of 10,000 MFLOPS. If the algorithm and architecture are both parallel and scalable, then it is possible to apply the increasing level of circuit integration to improve the rate at which signals can be processed (i.e. the *sample-rate*).

Recursive algorithms are very restrictive, as they have a sequential dependence between operations, as by their definition they use previous outputs to generate the next. In this case, the maximum sample-rate achievable is governed by the time it takes to perform the sequence of operations. In which case, improvements can only be made by either transforming the algorithm to reduce the number of operations, or implementing the operators in a way which reduces their delay, referred to as *latency*.

Most-significant-digit-first (msdf) arithmetic is a technique which has been used to minimise the latency of an operator, and has been applied in the design of a multiplier-adder for a high-sample-rate infinite impulse response (IIR) filter. However, this is a relatively simple application, and so the general applicability of this technique has not yet been fully established.

## 1.2 Objective of Research

The objective of this research has been to examine the VLSI implementation of an array processor for adaptive filtering. Currently, ASIC solutions employing parallel architectures are highly relevant due to the enormous levels of computation required by applications such as radar, sonar and communications. For example, radar applications can require computation levels of 50,000 MFLOPS. One adaptive algorithm which is of particular interest is recursive least squares, as this requires only low wordlength arithmetic when implemented

using *QR decomposition* by *Givens rotations*, and has a parallel architecture for high-throughput implementations. However, this algorithm, which henceforth shall be referred to as the *QR-algorithm*, is recursive and this can limit sample-rate at which an implementation may operate. In certain radar and communications applications the sample-rate can be very high (in excess of 100MHz). Therefore, a specific objective of this work has been to examine techniques to maximise the sample-rate of the QR-algorithm. Before considering the implementation issues any further, it is worth introducing the concepts of adaptive filtering, and presenting applications in which it could be applied.

## 1.3 Adaptive Filtering

A filter is a device for extracting information from a noisy signal, where the noise is considered to be any unwanted component of that signal. For example, the noise could be interference introduced into sensors or the circuits of a system, or be due to distortions or signal echoes resulting from imperfections in a transmission channel.

When it is not possible to determine the coefficients of a suitable filter because there is insufficient *a priori* knowledge of the signal and noise, or if the filter characteristics vary in an unknown way, it is necessary to use an adaptive filter. In this event an *adaptive algorithm* is used to update the filter parameters as new samples of the signal become available.

#### 1.3.1 Adaptive Linear Combiner

At the heart of most adaptive filters is the adaptive linear combiner shown in Figure 1.1.

Figure 1.1 Adaptive linear combiner

The combiner has (p-1) auxiliary inputs and a single primary input, which are given in a discrete time form at time  $t_n$  by x(n) and y(n) respectively. (Note that bold lower-case lettering has been used to denote a vector quantity, and bold upper-case will be used to denote a matrix quantity). The combiner forms a sum of the auxiliary inputs weighted by parameters  $w_1$  to  $w_p$ , which is added to the primary input to form an error signal e(n). These parameters, which are referred to as weights, are controlled by an adaptive algorithm to minimise a measure of the error signal, such as its mean squared value. The error is also, on occasions, referred to as the residual, and is given by

$$e(n) = x^{T}(n)w + y(n)$$

(1.1)

where  $\mathbf{w}$  denotes the optimum weights in vector form, and  $\mathbf{x}^T$  is the transpose of auxiliary input data vector.

#### 1.3.2 Applications of Adaptive Filtering

Two important applications of adaptive filtering are *channel equalisation* and *adaptive beamforming*. The channel equaliser is used in Chapter 7 to evaluate the numerical properties of algorithms for performing Givens rotations, whereas adaptive beamforming is considered to be the primary application for the work of this thesis.

#### 1.3.2.1 Channel Equalisation

If the bandwidth of a transmission channel is restricted, then dispersion of the conveyed signal will occur resulting in intersymbol interference. If severe, this will cause the signal to be incorrectly detected at the receiver. The channel equaliser, shown in Figure 1.2, aims to undo the distortion of an imperfect channel by implementing its inverse (as described in [Hayk91], p. 492). This is done using an adaptive transversal filter, which is constructed from an adaptive linear combiner fed by a tapped delay line. A predetermined sequence of data is generated at the transmitter and receiver to provide the adaptive filter with an uncorrupted version of the transmitted signal from which to adapt its weights.

An adaptive equaliser is useful when the channel characteristics are unknown, or vary with time.

Figure 1.2 Channel equalisation using an adaptive filter

#### 1.3.2.2 Adaptive Beamforming

In the adaptive beamforming application, the adaptive linear combiner is used to provide spatial filtering to reduce the effects of interference impinging upon an antenna array from a direction other than the direction of interest (i.e. the *look direction*). Figure 1.3 depicts an adaptive sidelobe canceller.

Figure 1.3 Diagram of an adaptive sidelobe canceller

Chapter 1 Introduction

The primary signal constitutes the input from a main antenna which has high directivity, but, due to theoretical and practical design constraints, has a small but significant gain in other directions (i.e. it has sidelobes). If there is a strong unwanted signal incident on the array in the direction of a sidelobe, e.g. due to jamming, it is possible that enough interference will be received to swamp a signal of interest in the look direction. To overcome this, a number of omnidirectional auxiliary antennae are used to sample the interference. The adaptive combiner is then used to remove any signal common with the main antenna. At this stage in the processing, it is assumed that the signal of interest is hidden by noise, so only interference is suppressed. The effect of the combiner on the beam pattern of the main antenna is to introduce deep nulls in the direction of the interference as shown in Figure 1.3.

### 1.4 The QR-Algorithm

The adaptive linear combiner residual can be minimised in a least mean squares sense using the *QR-algorithm*. This algorithm is of interest to an ASIC implementation as it has good numerical properties. In particular Ward *et al.*[Ward86a] have shown its use can reduce the wordlength requirement over a matrix inversion approach from 24-bits to 16-bits in their particular adaptive beamforming example.

The residuals up to time n can be expressed collectively in matrix form as

$$\begin{bmatrix} e(1) \\ e(2) \\ \vdots \\ e(n) \end{bmatrix} = \begin{bmatrix} \mathbf{x}^{T}(1) \\ \mathbf{x}^{T}(2) \\ \vdots \\ \mathbf{x}^{T}(n) \end{bmatrix} \mathbf{w}(n) + \begin{bmatrix} y(1) \\ y(2) \\ \vdots \\ y(n) \end{bmatrix}$$

(1.2)

A more compact representation is

$$\mathbf{e}(\mathbf{n}) = \mathbf{X}(\mathbf{n})\mathbf{w}(\mathbf{n}) + \mathbf{y}(\mathbf{n}) \tag{1.3}$$

where the square error is simply  $E(n) = |e(1)|^2 + |e(2)|^2 + ... + |e(n)|^2 = ||e(n)||^2$ .

A very numerically stable method of solving equation (1.3) is to use orthogonal triangularisation by QR-decomposition to obtain

$$\mathbf{R}(\mathbf{n})\mathbf{w}(\mathbf{n}) + \mathbf{u}(\mathbf{n}) = \mathbf{0} \tag{1.4}$$

where  $\mathbf{R}(n)$  is upper-triangular matrix obtained by applying a unitary matrix  $\mathbf{Q}(n)$  to the input data  $\mathbf{X}(n)$  i.e.

$$\mathbf{Q}(\mathbf{n})\mathbf{X}(\mathbf{n}) = \begin{bmatrix} \mathbf{R}(\mathbf{n}) \\ \mathbf{0} \end{bmatrix} \quad \text{and} \quad \mathbf{Q}(\mathbf{n})\mathbf{y}(\mathbf{n}) = \begin{bmatrix} \mathbf{u}(\mathbf{n}) \\ \mathbf{v}(\mathbf{n}) \end{bmatrix}$$

(1.5)

The matrix  $\mathbf{Q}(n)$  can be applied recursively using a simpler matrix  $\hat{\mathbf{Q}}(n)$  such that

$$\hat{\mathbf{Q}}(n)\mathbf{Q}(n-1) = \mathbf{Q}(n) \qquad \hat{\mathbf{Q}}(n) \begin{bmatrix} \mathbf{R}(n-1) \\ \mathbf{x}^{\mathsf{T}}(n) \end{bmatrix} = \begin{bmatrix} \mathbf{R}(n) \\ \mathbf{0} \end{bmatrix} \qquad \hat{\mathbf{Q}}(n) \begin{bmatrix} \mathbf{u}(n-1) \\ \mathbf{y}(n) \end{bmatrix} = \begin{bmatrix} \mathbf{u}(n) \\ \alpha(n) \end{bmatrix} \quad (1.6)$$

where  $\hat{\mathbf{Q}}(n)$  is also a unitary matrix which is chosen to set the elements of  $\mathbf{x}^T(n)$  to zero in the middle equation. The term  $\alpha(n)$  is used to obtain the residual and is discussed later. The transformation  $\hat{\mathbf{Q}}(n)$  can be constructed from a sequence of 2-dimensional rotations, known as Givens rotations, which progressively set, from left to right, each element of  $\mathbf{x}^T(n)$  to zero. To avoid undoing the effect of previous rotations, the Givens rotation is performed between the elements of  $\mathbf{x}^T(n)$  and the row of  $\mathbf{R}(n-1)$  which has the same number of leading zeros. For example, to zero the  $\mathbf{i}^{th}$  element in  $\mathbf{x}^T(n)$ , we use the  $\mathbf{i}^{th}$  row of  $\mathbf{R}(n-1)$  and the rotation

$$\begin{bmatrix} c & s \\ -s & c \end{bmatrix} \begin{bmatrix} 0 & \dots & 0 & r_{i,i} & r_{i,i+1} & \dots & r_{i,k} \\ 0 & \dots & 0 & x_i & x_{i+1} & \dots & x_k \end{bmatrix} = \begin{bmatrix} 0 & \dots & 0 & r'_{i,i} & r'_{i,i+1} & \dots & r'_{i,k} \\ 0 & \dots & 0 & 0 & x'_{i+1} & \dots & x'_k \end{bmatrix}$$

(1.7)

The 2-by-2 rotation matrix consists of the sine and cosine of the rotation angle obtained from the leading terms  $x_i$  and  $r_{i,i}$  using

$$c = \frac{r_{i,i}}{\sqrt{x_i^2 + r_{i,i}^2}} \qquad s = \frac{x_i}{\sqrt{x_i^2 + r_{i,i}^2}}$$

(1.8)

A complete derivation of the QR-algorithm can be found in Shepherd[Shep93].

# 1.5 The QR-Array

One benefit of performing QR-decomposition by Givens rotations is that it can be implemented using a highly parallel array processor, known as the *QR-array*, and shown in Figure 1.4. The array was originally proposed by Gentleman and Kung[Gent81], but contains important modifications made by McWhirter[McWh83] to generate the residual directly from the array. It presents a good starting point for the design of a parallel implementation of the adaptive linear combiner, as considered in Chapter 8.

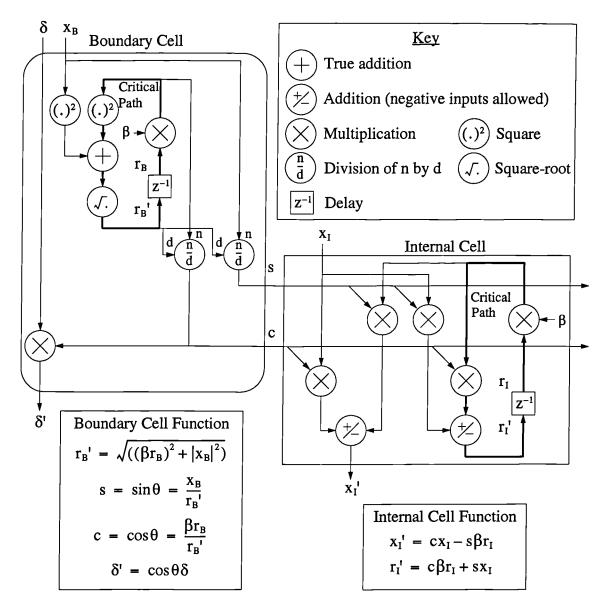

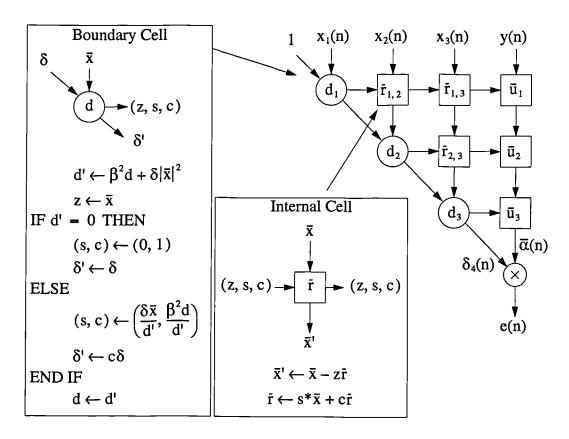

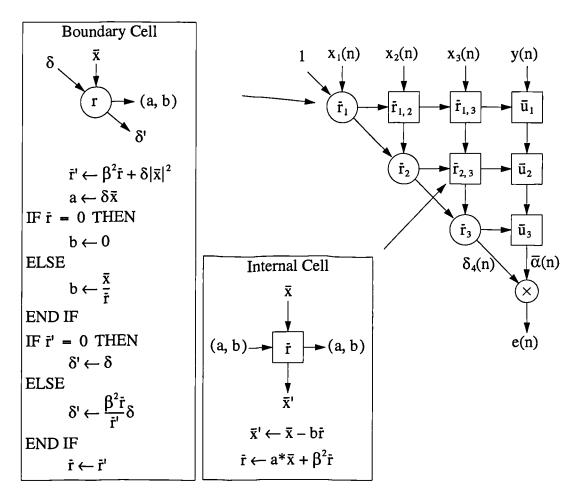

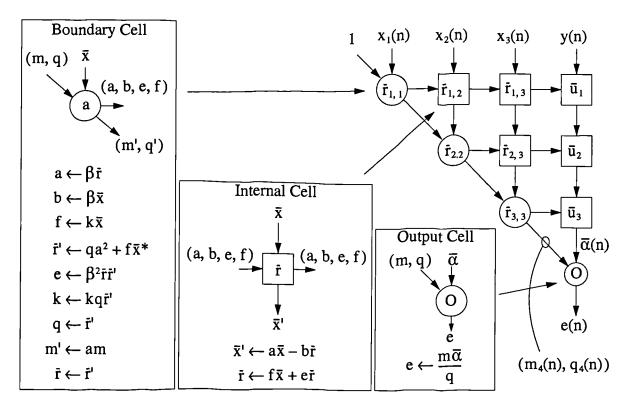

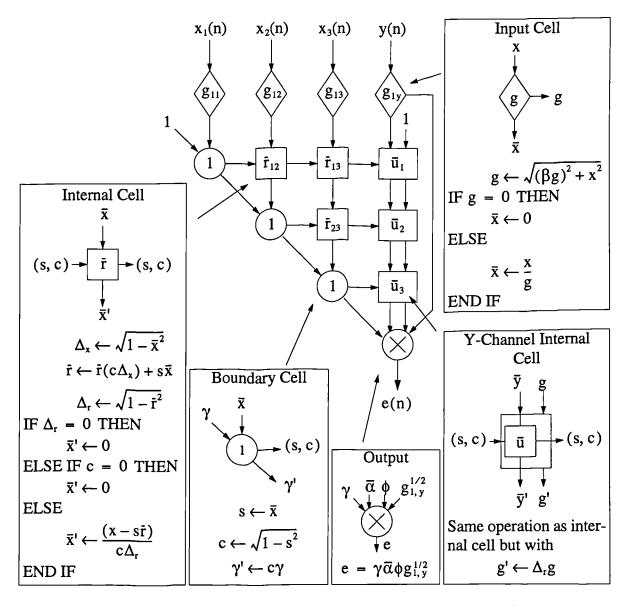

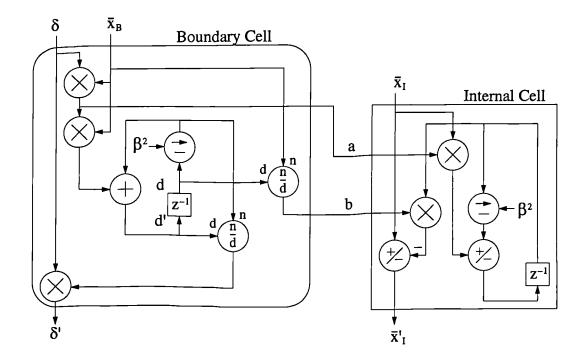

Figure 1.4 The QR-array architecture for performing the QR-algorithm

The array is composed from *boundary cells* and *internal cells* which perform the Givens rotation as indicated in the corresponding insets. The term  $\beta$  is generally referred to as the *forget-factor*, and is simply a constant, which is close to, but less than 1 (e.g.  $\beta = 0.996$  would be a typical value in adaptive beamforming).

Chapter 1 Introduction

The elements of  $\mathbf{R}(n)$  and  $\mathbf{u}(n)$  are stored within the cells of the array, and are initialised to zero. Each combiner input  $\mathbf{x}(n)$  enters the top of the array, and propagates down from row to row. On each row of the array the leading non-zero element of the vector is set to zero by the rotation performed in the boundary cell on its input and the stored element r. The same angle of rotation is applied to the remainder of the vector by the internal cells within the same row. The rotation in each cell is performed on a vector, formed from the cell input x and the stored variable, r or u. As a consequence of the rotation process, the stored variable is updated to r' and u' respectively. The term  $\beta$  provides a forget-factor, such that the stored variables decay over time.

The weights of the adaptive linear combiner can be obtained by extracting  $\mathbf{R}(n)$  and  $\mathbf{u}(n)$  from the array and solving equation (1.4) by back-substitution. However, in some applications, such as adaptive beamforming, it is the residual which is of primary interest. Direct residual extraction has been incorporated into the QR-array by McWhirter[McWh83] by noting that the residual can be obtained by multiplying the output of the right-hand column, denoted  $\alpha(n)$  in Figure 1.4, by the product of the rotation cosines, formed down the diagonal of the array (and denoted  $\gamma(n)$  in Figure 1.4).

## 1.6 Performing Rotations in VLSI

There are two principal approaches to performing the rotations required by the QR-array. CORDIC[Vold59][Walt71] (COordinate Rotation by Digital Computer) has been a popular approach as it implements the rotations directly using a single arithmetic component. Whether CORDIC can offer high sample-rate implementations was a question proposed earlier in this work, and has subsequently has been addressed by Hamill in [Hami95a].

In this thesis, the alternative approach based on the standard arithmetic operators, add, multiply, divide and square-root has been addressed. Figure 1.5 shows a *signal flow graph* (SFG) of the QR-array cells implemented using standard arithmetic operators. The conventional Givens rotation algorithm has been used, and the equations defining the operation of the cells

are shown in the figure.

Figure 1.5 Signal flow graph of conventional rotation algorithm

Several observations can be made about the algorithm:

- division and square-root operations are required and these are conventionally highlatency operations,

- loops exist in the boundary and internal cells to update the quantities  $r_B$  and  $r_I$ , and the latency of these will limit the sample-rate at which the QR-array may operate.

Increased sample-rate can be achieved by moving the square-root operation out of the loop

Chapter 1 Introduction

in the boundary cell by maintaining  $r_B$  in a squared form. However, there are other transformations which can be performed to the conventional algorithm which will completely remove the need for a square-root operation and also reduce the number of multipliers. As a consequence, there is a wide variety of algorithm possibilities for implementing the QR-array. To determine the best choice for a particular application, it is essential to consider the requirements of each algorithm for wordlength and fixed- and floating-point arithmetic as well the number of operations, their type and topology.

Fixed-point implementations of a DSP algorithm are often sought, as this simplifies the design of the arithmetic operators. For many conventional DSP operations, such as FFT and FIR filtering, this can be achieved with ease, and the solutions are generally fast and efficient. However, the QR-algorithm contains a greater range of arithmetic operations, and has many variants, and it is not obvious what fixed-point solutions are possible, and whether they would offer lower area, higher sample-rate or greater throughput. Therefore, both fixed- and floating-point solutions need to be considered.

Another important aspect of the arithmetic, irrespective of whether fixed- or floating-point arithmetic is used, is the type of rounding used. It is apparent from the SFG of the rotation algorithm that r and u are accumulated quantities. When a number is accumulated, so are the errors. If the errors are unbiased, i.e. their mean is zero, the error grows as  $\sqrt{n}$ , where n is the number of additions performed (as a consequence of the central limit theorem). If there is a bias, then the error will grow with n. Arithmetic errors are introduced in finite-precision arithmetic in the process of returning the wordlength of the result of an arithmetic operation to that of its input[Wilk63]. Unbiased arithmetic errors can be achieved by rounding the result to the nearest valid number. As will be shown later, this form of rounding takes more time than a simpler scheme, but is worth adopting because the accumulated numerical errors are significantly lower.

#### 1.7 VLSI Design Methodology

The task of implementing VLSI circuits has been greatly simplified over recent years. It is now possible to use CAD tools to synthesise circuits from VHDL (Very high speed integrated circuit Hardware Description Language) into optimised circuits composed of standard cells (such as gates and adders). Tools also exist which will generate circuit layout by automatic placement-and-routing of the standard cell circuit.

This automated design route provides a very rapid path into silicon. For the relatively low wordlengths required by the QR-algorithm applications considered in this thesis (i.e. less than 20-bits), it is possible to synthesise the operators as one complete entity with very good speed and area results. For wordlengths greater than this, the synthesis times become large, the results are not so good, and it is necessary to break down the operators into smaller parts.

Within the thesis, the synthesis tool Synopsys has been used to generate estimates of the circuit delay and number of gates required by arithmetic operators. VHDL descriptions have been produced, which have been parameterised in terms of wordlength and level of pipelining, and so specific circuits can be realised relatively easily (although synthesis times can be long). A 0.35µm standard cell CMOS process has been used as the target technology, and represents the minimum commercially available circuit geometry available at the time of writing. Some arithmetic operators have also been taken through to layout using automatic place-and-route tools, and this has provided a useful guide of how the number of gates translates into circuit area.

The synthesis tool Synopsys is able to identify full-adder components within a circuit description and employ an optimised standard cell for its realisation (if supplied within the standard cell library). This can lead to significant performance improvements over a realisation from basic gates. Hence, there is a strong motivation to use full-adder descriptions of circuits where possible. Within the thesis, full-adders are used almost exclusively to realise arithmetic circuits.

#### 1.8 Overview of Thesis

The QR-algorithm has been the subject of a number of implementation studies and designs, most notably by Rader[Rade96] and McWhirter *et al.*[Ward86b] for applications such as adaptive beamforming in radar systems. None of these, however, has directly addressed the issue of achieving high-sample-rate operation.

The thesis is in two parts. The first part (Chapters 3 to 5) considers the design of arithmetic operators with low-latency and high-throughput. Although this research was motivated by the needs of the QR-algorithm, the results are more generally applicable. The second part (Chapters 6 to 8) specifically addresses the issues of determining the algorithm, architecture and arithmetic implementation of a VLSI implementation of the QR-algorithm. A detailed overview by chapter now follows.

In Chapter 2 the important concept of redundant arithmetic is introduced, as this provides a means of avoiding carry-propagation, which enables the latency of an arithmetic operation to be reduced. On-line and msdf arithmetic techniques are presented as ways in which redundant arithmetic has been exploited to reduce the latency of operators. The extension of the msdf operators to floating-point arithmetic is discussed, as this is of some importance to modern DSP algorithms.

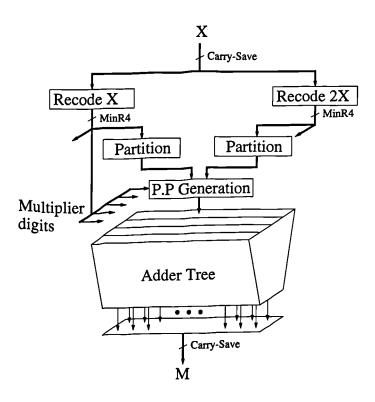

In Chapter 3 two schemes for achieving low-latency, high-throughput multiplication are investigated. Firstly, msdf approaches are analysed for a range of digit-sets, and a new architecture based on the minimally-redundant, radix-4 digit-set is presented as offering the best compromise between latency, area and redundancy. Circuit delay and gate numbers are presented here and later in the thesis to support the research. Secondly, low-latency multipliers based on trees of adders are presented as an alternative which does not require the data skewing of an msdf format. A multiplier with a single redundant input is developed as a replacement to the msdf multipliers considered, which offers single-cycle latency with an area less than a conventional tree-multiplier. For multipliers with two redundant inputs, a new archi-

Chapter 1 Introduction

tecture is presented, which uses a minimally redundant radix-n recoding on both multiplier and multiplicand inputs, to reduce the cost of the redundant representation by up to 25%. The application of this technique to a squarer is also addressed, as a dedicated squarer circuit offers significantly reduced area over a multiplier used for the purpose.

Division is a requirement of all but one of the Givens rotation variants examined, and is important in achieving an efficient processor implementation. In chapter 4 the various approaches to achieving low-latency, high-throughput division are examined. Two new architectures are presented, one a modification of a speculative SRT (Sweeney, Robertson and Tocher) divider, made to obtain an acceptable gate count, and the other a high-throughput implementation of the convergence approach.

Floating-point operators are required by the Givens rotation algorithms considered later in the thesis; a range of these has been developed and is presented in Chapter 5.

In Chapter 6 an overview of the Givens rotation variants is presented, and a generalised set of equations is given from which a number of relevant algorithms are derived. Also, normalisation of the Givens rotation is described, as a means of allowing implementation using fixed-point arithmetic.

The suitability of a range of Givens rotation variants for VLSI implementation is examined in Chapter 7. Their numerical performance and subsequent wordlength requirements have been investigated, together with the type, order and number of arithmetic operations used. An enhanced version of the *Squared Givens Rotation* (SGR) algorithm is developed, which obtains extremely high sample-rate with good numerical performance and low circuit area. A detailed comparison with other Givens rotation variants shows that it offers the highest sample-rate and lowest area of the algorithms investigated.

Developing an architecture for the QR-algorithm which can be mapped onto an integrated circuit is addressed in Chapter 8. A number of array architectures are presented that would

enable a range of problem sizes and sample-rates to be implemented. The circuit layout, for one of these architectures, is presented using the enhanced-SGR algorithm, and the area and speed has been derived and compared with a solution based on CORDIC and an array of programmable DSP chips.

The research has produced a range of results in the areas of arithmetic, algorithm and architecture from which conclusions have been drawn. These are presented in Chapter 9 and followed by a summary of topics on which further research could be productive.

# **Chapter 2** Redundant Arithmetic

#### 2.1 Introduction

The representation of a number plays a vital role in achieving low-latency arithmetic. In this chapter the important concept of a *redundant number representation* is introduced, and it is shown how it may be used to obtain fast addition, an operation fundamental to the implementation of all arithmetic operations. A simple, but effective, technique is presented to realise redundant adders using standard full-adders, and a number of examples are given. This technique is used extensively in later chapters to obtain low-latency arithmetic operators.

Redundant arithmetic also enables arithmetic operations to be performed in a most-significant-digit-first (msd-first) manner. This offers an approach for achieving arithmetic with latency which is low and independent of wordlength, and is considered later in the chapter.

## 2.2 Redundant Number Systems

#### 2.2.1 Redundant Representation

Consider the representation of a number using a fixed-positional number system with radix-r

$$X = x_{a}x_{a+1}...x_{-1}x_{0} \cdot x_{1}x_{2}...x_{b}$$

$$= \sum_{i=a}^{b} x_{i}r^{-i} \qquad x_{i} \in \{\rho_{min}, ..., \rho_{max}\}$$

(2.1)

Here and later in the thesis upper case letters are used to represent a complete word and lower case letter to represent individual digits.

In a conventional number representation each digit is allowed to assume one of r values. In a redundant number representation each digit assumes more than r values i.e.  $\rho_{max} - \rho_{min} \ge r.$  More formally, the cardinality of a digit set is  $C_r = \rho_{max} - \rho_{min} + 1$ , and by definition the digit-set is redundant if  $C_r > r$  and non-redundant if  $C_r = r$ . If there is only

Chapter 2 Redundant Arithmetic

one additional value in the digit-set (i.e.  $C_r = r + 1$ ) then the digit-set is minimally redundant. If  $C_r = 2r - 1$  then it is referred to as maximally redundant and over redundant if  $C_r \ge 2r$ . If negative digits are allowed, the representation is signed. If the digit set is symmetric (i.e.  $-\rho_{min} = \rho_{max}$ ) then it is a Signed Digit Number Representation (SDNR), otherwise it is asymmetric and a Generalised Signed-Digit Number Representation [Parh90].

Table 2.1[McQu92] presents a summary of the number systems, and for each gives examples of how the number 528<sub>10</sub> could be represented. An overbar is used as a more succinct representation of negative digit values.

| Number system                  | Digit-set         | Cardinality | Representation of 528 <sub>10</sub> |

|--------------------------------|-------------------|-------------|-------------------------------------|

| Conventional                   | [09]              | 10          | 528                                 |

| Non-redundant, signed          | [36]              | 10          | 532                                 |

| Minimally-redundant, symmetric | [55]              | 11          | 532, 1532                           |

| Maximally-redundant, symmetric | [99]              | 19          | 532, 1532, 1488                     |

| Over-redundant, symmetric      | [FF] <sup>a</sup> | 30          | 532, 1532, 1488, 4C8                |

| Asymmetric                     | [78]              | 16          | 528, 532, 1532                      |

Table 2.1 Representations of the number 528<sub>10</sub>

One advantage of a redundant representation is that the need for carry-propagation is reduced or completely eliminated when two numbers are added. This reduces the time to perform addition and also makes it independent of wordlength. Due to the fundamental importance of addition this has implications for the realisation of all arithmetic operators.

The *carry-save* representation constitutes a redundant number system, since each digit comprises a carry and a sum bit, and so may take values  $[0...2]_2$  (where the subscript is used to signify the radix of the digit-set). The carry-save representation has been used for many years to avoid carry-propagation, and so reduce the time to perform repeated additions in an accumulator or multiplier. On completion of either operation, the result is converted to conven-

a. Hexadecimal digit coding adopted (i.e. A=10, B=11 etc.)

tional, non-redundant binary by adding the sum and carry bits together using an adder which propagates the carries. In the worst case, the conversion takes as long as a carry takes to propagate from the least to the most significant bit of the result. However, it is performed only once, whereas the number of redundant additions is far greater.

SDNRs have the advantage that the truncation error is almost unbiased[Priv90], whereas asymmetric digit-sets, such as carry-save, require rounding to achieve similar low-levels of bias in truncation error. A particularly useful SDNR is the *minimally redundant radix-4 representation (MinR4)*, which uses the digit-set  $[\bar{2}...2]_4$ . This does not contain the digit 3 or  $\bar{3}$ , so it is possible to form products between its digits and a binary number using only shift and complement operations. More specifically, multiplies by 3 are not required, which avoids the need for an adder to produce them.

The MinR4 number representation has been used to reduce the number of partial products generated in multiplication, and is obtained from the conventional binary representation using *modified Booth's coding*. Both the original[Boot51] and the modified Booth's coding schemes[Rubi75] represent important arithmetic techniques, which are considered further in the next section.

#### 2.2.2 Booth's Coding

The original Booth's algorithm replaces sequences of 1's in a number with a 1 preceding the sequence and a  $\bar{1}$  at the end, e.g. 1111 would be represented by  $1000\bar{1}$ . In multiplication, this recoding operation can be applied to increases the number of 0s in a multiplier, and so reduce the number of partial-products which must be formed and added. The recoding of digits can be performed without carry-propagation. However, on occasions where there are few runs of 1s or 0s, this form of recoding can *increase* the number of non-zero digits.

The number of non-zero digits can be minimised by using an alternative recoding. However, it is time consuming as the whole word must be examined to determine each bit. Further-

more, the result is of little benefit, as in a synchronous parallel multiplier it is necessary to design for the worst-case number of non-zero bits, which is approximately half the total number of bits. Therefore, a modified form of Booth's coding is generally used, which achieves the same worst-case reduction of partial-products, but in much less time. The modified recoding ensures that there is at most one non-zero digit in each pair of output digits. Figure 2.1 presents an example. Each pair of digits can be obtained in parallel from 3-bits of the binary using the truth-table shown in the figure. When interpreted as a radix-4 number the result is in a MinR4 representation, as shown in the figure.

| Binary  | $0\overline{1}$                       | 1 1 | [0,1] |

|---------|---------------------------------------|-----|-------|

| Recoded | $\begin{bmatrix} 1 & 0 \end{bmatrix}$ | 0 1 | 01    |

| MinR4   | 2                                     | 1   | 1     |

| Input Triplet | Output | Radix-4 |

|---------------|--------|---------|

| 000 or 111    | 00     | 0       |

| 001 or 010    | 01     | 1       |

| 011           | 10     | 2       |

| 100           | 10     | 2       |

| 101 or 110    | 01     | 1       |

Figure 2.1 An example of modified Booth's recoding

# 2.3 Addition of Redundant Numbers

#### 2.3.1 Redundant Adders

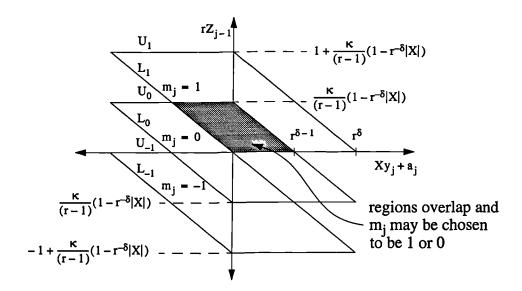

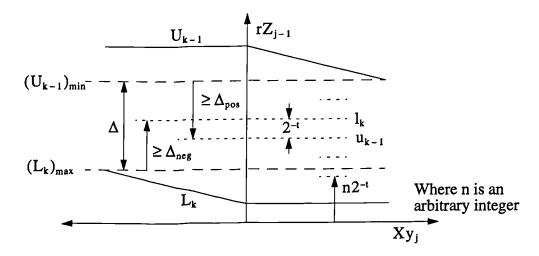

Avizienis[Aviz61] showed that two SDNR numbers could be added using one or two transfer digits as shown in Figure 2.2. In the figure, the digits to be added have been denoted  $a_i$  and  $b_i$ . Their sum has a greater range than can be represented by the output digit  $z_i$ . Therefore, the objective of the adders is to reduce the range of the input digits to that of the output using a number of stages of addition.

Chapter 2 Redundant Arithmetic

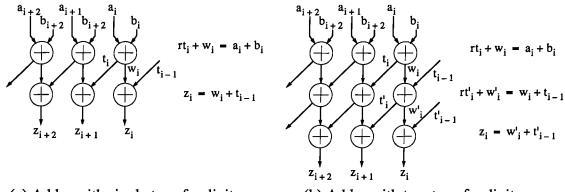

(a) Adder with single transfer digit

(b) Adder with two transfer digits

Figure 2.2 Redundant number adders

Figure 2.2 (a) shows this being achieved in radix-r arithmetic using only two stages of addition and one transfer-digit. The first stage generates the transfer digit  $t_i$  and an intermediate sum  $w_i$  from the input digits  $a_i$  and  $b_i$ . The second stage adds the intermediate sum to the transfer digit from the digit-slice to the right. This two-stage addition process ensures that the transfer digit propagates only one digit-slice to the left. For this to occur correctly, the two relationships presented in the figure, defining the operation of the adders, must be satisfied. This is not possible for a radix-2 representation when adding two or more redundant numbers, and it is necessary to use three stages of addition and two transfer digits, as shown in Figure 2.2 (b). It is also necessary to use three stages when the output digit-set has reduced redundancy, as will be demonstrated later in the chapter by an adder design with a MinR4 output. In either case, the extra level of adders means that the transfer digits may now propagate two digits to the left.

The number of transfer digits required depends upon the radix, the number of inputs, and the level of redundancy in the input and output of the adder. The design of redundant adders has also been considered by Parhami[Parh90] for generalised signed digit numbers. The logical design of the adders is not considered, yet is important, as the efficiency of the adder is dependent upon the representation used for intermediate digits. Carter and Robertson[Cart90] have simplified the design of adder logic by decomposing higher-radix adders into a number of stages of lower-radix addition. If decomposed into radix-2, then only 3 primitive operators

Chapter 2 Redundant Arithmetic

are required to construct an adder. However, the logical implementation of the adders must be chosen to accommodate the digit-sets used within the adder and these digit-sets are identified by an exhaustive search.

In this thesis, it is proposed that the adder design process be further simplified by basing the adder design on a single primitive component, which consists of a generalised interpretation of the full-adder. Also, and perhaps more significantly, the use of a single full-adder primitive offers high speed and low area when an optimised full-adder standard cell is available. This strategy is supported by recent work by Oklobdzija *et al.*[Oklo96] which demonstrates that, for the case of an unsigned adder for multipliers, an approach using full-adders with a careful choice of inputs and outputs to accommodate their differences in timing, can be an effective approach for obtaining high-speed implementations of large adders. In this thesis, SDNR adders are required. To accomplish this, it is necessary to encode signed-digits using a binary representation so that they may be added using full-adders. This is discussed in the following sections.

#### **2.3.2** Encoding of Redundant Numbers into Binary

Signed-digits can be encoded into binary in various ways. Signed magnitude and 2's complement are two possible approaches. Another method is to use a convenient choice of positively or negatively weighted bits to represent each digit. For example, the MinR4 digit can be represented by three bits: one bit with weight  $\bar{2}$  and two bits with weight 1. The advantage of this representation is that a generalised version of the full-adder can be used to add digits.

#### 2.3.3 Generalised Full-Adders

The addition of positively- and negatively-weighted bits can be achieved using a full-adder, providing that the coding presented in Table 2.2 is adopted. As given, the usual logical encoding is used for positively-weighted bits, but an inverted coding is used for negatively-weighted bits. The conversion from a positively-weighted to a negatively-weighted bit is ob-

tained by inverting it.

Table 2.2 Encoding of signed bits

| Arithmetic Value of Bit | Logical<br>Value |  |

|-------------------------|------------------|--|

| 0                       | 0                |  |

| +1                      | 1                |  |

| Arithmetic Value of Bit | Logical<br>Value |

|-------------------------|------------------|

| 0                       | 1                |

| -1                      | 0                |

(a) Encoding of a positively-weighted bit (b) Encoding of a negatively-weighted bit

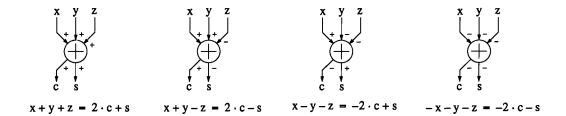

By adopting this coding, it is possible to realise the four 3-input adder combinations of the *generalised adder* shown in Figure 2.3 using the conventional full-adder. It is no longer necessary, as suggested by Hwang[Hwan79] p. 173 and others, to change the logic itself. Extensive use is made of this fact in this and the next chapter.

Figure 2.3 The generalised full-adder

#### 2.3.4 Redundant Adders Based on Generalised Full-Adders

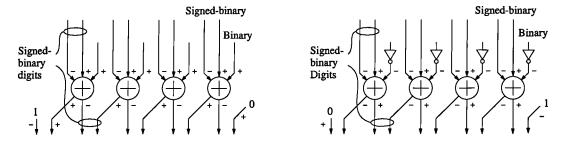

Redundant number adders can be constructed from generalised full-adders. For example, Figure 2.4 (a) shows the addition of a signed-binary number and a binary number.

(a) Addition of signed-binary and binary

(b) Subtraction of binary from signed-binary

Figure 2.4 Using full-adders to add a signed-binary and a binary number

A single redundant input means that only one transfer digit is required in this addition, and this is added to the output by appending the digit, avoiding a second row of adders. Figure 2.4

(b) shows that subtraction of the binary input can be obtained by adding a negated version of it, obtained by inversion. The sign of the full-adder output must change to accommodate the two negative input bits. Also, it is necessary to ensure that arithmetically-zero signals are set to the correct logical values. This means that the transfer digit entering the least-significant-digit of the result should be set to logic one. Note that obtaining subtraction in this way (i.e. by inverting bits and adding 1) is the same process as taking the 2's complement. However, allowing individual bits to take on positive or negative signs offers greater flexibility, as demonstrated by the following examples.

#### 2.3.5 Further Examples of Redundant Adders

Two further examples of redundant adders constructed using full-adders are presented in this section. In these and other designs developed in the thesis, the specification of the coding and the use of full-adders has so constrained the design space that an optimum solution is simply found by trial and error. When the number of inputs is large, a more systematic design procedure can be used, and an adder structure based on an adder-tree can be adopted.

As mentioned earlier, the addition of two signed-binary numbers requires at least two transfer digits. Figure 2.5 (a) shows one digit-slice of the generic adder with digit bounds specified for signed-binary addition. Its implementation using full-adders is shown in Figure 2.5 (b). As in the previous example, the final row of addition is achieved without the need for logic circuits. Furthermore, the first transfer digit is determined using three of the four input bits, so there is a degree of flexibility in its calculation which has been exploited to simplify its generation.

In Figure 2.5 (a) the first intermediate sum is a redundant number (i.e.  $(w_i)_{max} - (w_i)_{min} > r$ ). This avoids a transfer digit from the first adder with the bounds  $[\bar{1}...1]$ , requiring two bits. This would have been a valid solution, but would have required an additional half-adder to implement the first row of adders.

Chapter 2 Redundant Arithmetic

- (a) Two transfer digit adder-slice

- (b) Adder implemented using full-adders

Figure 2.5 Using full-adders to add two signed-binary numbers

As a final example, consider the implementation of the MinR4 adder mentioned briefly in section 2.3. At least two transfer digits are required, but these can be coded using single bits by allowing a redundant intermediate sum (as done in Figure 2.5 (a)). This implementation using full-adders is shown in Figure 2.6 (b).

(a) MinR4 adder-slice

(b) Adder implemented using full-adders

Figure 2.6 Using full-adders to add two MinR4 numbers

In conclusion, in this section it has been shown how full-adders may be used to implement SBNR adders by a suitable binary encoding of positively- and negatively-weighted bits. The output representation of an adder, or converter, can be controlled by a suitable choice of out-

Chapter 2 Redundant Arithmetic

put coding. The design process then becomes a matter of constructing a network of full-adders which compresses the adder inputs into the bit representation of the output.

Conversion from a redundant representation into a non-redundant one, such as a 2's complement representation, can also be performed by generalised full-adders. Alternatively, the negatively-weighted bits can be converted to a negative 2's complement number and added to the positively-weighted bits using a conventional 2's complement adder. In either case, carry-propagation the full length of the adder will be required. To obtain high-throughput, the addition should be pipelined. If low-latency is required, then a fast carry-propagation technique can be used, such as carry-look-ahead (CLA)[Wein56] or carry-select addition[Bedr62].

# 2.4 Most-Significant-Digit-First Arithmetic

Employing redundant arithmetic to reduce carry-propagation time is one effective method of reducing operator latency. However, another application, which aims to offer further reductions, is to allow arithmetic to be performed in a most-significant-digit-first (msd-first) manner. There are serial and parallel forms of msd-first arithmetic. The parallel form offers high-throughput and is of particular relevance in this thesis, but by way of introduction, the serial form, referred to as *on-line arithmetic*, is considered first.

On-line arithmetic was proposed by Ercegovac [Erce77], and since then there has been considerable development of the approach[Triv77][Irwi87]. Figure 2.7 (a) shows how numbers are represented by a serial sequence of digits presented in a msd-first order. Unlike conventional arithmetic, the arithmetic calculation starts with the msd and generates the result in the same order. The benefits of performing the operation this way are that it offers lower latency, and the calculation can be stopped as soon as the required number of significant digits has been calculated.

In contrast, using a conventional least-significant-bit-first serial approach, as employed by

Denyer[Deny85], it would be necessary in multiplication to calculate all the least significant digits of the result in the process of calculating the most significant ones - even if they are not required. This is particularly true in repeated multiplications, since the lower half of each intermediate product must be discarded to avoid wordlength growth.

Figure 2.7 Digit-serial, on-line computation

As shown in Figure 2.7 (b) the on-line operators can be cascaded to obtain the result of a whole sequence of operations with low-latency. The latency can sometimes be reduced further by merging two or more operations into a single combined operator. The most relevant example of this is by Ercegovac[Erce88] who computes the function  $z = \frac{1}{\sqrt{x^2 + y^2}}$ , which is a requirement of the conventional Givens rotation.

The serial format of on-line arithmetic minimises the number of wires required to communicate a number, which has advantages in chip design. However, it requires that one calculation be completed before another starts and so provides low throughput. To obtain higher throughput, Woods and Knowles[Wood88] proposed the extension of on-line arithmetic to parallel architectures (generally referred to as *msdf arithmetic*). They also generalised the approach to allow inputs in both msdf and parallel formats, as shown in Figure 2.8.

Figure 2.8 Msdf arithmetic

An application which has benefited from msdf arithmetic is recursive filtering, in particular, the infinite impulse response (IIR) filter. In this application, the filter output is generated by summing weighted versions of previous outputs. High sample-rate operation is obtained by generating and feeding back the output as quickly as possible, using an architecture which can sustain the rate of computation. An msdf multiply-add operator offers both the high-throughput and low-latency necessary for high sample-rate operation to be achieved[Wood95].

## 2.4.1 Converting To and From the Msdf Format

Converting a number into an msdf representation is trivial. However, converting back the skewed representation of msdf into a parallel non-redundant representation incurs a delay while all the digits are aligned, and requires a carry-propagate addition. The addition can be performed as the digits are being aligned using 'on-the-fly' conversion. This was originally proposed for radix-2 by Majerski[Maje85] and extended to higher radices by Ercegovac and Lang[Erce87], and is achieved in the following way.

For each input digit the sum up to and including digit  $d_j$  is obtained recursively by  $A_j = A_{j-1} + 2^{-j}d_j$ . If carry-propagation is to be avoided, then the result must be assembled by only *appending* bits to the binary result. If the signed-binary digit,  $d_j$ , is 1 or 0 the output is updated by simply appending a 1 or 0 to  $A_{j-1}$ . If the digit is  $\bar{1}$  then a subtraction is required, which will result in a borrow. This can be avoided by maintaining a second term in which the borrow has already been performed, i.e.  $B_{j-1} = A_{j-1} - 2.2^{-j}$ . The result for

Chapter 2 Redundant Arithmetic

$d_j = \overline{1}$  is then  $B_{j-1} + 2^{-j}$ . The  $B_j$  term can be updated in a similar fashion to  $A_j$ .

Knowles[Know89b] produced an alternative form of the signed-binary to binary converter by noting that the addition of the digit  $\bar{1}$  had the effect of inverting the preceding string of bits of the form 10...0 in  $A_{j-1}$  (where the number of logic 0s may be zero). For example  $101\,1000\,\bar{1} = 101\,01111$ . Now only  $A_j$  need be maintained, although a second term is not avoided as a flag must be included for each bit to indicate whether it should be inverted when a  $\bar{1}$  occurs. However, this solution does offer simplification of the hardware and is used later in the thesis when conversion is required (e.g. at the output of the modified-SRT divider).

# 2.5 DSP Using Msdf Arithmetic

A wide range of arithmetic operators can be performed using msdf parallel structures, and it is possible to implement complete DSP algorithms using a combination of msdf operators to achieve low-latency, high-throughput implementations. For algorithms with feedback this offers the potential for high sample-rate operation.

DSP system implementation using on-line arithmetic has already been widely addressed, and the principles can be directly extended to the msdf approach. With a view to exploiting this work for implementing msdf systems, McQuillan reviewed the on-line arithmetic literature and considered its application in areas other than IIR filtering[McQu92]. He also examined the extension of on-line fixed-point operators to floating-point arithmetic. This work is of particular relevance to this thesis and identifies a serious limitation of the msdf approach, so is considered next.

Floating-point requires the number representation to be composed from an exponent and a normalised mantissa. Exponents can be processed very rapidly using conventional arithmetic as they generally have short wordlength. The mantissas can be processed using fixed-point msdf operators providing that *normalisation* and *alignment* operations are used to convert to and from the normalised representation (where normalisation is a shift-left and alignment a

shift-right operation).

Conventionally, a mantissa of a floating-point number, M, is normalised if  $r^{-1} \le |M| < 1$  [IEEE85]. To determine if this is true for a redundant representation, it is necessary to examine all digits (e.g the signed-binary number  $0.1000000\overline{1}$  is unnormalised). Therefore, *quasi-normalised* numbers have been proposed (by Watanuki[Wata81]), where the mantissa is quasi-normalised if  $r^{-2} \le |M| < 1$ . To determine if this is the case only the first two digits of a number need be examined. However, the truncation error is greater and the wordlength must be increased by one bit to maintain the same worst-case relative error.

McQuillan showed that all the basic arithmetic floating-point operators (i.e. multiply, divide, square-root and addition) offer fixed low-latency, apart from true subtraction which could require a latency of n + 3 (where n is the mantissa wordlength). In subtraction, the problem arises from the large number of leading zeros which occur when two numbers which have similar values are subtracted. Consequently, to normalise the result a wordlength dependent delay can be incurred. In applications where the latency of the subtraction operation is critical, for example when it is performed within a loop, floating-point msdf arithmetic in its current form, will be of little benefit. McQuillan identified three approaches to tackling the problem.

Variable Precision Arithmetic: Unnormalised numbers which require more than m-cycles to normalise are assumed to be zero. Hence, only a delay of m + 3-cycles is introduced where m < n. The smaller m is, the greater the numerical implications of this approach will be. Unless the system is trivial, it will be necessary to establish the impact on the quality of the result using numerical simulations. In the QR-algorithm, the implications of this approach are likely to be severe.

Unnormalised Arithmetic: Floating-point arithmetic, in which the mantissas are not normalised, has been considered by Metropolis in [Metr63]; although normalisation before di-

vision was still proposed. A limitation of this approach is a lack of error and stability analysis for unnormalised arithmetic. Owens considers the normalisation problem in detail in [Owen83] and suggests that certain algorithms can be coerced into generating numbers that are normalised or nearly so. Generating normalised values has the added benefit that classical error and stability analysis can be applied.

Asynchronous Systems: The average normalisation delay will be considerably less than the worst-case delay. If a system is designed to operate in an asynchronous manner, the variable normalisation delay can be accommodated. Such a system will need buffers to queue data and a greater level of control to manage its operation, so the extra complexity of implementing these would need to be assessed and compared with the savings offered by msdf arithmetic.

All of the above approaches will require extensive computer simulations to ensure that the numerical performance and, in the asynchronous case, the throughput are acceptable. This can be a computer-intensive task, particularly if very detailed modelling of the operators is required to faithfully generate numerical errors.

# **Chapter 3** High-Throughput, Low-Latency Multipliers

# 3.1 Introduction

## 3.1.1 Importance of Multiplication

Many DSP algorithms are dominated by multiply-add operations. Multipliers can also be used to realise other operations, such as divides, square-roots and transcendental functions, using convergence or series expansion approaches. For these reasons high-throughput, low-latency multipliers have been the primary focus of modern computer arithmetic research.

High-throughput multipliers can be achieved by pipelining. This divides the operation into stages using latches, so that only the smaller delay of a single stage determines the rate at which inputs may be applied. Unfortunately, this does not reduce the latency of the result, as this is generated by the combination of all stages, irrespective of how they are partitioned. In microprocessors, latency complicates operation and programming, and in the implementation of recursive systems, limits the sample-rate. One approach to reducing latency is to use redundant arithmetic, as considered in this chapter.

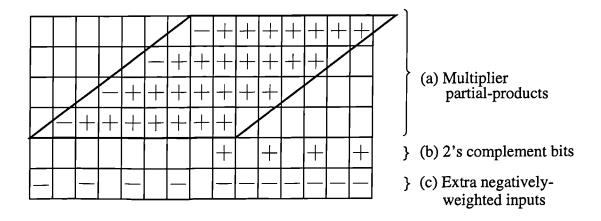

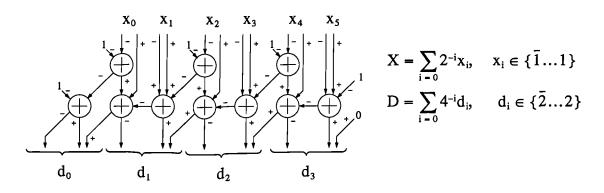

#### 3.1.2 Low-Latency, Redundant Multiplication