#### Technical University of Denmark

### **High Efficiency PFC Frontend for Class-D Amplifiers**

Li, Qingnan; Andersen, Michael A. E.; Thomsen, Ole Cornelius; Hansen, Lars B. R.; Frium, Mads P.

Publication date:

Link back to DTU Orbit

Citation (APA):

Li, Q., Andersen, M. A. E., Thomsen, O. C., Hansen, L. B. R., & Frium, M. P. (2012). High Efficiency PFC Frontend for Class-D Amplifiers.

### DTU Library

Technical Information Center of Denmark

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Technical University of Denmark

Qingnan Li

# **High Efficiency PFC Frontend for Class-D Amplifiers**

PhD thesis, March 2012

### High Efficiency PFC Frontend for Class-D Amplifiers

#### Author:

Qingnan Li

#### **Supervisors:**

Michael A. E. Andersen Ole C. Thomsen Lars B. R. Hansen Mads P. Frium

#### **Electrical Engineering**

Technical University of Denmark Ørsteds Plads, Building 349 DK-2800 Kgs.Lyngby Denmark http://www.elektro.dtu.dk elektro@elektro.dtu.dk

Tel: (+45) 45 25 38 00 Fax: (+45) 45 93 16 34

### **Preface**

This thesis is submitted in partial fulfilment of the requirements for obtaining the PhD degree at the Technical University of Denmark, DTU Elektro, Electronics Group. The Ph.D. project was carried out during the period from the period from March 2009 through March 2012 and was conducted in cooperation with Technical University of Denmark and Bang & Olufsen ICEpower.

The Ph.D. project was supervised by Professor Michael A. E. Andersen and Associate Professor Ole C. Thomsen at Technical University of Denmark and Lars B. R. Hansen and Mads P. Frium at Bang & Olufsen ICEpower.

## **Acknowledge**

During my Ph.D. studying period, I would like to deeply indebted and grateful to all of those who has stood by me and helped me throughout this project.

My special appreciation, thanks and love goes to:

- My supervisors, Michael A. E. Andersen, Ole C. Thomsen, Lars B. R. Hansen and Mads P. Frium for giving me this opportunity and their support, encouragement and endless confidence in me.

- All of my colleagues for their help, support, and precious discussions.

- My dear husband, Liang Chen and parents Feng Li and Yanmei Deng for their love and endless understanding and tolerance during this project.

### **Abstract**

This thesis investigates the design of high efficiency Power Factor Correction (PFC) converter for Class-D amplifier at universal line and 3.5kW power range.

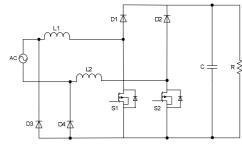

The work starts with an overview on different high efficiency Bridgeless PFC topologies and investigates their applicability with respect to the given specifications in Chapter 1. Based on the conclusions of Chapter 2, the single-phase Two-Boost-Circuit Bridgeless PFC converter topology is considered the most promising to start with regarding the achievable converter efficiency and the EMI performances.

The subsequent Chapters discuss the method to optimize and improve the performance of Two-Boost-Circuit BPFC converter in detail.

Chapter 3 explains the working principle of the Two-Boost-Circuit BPFC converter firstly. And then, an optimized design procedure is implemented to achieve an useful compromise between efficiency and power density. Where, impacts of the Boost inductor design is analyzed carefully.

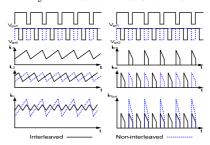

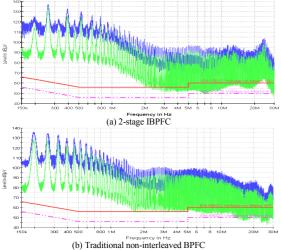

Chapter 4 firstly presents a novel interleaved BPFC (IBPFC) topology, which can be consider as the extension version of traditional Two-Boost-Circuit BPFC in Chapter 3 for EMI improvement. And then, the IBPFC's EMI model is used to study the insight of the relationship of EMI reduction and the number of interleaved stages. Moreover, an multi-objective optimization design procedure is proposed for designing a high efficiency, high power density and low EMI IBPFC system. Finally, frequency dithering technique is researched and implemented for the proposed IBPFC to gain further EMI attenuation.

$Chapter\ 5$  analyzes the measurement accuracy of the efficiency results presented in this thesis in Chapter 4, which makes the efficiency measurement in this report more convictive.

$Chapter\ 6$  summarizes the obtained results and concludes this work. Furthermore, an outlook regarding future researches in the IBPFC converter is presented.

### Resumé

Denne afhandling undersøger design af høj effektivitet Power Factor Correction (PFC) konverter for klasse-D forstærker på universel linje og 3.5kW effektområde.

Arbejdet starter med en oversigt over forskellige høj effektivitet uden bro PFC topologier og undersøger deres anvendelighed i forhold til de givne specifikationer i kapitel 1. Baseret på konklusionerne i kapitel 2, enkelt-fase to-Boost-Circuit uden bro PFC konverter topologi betragtes som den mest lovende at starte med om opnåelige konverterens virkningsgrad og EMI forestillinger.

De efterfølgende kapitler diskuterer metode til at optimere og forbedre effektiviteten af to-Boost-Circuit BPFC konverter i detaljer.

Kapitel 3 forklarer arbejder princippet om to-Boost-Circuit BPFC konverter først. Også er en optimeret design procedure gennemføres for at nå et nyttigt kompromis mellem effektivitet og effekttæthed. Hvor er konsekvenserne af den Boost spole design analyseret grundigt.

Kapitel 4 For det første præsenterer en ny interleaved BPFC (IBPFC) topologi, som kan betragte som en udvidelse version af traditionelt to-Boost-Circuit BPFC i kapitel 3 for EMI forbedring. Og derefter bliver IBPFCs EMI model anvendt til at undersøge den indsigt af forholdet af EMI reduktion og antallet af sammenflettede trin. Endvidere er en multi-mål optimering design foreslåede metode til at designe en høj effektivitet, høj effekttæthed og lav EMI IBPFC system. Endelig er frekvensen dithering teknik forsket og gennemført den foreslåede IBPFC at få yderligere EMI dæmpning.

$Kapitel\ 5$  analyserer målenøjagtighed af de effektiviseringsgevinster resultater, der præsenteres i denne afhandling i kapitel 4, hvilket gør den høje effektivitet måleresultater i denne rapport mere convictive.

Kapitel 6 sammenfatter de opnåede resultater og konkluderer dette arbejde. Desuden er en prognose om den fremtidige forskning i IBPFC konverter præsenteret.

### **Contents**

| Pı | refac | е                                    | i   |

|----|-------|--------------------------------------|-----|

| A  | ckno  | wledge                               | iii |

| A  | bstra | ct                                   | v   |

| R  | esum  | n <b>é</b>                           | vii |

| 1  | Intr  | roduction                            | 1   |

|    | 1.1   | Scope                                | 1   |

|    | 1.2   | Background and Motivation            | 2   |

|    | 1.3   | Specifications                       | 3   |

|    | 1.4   | Project Objectives and Contributions | 4   |

|    | 1.5   | Project Plan and Content             | 5   |

|    | 1.6   | Thesis Structure                     | 5   |

x CONTENTS

| 2 | Stat | te of tl | ne Art                                                   | 9  |

|---|------|----------|----------------------------------------------------------|----|

|   | 2.1  | Deriva   | ation of Bridgeless PFC Converters                       | 10 |

|   | 2.2  | BPFC     | Topologies Overview                                      | 10 |

|   |      | 2.2.1    | Basic BPFC System                                        | 10 |

|   |      | 2.2.2    | BPFC with Two Boost Circuits                             | 11 |

|   |      | 2.2.3    | Basic BPFC with Bidirectional Switch                     | 12 |

|   |      | 2.2.4    | Pseudo Totem-pole BPFC                                   | 14 |

|   |      | 2.2.5    | Totem-pole BPFC                                          | 15 |

|   | 2.3  | Summ     | ary of State-of-the-art Analysis                         | 16 |

| 3 | Des  | _        | the High Efficient BPFC - Boost Inductor Optimiza-       | 19 |

|   | 3.1  | Topolo   | ogy Basic Operation                                      | 19 |

|   | 3.2  | High I   | Efficiency Boost Inductor Design                         | 21 |

|   |      | 3.2.1    | Conventional Boost Inductor Design Procedure             | 21 |

|   |      | 3.2.2    | Optimized Design Procedure                               | 23 |

|   |      | 3.2.3    | Mathematical Modelling                                   | 25 |

|   |      | 3.2.4    | Inductance vs. Semiconductor Losses                      | 28 |

|   |      |          | 3.2.4.1 Semiconductor Losses                             | 28 |

|   |      |          | 3.2.4.2 Inductance Optimization vs. Semiconductor Losses | 30 |

|   |      | 3.2.5    | Efficiency and Volume Optimization                       | 31 |

|   |      |          | 3.2.5.1 Cores Selection                                  | 31 |

|   |      |          | 3.2.5.2 Winding Losses                                   | 32 |

CONTENTS xi

|   |     |                | 3.2.5.3 Core Losses                                                                                          | 33 |

|---|-----|----------------|--------------------------------------------------------------------------------------------------------------|----|

|   | 3.3 | Exper          | iment Results from a 3.2kW Bridgeless PFC                                                                    | 36 |

|   | 3.4 | Conclu         | usions on the Design of High Efficient Boost Inductors 3                                                     | 38 |

| 4 | EM  | I <b>A</b> nal | ysis and Suppression 3                                                                                       | 39 |

|   | 4.1 | EMI N          | Modelling                                                                                                    | 39 |

|   | 4.2 | EMI S          | Suppression                                                                                                  | 10 |

|   |     | 4.2.1          | EMI Reduction Using Interleaving Technique                                                                   | 11 |

|   |     | 4.2.2          | Multi-Interleaved Stages and EMI Cancellations 4                                                             | 11 |

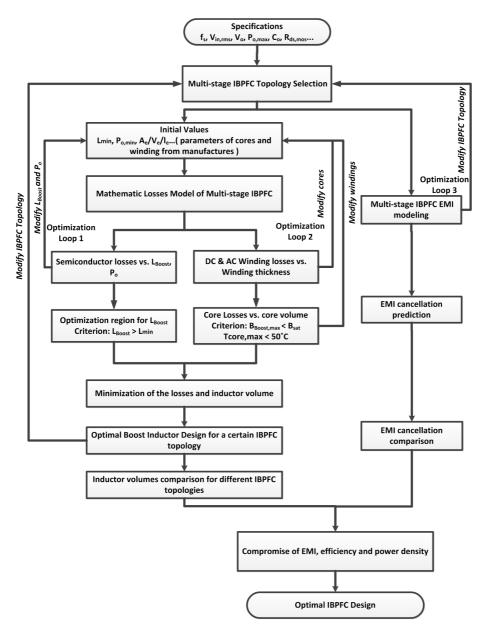

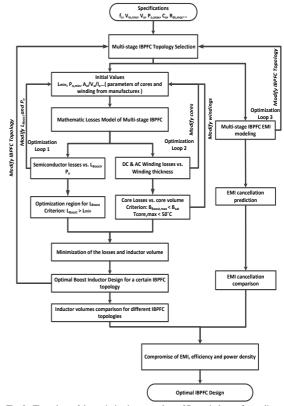

|   |     | 4.2.3          | Novel High Efficient Interleaved BPFC Converter Design using Multi-Objective Design Optimization Procedure 4 | 16 |

|   |     |                | 4.2.3.1 Definition of MDOP                                                                                   | 17 |

|   |     |                | 4.2.3.2 The MDOP Design Flow Chart for IBPFC System 4                                                        | 17 |

|   |     | 4.2.4          | Experimental Results                                                                                         | 50 |

|   | 4.3 | EMI F          | Reduction Using Frequency Dithering                                                                          | 52 |

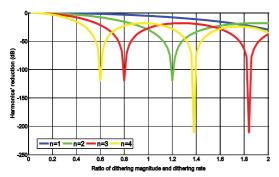

|   |     | 4.3.1          | Operation Principles                                                                                         | 53 |

|   |     | 4.3.2          | Advantages and Limitations                                                                                   | 56 |

|   |     |                | 4.3.2.1 Advantages of Frequency Dithering 5                                                                  | 57 |

|   |     |                | 4.3.2.2 Limitations of Frequency Dithering 5                                                                 | 58 |

|   |     | 4.3.3          | Conclusions on Frequency Dithering and EMI Reductions 5                                                      | 59 |

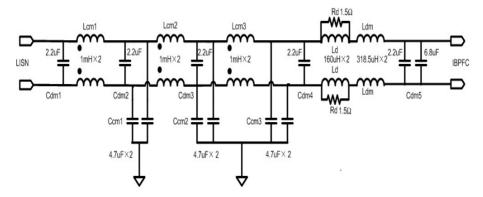

|   | 4.4 | EMI F          | Filter Design Considerations                                                                                 | 60 |

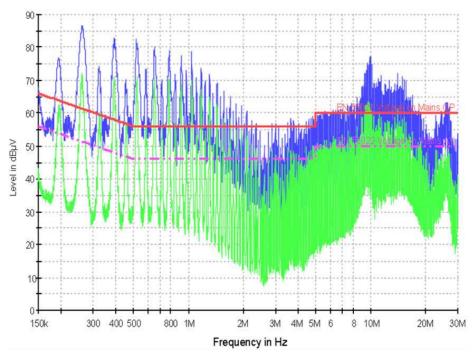

|   | 4.5 | Exper          | imental Results                                                                                              | 33 |

|   | 4.6 | Conclu         | usions of EMI Analysis and Suppression 6                                                                     | 34 |

xii CONTENTS

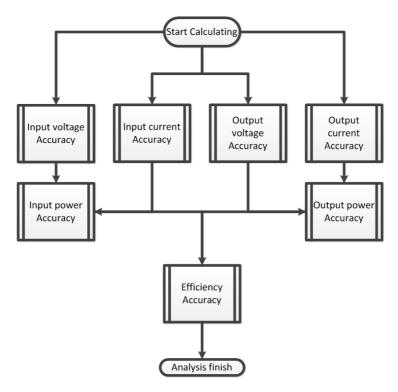

| 5  | Acc         | uracy Analysis                                         | 69           |

|----|-------------|--------------------------------------------------------|--------------|

|    | 5.1         | Experiment Set Up                                      | 69           |

|    | 5.2         | Accuracy Analysis                                      | 70           |

|    |             | 5.2.1 Accuracy of Measured $P_{in}$ and $P_o$          | 71           |

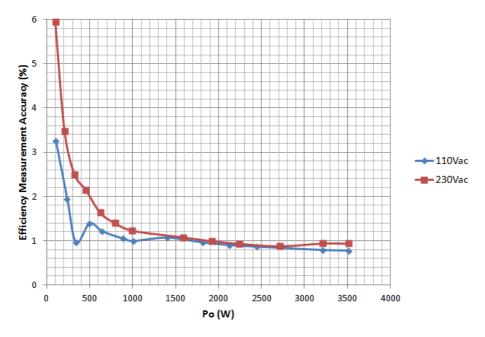

|    |             | 5.2.2 Accuracy of Measured Efficiency                  | 72           |

|    |             | 5.2.3 Estimation of Worst-case Accuracy of Efficiency  | 72           |

| 6  | Con         | clusions and Future Works                              | <b>7</b> 5   |

|    | 6.1         | Summary and Conclusions                                | 75           |

|    | 6.2         | Future Works                                           | 77           |

| Bi | bliog       | raphy                                                  | 77           |

| A  | Pub         | dications                                              | 87           |

|    | A.1         | PEDS2009 Published                                     | 87           |

|    | A.2         | ECCE Asia 2011 Published                               | 94           |

|    | A.3         | ACEMP 2011 Published                                   | 103          |

|    | A.4         | APEMC 2012 Published                                   | 109          |

|    | A.5         | ECCE Asia 2012 Published                               | 114          |

|    | A.6         | ECCE Asia 2012 Published                               | 121          |

|    | A.7         | Transactions on Industrial Electronics Paper Submitted | 127          |

| В  | <b>C</b> +- | + Code Fragment                                        | L <b>3</b> 9 |

|    | B.1         | Common Header                                          | 139          |

| CONTENTS | xii |

|----------|-----|

| CONTENTS | xi  |

| B.2 | Header for Magnetic Core   |

|-----|----------------------------|

| B.3 | Function for Magnetic Core |

| B.4 | Loop 1                     |

| B.5 | Loop 2                     |

| B.6 | Loop 3                     |

| B.7 | Model of losses            |

# **List of Figures**

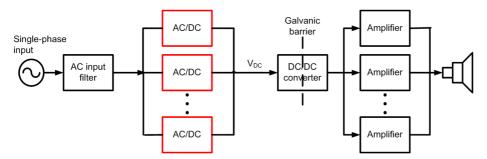

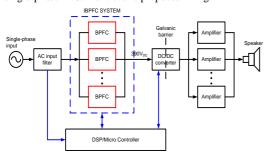

| 1.1 | Block diagram of typical power supply configuration for supplying Class-D amplifiers system from the AC mains | 2  |

|-----|---------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Passive single-phase diodes rectifier and its characteristic waveforms                                        | 3  |

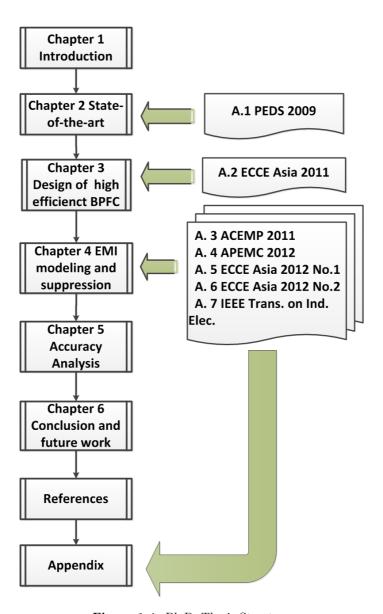

| 1.3 | Ph.D. Project Overview                                                                                        | 6  |

| 1.4 | Ph.D. Thesis Structure                                                                                        | 7  |

| 0.1 | D : DDDG 1G ID DDGT 1:                                                                                        | 10 |

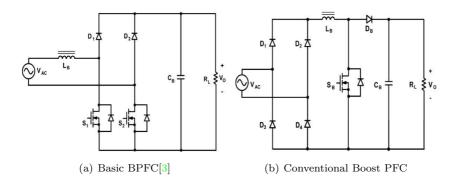

| 2.1 | Basic BPFC and Conventional Boost PFC Topologies                                                              | 10 |

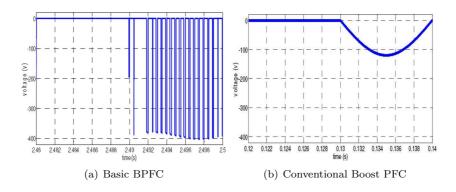

| 2.2 | Voltage Waveforms Between Neutral and Output Power Ground [27]                                                | 11 |

| 2.3 | Two-Boost-Circuit BPFC                                                                                        | 12 |

| 2.4 | Basic BPFC with Bidirectional Switch                                                                          | 13 |

| 2.5 | Pseudo Totem-pole BPFC                                                                                        | 14 |

| 2.6 | Totem-pole BPFC                                                                                               | 15 |

| 3.1 | Two-Boost-Circuit BPFC with good efficiency and low conducted EMI                                             | 20 |

| 3. | 2 Operation principles of the Two-Boost-Circuit BPFC                                                                                    | 20 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

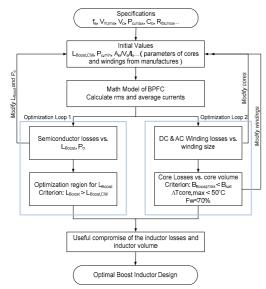

| 3. | Optimization procedure of inductor design in CCM for Two-Boost-Circuit BPFC with balance of efficiency and power density                | 24 |

| 3. | 4 Boost inductor current waveform in a switching cycle in CCM                                                                           | 25 |

| 3. | 5 Boost inductor current waveform in a switching cycle in DCM                                                                           | 27 |

| 3. | 6 Semiconductor Losses Ratio vs. Boost Inductance and Output Power                                                                      | 30 |

| 3. | 7 Increase of layer copper losses proximity effect as a factor $\varphi$ and MMF force ratio m [37]                                     | 33 |

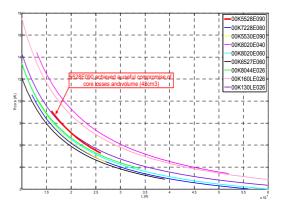

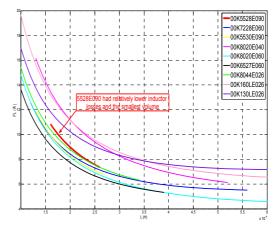

| 3. | 8 Inductor Winding Losses vs. Thickness of Copper Foil and Inductance. The core is Kool Mu E core 5528E90 from $Magnetics^{\circledR}$  | 34 |

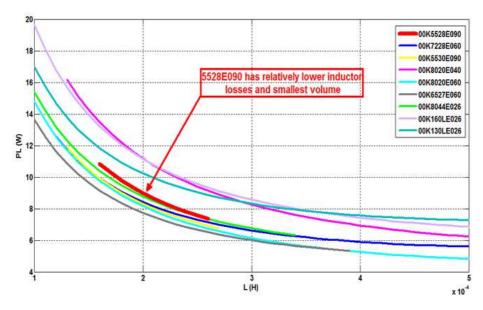

| 3. | 9 Core Losses vs. Boost Inductance for All Qualified Kool Mu E cores from $Magnetics^{\textcircled{\tiny{\$}}}$                         | 35 |

| 3. | 10 Total inductor losses vs. Boost inductance for different qualified Kool Mu E cores from $Magnetics^{\textcircled{\$}}$ when h=0.13mm | 36 |

| 3. | 11 Efficiency comparison of Two-Boost-Circuit BPFC at $220V_{ac}$ input and 390V output using core $5528E090$                           | 37 |

| 3. | 12 Input voltage and current waveforms from Two-Boost-Circuit at $220V_{ac}$ input and 390V output using core $5528E090$                | 37 |

| 4. | 1 DM EMI Modeling Process of the Two-Boost-Circuit BPFC                                                                                 | 40 |

| 4. | 2 CM EMI Modelling of the Two-Boost-Circuit BPFC                                                                                        | 41 |

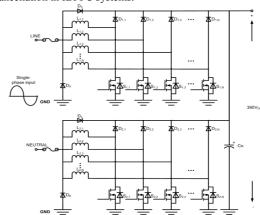

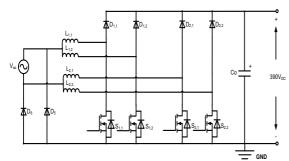

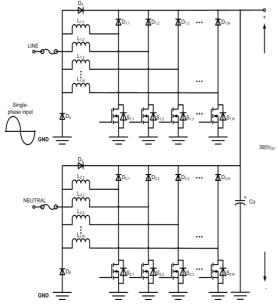

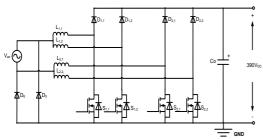

| 4. | 3 Proposed novel 2-stage Two-Boost-Circuit IBPFC                                                                                        | 42 |

| 4. | 4 Possible architecture of multi-stage IBPFC system                                                                                     | 43 |

| 4. | 5 DM (left) and CM (right) EMI modeling of the N-stage Two-<br>Boost-Circuit IBPFC                                                      | 43 |

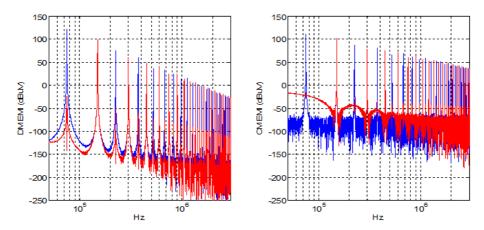

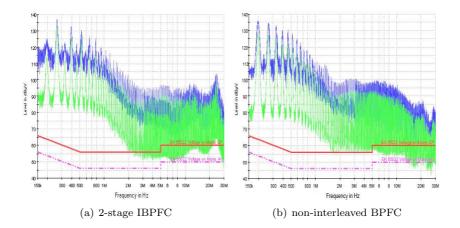

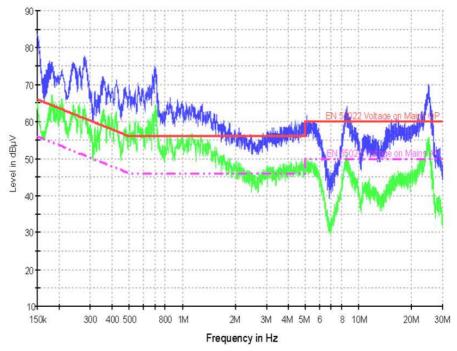

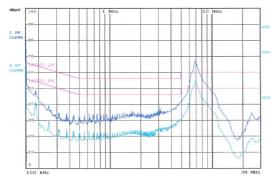

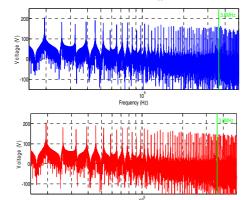

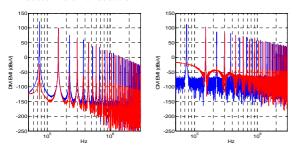

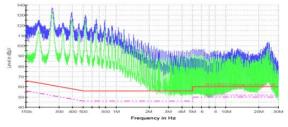

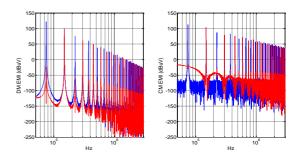

| 4.6  | DM (right) and CM (left) EMI comparison of 2-stage interleaved (red) and non-interleaved (blue) Two-Boost-Circuit BPFC at 3.5kW with improper switching frequency at 75kHz        | 46 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.7  | The MDOP design flow chart of IBPFC system                                                                                                                                        | 48 |

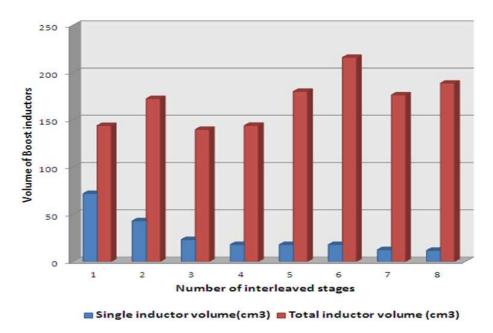

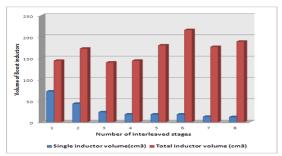

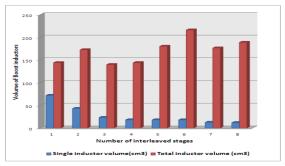

| 4.8  | Minimal single (blue) and total (red) inductor's volume comparison of interleaved and non-interleaved Two-Boost-Circuit BPFCs                                                     | 49 |

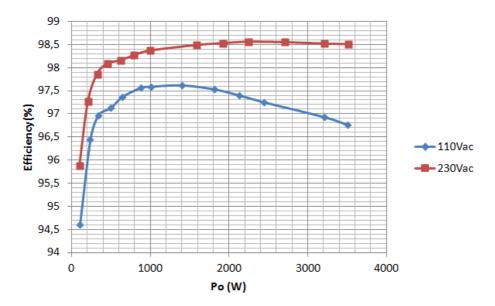

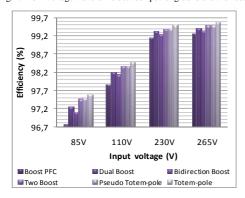

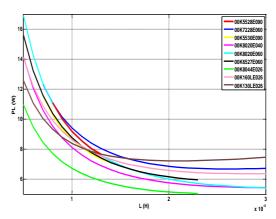

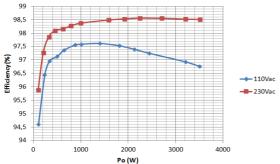

| 4.9  | Efficiency comparison of 2-stage IBPFC at different input voltages                                                                                                                | 50 |

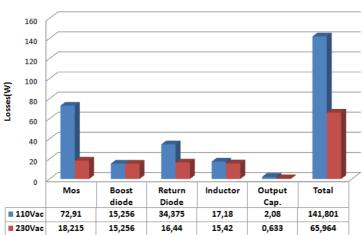

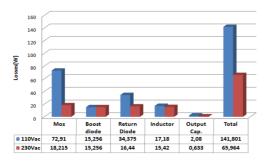

| 4.10 | Key components' losses distribution at $3.5 \mathrm{kW}$                                                                                                                          | 51 |

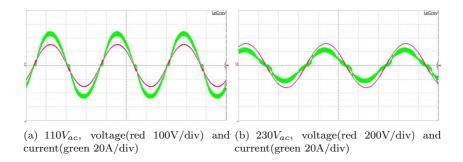

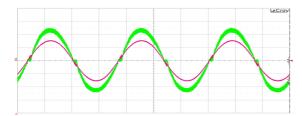

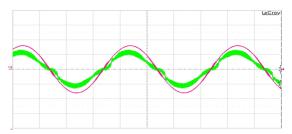

| 4.11 | Input voltage and current waveforms of 2-stage IBPFC at 3.5kW, PF=99%                                                                                                             | 51 |

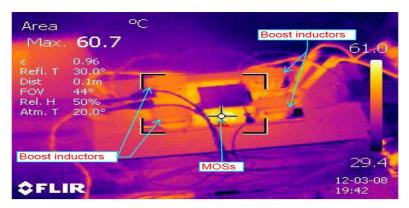

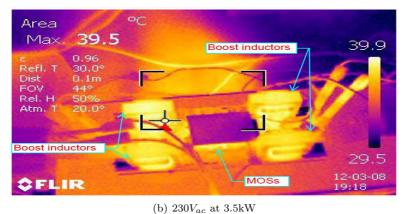

| 4.12 | Thermal measurement comparison of the proposed IBPFC system                                                                                                                       | 52 |

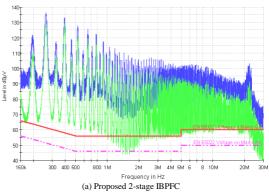

| 4.13 | EMI comparison at one eighth of full power and $230V_{ac}$ input without EMI filter                                                                                               | 53 |

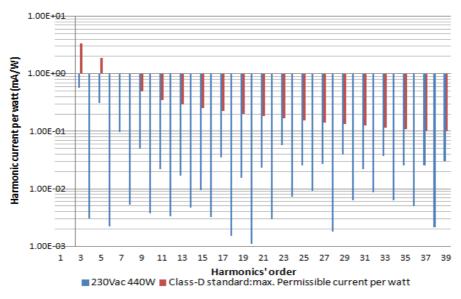

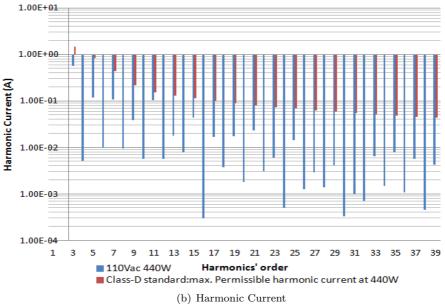

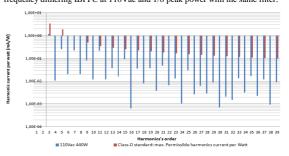

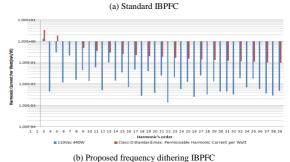

| 4.14 | Harmonic Current vs Class D Standard                                                                                                                                              | 54 |

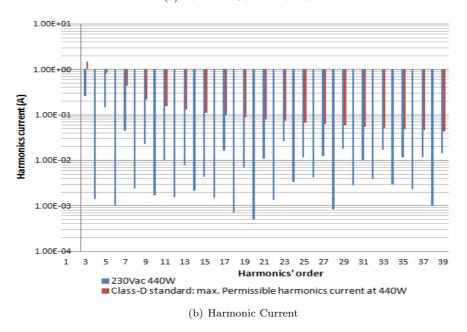

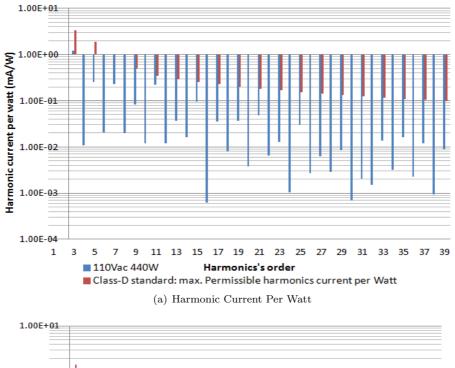

| 4.15 | Harmonic Current vs Class D Standard                                                                                                                                              | 55 |

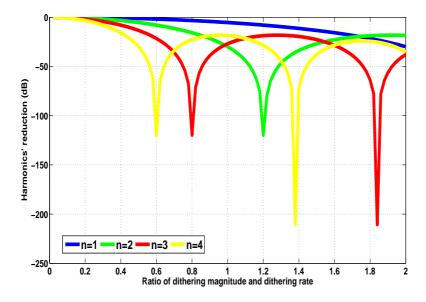

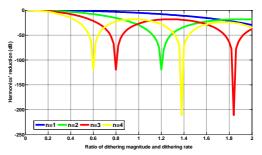

| 4.16 | Harmonics' reduction vs. dithering factor $\gamma$ when harmonics' order n changes from 1 to 4                                                                                    | 57 |

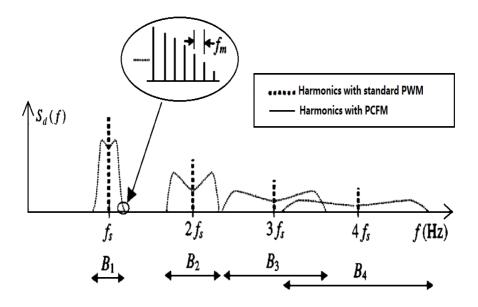

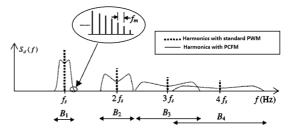

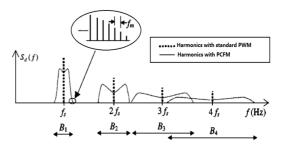

| 4.17 | Harmonics' spectrum comparison [67]                                                                                                                                               | 59 |

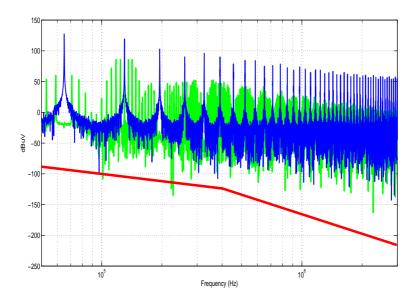

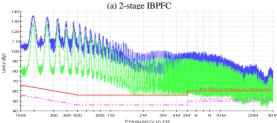

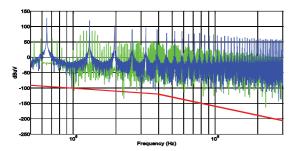

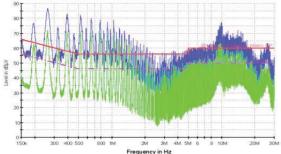

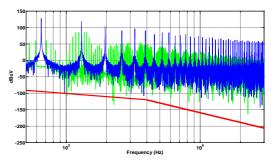

| 4.18 | Harmonics' spectrum comparison for frequency dithering PWM (green) and standard PWM (blue), the red line is the filter's attenuation characteristic                               | 60 |

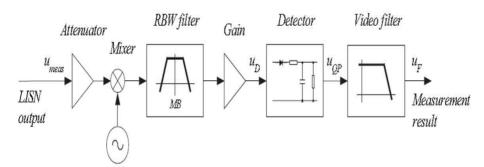

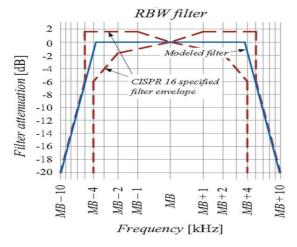

| 4.19 | Simplified heterodyne measurement chain and QP detection model of a test receiver[80]                                                                                             | 62 |

| 4.20 | Upper and lower envelope of the characteristic of the resolution bandwidth (RBW) filter as specified in CISPR 16 and filter characteristic used when modeling the RBW filter [80] | 62 |

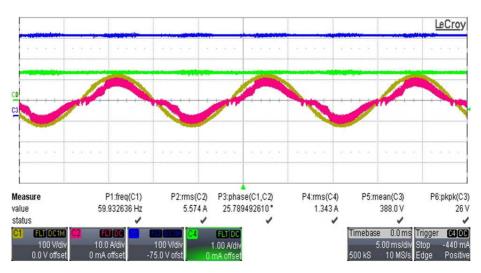

| 4.21 | Input voltage (yellow, C1) and current (red, C2);output voltage (blue, C3) and current (green, C4) waveforms of the proposed frequency dithering IBPFC                            | 63 |

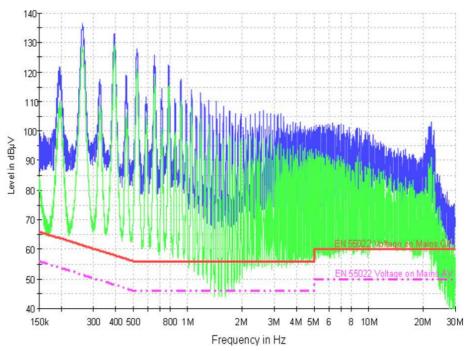

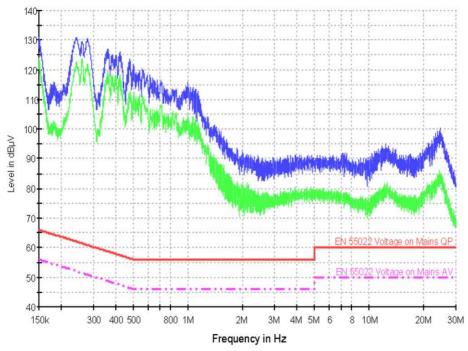

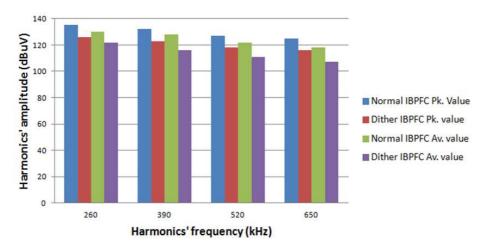

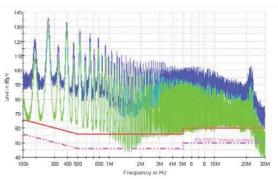

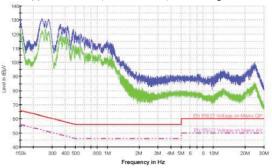

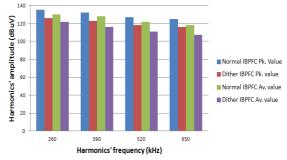

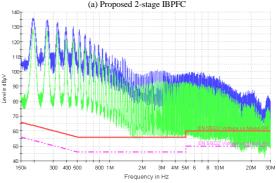

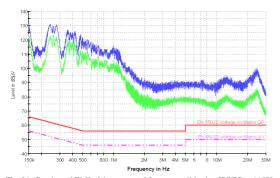

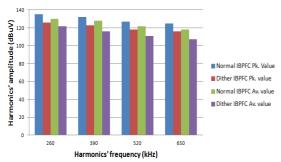

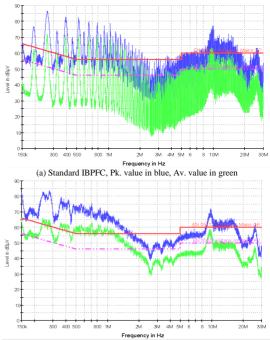

| 4.22 | Conducted EMI comparison of standard IBPFC and proposed frequency dithering IBPFC without filter at $110V_{ac}$ input and 1 over 8 peak power | 65 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.23 | Detailed EMI comparison of 4 highest harmonics in Fig.4.22                                                                                    | 66 |

| 4.24 | The schematic of the EMI filter                                                                                                               | 66 |

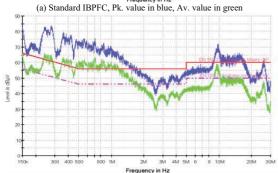

| 4.25 | Conducted EMI comparison of standard IBPFC and proposed frequency dithering IBPFC at $110V_{ac}$ and $1/8$ peak power with the same filter    | 67 |

| 5.1  | Simplified diagram of efficiency measurement set up                                                                                           | 70 |

| 5.2  | Accuracy analysis procedure                                                                                                                   | 71 |

| 5.3  | Measurement Accuracy Prediction                                                                                                               | 72 |

### **List of Tables**

| 1.1 | PFC Specification                                                                         |    |

|-----|-------------------------------------------------------------------------------------------|----|

| 2.1 | Comparison of five popular BPFC systems and the traditional Boost PFC system              |    |

| 3.1 | Dimensions of The Kool Mu E Cores from $Magnetics^{\circledR}$ 34                         |    |

| 4.1 | EMI Comparison of Critical Harmonics 64                                                   |    |

| 5.1 | Accuracy Specification of $N4L^{\textcircled{\$}}$ Precision Power Analyzer PPA5530[85] 7 | 'n |

### Chapter 1

### Introduction

### 1.1 Scope

The scope of this thesis is to present the results obtained in the Ph.D. project "High Efficiency PFC front-end for Class-D Amplifiers", performed by the author during the period from March 2009 through March 2012. Many of the scientific results obtained in the project have been or will be published in the form of conference papers and peer reviewed journal. The published and future published papers forming an integral part of this thesis are included in appendix [A1]-[A7].

The objective of this thesis is to supplement the already or future published information in [A1]-[A7] by placing the published papers in the context of the overall project and thereby present a more coherent and complete overview of the whole work and results obtained.

Furthermore, the author hopes that this thesis can serve as a small condensed "Designer's Theoretical Handbook" on key fundamental issues related to the design and optimization of high efficient PFC for audio applications.

2 Introduction

### 1.2 Background and Motivation

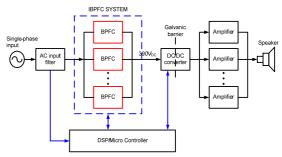

Due to the higher efficiency compared to linear audio amplifiers, the class-D amplifiers make it possible for more compact and high-power audio applications [1]. The power supply for the class-D amplifiers system from the AC mains is usually carried out in two stages (Fig.1.1): the single-phase main AC voltage is first converted into a DC voltage and then adapted to the load voltage level with a DC-DC converter with or without galvanic isolation. The simplest way of the rectification can be done by implementing unidirectional diode rectifier with DC capacitors smoothing of the output voltage (Fig.1.2(a)). Although this concept has its advantages of low complexity and high robustness, its disadvantages of relatively high effects of current distortion on AC mains and an unregulated output voltage directly dependent on the mains voltage level must be considered together. According to the guidelines to the harmonics current emission

Figure 1.1: Block diagram of typical power supply configuration for supplying Class-D amplifiers system from the AC mains

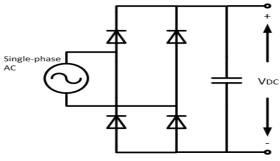

limitation standard EN61000-3-2[2], the main behavior of a power converter can be characterized in general by the power factor (PF) and the input current harmonic emissions. The conduction state of the passive rectifier shown in Fig.1.2(a) is essentially determined by the mains line-to-line voltages, whereby only two diodes carry current at the same time when the input voltage higher than the output voltage on the DC capacitor. This means that each diode of the positive and negative bridge carries current only for a very short period(fig.1.2(b)). Hence, the phase difference of input current and input voltage is huge, the PF is very low and the harmonic current emissions of input current is far above the EN61000-3-2 limitation. In order to avoid the low PF and high current harmonic emissions problems, the active PFC Converter must be built inside the rectifier system. Furthermore, for maintaining the natural advantage of high efficiency of class-D amplifiers, as its front-end, the PFC system is required to have an outstanding efficiency in a wide output power range.

(a) Passive single-phase diodes rectifier

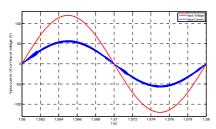

(b) Input voltage (green) and current (blue) waveforms

Figure 1.2: Passive single-phase diodes rectifier and its characteristic waveforms

### 1.3 Specifications

The specifications of the PFC converter investigated in this work (Table.1.1) have been compiled in collaboration with our industry partner. The PFC system comprises of a DC voltage output with the terminal voltage  $V_o$  equals to 390V and universal AC line voltage input  $V_{in}$  (85 $V \le Vin \le 265V$ ). An output peak power  $P_o$  of 3.5 kW is required. Moreover, the system is expected to achieved as high efficiency as possible.

Another important design parameter need to be defined in this project is the switching frequency  $f_s$ . The author selected  $f_s$  equals to 65kHz based on the consideration of system EMI optimization. Detailed analysis on switching frequency selection will be presented in Chapter 4 in this thesis.

4 Introduction

| Parameter                        | Value                | Comments                     |

|----------------------------------|----------------------|------------------------------|

| Output Power $P_o$               | $3.5~\mathrm{kW}$    | Maximum achievable power in  |

|                                  |                      | single-phase PFC converter   |

| Output voltage $V_o$             | $390V_{dc}$          | As required                  |

| Input Voltage $V_{in}$           | $85-265 \ V_{ac}$    | Universal line input         |

| Maximum Efficiency $\eta$        | ≥98%                 | At high line $230V_{ac}$     |

| Input Harmonic Current Emissions | EN61000-3-2, Class D | Measurement required to take |

|                                  |                      | under one eighth of the peak |

|                                  |                      | power                        |

| Switching Frequency $f_s$        | $65 \mathrm{kHz}$    | For better EMI performance   |

Table 1.1: PFC Specification

### 1.4 Project Objectives and Contributions

The primary objectives of this project regarding the selection and design of the single-phase PFC converter are:

- Converter peak efficiency > 98% at the high line operating condition  $(V_{in} = 230V)$ ;

- Converter efficiency > 90% under universal line input at peak power ( $P_o \le 3.5kW$ );

- High power density;

- Suggestions for cost-efficient EMI suppression.

The contributions of this work are:

- A overview on Bridgeless PFC converter topologies, includes a detailed comparison to judge which one should be the best suitable to fulfil the specifications in Table.1.1 (Chapter 2);

- An optimization for high efficient Two-Boost-Circuit BPFC converter based on high efficiency and high power density Boost inductor design (Chapter 3);

- A simplified EMI modelling process is used to predict the EMI performances of the BPFC converter (Chapter 4);

- A novel Interleaved BPFC(IBPFC) topology is proposed, the insight of EMI suppression versus the number of interleaved stages is investigated (Chapter 4);

- A multi-objective optimization design procedure (MDOP) is implemented to find the optimal parameters for the novel IBPFC system to achieve high efficiency, low EMI and high power density at the same time (Chapter 4);

- A detailed research on frequency dithering modulation based on its advantages and limitations is carried out for further reducing the EMI emissions of the novel IBPFC topology (Chapter 4).

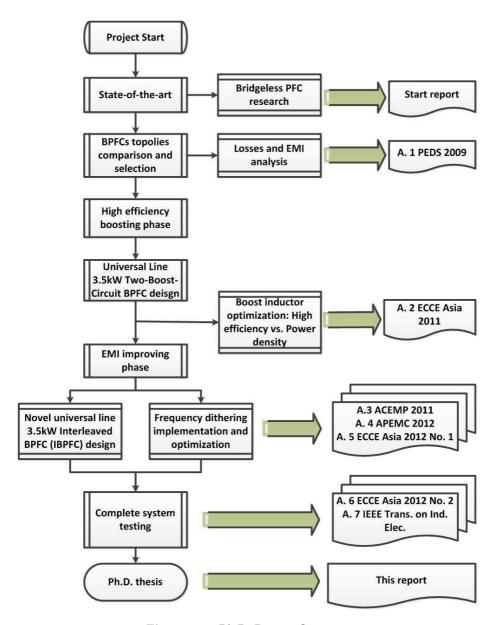

### 1.5 Project Plan and Content

A flow chart presents the work packages carried out in the course of this Ph.D. project (Fig.1.3). Six conference papers have been published and one journal has been submitted for peer reviewed. Additionally, the flow chart also illustrates how the publications relate to the key parts of the Ph.D. project.

#### 1.6 Thesis Structure

The structure, organization and content of this Ph.D. thesis in the flowing chapters are presented (Fig.1.4). The conference papers and journal paper in [A1]-[A7] form an integral part of this Ph.D. thesis and are appended. Because the purpose of this thesis is to complement the already and future published papers by providing a condensed and coherent presentation of the overall project and its results, special focus will be devoted to presenting a coherent derivation of the key fundamental theoretical aspects of this project.

6 Introduction

Figure 1.3: Ph.D. Project Overview

1.6 Thesis Structure 7

Figure 1.4: Ph.D. Thesis Structure

### Chapter 2

### State of the Art

As it has been emphasized in Chapter 1, the major task of the PFC design in this work is efficiency optimization. However, due to the traditional single-phase PFCs usually have full-wave rectifiers in the input side, which contribute a large part of the semiconductor losses; recently, a new PFC family named Bridgeless PFCs (BPFCs) has been proposed to achieve higher efficiency by removing the full-wave AC rectifiers in front. Therefore, in this work, the author mainly interested in the high efficiency BPFC topologies.

However, may the BPFC topologies be suitable for this work, is unclear. Moreover, beyond their high efficiency characteristics, the electromagnetic interference (EMI) of the BPFCs need to be weighed as well.

The purpose of this Chapter is to present an overview of the high performance state-of-the-art BPFC converters. The recent published literatures primarily in the form of journal papers and conference papers has been researched and analyzed. Main focus has been devoted to compare and evaluate their efficiency and EMI together and to select the most proper BPFC topology to meet the overall specifications of this project in Chapter 1 (Table.1.1).

Furthermore, for each compared BPFC solution, a short description of the operation principle is given, too.

10 State of the Art

In additional, the paper published as part of this project is also included in the state-of-the-art analysis (appendix A1).

### 2.1 Derivation of Bridgeless PFC Converters

The idea of the basic Bridgeless PFC (BPFC) converters (Fig.2.1(a)) goes back to eighties [3]. Comparing to the traditional most popular Boost type PFC (Fig.2.1(b)), this smart concept improves PFC's efficiency by removing the bridge rectification system in front of it. During the last decades, researches of the BPFC converters were taken not only to analyse the operation principles but also to investigate its performances in different aspects [4–26]. With the

Figure 2.1: Basic BPFC and Conventional Boost PFC Topologies

increasing demands on energy saving, in recent years the implement of BPFC system have became more and more attractive. The collection below lists five classic published BPFC solutions for high efficiency applications. And in each selected BPFC converter, the brief descriptions of the topology and its merits and disadvantages are provided.

### 2.2 BPFC Topologies Overview

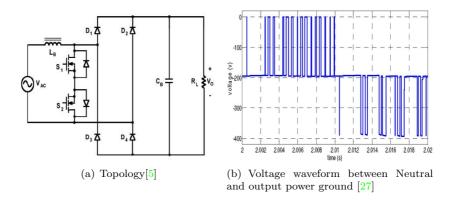

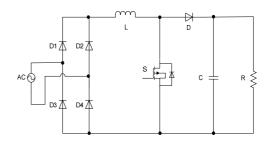

### 2.2.1 Basic BPFC System

The basic BPFC system shows in Fig.2.1(a). Compare to the conventional Boost PFC (Fig.2.1(b)), the most important advantage of it is that it doesn't need four

line frequency diodes operating as voltage rectifier.

Operation principles: Due to the basic BPFC works symmetrically, only half of the AC line period is considered here. For example, in the positive AC line period, when MOS  $S_1$  is on, the Boost inductor is charged by  $S_1$  and the body diode of MOS  $S_2$ . When MOS  $S_1$  is off, the Boost inductor is discharged through Boost diode  $D_1$  and the body diode of MOS  $S_2$ .

#### Merits:

Compared to the Boost PFC, the basic BPFC has one less line frequency diode in current flowing path, which reduces the semiconductor losses and enhance the system efficiency.

#### Disadvantages:

However, compare to the conventional Boost PFC, the output ground of basic BPFC has high frequency voltage pulses in the negative AC line period due to it doesn't connect to the positive terminal of AC source directly (Fig.2.2). These voltage pulses can induce high CM EMI noises which may affect system stability and bring difficulties to EMI filter design.

Figure 2.2: Voltage Waveforms Between Neutral and Output Power Ground [27]

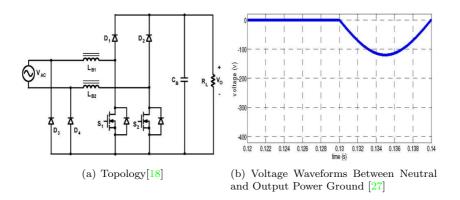

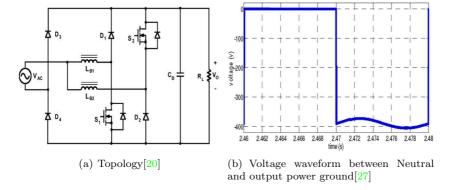

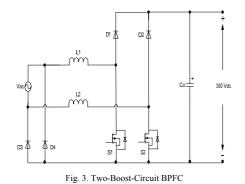

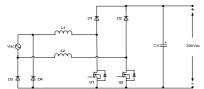

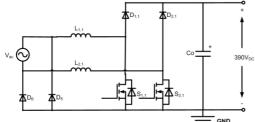

#### 2.2.2 BPFC with Two Boost Circuits

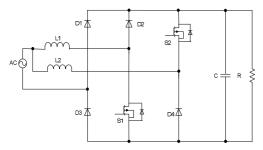

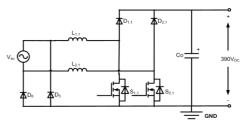

The Two-Boost-Circuit BPFC in Fig.2.3(a) is an EMI improved version of basic BPFC.

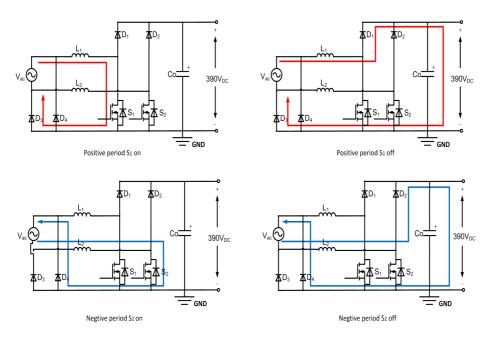

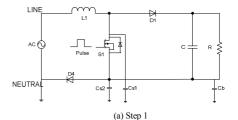

#### Operation Principles:

Due to the Two-Boost-Circuit BPFC works symmetrically, only half of the AC line period is considered here. For example, in the positive AC line period, when

12 State of the Art

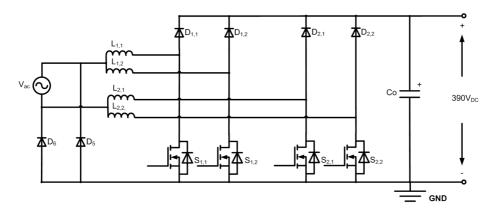

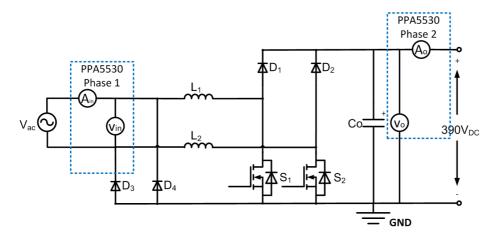

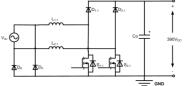

Figure 2.3: Two-Boost-Circuit BPFC

MOS  $S_1$  is on, the Boost inductor is charged by  $S_1$  and line frequency diode  $D_4$ . When MOS  $S_1$  is off, the Boost inductor is discharged through Boost diode  $D_1$  and the line frequency diode  $D_4$ .

#### Merits:

By implementing two line frequency diodes  $D_3$  and  $D_4$ , the output ground is connected to the terminals of AC mains directly in the whole AC line period, which stabilizes voltage potential of output ground and reduces CM EMI generation (Fig.2.3(b)). In additional, instead of using the relatively high forward voltage MOS's body diodes as a part of the current flowing path, using normal line frequency diodes  $D_3$  and  $D_4$  helps to improve system efficiency.

#### Disadvantages:

Due to the two extra line frequency diodes  $D_3$  and  $D_4$  and the one extra Boost inductor  $L_{B2}$ , this topology has higher cost and volume than the basic BPFC.

In publication [25], a 1kW universal line Two-Boost-Circuit BPFC is presented. The output DC voltage is 400V. The maximum measured efficiency reaches 97% at  $220V_{ac}$  input and 600W.

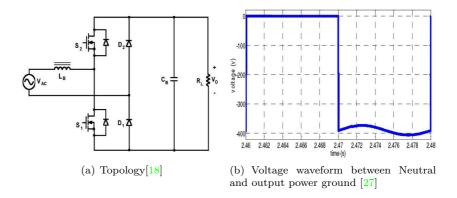

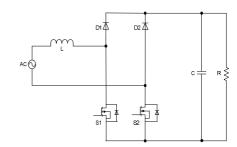

#### 2.2.3 Basic BPFC with Bidirectional Switch

Fig.2.4(a) is an modification of Two-Boost-Circuit BPFC (Fig.2.3(a)) by disconnecting the sources of MOSs  $S_1$  and  $S_2$  from output ground.

Operation Principles:

Figure 2.4: Basic BPFC with Bidirectional Switch

Due to the BPFC with bidirectional switch works symmetrically, only half of the AC line period is considered here. For example, in the positive AC line period, when MOS  $S_1$  is on, the Boost inductor is charged by  $S_1$  and the body diode of MOS  $S_2$ . When MOS  $S_1$  is off, the Boost inductor is discharged through Boost diode  $D_1$  and  $D_4$ .

#### Merits:

By removing one Boost inductor  $L_{B2}$ , this topology has lower cost and volume than the Two-Boost-Circuit BPFC in Fig.2.3(a).

#### Disadvantages:

It should be noticed in Fig.2.4(a), all the diodes are fast recovery diodes, however, in Fig.2.3(a), only  $D_1$  and  $D_2$  are fast recovery diodes,  $D_3$  and  $D_4$  are line frequency diodes because each of them conducts in half of the AC line period. Normally, at the same voltage and current rating, the forward voltage drop of the line frequency diodes are lower than the fast recovery diodes, which means, with the same forward current, the line frequency diodes has lower conduction losses than fast recovery diodes. Therefore, if other semiconductors are the same, the total semiconductors' conduction losses of the Two-Boost-Circuit can be expected lower than the basic BPFC with bidirectional switch.

Furthermore, compare to the Two-Boost-Circuit BPFC and basic BPFC, the output ground of basic BPFC with bidirectional switch has high frequency voltage pulses in the whole AC line period due to it doesn't connect to the terminals of AC mains directly all the way (Fig.2.4(b)). These voltage pulses will induce high CM EMI noises and bring difficulties to EMI filter design. Besides, the BPFC in Fig.2.4(a) requires a complex control and drive circuit, due to the sources of MOSs do not connect to the output ground.

14 State of the Art

#### 2.2.4 Pseudo Totem-pole BPFC

Pseudo totem-pole BPFC (Fig.2.5(a)) can be considered as another modification of Two-Boost-Circuit BPFC (Fig.2.3(a)).

Figure 2.5: Pseudo Totem-pole BPFC

#### Operation principles:

Due to the Pseudo totem-pole BPFC works symmetrically, only half of the AC line period is considered here. For example, in the positive AC period, Boost inductor  $L_{B1}$  is charged by MOS  $S_1$  and diode  $D_4$ , and discharged through diodes  $D_1$  and  $D_4$ . Therefore, the same as Fig.2.3(a), diode  $D_1$  should be the fast recovery diode and diode  $D_4$  is the normal line frequency diode due to it conducts in the whole positive AC line period.

#### Merits:

By implementing two line frequency diodes  $D_3$  and  $D_4$ , the voltage positional of output ground is stabilized in the whole AC period which reduces CM EMI generation (Fig.2.5(b)).

#### Disadvantages:

However, this BPFC also requires a complex control and drive circuit, due to the source of MOS  $S_2$  does not connect to the ground. Besides, comparing to basic BPFC (Fig.2.1(a)), the Pseudo totem-pole BPFC asks for one more Boost inductor, which increase the system volume.

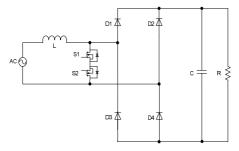

#### 2.2.5 Totem-pole BPFC

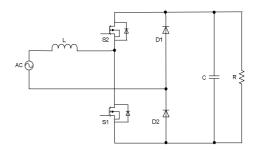

Fig.2.6(a) is a modification of Basic BPFC (Fig.2.1(a)). by exchanging the position of Boost diode  $D_1$  and MOS  $S_2$ .

Figure 2.6: Totem-pole BPFC

#### Operation Principles:

Due to the Totem-pole BPFC works symmetrically, only half of the AC line period is considered here. For example, during the positive AC period, when MOS  $S_1$  and diode  $D_1$  conduct, the Boost inductor is charged. When MOS  $S_1$  turns off, the Boost inductor is discharged through body diode of MOS  $S_2$  and  $D_1$ .

#### Merits:

Due to the output ground is directly connected to the terminal of AC source by  $D_1$  in the positive line period and the terminal of Boost inductor by the body diode of  $S_1$  in the negative line period, the CM EMI generation problem from basic BPFC can be solved.

#### Disadvantages:

However, the reverse-recovery performance of the body diodes of the switches makes continuous current mode (CCM) operation of this BPFC (Fig.2.6(a)) impractical. Furthermore, compare to the basic BPFC, although they have the same semiconductor numbers in the current flowing path, in the Totem-pole BPFC, each MOS's body diode conducts in the switching frequency. For normal MOSs, their body diodes are very slow, which are not good for fast recovery application. Additionally, the Totem-pole BPFC requires a complex control and drive circuit, due to the source of MOS  $S_2$  doesn't connect to ground.

16 State of the Art

In publication [28], an optimized 500W universal line Totem-pole BPFC is presented. The output DC voltage is 380V. The maximum measured efficiency reaches 96.8% at  $220V_{ac}$  input and 500W. In publication [29], a 800W universal line interleaved Totem-pole BPFC is presented. The output DC voltage is 400V, the maximum measured efficiency reaches 97.8% at 264  $V_{ac}$  input and 800W.

#### 2.3 Summary of State-of-the-art Analysis

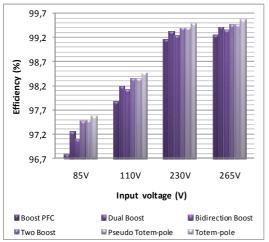

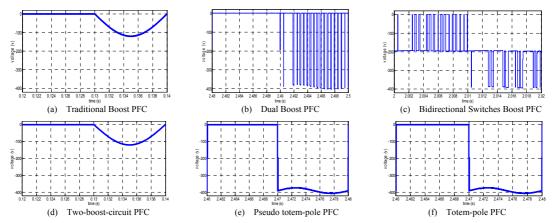

In this Chapter, the derivation of BPFC is introduced firstly. And then, five popular BPFC systems are selected for detailed comparison. Their operation principles, advantages and disadvantages are analysed. The summary of their performances are given in Table.2.1. Where, the type and number of semiconductors operating in each half line period are shown, the system peak efficiency and EMI performance are highlighted.

According to the information from Table.2.1, the conclusions can be drawn as below:

- 1. In these classic BPFC topologies, very few of them are verified by experiments;

- 2. The designs of Two-Boost-Circuit BPFC and Totem-pole BPFC are achieved only in low and medium power and their peak efficiency are 97% and 97.8% respectively;

- 3. There are lack of researches based on high power universal line BPFC design and optimization;

- 4. The Two-Boost-Circuit BPFC can be a very useful topology for this work due to it has the possibility to run in a high power level with good efficiency, relatively lower EMI and less complex control and gate drive systems.

Table 2.1: Comparison of five popular BPFC systems and the traditional Boost PFC system

| Topology                   | Inductor  | lo.oN          | lo.of No.of        | No.of | lo.oN             | Total | Power Level    | CM EMI | Peak   |

|----------------------------|-----------|----------------|--------------------|-------|-------------------|-------|----------------|--------|--------|

|                            | Opera-    | $D_F{}^{ m a}$ | $D_L^{\mathrm{b}}$ | MOS   | $D_{MOS}^{c}$ No. | No.   |                |        | Effi-  |

|                            | tion      |                |                    |       |                   |       |                |        | ciency |

| Boost DEC                  | Charge    | 0              | 2                  | 1     | 0                 | 3     | High           | 7000   | p      |

| DOOR I L.                  | Discharge | 1              | 2                  | 0     | 0                 | 2     | 11811          | noog   |        |

| Besis BDEC                 | Charge    | 0              | 0                  | 1     | 1                 | o c   | Modium         | 4000   |        |

| Dasic Di I                 | Discharge | 1              | 0                  | 0     | 1                 | 1     | IMEMINI        | poor   |        |

| Two Boost Cinomit BDEC     | Charge    | 0              | 1                  | 1     | 0                 | ٠     | High           | 7000   | 2020   |

| I WO-DOOSG-CHICAIG DI F.C. | Discharge | 1              | 1                  | 0     | 0                 | 1     | 11811          | മറ്റെ  | 0/16   |

| Basic BPFC with            | Charge    | 0              | 0                  | 1     | 1                 | ·     | Modium         | 3000   |        |

| Bidirectional Switch       | Discharge | 2              | 0                  | 0     | 0                 | 1     | Mediaiii       | poor   | ı      |

| Penido totom nolo BPFC     | Charge    | 0              | 1                  | 1     | 0                 | 6     | Modium         | poox   |        |

| r seado cotemi-pore Di FO  | Discharge | 1              | 1                  | 0     | 0                 | 1     | Medium         | മറാള   | ı      |

| Totom nole BDEC            | Charge    | 0              | 1                  | 1     | 0                 | 0     | I our Modium   | 5000   | 208 20 |

| Totall-pole Di I           | Discharge | 0              | 1                  | 0     | 1                 | 1     | TOW-INTEGRITIE | മറാള   | 0/0.16 |

<sup>a</sup>  $D_F$  means fast recovery diode <sup>b</sup>  $D_L$  means line frequency diode <sup>c</sup>  $D_{MOS}$  means the body diode of MOS <sup>d</sup> Symbol '-'means no data available

## Chapter 3

# Design of the High Efficient BPFC - Boost Inductor Optimization

In this Chapter, a useful design procedure is presented for Two-Boost-Circuit Bridgeless PFC (BPFC) converter based on Boost inductor optimization, which can be utilized to gain high efficiency and high power density at the same time.

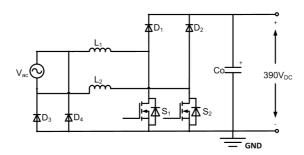

#### 3.1 Topology Basic Operation

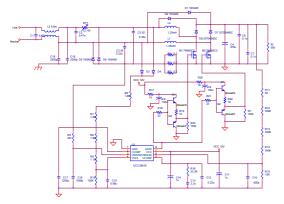

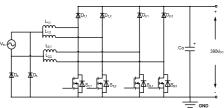

Chapter 2 discussed the basic performances of five BPFC topologies. These topologies can be expected to have higher efficiency than traditional Boost PFC due to the reduction of semiconductor numbers in current flowing path. According to its conclusion, the Two-Boost-Circuit BPFC (Fig.3.1) shows better performances than others due to system efficiency improvement without inducing EMI problems.

The Two-Boost-Circuit BPFC has a symmetric structure. During the positive AC line, diode  $D_1$  operates when MOS  $S_1$  turns off, and Boost inductor  $L_1$

Figure 3.1: Two-Boost-Circuit BPFC with good efficiency and low conducted EMI

discharges, meanwhile gives energy to load. When MOS  $S_1$  turn on, Boost inductor is charged, and diode  $D_1$  is off. The output capacitor discharges and transfers energy to load. Line frequency diode  $D_3$  returns current from output ground to neutral and stabilize its voltage potential. In the negative AC line, the BPFC works symmetrically. Its operation principles are shown in Fig. 3.2. And it is easy to see that the BPFC in Fig.3.1 is equal to two normal Boost PFCs, one works in positive line period and the other works in negative line period.

Figure 3.2: Operation principles of the Two-Boost-Circuit BPFC

In our application, the BPFC works at 3.5kW power level. In order to reduce the core losses from Boost inductors, the BPFC runs in the continuous current mode (CCM). Because the average energy stored in Boost inductors in each switching cycle is approximately zero in steady states, the input and output transfer function of the selected Two-Boost-Circuit BPFC (Fig.3.1) is the same as normal Boost PFC, which can be expressed as:

$$V_o = \frac{\sqrt{2}V_{in,rms}|\sin(2\pi f_L t)|}{1 - d(t)}$$

(3.1)

Where  $V_o$  is output voltage,  $V_{in,rms}$  is the input RMS voltage,  $f_L$  is line frequency and d(t) is the instantaneous switch on duty cycle.

#### 3.2 High Efficiency Boost Inductor Design

The Boost inductor design is tough and important for any Boost type PFC converters, due to a good design can reduce not only the losses but also the volume of the system. In order to optimize the Boost inductor and improve the efficiency in the Two-Boost-Circuit BPFC, the questions below should be taken into considerations at the very beginning:

- 1. Is there any reasonable region for Boost inductance selection?

- 2. How to choose windings and cores to minimize the magnetic losses while still maintaining high power density?

By answering these questions, in this Section, a useful balance between efficiency and power density of the Boost inductor design in a Two-Boost-Circuit BPFC is achieved through using the optimized design procedure.

#### 3.2.1 Conventional Boost Inductor Design Procedure

Generally speaking, it is typical to design the Boost inductor based on its inductance and average current. It is well known that the peak inductor current ripple limitation and the inductor operating condition determine the minimal value of the Boost inductance together [30].

Since the worst-case peak inductor current occurs at low line and maximum load, which is:

$$\hat{I}_{L,max} = \hat{I}_{in,max} + 0.5\hat{I}_{ripple,max} \tag{3.2}$$

Where, 'max'means maximum value and symbol means the peak value. Therefore,  $\hat{I}_{L,max}$  means the peak value of maximum inductor current,  $\hat{I}_{in,max}$  means the peak value of maximum input current, and  $\hat{I}_{ripple,max}$  means the peak value of maximum inductor ripple current.

Many design cookbooks claims that a good compromise between the peak inductor current ripple and its peak current is to allow a 20% current radio. Assuming:

$$\hat{I}_{ripple,max} = 0.2\hat{I}_{in,max} \tag{3.3}$$

Hence, the minimal inductance to meet the peak current ripple limitation can be calculated as:

$$L_{min1} = \frac{\hat{V}_{in,min} D_{worst}}{\hat{I}_{ripple,max} f_s}$$

(3.4)

Where, 'min'means minimal value and ' $D_{worst}$ 'is the worst-case on duty ratio which is 0.69.

Since the BPFC in this work is designed to operate in CCM mode, the inductance should also be big enough to avoid the inductor current dropping to zero during its discharge period in each switching cycle. So, at any switching period:

$$I_{L,min}(n) = I_{in}(n) - 0.5I_{ripple,max}(n) > 0 \downarrow$$

$$\frac{2P_{in}}{\hat{V}_{in}} \sin(\frac{n}{N}\pi) > \frac{1}{2} \frac{\hat{V}_{in}}{L} \sin(\frac{n}{N}\pi) (1 - \frac{\hat{V}_{in}}{V_o} \sin(\frac{n}{N}\pi)) T_s \downarrow$$

$$L > \frac{\hat{V}_{in}^2 T_s \eta}{4P_o} \left( 1 - \frac{\hat{V}_{in}}{V_o} \sin(\frac{n}{N}\pi) \right)$$

(3.5)

Where, 'N'means the total number of sample points, 'n'means sample step,  $T_s$  is switching period, ' $\eta$ 'means system efficiency.

The boost inductor L in Eq.3.5 reaches maximum value when:

$$\sin(\frac{n}{N}\pi) \to 0 \tag{3.6}$$

Hence,

$$L_{min2} > \frac{\hat{V}_{in}^2 T_s \eta}{4P_o} \tag{3.7}$$

According to Eqs.(3.4) and (3.7), the minimal Boost inductance should satisfy the following condition:

$$L_{min} > \{L_{min1}, L_{min2}\}_{max}$$

(3.8)

When the selection of inductance is ready, suitable cores and windings can be chosen based on the maximum DC and RMS current flowing through the inductor. Normally, the core and winding selection processes can be quickly done by following the guideline provided by the magnetic manufacturers, such as: [31–33].

It is obviously that using the inductor design method above will lead to a quick design and short the development period. However, this design method almost come from experiences, whether it have been optimized is doubtable. For example: considering the amount of input current ripple, on one hand, allowing more current ripple will reduce the inductance, this may reduce the size of the inductor due to the inductor's volume is in direct proportion to its inductance. However, on the other hand, it will increase the input line noise, ripple current in the Boost inductors and the peak current through the diodes and MOSs. These may not only increase the difficulties of EMI filter design, but also lead to higher core losses, AC winding losses and higher semiconductor losses. Furthermore, the reason for using the 20% peak to peak ripple to peak current ratio is unclear.

Because the Boost PFC inductor design has been ambiguous for long, the discussion below will firstly focus on how to improve the system efficiency by optimizing the Boost inductance. And then, the detailed study on system volume optimization will be presented. In order to avoid including too much critical issues at one time, the EMI is not discussed in this Chapter.

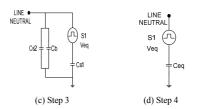

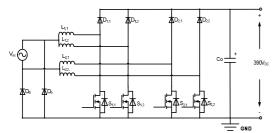

#### 3.2.2 Optimized Design Procedure

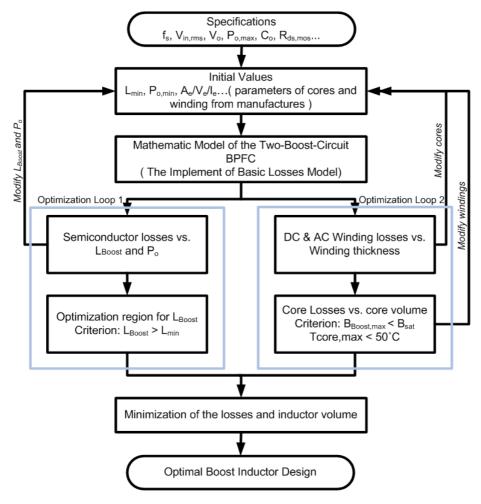

The optimization procedure below (Fig.3.3) is carried out based on high efficiency Two-Boost-Circuit BPFC in Fig.3.1 operating in CCM. And basically any Boost type PFCs working in CCM could be considered in this procedure as well.

In the optimization, the switching frequency is limited to 65kHz. The start point of this procedure is the specifications definition, which including all the fixed critical parameters in the main circuit. For example: input and output voltages, output peak power, output capacitors, inner parameters of the semiconductors and so on. Next, the important initial starting values of the BPFC variables are

**Figure 3.3:** Optimization procedure of inductor design in CCM for Two-Boost-Circuit BPFC with balance of efficiency and power density

set. Such as: minimal CCM Boost inductance  $L_{min}$ , starting minimal output power  $P_{o,min}$ , parameters of cores and windings from manufactures. After finishing defining all the specifications and initial values, the mathematical BPFC model will be used to calculate the RMS and average currents flowing through all the components in the circuit, finally semiconductor losses and inductor losses can be predicted.

There are two inner optimization loops in the procedure. Inner optimization loop 1 seeks the characteristics of semiconductor losses versus Boost inductance

and output power, which will give a most suitable region of Boost inductance at certain power level. And inner optimization loop 2 gets a compromise of volume and efficiency of the inductor. Both of the two optimization loops will be explained in detail in the later sections. The optimal design can be realized by running optimization loop 1 and 2 together.

#### 3.2.3 Mathematical Modelling

In order to predict the performances of Boost inductors, the mathematical model should be able to show the RMS and average currents of the BPFC for calculating losses and choosing magnetic components. In the derivations below, the normalization has been taken in order to make the modelling process more clear. For more details please refers to Appendix A.2.

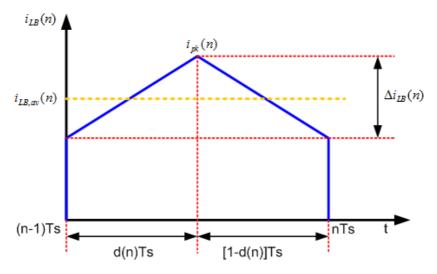

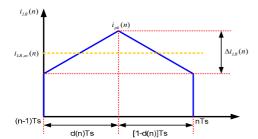

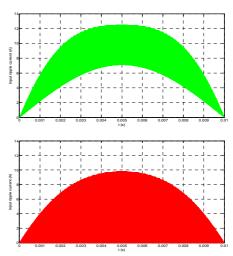

Figure 3.4: Boost inductor current waveform in a switching cycle in CCM

Starting from the Boost inductor, its current waveform during a switching cycle can be approximated as in Fig.3.4. The normalized average Boost inductor current in the nth switching cycle is:

$$i_{LB,av,n}(n) = |i_{in}(n)|/I_o = \hat{I}_{in,n} |\sin(2\pi n T_s/T_L)|, n = 1, \dots, N$$

(3.9)

Where, subscript n means normalized, subscript av means average and  $T_L$  is the AC line period.

The current ripple in Boost inductor in the nth switching cycle is determined

as:

$$\Delta i_{LB,n}(n) = \frac{|v_{in}(n)|}{I_o L_B(n)} d(n) T_s$$

(3.10)

$$=\frac{|v_{in,n}(n)|(1-|v_{in,n}(n)|)}{L_{B,n}}$$

(3.11)

Where, d is the switching on duty ratio. In CCM mode, its discrete time function is:

$$d(n) = 1 - \frac{|v_{in}(n)|}{V_o} = 1 - |v_{in}(n)|$$

(3.12)

And,

$$L_B = L_{B0} \frac{A_{L,effi}}{A_{L,0}}, A_{L,effi} = f(Mi_{in})$$

(3.13)

$L_B$  is the Boost inductance with DC bias. It is a function of number of turns M and input current  $i_{in}$  due to the DC magnetizing force.  $A_{L,0}$ , is the initial nominal inductance, and  $A_{L,effi}$  is the nominal inductance with DC bias which can be calculated based on the data sheet of the core. For example, reference [34] shows the DC bias performance of Kool Mu cores from  $Magnetics^{\textcircled{\$}}$ .

The relevant RMS and average currents for Boost inductor and semiconductor losses calculations under CCM in the nth switching cycle are listed below:

$$i_{LB,rms,n}(n) = \frac{|I_{in}(n)|}{I_o} \sqrt{1 + \frac{1}{3} \left(\frac{\Delta i_{LB}(n)}{2i_{in}(n)}\right)^2}$$

$$= \sqrt{i_{in,n}(n)^2 + \frac{\Delta i_{LB,n}(n)^2}{12}}$$

(3.14)

$$i_{S1,rms,n}(n) = \frac{|I_{in}(n)|}{I_o} \sqrt{1 + \frac{1}{3} \left(\frac{\Delta i_{LB}(n)}{2i_{in}(n)}\right)^2} \sqrt{d(n)}$$

$$= \sqrt{d(n) \left(i_{in,n}(n)^2 + \frac{\Delta i_{LB,n}(n)^2}{12}\right)}$$

(3.15)

$$i_{D1,av,n}(n) = (1 - d(n)) \frac{|i_{in}(n)|}{I_o} = (1 - d(n))|i_{in,n}(n)|$$

(3.16)

$$i_{D3,av,n}(n) = \frac{|i_{in}(n)|}{I_o} = |i_{in,n}(n)|$$

(3.17)

Where, subscript av means average.

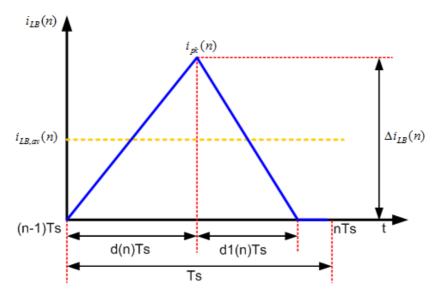

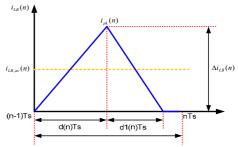

It should be noticed that even in the CCM condition, around the zero crossing of the line voltage, during a few switching cycles, the BPFC operates in DCM mode inevitably. The DCM periods are also taken into consideration during the calculation in order to obtain a more precise prediction.

The CCM and DCM boundary condition happens when:

$$i_{in,n}(n) = 0.5\Delta \hat{i}_{LB,n}(n)$$

(3.18)

Figure 3.5: Boost inductor current waveform in a switching cycle in DCM

The same as the previous procedure, in DCM operations, the current waveform of Boost inductor during a switching cycle can be approximated as in Fig.3.5. The normalized average Boost inductor current in the nth switching cycle is the same as Eq.(3.9).

In DCM condition, MOSFET's duty ratio is:

$$d(n) = \sqrt{\frac{2(1 - |v_{in,n}(n)|)|i_{in,n}(n)|}{|v_{in,n}(n)|}} L_{B,n}$$

(3.19)

And  $d_1$  is the conduction duty ratio of the Boost diodes:

$$d_1(n) = \sqrt{\frac{2|v_{in,n}(n)i_{in,n}(n)|}{(1-|v_{in,n}(n)|)}} L_{B,n}$$

(3.20)

The  $\hat{i}_{LB,n}$  is the normalized peak inductor current in DCM.

$$\hat{i}_{LB,n}(n) = \sqrt{|i_{in,n}(n)| \frac{2|v_{in,n}(n)|(1-|v_{in,n}(n)|)}{L_{B,n}}}$$

(3.21)

The relevant RMS and average currents for Boost inductor and semiconductor losses calculations under DCM in the nth switching cycle are listed below:

$$i_{LB,rms,n}(n) = \sqrt{\frac{d(n) + d_1(n)}{3}} \hat{i}_{LB,n}(n)$$

(3.22)

$$i_{S1,rms,n}(n) = \hat{i}_{LB,n}(n)\sqrt{\frac{d(n)}{3}}$$

(3.23)

$$i_{D1,av,n}(n) = d_1(n)\frac{\hat{i}_{LB,n}(n)}{2}$$

(3.24)

$$i_{D3,av,n}(n) = \frac{i_{in}(n)}{I_o} = |i_{in,n}(n)|$$

(3.25)

The corresponding normalized RMS and average currents during a half line period are as below:

$$I_{X,rms,n} = \sqrt{\frac{1}{N'} \sum_{n=1}^{N'} i_{X,rms,n}(n)^2}$$

(3.26)

$$I_{Y,av,n} = \frac{1}{N'} \sum_{n=1}^{N'} i_{Y,av,n}$$

(3.27)

Where, X symbolizes MOSs and Boost inductors and Y represents Boost diodes and return diodes. N' is the number of sampling data in half line period.

#### 3.2.4 Inductance vs. Semiconductor Losses

In this section, the insight of Boost inductance versus semiconductor losses is presented. It shows the method to evaluate the system efficiency affected by Boost inductance and gives the most suitable region for Boost inductance selection.

#### 3.2.4.1 Semiconductor Losses

The basic losses model is implemented in this section to predict the semiconductor losses. The key semiconductors' data of the BPFC are:

- 1. MOSs:IPW60R045CP from Infineon®

- 2. Boost diodes:STPSC1206 SiC diode from  $ST^{(\mathbb{R})}$

- 3. Current return diodes: STTH6004W from  $ST^{\mathbb{R}}$

For all calculations and measurements in this Chapter, a reference ambient temperature ( $T = 25^{\circ}C$ ) has been used.

MOSFET Losses The calculation of the power dissipated in the switches considers two different losses mechanisms: conduction losses and switching losses. The RMS currents through the switches determine the respective conduction losses.

According to Eq.(3.26), in half line period, the switch generates the total conduction losses:

$$P_{Rds} = (I_{S1,rms,n}I_o)^2 R_{S1} (3.28)$$

Where  $R_{S1}$  is the on resistance of MOS.

The calculation of the switching losses is more complex, since it not only depend on the selected power MOS's intrinsic parameters, but also the parasitic parameters (e.g. PCB stray inductances). In this thesis, all the switches operate in hard switching mode, the accrue switching loss is due to high current and high voltage being present in the device simultaneously for a short period. It can be calculated approximately as below [35]:

$$P_{sw} = \frac{V_{DS} \cdot I_{DS}}{2} \times \frac{t_2 + t_3}{T_s} \tag{3.29}$$

$$t_2 = (C_{GS} - C_{RSS}) \frac{V_{GS,Miller} - V_{TH}}{I_{G2}}$$

(3.30)

$$I_{G2} = \frac{V_{DRV} - 0.5 \cdot (V_{GS,Miller} + V_{TH})}{R_{gate}}$$

$$(3.31)$$

$$t_3 = C_{RSS} \cdot \frac{V_{DS}}{I_{G3}} \tag{3.32}$$

$$t_{3} = C_{RSS} \cdot \frac{V_{DS}}{I_{G3}}$$

$$I_{G3} = \frac{V_{DRV} - V_{GS,Miller}}{R_{gate}}$$

$$(3.32)$$

Where,  $R_{gate}$  is gate resistor,  $V_{GS,Miller}$  is the miller plateau level,  $V_{TH}$  is the threshold voltage,  $V_{DRV}$  is gate drive voltage,  $C_{GS}$  is the capacitor formed by the overlap of the source and channel region by the gate electrode,  $C_{RSS}$  is the capacitance from gate to drain.

Therefore, the total losses dissipate on MOS is:

$$P_{MOS,tot} = P_{Rds} + P_{sw} (3.34)$$

**Diode Losses** In the BPFC prototype, both of the Boost diode and line frequency diode are implemented with Silicon carbide (SiC) diodes. Their switching losses can be neglected due to they do not suffer from reverse recovery.

According to Eq.(3.27), in half line period, the conduction losses of Boost diode and line frequency diode are:

$$P_{DB,con} = (I_{DB,av,n}I_o)V_{F,DB} \tag{3.35}$$

$$P_{DL,con} = (I_{DL,av,n}I_o)V_{F,DL} \tag{3.36}$$

Where, DB means Boost diode and DL means line frequency diode,  $V_{F,DB}$  and  $V_{F,DL}$  are the forward voltages of Boost diodes and line frequency diodes.

#### 3.2.4.2 Inductance Optimization vs. Semiconductor Losses

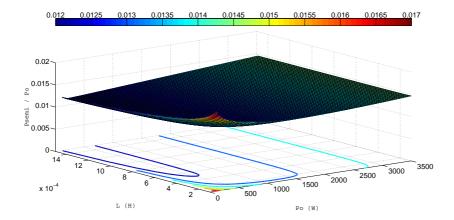

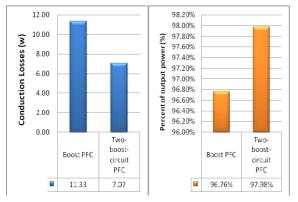

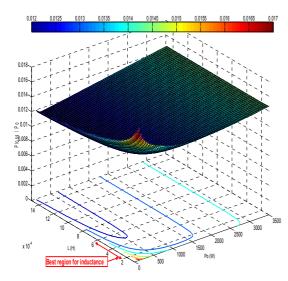

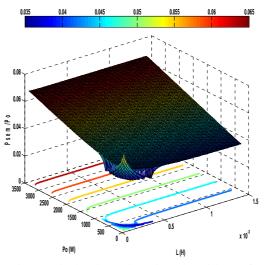

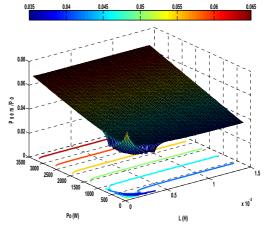

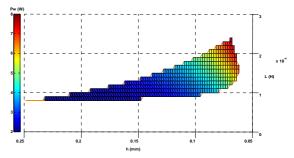

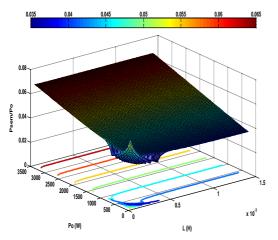

Fig.3.6 displays the semiconductor losses ratio (including conduction and switching losses) in function of the output power and Boost inductance when the input voltage is  $220V_{ac}$  and output voltage is 390V. From Fig.3.6, it can be seen:

Figure 3.6: Semiconductor Losses Ratio vs. Boost Inductance and Output Power

- For constant output power, considering the Boost inductance starts to increase from CCM limitation value  $L_{min}$ . At the beginning, semiconductor losses ratio reduces significantly, while the Boost inductance increases. However, as soon as the Boost inductance reaches the value around 0.6mH, the losses ratio reduction vs. Boost inductance is not evident any more. That means: it is not necessary to use a very large Boost inductor to reduce the semiconductor losses and improve system efficiency in Two-Boost-Circuit BPFC.

- If the BPFC operates in variable output power, take the audio application

as an example, there will be a best region for Boost inductance with relatively low and stable semiconductor losses ratio and higher power density.

As what has been shown in Fig.3.6, the inductance from  $0.2 \mathrm{mH}$  to  $0.6 \mathrm{mH}$  should be the best suitable region from  $300 \mathrm{W}$  up to  $3.2 \mathrm{kW}$  application. This optimized inductance range will do benefit to reduce magnetic volume, which will be shown in the next section.

#### 3.2.5 Efficiency and Volume Optimization

Boost inductors occupies the majority of the volume in BPFC converters. In order to make a compact BPFC converter, the inductor design should be paid high attention. Besides, the power losses in the inductors are function of inductors' volumes as well. In optimization loop 2, a useful compromise between size and efficiency of a Boost inductor can be achieved.

#### 3.2.5.1 Cores Selection

The inductor losses come from core losses and winding losses. In order to predict the total inductor losses, the first step is choosing the core. A suitable core for Boost inductor must have high flux saturate limitation, low core losses and acceptable price. On the magnetic manufacturers' website, there will be very specific information about each core's shape and its material. In this work, the author chose the Kool Mu E cores because of their advantages of high saturation level, relatively low core losses and cheaper price [36]. And all the details of every Kool Mu E core are defined as the initial values at the beginning of the optimization procedure.

#### 3.2.5.2 Winding Losses

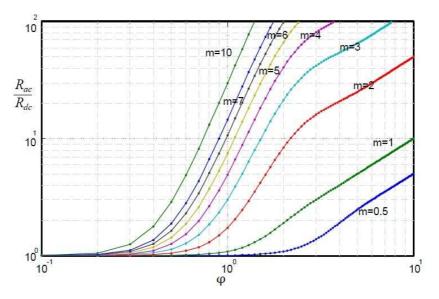

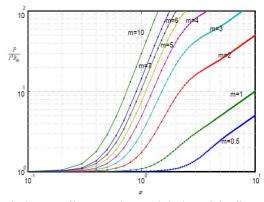

Considering the winding losses, the DC losses part usually keeps constant in fixed power level when the type and length of the winding is given; however the AC losses is more complex due to the skin and proximity effects. In this design, copper foil is used in order to decrease the proximity effect. Eqs. (3.37) - (3.40) give the functions of winding losses, switching frequency, layers and copper foil thickness [37]. Where, h is the thickness of copper foil,  $\delta$  is skin depth, and  $\varphi$  is the ratio between copper thickness and skin depth.

$$P_W = \varphi \left[ G_1(\varphi) + \frac{2}{3} (M^2 - 1) [G_1(\varphi) - 2G_2(\varphi)] \right] \times P_{dc}$$

(3.37)

$$\varphi = \frac{h}{\delta} = \frac{h\sqrt{f_s}}{7.5} \tag{3.38}$$

$$G_1(\varphi) = \frac{\sinh(2\varphi) + \sin(2\varphi)}{\cosh(2\varphi) - \cos(2\varphi)}$$

(3.39)

$$G_2(\varphi) = \frac{\sinh(\varphi)\cos(\varphi) + \cosh(\varphi)\sin(\varphi)}{\cosh(2\varphi) - \cos(2\varphi)}$$

(3.40)

According to the equations above, Fig.3.7 shows the increase of layer copper losses producing by proximity effect vs.  $\varphi$  and MMF force ratio m. It can be found in Fig.3.7, with the factor  $\varphi$  and layer m increasing, the AC losses increase significantly.

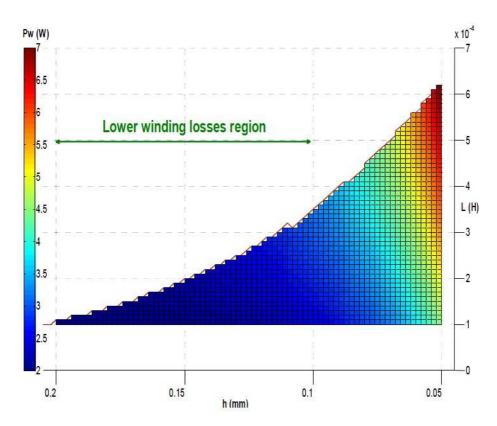

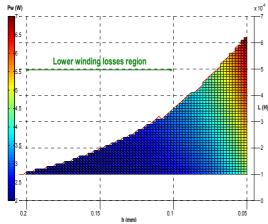

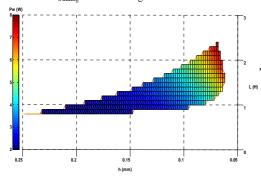

Assuming the switching frequency is 65kHz, and all the simulations are under the same condition:  $220V_{ac}$  input and 390V output on 3.2kW. Because the trend of winding losses' increase independents on the core size, in Fig. 3.8, the inductor winding losses vs. thickness of copper foil and inductance are given using Kool Mu E core 5528E090 from  $Magnetics^{\oplus}$ . It can be found that at the same inductance, when the copper foil's thicknesses increase, the total winding losses reduce due to DC winding losses reduction. But the maximum inductance which can be wound on the core decreases as well. However the inductance dropping will not enhance the semiconductor losses ratio as long as carefully choosing the suitable inductance according to what has been mentioned in previous section. Therefore, h varies from 0.1mm to 0.15mm could be a good range for copper foil selection in order to gain low winding losses.

Figure 3.7: Increase of layer copper losses proximity effect as a factor  $\varphi$  and MMF force ratio m [37]

#### 3.2.5.3 Core Losses

Eq.(3.41) gives the function of core losses, flux density, switching frequency and the volume of the Kool Mu cores [38].

$$P_{core} = K_H f_s^{\beta} B_{av}^{\alpha} V_e \tag{3.41}$$

Where  $K_H$ ,  $\alpha$  and  $\beta$  are constant parameters, which are determined by the material of the core.  $V_e$  is the volume of the core.  $B_{av}$  is the average flux density in the core during half line period. It can be calculated as below:

$$B_{av} = \frac{1}{N'} \sum_{n=1}^{N'} \frac{v_L(n)d(n)}{2MA_e f_s}$$

(3.42)

Where the  $v_L(n)$ , d(n) are the instant value of inductor voltage and switch duty circle at each switching cycle. M is the number of turns of the inductor and  $A_e$  is cross section of the core. N' is the number of switching cycles in a half line cycle, which is the greatest integer of  $\frac{f_s}{2f_L}$ .

Figure 3.8: Inductor Winding Losses vs. Thickness of Copper Foil and Inductance. The core is Kool Mu E core 5528E90 from  $Magnetics^{\circledR}$

| Core Type   | Volume <sup>a</sup> | $A^{b}$ | $\rm B_{p}$ | $C_{\rm p}$ | $D_{\rm p}$ | $\mathrm{F^{b}}$ | $\Gamma_{\rm p}$ | $M^{b}$ |

|-------------|---------------------|---------|-------------|-------------|-------------|------------------|------------------|---------|

| 00K5528E090 | 43100               | 54.86   | 27.56       | 20.62       | 18.50       | 16.76            | 8.38             | 10.29   |

| 00K7228E060 | 50300               | 72.39   | 27.94       | 19.05       | 17.75       | 19.05            | 9.52             | 16.89   |

| 00K5530E090 | 51400               | 54.86   | 27.56       | 24.61       | 18.50       | 16.76            | 8.38             | 10.29   |

| 00K8020E040 | 72100               | 80.01   | 38.10       | 19.81       | 28.02       | 19.81            | 9.91             | 19.81   |

| 00K8020E060 | 72100               | 80.01   | 38.10       | 19.81       | 28.02       | 19.81            | 9.91             | 19.81   |

| 00K6527E060 | 79400               | 65.15   | 32.50       | 27.00       | 22.20       | 19.65            | 10.0             | 12.1    |

| 00K8044E026 | 80912               | 80.01   | 44.58       | 19.81       | 34.36       | 19.81            | 9.91             | 19.81   |

| 00K160LE026 | 212000              | 160.0   | 38.1        | 39.62       | 28.1        | 19.81            | 9.9              | 59.28   |

| 00K130LE026 | 237000              | 130.3   | 32.51       | 53.85       | 22.2        | 19.81            | 10.0             | 44.2    |

$<sup>^{\</sup>rm a}$  Unit:  $mm^3$

**Table 3.1:** Dimensions of The Kool Mu E Cores from  $Magnetics^{\circledR}$

<sup>&</sup>lt;sup>b</sup> Unit: mm, parameters describe the dimensions of the cores, the meanings can be found in the datasheet [34]

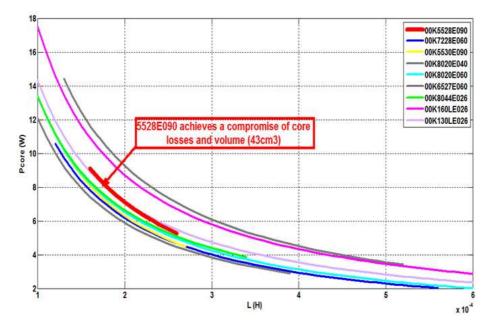

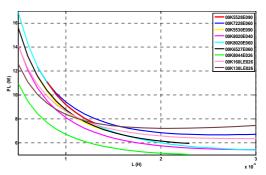

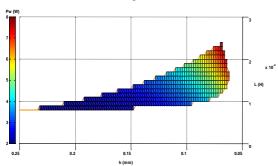

From Eqs.(3.41) and (3.42), Fig.3.9 shows the core losses vs. Boost inductance for all the qualified Kool Mu E cores from  $Magnetics^{\textcircled{\$}}$ . In the legend on the right side, the cores were ranked by size, the topper the smaller. The volume of the cores are listed in table 3.1. According to this figure, it is clear that when the inductance increases, the core losses decrease due to the increasing of turns.

Figure 3.9: Core Losses vs. Boost Inductance for All Qualified Kool Mu E cores from  $Magnetics^{\textcircled{\$}}$

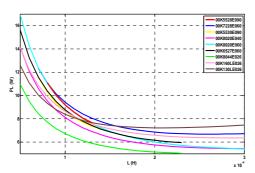

Fig.3.10 shows the total Boost inductor losses vs. inductance for different qualified Kool Mu E cores (see table 3.1) from  $Magnetics^{\textcircled{\$}}$  when h equals to 0.13mm. From Fig.3.10, comes the conclusion that:

- At a certain power level, the Boost inductor losses have its minimal value when the inductance changes.

- The minimal inductor losses are different depending on cores. However, the relationship is not exactly the same as: the bigger the core, the lower the losses. It depends on several factors. Such as geometry of core, permeability, DC bias performance and temperature rising. For example, core 5528E090 (51.4cm³) is smaller than 8020E060 (72.1cm³), but its inductor losses are lower due to its higher permeability.

Figure 3.10: Total inductor losses vs. Boost inductance for different qualified Kool Mu E cores from  $Magnetics^{\textcircled{\$}}$  when h=0.13mm

It should be noticed that in Fig. 3.10, the total inductor losses drop with the inductance increasing. This is due to in the range of inductance from 0.1mH to 0.5mH, the core losses dominate the total inductor losses. So, when the inductance increases, the core losses reduce because of the higher number of turns. If the inductance keeps on increasing, the winding losses will increase. Finally, the winding losses will dominate the total losses, and then, the inductor losses will start to increase.

According to section 3.2.4 and 3.2.5, the expectable Boost inductor parameters for the Two-Boost-Circuit BPFC in Fig.3.1 at 3.2kW and  $220V_{ac}$  input can be: L=0.23mH, the copper foil is 0.13mm, using Kool Mu E core 5528E090 (volume is  $43.1cm^3$ ) for high efficiency and power density application.

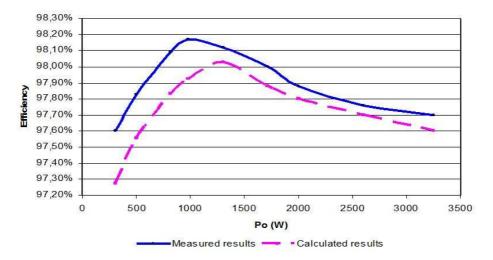

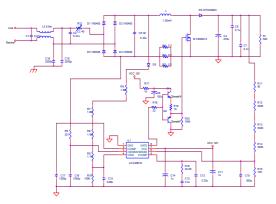

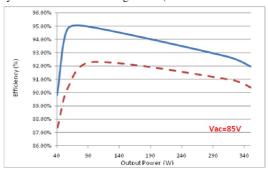

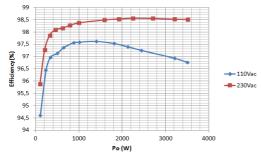

#### 3.3 Experiment Results from a 3.2kW Bridgeless PFC

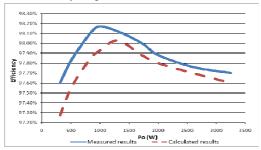

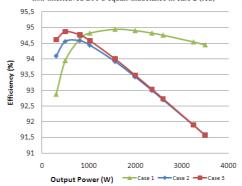

Efficiency comparison of the simulations based on the optimization design procedure and the measurement results of the proposed Two-Boost-Circuit BPFC

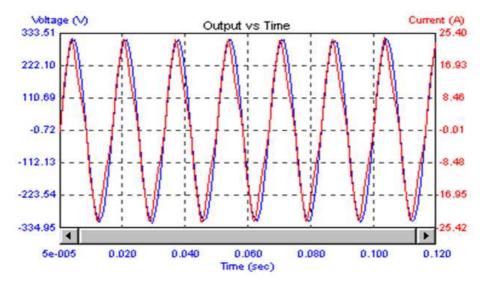

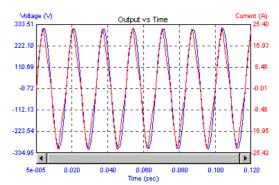

system is given in Fig.3.11. It output power range is from 300W to 3.2kW. Fig.3.12 gives the measured input voltage and current waveforms of this BPFC at 3.2kW and  $220V_{ac}$ .

Figure 3.11: Efficiency comparison of Two-Boost-Circuit BPFC at  $220V_{ac}$  input and 390V output using core 5528E090

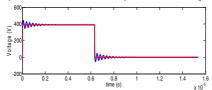

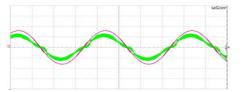

Figure 3.12: Input voltage and current waveforms from Two-Boost-Circuit at  $220V_{ac}$  input and 390V output using core 5528E090

According to Fig.3.11 and 3.12, it can be concluded that the calculated values from the optimization design procedure predict the performances of the Two-Boost-Circuit BPFC correctly and give an optimized design of the Boost inductor.

## 3.4 Conclusions on the Design of High Efficient Boost Inductors

According to the discussions in this Chapter, the key point for high efficiency and high power density BPFC design is the Boost inductor optimization. In order to achieve as high efficiency as possible, the Boost inductance should be selected carefully based on the BPFC's power level and semiconductor losses. Furthermore, there should be a best value for boost inductance at a constant power. Additionally, it is not necessary to use very large inductance to reduce semiconductor losses.

In conclusion, in order to best compromise the inductor losses and its volume for the high power Two-Boost-Circuit BPFC system, the proposed optimization procedure is a useful method for implementation.

### Chapter 4

## **EMI Analysis and Suppression**

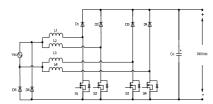

Working as an electronic pollution eliminator, the PFC's own Electromagnetic Interference (EMI) problems have been blocking its performance improvement for long. In this Chapter, a systematic research on the generation of EMI in the selected Two-Boost-Circuit Bridgeless PFC in Chapter 3 is presented. And two cost-efficient methods for EMI reduction are discussed. Furthermore, a novel BPFC topology is proposed for EMI improvement.

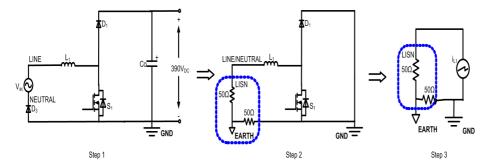

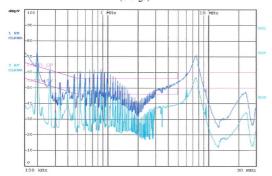

#### 4.1 EMI Modelling

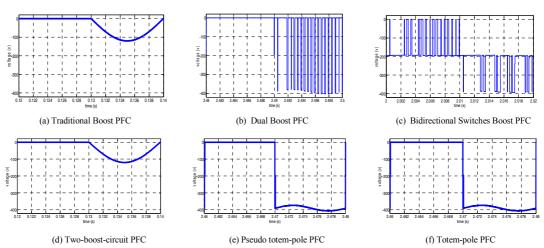

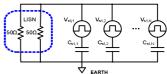

To better explain how exactly the EMI generating from the Two-Boost-Circuit BPFC, this section starts from analyzing and modelling the common mode (CM) and differential mode (DM) noises of this BPFC firstly. Because it is well known that the real EMI performances typically depend strongly on the circuit layout, semiconductor characteristics, gate drivers, operating currents, voltages and temperature and parasitic elements, the actual EMI performances above 1MHz are very difficult to simulate. In order to avoid to push the research into unlimited complexity, in this section, only the noises frequency below 1MHz are taken into consideration. Besides, the model of EMI receiver is not considered at this section neither.

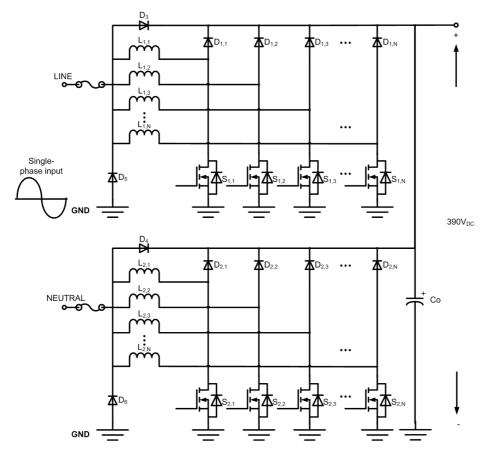

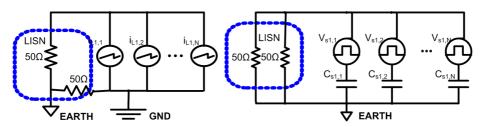

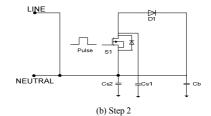

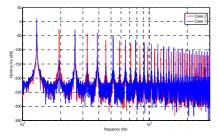

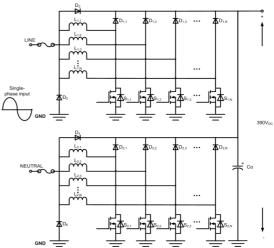

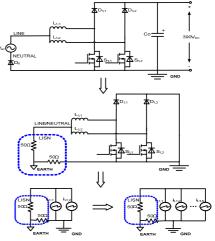

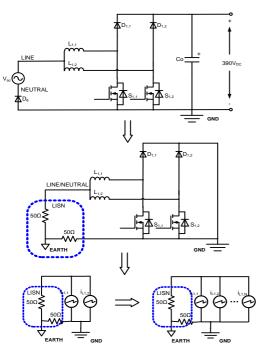

Start from DM noise modelling, the basic key steps are given in Fig.4.1.

- Using the symmetrical operation structure to simplify the topology. As the discussions in previous Chapters, due to the converter operates symmetrically, only the positive AC line period needs to be considered. In the negative AC line period, the operation principles are the same.

- Because the output filter capacitor can be considered as a short circuit in high frequency, and the return diode  $D_3$  is always conducted in the positive AC line period, these two components can be simplified.

- Simplify the MOS, Boost diode and the Boost inductor. In high frequency domain, the Boost inductors charge and discharge through MOS  $S_1$  and Boost diodes  $D_1$ , therefore, it can be considered as a triangle current source.

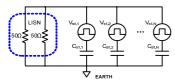

Figure 4.1: DM EMI Modeling Process of the Two-Boost-Circuit BPFC

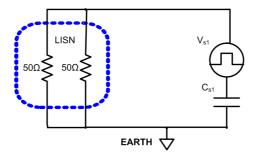

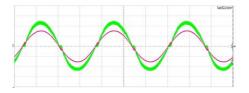

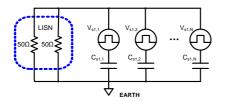

Following the same modelling concept above, the CM model of the BPFC is shown in Fig.4.2. Where the capacitor  $C_{s1}$  is the sum of the parasitic capacitors between the MOS to the earth, which offers a high frequency noise current loop from BPFC to the AC mains. Through Fig.4.1 and Fig.4.2, it can be concluded that for the proposed BPFC in Chapter 3, its DM and CM model are equivalent to a triangle current source and a pulse voltage source respectively.

#### 4.2 EMI Suppression

With the increasing demands on environment-friendly power electronics, research and development on EMI reduction are attracting more and more attentions. During the last decades of years, plenty of researchers presented their

Figure 4.2: CM EMI Modelling of the Two-Boost-Circuit BPFC