### Technical University of Denmark

### **Programming Models and Tools for Intelligent Embedded Systems**

Sørensen, Peter Verner Bojsen ; Madsen, Jan

Publication date: 2010

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Sørensen, P. V. B., & Madsen, J. (2010). Programming Models and Tools for Intelligent Embedded Systems. Kgs. Lyngby, Denmark: Technical University of Denmark (DTU). (IMM-PHD-2010-232).

#### DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## **Programming Models and Tools for Intelligent Embedded Systems**

Peter Verner Bojsen Sørensen

Kongens Lyngby 2010 IMM-PHD-2010-70

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk

IMM-PHD: ISSN 0909-3192

# Summary

Design automation and analysis tools targeting embedded platforms, developed using a component-based design approach, must be able to reason about the capabilities of the platforms. In the general case where nothing is assumed about the components comprising a platform or the platform topology, analysis must be employed to determine its capabilities. This kind of analysis is the subject of this dissertation.

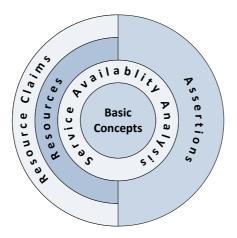

The main contribution of this work is the Service Relation Model used to describe and analyze the flow of service in models of platforms and systems composed of re-usable components. Fundamental to the service relation model is the novel concept of service aggregation that simply states that one service is accessible through another.

The usefulness and versatility of the Service Relation Model is demonstrated by means of three different applications. In the first application, the model is used for checking the consistency of a design with respect to the availability of services and resources. In the second application, a tool for automatically implementing the communication infrastructure of a process network application, the Service Relation Model is used for analyzing the capabilities of a platform and as a basis for efficient code generation. In the third application, the Service Relation Model and the concept of consistency are used to guide an automated procedure for designing systems composed of components. ii

# Resumé

Værktøjer til automatisering af design opgaver målrettet indlejrede platforme, der er udviklet ved brug af en komponent-baseret design metode, skal have adgang til information vedrørende platformenes funktionelle egenskaber. I det generelle tilfælde hvor intet kan antages vedrørende en platforms topologi eller komponenterne, der indgår i platformen, må analyse benyttes til at bestemme platformens egenskaber. Denne form for analyse er emnet for denne afhandling.

Hovedbidraget i dette arbejde er Service Relations Modellen, som benyttes til at beskrive og analysere tilgængeligheden af tjenester i modeller af platforme og systemer bestående af gen-brugbare komponenter. Service Relations Modellen er baseret tjeneste-opsamlings konceptet, der beskriver hvorledes tjenester kan være tilrådighed igennem andre tjenester.

Brugbarheden og alsidigheden af service relations modellen bliver demonsteret igennem tre eksempeler på forskellige anvendelser. I den første anvendelse benyttes modellen til at kontrollere konsistensen af et design med hensyn til tilrådigheden af tjenester og resourcer. I den anden anvendelse, et værktøj til automatisk at implementere kommunikations infrastrukturen i et process netværk, benyttes Service Relations Modellen til at analysere en platforms funktionelle egenskaber og som grundlag for effektiv kode generering. I den tredje anvendelse, benyttes Service Relations Modellen sammen med konceptet om konsistens som grundlag for en automatiseret procedure til at designe systemer bestående af komponenter. iv

# Preface

This thesis was prepared at Informatics Mathematical Modelling, the Technical University of Denmark in partial fulfillment of the requirements for acquiring the Ph.D. degree in engineering.

**Acknowledgment** I would like to thank my supervisor Jan Madsen for his support and help during my studies and the preparation of this thesis. I also want to thank my colleague through many years Per Larsen for his relentless criticism of my work. Finally, I would like to thank my family and my girlfriend Ane Skak for their patience and support during the writing of this thesis.

Lyngby, February 2010

Peter Verner Bojsen Sørensen

# **Papers contributed**

- [88] Peter Verner Bojsen Sørensen and Jan Madsen. Consistency Check for Component-Based Design of Embedded Systems using SAT-Solving. *Proceedings of the 20th Nordic Workshop on Programming Theory*, 2008. Published.

- [87] Peter Verner Bojsen Sørensen and Jan Madsen. Component-based Service Availablity Checking. *Nordic Workshop and Doctoral Symposium on Dependability and Security*, 2008. Published.

- [89] Peter Verner Bojsen Sørensen and Jan Madsen. Generating Process Network Communication Infrastructure for Custom Multi-Core Platforms. *International Journal of Embedded and Real-Time Communication Systems* (*IJERTCS*), 2010. Accepted (to appear 2010).

viii

## Contents

| Su  | mma                                             | ry                                                                                                                                                                 | i                                       |

|-----|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Re  | sume                                            |                                                                                                                                                                    | iii                                     |

| Pro | eface                                           |                                                                                                                                                                    | v                                       |

| Pa  | pers                                            | contributed                                                                                                                                                        | vii                                     |

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | oduction         Dealing with Complexity         Design Methodologies         Scope of Work         Problem Statement         Contributions         Thesis Outline | 1<br>2<br>4<br>7<br>11<br>17<br>18      |

| 2   |                                                 | Service Relation Model         Informal Presentation         Basic Concepts         In-depth Presentation         Analysis         Discussion & Summary            | <b>19</b><br>19<br>29<br>35<br>50<br>52 |

| 3   | Con<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5          | sistency Checking<br>Service Classes and Hierarchies                                                                                                               | <b>55</b><br>56<br>59<br>62<br>80<br>84 |

|   | 3.6 Related Work                          | 95  |  |  |  |

|---|-------------------------------------------|-----|--|--|--|

|   | 3.7 Discussion & Summary                  | 101 |  |  |  |

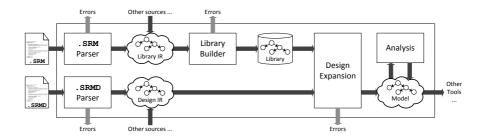

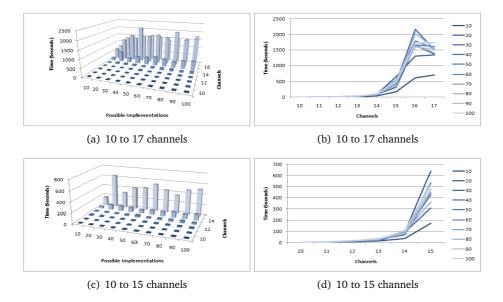

| 4 | Automated Programming 10                  |     |  |  |  |

|   | 4.1 Introduction                          | 103 |  |  |  |

|   | 4.2 The Procedure                         | 105 |  |  |  |

|   | 4.3 Code Generation                       |     |  |  |  |

|   | 4.4 The PAL Generation Tool               | 119 |  |  |  |

|   | 4.5 Case Study: MJPEG                     | 139 |  |  |  |

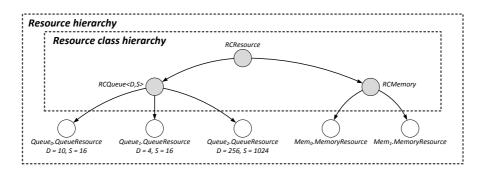

|   | 4.6 Related Work                          | 145 |  |  |  |

|   | 4.7 Discussion & Summary                  | 148 |  |  |  |

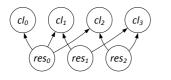

| 5 | Automated Design Generation               | 149 |  |  |  |

|   | 5.1 Introduction                          | 149 |  |  |  |

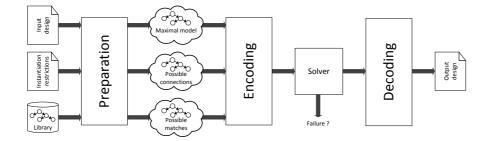

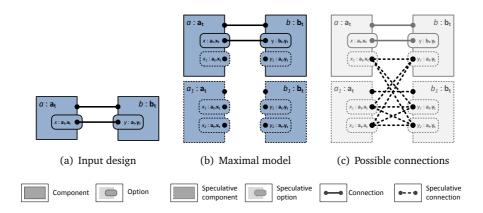

|   | 5.2 Procedure Overview                    | 152 |  |  |  |

|   | 5.3 Preparation                           | 155 |  |  |  |

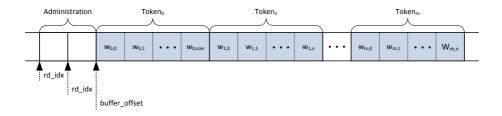

|   | 5.4 Encoding                              | 158 |  |  |  |

|   | 5.5 Decoding                              | 169 |  |  |  |

|   | 5.6 Experiments                           | 169 |  |  |  |

|   | 5.7 Optimizations                         | 182 |  |  |  |

|   | 5.8 Discussion & Summary                  | 184 |  |  |  |

| 6 | Conclusion 185                            |     |  |  |  |

|   | 6.1 Contributions                         | 185 |  |  |  |

|   | 6.2 Discussion                            | 187 |  |  |  |

|   | 6.3 Future Work                           | 187 |  |  |  |

| Α | Alternative Analysis Algorithm 18         |     |  |  |  |

| B | Evaluation Functions                      | 191 |  |  |  |

| С | Implementation Scheme C Templates         |     |  |  |  |

| D | Automated Programming Timing Measurements |     |  |  |  |

| E | Design Generation Timing Measurements     |     |  |  |  |

<u>x</u>\_\_\_\_\_

Assumption is the mother of all fuck up's!

Travis Dane, Under Siege 2: Dark Territory

## CHAPTER 1

# Introduction

Embedded systems are specialized computing platforms and an integral part of a device or a machine and typically used for control and data processing. In contrast to general purpose computers, such as personal computers (PC's), embedded systems are characterized by only having a single purpose that never changes. More often than not, an embedded system is associated with strict constraints on metrics such as performance, power consumption, reliability and, naturally, cost. Embedded systems can be found in a very broad range of products from cellular phones to household appliances. In 2006, the number of embedded systems outnumbered the number of PC's by a factor of 10 [11]. In 2009 the total revenue from embedded systems was 88 billion dollars, up from 46 billion dollars in 2004 which yields an average annual growth of 14%, [4].

For high volume products it is imperative to keep the cost per unit to a minimum which often complicates the design significantly resulting in a relatively high non-recurring engineering (NRE) cost. This is acceptable because the NRE cost can be amortized across a large number of units and, thus, contributes marginally to the unit cost. For such products, custom hardware or application specific integrated circuits (ASIC's) are often used since they offers the best performance and the lowest power usage. For low volume products, on the other hand, the NRE cost must be kept low at the expense of a higher cost per unit which implies that the design must be kept relatively simple. For such products more general purpose common-of-the-shelf (COTS) platforms, such as microcontrollers, are employed.

In some markets, such as the market for electronic consumer products, the time from a product is conceived until it is available for sale, called time-to-market, is of critical concern.

Ever since the dawn of the semi-conductor era, the density of transistors in integrated circuits has increased according to Moore's law [66] and it is likely to continue to do so in the foreseeable future. The increase is based on the use of smaller wires and transistors. The technological progress has enabled the construction of more complex chips. Today, it is entirely possible to integrate complete computing platforms with processors, networks, memories, sensors and actuators in a single chip. The ability to cram a historical amount of transistors onto a silicon wafer means that we are able to produce very advanced systems. The setup costs associated with the manufacturing of such hardware is, however, overwhelming and is only feasible for parts that can be guaranteed a high-volume production. As a consequence, the general trend in embedded systems design is shifting from the use of ASIC's to programmable general purpose or domain specific platforms and from hardware design to embedded software design.

The increase in complexity of modern embedded systems in general and embedded software in particular means that the design costs has risen exponentially. Unfortunately, the methodologies used to design embedded systems have not been progressing accordingly which has led to a situation where the complexity of many designs are pushing the limits of what can reasonably be handled with current design methodologies. This gap between what we can build and what we can design is sometimes referred to as the productivity gap [51] or the implementation gap [70].

## 1.1 Dealing with Complexity

The design of an embedded system, or any kind of system for that matter, can be seen as a series of design decisions taking the system from idea to implementation. These decisions are capture using models – abstract representations of the design. Associated with a model is a "level of abstraction" that specifies the modeling concepts and the semantics of the model. Exactly what these concepts and associated semantics are depends on what one considers the implementation. For example, for a hardware design one might take transistors as the basic concept and for a software design the central concept could be the instructions of some processors instruction set. The number of design decisions captured by such a model is astronomical even for the smallest designs of practical interest. The lack of efficient ways of making these decisions is the cause of the productivity gap. Within the field of embedded systems design complexity has traditionally been addressed by a combination of abstraction, hierarchy and domains [53]:

**Abstraction.** An abstraction is a representation of some concept containing only relevant information with respect to some task. An abstraction level is a definition of the modeling concepts and their semantics used to represent a system. The term "level of abstraction" implies that abstraction levels can be ordered. A level of abstraction x is said to be higher than another abstraction level y if x has less information than y for some model and if x is at least as expressive as y. In other words, abstraction levels can be partially ordered. A characterizing feature of an abstraction is that it allows for multiple realizations at a lower level of abstraction. Moving from a high-level of abstraction to a lower level thus usually involves a number of design decisions. Design automation tools are based on abstractions. They take as input a model of a system at a given abstraction level and produces as output another model at a lower level of abstraction.

**Hierarchy** Hierarchy is a recursive partitioning of a model such that the details of each part are hidden in a lower hierarchical level. Hierarchy reduces complexity by simply reducing the number of entities that needs to be considered.

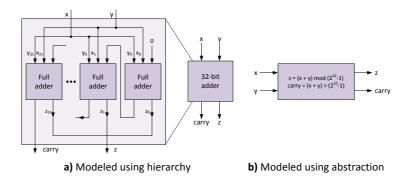

In some cases it may be difficult to distinguish between hierarchy and abstraction. As an example consider the 32-bit adder box in figure 1.1. Besides the 32-bit adder box, the figure also shows two possible internal models. The behavior of the adder may be given as a network of full adders in which case the adder box is a mere substitution for a network of full adders at a different hierarchical level. Alternatively, the behavior of the adder box could be given as a pair of equations. Expressing the behavior of the adder box as a network of full adders is an example of the use of hierarchy whereas expressing the behavior using simple equations is an example of applying abstraction. From the point of view of the designer both hierarchy and abstraction serves him equally well since only the behavior of the adder is of interest – how the adder is implemented is irrelevant.

**Domains (Separation of Concerns)** A design can be split into a number of different domains each of which emphasizes a certain aspect of a design. Such

**Figure 1.1** – Hierarchy vs. Abstraction. Example showing the difference between hierarchy and abstraction [53]. The figure shows two different meanings of the simple 32-bit adder box. To the left we have a meaning expressed using hierarchy as a network of full adders. To the right the meaning of the box is expressed using abstraction. Here the complex full adder network has been replaced by a simpler model based on algebraic formulae.

domains can be logically analyzed in isolation from other domains [58]. A prime example of separation of concerns is the separation of computation and communication, exemplified by the concept of transaction level modeling (TLM) [18], which has received a lot of attention from both industry and academia. Another example is the separation of time and computation in the synchronous data flow models.

It may be difficult to distinguish between abstraction and domain separation. The reason for this is that in most practical models these two are intimately linked together in the sense that a domain focus is often realized as an abstraction layer. For example, in the context of transaction level modeling two level of abstraction are of interest: the TLM level and the pin-accurate level. The TLM level focuses on the behavior of the design abstracting the details of communication whereas the pin-accurate level includes a detailed description of the communication in addition to the behavior. In principle, however, the domains of computation and communication are independent of these abstraction layers.

### 1.2 Design Methodologies

A design methodology, or a design process, is a sequence of steps necessary to build something. Besides the obvious goal to build something that is function-

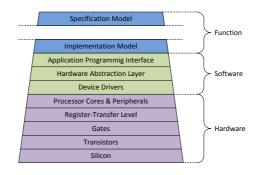

**Figure 1.2** – A stack of abstraction layers taking a design from specification to silicon implementation [82]. The gap between specification and implementation represents the manual step of going from an informal specification to a (high-level) formal description.

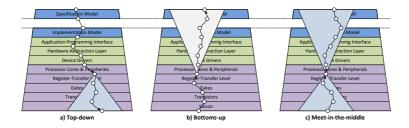

Figure 1.3 – Top-down, bottoms-up and meet-in-the-middle methodologies.

ally correct, a methodology may have other equally important goals: time-tomarket, design cost and/or quality. Being explicit about the process is important to ensure that the design team pulls in the same direction. More importantly, a methodology provides a context for understanding the models, methods and tools that are an indispensable part of modern embedded systems development.

Methodologies for embedded systems development are often described relative to a set of abstraction levels linking the specification with the implementation. These are ordered in a stack according to their level of abstraction with the most abstract representation (the specification) at top and the least abstract (the implementation) at the bottom. The number and types of abstraction levels in a stack depends on the concrete methodology. Figure 1.2 shows an example of a typical stack. Relative to such a stack, a design methodology can be classified as a top-down, bottoms-up or a meet-in-the-middle approach: **Top-down (Figure 1.3.a)** The starting point of a top-down approach is a specification given at the highest level of abstraction. The specification is gradually refined into an implementation at the lowest level of abstraction by a process called stepwise refinement. Top-down approaches can potentially yield the most optimal implementation because it allows for fine-tuning at all levels of abstraction and does not exclude any portions of the design space. For the same reasons, top-down approaches are also the most expensive and time-consuming.

**Bottoms-up (Figure 1.3.b)** The starting point of a bottoms-up approach is a set of entities at the lowest level of abstraction. These entities are assembled into richer entities that are abstracted to the second level of abstraction. The resulting entities are again assembled into even richer entities that are abstracted at the third level of abstraction. This process continues until a single entity that, hopefully, implements the specification, emerges at the highest level of abstraction. Bottoms-up approaches inevitably leads to over design because the choices made at each level of abstraction must be conservative enough to ensure that the resulting system will satisfy the specification. In favor of bottoms-up approaches is the fact that the decisions made at the lower levels of abstraction can be re-used in other designs.

**Meet-in-the-middle (Figure 1.3.c)** A meet-in-the-middle approach is, as the name suggests, a combination of the top-down and bottoms-up approaches and is often referred to as *platform-based design* [83, 58]. In platform-based design, a platform is constructed bottoms-up and combined with a specification of the intended system behavior refined top-down. This enables the trade-off between design space and other design objectives such as time-to-market or cost. This is so because the platform can be designed independently of any actual application which means that the associated design time and cost does not (necessarily) contribute to the cost and time-to-market of the final system. The overwhelming design and setup costs associated with the development of hardware has been one of the primary motivating factors behind the concept of platform-based design.

In practice, all methodologies are meet-in-the-middle or bottoms-up since the entities of the lowest abstraction layer necessarily must be given in order for the methodology to make sense. A number of other conceptual frameworks have been developed for understanding and comparing methodologies for embedded systems design [54, 33, 38] that will not be discussed here.

#### 1.2.1 System-level Platform-based Design

A particularly interesting class of platform-based design methodologies are those where the refined specification, called the application hence forth, meets the platform at the so called *system-level of abstraction*. The system-level of abstraction has traditionally been defined as an abstraction layer above the register-transfer level that comprises software in addition to hardware [37]. At this level, a hardware platform is described as a netlist of high-level components such as processors, memories and interconnects. In addition to the hardware, a platform may also consist of software such as operating systems and other mid-dleware components, executing on the programmable processors of the hardware platform.

The task of choosing the right platform and mapping of the application onto the chosen platform is central to platform-based design. Ideally, the application is a pure description of behavior containing no implementation details meaning that the performance characteristics of the final system are determined by the choice of platform and mapping alone. Much research has been devoted to the problem of exploring the design space to determining an optimal mapping and/or platform using both formal (e.g. [46, 45, 79]) and simulation-based approaches (e.g. [64, 22]).

Many of these approaches uses the concept of abstract services to link abstract representations of applications and platforms [43, 92]. In this view, an application is seen as a service consumer whose function or behavior is defined by the temporal ordering of a set of service requests and platforms as the provider of services. Different platforms may provide different implementations of the same services. Using simulation or formal methods the performance of an application with respect to a particular platform and mapping can be evaluated and quantitatively compared to alternative platforms and mappings.

## 1.3 Scope of Work

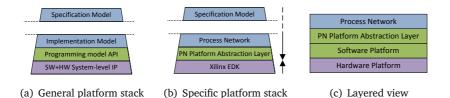

In this thesis, we will focus on a class of system-level platform-based design methodologies that can be described using three different level of abstraction as shown in Figure 1.4(a). The lowest of level of abstraction is the system-level where a platform is designed using a component-based design approach. On top of the system-level we have an API level that implements a specific programming model, to the highest abstraction level, the implementation model.

Figure 1.4 – Organization of the design methodology used in this thesis.

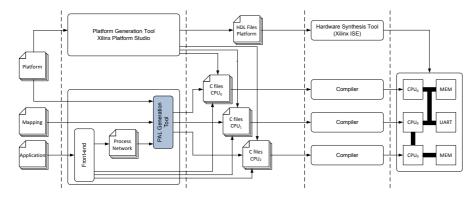

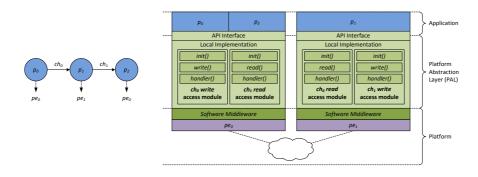

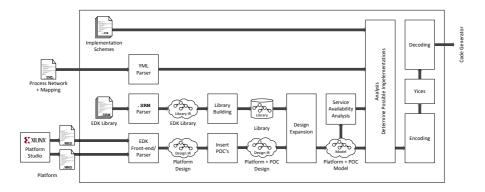

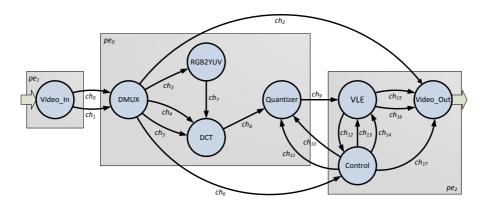

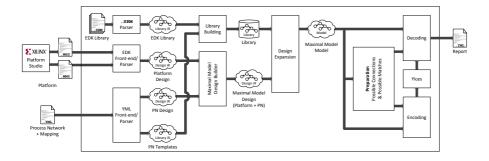

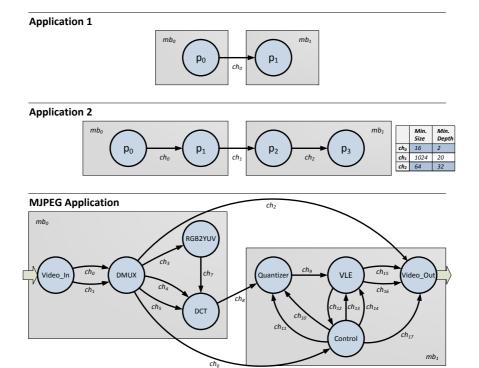

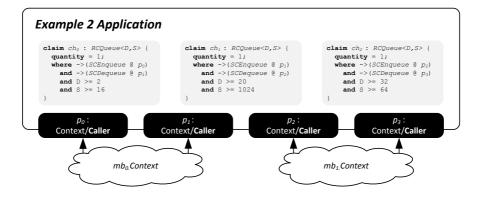

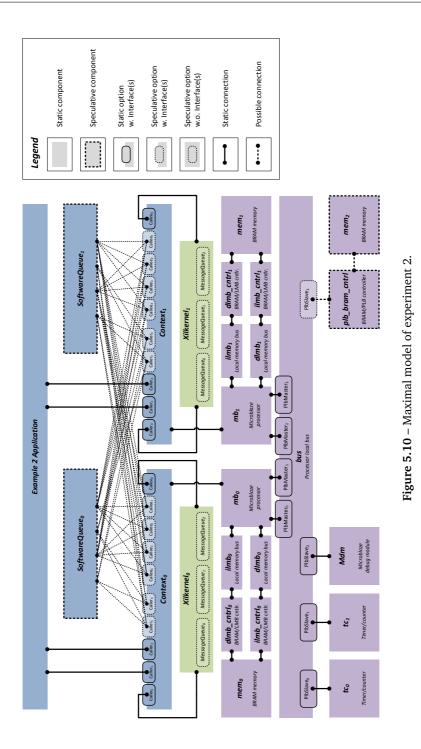

Most of the experiments and case studies presented in this thesis will be given relative to a methodology where platforms are created using the Xilinx Embedded Development Kit design flow and applications are specified using the process networks model of computation (MoC). In this methodology, an application is tied to a platform by means of a platform abstraction layer providing an implementation of the process network MoC. As shown in Figure 1.4(b) the platform is created bottoms-up where as the application and the platform abstraction layer is created top-down. For reference, Figure 1.4(c) shows a layered view of systems designed using the methodology. In the rest of this thesis we will use the term "system" for a complete system comprising both a platform and an application.

Even though most examples will be given relative to this specific methodology most of the principles and methods presented in this work are independent of the actual methodology and may be applied to other methodologies as well.

#### 1.3.0.1 Component-Based Design

Component-based design is based on the idea that system can be decomposed into components. A component is a self-contained part or sub-system that can be used as a building block in the design of a larger and more complex system. It provides specific services to its environment across well-specified interfaces. In the context of embedded systems design, a component is a piece of functionality implemented as software, hardware or a combination of the two. Components are units of composition that can be composed into new components with richer functionality using hierarchy. Ideally, a component should be re-usable and may provide some degree of customizability.

In a component-based design approach, the task of developing components and the task of assembling systems are independent of each other. This separation is what makes component-based design appealing for embedded systems development because the development of the components is not part of the critical time-to-market. Obviously, the truth of this depends on the availability of components which implies that component-based design disfavors design with very specialized needs [52]. In general, component-based design is appropriate when the market is unable to support expensive design costs or when ones competitive advantage is not in the design of platforms [85]. The strength of the component-based design is the natural focus on component re-use.

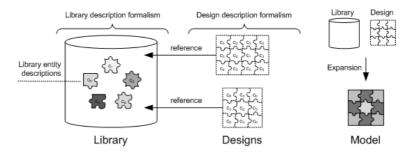

Given is a library of (re-usable) components and the objective is to assemble these into a network that implements the desired behavior (given in the specification). The process of integrating a component into a design can be divided into a series of steps:

- 1. The first of these is *component matching*. Here, the functional requirements of the component is matched against the functions offered by the available components. The result of this step is a set of components that may satisfy the functional requirements.

- 2. The second step is *component selection* and involves selecting the most appropriate component with respect to any non-functional constraints placed on the design.

- 3. The third step is *component integration* where the component is integrated (i.e. connected) into the design.

The resulting design is characterized by its *allocation*, *configuration* and *topology* where the allocation specifies the number and types of components in the design, the configuration specifies, for each allocated component, the value of any required parameters and the topology defines the communication infrastructure of the design.

#### 1.3.0.2 Programming Models & Abstraction Layers

Compared to single processor systems, heterogeneous multi-processor systems are difficult to program. In the absence of a platform-wide programming solution, shielding the application developer from the details of the platform, the developer must program each processor individually. This is problematic for several reasons:

• First, the application becomes dependent on the particular platform making re-use hard and changes in the platform, application and/or mapping difficult.

- Second, a partitioning and mapping of the application must be decided upon before any code is written which leaves little room for errors and may lead to resource waste due to over-engineering.

- Finally, in addition to implementing the application, the application developer must also worry about low-level processor-to-processor interfacing that in turn will require intimate knowledge of the platform in particular and low-level programming in general.

Through the use of a parallel programming model (e.g. TTL [94], YAPI [28], OpenMP [1]) it is possible to abstract away different aspects of the platform, such as communication and synchronization, and thus effectively de-couple the application from any actual platform [55, 74, 36]. A programming model can be provided as an integral part of a programming language or as an add-on in the form of an API. In most cases, a given platform does not directly implement a given programming model and thus an abstraction layer, realizing the abstractions of the programming model, is needed. An abstraction layer can be application-specific so that it only provides support for the functionality that is actually used by a particular application. The opposite of an application-specific layer is a general purpose layer where functionality is provided to support a broader range of applications.

A general purpose layers are constructed bottoms-up whereas special purpose layers are constructed top-down.

#### 1.3.0.3 Process Networks

For embedded systems, programming models based on the Kahn Process Network (KPN) [57, 62] model of computation have been studied intensively. An application modeled as a KPN consists of processes communicating and synchronizing using unidirectional FIFO channels. In theory, the capacity of the channels is unbounded and writing to them is a non-blocking operation. In this work, we will consider a more practical version with bounded channel capacity and blocking write that we will refer to simply as a *process network*. The process network MoC is especially well suited for capturing streaming (e.g. image processing) applications and has previously been shown to be a suitable representation for efficiently mapping applications onto multi-processor platforms [5, 91, 77].

The process network model of computation is favored because interactions between processes are explicitly modelled by means of channels. In other models of computation, interactions are often implicit which means that program analysis is required to determine dependencies amongst the behavioral entities of an application.

### 1.4 Problem Statement

Tools supporting exploration and synthesis must be able to reason about the capabilities of the target platform. Having knowledge of what can be done with a particular platform and how to do it is fundamental for refinement and, similarly, knowing what a platform can do and the cost associated with doing it is fundamental for design space exploration. If the target platform is known in advance then this knowledge can be embedded within the algorithm used. If, on the other hand, the target platform is not known in advance then the algorithm must be independent of any particular platform and a method for analyzing the actual capabilities of a given platform must be employed. In the case of tools targeting platforms built from re-usable components little or nothing can be assumed about capabilities of the actual platforms. This is so because the components are essentially black boxes.

By cleverly choosing and imposing a set of restrictions on the supported platforms it is often possible to significantly reduce the required analysis effort for a given task. This is so because, given an appropriate set of restrictions, it is possible to make assumptions about *all* possible target platforms. For example, a tool for evaluating the mapping of an application onto an execution platform might assume that all processing elements are connected to the same interconnect so that communication between the parts of the application mapped to different processing elements is always possible. The tool will thus be limited to platforms where the processing elements are fully connected. Similarly, a tool for compiling a high-level specification of an application onto a heterogeneous multi-processor platform might assume that standard C compilers exists for each of the different processors thus limiting the use of the tool to platforms with processors for which C compilers are available. Exactly what kind of assumptions, and thus restrictions, are useful depends on the task at hand and, of course, on whether or not the restrictions are justifiable. In many cases, it is even possible to completely trivialize the analysis so that it becomes an implicit part of the tool or the algorithm. A compiler for a class of very similar processors (e.g. ARM) that may generate different results depending on exactly which processor is the target is an example of this.

The point here is that whenever assumptions are required in order for a tool to avoid having to automatically discover the capabilities of the actual target platform (which might not be trivial) then these assumptions impose restrictions on the targeted platforms which in turn limits the design space. The alternative to imposing restrictions is to allow errors in the tools. For example, the mapping tool might come up with a mapping that is infeasible because two dependent parts of the application are mapped so that their dependency is violated. If one is unable, or unwilling, to accept imposing restrictions on the platform then nothing can be assumed about the platform and, consequently, any information required for decision making must be extracted from the platforms themselves. Extracting this information is, in general, not trivial and the subject of this thesis. In other words: there exists a trade of between how easy it is to design a tool and the usefulness of the tool.

We believe that a number of tools for key problems, primarily within the platformbased design, could benefit from improved analysis techniques for analyzing the capabilities of platforms and systems. By improving these techniques it is possible to develop more generally applicable tools supporting a broader range of architectures and design styles. In this work, we will focus on the task of extracting information about the capabilities of platforms that either is, or can be seen as, a network of components without imposing restrictions on the type of the components or the topology of the network.

#### 1.4.1 Platform Capability Analysis Challenges

In the following, we will give two examples of some of the problems that makes analyzing the capabilities of a platform a challenge.

#### 1.4.1.1 Localization of Services

Since modern embedded platforms are increasingly based on heterogeneous multicore architectures, the services offered by the different programmable elements are very likely to differ. As a consequence, talking about the services provided by the platform as a whole is too simplistic, instead we have to focus on the services provided at the different *points-of-contact* between the platform and its application. Example 1 illustrates this.

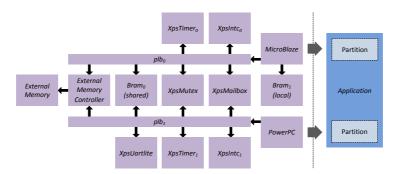

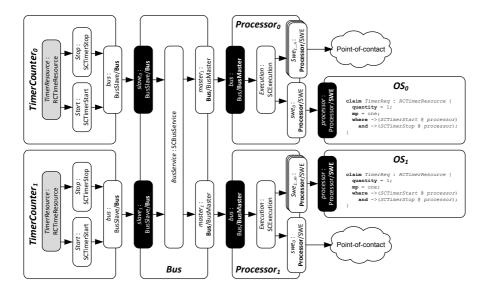

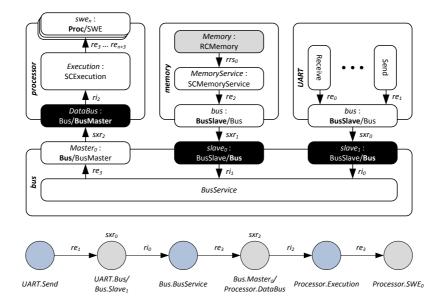

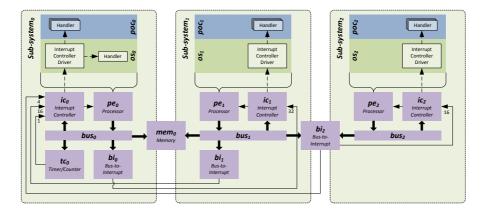

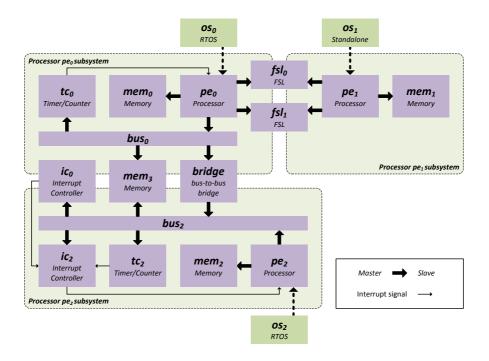

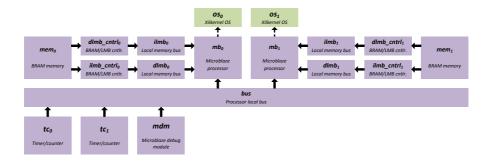

**Example 1.1** Figure 1.5 shows a relatively simple multi-processor platform created using the *Xilinx Embedded Development Kit* tool. The platform is taken from an official application note published by Xilinx for demonstrating multi-processor designs using the tool. The platform consist of two processors, a Mi-

**Figure 1.5** – Multi-processor platform created using the *Xilinx Embedded Development Kit*. Source: Xilinx Application Note, [12]

croblaze and a PowerPC, and a number peripheral cores. Each of the processors are connected to a private bus through which each of them may access a subset of the peripheral in the platform. The sets of peripherals accessible from each of the two processors are given below:

| From Microblaze            | From PowerPC               |  |  |

|----------------------------|----------------------------|--|--|

| Microblaze                 | PowerPC                    |  |  |

| Plb0                       | Plb <sub>1</sub>           |  |  |

| XpsTimer <sub>0</sub>      | XpsTimer <sub>1</sub>      |  |  |

| XpsIntc <sub>0</sub>       | XpsIntc <sub>1</sub>       |  |  |

| External Memory Controller | External Memory Controller |  |  |

| External Memory            | External Memory            |  |  |

| $\texttt{Bram}_0$          | $\texttt{Bram}_0$          |  |  |

| XpsMutex                   | XpsMutex                   |  |  |

| XpsMailbox                 | XpsMailbox                 |  |  |

| Bram <sub>1</sub>          | XpsUartlite                |  |  |

It is obvious that the two sets are different. For example, only software executing on the PowerPC will be able to use the UART (XpsUartlite) and although the platform features two timer peripherals only one can be accessed from each processor.

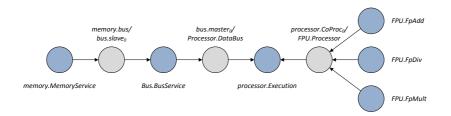

Peripherals accessible from several points-of-contact may be accessed differently depending on the point of contact. A dual-port memory, for example, can be mapped to different segments of the address spaces of two different processors.

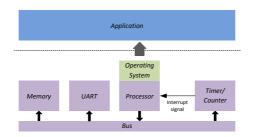

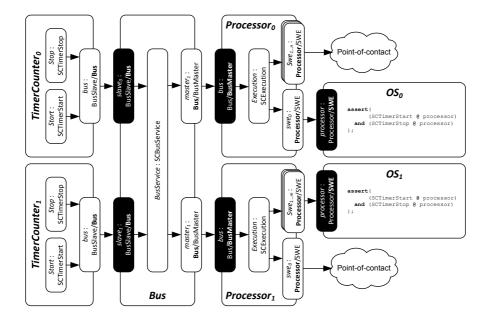

**Figure 1.6** – A simple single processor platform. The Timer/Counter peripheral is not part of the capabilities of the platform since it is used internally by the operating system.

#### 1.4.1.2 Resources

The services offered by a network of components comprising a platform at a given point-of-contact is not simply the sum of the services accessible from that point. Some services are only available in finite quantities and may be used internally by the platform as is illustrated by the next example.

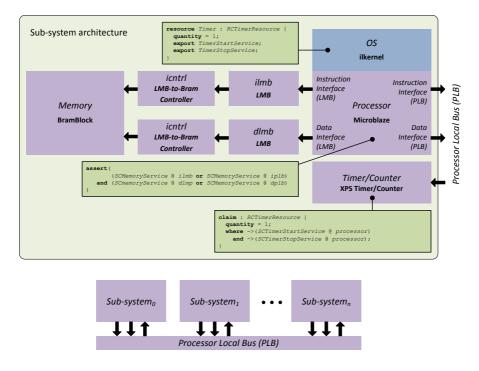

**Example 1.2** Consider the simple platform of figure 1.6. The hardware of platform consists of a single processor, a bus and a handful of peripheral cores including a timer/counter. Besides the hardware the platform also includes an operating system featuring time-sliced multiprocessing executing on the processor. In order to provide multiprocessing, the operating system requires (exclusive) access to the timer/counter and, consequently, the services provided by the timer/counter peripheral is not part of the capabilities the platform.

#### 1.4.2 Case Study: Xilinx Embedded Development Kit

Field Programmable Gate Arrays (FPGA) is an example of a class of platforms that provides a high degree of customizability. The use of FPGA's have traditionally been associated with a long time-to-market compared to the use of microcontrollers. The reason for this is that FPGA's must be "programmed" using hardware description languages such as VHDL or Verilog. Today, however, tools exists that can generate synthesizable designs for FPGA's from higher-level models eliminating the need for the hardware description languages. Two such tools are the *Embedded Development Kit* [97] from Xilinx and the *System-on-a-Programmable-Chip Builder* [9] from Altera. These tools allows for an

FPGA to be configured as a customized computing platform complete with programmable processors, peripherals and sophisticated interconnects. Another tool is the System Generator [98] that can be used as a backend to Simulink for realizing DSP algorithms in programmable logic. In the terms of platform-based design, these tools may represent an abstraction layer above the FPGA platform.

Of special interest to this thesis are the before mentioned tools for configuring an FPGA as a more general purpose computing platform. Next, we will present a few shortcomings of the Xilinx Embedded Development Kit tool that are representative for the more general issues addressed in this thesis.

#### 1.4.3 Xilinx The Embedded Development Kit

The Xilinx Embedded Development Kit (EDK) consists of a number of integrated tools for developing embedded processor systems based on the Microblaze [101] and PowerPC [99] processors targeting the Xilinx line of FPGA's.

The *Platform Studio* tool is a graphical system editor used for assembling computing platforms using a rich library of existing IP-cores. Among the provided cores are a number of different buses and point-to-point links that can be mixed in a platform to provide a custom communication infrastructure. Additional cores, written in VHDL or Verilog, can easily be added to the library if they implement an interface to one of the supported buses or point-to-point links. A core in the library is organized as a set of parameterized VHDL or Verilog files and a high-level description of its interfaces and possible configurations. Platform Studio generates a hardware specification, in the form of a Microprocessor Hardware Specification (MHS) file, specifying a set of IP core instances, their configurations and the connections between them.

A deployable bitfile is generated on the basis of an MHS file using the *Platgen* tool. This tool first generates a description of the system in a hardware description language and then it uses the Xilinx ISE implementation flow to synthesize the bitfile. Because of the hardware synthesis involved, running Platgen can be quite time consuming. It can easily take up to 15 to 20 minutes to synthesize even relatively small designs. Before attempting to generate a bitfile, the MHS file is subjected to a verification/consistency check using TCL scripts.

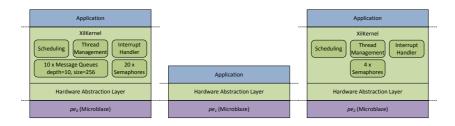

The EDK also comprises a number of tools supporting the development of software for hardware platforms generated using the Platform Studio and Platgen tools. The most interesting of these tools is the *Libgen* tool – a tool for generating libraries and drivers for the processors of a platform. This tool takes as input a MHS file specifying a hardware platform and a Microprocessor Software Specification (MSS) file created by hand or using the Platform Studio graphical IDE. The MSS file specifies the drivers associated with peripherals, which peripherals should be used for standard input/output and other software related features. Libgen can also be used to configure an operating system for each processor in the platform. The EDK is shipped with a single operating system called *Xilkernel* [102]. The Xilkernel operating system can be configured to include a number of optional features such as semaphore and message queue support.

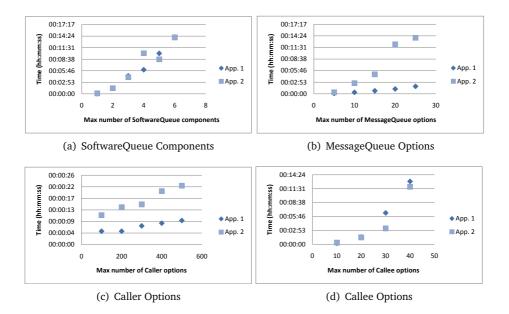

#### 1.4.3.1 Issues

Using the tools of the EDK to create sophisticated systems is surprisingly easy. There are, however, some limitations in the tools that indirectly restricts the freedom of the designer. More specifically, the analysis capabilities of the Libgen tool are too limited and based on assumptions about the IP cores used as well as on how the communication infrastructure is realized. In order to make use of the Libgen tool these assumptions must be justified which in practice limits the freedom of the designer.

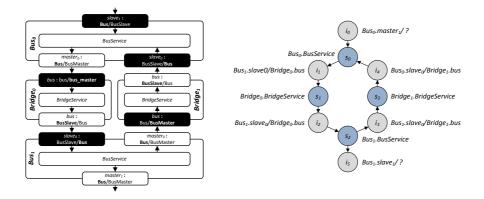

Based on our experience with the EDK, we believe that the identification of the set of peripherals reachable from a processor is done in the following way: First the processor in question is located. Next, the buses connected to the processor are enumerated. Finally, the slave attachments of these buses are added to set of reachable peripherals. For this to be possible, the analysis backend must know which components represent buses and processors. It should be noted that this is speculation as the documentation [100] does not describe the analysis capabilities of the tools in any kind of detail. Our experiments shows that the analysis back-end of the EDK fails to locate peripherals that are indirectly connected the address space of a processor through a bridge. More specifically, the Libgen tool fails with a somewhat arcane error message stating that there was an error in the address specification.

Furthermore, the component-model underlying the EDK tool does not model resources. For example, the Xilkernel operating system requires a timer of the type XPS Timer/Counter or *fit timer* to provide it with the ticks necessary to implement time-sliced multitasking. The XPS Timer/Counter is a standard busmounted peripheral accessible via a set of memory mapped registers. In order to work, the timer/counter must be connected so that its memory mapped registers are accessible from the processor running the operating system. Also, the interrupt port of the timer/counter must be connected to the processor either directly or indirectly via an interrupt controller. Our experiments has shown that it is possible to create a dual processor design with two Xilkernel operating systems using the *same* timer/counter instance. This error is not caught at design

time. One could argue that, in theory, two identical operating systems could use the same timer for generating ticks. This, however, is most likely not the case with the Xilkernel as the time between ticks is a customizable parameter.

From the point of view of the end-user, the real problem is not so much the shortcoming of the analysis back-end but rather the lack of proper error detection and reporting. Debugging a complex system can be a very time consuming process. This is especially true if the error does not show up at design time so that hardware synthesis must be re-run for each iteration of the debug cycle.

### 1.5 Contributions

We have developed a formalism called the *Service Relation Model* for describing systems composed of components based on the novel concepts of service aggregation and service exchange relations. The formalism can be used to create re-usable abstract descriptions of hardware and software components that may be combined into models of platforms and systems. The resulting models may be analyzed to obtain information about service availability and flow. We consider the Service Relation Model and the associated analysis method the main contribution of this work.

To demonstrate the usefulness and versatility of the proposed model we have developed a number of procedures and associated proof-of-concept tools for assisting the designer in tasks related to component integration and low-level programming:

- **Consistency Checking.** A procedure for checking the consistency of a platform or system modeled as a network of re-usable components with respect to service and resource availablity. Using our consistency checking procedure, we are able to capture some inconsistencies that will show up as run-time errors in industry standard component-based design tools.

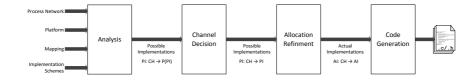

- Automated Programming. A procedure for automatically generating an application-specific abstraction layer implementing the communication infrastructure of an application given as a process network. The procedure uses a Service Relation Model representation of a platform for determining different implementation alternatives and for code generation purposes.

- Automated Design Generation. A procedure for automatically transforming an inconsistent model of a system into a consistent model by allocating, configuring and inserting new components into the model. This

procedure has a number of different uses in the context of "automated design generation" and generalizes the analysis and decision making parts of the procedure for automated programming.

All of the three procedures are central contributions to this work. The proofof-concept tools supporting the different procedures are all based on a common framework, called the xSRM framework, for working with service relation models that we also consider an important, albeit theoretically less interesting, contribution.

## 1.6 Thesis Outline

This thesis is organized as follows: In chapter 2, the basic concepts of the Service Relation Model and its associated analysis method are presented. In chapter 3, a number of additional concepts are added to the basic Service Relation Model that forms the basis of the procedure for consistency checking presented in the same chapter. This chapter also contains an overview of related work. The procedure for automated programming is presented in chapter 4 followed by the presentation of the procedure for automated design generation in chapter 5. Chapter 6 contains the concluding remarks.

## Chapter 2

## **The Service Relation Model**

The Service Relation Model, presented in this chapter, is an abstract componentcentric model used to extract information about the capabilities of a system given as a network of components. The model does not impose any restrictions on what a component is and may be used to describe platforms and systems comprised of both hardware and software. The Service Relation Model is an analysis model, as opposed to a composition model, meaning that it is primarily intended to analyze systems created using other tools and models. A key feature of the model is that it allows for re-use of component descriptions by separating the definition of components from any actual model.

This chapter is organized as follows: The first section contains an informal introduction to the basic concepts of the Service Relation Model. After the informal introduction the basic concepts are formalized with the intent of providing a precise and unambiguous presentation.

## 2.1 Informal Presentation

Most models supporting component-based design of execution platforms (e.g. [97, 9]) employs the basic concepts of components, interfaces and connections.

In these models, a component represents a physical entity such as a processor, bus or a block of memory. Likewise, an interface represents a physical connection point where a component may be connected to another component with a matching interface. The *Service Relation Model* extends this line of thought to also include conceptual components and conceptual connections (called *relations*). In other words, the components of the service relation model need not necessarily have a physical manifestation and their relationships (connections) can be conceptual as well as physical.

The components of the Service Relation Model are defined by the service or services they offer to other components. A service can be any kind of work that a component carry out on behalf-of another component. As an example, consider a bus: the ability of a bus master attachment to issue read and write requests to slave attachments can be seen as a service provided by the bus to the master attachment. A component representing a function in the C programming language might be considered to provide other components with the service that it describes. The service relation model explicitly separates the concept of a service and its provider (a component).

The Service Relation Model supports only one kind of binary relations called service exchange relations. A service exchange relation is characterized by facilitating some kind of exchange of services between two components. The relation between a bus master attachment and a bus is an example of such a relation since the bus master attachment may request service from the bus. Similarly, a software module may have a service exchange relationship with its processor because it, conceptually, is serviced by the processor. On the other hand, a relation stating that two components are identical is not a service exchange relation because no exchange of service can be attributed to it. A service exchange relation consists of three parts: the relation itself and two roles (the subject and the object). A component in the Service Relation Model exposes its services through a set of interfaces each of which is associated with exactly one role of a predefined service exchange relation. Two components may be connected to each other, using a service exchange relation, only if one of the components define an interface with the subject role of the relation and the other define an interface with the object role of the relation (see Figure 2.1). The flow of service through service exchange relations is unidirectional and service always flow from the object interface to the subject interface.

Besides the service exchange relation the model supports two additional relations: *service import relations* and *service export relations*. In contrast to service exchange relations, the service import and export relations are used inside components to relate services and interfaces to each other. An export relation states that a given service is exported to a given interface. Recall that we said that the services of a bus are provided *to* its master attachments. In the Service Relation

**Figure 2.1** – **a.** A service exchange relation modeling the relationship between a bus master and the bus. **b.** The same relation used to relate the data bus interface of a processor with a bus (note: role names are not included but suggested with the coloring of the boxes representing interfaces).

Model, this is modeled by an export relation relating the bus services with the interfaces representing the bus role of a bus-master/bus service exchange relation. A service exported to an interface is said to be *available* at that interface. Services available at an interface are also considered to be available at the interface of another component if the two interfaces are (properly) connected by means of a service exchange relation.

The import relation facilitates *service aggregation* which essentially is an "available through" relationship between any services available at an interface and a service defined in the component. A service representing the ability to execute software on a RISC processor can be said to aggregate services of its attached data bus since the services of the bus may be invoked using the memory LOAD and STORE instructions of the processor. A driver is another example of service aggregation. The service offered by a driver aggregates the service offered by the underlying device. A service aggregated by another service is considered available at that service and at any interfaces and services where the aggregating service is considered available.

#### 2.1.1 Example: Hardware Platform

As an example, we will consider a simple hardware platform consisting of a memory, a bus, a processor core and a floating point co-processor (FPU). These four components are organized in the following way: The data bus interface of the processor is attached to the bus as a master attachment and the memory as a slave attachment. The FPU is an optional part of the processor core and thus the instruction set of the processor includes instructions for operations on floating point numbers. If the FPU is not included these instructions are undefined.

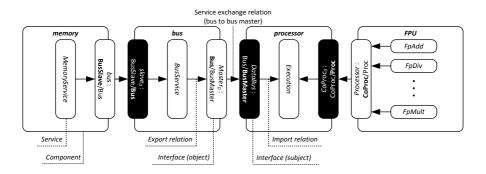

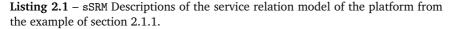

Figure 2.2 shows a graphical representation of a service relation model of

Figure 2.2 – A simple system described in the Service Relation Model.

the platform. In the graphical notation, a component is represented as a box with its name printed on it. An interface is represented as a box placed on the border of a component. Object interfaces are represented using white boxes and subject interfaces using black boxes. The text printed in the boxes representing interfaces (name : relation) gives the name of the interface as well as the relation to which it belongs. In this thesis, all relations names follows the same generic naming convention based on the types of the components that it relates. For example, the relation relating a bus slave to a bus is named *Bus*-*Slave/Bus* and, similarly, the relation relating a co-processor to the processor is named CoProc/Proc. Notice that the component with the role of the object is always mentioned first. Service exchange relations are represented as arrows connecting an object interface with a subject interface. Services are represented as boxes completely contained within the bounds of a component. A service is associated with a name printed inside it. Import and export relations are represented using arrows connecting interfaces to services and services to interfaces respectively.

Next, the meaning of the different parts of the model will be explained:

- Memory: The memory has a single object interface of type BusSlave/Bus meaning that it may participate in a single BusSlave/Bus relation in the role of the bus slave. The memory provides other parts of the system with the ability to read and write its data through its bus interface. The ability of the memory to be read and written is modeled using a service called MemoryService that is exported through the bus slave interface.

- Bus: The bus component has two interfaces a subject interface of type BusSlave/Bus and an object interface of type Bus/BusMaster. Consequently, the bus may participate in a maximum of two relations (in the

role of the bus). The function of the bus is to provide the bus master with (read/write) access to the bus slave. This is modeled using the service BusService that aggregates services available on slave<sub>0</sub> interface and is exported to the Master<sub>0</sub> interface.

- **Processor:** The processor provides the capability of executing software. This capability is modeled by means of a single service, called Execution, that represents the possible execution of one instruction of the processors instruction set. The service can import services from the data bus interface (where the bus is connected) because the data bus is accessible by means of the processors LOAD and STORE instructions. Similarly, the Execution service may import services from the co-processor interface because these can be accessed through the special FPU instructions of the processor. At this time, Execution service itself is not exported anywhere.

- **FPU:** The FPU component provides the processor with the ability to execute a set of predefined floating point instructions. Each of these instructions is modeled using an appropriately named service exported to the connected processor through the CoProc/Proc interface of the FPU component.

The components are related to each other using three different service exchange relations:

- Bus/BusMaster This relation represents a bus masters ability access services provided by a bus by issuing read and write requests to it.

- BusSlave/Bus This relation represents the ability of a bus to access services provided by slave peripherals by forwarding read and write requests.

- CoProc/Proc This relation represents a processors ability to use a coprocessor. The understanding here is that only services representing a predefined set of FPU instructions can be propagated through the relation.

It is important to note that even though the names of the components, services and service exchange relations are fairly generic the intention is that they refer to actual components rather than abstract classes. For example, the processor component represents a concrete processor rather an unspecified instance of a generic processor type and, similarly, the BusSlave/Bus service exchange relations represents a relation between a specific type of bus and components implementing a compatible slave interface. Using the information asserted in the model and our knowledge of the meaning of the different concepts we can determine the availability (or accessability) of the 11 services in the model. Below the services available at the different interfaces and service of the model is given:

```

SA[memory.MemoryService] = { memory.MemoryService }

SA[memory.bus] = { memory.MemoryService }

SA[bus.slave_0] = { memory.MemoryService }

SA[bus.BusService] = { memory.MemoryService, memory.BusService }

SA[bus.Master_0] = { memory.MemoryService, memory.BusService }

SA[bus.Master_0] = { memory.MemoryService, memory.BusService }

SA[processor.DataBus] = { memory.MemoryService, memory.BusService }

SA[processor.Execution] = { memory.MemoryService, memory.BusService, memory.BusService, memory.BusService

```

The sets above describe the availablity of the services in the model and this can be considered an abstract representation of the capabilities of the platform. From the information contained in the sets we may, for example, infer that software executing on the processor can access the memory and it may use the floating point instructions provided by the attached co-processor because the services representing these capabilities are available through the Execution service representing the instruction set of the processor.

## 2.1.2 Example: Software

The next example will show how the Service Relation Model can be used to model software and how such a model can be combined with a model of a hardware platform.

As an example of an application, we will use a simple program for solving quadric equations. A quadric equation,  $ax^2 + bx + c$ , is defined by means of three real values (*a*, *b* and *c*) and has two solutions (*r*<sub>0</sub>, *r*<sub>1</sub>)) given by:

$$r_0, r_1 = \frac{-b \pm \sqrt{d}}{2a}, \qquad D = b^2 - 4ac$$

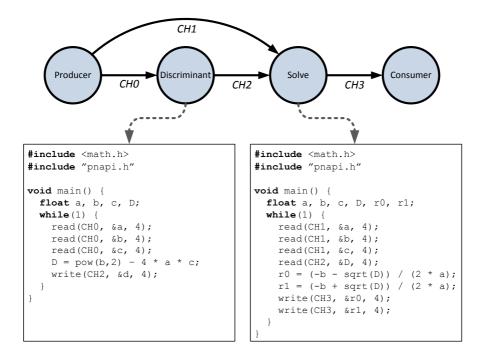

Figure 2.3 – Process network for solving quadric equations.

where D is the discriminant.

Figure 2.3 shows a process network for a simple application for solving quadric equations. The network has a four processes (Producer, Discriminant, Solve and Consumer) and four channels (CH0, CH1, CH2 and CH3). The Producer process produces data for the process network by continuously writing three values (a, b and c) to both of the channels CH0 and CH1. The Discriminant process reads the values of the variables a, b and c from channel CH0, computes the discriminant and writes the result to channel CH2. The Solve process reads the values of a, b and c from channel CH1 and the value D of the discriminant from channel CH2. The process then computes the two solutions to the equation and writes the result to channel CH3. The last process, Consumer, continuously reads pairs of values representing solutions to quadric equations from the channel CH3.

A C code implementation of the two processes Discriminant and Solve is also shown in figure 2.3. Each of the two processes are given as a standalone C program. Both processes uses functions from the math library and from a li-

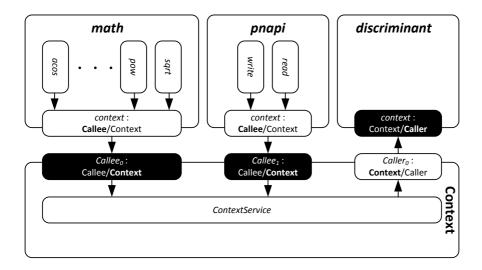

**Figure 2.4** – Service relation model of the C program implementing the discriminant process.

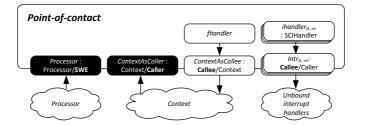

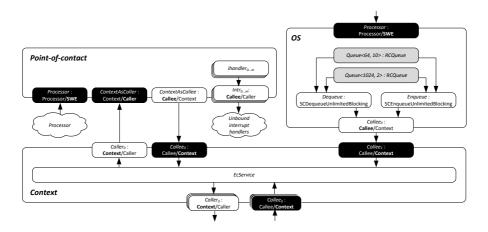

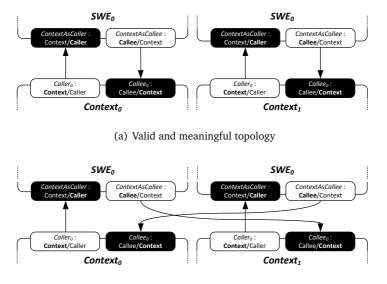

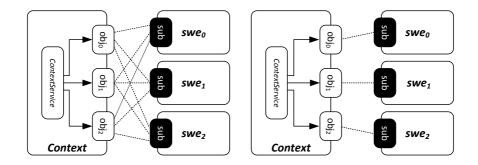

brary pnapi that implements a simple API for accessing channels in a process network. The channels of the process network are accessed by means of two function read and write. Figure 2.4 shows a service relation model of the C program implementing the discriminant process. The model consists of four components representing the math library, process network API, the discriminant main function and a context. The context components represents the "execution context" of a program – the conceptual infrastructure through which the different entities of the program communicates. The components of Figure 2.4 are related to each other by means of two different service exchange relations:

- **Callee/Context.** The Callee/Context service exchange relation models a relation between two components where the object provide C functions that are made accessible through a context (the subject).

- **Context/Caller.** The Context/Caller service exchange relation models a relation where the subject can access C functions available in a context (the object).

The context component and the two relations allows us to model the accessibility of functions in a C program. From Figure 2.4 we may infer that the discriminant component has access to the services of both the math library and the process network API.

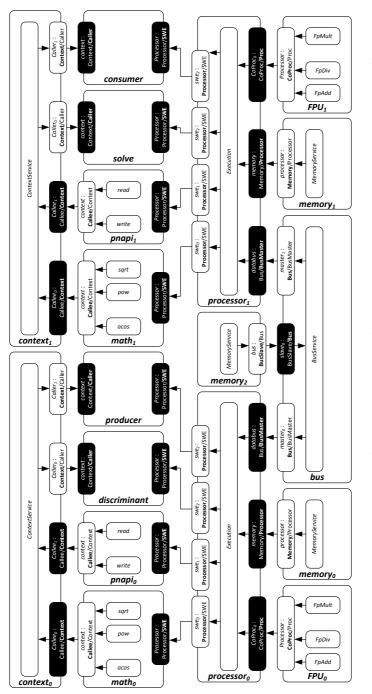

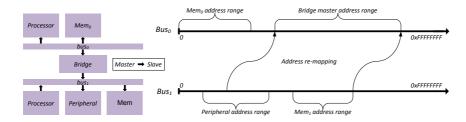

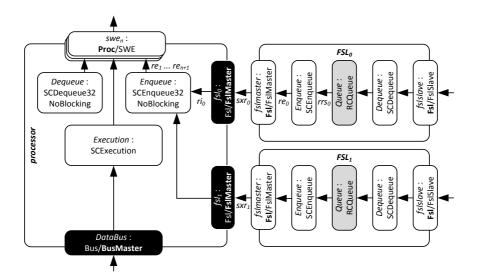

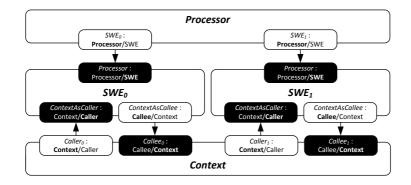

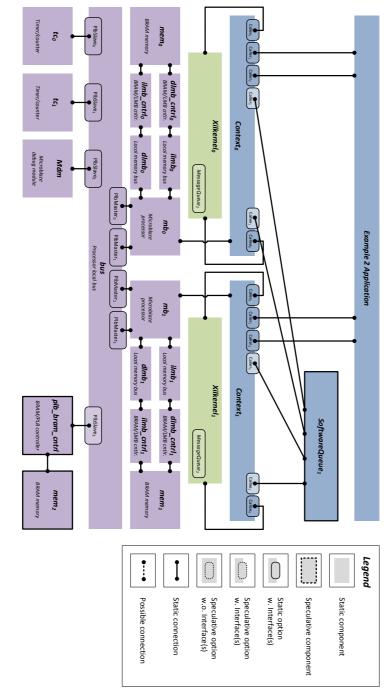

Figure 2.5 shows a service relation model of the process network from Figure 2.3 mapped to a simple dual-processor platform. The platform consists of two processors (Processor<sub>0</sub> and Processor<sub>1</sub>) connected to a shared bus (Bus). Besides the bus, each of the processors are also connected to a local memory (Memory<sub>0</sub> and Memory<sub>1</sub>) and a floating point co-processor (FPU<sub>0</sub> and FPU<sub>1</sub>). A third memory, Memory<sub>2</sub>, is connected to the shared bus and is used for interprocessor communication.

In the model, the Producer and Discriminant processes are mapped to Processor<sub>0</sub> and the other two processes, Solve and Consumer, to Processor<sub>1</sub>. The programs executing on the two processors of the platform are modeled using two context components to which the components representing the four processes are mapped. Each context is related to a total of four other components – two processes, a component representing the math library and a component representing the process network API. Besides being related to a shared context component, the four components are also related to the processor that they execute on. This is done by means of the service exchange relation Processor/SWE where SWE is short for "software entity". These relations provides the means for relating the capabilities (services) offered by a processor through its instruction set to the software entities in the program executing on the processor.

Using the information embedded in the model of Figure 2.5 we may infer a number of interesting things about the system. First, we can check if the processes are properly mapped meaning that they have access any services they may require to function properly. Below the sets of services available at the Context and Processor interfaces of the Discriminant component are given:

Looking at these sets we can conclude that the process is indeed properly mapped because it has access to an Execution service needed for basic execution, the pow service needed to compute the value of the discriminant, the read and write functions for accessing channels and, finally, a set of services needed for doing computations on floating point values. In the model, we assume that the process network API implements the communication infrastructure of the process network. This means that all processes that can access a pair of write and read functions can somehow, magically, communicate. Obviously, this imposes some requirements on the two components representing the process network API's. Assuming that communication between two process network API's can be accomplished by means of shared memory we can check if communication is in fact possible. To do this, we compute the intersection of the sets of services available at the Processor interfaces of the two process network API components. If the result contains one of the MemoryServices in the system then a memory exists that can be accessed from both components and, consequently, communication is possible.

This example shows one way to model software using the Service Relation Model. Depending on the purpose of the model other ways may be more appropriate.

# 2.2 Basic Concepts

The Service Relation Model is based on a number of novel concepts that will be explained in this section.

Fundamental for this thesis and the Service Relation Model is the concept of *service aggregation* which was conceived during the early phases of the project ending in the writing of this thesis. Service aggregation is a relation between two services stating that one is accessible through the other. These kinds of relations is the basic building block of the Service Relation Model. Service aggregation is, per definition, a transitive relation meaning that if we know that service  $s_0$  is aggregated by service  $s_1$  and that service  $s_1$  is aggregated by service  $s_2$  then we may infer that  $s_0$  is also aggregated by (accessible from)  $s_1$ . Using service aggregation relations, the service of some system can be arranged in a graph representing the flow of service in the system. Using such a graph, the service flow of a model can be analyzed with the aim of determine which services are accessible where.

When dealing with platforms or systems given as a network of re-usable components information about service aggregation is not readily available. This is so because the (re-usable) components are defined in isolation of each other and, in general, are not based on assumptions about the context in which they are used. For example, the description of a component representing a hardware bus consisting of a single service cannot contain a list of the services of other components that are aggregated by its service simply because the set of components to which the bus is connected is not known. When defining a component one usually knows something about the types of components that it may be immediately connected to. For example, the hardware bus component will always be connected to components implementing a compatible slave and/or master interface. In the Service Relation Model, service aggregation relations between services of different components are established in-directly through interfaces and service exchange relations. Service exchange relations defines relations between two classes of components (e.g a specific bus and its compatible slaves) and interfaces acts as proxies when defining the service flow.

In order to more clearly understand service aggregation and, more importantly, what needs to be true in order for an import or export relation to be justified we first need a way to more formally describe the phenomenon represented by services and service exchange relations. In the following, a characterization of services and service exchange relation based on the concept of functions will be presented. This characterization can be used to more formally define what is service aggregation is – and what it is not.

# 2.2.1 Service Characterization

Most people have an intuitive idea about what a service is and will agree that a service is "some work" that an individual does on behalf-of another individual. Here, an individual can be anything ranging from a person to a conceptual component. A service in the Service Relation Model represents the potential for service rather than the use of it. When we say that "*a* provides *b* with service *c*" it means that the service *c* is at the disposal of the component *a*. A given component can provide the same service to several other components and it may provide different services to different groups of other components. Knowing what services a given component provides to other components is the same as knowing the capabilities of the component. In other words, a service can be considered a capability – a possibility of performing some function.

The Service Relation Model is exclusively concerned with services that can, and must be, actively invoked by a service consumer in order for them to carry out their function. This is as opposed to services that are randomly or continuously being provided to the consumer without the consumers explicit consent. A service can be described as a function taking *n*-inputs and returning *m*-outputs:

$$\langle o_0, \ldots, o_m \rangle = ServiceName(i_0, \ldots, i_n)$$

Intuitively, such a service can be invoked by a service consumer by providing a proper valuation of its inputs. The invoked service may produce zero or more

outputs that are passed back to the service consumer. In keeping with the terminology of functions, the set of possible inputs to a service is called the *domain* of the service and the set of possible outputs the *range* of the service. The domain D(s) of a service s is defined as the Cartesian product of the domains of the inputs:

$$D(s) = I_0 \times \ldots \times I_n$$

and, similarly, the range R(s) as the Cartesian product of the domains of the outputs:

$$R(s) = O_0 \times \ldots \times O_m$$

The domain of a service is allowed to contain elements that does not represent a proper service invocation (i.e. invalid valuations of its inputs) as well as multiple elements that will result in the invocation of the same functionality. This provides an additional degree of freedom in choosing the domain used to describe a service which helps to make the description more intuitive.

Note that a service is not a proper mathematical function because it represents a phenomenon that is allowed to have side effects and whose outputs may depend on the state of the system in addition to its inputs. Also, in the Service Relation Model, services are abstractions meaning that we do not concern ourselves with the definition of the behavior or function implemented by the service.

**Example 2.1 (Memory Access Services)** Services representing access to memory are quite common. Such services can be represented using four inputs and one output:

where  $op \in \{rd, wr\}$  specifies the type of operation (read or write),  $w \in \{1, 2, 4\}$  specifies the width of the access (1, 2 or 4 bytes),  $addr \in \mathbb{N}_0$  specifies the address to be accessed and  $val \in \mathbb{Z}$  the value to be written in case of op = wr. The MemoryService and BusService from the previous examples are examples of such services.

**Example 2.2 (Functions)** The service representation of C functions is straightforward: one output representing the function return value and a single input for each function argument:

$$\langle result \rangle = FunctionName(arg_0, arg_1, \dots, arg_n)$$

For example, the power function of the C math library can be modeled as  $\langle result \rangle = pow(a, b)$  where  $result, a, b \in \mathbb{R}$ .

**Example 2.3 (Execution)** Another interesting, and often used, class of services is the monolithic Execution service of processors. The inputs and outputs of this service is highly dependent upon the actual processor and, in general, not trivial to describe. Fortunately, we can get around this by assuming that the services of a processor are accessed through a high-level language such as C.

For a given processor only a selection of instructions will be used to access services provided by the connected hardware. Common examples of such instructions are the LOAD and STORE instructions of a RISC machine. Assuming that a high-level function wrapper (e.g. void load(int\* addr)) is available for each of these instructions, the execution service can be described as:

```

\langle result \rangle = Execution(name, arg_0, arg_1, \dots, arg_{max})

```

where *result* is the return value, *name* is the name of the wrapper function,  $arg_x$  is an argument and *max* is the maximum number of arguments any function can take. Notice that many of the combinations of inputs for this function does not correspond to a proper invocation of the execution service. For example, the valuation *load*, *void*, 10, 10, ... *void* does not make sense.

### 2.2.2 Service Exchange Relation Characterization

Like services, the phenomenon represented by service exchange relations may also be described using functions. The purpose of such a function is to define the possible service requests (inputs) and results (outputs) that may pass through a particular service exchange relation. In comparison with the functions describing services, the functions describing service exchange relations does not represent any "work" to be done at run-time. As was the case for services, the Cartesian product of the domains of the inputs of a service exchange relation is called the *domain* of the relation and, similarly, the Cartesian product of the domains of the outputs the *range* of the relation.

**Example 2.4 (Memory Interfaces)** A common way of interfacing hardware components is through memory interfaces where a master component may access a slave by issuing read and write requests. The function signature describing a service exchange relation representing a memory interface can be given as:

$$\langle val \rangle = BusToBusSlave(op, w, addr, val)$$

where  $op \in \{rd, wr\}$  specifies the type of operation (read or write),  $w \in \{1, 2, 4\}$  specifies the width of the access (1, 2 or 4 bytes),  $addr \in \mathbb{N}_0$  specifies the address

to be accessed and  $val \in \mathbb{Z}$  the value to be written in case of op = wr. Notice that the function has exactly the same inputs and outputs as the function used for describing memory access services.

**Example 2.5 (Function Invocation)** The service exchange relations the Context/Caller and Callee/Context representing the exchange of service between a context and a software entity using function invocation can be described as:

$$\langle result \rangle = FunctionSxr(name, arg_0, arg_1, \dots, arg_n)$$

where *name* is the domain of valid function names, *n* is the maximum number of allowed arguments a function can take and  $arg_x$  is an input representing the value of an argument.  $arg_x$  is in the domain  $TYPE \cup \bot$  where TYPE is the domain of values for the corresponding type and  $\bot$  represents "not used".