### Technical University of Denmark

### **Design Techniques for Sub-micron RF Power Amplifiers**

Fallesen, Carsten

Publication date: 2001

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Fallesen, C. (2001). Design Techniques for Sub-micron RF Power Amplifiers.

### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Carsten Fallesen

## Design Techniques for Sub-micron RF Power Amplifiers

PhD thesis

Nokia Mobile Phones and Department of Information Technology Technical University of Denmark

May 2001

# Design Techniques for Sub-micron RF Power Amplifiers

**Carsten Fallesen**

**Nokia Mobile Phones**

Department of Information Technology Technical University of Denmark

#### Abstract

In the last couple of years there has been an increased focus on integrated RF power amplifiers for wireless communications, especially mobile phones. The drivers of the development high integration and low cost. The highest integration possible will most probably be achieved with CMOS processes. At the same time CMOS is without doubt the cheapest process available.

To be able to reach the goal some theory on RF power amplifiers is necessary. The different classes of operation are explained, then the principles of impedance matching is discussed. This includes the development of the simulated load-pull method and synthesis of impedance matching networks. Then the biasing of the power amplifier is discussed along with the stability issues.

The choice of CMOS as a preferred technology for the power amplifier is justified. The issues of modeling a complete power amplifier is treated. This includes modeling of the transistors, the passive devices on-chip and off-chip as well as the package and PCB. To ease the design of power amplifier a design method is developed based on the theory and the experimental work.

At last the experimental work is described. The first part is a linearization system based on digital predistortion. The digital predistortion can be used to increase the overall efficiency of varying envelope systems. Then three CMOS power amplifiers designed during the project are introduced. The last of these power amplifiers shows superior performance when compared to other CMOS power amplifiers. The output power of this power amplifier is 30.4dBm with a power added efficiency of 55%. The last power amplifier utilizes the design method develop as well as the models described. The accurate modeling combined with superior performance proves the future of integrated CMOS power amplifiers for wireless communication.

#### **Resume (Danish)**

I de seneste år har der været øget fokus på integrerede RF effektforstærkere til trådløs kommunikation, især mobiltelefoner. Det der har drevet udviklingen er især ønsket om høj integration og lav pris. Den højeste integration vil formentlig ske i en CMOS teknologi. Samtidigt er CMOS uden tvivl den billigste teknologi der er til rådighed.

For at nå målet er det nødvendigt at gennemgå den basale teori om RF effektforstærkere. De forskellige klasser af forstærkere bliver forklaret, efterfølgende bliver teorien bag impedans tilpasning diskuteret. Dette inkluderer udviklingen af en metode til simuleret load-pull og syntese af impedans tilpasnings netværk. Derefter bliver biasing af effektforstærkere diskuteret sammen med stabilitet af effektforstærkere.

Valget af CMOS som den fortrukne teknologi til effektforstærkere bliver begrundet. Spørgsmålene omkring modellering af komplette effektforstærkere bliver behandlet. Dette inkluderer modellering af transistorerne, de passive komponenter på og udenfor den integrerede kreds såvel som pakken og printkortet. For at lette udviklingen af effektforstærkere er en design metode blevet udviklet baseret på både teorien og det eksperimentelle arbejde.

Til sidst bliver det eksperimentelle arbejde beskrevet. Den første del er et lineariserings system baseret på digital predistortion. Den digitale predistortion kan bruges til at øge effektiviteten i systemer med varierende amplitude. Efter det bliver tre CMOS effektforstærkere der er blevet udviklet i løbet a projektet beskrevet. Den sidste af disse effektforstærkere udviser bedre egenskaber end nogen anden CMOS effektforstærker. Denne effektforstærker giver en udgangseffekt på 30.4dBm med en effektivitet på 55%. Den sidste effektforstærker blev udviklet ved hjælp af den nye design metode sammen med de modeller der bliver beskrevet. Den præcise simulering sammen med de uovertrufne egenskaber demonstrerer fremtiden i integrerede CMOS effektforstærkere til trådløse produkter.

# **Table of Contents**

|   | Tab             | le of Contents                                                                         | ••   | V              |

|---|-----------------|----------------------------------------------------------------------------------------|------|----------------|

|   | List of Figures |                                                                                        |      | ix             |

|   | List of Tables  |                                                                                        |      | ciii           |

|   | Glo             | ssary                                                                                  | •    | xv             |

| 1 | Intr            | oduction                                                                               | ••   | .1             |

|   | 1.1             | Basics of RF Power Amplifiers                                                          |      | . 1            |

|   |                 | 1.1.1 Definitions of Efficiency         1.1.2 Definitions of Linearity                 |      |                |

|   | 1.2             | Mobile Phone Standards                                                                 |      | . 4            |

|   |                 | 1.2.1 First Generation1.2.2 Second Generation1.2.3 Third Generation                    |      | . 5            |

|   | 1.3             | Summary                                                                                |      | .7             |

|   | 1.4             | Acknowledgements                                                                       |      | .7             |

|   |                 | References                                                                             |      | . 8            |

| 2 | Cla             | sses of Operation                                                                      |      | .9             |

|   | 2.1             | Class A through C                                                                      |      | . 9            |

|   |                 | 2.1.1 Knee Effect<br>2.1.2 Class A<br>2.1.3 Class B<br>2.1.4 Class AB<br>2.1.5 Class C | <br> | 15<br>16<br>16 |

|   | 2.2             | Class D and F                                                                          |      | 17             |

|   | 2.3             | Class E                                                                                |      | 18             |

|   | 2.4             | Class S                                                                                |      | 19             |

|   | 2.5             | Differential Power Amplifiers                                                          |      | 21             |

|   | 2.6             | Summary                                                                                |      | 21             |

|   |                 | References                                                                             |      | 22             |

| 3 | Loa             | d-Line Theory and Impedance Matching Networks .                                        |      | 23             |

|   | 3.1             | Small-Signal Impedance Matching                                                        |      | 23             |

|   |     | 3.1.1 S-Parameters3.1.2 The Smith Chart3.1.3 Transducer Gain Method3.1.4 Available Gain Method3.1.5 Operating Gain Method                                                                                                                                                     | . 24<br>. 25<br>. 27         |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|   | 3.2 | Large-Signal Impedance Matching                                                                                                                                                                                                                                               | . 30                         |

|   |     | 3.2.1 Load-Pull Contours                                                                                                                                                                                                                                                      | . 31<br>. 33                 |

|   | 3.3 | Synthesizing Impedance Matching Networks                                                                                                                                                                                                                                      | . 35                         |

|   |     | <ul> <li>3.3.1 Impedance Matching Basics</li> <li>3.3.2 Plotting Passive Components in the Smith Chart</li> <li>3.3.3 The L Matching Section</li> <li>3.3.4 The T Matching Section</li> <li>3.3.5 The Π Matching Section</li> <li>3.3.6 Cascaded Matching Networks</li> </ul> | . 36<br>. 36<br>. 38<br>. 39 |

|   | 3.4 | Summary                                                                                                                                                                                                                                                                       | . 40                         |

|   |     | References                                                                                                                                                                                                                                                                    | 42                           |

| 4 | Sta | bility and Biasing                                                                                                                                                                                                                                                            | .43                          |

|   | 4.1 | Bias Circuits                                                                                                                                                                                                                                                                 | . 43                         |

|   |     | 4.1.1 DC Isolation4.1.2 RF Isolation4.1.3 Generating the Bias Signals                                                                                                                                                                                                         | . 44                         |

|   | 4.2 | Stability of Power Amplifiers                                                                                                                                                                                                                                                 | . 45                         |

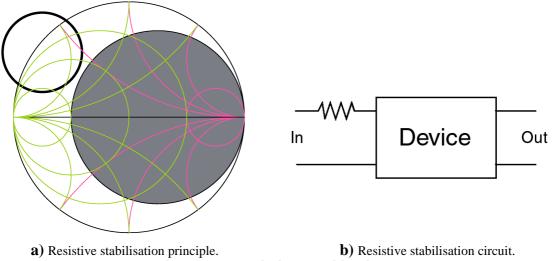

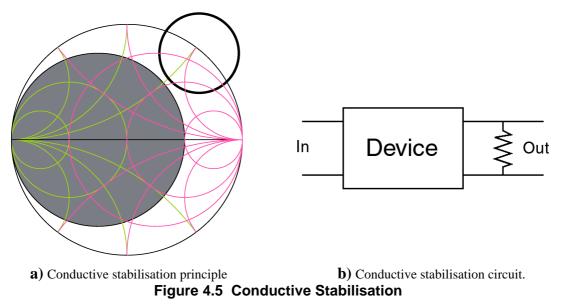

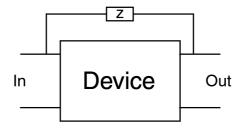

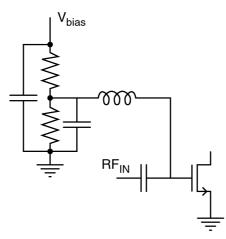

|   |     | <ul> <li>4.2.1 Stability Circles</li> <li>4.2.2 Resistive Stabilisation</li> <li>4.2.3 Conductive Stabilisation</li> <li>4.2.4 Feedback Stabilisation</li> </ul>                                                                                                              | . 46<br>. 47                 |

|   | 4.3 | Bias Circuit Instability                                                                                                                                                                                                                                                      | . 48                         |

|   | 4.4 | Verifying Stability through Simulations                                                                                                                                                                                                                                       | . 48                         |

|   | 4.5 | Summary                                                                                                                                                                                                                                                                       | . 49                         |

|   |     | References                                                                                                                                                                                                                                                                    | . 49                         |

| 5 | CM  | OS Technology                                                                                                                                                                                                                                                                 | 51                           |

|   | 5.1 | Basic RF CMOS Behavior                                                                                                                                                                                                                                                        | 51                           |

|   |     | 5.1.1 I-V Characteristics                                                                                                                                                                                                                                                     |                              |

|   | 5.2 | Comparison to Other Technologies                                                                                                                                                                                                                                              | . 53                         |

|   |     | 5.2.1 SOI                                                                                                                                                                                                                                                                     | . 54                         |

|   |      | 5.2.4 Silicon BJT                                                                                                                                                                               | 54                   |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|   | 5.3  | Simulation Models                                                                                                                                                                               | 55                   |

|   |      | 5.3.1 BSIM3         5.3.2 MOS9         5.3.3 EKV         5.3.4 BSIM4         5.3.5 Layout Related Issues                                                                                        | 55<br>55<br>56<br>56 |

|   | 5.4  | Modeling of Modules                                                                                                                                                                             | .56                  |

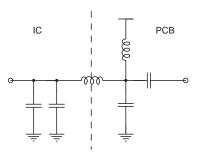

|   |      | 5.4.1 Capacitors5.4.2 Spiral Inductor5.4.3 Interconnects5.4.4 Packaging5.4.5 PCB5.4.6 Thermal Modeling                                                                                          | 57<br>57<br>58<br>59 |

|   | 5.5  | Summary                                                                                                                                                                                         | 60                   |

|   |      | References                                                                                                                                                                                      | 60                   |

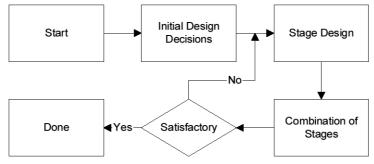

| 6 | Des  | ign Method for Integrated Power Amplifiers                                                                                                                                                      | 63                   |

|   | 6.1  | Initial Design Decisions                                                                                                                                                                        | .64                  |

|   |      | 6.1.1 Differential or Single-ended Operation6.1.2 Number of Stages6.1.3 Gain & Efficiency Budget                                                                                                | 64<br>64             |

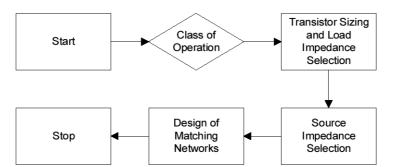

|   | 6.2  | Design of Individual Stages                                                                                                                                                                     | .64                  |

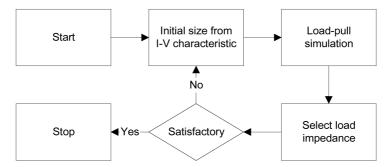

|   |      | <ul> <li>6.2.1 Class of operation</li> <li>6.2.2 Transistor Sizing and Load Impedance Selection</li> <li>6.2.3 Source Impedance Selection</li> <li>6.2.4 Design of Matching Networks</li> </ul> | 66<br>66             |

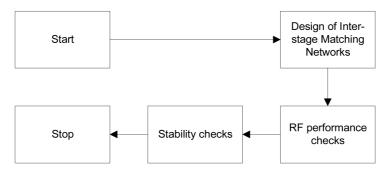

|   | 6.3  | Combination of Stages                                                                                                                                                                           | .67                  |

|   |      | <ul><li>6.3.1 Design of Interstage Matching Networks</li><li>6.3.2 Check RF Performance of Power Amplifier</li><li>6.3.3 Check Stability</li></ul>                                              | 68                   |

|   | 6.4  | Summary                                                                                                                                                                                         | 68                   |

|   |      | References                                                                                                                                                                                      | .68                  |

| 7 | Digi | ital Predistortion                                                                                                                                                                              | .71                  |

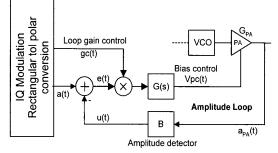

|   | 7.1  | Theory of Digital Predistortion                                                                                                                                                                 | .73                  |

|   |      | <ul><li>7.1.1 Digital Modulation of IS-95 Signal</li><li>7.1.2 Modeling of Nonlinearities</li><li>7.1.3 Predistorting a Nonlinear Signal</li></ul>                                              | 74                   |

|   | 7.2  | Implementation                                                                                                                                                                                  |                      |

|   |      |                                                                                                                                                                                                 |                      |

|   |     | 7.2.1 Equipment                                                                                                                                                                                                                       |                      |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

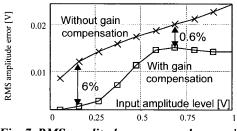

|   | 7.3 | Measurements                                                                                                                                                                                                                          | .76                  |

|   | 7.4 | Continued Work                                                                                                                                                                                                                        | . 77                 |

|   | 7.5 | Summary                                                                                                                                                                                                                               | .79                  |

|   |     | References                                                                                                                                                                                                                            |                      |

| 8 | Des | sign of CMOS Power Amplifiers                                                                                                                                                                                                         | . 81                 |

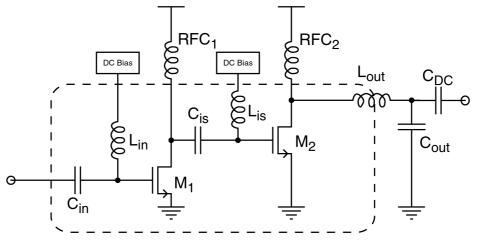

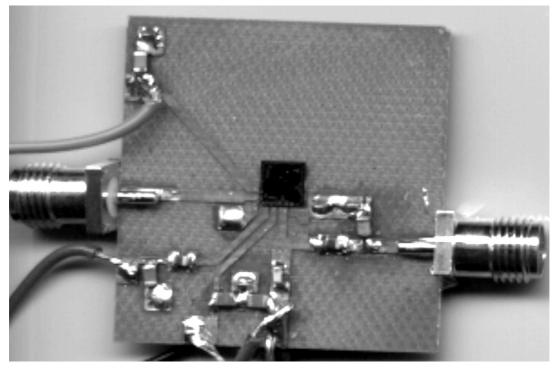

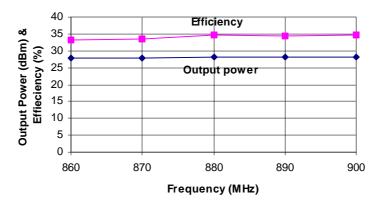

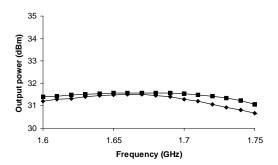

|   | 8.1 | The First CMOS Power Amplifier                                                                                                                                                                                                        | . 82                 |

|   |     | 8.1.1 Specifications8.1.2 Packaging8.1.3 Design of the Power Amplifier8.1.4 Measurements8.1.5 Summary of First CMOS Power Amplifier                                                                                                   | 82<br>83<br>84       |

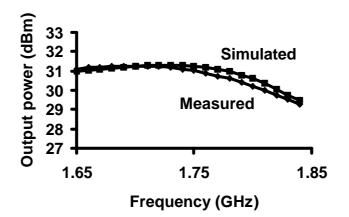

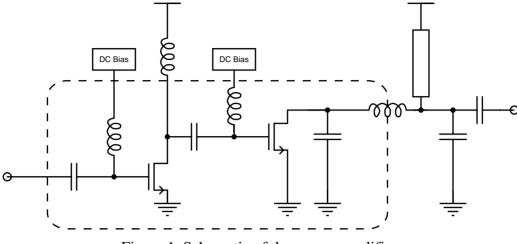

|   | 8.2 | The Second CMOS Power Amplifier                                                                                                                                                                                                       | . 86                 |

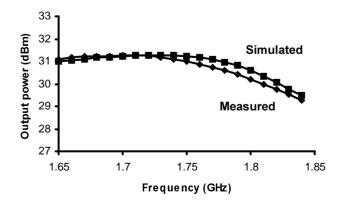

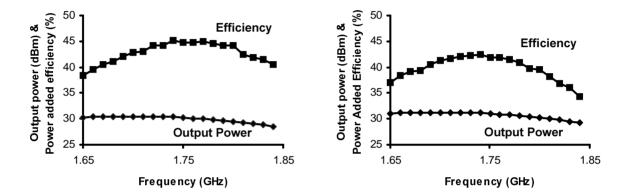

|   |     | <ul> <li>8.2.1 Specifications</li> <li>8.2.2 Design of the Power Amplifier</li> <li>8.2.3 Simulations</li> <li>8.2.4 Measurements</li> <li>8.2.5 Revised PCB Version</li> <li>8.2.6 Summary of Second CMOS Power Amplifier</li> </ul> | 86<br>87<br>88<br>89 |

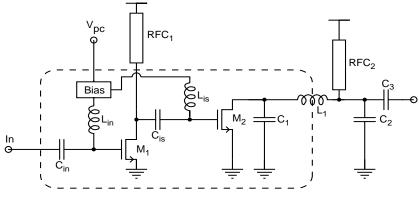

|   | 8.3 | Third Revision CMOS Power Amplifier                                                                                                                                                                                                   |                      |

|   |     | <ul> <li>8.3.1 Design</li> <li>8.3.2 Measurements</li> <li>8.3.3 Summary of Third CMOS Power Amplifier</li> </ul>                                                                                                                     | 95                   |

|   | 8.4 | Summary                                                                                                                                                                                                                               | . 99                 |

|   |     | References                                                                                                                                                                                                                            | 101                  |

| 9 | Cor | nclusion                                                                                                                                                                                                                              | 103                  |

|   |     | oendix A<br>sign Details                                                                                                                                                                                                              | 105                  |

|   | 9.1 | Initial Design Decisions                                                                                                                                                                                                              | 105                  |

|   | 9.2 | Design Individual Stages                                                                                                                                                                                                              | 106                  |

|   | 9.3 | 9.2.1 Transistor Sizing and Load Selection                                                                                                                                                                                            |                      |

|   |     | oendix B<br>olished Papers                                                                                                                                                                                                            | 109                  |

|   |     | References                                                                                                                                                                                                                            | 109                  |

# **List of Figures**

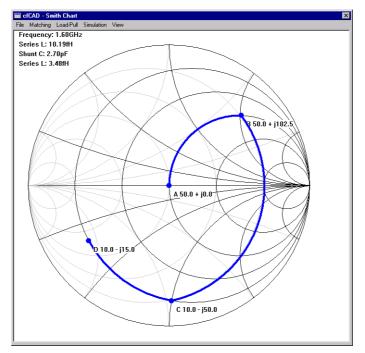

| Figure 3.20 Two cascaded L sections.                                                       | . 41 |

|--------------------------------------------------------------------------------------------|------|

| Figure 3.21 Insertion loss of one or two cascaded L section.                               | . 41 |

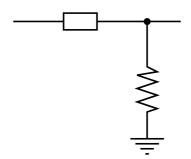

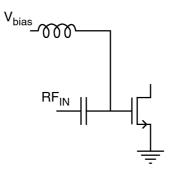

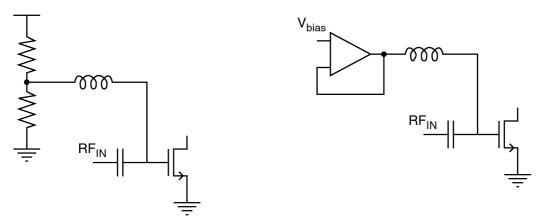

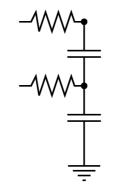

| Figure 4.1 Bias circuit for MOSFET power amplifier.                                        | . 44 |

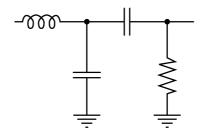

| Figure 4.2 Passive and active bias circuit.                                                | . 44 |

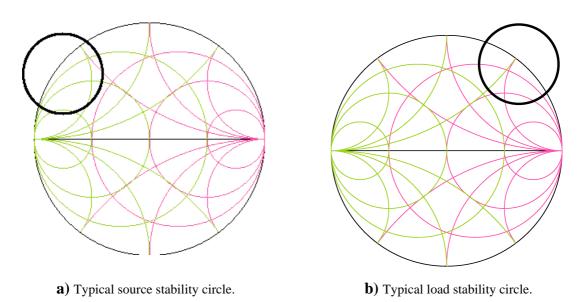

| Figure 4.3 Stability circles.                                                              |      |

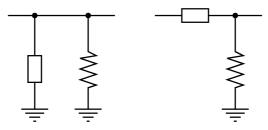

| Figure 4.4 Resistive stabilisation.                                                        | . 46 |

| Figure 4.5 Conductive Stabilisation                                                        |      |

| Figure 4.6 Feedback stabilisation.                                                         | . 47 |

| Figure 4.7 Example of stable bias circuit.                                                 | . 48 |

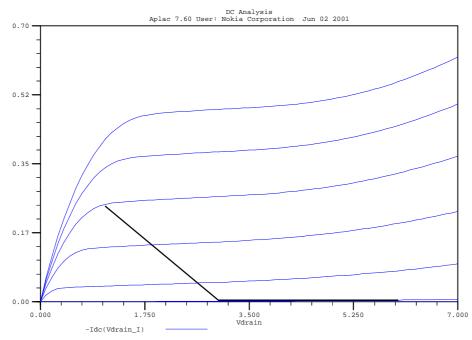

| Figure 5.1 I-V characteristic of a typical submicron NMOS transistor [1]                   |      |

| Figure 5.2 Enhanced RF MOS transistor model.                                               | . 56 |

| Figure 5.3 On-chip capacitor model.                                                        | . 57 |

| Figure 5.4 Simple Π network inductor model.                                                |      |

| Figure 5.5 On-chip inductor model.                                                         |      |

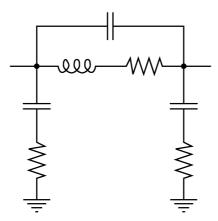

| Figure 5.6 Simple RLC network metal wire model.                                            | . 58 |

| Figure 5.7 Leadframe model for two adjacent pins.                                          | . 59 |

| Figure 5.8 Simplified thermal model of a power amplifier.                                  | . 60 |

| Figure 6.1 Overall design flow.                                                            | . 63 |

| Figure 6.2 Design flow for initial design decisions.                                       | . 64 |

| Figure 6.3 Design flow for individual stage design.                                        | . 65 |

| Figure 6.4 Design flow for transistor sizing and load impedance selection.                 | . 66 |

| Figure 6.5 Design flow for combination of individual stages.                               | . 67 |

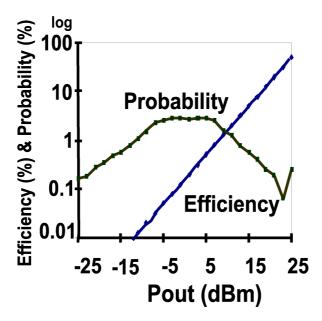

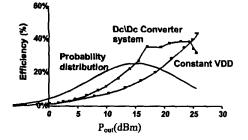

| Figure 7.1 Probability and class A efficiency vs. power levels.                            | . 72 |

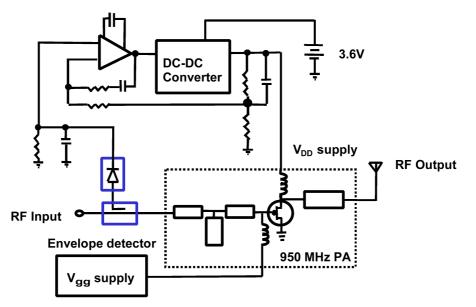

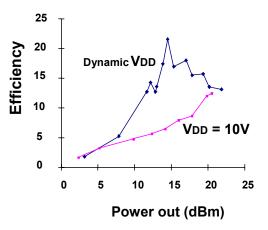

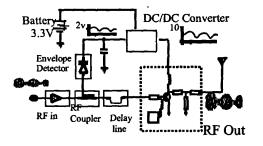

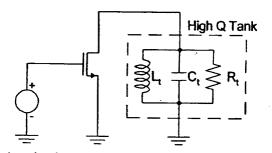

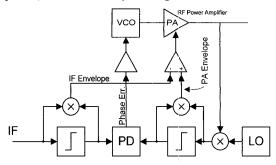

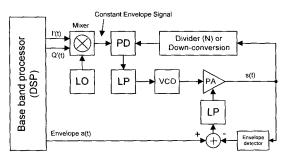

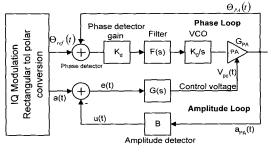

| Figure 7.2 Schematic of dynamic supply voltage power amplifier.                            | . 72 |

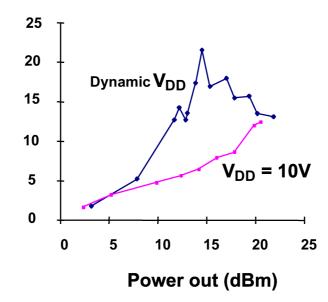

| Figure 7.3 Total efficiency as a function of the output power.                             | . 73 |

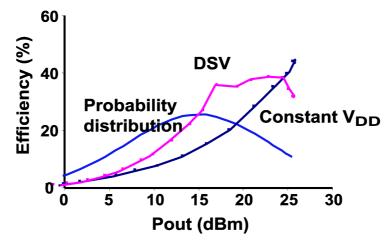

| Figure 7.4 Probability and efficiency combined.                                            |      |

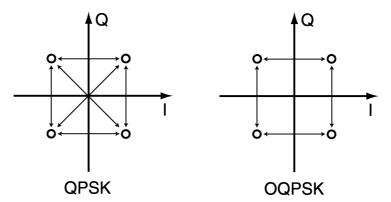

| Figure 7.5 Constellation diagram showing phase transitions in QPSK and OQPSK               | . 74 |

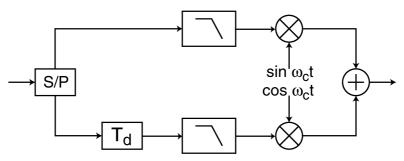

| Figure 7.6 Block diagram of digital OQPSK modulation.                                      |      |

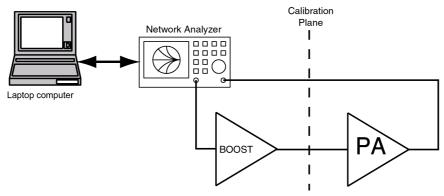

| Figure 7.7 Measurement setup for retrieving AM-AM and AM-PM data                           |      |

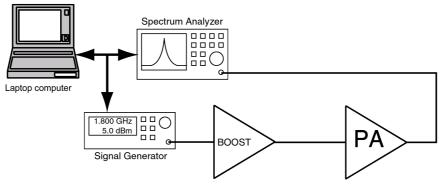

| Figure 7.8 Measuring ACPR for digital predistortion system.                                | . 77 |

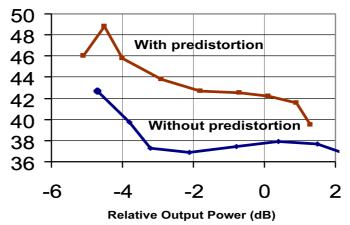

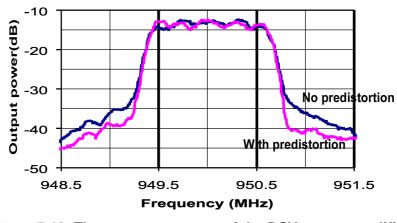

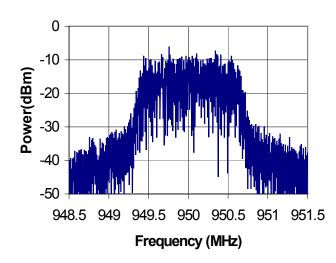

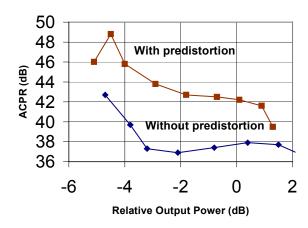

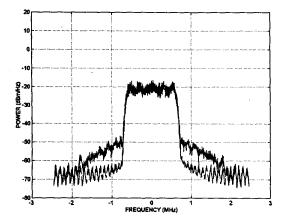

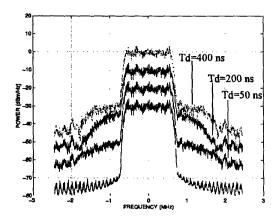

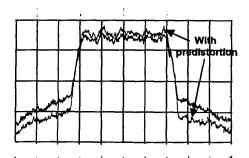

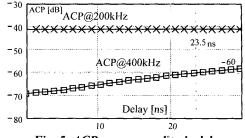

| Figure 7.9 ACPR measurements with and without digital predistortion.                       | . 77 |

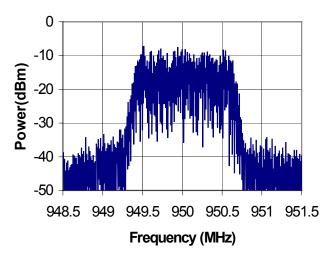

| Figure 7.10 The output spectrum of the DSV power amplifier                                 |      |

| with and without digital predistortion.                                                    | . 78 |

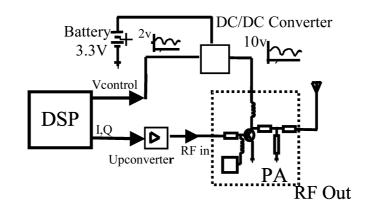

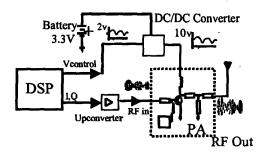

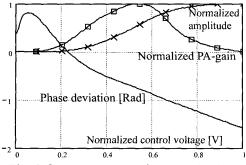

| Figure 7.11 Schematic of improved digital predistortion system.                            | . 78 |

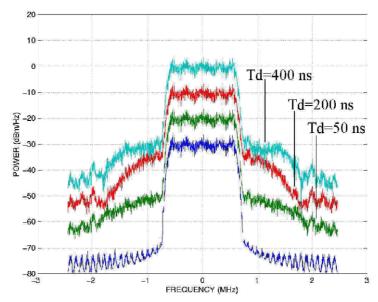

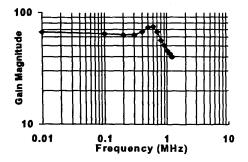

| Figure 7.12 Effect of delay in DC-DC converter control loop                                | . 79 |

| Figure 7.13 Spectrum of improved digital predistortion system.                             | . 79 |

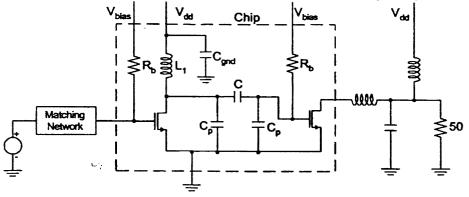

| Figure 8.1 Schematic of the first CMOS power amplifier prototype                           |      |

| Figure 8.2 Photograph of the first CMOS power amplifier PCB                                |      |

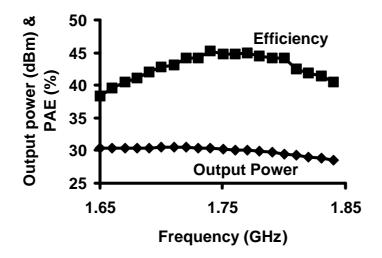

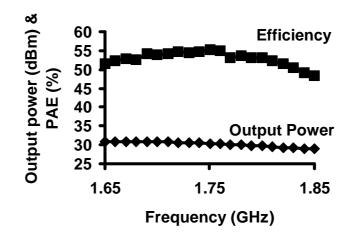

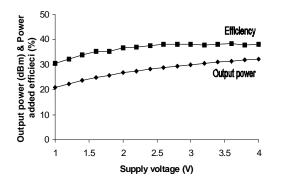

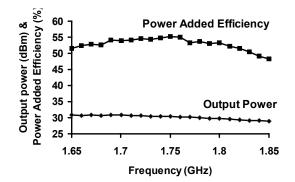

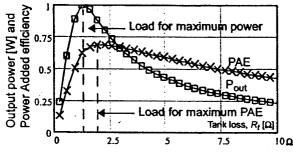

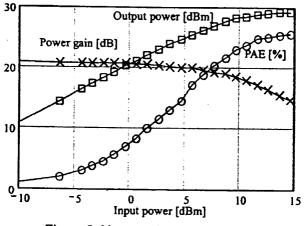

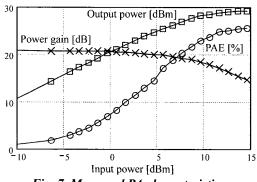

| Figure 8.3 Output power and power added efficiency of first CMOS PA                        |      |

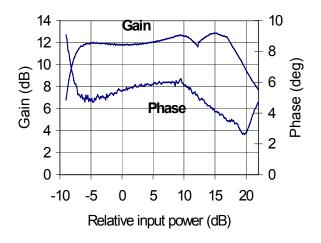

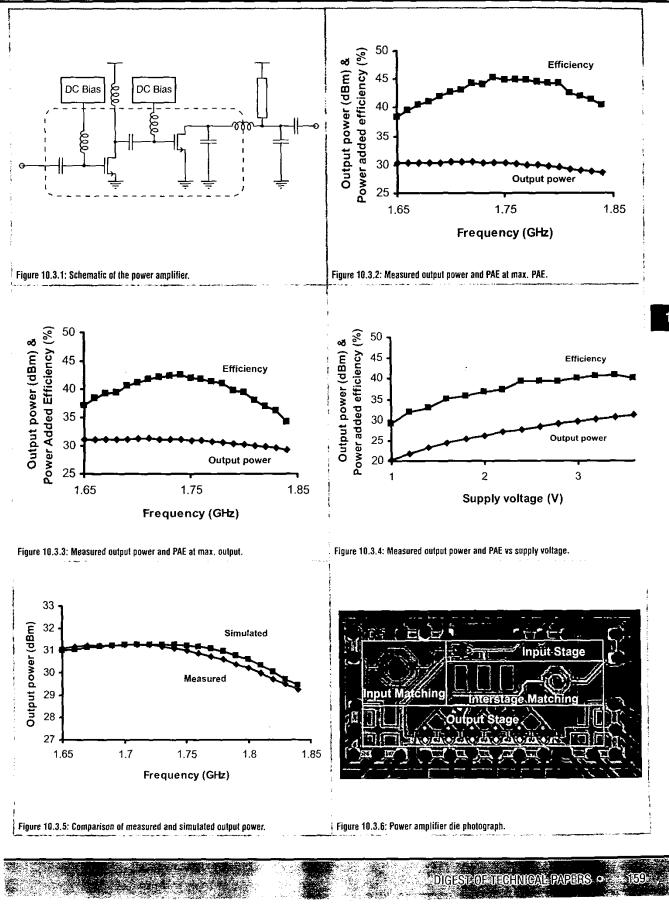

| Figure 8.4 Comparison of simulated and measured data.                                      | . 87 |

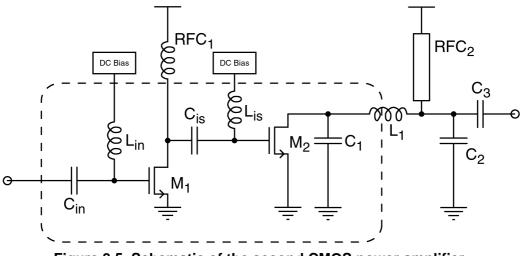

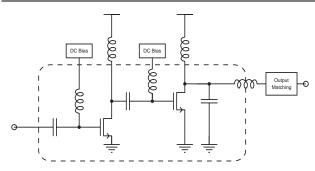

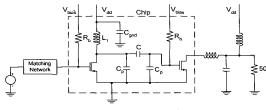

| Figure 8.5 Schematic of the second CMOS power amplifier.                                   | . 88 |

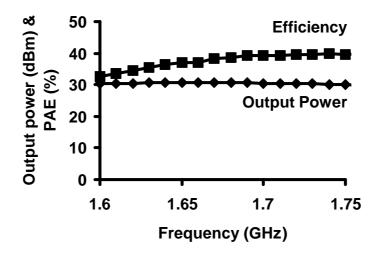

| Figure 8.6 Measured output power and efficiency, biased for maximum power added efficiency | ncy. |

|                                                                                            |      |

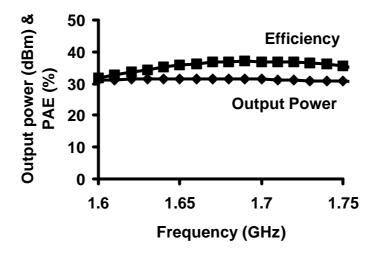

| Figure 8.7 Measured output power and efficiency, biased for maximum output power           |      |

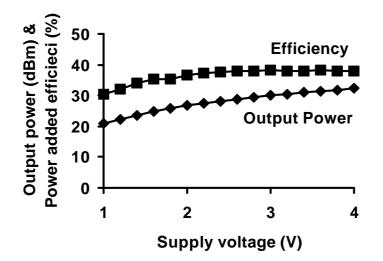

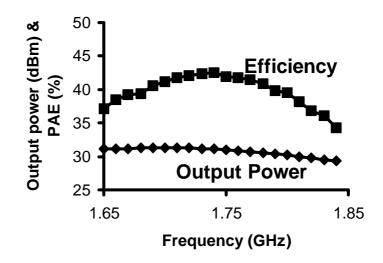

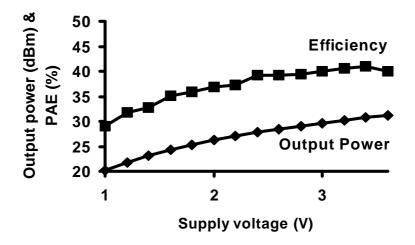

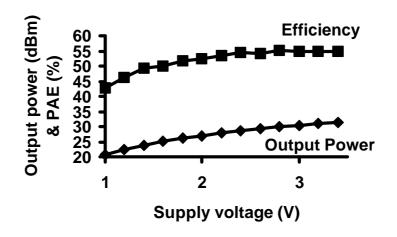

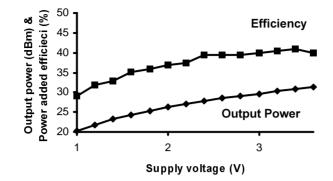

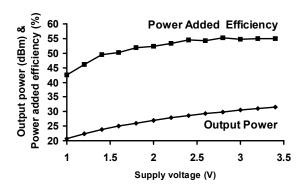

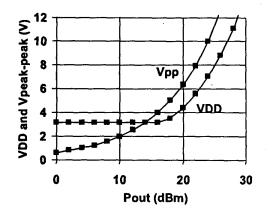

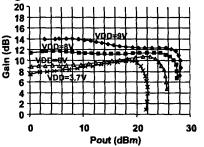

| Figure 8.8 Measured output power and efficiency vs. supply voltage                         |      |

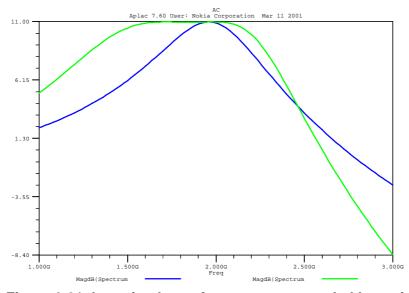

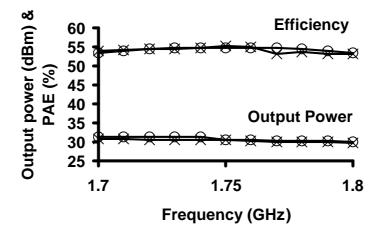

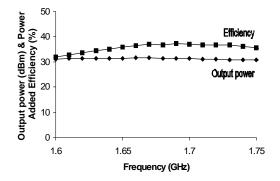

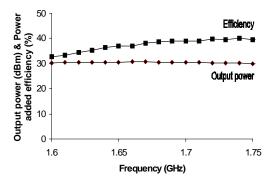

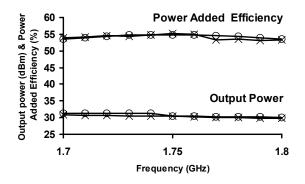

| Figure 8.9 Output power and efficiency vs. frequency, biased for maximum efficiency        |      |

| Figure 8.10 Output power and efficiency vs. frequency, biased for maximum output power     |      |

| Figure 8.11 Measured output power and efficiency vs. supply voltage at 1730 MHz            |      |

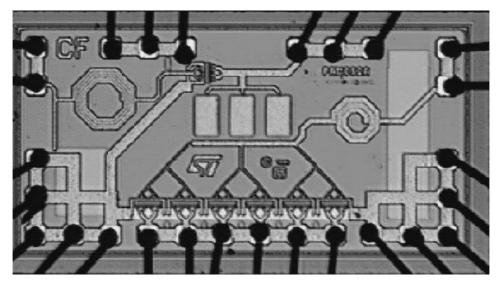

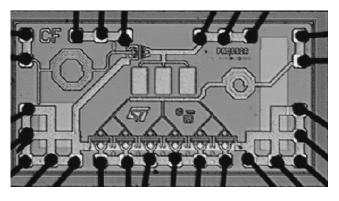

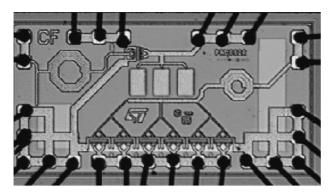

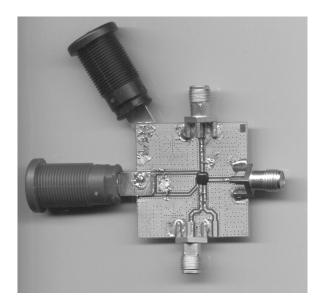

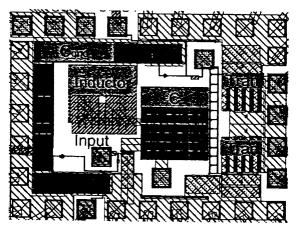

| Figure 8.12 Photograph of the IC.                                                          |      |

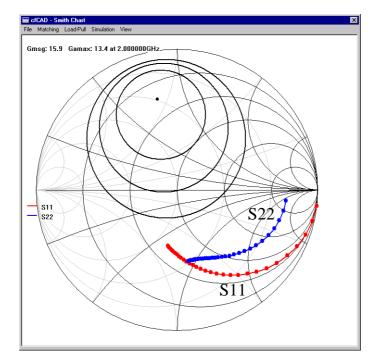

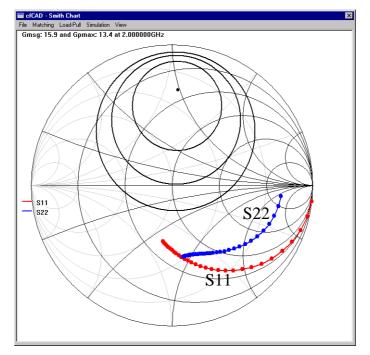

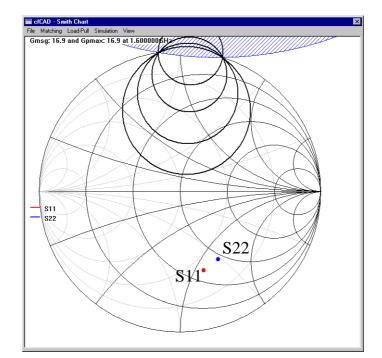

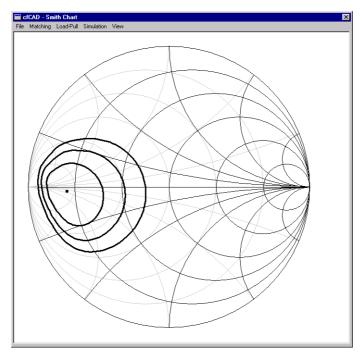

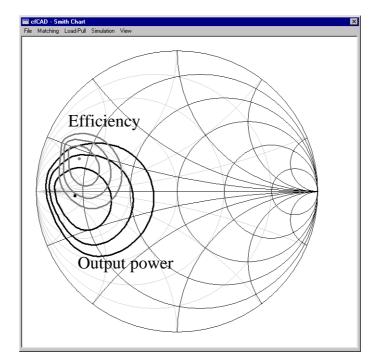

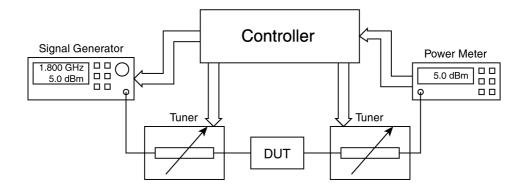

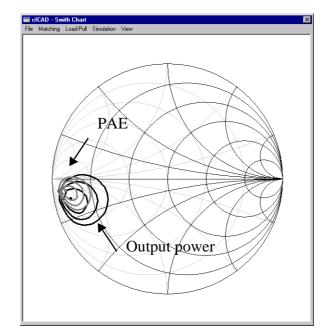

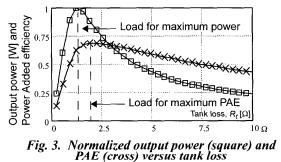

| Figure 8.13 Load-pull simulation of third CMOS power amplifier.                            | . 94 |

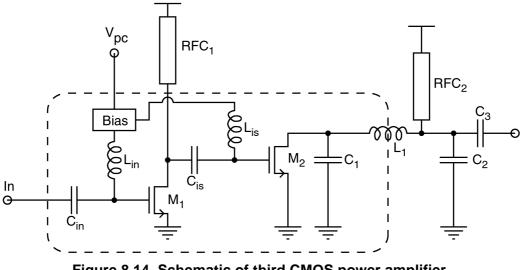

| Figure 8.14 Schematic of third CMOS power amplifier.                                       | 95  |

|--------------------------------------------------------------------------------------------|-----|

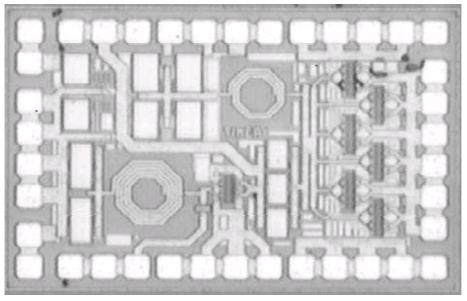

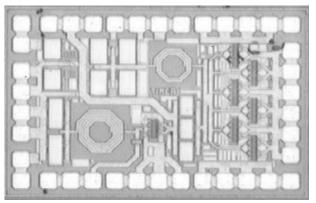

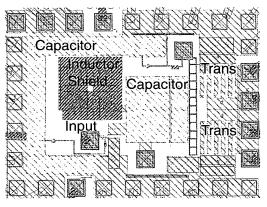

| Figure 8.15 Die photograph.                                                                | 96  |

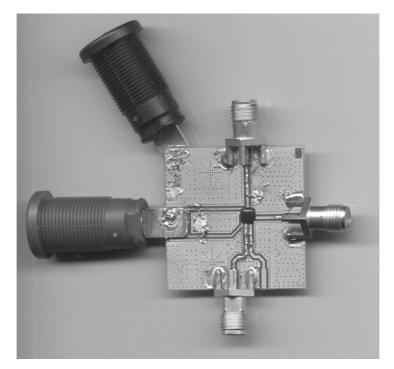

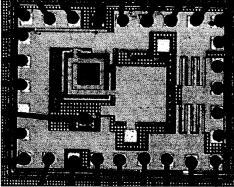

| Figure 8.16 PCB photograph.                                                                | 97  |

| Figure 8.17 Output power and power added efficiency vs. frequency when biased for efficien | cy. |

|                                                                                            | 97  |

| Figure 8.18 Measured output power and power added efficiency vs. supply voltage at 1750    | )   |

| MHz                                                                                        | 98  |

| Figure 8.19 Comparison of simulated and measured data.                                     | 98  |

| Figure A.1 I-V characteristics of 1mm wide transistor.                                     | 106 |

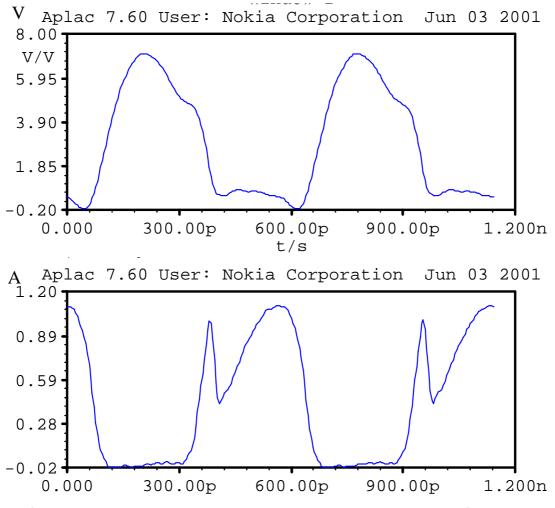

| Figure A.2 Voltage across and current through the output transistor channel                | 108 |

|                                                                                            |     |

# **List of Tables**

| Quick overview of the classes of operation.          | 21  |

|------------------------------------------------------|-----|

| Specifications for the first CMOS PA prototype       | 82  |

| Characteristics of the first CMOS power amplifier.   | 86  |

| Specifications for the second CMOS PA prototype      |     |

| Component values for the second CMOS power amplifier | 92  |

| Characteristics of the second CMOS power amplifier   |     |

| Component values for third CMOS power amplifier      | 96  |

| Comparison of CMOS power amplifiers.                 | 99  |

| Characteristics of the third CMOS power amplifier.   | 99  |

| Evolution of CMOS power amplifiers                   | 101 |

| Specifications for the third CMOS PA prototype       |     |

| Gain and efficiency budget                           |     |

# Glossary

| ACP    | Adjacent channel power                            |

|--------|---------------------------------------------------|

| ACPR   | Adjacent channel power ratio                      |

| AMPS   | Advanced mobile phones system                     |

| CAD    | Computer aided design                             |

| CDMA   | Code division multiple access                     |

| CMOS   | Complementary metal-oxide-semiconductor           |

| СОВ    | Chip on board                                     |

| DSP    | Digital signal processor                          |

| DSV    | Dynamic supply voltage                            |

| GaAs   | Gallium Arsenide                                  |

| GMSK   | Gaussian minimum phase shift keying               |

| GSM    | Global system for mobile communications           |

| HBT    | Heterojunction bipolar transistor                 |

| IMD    | Intermodulation distortion                        |

| LDMOS  | Laterally diffused MOS                            |

| MOSFET | Metal oxide semiconductor field effect transistor |

| MESFET | Metal semiconductor field effect transistor       |

| OQPSK  | Offset quadrature phase shift keying              |

| PAE    | Power added efficiency                            |

| PCB    | Printed circuit board                             |

| QPSK   | Quadrature phase shift keying                     |

| RFC    | RF choke                                          |

| SAR    | Specific absorption rate                          |

| SiGe   | Silicon Germanium                                 |

| SMD    | Surface mount device                              |

| SOI    | Silicon on insulator                              |

| TDMA   | Time division multiple access                     |

| UMTS   | Universal mobile telephone system                 |

| W-CDMA | Wideband code division multiple access            |

|        |                                                   |

# **Errata**

| p.4, eq. 1.4    | $P_{ch}$ is the power in the channel, while $P_{adj}$ is the power in the adjacent channel |

|-----------------|--------------------------------------------------------------------------------------------|

| p. 10, l. 9     | output impedance should be load impedance                                                  |

| p. 17, l. 3     | power added efficiency should be output power                                              |

| p. 28, eq. 3.19 | $K = \frac{1 -  S_{11} ^2 -  S_{22} ^2 +  \Delta ^2}{2 S_{12}S_{21} }$                     |

| p. 37, l. 15    | the impedance 10 - j10 should be 10 - j15                                                  |

| p. 41, fig 3.21 | The gain in Fig 3.21 has not been normalized and the maximum should be 0dB                 |

# CHAPTER 1 INTRODUCTION

Over the last couple of years there has been an increasing focus on highly integrated high efficiency power amplifiers for wireless communication systems, especially mobile phones. This is also the topic of this thesis.

In the first chapters of this thesis the basic theory is explained. Then the concept of simulated load-pulling is introduced in conjunction with automated impedance matching network synthesis. This is followed by a comparison of semiconductor technologies with focus on CMOS. Then the modeling of active and passive components is described. A number of experimental CMOS power amplifiers were constructed during the project and the results of these are presented at last.

The design of power amplifiers in the past did not follow a stringent design method, it rather seemed like black magic was performed. In this thesis a design method is developed based on the basic theory of power amplifier design and this is used to formalize the design process.

In the last part of this thesis experimental results on CMOS power amplifiers as well as a digital linearizations system is presented. The CMOS power amplifiers show results better than any other CMOS power amplifier presented so far, the results are even comparable to commercial power amplifiers in more exotic technologies.

In the remainder of this chapter the basic definitions used in conjunction with power amplifiers will be explained.

## **1.1 Basics of RF Power Amplifiers**

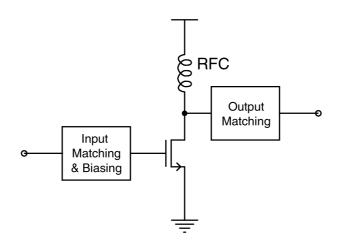

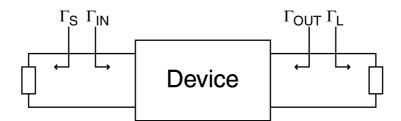

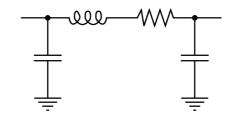

A simple power amplifier is illustrated in Figure 1.1. The power amplifier consists of an input impedance matching network, an amplifying stage and an output impedance matching network. Furthermore DC bias is applied at the input and output ports of the amplifying stage [1][2].

Figure 1.1 Simple power amplifier.

The power amplifiers can be divided into narrowband and broadband power amplifiers. In most communication systems narrowband power amplifiers are used, since they are usually more efficient than the broadband amplifiers.

The power amplifier has a number of characteristic properties that will now be explained. First of all the power gain of a power amplifier is defined as the output power divided by the input power:

$$G = \frac{P_{out}}{P_{in}}$$

(1.1)

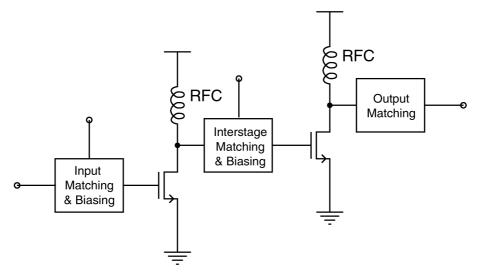

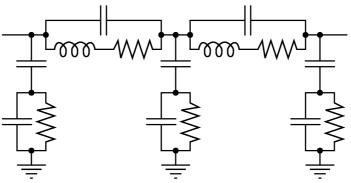

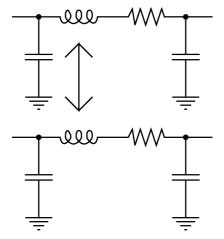

In practice most power amplifiers will be multistage amplifiers to obtain sufficient power gain. The combination of several stages often introduces problems with stability of the power amplifier due to the increased gain from input to output. The principle of a two-stage power amplifier is shown in Figure 1.2.

Figure 1.2 Principle of a two-stage power amplifier.

### 1.1.1 Definitions of Efficiency

The efficiency is probably the most important property of the power amplifier, since a very large part of the total power dissipated in a mobile phone is dissipated in the power amplifier. The efficiency is limited by the selected class of operation and the parasitic components, as described in chapter 2. The efficiency can be expressed as either drain efficiency or power added efficiency. The drain efficiency is given by:

$$\eta_{\rm drain} = \frac{P_{\rm out}}{P_{\rm DC}}$$

(1.2)

On the system level the efficiency of the driver stages is also important, and then the power gain of the power amplifier must be included. The power gain of a power amplifier is also dependent upon the class of operation, as well as the chosen technology. Different classes of operation have different relative power gains. The inclusion of the power gain leads to the expression for power added efficiency:

$$\eta_{add} = \frac{P_{out} - P_{in}}{P_{DC}} = \frac{P_{out}}{P_{DC}} \cdot \left(1 - \frac{1}{G}\right)$$

(1.3)

The power added efficiency is more relevant to the system designer than the drain efficiency, but as mentioned above this depends highly of the technology. It is therefore difficult to compare two classes of operation, without knowing the properties of the power transistor.

### 1.1.2 Definitions of Linearity

One of the other important parameters in power amplifier design is the nonlinearity of the power amplifier. The nonlinearity originates from the active components. If the wireless communication system utilizes a varying envelope modulation the nonlinearities will cause spectral regrowth which will pollute the neighboring channels.

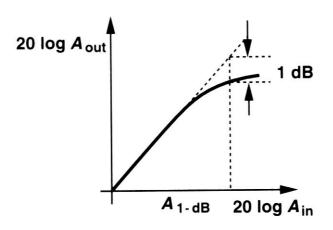

#### Gain Compression

Gain compression describes the phenomenon, when the relationship between the input and output power levels is no longer linear. When the output power is 1dB less than expected by the linear relationship the so-called 1dB Gain Compression Point ( $P_{1dB}$ ) is reached. The gain compression is also known as AM-AM conversion.

#### **AM-PM** Conversion

The AM-PM conversion is caused by the phase shift of the power amplifier caused by the amplitude of the signal. This can for instance be caused by the non-linear drainsource capacitance of the MOSFET.

#### **Intermodulation Distortion**

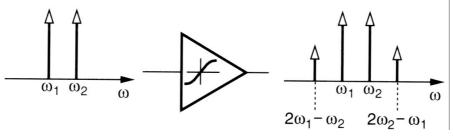

The harmonic distortion is caused by the nonlinear active components of the amplifier. The result is distortion components at integer multiples of the signal frequency.

Figure 1.3 Output power as a function of input power [3].

Intermodulation distortion (IMD) is generated when more than one signal is present on the input. The intermodulation distortion is also caused by the nonlinearities of the amplifier. New third-order signals are generated at e.g.  $2f_1 - f_2$  and  $2f_2 - f_1$ . The third-order products increase by 3 dB when the input signals increase by 1 dB. The point at which the extrapolated power levels of the third-order products reach the wanted power is called the Third-order Intercept Point (P<sub>3IP</sub>). Although third-order distortions will probably be the most important a number of other orders may also be significant.

Figure 1.4 Third-order intermodulation products [3].

#### Adjacent Channel Power Ratio

The adjacent channel power ratio (ACPR) is one of the most important ways of characterizing the nonlinearity of a power amplifier in linear communication standards.

$$ACPR = \frac{P_{adj}}{P_{ch}}$$

(1.4)

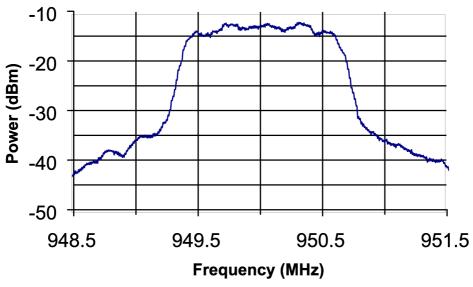

In Figure 1.5 a typical spectrum showing the ACPR is illustrated. The ACPR is an easy way to measure the total distortion caused by the above mentioned nonlinearities.

## **1.2 Mobile Phone Standards**

The mobile phone standards have evolved quickly over last decades. The first standards used continuos time frequency modulation (FM), now wideband code division multiple access (W-CDMA) or time division multiple access (TDMA) systems with quadrature

Figure 1.5 Spectrum showing ACPR measurement.

modulation formats are being deployed. In the following sections the most important features of the three generations introduced until now will be described.

## **1.2.1 First Generation**

The first generation mobile phone standards employed analog modulation formats. The first systems were used in USA in the 1950s. One of the most successful first generation standards was the Nordic Mobile Telephone standard (NMT), developed in the nordic countries in the early 1980s. This standard served as an example of the importance of roaming across countries and different network operators.

A few of the first generation systems are still in use most notably the NMT and the north-american Advanced Mobile Phone System (AMPS). Since these systems are all FM systems, the nonlinearities of the power amplifiers are not a problem.

## **1.2.2 Second Generation**

The second generation mobile phone standards all use digital modulation formats. The the digital modulation allows for digital data services. The main advantage of the digital modulation is however the possibility to share a single channel between several users. The sharing is done either through time division multiple access (TDMA) or code division multiple access (CDMA).

#### GSM-900/1800/1900

The Global System for Mobile Communications (GSM) standard is used all through Europe, as well as most of North America and some parts of the Asia-Pacific area. The GSM system employs GMSK modulation which is a constant envelope modulation. The sharing of the channel is done through time division. A constant envelope modulation uses a constant amplitude in the modulation, which means that the power amplifier can be nonlinear. The GSM system features global roaming between different operators. The bitrate of the GSM system is 9.6 kbits/s in a standard system, but changing the error coding and using more than one timeslot up to 43.2 kbits/s has been achieved.

#### EDGE

The EDGE standard was originally developed as an extension for GSM only, but has now been integrated in other standards as well. The EDGE standard uses a modified 8PSK modulation, which is not constant envelope. The new modulation means that the nonlinear power amplifiers can no longer be used. The EDGE standard allows for bitrates up to 384 kbits/s.

The linearity requirements of the EDGE standard is expressed in terms of ACPR. In the adjacent channel the ACPR must be better than -30dBc while in the alternating channel the ACPR must be better than -54dBc. Since nonlinearities are also introduced in the circuits prior to the power amplifier then specifications for the power amplifier will typically be even harder. The ACPR is measured with a 30 kHz resolution bandwidth at the center of the channels.

#### **IS-95 CDMA**

The IS-95 standard is used primarily in North America as well as some places in the Asia-Pacific area. The IS-95 system uses QPSK modulation which utilizes varying envelope, the sharing of the channel is achieved through code division [3].

While the number of simultaneous users on a channel in a TDMA systems is determined by the number of timeslots, the number of simultaneous users in IS-95 is determined by the noise level in the channel. The noise level is optimized through aggressive power control to maximize the number of simultaneous users. Due to the power control the power amplifier has to be able to control the output power in 1dB steps over a range of 85dB.

The linearity requirements of the IS-95 standard is also expressed as ACPR. The ACPR of the adjacent channel has to be better than -42dBc, but this is for the total output power compared to a 30 kHz band, this relates to an ACPR of -26dBc.

### **1.2.3 Third Generation**

The third generation of mobile phones is primarily focused on higher bitrates. The only serious standard until now is the Universal Mobile Telephones System (UMTS) which is a wideband CDMA system. The UMTS system will probably be the first standard with true global coverage across countries and network operators.

The UMTS standard features bitrates up to 2 Mbits/s. This bitrate will be used for multimedia applications on the mobile terminal e.g. audio and video clips. As was the case for IS-95 the power control has 1dB steps and the dynamic range is 70dB posing a real challenge for the power amplifier designer

## 1.3 Summary

The power amplifier is the most power consuming component in a mobile phone, and it is therefore interesting to reach higher efficiency levels for the power amplifier. There are several ways to improve the efficiency, e.g. new circuit topologies, higher level of integration and better technologies.

The linearity of a power amplifier will be an issue in future telecommunication standards, such as EDGE and UMTS. There will therefore be a need for linear power amplifiers, this can be achieved either by using linear topologies and/or linearization techniques.

The future UMTS handsets will probably contain dual-mode functionality with GSM, this means that the power amplifier must also be able to handle ordinary GSM efficiently. The dual-mode solution will be very challenging, and might not even be the optimal solution.

In this chapter the basic properties of an RF power amplifier has been defined. In the following chapters the details of the power amplifiers will be discussed. In chapter 2 the classes of operation are discussed. The trade-offs between different class of operation are discussed. The impedance matching of the power amplifier is described in chapter 3. This includes methods to obtain optimal impedance matching as well as methods for synthesizing the impedance matching networks. Chapter 4 deals with the biasing of the power amplifier. In this chapter the issues of RF and bias stability is also discussed.

In chapter 5 the implementation technologies are discussed with focus on the deep sub-micron CMOS technologies. The modeling of active and passive components onchip as well as on the PCB is also discussed. In chapter 6 the theory is collected in a design method for integrated power amplifiers. The design method covers the complete design of a power amplifier, from specification to verification.

In chapter 7 a digital predistortion is presented, which enables the use of nonlinear power amplifiers in systems with varying envelope. The digital predistortion system was built and experimental results obtained. Three CMOS power amplifiers have been designed during the Ph.D. project. These power amplifiers are described in chapter 8. In comparison with other published CMOS power amplifiers they shows superior performance.

## 1.4 Acknowledgements

This Ph.D. project have been funded by Nokia Mobile Phones in Copenhagen. I have had very fruitful discussions with a number of design engineers at Nokia. I would especially like to thank Dan Rebild for an enormous support during the entire Ph.D. project.

## References

- [1] S. C. Cripps, *RF Power Amplifiers for Wireless Communications*. Artech House, 1999.

- [2] H. L. Krauss, C. W. Bostian, and F. H. Raab, *Solid State Radio Engineering*. John Wiley Sons, 1980.

- [3] B. Razavi, *RF Microelectronics*. Prentice Hall, 1998.

# CHAPTER 2 CLASSES OF OPERATION

The different topologies for power amplifiers can be divided into a number of classes of operation. The classes have different properties with respect to e.g. linearity, efficiency and power gain.

Usually the classes A, AB, B and C are treated as distinct modes of operation, although in reality they are a continuum of biasing conditions for the same basic mode of operation. It is therefore possible to describe class A through C as a single class with different conduction angles. The analysis of class A through C is done in Section 2.1. The classes D and F can also be analyzed as one class, this analysis will be carried out in Section 2.2. The class E operation is quite different from the other classes and will be treated separately in section 2.3. At last the class S operation will be described in Section 2.4.

One of the important parameters of the amplifier classes is the load line, as the name implies the load of the amplifier has an influence on the load line. The other parameter that influences the load line is the quiescent bias point.

## 2.1 Class A through C

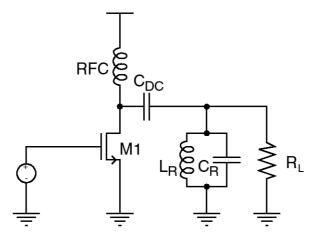

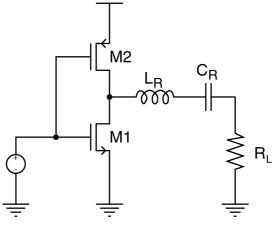

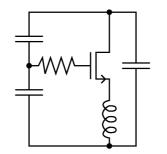

The class A, AB, B and C amplifiers are very similar, except for the biasing and the output matching network. The basic class A through C power amplifier is illustrated in Figure 2.1. The biasing of the output is obtained by the RF choke (RFC). To prevent a DC current from flowing a DC block ( $C_{DC}$ ) is incorporated into the design. The loadline of the power amplifier is controlled by the load resistance ( $R_L$ ), while the resonator ( $L_R$ ,  $C_R$ ) filters out the harmonics at the output. The input matching, not illustrated here, usually contains the biasing of the input, as will be described in Chapter 4.

Which of the classes the power amplifier actually operates in is defined by the quiescent drain current, which again is defined by the input bias point. Apart from the bias point of the amplifier the loadline is the most important feature. The transistor has a large impact on the selection of the loadline of the power amplifier. To optimize the

Figure 2.1 The generic setup for class A, AB, B and C amplifiers.

power amplifier, with respect to output power, efficiency or linearity, the load line should be placed correctly. When the loadline is not selected properly the power amplifier will be either current or voltage limited. The optimal load line of a power amplifier is primarily controlled by the I-V characteristic of the transistor. To obtain maximum output power the load line should be placed such that the amplifier is neither current nor voltage limited.

In the analysis of the class A through C power amplifiers it is assumed that the resonator has infinite impedance at the fundamental frequency while the impedance is zero at all other frequencies. The output impedance is defined by the load resistor ( $R_L$ ). The RF choke (RFC) is ideal and allows only DC currents to flow to the transistor. Under these assumptions it is possible to derive the current and voltage waveforms at the output of the power amplifier assuming a sinusoidal drive at the input.

The analysis starts by defining the conduction angle  $\alpha$ , which is the amount of time the transistor is conducting. Assuming a MOSFET, the conduction angle is determined by the quiescent bias voltage (V<sub>q</sub>) on the gate of the transistor, with a corresponding quiescent current (I<sub>q</sub>). The transistor is assumed to have a threshold voltage, below

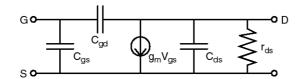

Figure 2.2 Simple RF small-signal model of MOS transistor.

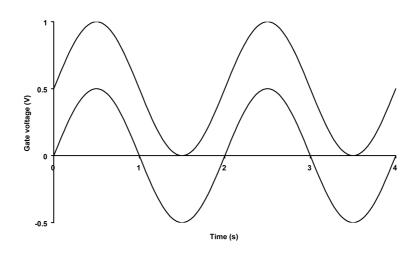

which the transistor will not draw any current. The maximum current that can be drawn by the transistor is defined as  $I_{max}$ . The relation between conduction angle and bias point is shown in Figure 2.3, where biasing for 360°, and 180° conduction angles are illustrated. The selected bias points correspond to class A and B. In the same figure the ideal currents drawn by the transistor is shown.

The currents drawn by the transistor can be formulated as:

Figure 2.3 Relationship between biaspoint and conduction angle.

$$i_{d}(\theta) = \begin{cases} I_{q} + (I_{max} - I_{q})\cos\theta , -\alpha/2 \le \theta \le \alpha/2 \\ 0 , -\pi < \theta < -\alpha/2; \alpha/2 < \theta < \pi \end{cases}$$

(2.1)

where

$$\cos(\alpha/2) = -\frac{I_q}{I_{max} - I_q}$$

(2.2)

isolating  $I_q$  in this equation gives:

$$I_{q} = \frac{I_{max}\cos(\alpha/2)}{\cos(\alpha/2) - 1}$$

(2.3)

substituting (2.3) in (2.1) gives

$$i_{d}(\theta) = \begin{cases} \frac{I_{\max}}{1 - \cos(\alpha/2)} [\cos\theta - \cos(\alpha/2)], -\alpha/2 \le \theta \le \alpha/2 \\ 0, -\pi < \theta < -\alpha/2; \alpha/2 < \theta < \pi \end{cases}$$

(2.4)

The DC current as well as the magnitude of harmonic frequency components can be found using Fourier analysis. The DC current is then:

$$I_{dc} = \frac{1}{2\pi} \int_{-\alpha/2}^{\alpha/2} \frac{I_{max}}{1 - \cos(\alpha/2)} [\cos\theta - \cos(\alpha/2)] d\theta$$

$$= \frac{I_{max}}{2\pi} \frac{2\sin(\alpha/2) - \alpha\cos(\alpha/2)}{1 - \cos(\alpha/2)}$$

(2.5)

The magnitude of the harmonic frequency components can be found by applying Fourier analysis on the waveform described by (2.4). The magnitude of the *n*th is then:

$$I_{n} = \frac{1}{\pi} \int_{-\alpha/2}^{\alpha/2} \frac{I_{max}}{1 - \cos(\alpha/2)} [\cos\theta - \cos(\alpha/2)] \cos \theta d\theta$$

(2.6)

Solving (2.6) for the fundamental frequency gives:

$$I_1 = \frac{I_{\max}}{2\pi} \frac{\alpha - \sin(\alpha)}{1 - \cos(\alpha/2)}$$

(2.7)

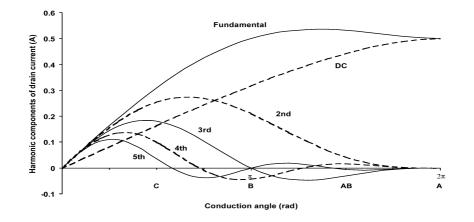

The DC and first five harmonic currents have been plotted against the conduction angle in Figure 2.4.

#### Figure 2.4 Harmonic components of current plotted as a function of conduction angle.

The power consumption and output power can now be found with the help of the the supply voltage  $V_{DD}$  and the load impedance  $R_L$ . Before the analysis the load impedance has to be defined. Assuming an ideal transistor this corresponds to:

$$R_{\rm L} = \frac{V_{\rm DD}}{I_{\rm max}}$$

(2.8)

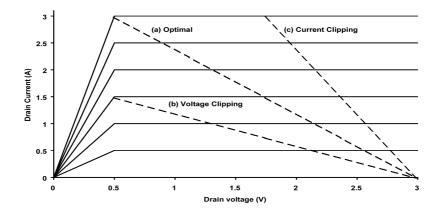

This gives maximum voltage and current swing as illustrated by line (a) in Figure 2.5. The case of voltage clipping where be current swing is reduced is illustrated by line (b) while current clipping and the following reduced voltage swing is line (c).

When the load impedance is too high it corresponds to voltage clipping as illustrated by line (b). In the case of voltage clipping it is easy to see that the value of  $I_{max}$  is reduced to the effective value:

$$I_{\text{max, eff}} = \frac{V_{\text{DD}}}{R_{\text{L}}}$$

(2.9)

When on the other hand the load impedance is too low the opposite case of current clipping occurs. This can be accounted for by using the effective voltage  $V_{DD,eff}$  in place of  $V_{DD}$ .

By substituting  $I_{max}$  with  $I_{eff}$  in (2.7) the effective RF current is found:

$$I_{\text{max, eff}} = \begin{cases} \frac{V_{\text{DD}}}{R_{\text{L}}}, \frac{V_{\text{DD}}}{R_{\text{L}}} < I_{\text{max}} \\ I_{\text{max}}, \frac{V_{\text{DD}}}{R_{\text{L}}} \ge I_{\text{max}} \end{cases}$$

(2.11)

$$I_1 = \frac{I_{\max, eff}}{2\pi} \frac{\alpha - \sin(\alpha)}{1 - \cos(\alpha/2)}$$

(2.12)

Using the above equations it is now possible to obtain the DC and output power of the power amplifier:

$$V_{DD, eff} = \begin{cases} I_{max} R_L, R_L I_{max} < V_{DD} \\ V_{DD}, R_L I_{max} \ge V_{DD} \end{cases}$$

(2.13)

$$P_{DC} = V_{DD}I_{DC}$$

(2.14)

$$P_{out} = \frac{V_{DD, eff}}{\sqrt{2}} \frac{I_1}{\sqrt{2}} = \frac{V_{DD, eff}I_1}{2}$$

(2.15)

it is now possible to define the drain efficiency of the power amplifier:

$$\eta_{\rm drain} = \frac{P_{\rm out}}{P_{\rm DC}}$$

(2.16)

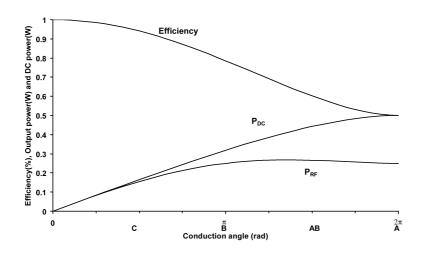

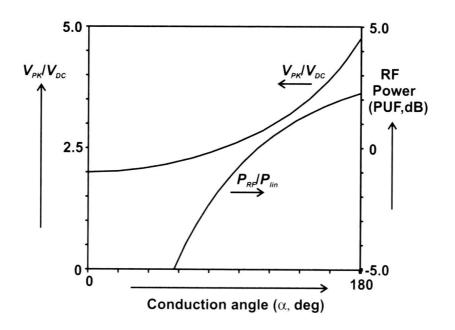

it is now possible to plot the relationship between conduction angle, output power and efficiency, see Figure 2.6.

## 2.1.1 Knee Effect

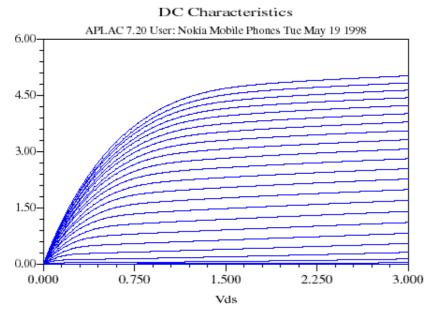

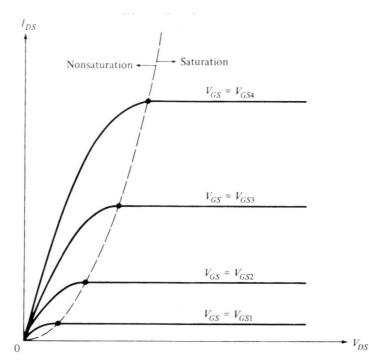

The knee effect is a property of the transistor used for the power amplifier. Due to the behavior of the MOS transistor the drain current will not only depend on the gate voltage but also on the drain voltage. This is especially noticeable at low drain voltages. The I-V characteristic of a typical submicron NMOS transistor is shown in Figure 2.7, where each of the curves represent a 0.25V increment in gate voltage.

Figure 2.7 I-V characteristic of a typical submicron NMOS transistor.

The knee voltage is defined as the drain voltage at which the transistor starts operating in saturation for a given gate voltage. Due to the knee effect it is not possible obtain maximum voltage and current swing using the same load-line, actually maximum voltage swing is only available at zero drain current. The impact of the knee effect can be calculated by realizing that only the values of  $V_{eff}$  and  $I_{eff}$  are affected. Since the value of  $I_{eff}$  affects only the output power of the power amplifier and  $V_{eff}$  affects output power as well as efficiency it is possible to make trade-offs between output power and efficiency for a given transistor.

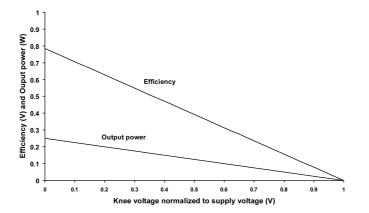

To illustrate how seriously the knee-effect reduces the efficiency the output power and efficiency is plotted vs. knee-voltage in Figure 2.8 for a class B amplifier.

Figure 2.8 Efficiency and output power vs. knee-voltage for a class B amplifier.

Now that the general coverage of the classes A through C is done, it is natural to discuss the specific behavior of the original class definitions. This will be done in the following sections.

### 2.1.2 Class A

The conduction angle of a class A amplifier is  $360^{\circ}$ . The maximal efficiency of a class A amplifier is therefore 50%. The class A amplifier is the class with the best linearity, but also the lowest efficiency. Ideally the load line of a class A amplifier is placed in such a way that the quiescent current is half that of the maximal current needed. The drain efficiency of a class A amplifier is given by [1][2]:

$$\eta = \frac{P_{out}}{P_{DC}} = \frac{I_q^2 \cdot R_L^2}{2 \cdot V_{dd}^2}$$

(2.17)

The load which gives the maximum power at the output is  $V_{dd}/I_q$ , with this load the maximum efficiency is 50%. When the saturation voltage of the device is taken into account, the situation is even worse. The possible voltage swing is then only  $V_{dd} - V_{knee}$ , this gives the load line  $(V_{dd} - V_{knee})/I_q$ . The maximum efficiency is then given by:

$$\eta_{\text{max}} = \frac{\left(1 - \frac{V_{\text{knee}}}{V_{\text{dd}}}\right)^2}{2}$$

(2.18)

For a 3.3 V process with a knee voltage of 0.5 V the maximum efficiency will be 42%. Although the efficiency is poor at maximum output power, it gets even worse when less than maximum power is needed since the DC power  $P_{DC}$  is unchanged, but the output power  $P_{out}$  is lower.

### 2.1.3 Class B

The class B amplifier is biased in such a way that it amplifies only the positive part of the signal. In the remaining part of the time, the output from the amplifier is zero. Since the conduction angle of a class B amplifier is only  $180^{\circ}$ , a filter must be placed at the output in order to filter the harmonics out of the signal. Another way to retrieve the original signal is to couple two class B amplifiers in a push-pull configuration.

The class B amplifier is basically linear and has a maximum efficiency of 78.5% with  $V_{knee} = 0$ , this can be shown for a single-ended amplifier as below.

$$I_{p} = \frac{V_{dd} - V_{knee}}{R_{L}}$$

(2.19)

$$P_{out} = R_{L} \cdot \frac{1}{T} \int_{0}^{\frac{T}{2}} (I_{p} \sin \omega t)^{2} d\omega = \frac{I_{p}^{2} \cdot R_{L}}{4} = \frac{(V_{dd} - V_{knee})^{2}}{4 \cdot R_{L}}$$

(2.20)

$$P_{DC} = I_D V_{dd} = \frac{I_p V_{dd}}{\pi} = \frac{V_{dd} \cdot (V_{dd} - V_{knee})}{\pi \cdot R_L}$$

(2.21)

$$P_{diss} = \frac{1}{T} \int_{0}^{T} i_{DS}(t) v_{DS}(t) dt$$

(2.22)

$$\eta_{\max} = \frac{P_{out}}{P_{DC}} = \frac{(V_{dd} - V_{knee})^2}{4 \cdot R_L} \cdot \frac{\pi \cdot R_L}{V_{dd} \cdot (V_{dd} - V_{knee})} = \frac{V_{dd} - V_{knee}}{V_{dd}} \cdot \frac{\pi}{4}$$

(2.23)

### 2.1.4 Class AB

Class AB amplifiers are biased in such a way that the conduction angle is between 180° and 360°. The maximal efficiency is therefore between 50% and 78.5% depending on the conduction angle. In practice most class B amplifiers will be designed slightly into the class AB region, due to the nonlinearities of the turn-on region in the transistor. This means that a vast majority of the power amplifiers for wireless communications operate in class AB.

## 2.1.5 Class C

In a class C amplifier the conduction angle,  $\theta$ , is less than 180°. The efficiency depends upon the conduction angle and can ideally reach 100%. As the efficiency rises the power gain decreases, and the power added efficiency, will eventually fall to 0. The Class C amplifier operates highly non-linearly.

$$P_{out} = \frac{I_p^2 \cdot R_L^2}{4\pi^2} \cdot (2\theta - \sin 2\theta)^2$$

(2.24)

$$P_{DC} = \frac{V_{dd} \cdot I_p}{\pi} \cdot (\sin\theta - \theta\cos\theta)$$

(2.25)

$$\eta_{\max} = \frac{P_{out}}{P_{DC}} = \frac{2\theta - \sin 2\theta}{4(\sin \theta - \theta \cos \theta)}$$

(2.26)

## 2.2 Class D and F

Figure 2.9 Class D amplifier.

Much like the class A-C power amplifiers it is possible to treat class D and F as special cases of the same general theory. The original definition of a class D power amplifier uses two transistors operated as switches, see Figure 2.9. The on-resistance and therefore the loss in the transistor should be zero. The efficiency is limited by the switching time and the on-resistance of the transistor. Due to the switching behavior of the class D amplifier it is very non-linear and in principle not even power control is possible. The drain efficiency of a class D power amplifier is given by [2]:

$$V_{eff} = V_{DD} \frac{R_{dc}}{R_{dc} + R_{on}}, R_{dc} = \frac{8R_L}{\pi^2}$$

(2.27)

$$\eta = \frac{V_{eff} \sin \theta_s}{V_{dd} \theta_s}$$

(2.28)

where  $\theta_s = 2\pi t_s$  is the angle associated with the switching. The transient time  $t_s$  is the time required for one of the transistor to switch. This means that the switching of the power amplifier is completed within  $2t_s$ .

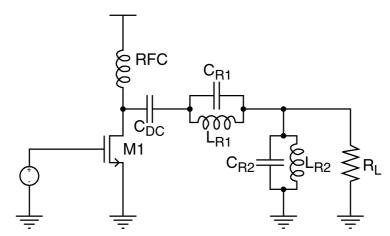

The basic idea of class F amplifiers is to reduce the power dissipated in the transistor by minimizing the voltage across the transistor at the time where the current through the transistor is largest. This is accomplished by modifying a class B amplifier with a quarter-wave stripline to short all even harmonics and appear as open at odd harmonics, while the fundamental does not see the load as normal. The harmonic termination means that the waveform of the output signal will be a square wave. This gives a maximum achievable efficiency of 100% and is actually the same condition as class D although single-ended [3].

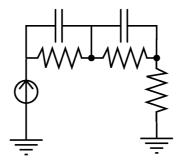

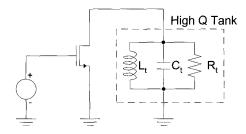

Instead of a stripline a 3rd harmonic termination using a resonator consisting of an inductor and a capacitor can be used. The maximum achievable efficiency for this type of amplifier is then approximately 88%, which is about 10% better than the class B amplifiers. The principle of the class F power amplifier with third harmonic termination is shown in Figure 2.10.

Figure 2.10 Class F power amplifier with third harmonic termination.

It is also possible to use a 2nd harmonic termination. The maximum achievable efficiency for this type of amplifier is then approximately 85%. A number different configurations are possible, but in general the increased efficiency is followed by increasing complexity. It is also important to bear in mind that the increased complexity increases the total losses in the nonideal passive components.

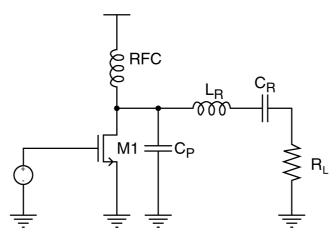

## 2.3 Class E

The class E amplifier is a tuned amplifier, which ideally can reach an efficiency of 100% [4]. The transistor works as a switch as is the case with class D amplifiers, but only one transistor is used. The basic idea is to delay the voltage curve so that the drain voltage does not rise till after the switching is done. This kind of operation causes the class E amplifier to be very nonlinear. Even for a non-ideal transistor the efficiency of a class E power amplifier can be quite high.

Figure 2.11 Generic class E power amplifier.

The design of a class E power amplifier is characterized by the choice of conduction angle, supply voltage and peak current. The output power and peak voltage depends on the conduction angle. This means that they both rise with increasing conduction angle. For a reasonable output power the peak voltage is at least three times the supply voltage. This causes problems if the transistors used have relatively low breakdown voltage.

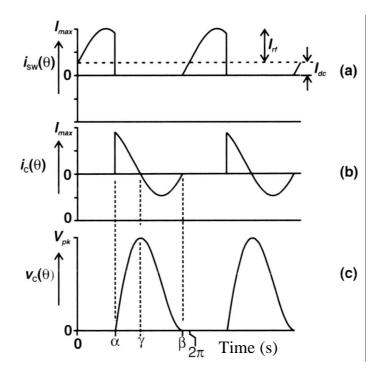

Figure 2.12 Drain and capacitor current and drain voltage of a class E PA [1].

# 2.4 Class S

The class S amplifiers operate in the same way as class D, but the pulse width is modulated. The class S amplifier demands even faster transistors than the class D

amplifier, since the pulsewidth modulation causes very short pulses to be generated. Once again the efficiency can ideally reach 100%.

The pulsewidth modulations means that the power amplifier acts linearly assuming the pulsewidth modulation is linear. In principle this configuration makes it possible to build very high efficiency power amplifiers, but the generation of the pulsewidth modulation is very troublesome.

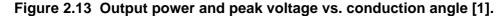

One approach to the pulsewidth modulation is  $\Sigma\Delta$ -modulation [5], this is illustrated in Figure 2.14. The RF signal is then oversampled, e.g. an oversampling rate of eight. The drawback of this approach is that the digital logic will have to run at eight times the frequency of the RF signal. At these frequencies the digital logic will have a large power consumption which will degrade the total efficiency. Another drawback is the need for a bandpass filter at the output of the power amplifier.

Figure 2.14 Class S power amplifier with  $\Sigma\Delta$ -modulation.

# **2.5 Differential Power Amplifiers**

The differential power amplifier differs from an ordinary power amplifier in a number of ways. There are advantages as well as disadvantages of differential power amplifiers. In principle a differential amplifier might just be two separate amplifiers coupled in parallel, although a lot of the advantages will not be available then.

One of the big challenges of high efficiency power amplifiers is the inductance in series with the ground. The effect of the ground inductance can be reduced by a differential amplifier.

One of the main motivations to use differential power amplifiers is the tempting idea that they can drive a differential antenna. The differential antennas have not yet proven to be usable in mobile phones. One of the problems with differential antennas is that the specific absorption rate (SAR) is higher than in single-ended antennas. Another problem with the differential antennas is the fact that either the efficiency or the bandwidth of the antennas drops when operated in differential mode. Since the bandwidth of an antenna for mobile phones is already close to the specifications, a differential antenna will have lower efficiency, thereby eliminating the best argument for differential power amplifiers.

If a differential power amplifier will have to drive a single-ended antenna a differential to single-ended conversion will have to take place somewhere after the power amplifier. A differential to single-ended conversion is always associated with loss and increased cost.

# 2.6 Summary

As described above there are numerous classes of operation, with different advantages and disadvantages. In order get a quick overview of the different classes Table 2.1 can be used.

| Class | Maximum<br>efficiency | Linearity | Note       |

|-------|-----------------------|-----------|------------|

| А     | 50%                   | Good      |            |

| AB    | 50-78.5%              | Fair      |            |

| В     | 78.5%                 | Fair      |            |

| С     | 78.5-100%             | Poor      |            |

| D     | 100%                  | Poor      |            |

| Е     | 100%                  | Poor      |            |

| F     | 85%                   | Fair      | 2nd harm.  |

| F     | 88%                   | Fair      | 3rd harm.  |

| F     | 100%                  | Fair      | Even harm. |

| S     | 100%                  | Good      |            |

Table 2.1 Quick overview of the classes of operation.

For a more detailed comparison, the properties of the transistor have to be included, especially the maximum power gain, the supply voltage and the knee voltage.

In practice only a few of the classes of operation are useful for wireless communication. The class A power amplifier is typically used for basestations as well as mobile phone standards with high linearity requirements. The class AB power amplifiers are used for a broad range of mobile phones. The class C power amplifiers are also in use but typically introduce practical problems due to the relatively low output power for a fixed transistor size.

The class B power amplifier does not exist in practical applications due to the nonideal devices, which will cause the power amplifier to operate in either class AB or C. The class D and E power amplifiers are difficult to use since they do not even facilitate power control, class S on the other hand is almost impossible to use at RF frequencies.

The only class of operation not in common use, which is suitable for wireless communications is the class F power amplifier. The class F power amplifier is currently the subject of a lot of research.

If one of the strongly nonlinear class of operation is to be used for wireless communications one of the linearization systems will have to be introduced, but in general they add complexity as well as lower the total efficiency.

## References

- [1] S. C. Cripps, *RF Power Amplifiers for Wireless Communications*. Artech House, 1999.

- [2] H. L. Krauss, C. W. Bostian, and F. H. Raab, *Solid State Radio Engineering*. John Wiley Sons, 1980.

- [3] F. H. Raab, "Class-F power amplifiers with maximally flat waveforms," *IEEE Transactions on Microwave Theory and Techniques*, vol. 45, pp. 2007--2012, November 1997.

- [4] N. O. Sokal and A. D. Sokal, "Class E a new class of high efficiency tuned single-ended power amplifiers," *IEEE Journal of Solid State Circuits*, pp. 168--176, June 1975.

- [5] M. Iwamoto, J. Hinrichs, J. Arun, L. Larson, and P. M. Asbeck, "A push-pull bandpass delta-sigma class-S amplifier," in 2000 IEEE Topical Workshop on Power Amplifiers for Wireless Communications Technical Digest, September 2000.

# CHAPTER 3 LOAD-LINE THEORY AND IMPEDANCE MATCHING NETWORKS

As explained in Chapter 2 the load impedance along with the class of operation are probably the most important aspects of power amplifier design. The source impedance of the power amplifier stage will of course also have to be selected.

In the following sections a number of methods for selecting the source and load impedances will be described. First the small-signal methods will be introduced, since they are simple and can be based on S-parameter data which are usually available. After the small-signal methods the large-signal methods will be described. The classical load-pull measurement technique will be introduced. Then a similar simulation technique will be developed for use in integrated circuit design.

After the proper source and load impedances has been selected, the impedance matching networks must be synthesized. The different kinds of matching networks will be described in this chapter. The steps involved in synthesis of the impedance matching networks will also be explained. The synthesis methods will also be used as a part of the load-pull simulation method.

# 3.1 Small-Signal Impedance Matching

The small-signal impedance matching approaches are primarily suited for small-signal RF components such as LNAs. It is however useful to know the small-signal impedance matching methods, since they can be used as a starting point for especially the matching of the input of the power amplifier. The small-signal impedance matching methods are all based on the properties of S-parameters which will be described shortly in the following section.

To obtain maximum gain in a device the transducer gain method is used. It is however not always desirable to achieve maximum gain match, since other parameters such as noise and output power might be more important than the gain of the amplifier. This means that the matching network is often a compromise between gain, output power and noise. There are two methods to optimize the trade-offs of the matching networks, namely the operating gain method and the available gain method. All of the above mentioned matching methods will be described in the following sections.

#### 3.1.1 S-Parameters

The scattering parameters, better known as S-parameters, is the most common set of small-signal parameters used to characterize RF devices, active or passive. This is due to the fact that Z and Y parameters can not be measured accurately at RF frequencies. The difficulties of measuring Z and Y parameters at RF frequencies are caused by the lack of good open and short terminations at RF frequencies. Furthermore the short-circuits used in Z and Y parameter measurements, will often cause the device under test (DUT) to become unstable.

The S-parameters are measured using normalized incident and reflected travelling waves of transmission lines at the ports. The four parameters of a two-port S-parameter measurement are:

$S_{11}$  = the input reflection coefficient

$S_{12}$  = the reverse transmission coefficient

$S_{21}$  = the forward transmission coefficient

$S_{22}$  = the output reflection coefficient

Once the S-parameters have been measured it is of course possible to convert them to other small-signal representations, e.g. Z and Y parameters.

#### 3.1.2 The Smith Chart

The Smith chart is used to represent the S-parameter data described above. The Smith chart is a graphical representation of the reflection coefficient plane, the  $\Gamma$  plane, with the relation

$$\Gamma = \frac{Z - Z_0}{Z + Z_0}, \qquad \operatorname{Re}[Z] \ge 0 \tag{3.1}$$

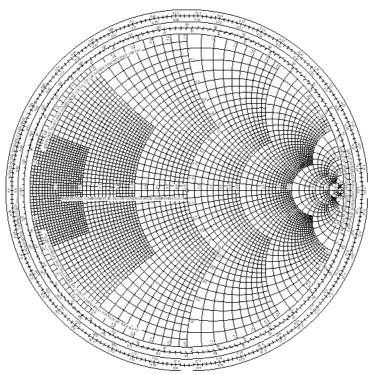

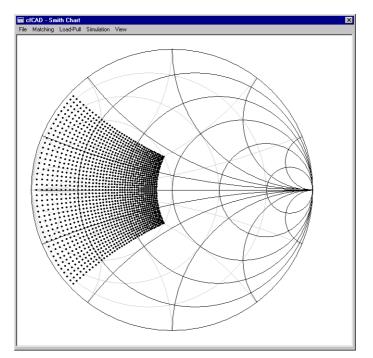

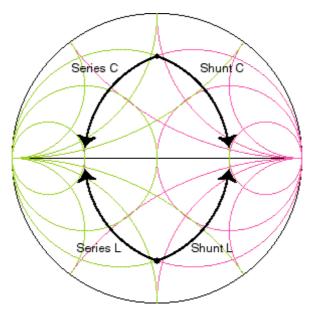

where  $Z_0$  is the reference impedance value. The basic Smith chart is shown in Figure 3.1. The advantage of the Smith chart is that it is possible to depict all impedances with a positive real part in a finite chart. The Smith chart is constructed of circles representing constant resistance and constant reactance.

Another feature of the Smith chart is the possibility to plot a number of important RF parameters as circles. Examples are stability circles, noise circles and constant Q circles[1][2][3].

Figure 3.1 The Smith chart.

#### 3.1.3 Transducer Gain Method