Technical University of Denmark

### Modelling and Analyses of Embedded Systems Design

Brekling, Aske Wiid; Hansen, Michael Reichhardt; Madsen, Jan

Publication date: 2010

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Brekling, A. W., Hansen, M. R., & Madsen, J. (2010). Modelling and Analyses of Embedded Systems Design. Kgs. Lyngby, Denmark: Technical University of Denmark (DTU). (IMM-PHD-2011-236).

#### DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Modelling and Analyses of Embedded Systems Design

Aske Brekling

Kongens Lyngby 2010 IMM-PHD-2010-236

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk

IMM-PHD: ISSN 0909-3192

## Summary

Designing embedded systems that are guaranteed to act correctly in any given situation is an extremely hard task. Modern embedded systems consist of applications that are typically executed on multi-core execution platforms. Analyzing timing aspects of such multi-core platforms is particularly difficult, as they may exhibit counter-intuitive behavior - so-called timing anomalies - where e.g. faster execution time of an individual part of a system may cause increased execution time for the system as a whole. In the work described here, we focus on the timely aspects and show examples of systems containing such timing anomalies.

The ARTS framework is an abstract simulation framework for embedded systems that is used where an application meets an execution platform. The application is described by a task graph and the execution platform through its processing elements and interconnects. A mapping of tasks onto the processing elements concludes a system described in ARTS. In this simulation framework, designers can - early in the design process - conduct design space exploration and analyze different configurations and setups of systems in terms of their timely behavior and resource usage. As analysis is based on simulation, only indications of the system behavior can be identified, but no guarantees can be given.

In the work presented in this dissertation, we aim at capturing this scenario: an application, an execution platform and the mapping, in a formal model. On the basis of this formal model, we conduct verification of real-time constraints and guarantee that the system acts correctly in terms of meeting all its timely requirements. We present the MoVES languages: a language with which embedded systems can be specified at a stage in the development process where an application is identified and should be mapped to an execution platform (potentially multicore).

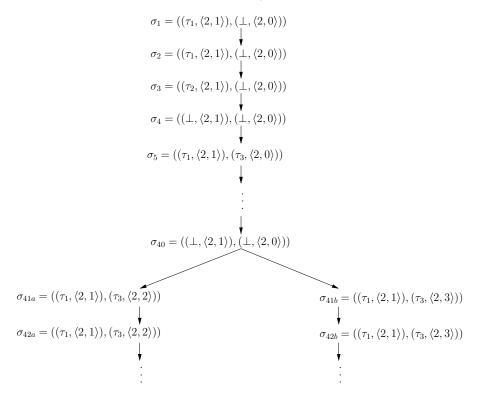

We give a formal model for MoVES that captures and gives semantics to the elements of specifications in the MoVES language. We show that even for seemingly simple systems, the complexity of verifying real-time constraints can be overwhelming - but we give an upper limit to the size of the search-space that needs examining. Furthermore, the formal model exposes important scheduling situations that become central in establishing timed-automata models that can be used for analysis of MoVES specifications effectively.

Finally we present the MoVES tool, which can conduct automatic verification of interesting properties of MoVES specifications. In several examples, we use the MoVES tool to conduct analysis that identifies timing anomalies. We also conduct design space exploration in an example using the MoVES tool. And we show that it can be used for analysis of systems that, in size, resemble industrially-interesting systems.

We find that semantically-based verification is a promising approach for assisting developers of embedded systems. We provide examples of system verifications that, in size and complexity, point in the direction of industrially-interesting systems.

## Resumé

At designe indlejrede systemer der kan garanteres at virke korrekt i enhver situation, er vanskeligt. Moderne indlejrede systemer er anvendelser, som typisk afvikles på platforme med flere processorer - såkaldte kerner - og at analysere tidslige aspekter af sådanne multi-kerne platforme er især svært, da de kan udvise kontraintuitiv adfærd - såkaldte tidslige anomalier - hvor for eksempel hurtigere eksekveringstid for en enkelt del af systemet kan resultere i en langsommere eksekveringstid for hele systemet. Med dette arbejde fokuserer vi på tidslige aspekter og vi viser eksempler på systemer med sådanne tidslige anomalier.

Framework'et ARTS er et abstrakt simuleringsframework for indlejrede systemer, der benyttes til analyse, hvor anvendelser møder eksekveringsplatforme. Anvendelser er beskrevet ved task-grafer og eksekveringsplatforme i form af processeringselementer og deres forbindelser. Efter mapning af de individuelle tasks til processeringselementer er et fuldt system beskrevet i ARTS. I dette simuleringsframework kan designere tidligt i design processen afprøve forskellige design af systemer i form af tidslige aspekter og aspekter vedrørende brug af resourcer. Eftersom analysen er baseret på simulering, kan den kun bruges som indikation på, hvordan systemet opfører sig, men der kan på ingen måde gives garantier i forhold til systemets tidslige krav.

I denne afhandling går vi efter at indfange netop dette scenarie; anvendelser, eksekveringsplatforme og mapning i en formel model. På basis af denne model kan verifikation af realtidskrav af tasks eksekveret på kerner udføres, og der kan gives garantier om alle systemets tidslige krav.

Vi præsenterer sproget MoVES, et sprog med hvilket indlejrede systemer kan specificeres på et tidspunkt i designprocessen, hvor anvendelser er identificeret, og disse skal mappes på eksekveringsplatforme potentielt med flere kerner.

Vi giver en formel model, der indfanger og giver semantik til specifikationer beskrevet i sproget MoVES. Vi viser, at det at verificere realtidskrav for selv tilsyneladende simple systemer kan have stor kompleksitet, men vi giver en øvre grænse for den del af søgerummet, der skal undersøges. Den formelle model viser derudover, hvordan vigtige skeduleringssituationer er centrale når man skal udvikle tidsautomatimplementeringer der kan bruges til at analysere MoVES specificationer effektivt.

Sidst men ikke mindst præsenterer vi værktøjet MoVES, som kan udføre automatisk verifikation af interessante egenskaber på baggrund af MoVES specifikationer. Vi benytter værktøjet på en række eksempler, hvor tidslige anomalier identificeres. Vi giver også eksempler på, hvorledes man kan afprøve forskellige design af systemer (design space exploration) med værktøjet, og vi viser, at det kan benyttes til analyse af systemer, som i størrelse kunne have industriel interesse.

Vi fastslår, at semantisk baseret verifikation er en lovende mulighed for udviklere af indlejrede systemer, og vi viser eksempler på systemverifikationer, som i størrelse og kompleksitet peger i retning af for industrien interessante systemer.

## Preface

This dissertation was prepared at DTU Informatics, the Technical University of Denmark, in partial fulfillment of the requirements for acquiring the degree of Doctor of Philosophy.

The dissertation deals with analysis and verification of embedded systems. The main focus is to develop languages, methods and tools that assist developers in early stages of the process of designing embedded systems.

The dissertation is self contained and relies on the work done in a number of research papers written during the period 2006–2010.

The PhD project has been funded by MoDES (Danish Research Council 2106-05-002).

The collaboration on the MoDES and DaNES projects has inspired most of this work, with input and examples from the academic partners: Technical University of Denmark, Aalborg University and University of Southern Denmark, as well as industrial partners: Hardi International A/S, Skov A/S, Danfoss A/S, Reactive Systems inc, CSI Center for Software Innovation, PAJ Systemteknik, ICEpower, Novo Nordisk, Terma and Prevas.

Lyngby, 2010

Mu Th

Aske Brekling

vi

## Acknowledgements

First and foremost I would like to thank my main supervisor, Michael R. Hansen, for his support and encouragement over the years. He has been available for discussion and comments at all times, and has been a source for both inspiration and guidance in all aspects of the project. He has been the most perfect supervisor anyone could ever ask for. Without him, this work would not have been possible at all.

Also thanks to my other supervisor, Jan Madsen. He has provided great insight in the area of embedded systems and the current state of the art research. Jan has an incredible way of looking at issues from different angles. This has made it possible to think out-of-the-box and come up with very interesting solutions and ideas.

Part of the work was carried out while visiting Virginia Tech University and Aalborg University. I would like to thank Patrick Schaumont for inviting me and for welcoming me at Virginia Tech. My stay gave great insight into how hardware descriptions can be done at higher abstraction levels, and how the Gezel language can be used as part of development. I also got to see how he uses Gezel in the courses given on Introduction to Hardware/Software Codesign. Also thanks to Kim G. Larsen for inviting me and giving me a chance to take part of the inspiring research community at Aalborg University. While visiting, I got the chance to meet developments. I also got a chance to discuss issues of modelling with timed-automata with some of the researchers.

Thanks to all of the fellow PhD students in the Embedded Systems Engineering

section at DTU Informatics. Together we have created a great atmosphere that supports both the social sides and generates room for the exchange of opinions that can lead to great synergies in our work. I especially would like to thank Per Larsen, Peter V. B. Sørensen, Stavros Passas and Pascal Schleuniger for sharing office space with me. We have had some great times, and inspiring talks.

Thanks to everyone I have met throughout the past years. People that I have discussed and turned an amazing amount of interesting stones with. Kristian S. Knudsen and Jens Ellebæk were during their Master's work a great driving factor for the development of MoVES. My fellow university students... special thanks to Anders Høeg Dohn, Pavel Kozin and Søren G. Christensen for keeping me sane, and to all the great people I met and had great moments with at the Marktoberdorf summer school 2008.

Finally, the greatest thanks goes to my family; my mother and father, my siblings and their families - you are the strong base that every inspiring thought and all development in my thoughts comes from. My daughter Adia, who can make me continue that extra mile, and who makes me realize why I do the things I do. The love of my life, my wife Jeanifer! Always supportive, understanding and helpful. You make it possible for me to succeed.

## Contents

| Su | immary                                                                                                         |                                                                    |       | i                     |

|----|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------|-----------------------|

| Re | esumé                                                                                                          |                                                                    |       | iii                   |

| Pr | reface                                                                                                         |                                                                    |       | $\mathbf{v}$          |

| Ac | cknowledg                                                                                                      | ements                                                             |       | vii                   |

| 1  | <ol> <li>1.2 Motiv</li> <li>1.3 Purper</li> </ol>                                                              | tion<br>rent Approaches for Analysis of Embedded Systems<br>vation | · ·   |                       |

| 2  | <ul> <li>2.1 Appli</li> <li>2.2 Exect</li> <li>2.3 Mapp</li> <li>2.4 Scheet</li> <li>2.5 Simulation</li> </ul> | Description         Image: Model           ication                 | · · · |                       |

| 3  | 3.1 Conc                                                                                                       | <b>/ES Language</b><br>rete Syntax for the MoVES Language          |       |                       |

| 4  | 4.1 Sema                                                                                                       | s for MoVES<br>antical Concepts Explained Informally               |       | <b>39</b><br>39<br>43 |

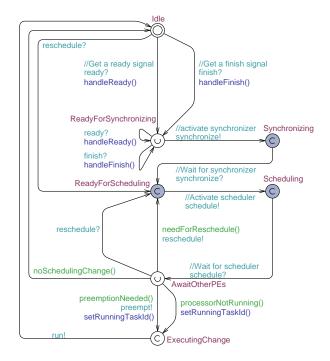

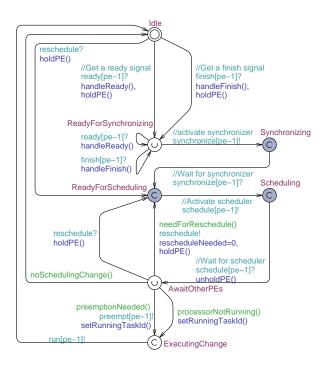

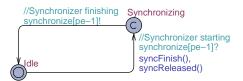

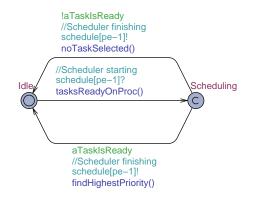

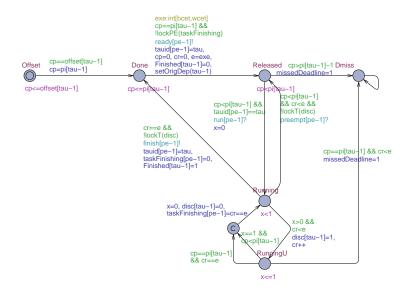

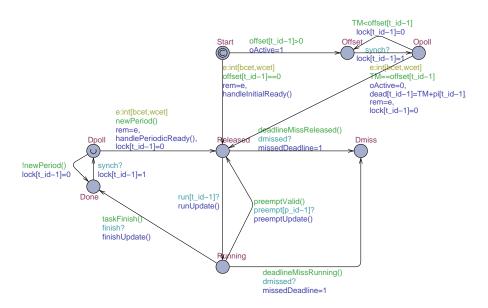

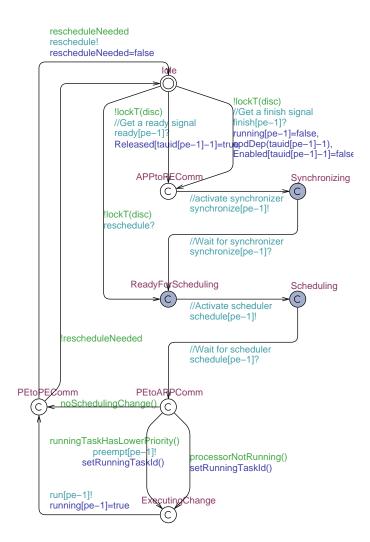

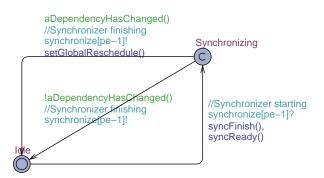

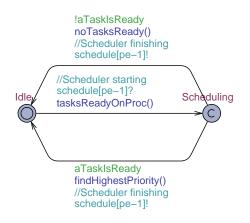

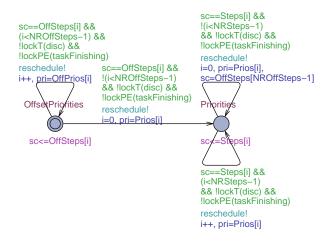

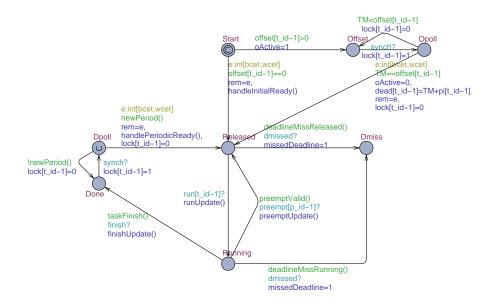

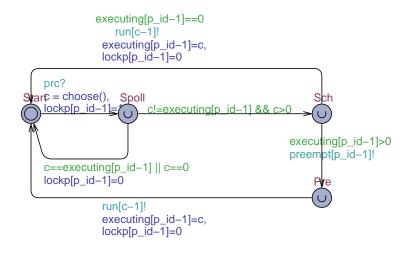

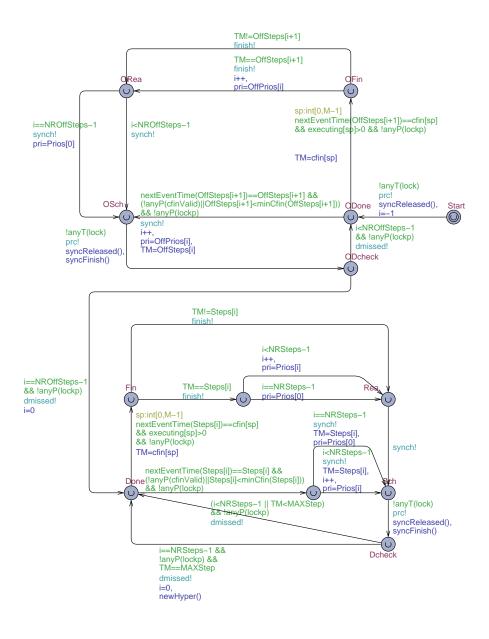

| 5  | 4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br><b>Mo</b><br>5.1<br>5.2<br>5.3<br>5.4 | Model of the Execution Platform                            | 43<br>44<br>45<br>49<br>53<br><b>55</b><br>56<br>71<br>72<br>74 |

|----|---------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------|

| 6  | Tho                                                                             | MoVES Tool                                                 | 75                                                              |

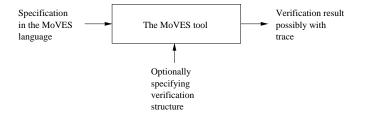

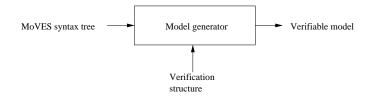

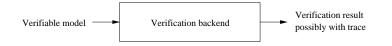

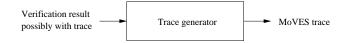

| 0  | 6.1                                                                             | A User's Perspective of the MoVES Tool                     | 76                                                              |

|    | 6.2                                                                             | The MoVES Framework                                        | 80                                                              |

|    | 6.3                                                                             | Integrating the Pieces                                     | 89                                                              |

|    | 6.4                                                                             | The MoVES Tool Available Online                            | 90                                                              |

|    | 6.5                                                                             | Summary                                                    | 91                                                              |

| 7  | Exa                                                                             | mples                                                      | 93                                                              |

|    | 7.1                                                                             | The Windmill Control System                                | 94                                                              |

|    | 7.2                                                                             | MP3 Decoder                                                | 98                                                              |

|    | 7.3                                                                             | Multiprocessor Anomalies                                   | 101                                                             |

|    | 7.4                                                                             | Very Late Deadline Miss                                    | 103                                                             |

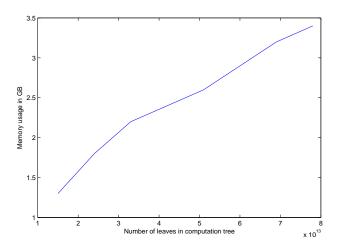

|    | 7.5                                                                             | Systems with Large Hyper-Periods                           | 104                                                             |

|    | 7.6                                                                             | Summary                                                    | 106                                                             |

| 8  | Pers                                                                            | spective                                                   | 109                                                             |

|    | 8.1                                                                             | Verification Structures and Backends                       | 110                                                             |

|    | 8.2                                                                             | Purely Deterministic Systems                               | 110                                                             |

|    | 8.3                                                                             | Analysis of Resource Usage                                 | 111                                                             |

|    | 8.4                                                                             | Hardware Specifications and Tasks in MoVES                 | 112                                                             |

|    | 8.5                                                                             | Ideal Assumptions                                          | 115                                                             |

|    | 8.6                                                                             | MoVES in the Context of Networked Embedded Control Systems | 115                                                             |

|    | 8.7                                                                             | MoVES in a Greater Development Process                     | 116                                                             |

| 9  | Con                                                                             | clusion                                                    | 119                                                             |

|    | 9.1                                                                             | Final Remarks                                              | 120                                                             |

| AĮ | open                                                                            | dix                                                        | 122                                                             |

#### CONTENTS

| $\mathbf{A}$ | Timed-Automata Templates for Verification Structures |                                               |     |  |

|--------------|------------------------------------------------------|-----------------------------------------------|-----|--|

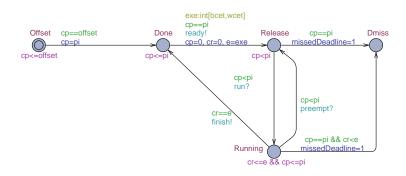

|              | A.1                                                  | Stop-watch automata model                     | 123 |  |

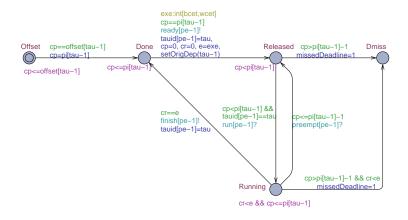

|              | A.2                                                  | Alternative stop-watch automata model         | 132 |  |

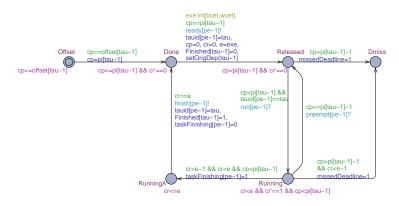

|              | A.3                                                  | Model with discretization of the running time | 142 |  |

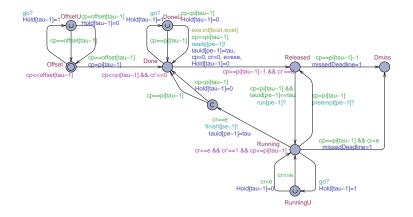

|              | A.4                                                  | Genuine discrete model                        | 151 |  |

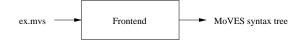

| в            | Sou                                                  | rce Code for the MoVES Tool                   | 161 |  |

|              | B.1                                                  | Frontend                                      | 161 |  |

|              | B.2                                                  | Model generator                               | 168 |  |

|              | B.3                                                  | Trace generator                               | 183 |  |

| $\mathbf{C}$ | Bat                                                  | ch Scripts for MoVES                          | 191 |  |

|              | C.1                                                  | For Windows Users                             | 191 |  |

|              | C.2                                                  | For Linux Users                               | 193 |  |

### CHAPTER 1

## Introduction

Embedded systems are computer systems that are integrated into any kind of system - physical, mechanical, etc, and which are not easily accessible. They are characterized as being able to conduct one or more dedicated tasks for that specific system. There are increasing uses of embedded systems within many industries: avionics, automotive, medical equipment and consumer electronics, just to name a few.

Let us take an example from the automotive industry. A modern car can have embedded systems consisting of about 100 electronic control units. These units can execute tasks in anything from the climate control system to entertainment systems such as radio, navigation, video, etc, to the anti-lock braking system. This allows for capabilities that are much more advanced than could otherwise be included in the car. In this way, the user can enjoy these added features. It also offers more safety because it can use complex computation to adjust the behavior of the car in critical situations.

Within the area of consumer electronics, embedded systems practically are the products. Handheld gadgets such as multimedia players, GPS navigation equipment and smart phones are systems that can be viewed as a complete embedded system with just a simple interface to the user in terms of keypad, screen, loudspeakers, headphones, etc. For example, when handheld CD-players were popular, they comprised mechanical components that turned the disk, read it,

etc., together with the electronics. But today's MP3 players have no mechanical components. They are basically embedded systems that contain processing elements, storage, interconnections and simple user interfaces.

#### Dangers of faulty embedded systems

Some embedded systems are extremely safety critical. Consider, for example, the airbag safety system in a car. In the case of an accident, if the airbag does not deploy (or deploys milliseconds too early or too late), it can have fatal consequences. Within avionics, practically every component is considered safety critical; even a small error here can be life threatening. In 1996, Ariane 5's (Figure 1.1) first test flight, resulting in self destruction 37 seconds after launch, is one of the best-known faulty embedded systems. A data conversion from a 64-bit floating point value to a 16-bit signed integer value was the cause of the rocket's total destruction.

Figure 1.1: Ariane 5

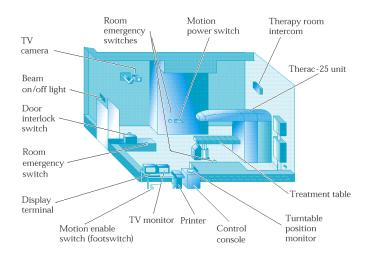

The area of medical electronics is obviously safety critical as well: The case of Therac-25 (Figure 1.2) resulted in six incidents between 1985 and 1987, where patients were given massive radiation overdose caused by a faulty embedded system in the radiation accelerator.

The Mars Pathfinder mission (see the Mars Pathfinder on Figure 1.3) is an example where timing properties and resource usage resulted in system failure. After a few days on Mars, the space craft began experiencing total resets, resulting in loss of data. It turned out to be a case of priority inversion in a concurrent execution context. If the problem had not been fixed, the whole mission would have been a total failure. Fortunately, the onboard software could be modified and the mission resumed with complete success.

Figure 1.2: Typical Therac-25 facility

Figure 1.3: Mars Pathfinder

For many embedded systems, especially within consumer electronics, flawed systems can have a detrimental effect on the image of the producing company. If a manufacturer of cell phones releases a model that has a tendency to freeze up and needs to be reset often, users quickly communicate this to each other, and many people would come to prefer a different manufacturer for their next product. In the case of severe manufacturing defects, the product may need to be recalled. This both tarnishes the brand's reputation and is an extremely lengthy and expensive process. A flawed system like this can result in a decrease in market shares. Whether the consequences of erroneous systems are dangerous or financially disastrous, a way to avoid such errors is much needed. The earlier in the design process these errors can be detected the better. However, these systems are growing in numbers; they are being used in a wider range of industries and are becoming more and more complex. It therefore becomes more difficult to detect system flaws. This is why it is crucial to use a systematic approach of analysis and constructive development. This approach should allow designers to make decisions when some details of the system are still undetermined, in order to detect possible flaws early in the design process.

### 1.1 Different Approaches for Analysis of Embedded Systems

Model-based development of embedded systems [53] has become an important discipline. This development start with abstract specifications of the system in terms of functional- and non-functional requirements. Functional requirements specify what the system is supposed to do, whereas non-functional requirements specify issues such as timing and other resource constraints on the system. Through a number of refinement steps, the development may end at a stage where the tasks of the systems have been identified together with their interdependencies, and a platform for executing the system is identified together with a mapping of the tasks onto the platform.

In order to avoid development of faulty systems, analyses of designs are needed at every stage of the development process. A key goal for such analyses is to determine whether the system is able to run without faults. If a system is defined as a number of tasks being executed and each task (or the system as a whole) having deadlines, this analysis will determine if any deadline of the system is missed, i.e. the system is not schedulable.

Analyses of systems that execute several tasks or processes have been studied extensively the last decades [7, 43]. This section will attempt to provide an overview of different approaches starting with the very general topic addressed by classic schedulability theory and ending with approaches specifically aimed at embedded systems.

#### 1.1.1 Classic schedulability analysis

Liu and Layland [42] analytically studied schedulability of systems consisting of multiple tasks sharing processing elements as early as 1973. Classic schedula-

bility theory originated in scheduling of multiple tasks on a single processor but has developed into the area of distributed systems.

#### 1.1.1.1 Single processor

In [42], Liu and Layland studied the problem of multiple task scheduling on a single processor. The results in this paper include an upper bound to processor utilization for an optimum fixed-priority scheduler (i.e. a rate-monotonic scheduler). It is optimal in the sense that if a system is schedulable using any fixed-priority scheduler, it is schedulable using rate-monotonic scheduling. This upper bound can be calculated as follows:

$$\sum_{i=1}^{m} (C_i/T_i) \le m(2^{1/m} - 1)$$

where m is the number of tasks in the system,  $C_i$  and  $T_i$  are the execution time and the period of task i, respectively.

Also, it is shown that full processor utilization can be achieved by dynamically assigning priorities based on their current deadlines (i.e. earliest-deadline-first scheduling), provided that

$$\sum_{i=1}^{m} (C_i/T_i) \le 1$$

Much of the later research in the area of schedulability analysis is based on these results. See e.g. [13, 14] for an overview of some of the later research results.

In [64, 63], Tindell extends these results to a more general approach for analyzing fixed priority hard real-time tasks. This approach captures aspects such as static priority preemptive systems, arbitrary deadlines and release jitter. This analysis uses a window approach to find worst-case response times. The window-based approach is based on the general concept of a busy period. The busy period is the maximum time that a task has to wait for higher prioritized tasks before it can execute. This busy period is divided up into a sequence of windows that correspond to each invocation of tasks with higher priority. When tasks of a system have different periods and if some tasks' deadlines are greater than their periods, a number of windows need to be examined to find the worst-case response time. In general the system's worst case response time could correspond to the response time in any one of the windows.

In a simple case where deadlines for all tasks are smaller than or equal to their periods, the worst-case response time  $r_i$  for task *i* can be computed by the following recursive function:

$$r_i = C_i + \sum_{j \in hp(i)} \left\lceil \frac{r_i}{T_j} \right\rceil$$

where  $C_i$  is the execution time for task *i*, hp(i) is the set of tasks with higher priority than task *i* and  $T_j$  is the period of task *j*.

For cases where some deadlines for tasks are greater than their periods, this equation becomes more complex as it has to take into account the response time in any one of the windows. Schedulability analysis in this context is to calculate the worst-case execution times for all tasks, and to ensure that they are all less than their deadlines.

#### 1.1.1.2 Distributed systems

When analyzing distributed systems, much more complex issues arise compared with analyzing single processor systems. In distributed systems, several tasks can execute concurrently, however, the issue of communication between processors must be addressed. If dependencies among tasks executing on different processors are taken into account, some timing anomalies can arise, i.e. local worst-case behavior does not give global worst-case behavior (when the whole system is addressed).

In [65], Tindell and Clark extend the analysis approach associated with static priority preemptive based scheduling with a so-called "holistic" approach. It is holistic in the sense that it takes the results from single processor scheduling theory and combines it with communication analysis to get a holistic view of the system. It addresses schedulability of distributed hard real-time systems. Specifically analysis of tasks with arbitrary deadlines, message parsing and shared data is derived. In all communication a simple TDMA protocol is assumed. The same window-based analysis technique as described for single processor analysis is used to find worst-case response times of distributed task sets. This approach introduces more complexity to the equations from the single-processor case. In the holistic approach, message parsing is included as tasks that need their response times calculated. Also, the time it takes to deliver a message at a receiving processor is taken into account. The approaches presented in [63, 64, 65] were refined and extended by Palencia et al. in [24, 25]. This was done by completing the proof of validity of the schedulability analysis technique as well as including offset information into the analysis. Thereby, an increase of the maximum schedulable utilization was achieved. In [29], González Harbour et al. describe the MAST [16] toolset. It contains several schedulability analysis tools capable of analyzing single processor and distributed systems. The tools are based on different scheduling analysis techniques, including the aforementioned approaches by Tindell and Clark as well as Palencia et al.

In [58], Pop et al. propose an optimization strategy for bus accesses in distributed embedded systems based on classic schedulability analysis, in particular the approach by Tindel and Clark [65]. The communication model is based on a time-triggered protocol and analysis for communication delays is presented.

The classic scheduling theory addresses issues regarding shared resources and blocking, however, the concept of dependencies among tasks is not directly addressed. Therefore, the aforementioned timing anomalies cannot be analyzed through classic scheduling theory. This model is coarse in the sense that for concrete systems with data dependencies it is non-trivial to give approximations of the communication overhead.

#### 1.1.2 Event stream analysis

The classic schedulability theory is not easily adapted to include analysis of heterogeneous systems. Furthermore, the complexity of the equations in the underlying analysis increases dramatically with size of systems. In [61], Thiele et al. propose a real-time calculus for schedulability analysis. In this analysis, a link between three areas is established: Max-Plus Linear System Theory [18], Network Calculus [17] and real-time scheduling [42]. In particular, the notions of request curves as a model for task behavior and delivery curves modelling hardware components' service of tasks are introduced. This provides a compositional approach, where each task executing on a hardware component is analyzed individually and given request- and service curves, which are then propagated through the distributed system. By the use and operations on these curves, an over-approximation is used. Thus, the results of these analyses do not provide exact results, and some results may be overly pessimistic. This work has resulted in the Real-Time Calculus (RTC) toolbox [67], which is a free Matlab toolbox for system-level performance analysis of distributed real-time and embedded systems.

In [32], Henia et al. present the SymTA/S approach. This work is based on the same compositional idea as in the work of Thiele et al., but instead of using generic request- and delivery curves and therefore having to introduce new complex stream representations, the notion of standard event models is presented (e.g. periodic-, sporadic-, periodic with jitter event models). These event models are described by sets of parameters. An example of an event model is a periodic with jitter event model, which has parameters for the period (i.e. time between periodic occurrence) and the jitter (i.e. the interval in which the exact occurrence takes place). Also, in the SymTA/S approach an overapproximation is used in the analysis, like with the Real-Time Calculus.

#### 1.1.3 Timed-automata analysis

In [5], Alur and Dill propose timed (finite) automata to model the behavior of real-time systems over time. Timed-automata theory is shown to be adequate for automatic verification of real-time requirements of finite-state systems. Real-time properties of such systems can be expressed as reachability problems of their timed automata models, e.g. in timed temporal logics. Several model checkers such as Kronos [68, 20] and UPPAAL [40, 8, 66] are available for automatic verification of such requirements.

There have been several examples of using timed-automata theory to model scheduling problems and in analyzing embedded systems: Abededdaïm and Maler show in [2] how the classic job-shop scheduling problem can be modelled as timed automata. In [1], this strategy is extended and includes problems with uncertainty in task durations. In [3], Altisen and Tripakis propose an implementation methodology for transformation of a timed automaton into a program with a check of whether the execution of this program on a given platform satisfies a desired property. The platform is modelled through its digital clock. In [26], Halkjaer et al. use timed-automata modelling to identify that a particular scheduler (i.e. the legOS scheduler) suffers from starvation and shows that a revised design of the scheduler does not. In [31], Hendriks and Verhoef show that timed automata can be used to model and analyze timeliness properties of embedded systems architectures, by systematically modelling and analyzing a case study. However, this is done by constructing the timed-automata models manually. In [54], Ovatman et al. provide experiments using priced timed automata for schedulability analysis as well as analysis of resource consumption.

In [23, 22], Fersman et al. present decidability results for schedulability analysis using timed automata. The overall conclusion of this work is that the schedulability-checking problem is undecidable if the following three conditions hold: 1) execution times are intervals; 2) the precise finishing time of a task instance influences other task releases; and 3) preemption is allowed. In [39], Krcál and Yi show that if one of the three conditions is dropped, the problem is decidable. Based on these results and the work on the UPPAAL model checker, Uppsala University has released the Times Tool [6, 21], which is a tool set for modelling, schedulability analysis and synthesis of schedulers and executable code. The version of Times Tool available at the current time is directly applicable for single-processor systems only.

In [19], David et al. provide alternative timed-automata implementations based on the models provided in [9]. The implementations generalize in certain areas, e.g. to include notion of jitter in task releases. The authors claim to provide an "...alternative account on how to model multiprocessor-scheduling scenarios most efficiently, by making full use of the modeling formalism of UPPAAL". It is unclear how this is most efficient and there are no examples verified that could substantiate this claim. The models provided in [9] are similar to the ones given in this dissertation in Section 5.1.6. The authors of [19] do not relate to stopwatch models like the ones in Sections 5.1.4 and 5.1.5 or to genuine discrete models like the one in Section 5.1.7. It turns out that most types of analysis are verified more efficiently on the basis of such models.

#### 1.1.4 Simulation-based analysis

Simulation-based methodologies are still the predominant technique for performance evaluation of embedded systems. In simulation-based approaches SystemC [41] is a de-facto language for system modelling. SystemC is a C++ library that supports modelling, which is true to the underlying hardware and provides an executable model that can be used for simulation. These SystemC-based simulation approaches can target either a specific area (e.g. communication or the real-time operating system) or provide system-level analysis. In system-level analysis, the full embedded system is modelled from application to execution platform, also modelled is the mapping of the application onto the platform as well as the communication.

#### 1.1.4.1 Specific-area analysis

In [44], Loghi et al. present MPARM, a cycle-accurate and signal-accurate analysis of on-chip communication in a MPSoC environment. The interconnects are simulated and different architectures are compared. The processors in the system are modelled by instruction-set simulators and all hardware is coded in SystemC.

There have been several examples of using simulation-based SystemC models for analysis specifically of the real-time operating system (RTOS). In [33], Hessel et al. provide an abstract RTOS model for embedded systems. The model includes a task model, a scheduler and synchronization. The goal of this work is to minimize the number of context switches. In [52], Moigne et al. present a generic RTOS model. The model includes synchronization, message parsing and global data sharing. The work focuses on durations of scheduling, context loads and context saves.

#### 1.1.4.2 System-level analysis

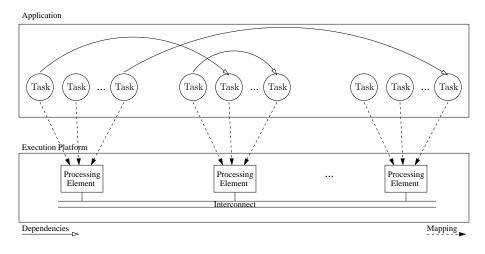

Within simulation-based system-level analysis much work has been conducted. Most of the modelling done at system level is based on the Y-chart of system design [57]. In the Y-chart there is a clear distinction between the application and the execution platform, and there is an explicit mapping of elements of the application onto the different parts of the platform.

In [38], Kempf et al. propose a SystemC-based simulation framework that allows evaluation of different mappings of the application onto the execution platform. The evaluation is conducted on an executable model of the system with annotated timing characteristics. The key element of this approach is a configurable event-driven virtual processing unit, which captures timing behaviors of the platform.

In [30], Haubelt et al. present a SystemC-based design methodology for mixed hardware/software solutions mapped to FPGA-based platforms. The approach supports automatic design space exploration, automatic performance evaluation and automatic system generation. The core result of this work is SysteMoC, a SystemC-based library that permits execution of well-known models of computation, which have been applied in the design of digital signal processing algorithms.

In [56], Pimentel et al. present the Sesame framework, which provides high-level modelling and simulation methods as well as tools for system-level performance

evaluation and exploration of heterogeneous embedded systems. Models of both the application and the platform are represented by graphs annotated with performance characteristics, e.g. computation requirements for each node in the application graph and processing capacity and power consumption for each node in the platform. In the exploration, the authors use the Strength Pareto Evolutionary Algorithm to find sets of approximated Pareto-optimal mapping solutions, i.e. solutions that are not dominated in terms of quality (performance, power and cost) by any other solution in the feasible set. SystemC simulation is used to provide performance estimates for the candidate solutions.

In [48, 47, 50], Madsen et al. present the SystemC-based framework ARTS. ARTS allows designers of multiprocessor system-on-chips to explore and analyze network performance, consequences of different mappings including memory and power usage and effects of RTOS selections including scheduling, synchronization and resource allocation policies. We will base our work on ARTS and will elaborate on this approach in Chapter 2.

#### 1.1.5 Summary of different analysis approaches

Classic scheduling theory works well for single processor systems under rather ideal assumptions. However, for larger multiprocessor systems, the classic approach lacks structure and compositionality, which dramatically increases the complexity of the equations in the underlying analysis. Although some approaches for including properties of the platform (e.g. communication strategies as in [58]) have been examined, actual system-level analysis - where all levels of the system are analyzed - is not. Also, the classic scheduling theory is based on pretty idealized models, e.g. although issues regarding allocation of shared resources are addressed, there is no concept of dependencies among tasks.

The event-stream analysis approaches introduces structure and compositionality. It does this through an over-approximation. Although this approach yields results for systems of very large size, the over-approximation can also in some cases lead to very pessimistic analyses.

The timed-automata approaches generally has two down falls. Many timedautomata-based analyses are very case oriented. This means that a very specific system is analyzed, but there is little (if any) automation and no clear underlying formal model. If any other system is to be analyzed, it must be manually modelled from scratch. Other timed-automata approaches such as Times Tool become very general. The analysis becomes mostly an analysis of the application as very little of the platform is modelled.

The simulation-based approaches give valuable input to designers early in the design process. However, as these approaches only examine some of the state space of the system, these approaches cannot provide guarantees. On the other hand, some of these simulation-based approaches, in particular ARTS, capture the generic structures and provide a modelling terminology that is very useful in embedded systems analysis. This terminology just lacks a clear formal model as a basis. In Chapter 4, we will formalize this terminology.

### 1.2 Motivation

The work described in this dissertation is intended to help designers of embedded systems. The aim is to provide designers with tools, models, languages, methodologies, etc., that in early stages of the design process can help the designer analyze different configurations and setups of systems.

Embedded systems today are getting more complex. It is difficult to use traditional methods to design, verify, validate and test them to make sure they are correct, reliable and not over-dimensioned. Over-dimensioning is when a designer would use larger, faster, more expensive, etc. components in systems in order to be "on the safe side". Results of over-dimensioning are usually waste of energy, space, money, etc.

Designs can also be oversimplified due to the complexity and lack of analysis methods. Oversimplification could be when a system is divided up into several individual parts that do not interact (e.g. an automotive embedded system where the airbag system is isolated from the rest of the embedded system). This oversimplification could result in limited functionality (e.g. lack of communication between systems) or in redundant subcomponents such as several identical sensors one for each individual part of the system in order to avoid interaction.

Since embedded systems are growing dramatically in complexity, they can do more and have more internal actions between very different components. This makes it hard to have an overview and to know what areas are critical and then test them. Many embedded systems are safety critical, and faulty systems could have fatal consequences.

When able to verify complex systems, one can:

- 1. Make bigger, life-critical systems that have more functionality, correctness and reliability. This can result in being able to solve bigger and more interesting problems while guaranteeing certain properties of the system.

- 2. Avoid over-dimensioning by creating less wasteful systems that are cheaper, smaller and more energy efficient.

- 3. Employ a systematic approach based on formal methods. This allows for a systematic design process in which one can easily re-verify system properties when making small alterations early in the design phases.

#### 1.2.1 An embedded system - windmill control

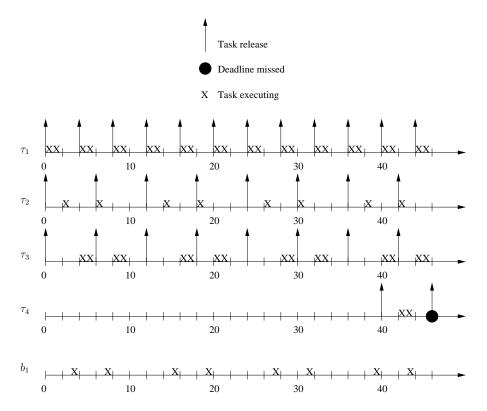

Consider an embedded control application for a windmill - this has deliberately been chosen as an academic example (not as a realistic real-life control system), in order to provide a more intuitive understanding of concepts. The windmill has an anemometer that measures wind speeds and a windvane that measures wind direction. The purpose of the embedded control application is a) to point the windmill as close as possible to the current wind direction and b) for safety reasons, to deploy a brake to stop the motion of the windmill when wind speeds exceed some threshold (e.g. 30 m/s). In order to meet these purposes, four individual tasks ( $\tau_1, \tau_2, \tau_3$  and  $\tau_4$ ) of the application can be identified:

- $\tau_1$  Take a reading from the anemometer and add it to a list of the 10 latest wind speed readings every 4 milliseconds

- $\tau_2$  Take a reading from the windvane and compare that direction to the direction that the windmill is currently pointing. The result of this comparison is a message, which can be represented in 2 bits every 6 milliseconds

- $au_3$  Based on the current comparison (conducted by  $au_2$ ), turn the windmill toward the direction of the wind. In order for  $au_3$  to begin execution,  $au_2$  must have finished its execution. We say that there is a dependency from  $au_2$  to  $au_3$ . every 6 milliseconds

$\tau_4$  While the windmill is running, if three or more of the 10 latest wind speed readings exceed the threshold, employ the brake to stop the windmill. While the windmill is not running (i.e. the brake is employed), if all of the 10 latest wind speed readings are below the threshold, release the brake to start the windmill. This task should not be executed before 10 readings are available (i.e. 40 milliseconds after the system starts). These checks are to be conducted every 6 milliseconds

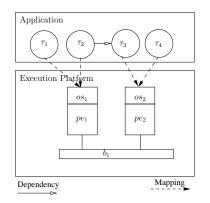

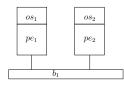

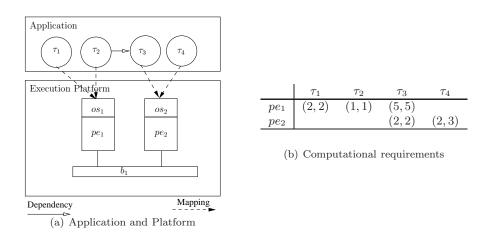

These four tasks are to be executed on an execution platform. Consider an execution platform made up of two processing elements  $(pe_1 \text{ and } pe_2)$ . The operating systems on both of these,  $os_1$  and  $os_2$ , can schedule tasks mapped to them based on a scheduling principle, either rate-monotonic or earliest-deadline-first. Initially rate-monotonic scheduling is chosen on both. In order to communicate messages from one to the other processing element resulting from inter-processor dependencies - i.e. when tasks in a dependency are mapped to different processing elements - the processing elements are connected via a bus  $(b_1)$ . This bus can transfer 2 bits/millisecond and uses a first-in first-out (FIFO) arbiter.

The mapping of the application onto the execution platform is as follows:  $\tau_1$  and  $\tau_2$  are mapped to  $pe_1$ , whereas  $\tau_3$  and  $\tau_4$  are mapped to  $pe_2$ . Note that since  $\tau_2$  and  $\tau_3$  are mapped to different processing elements, their dependency require the data (2 bits) to be transferred on  $b_1$  (at speed 2 bits/millisecond) - obviously this transfer takes 1 millisecond. In Figure 1.4, a graphical presentation of this system is given.

Figure 1.4: A windmill control system

The best-case execution time (bcet) and worst-case execution time (wcet) in milliseconds of executing the individual tasks of the application on the processing elements are given as (bcet, wcet) here:

Note that  $\tau_3$  can be executed by both processing elements, but execution on  $pe_2$  is much faster. Note also that for all tasks other than  $\tau_4$ , *bcet* and *wcet* are the same - i.e. execution of these tasks takes the same amount of time each time they are executed. However,  $\tau_4$  can be executed in 2 milliseconds in best case, that is, if no action is needed (i.e. the brake need not be deployed or released), whereas execution takes 3 milliseconds in worst case, if action is needed.

It is worth noting here, that in other approaches such as RTC [61] and SymTA [32] the notion of jitter is used to analyze and explain the issues that occur when dependent tasks mapped to different processing elements have a difference between best-case execution time and worst-case execution time. In analysis using jitter, the individual parts of the system are analyzed separately, and jitter propagates the uncertainty of tasks finishing times. In the analysis explored here, we will not use the notion of jitter. Instead, we consider all possible traces of the system in question, beginning from the initial start of the system.

The general question we would like an answer to, is whether or not the system will be able to autonomously execute the tasks forever (or at least infinitely long). In other words, will the chosen settings and properties make the overall system schedulable? If the answer is no, it would be desirable to have evidence of a situation where the system is not able to execute some task, i.e. where the system deadlocks.

Actual schedulability analysis of this system will reveal that the system can miss deadlines. If the platform is modified slightly, by choosing earliest-deadline-first as scheduling principle for the operating system  $os_2$ , the system will pass schedulability analysis without revealing deadline misses.

The windmill control system shown here is deliberately chosen as an academic example. We do not conclude that a windmill control system should be executed on a platform consisting of two processing elements as described here or that the exact timing properties are realistic. The example only highlights the terminology used and provides more intuitive understanding of some of the concepts involved when specifying embedded systems.

### 1.3 Purpose of this Project

In this project we aim at a concrete syntax and semantics that are based on ARTS models. These models are suitable for specification and analysis of systems early in the design process, at a stage where application and execution platform can be identified, but where neither are implemented or fully produced.

The application is characterized by only a task graph and timing requirements but without any detailed implementation details. The execution platform is defined simply in terms of number of processing elements, their general operating system properties and the interconnects, again without specific details on concrete implementation or synthesis.

Analysis at this stage gives the designer opportunity to make important design decisions without paying for decisions being made at later stages, when more implementation detail has been decided on, or when parts of the system have been developed or synthesized.

The thesis of our work is two fold:

- 1. That semantically-based verification of embedded systems can be suitable for problems that resemble industrially interesting examples of systems in size and complexity.

- 2. That models of timed automata, together with tools (specifically UPPAAL), are valuable as implementation platforms and verification backends for verifying properties of systems modelled.

### 1.4 The Structure of the Dissertation

The structure of the dissertation is as follows:

**Chapter 2:** We elaborate on the approach used in ARTS. The different components of ARTS specifications are explained and the underlying model used when simulating is discussed.

**Chapter 3:** We provide a language for specification of systems at an early point in the design process. This point is when the following three parts have been identified: 1) an application consisting of a number of interacting tasks , 2) an

execution platform made up of a number of interconnected processing elements and 3) a mapping of the tasks onto the processing elements.

**Chapter 4:** We derive a formal model that captures the different aspects of embedded systems and, in particular, formalizes the schedulability problem for embedded systems.

**Chapter 5:** We provide examples of how this formal model can be used as a basis for analysis and, in particular, how model checking of timed automata models implementing the formal model can be used to verify the schedulability problem.

**Chapter 6:** The tool MoVES is presented. MoVES can analyze systems specified in the language and, using an implementation of the formal model, make automatic verification of the schedulability problem possible.

**Chapter 7:** We give a range of different examples of systems, their specifications, their interesting properties and explanations of analysis using MoVES.

**Chapter 8:** We give indications to how this work can be further developed and what some of the consequences of early phase modelling have. We also show how the abstract models relate to models and implementations much closer to a final product.

Introduction

### Chapter 2

# ARTS Concepts and Informal Model

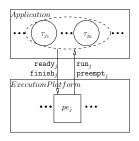

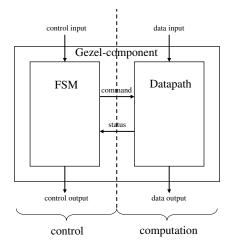

This chapter will introduce the concepts used in ARTS, a multi-processor systemon-chip (MPSoC) simulation framework developed at the Technical University of Denmark. There will also be explanations of the underlying informal model. ARTS is a SystemC-based framework that is constructed to make it easy for developers to try out different setups early on in the design process. It provides a simulation engine that can assist in evaluating crosslayer causality between the application, the operating system and the platform architecture. ARTS is a system-level framework, which can be identified as a framework for the overall system comprising the application, real-time operating system and the execution platform. It has been a conscious design decision that the simulation engine is clearly separated from the model.

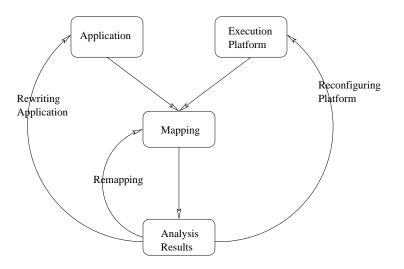

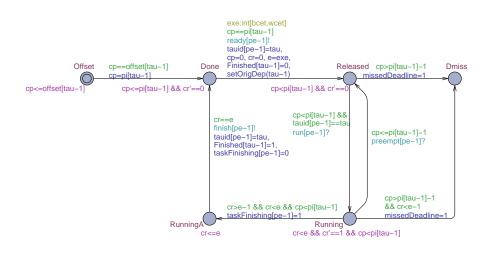

The ARTS framework models the *application* (described as *task* graphs capturing *dependencies* among tasks), the *execution platform*, i.e. the *processing elements*, their *interconnects* and the overall architecture and finally the *mapping* of the tasks onto the processing elements. In Figure 2.1 these components are depicted.

A SystemC implementation of the models is then instantiated and can simulate the system for a given amount of time. The result of the simulation is a runtime profile that allows the designer to evaluate the modelled system. The runtime

Figure 2.1: ARTS components

profile includes processor utilization, task response times and possible deadline misses, as well as memory-, communication-, and power-usage profiles. In the following sections the ingredients of ARTS are introduced.

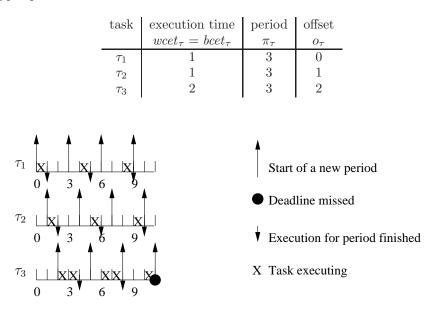

### 2.1 Application

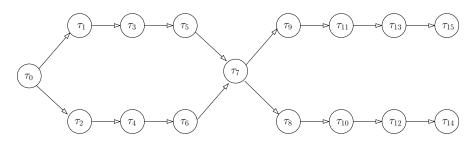

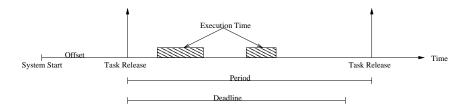

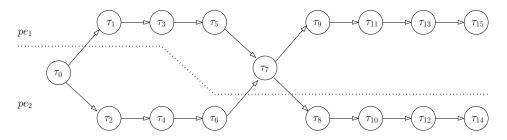

An application in ARTS is characterized by task graphs with a number of individual tasks and their data *dependencies*. Figure 2.2 shows a task graph for an example of a real-life application, an MP3 decoder. The tasks in the top row of the figure  $(\tau_1, \tau_3, \tau_5, \tau_9, \tau_{11}, \tau_{13} \text{ and } \tau_{15})$  operate on the right channel of a stereo signal, whereas the tasks in the bottom row  $(\tau_2, \tau_4, \tau_6, \tau_8, \tau_{10}, \tau_{12} \text{ and} \tau_{14})$  operate on the left channel. The tasks  $\tau_0$  and  $\tau_7$  are synchronization points from the MP3 decoder application. This example is examined and analyzed with ARTS in [48]. Each task is defined by the relative *deadline*, the *period*, an initial *offset* (or phase) and the *execution time*. Figure 2.3 gives an idea of what these terms mean on a timeline and each term is explained further here:

A Task dependency (the arrows in Figure 2.2) indicates that some task needs to finish its execution before another can start. That the task  $\tau_2$  is dependent on the task  $\tau_1$  (also written  $\tau_1 \prec \tau_2$ ) means that  $\tau_1$  must finish executing before  $\tau_2$  can start. Each arrow in the task graph corresponds to such a dependency. In the case of dependencies between tasks mapped to different processing elements, the dependency may be defined with a size. This size indicates how large a mes-

Figure 2.2: Task graph of an MP3 decoder

Figure 2.3: Timeline of a task from system start to its first period

sage is transferred as a result of the dependency. This transfer is done through the interconnects of the system; see more on interconnects in Section 2.2.2.

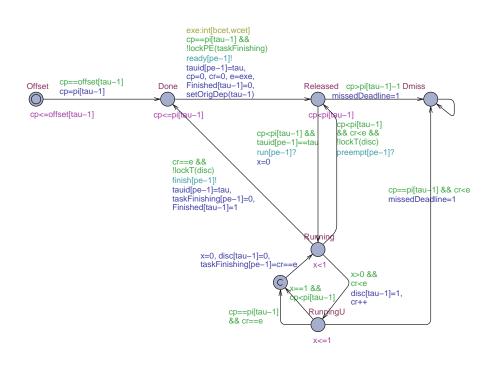

The relative deadline indicates how long after the release the task has to finish executing. If any deadline in any period of any task of the system is not met, the system is not schedulable.

The period of a task indicates how often the task is released, e.g. a period of 5 milliseconds for a task means that a new instance of the task is released every 5 milliseconds.

The offset (or phase) of a task defines when the first instance of the task is released relative to the start of the system, e.g. an offset of 3 milliseconds indicates that the first instance of the task is released 3 milliseconds after the start of the system.

The execution time of a task indicates how much processor time each instance of the task needs for execution, e.g. an execution time of 2 milliseconds means that the task needs 2 milliseconds of execution time each period. The execution time can be defined as an interval from best-case execution time (bcet) to worst-case execution time (wcet), meaning that each instance of the task needs an amount of execution time that is in this interval. Note that the execution time may depend on which processing element the task is mapped to. The tasks considered within this terminology are cyclic tasks. This means that for each period a new instance of the task is released, and the task requires execution time in each period.

## 2.2 Execution Platform

The execution platform is characterized by the processing elements, their interconnects and the overall architecture of the system. Processing elements provide processing power to execute the tasks of the system. These processing elements can be either dedicated components that only execute one specific task (e.g. an application-specific integrated circuit (ASIC)), more general components that can execute many different tasks (e.g. a general purpose processor (GPP)), or even components that can do a few specific tasks (e.g. a field-programmable gate array (FPGA)). Figure 2.4 shows an example of an execution platform con-

Figure 2.4: A platform example

sisting of the two processing elements  $pe_1$  and  $pe_2$ , with the real-time operating systems  $os_1$  and  $os_2$ , respectively. The two processing elements are connected via the shared bus  $b_1$ .

### 2.2.1 Processing elements

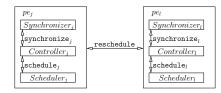

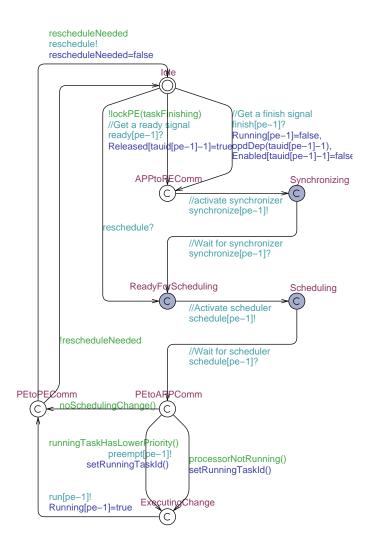

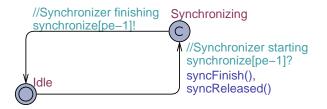

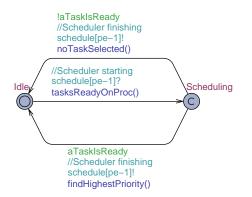

A processing element in ARTS is modelled by its real-time operating systems and has the following functionalities: a scheduler, a synchronizer and an allocator.

#### Scheduler

The scheduler will grant processing time to the tasks on the processing element. The scheduler can do this based on a priority-based scheduling principle, which means that whenever two or more tasks are ready to be executed on that processing element, the task with highest priority is selected for execution.

Scheduling can be either preemptive or non-preemptive.

*Preemptive scheduling* is when the scheduler can temporarily stop (preempt) currently executing tasks to allow more important (higher prioritized) tasks to execute instead. This implies that scheduling can occur whenever a task becomes ready or when a task finishes and others are waiting for execution.

For *non-preemptive scheduling*, when a task has started execution, it will continue its execution until it finishes, regardless of whether tasks with higher priority are released. The implication of non-preemptive scheduling is that scheduling can only occur when a task finishes and others are ready for execution or when a task becomes ready and no other tasks are waiting.

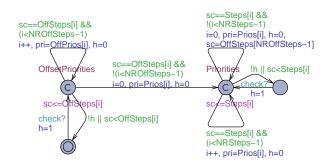

A scheduling principle is either static or dynamic.

Static scheduling principle: A processing element running a static scheduling principle bases each scheduling decision on a pre-determined prioritized list of all tasks; this list can be made at compile-time. An example of a static scheduling principle is rate-monotonic (RM) scheduling, for which tasks with shorter periods have higher priority.

*Dynamic scheduling principle:* A processing element using a dynamic scheduling principle bases each scheduling decision on properties of the current situation. An example of a dynamic scheduling principle is earliest-deadline-first (EDF) scheduling, where tasks closer to their deadline have higher priority.

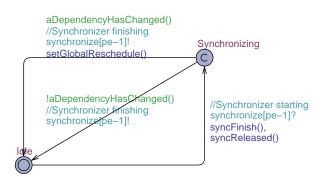

#### Synchronizer

The synchronizer manages task dependencies. When a task  $\tau$  is released, the synchronizer determines whether the task  $\tau$  depends on has already finished. When a task finishes, the synchronizer notifies any tasks that are dependent on it. Note that if dependent tasks are located on different processing elements, this notification must be communicated.

### Allocator

The allocator manages access to shared resources; this could be shared busses, memories, i/o devices, etc. The allocator can implement a principle such as priority ceiling in order to avoid blocking. Blocking occurs when a lower prioritized task blocks access to a processing element through a shared resource. In the priority ceiling protocol, a lower prioritized task will inherit the priority of higher prioritized tasks for which it holds access to a resource shared between the tasks.

Note that certain properties of tasks may depend on which of the processing elements it is mapped to. For example, a task may run faster or slower on different processing elements, and some tasks may not be able to execute on certain processing elements at all. Also, when including resource usage such as powerand memory-usage in the analysis, the individual power- and memory-footprints for each task may differ when executed on different processing elements.

### 2.2.2 Interconnects

Interconnects are links between different processing elements. These interconnects are defined in terms of their speed, i.e. how fast they can deliver messages. Dependencies of tasks mapped to different processing elements (inter-processor dependencies) may need to have a message transferred, and these messages are given in terms of their size. The time that it takes to deliver the message is then determined by the speed of the link and the size of the message, e.g. a message with the size 4 bits delivered on a link with the speed 2 bits/millisecond will take 2 milliseconds to deliver. An example of such a link is the bus  $b_1$  in Figure 2.4.

## 2.3 Mapping

Mapping of an application onto an execution platform is valuable to include in analysis. Through explicit mapping of different parts of the application onto the specific processing elements, inter-processor dependencies are identified and task-specific properties, ones that depend on which processing element they are mapped to, can be revealed. Inter-processor dependencies have the capability to introduce *multiprocessor anomalies*. A multiprocessor anomaly is a timing anomaly that occur when a local worst-case behavior does not give global worstcase behavior. Including the mapping in analysis allows for identification of such multiprocessor anomalies.

The mapping defines which tasks are to be executed on which processing elements. This mapping may have greater implications than one realizes. Some tasks may be able to be executed on different processing elements, but they may have different characteristics, e.g. required execution time on different processing elements. Also, mapping dependent tasks to different processing elements may require transfer of messages over links. Finally, some processing elements may run different real-time operating systems, and the system performance may vary extensively when a task is mapped to one processing element as opposed to another.

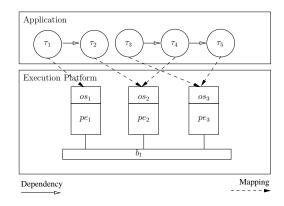

Figure 2.5 shows the MP3 decoder from Figure 2.2 mapped onto the platform on Figure 2.4, where the tasks above the dotted line are mapped to  $pe_1$  and the task below are mapped to  $pe_2$ . Note that the dependencies crossing the dotted line, i.e.  $\tau_0 \prec \tau_1$ ,  $\tau_6 \prec \tau_7$  and  $\tau_7 \prec \tau_8$  are inter-processor dependencies and may require data transfer over the bus  $b_1$  (see Figure 2.4). This is only one possible

Figure 2.5: Mapping of an MP3 decoder onto a platform

mapping, and the system may behave quite differently if even a slightly different mapping is used.

### 2.4 Schedulability

Schedulability of a system defined through the ARTS terminology as described here is to be understood as follows: A system is schedulable if no deadline for any task in any period is ever missed. For systems where tasks have execution times as intervals from beet to weet, this means that for every period, all execution times in that interval should not lead to missed deadlines anywhere in the system. Note that it is not enough to just examine weet as systems may contain multi-processor anomalies. In such cases, execution times that are not weet can trigger missed deadlines in the system.

## 2.5 Simulation

Once a system has been modelled through the aforementioned components, the system can be simulated. A simulation is conducted by letting the modelled components of the system run according to the properties specified. In the case of execution time as an interval, for each time the task is released, a random number between beet and weet is chosen. The duration of simulation is specified beforehand as a number of cycles. After this number of cycles the simulation is stopped and the results are available. These results can be valuable to a developer as he can try out setups of a system early in the design process. It gives an indication of how the system will act in the average case. But the simulation can give no guarantees about best- or worst-case performance.

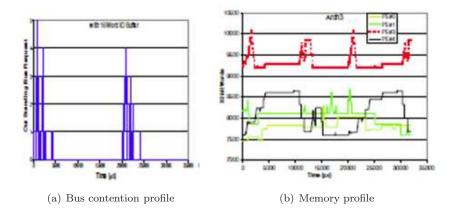

The result of simulating a system modelled in ARTS is a runtime profile. This profile can include processor utilization, task response times and possible deadline misses, as well as memory-, communication-, and power-usage profiles of the modelled system for the simulated duration. In Figure 2.6 examples of simulation output from ARTS are given with profiles for bus contention (2.6(a)) and memory (2.6(b)). These profiles are part of examples published in [49]. Since this is a simulation examining only certain (random) traces of the system's execution, there is no guarantee that best- or worst-case performance of the system has been targeted. Therefore, this is a good guide for average case system performance, but not for giving guarantees on system behavior.

## 2.6 Summary

In this chapter we have provided an overview of the underlying model of the multi-processor system-on-chip simulation framework ARTS. This framework allows developers to try out different setups of the systems they wish to design early in the design process. Although informal, the underlying model has a clear structure with which the different components of a system are modelled individually and systematically.

An ARTS model of a system consists of an application mapped onto an execution platform. An application is made up of task graphs, including the tasks'

Figure 2.6: Example of ARTS simulation results

dependencies, and an execution platform is modelled through the processing elements as well as their interconnects.

ARTS also provides a terminology that is useful when we look deeper into the model and give it semantics. A great advantage of the approach used in developing ARTS is that there has been a conscious decision to keep the simulation engine apart from the model. This makes the model much more suitable for establishing a formal semantics. It also keeps the model generic so there is a clear structure, which makes it easy to define new systems within the same framework.

**ARTS Concepts and Informal Model**

## Chapter 3

## The MoVES Language

The exploration in Chapter 1 identified that most of the approaches in the area of analysis of embedded systems seem to fall into categories, where either a) analysis is done for only one specific part of the system so global effects on local choices are not analyzed, or b) analysis is based on informal or sparse models that make it hard to comprehend the full system and that only allow for sporadic analysis (simulation), thereby cannot give guarantees.

This chapter aims at providing a formal model for embedded systems. The model should contain clear and precise characteristics of all components (such as tasks, processing elements, operating systems, etc.) of a system as well as the system's architecture (how different components communicate and how they are connected physically). This structure is chosen in order to be able to conduct *cross-layer analysis*, i.e. analysis of systems across several layers (e.g. application layer, execution-platform layer and mapping layer). Only through this type of analysis, problems originating at one level that results in issues at another level, can be thoroughly analyzed. As a basis, this model uses the informal model and terminology defined by ARTS, which was explained in Chapter 2. One could say that it is an attempt to give semantics to ARTS models.

The model, which is defined in Chapter 4, captures the characteristics of each

individual component in the system and their communication. Furthermore, it keeps a clear structure that reflects the architecture of the system. Before reaching a formal model in Chapter 3, we will establish a concrete syntax for a language, the *MoVES language*, that can be used to specify systems that can be captured by such a model.

This chapter is based on the work initiated in [12], where a grammar was given. Here we extend the work and provide examples to help the understanding of the use and structure of the language.

### 3.1 Concrete Syntax for the MoVES Language

In order to specify an embedded system and the problem to be analyzed, a syntax should be established. Although many of the approaches mentioned in Section 1.1 provide languages or at least a specification structure with which systems can be expressed, most of these fail to capture each component individually and keep a clear structure that reflects the system architecture.

This section serves as the establishment of a syntax for a language, the MoVES language, which allows designers to express systems, consisting of applications executing on execution platforms and their mapping, through their individual components. At the same time the structure reflects the physical architecture of the system. The terminology used to capture individual components is identified from ARTS in Chapter 2, and the structure follows that of ARTS models as well.

### 3.1.1 Grammar

In Figure 3.1(a), the grammar for the MoVES language is given. This language is intended to be used to specify embedded systems and their analysis problems. In general, an embedded system is specified through a specification of its application (app), the execution platform (plat), a mapping (map) of the application onto the execution platform, computational requirements (cr) showing effects of different mappings and finally, the verification/validation property (prop) that should be examined.

| system ::= app plat map cr prop                    | Application          | Mapping                            |  |

|----------------------------------------------------|----------------------|------------------------------------|--|

| $app$ ::= Application $task^+$ $dep$               | Task: T1             | T1 : P1                            |  |

| task ::= taskid per off                            | Period: 4            | T2 : P1                            |  |

| taskid ::= Task: tid                               | Offset: 0            | T3 : P2                            |  |

| per ::= Period: n                                  |                      | T4 : P2                            |  |

| off ::= Offset: n                                  | Task: T2             |                                    |  |

| $dep$ ::= Dependencies $dp^{*}$                    | Period: 6            | Creq                               |  |

| dp ::= tid -> tid : n                              | Offset: 0            | T1 @ P1                            |  |

| $plat$ ::= Platform $proc^+$ $bus$                 |                      | Bcet: 2                            |  |

| proc ::= Proc: pid Sch: sch                        | Task: T3             | Wcet: 2                            |  |

| sch ::= FP   RM   EDF                              | Period: 6            |                                    |  |

| bus ::= busid arbit speed                          | Offset: 0            | T2 @ P1                            |  |

| busid ::= Bus: bid                                 |                      | Bcet: 1                            |  |

| arbit ::= Arb: arb                                 | Task: T4             | Wcet: 1                            |  |

| arb ::= FIFO                                       | Period: 6            |                                    |  |

| speed ::= Speed: n                                 | Offset: 40           | T3 @ P1                            |  |

| <pre>map ::= Mapping mp +</pre>                    |                      | Bcet: 5                            |  |

| mp ::= tid : pid                                   | Dependencies         | Wcet: 5                            |  |

| $cr$ ::= Creq $tonp^+$                             | T2 -> T3 : 2         |                                    |  |

| tonp ::= tid @ pid bcet wcet                       |                      | T3 @ P2                            |  |

| bcet ::= Bcet: n                                   | Platform             | Bcet: 2                            |  |

| wcet ::= Wcet: n                                   | Proc: P1             | Wcet: 2                            |  |

| prop ::= Property p                                | Sch: RM              |                                    |  |

| <pre>p ::= Schedule?</pre>                         |                      | T4 @ P2                            |  |

| •                                                  | Proc: P2             | Bcet: 2                            |  |

|                                                    | Sch: RM              | Wcet: 3                            |  |

|                                                    |                      |                                    |  |

| $n \in \mathbb{N}$ , tid, pid and bid are strings, | Bus: B1              | Property                           |  |

| terminal symbols are in <b>Roman</b> ,             | Arb: FIFO            | Schedule?                          |  |

| non-terminals are in <i>italics</i>                | Speed: 2             |                                    |  |

|                                                    | T                    |                                    |  |

| (a) MoVES Grammar                                  | (b) Windmill control | (b) Windmill control specification |  |

Figure 3.1: MoVES grammar and example specification

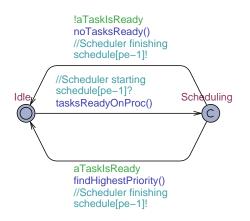

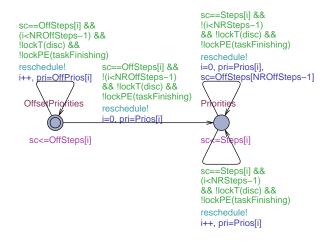

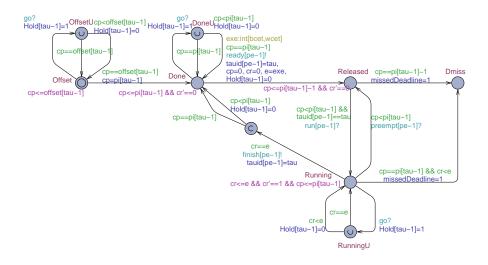

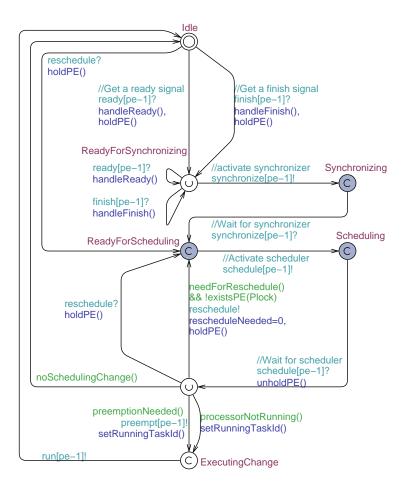

### 3.1.2 Example