#### Technical University of Denmark

#### Feedback Driven Annotation and Refactoring of Parallel Programs

Larsen, Per; Karlsson, Sven ; Madsen, Jan

Publication date: 2011

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Larsen, P., Karlsson, S., & Madsen, J. (2011). Feedback Driven Annotation and Refactoring of Parallel Programs. Kgs. Lyngby, Denmark: Technical University of Denmark (DTU). (IMM-PHD-2011; No. 251).

#### DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Feedback Driven Annotation and Refactoring of Parallel Programs

Per Larsen

Kongens Lyngby 2011 IMM-PHD-2011-251

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk

IMM-PHD: ISSN 0909-3192

# Summary

This thesis combines programmer knowledge and feedback to improve modeling and optimization of software. The research is motivated by two observations. First, there is a great need for automatic analysis of software for embedded systems – to expose and model parallelism inherent in programs. Second, some program properties are beyond reach of such analysis for theoretical and practical reasons – but can be described by programmers.

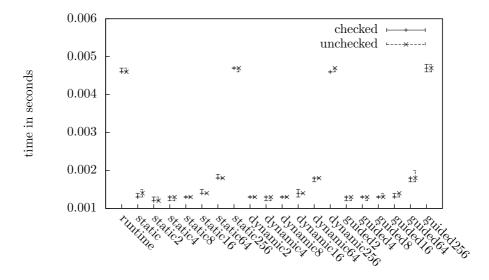

Three aspects are explored. The first is annotation of the source code. Two annotations are introduced. These allow more accurate modeling of parallelism and communication in embedded programs. Runtime checks are developed to ensure that annotations correctly describe observable program behavior. The performance impact of runtime checking is evaluated on several benchmark kernels and is negligible in all cases.

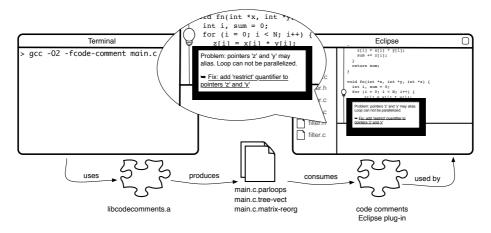

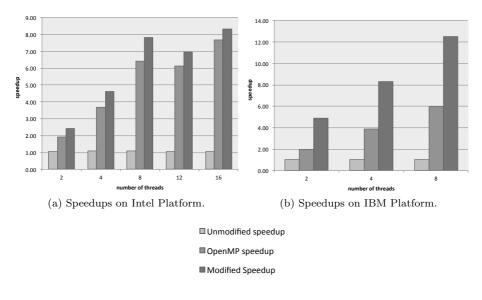

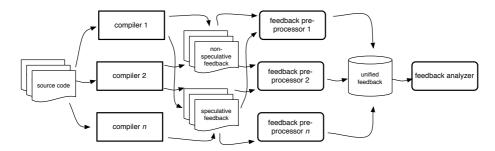

The second aspect is compilation feedback. Annotations are not effective unless programmers are told how and when they are beneficial. A prototype compilation feedback system was developed in collaboration with IBM Haifa Research Labs. It reports issues that prevent further analysis to the programmer. Performance evaluation shows that three programs performes significantly faster – up to 12.5x – after modification directed by the compilation feedback system.

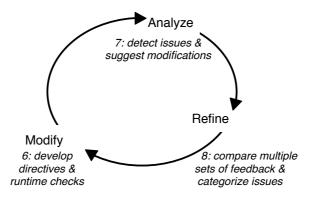

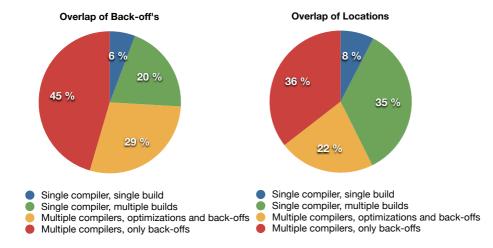

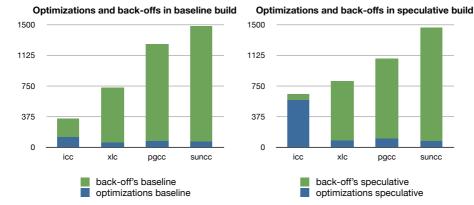

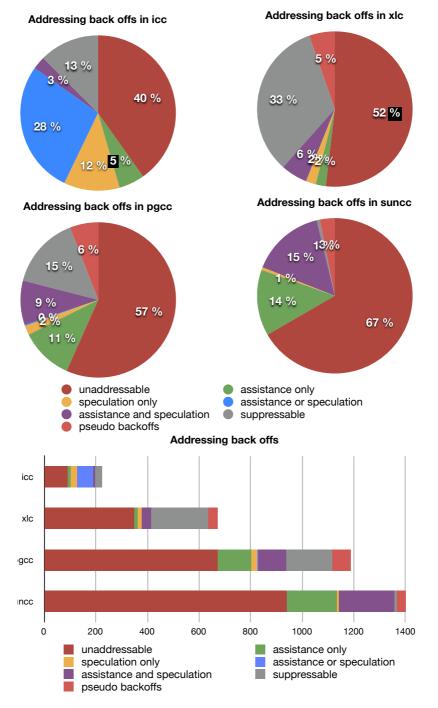

The last aspect is refinement of compilation feedback. Out of numerous issues reported, few are important to solve. Different compilers and compilation flags are used to estimate whether an issue can be resolved or not. On average, 43% of the issues reported can be categorized as potentially resolvable (27%) or unresolvable (15%).

ii

# Resumé

Denne afhandling kombinerer computer programmørens ekspertise med feedback for bedre at modellere og optimere programmel. Forskningen er motiveret af to observationer. For det første er der et stort behov for automatisk analyse af programmel til indlejrede systemer. Programanalyse er nødvendigt for at identificere og modellere parallelisme i indlejrede programmer. For det andet så er programanalyse utilstrækkeligt til at udlede visse egenskaber af teoretiske og rent praktiske grunde – men programmører kan ofte beskrive disse.

Tre aspekter af denne problemstilling udforskes. Det første er annotationer som indsættes i kildekoden. To annotationer introduceres og det vises at disse tillader en mere præcis modellering af parallelisme og afhængigheder i kildekoden. Der blev implementeret funktionalitet som under programafvikling sikrer at annotationerne beskriver programmets afhængigheder på korrekt vis. Denne funktionalitets indflydelse på køretiden blev evalueret på en håndfuld test-programmer. Eksperimenterne påviste ikke en forringelse i ydeevnen.

Det andet aspekt er feedback fra oversættere. Annotation er ineffektivt med mindre det oplyses hvor og hvornår programmøren kan bidrage. En prototype af et feedback system blev udviklet i samarbejde med IBM Haifa Research Labs. Systemet rapporterer problemer som forhindrer programanalyse. Eksperimenter viste at tre test-programmer afvikles væsentligt hurtigere – op til 12.5 gange – efter modifikation vha. systemets anvisninger.

Det tredje aspekt er raffinering af feedback. Et fåtal af de mange problemer som rapporteres er værd at løse. Forskellige oversættere og oversætterflag blev dernæst anvendt til at estimere om et problem kan afhjælpes eller ej. I gennemsnit blev 27% af problemerne kategoriseret som potentielt løsbare og 15% blev kategoriseret som uløselige.

iv

# Preface

This thesis was prepared at DTU Informatics, Technical University of Denmark in partial fulfillment of the requirements for acquiring the Ph.D. degree in engineering.

Programmers gain a high-level understanding of programs after working with their source codes for some time. It was studied how such programmer knowledge can be leveraged to model and optimize software for embedded and parallel systems.

The thesis is based on a collection of five research papers written during the period 2009–2011, and elsewhere published.

Lyngby, June 2011

Per Amser

Per Larsen

# Papers included in the Thesis

- [94] Per Larsen, Sven Karlsson, Jan Madsen. Identifying Inter-Task Communication in Shared Memory Programming Models. Proceedings of 5th International Workshop on OpenMP, 2009.

- [95] Per Larsen, Sven Karlsson and Jan Madsen. Expressing Inter-task Dependencies between Parallel Stencil Operations. Proceedings of 3rd Workshop on Programmability Issues for Heterogeneous Multicores, 2010.

- [97] Per Larsen, Razya Ladelsky, Sven Karlsson and Ayal Zaks. Compiler Driven Code Comments and Refactoring. Proceedings of 4th Workshop on Programmability Issues for Heterogeneous Multicores, 2011. Received Best Paper Award

- [98] Per Larsen, Razya Ladelsky, Jacob Lidman, Sally A. McKee, Sven Karlsson and Ayal Zaks. Automatic Loop Parallelization via Compiler Guided Refactoring. Technical Report, *IMM-Technical Report-2011-12*, DTU Informatics, Technical University of Denmark, 2011. http://www2.imm. dtu.dk/pubdb/views/publication\_details.php?id=6041

- [96] Per Larsen, Sven Karlsson and Jan Madsen. Expressing Coarse-grain Dependences among Tasks in Shared Memory Programs Special Issue of IEEE Transactions on Industrial Informatics, 2011. Accepted for publication

viii

# Acknowledgements

First of all, I thank my primary supervisor Sven Karlsson for his tireless efforts to make a scientist out of me. The task has certainly not been easy and I am deeply grateful for his unfailing confidence in me. His determination, patience and optimism were sources of encouragement and an invaluable help throughout the project.

I also thank my co-supervisor Jan Madsen. He encouraged me to apply for the DTU Informatics PhD programme. Throughout my studies, I have benefited greatly from Jan's comprehensive knowledge of embedded systems and his positive and pragmatic attitude towards any and all challenges.

In the spring of 2010, I applied for summer internship through HiPEAC, a European Network of Excellence. I spent the summer working as an intern at the IBM Haifa Research Labs in Israel. The collaboration with the compiler technologies group in Haifa provided a critical boost to my research. Hence, I am deeply indebted to IBM and HiPEAC for making this possible. A special thank to my hosts Ayal Zaks and Razya Ladelsky for their help and inspiration for the work on compilation feedback and, additionally, for making me feel truly welcome in Haifa. I also want to thank the good friends I made during my stay including Vladimir Cakarevic, Lois Orosa, Waldemar Hummer and Mircea Namolaru.

Many persons at DTU Informatics have been of great assistance to me. I am truly grateful for their helpfulness. These include Karin Tunder, Dina Berenstein and Ulla Jensen among others. I also thank Michael R. Hansen for his careful advice early in this study.

I thank Xavier Martorell for hosting me during my stay at Universitat Politèchnica de Catalunya, Barcelona and for treating me to some magnificent Tapas. I also thank Per Stenström for encouraging me to submit my work to the fourth MultiProg workshop. Others who have been very helpful to me include Laust Nannestad-Brock, Mason Chang, Jacob Lidman and Sally A. McKee.

Before I entered the PhD programme, I had the pleasure of working at a small company in the heart of Copehhagen. I got a little real-world experience. I would like to thank Lars Mensal, Jacob Lildballe, Hans Steenberg and countless others for being great mentors, colleagues and friends.

Working hard is not worthwhile unless one can sometimes rest and relax in the company of good friends. I am grateful for the many good times I had in the company of Charlotte Vilhelmsen, Peter Sørensen, Mads Johnsen, Christian Rank, Michael R. Boesen, Stavros Passas, Aske Brekling, Pascal Schleuniger and many, many more than can be listed here. Thank you all.

Most of all I thank my parents Else Marie and Flemming, my brother, Bo, and my wonderful girlfriend, Britta, for their unconditional encouragement, love and support. I could not have done this without you. Thanks!

The research in this thesis has been partially supported by HiPEAC and Artist-Design, both European Union Networks of Excellence. It has also been partially supported by the SMECY project, a part of the ARTEMIS Joint Undertaking.

My years as a PhD student contained several unexpected turns of events. Leonard Cohen penned the words that best describe my current sentiment. They are taken from a song which means a lot to me, and incidentally, to my friends in Haifa and elsewhere. Cohen sings  $I \ did \ my \ best, \ it \ wasn't \ much.$

xi

### Contents

| Sτ | ımm                      | ary                               | i            |  |  |  |  |  |  |  |  |  |  |

|----|--------------------------|-----------------------------------|--------------|--|--|--|--|--|--|--|--|--|--|

| R  | esum                     | é                                 | iii          |  |  |  |  |  |  |  |  |  |  |

| Pı | refac                    | е                                 | $\mathbf{v}$ |  |  |  |  |  |  |  |  |  |  |

| Pa | pers                     | included in the Thesis            | vii          |  |  |  |  |  |  |  |  |  |  |

| A  | ckno                     | wledgements                       | ix           |  |  |  |  |  |  |  |  |  |  |

| 1  | Intr                     | oduction                          | 1            |  |  |  |  |  |  |  |  |  |  |

|    | 1.1                      | Embedded Systems Design           | 2            |  |  |  |  |  |  |  |  |  |  |

|    | 1.2                      | Annotations and Compiler Feedback | 4            |  |  |  |  |  |  |  |  |  |  |

|    | 1.3                      | Thesis Outline                    | 6            |  |  |  |  |  |  |  |  |  |  |

| 2  | Tec                      | hnical Background                 | 9            |  |  |  |  |  |  |  |  |  |  |

|    | 2.1                      | Computer Architecture             | 9            |  |  |  |  |  |  |  |  |  |  |

|    | 2.2                      | Programming Models                | 13           |  |  |  |  |  |  |  |  |  |  |

|    | 2.3                      | Program Analysis                  | 15           |  |  |  |  |  |  |  |  |  |  |

|    | 2.4                      | Program Optimization              | 19           |  |  |  |  |  |  |  |  |  |  |

| 3  | Exploiting Parallelism 2 |                                   |              |  |  |  |  |  |  |  |  |  |  |

|    | 3.1                      | Automatic Parallelization         | 21           |  |  |  |  |  |  |  |  |  |  |

|    | 3.2                      | Manual Parallelization            | 31           |  |  |  |  |  |  |  |  |  |  |

| 4  | Mo                       | deling Embedded Software          | 35           |  |  |  |  |  |  |  |  |  |  |

|    | 4.1                      | Embedded Systems                  | 35           |  |  |  |  |  |  |  |  |  |  |

|    | 4.2                      | Applications of Task Graphs       | 37           |  |  |  |  |  |  |  |  |  |  |

|    | 4.3                      | Task Graphs                       | 40           |  |  |  |  |  |  |  |  |  |  |

|   | $4.4 \\ 4.5$ | From Source Code to Task Graphs41Summary43 |

|---|--------------|--------------------------------------------|

| 5 | Mo           | tivation 45                                |

| Ŭ | 5.1          | The Importance of Feedback                 |

|   | 5.2          | The Need for Program Annotation            |

|   | 5.3          | Making Annotation Effective                |

| 6 | An           | notations for Task Graph Extraction 49     |

|   | 6.1          | Dependencies among Tasks 51                |

|   | 6.2          | Dependencies among Stencil Computations 61 |

|   | 6.3          | Related Work                               |

|   | 6.4          | Summary                                    |

| 7 | Gei          | nerating Compiler Feedback 87              |

|   | 7.1          | Exposing Compiler Problems 88              |

|   | 7.2          | Automatic Parallelization with gcc 90      |

|   | 7.3          | Interactive Compilation Feedback System    |

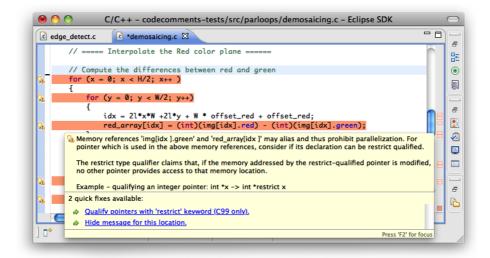

|   | 7.4          | Case Study: Demosaicing 95                 |

|   | 7.5          | Case Study: Edge Detection                 |

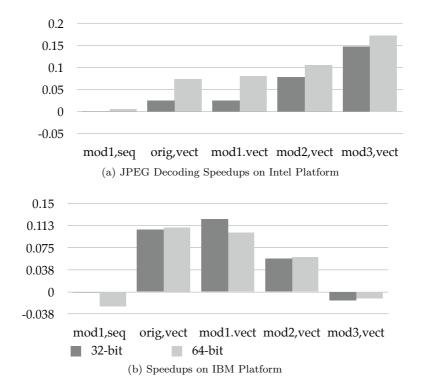

|   | 7.6          | Case Study: JPEG Decoding 101              |

|   | 7.7          | Experimental Results                       |

|   | 7.8          | Related Work                               |

|   | 7.9          | Summary                                    |

| 8 | Ref          | ining Compiler Feedback 117                |

|   | 8.1          | Approach                                   |

|   | 8.2          | Implementation                             |

|   | 8.3          | Experimental Results                       |

|   | 8.4          | Related Work                               |

|   | 8.5          | Summary                                    |

| 9 | Cor          | nclusions 143                              |

|   | 9.1          | Annotations for Task Graph Extraction      |

|   | 9.2          | Generating Compilation Feedback            |

|   | 9.3          | Refining Compiler Feedback                 |

|   | 9.4          | Outlook                                    |

# List of Figures

| 1.1        | Program fragment consisting of three tasks   |

|------------|----------------------------------------------|

| 2.1        | Parallel processing elements                 |

| 2.2        | Memory architectures 13                      |

| 2.3        | Approximation by program analysis            |

| 2.4        | Approximation of control-flow                |

| 4.1        | Y-chart                                      |

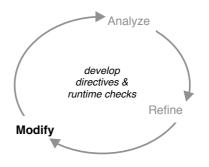

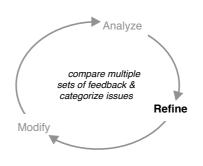

| 5.1        | Feedback loops                               |

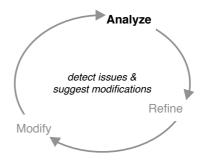

| 5.2        | Analysis feedback loop                       |

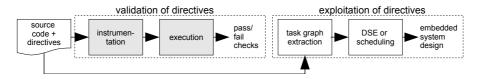

| 6.1        | Validation and exploitation of annotations   |

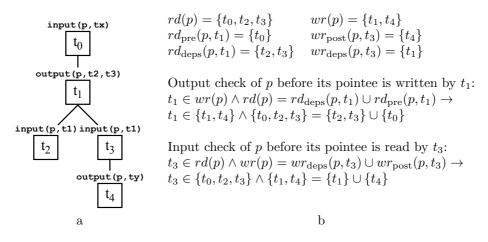

| 6.2        | Runtime check example                        |

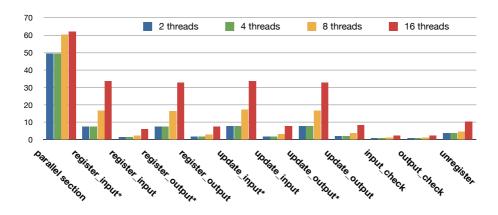

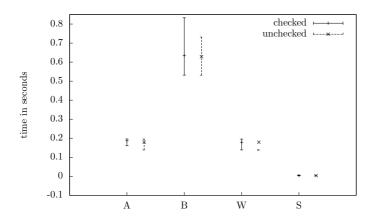

| 6.3        | Micro-benchmark results                      |

| 6.4        | Integer sort results                         |

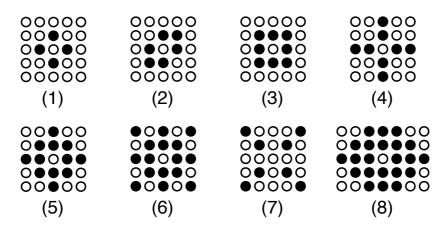

| 6.5        | Stencil patterns                             |

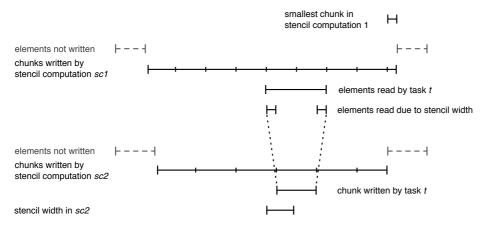

| 6.6        | Data sharing between stencil computations    |

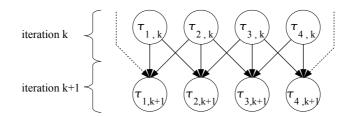

| 6.7        | Over-approximated dependencies in task graph |

| 6.8        | Inserting runtime checks                     |

| 6.9        | Heat diffusion results                       |

| 6.10       | Demosaicing results                          |

| 6.11       | Susan edge detection results   82            |

|            | Susan corner detection results   83          |

| 7.1        | Compilation feedback system                  |

| 7.1<br>7.2 |                                              |

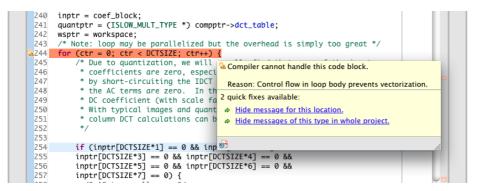

|            | Screenshot showing feedback on aliasing      |

| 7.3        | Screenshot showing feedback on control-flow  |

| 7.4                                     | Screenshot showing feedback on vector data type 108                     |

|-----------------------------------------|-------------------------------------------------------------------------|

| 7.5                                     | Screenshot demonstrating macro expansion 108                            |

| 7.6                                     | Screenshot showing feedback on data reference 108                       |

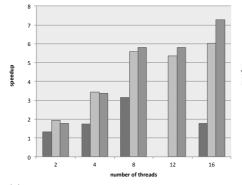

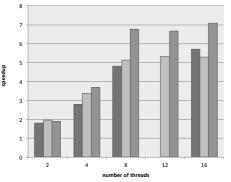

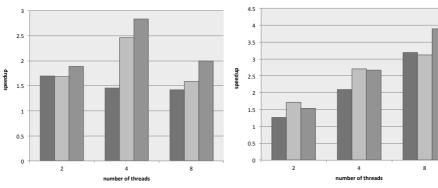

| 7.7                                     | Demosaicing speedups                                                    |

| 7.8                                     | Edge detection speedups                                                 |

| 7.9                                     | JPEG decoding speedups 113                                              |

|                                         |                                                                         |

|                                         |                                                                         |

| 8.1                                     | Refinement of compilation feedback                                      |

|                                         | Refinement of compilation feedback    122      Two coding styles    123 |

|                                         | *                                                                       |

| $\begin{array}{c} 8.2\\ 8.3\end{array}$ | Two coding styles                                                       |

| 8.2<br>8.3<br>8.4                       | Two coding styles    125      Overlap of back offs    126               |

### List of Tables

| 4.1  | Sizes of non-synthetic task graphs                         |

|------|------------------------------------------------------------|

| 6.1  | Auxiliary functions to explain runtime checks              |

| 6.2  | Characteristics of benchmark applications                  |

| 6.3  | Dependencies eliminated in heat diffusion                  |

| 6.4  | Dependencies eliminated in demosaicing                     |

| 6.5  | Dependencies eliminated in susan edges 82                  |

| 6.6  | Dependencies eliminated in susan corners                   |

| 7.1  | Loops parallelized by five compilers                       |

| 7.2  | Types of issues reported by compilation feedback system 94 |

| 7.3  | Characteristics of the benchmark inputs                    |

| 7.4  | Characteristics of benchmark systems                       |

| 8.1  | Compiler names and versions                                |

| 8.2  | Compiler options used in study 125                         |

| 8.3  | Co-location of back offs and other code comments           |

| 8.4  | Effect of speculation                                      |

| 8.5  | Assisting icc using xlc 131                                |

| 8.6  | Assisting icc using pgcc 131                               |

| 8.7  | Assisting icc using sunce                                  |

| 8.8  | Assisting xlc using icc 132                                |

| 8.9  | Assisting xlc using pgcc 132                               |

| 8.10 | Assisting xlc using suncc                                  |

| 8.11 | Assisting pgcc using icc                                   |

|      | Assisting pgcc using xlc 134                               |

|      | Assisting pgcc using sunce                                 |

| 8.14 | Assisting sunce using ice 135                              |

| 8.15 | Assisting sunce using pgcc     |  |  |  | • |  |  |  |  | • |  | 135 |

|------|--------------------------------|--|--|--|---|--|--|--|--|---|--|-----|

| 8.16 | Assisting suncc using pgcc     |  |  |  |   |  |  |  |  |   |  | 135 |

| 8.17 | Back offs by category          |  |  |  |   |  |  |  |  |   |  | 137 |

| 8.18 | Feedback locations by category |  |  |  |   |  |  |  |  |   |  | 138 |

### CHAPTER 1

### Introduction

Computers form an integral part of the developed world. We use laptops, smartphones, cameras and tablet computers every day. Some computers can go where man cannot – deep underwater, in space, nuclear power plants, munitions and autonomous vehicles, to mention a few.

In many cases, the computers are embedded into other devices. Such devices are quite different from personal computers, servers and super-computers. Devices that integrate computing capabilities, or *embedded systems*, account for the vast majority of computer systems.

The research in this thesis is motivated by challenges in analyzing and optimizing programs for embedded systems. Many challenges are primarily due to limitations in our ability to analyze program source codes. This thesis demonstrates that several concrete limitations can be mitigated by programmer inserted annotations and code refactoring. Compiler feedback is used to report to the programmer where and why program analysis encounters issues. Many issues are reported but not all can be resolved by changing the code. The possibility of resolving an issue via annotation and refactoring is estimated by combining compiler feedback from multiple builds of the same source code. This prioritizes the annotation and refactoring efforts.

This chapter has three parts. The first part characterizes embedded systems and their development. It also explains where and why the analysis of embedded systems rely on abstract models of programs. Finally, the difficulties in generating such models are outlined. The second part focuses on the programming aspects of embedded systems development. Most importantly, it explains the challenges of exposing parallelism to the underlying hardware. This part also describes techniques to *analyze* programs, techniques to *annotate* programs and their interaction. The final part motivates the work in this thesis and outlines its contents.

### 1.1 Embedded Systems Design

Embedded systems are often battery powered, are manufactured in high volume and must provide real-time performance. As a result, they are highly constrained in terms of cost, size and power consumption. To meet performance and powerconsumption constraints, critical parts may be realized as dedicated hardware blocks. The resulting systems often have a heterogeneous system architecture combining general-purpose units with dedicated hardware components. This complicates the system design [127]. Yet, design teams are expected to deliver increasingly complex designs within a short period of time. When combined, these circumstances create a need for automation of embedded systems design.

Typically, it is easier and less costly to make significant changes early rather than later in a project. It is therefore important to explore different choices early in the design process. Initially, the design team must determine what the embedded device will look like at the system level. For instance, the type and number of processing elements, memories and interconnects between these must be determined.

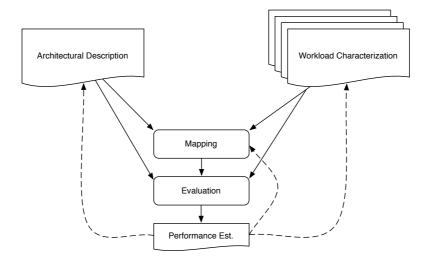

Devices having essentially the same function can be realized through a number of quite different system-level designs [144]. If two candidate designs can be evaluated and compared with respect to objectives such as power, cost and performance, a systematic search of the *design space* is feasible. This is called *design space exploration*, DSE. Early in the design process, simulators and hardware prototypes are typically unavailable. Alternatively, design teams can build analytical models of hardware components and relevant application workloads. Techniques using analytical models for evaluation are therefore important to identify corner cases early in the design process [68]. The *task graph* model is one, commonly used abstraction of application workloads.

#### 1.1.1 Task Graphs

Task graphs or variants thereof model coarse grain computation and communication in parallel programs. Task graphs are directed and acyclic. Sequentially executed instruction sequences are called *tasks* and form the nodes of a task graph. Communication and synchronization creates dependencies among tasks. These constrain the execution order among tasks. The dependence relation is represented by directed edges in the graph.

As previously mentioned, DSE tools often use task graphs to model embedded application workloads [143, 52, 168, 108, 58, 167]. This enables design space exploration to happen before simulators or hardware prototypes become available. Another area which relies on task graphs is scheduling and schedulability analysis [145, 48]. The accuracy of the analysis results, however, is only as good as permitted by the input. Hence, it is important that the task graphs reflect the application workloads as accurately as possible.

#### 1.1.2 Constructing task graphs

Programs are usually expressed in imperative programming languages such as C or C++. These languages partition programs into modules, functions and basic blocks that are connected by control-flow. The flow of data between program statements is implicit and must be found by analyzing the effects of statements. Task graphs, on the other hand, are partitioned into sequential sub-tasks connected by data dependencies. This makes it non-trivial to extract task graphs from source code.

**Manual approach** For very simple programs, it may be possible for the programmer to determine the tasks and their dependencies by hand [143]. Reasoning about data dependencies is known to be difficult and error prone. Therefore, a completely manual approach to task graph extraction is infeasible for all but the simplest programs.

**Execution based approaches** Instrumenting and executing the program is one alternative. This makes data dependencies occurring under a particular execution directly observable. There are two problems with this approach though. First, fine-grained instrumentation is required to find all dependencies. Such instrumentation slows down program performance by orders of magnitude. This means that profiling is only practical for small input sets. This is related to the

second problem. A single profiling run does not necessarily expose all data dependencies [155]. Hence, a task graph constructed via profiling may not capture all dependencies. Dependencies must not be overlooked because they constrain the execution order of tasks. Violating this ordering may lead to incorrect results.

**Program analysis approach** A third approach to task graph extraction relies on program analysis. Program analysis approximates the effect of each source statement. The dependencies between program tasks can be found by analyzing the source code. Compared to execution-based approaches, program analysis is typically faster and finds all dependencies. While this makes program analysis the most attractive option so far, it does have a significant drawback. To remain computable, the results of program analysis are necessarily *approximate* [118]. In case of dependence analysis, program analysis over-approximates the number of dependencies. Superfluous dependencies reduce the apparent amount of parallelism in a task graph. When given such graphs as input, scheduling and DSE tools have fewer degrees of freedom and are therefore prevented from considering all feasible solutions.

The approaches outlined above lead to task graphs that either *over-approximate* or *under-approximate* the dependencies between program parts. Missed dependencies lead to correctness issues while over-approximation may cause task graph tools to miss useful solutions. Techniques to analyze embedded systems via task graphs can therefore benefit from a more precise approach to extract task graphs from the source codes of programs. The next section explains techniques that enable programmers to assist program analyzers.

#### 1.2 Annotations and Compiler Feedback

Program analysis tools are built to analyze source code regardless of purpose or application domain. Programmers, on the other hand, typically spend most of their time working on relatively few programs. Programmers learn a great deal about programs this way. This knowledge is encoded in the choice of algorithms, data structures and symbol names.

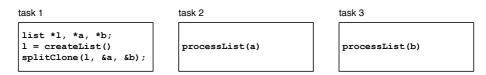

As an example, consider the three tasks shown in figure 1.1 on the facing page. A task graph extraction tool may not be able to determine if  $task \ 2$  and  $task \ 3$  are independent. Without additional information, the tool must consider  $task \ 2$  and  $task \ 3$  as potentially dependent. This adds a superfluous edge to the corresponding task graph. The programmer, on the other hand, can determine

Figure 1.1: Program fragment consisting of three tasks.

that tasks 2 and 3 are independent by interpreting symbol names and drawing on his or her understanding of the function calls involved. Program analysis on its own is therefore less potent than a combination of program analysis and programmer provided information. This makes *annotations* – declarative language constructs – attractive. In addition to annotations, code *refactoring* [62] can also make code more amenable to program analysis.

Annotations have traditionally been used by expert-programmers to allow a compiler or runtime system to perform additional optimization. This thesis explores source code annotation as a way to extract more precise task graphs from source code. Also, programmers traditionally use these annotations at their own peril. Erroneous use may cause the compiler to produce incorrect code without warning. The annotations proposed in this thesis are subject to runtime checks, which warn about incorrect use.

Annotation and refactoring take effort and must therefore be used judiciously. Ideally, annotation or refactoring is only performed:

- 1. when program analysis cannot determine an important program property; and

- 2. when annotation or refactoring helps program analysis determine said property.

Determining where programmers should modify programs was not studied in the context of task graph extraction. Rather, the focus was shifted to a related problem: finding parallelism in sequential code. The two problems are related as the analysis of data dependencies plays a central role in both instances. The change was necessary for practical reasons including the availability of tools.

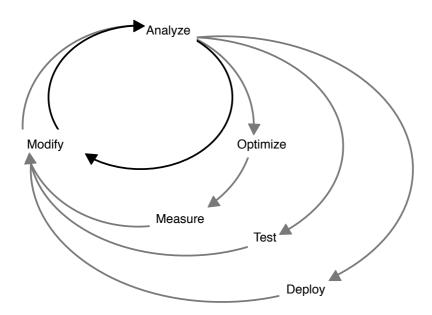

The first of the above points was addressed by extending a compiler to report issues that prevent automatic parallelization. The idea is that the programmer applies a potential workaround and recompiles until the issue is no longer reported. The high volume of issues reported creates a challenge of its own. Many of the reported issues cannot be resolved or do not improve program performance significantly.

To address the second point, the code was compiled several times in different contexts to estimate if annotation or refactoring is worthwhile. Compilers differ in their ability to automatically parallelize loops in sequential codes. Furthermore, the compilation options can greatly affect results of automatic parallelization. Multiple compilers and multiple compilation options were therefore used to compile the same code. This approach builds on two ideas. First, if one compiler reports failure to parallelize where another compiler is able to successfully optimize, the programmer may be able to resolve this issue. Similarly, if a compiler is able to parallelize a loop under potentially unsafe assumptions, then the programmer should determine whether the assumptions are safe to make or not. Together, the two techniques separate issues that may be resolved from issues that may waste programmer time.

Code can be made more amenable to analysis and optimization through improved interaction between programmers and program analyzers. The research in this thesis contributes to this important direction.

### 1.3 Thesis Outline

The following three chapters provide background information on areas related to the research in this thesis. Chapter 2 introduces the fundamentals of parallel computer architecture, programming abstractions and program optimization. Program analysis is also covered in more detail.

Chapter 3 concerns parallel programming. It covers the types of dependencies in programs and describes how to approximate these. Decomposition of sequential programs into tasks that may execute in parallel is also discussed. Finally, it covers manual and automatic ways to exploit parallelism.

Chapter 4 revisits embedded systems and models of embedded programs. It introduces task graphs and their role in the analysis of embedded systems. The last section of this chapter covers the correspondence between task graphs and programs parallelized with OpenMP – a parallel programming model.

Chapter 5 explains how the research in this thesis contributes to the state of the art and summarizes the major results presented herein.

Chapters 6 to 8 present the research upon which this thesis is based. Chapter 6 describes two annotations that transfer information from the programmer step to program analyzers. The impact of the directives are evaluated on benchmark kernels. Programmers need guidance on where and how to annotate. Hence, chapter 7 presents a system that provides the programmer with feedback from compiler analysis. This helps the programmer expose more parallelism to the compiler. The system is evaluated on three embedded codes. Finally, chapter 8 presents techniques to evaluate and filter the compilation feedback. This lowers the programmer effort required to address compilation feedback. The techniques are evaluated via feedback from compilation of an embedded benchmark suite. The final chapter summarizes the thesis and provides an outlook.

### Chapter 2

# **Technical Background**

This chapter serves as a foundation for the topics discussed in subsequent chapters. Each section covers a fundamental aspect of programming, namely: *what* we program, *how* we program and finally *where* and *how* we can improve the programs. The former two aspects are governed by the computer architecture and the programming model respectively. The latter aspects are addressed by program analysis and program optimization.

### 2.1 Computer Architecture

Computer architecture is concerned with the organization and design of hardware components. This includes processing elements, memories and the interconnects between these.

Until recently, processor designs were focused on sequential programs and high clock frequencies. In the period between 1978-2002, sequential performance increased approximately 50% annually. Since then, the annual growth in sequential performance has been significantly lower [125]. This slowdown can be attributed to the following observations, dubbed *walls*, in computer architecture:

- **Power wall** Power has become a limiting factor [66]. More transistors can be put on a chip than there is power to turn on.

- **Memory wall** Memory limits the performance of processor cores. Computation is fast but loads and stores are slow [165].

- **ILP wall** Finally, the gains from finding more parallelism at the instruction level are diminishing [125].

Moore's law [113], which predicts a doubling of transistors on a single chip every eighteen months, is still in effect [81]. However, the transistor budget is no longer spent on optimizing sequential performance. Rather, processor designers are integrating multiple, simpler and lower frequency cores on a single chip. While the move to multicore chips addresses the power wall, it also requires programmers to move from sequential to parallel programming models.

#### 2.1.1 Processing Elements

Flynn's taxonomy classifies computers according to the number of instruction and data streams that can be processed in parallel [61]. There are four possible combinations. Single instruction, single data stream, SISD describes a sequential computer. Single instruction, multiple data streams, SIMD, performs the same instruction on multiple data streams in parallel. Multiple instruction, multiple data streams, MIMD, is the most general class as the instruction and data streams are be fully independent. The final combination – multiple instruction, single data stream, MISD – is mostly of interest in fault tolerant processors and irrelevant to this discussion.

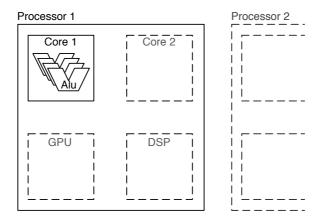

Figure 2.1 on the next page shows the relation between several types of *processing elements* – processors, processor cores and vector units respectively. At the outermost level, multiple processors can be combined to build a parallel system. If the processors are similar, the system is called a *symmetric multiprocessor*. Each processor can operate on a stream of instructions and data independent of other processors in the system. The system therefore supports MIMD parallelism.

Each individual processor may also support MIMD parallelism. Such processors duplicate the processor *core*, while sharing peripheral functionality such as IO and memory controllers. Such processors are called *multi-cores* and also support MIMD parallelism.

Figure 2.1: Processing elements supporting MIMD and SIMD parallelism.

Each general purpose processor core may also support SIMD parallelism via vector units. Scalar instructions operate on a single data element at a time. SIMD instructions operate on a short vector of data elements. The vector length is dependent on the size of each data element and are typically between 2 and 32 elements.

Notice that *Processor 1* in figure 2.1 contain two cores as well as two other types of processing elements. One is a *graphics processing unit*, GPU and the other is a *digital signal processor*, DSP. GPU's and DSP's are highly optimized for certain tasks but unsuitable for many others. Embedded processors typically have a heterogeneous configuration of processing elements.

#### 2.1.2 Memory Organization

Memory runs at a fraction of the processor speed. Hence, processors do not operate directly on the contents of main memory. Rather frequently used data is kept in a hierarchy of smaller and faster memories closer to the processor. This creates multiple copies of shared data. These copies must be consistent to give each processor a coherent view of the memory. The memory coherence problem must be addressed by computer architects, compiler writers and sometimes programmers.

**Caches, scratchpads and registers** A *cache* is a local memory that transparently stores data so requests to the same or a nearby memory address can

be sent to the processor faster. A coherence protocol can be used to maintain consistency of cached data. The exact type of memory consistency depends on the memory consistency model [1] implemented by the protocol. A *scratchpad* is another type of high-speed local memory. In contrast to caches, data is moved to and from scratchpads via data transfer instructions. They must therefore be managed by a runtime system or explicitly by the programmer. Finally, the memory closest to the processor – *registers* – is managed automatically by the compiler or manually by assembly programmers.

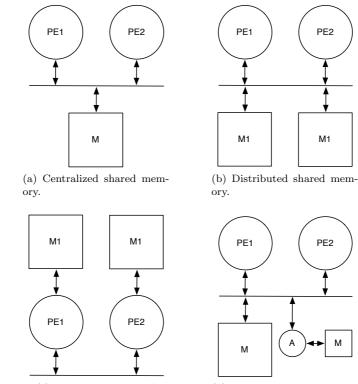

**Main memory** Multiple processing elements must be able to communicate among each other and with main memory. This raises the question whether the main memory should remain centralized or be distributed with the processing elements. MIMD systems is therefore further classified according to the memory architecture.

A system having a one or more shared memories is called a *shared memory multiprocessor*. There are two possible access policies when memory is distributed. With a private access policy, the memory can only be directly accessed by its associated processing element. This is known as *distributed memory*. With a shared access policy, a global address space makes the distributed memories accessible to all processing elements. This is called a *distributed shared memory*.

Processor/memory bandwidth is typically a limiting factor for the performance of shared memory multiprocessors. When memory is distributed with the processing elements, the memory bandwidth grows with the number of processing elements. Distribution of memory therefore allows systems with more processors.

The access time from a processor to a memory location depends on how close the processor is to the memory. Shared memory multiprocessors have uniform memory access times, UMA to main memory. With distributed memory, processors have non-uniform memory access times, NUMA. To mitigate NUMA effects, processors in a distributed-shared memory system have caches and a protocol to keep them coherent. These are known as cache coherent non-uniform memory access systems, ccNUMA.

Hybrid memory architectures are also possible. A system may consist of a set of homogeneous general purpose cores connected to one or more accelerators. The cores may access centralized shared memory whereas each accelerator may have its own memory. Figure 2.2 on the facing page shows four distinct memory architectures. One architecture is fully centralized, two are distributed and one is a hybrid between a centralized and a distributed architecture.

(c) Distributed memory.

(d) Hybrid between centralized and distributed memory.

Figure 2.2: Four different memory organizations.

### 2.2 Programming Models

The architecture of a parallel computer defines an interface between the software stack and the hardware that executes it. Similarly, a programming language and the libraries available define an interface between the programmer and the system being programmed.

The programming model is the abstraction or conceptualization of the underlying system that is presented to the programmer. The hardware/software interface presents a programming model for developers of hardware specific software such as of compilers, assemblers, operating systems and device drivers. The choice of programming language and libraries defines the programming model for application programmers. This section is about the latter kind. Programming models differ greatly in terms of programmer productivity, safety, availability, compatibility and execution speed. The interplay between these attributes is intricate. For instance, parallel programming models must carefully balance the opacity and visibility of the system architecture – non-essential details and idiosyncrasies should be hidden while features to enable the full computational power of the hardware must be exposed. The programming model also determines how program parts executing in parallel communicate and which synchronization constructs are available.

Programming models typically support one of the following memory abstractions – shared memory or distributed memory. The memory abstraction usually reflects the memory organization of the system but it is not necessarily so. For instance, a programming model can provide the programmer with the abstraction of a distributed memory on a shared memory multiprocessor. Software distributed shared memory middleware can provide the opposite: the abstraction of shared memory on a system with distributed memory [132].

Communication through shared memory has been compared to the use of a bulletin board [50]. Information is exchanged by posting data to shared locations which are agreed upon by the sender and the receiver.

In shared memory programming models, parallelism is introduced by running multiple threads inside a single process so threads can communicate directly using ordinary loads and stores. This is possible since threads share the address space of the parent process. Typically, a single *master* thread executes the sequential tasks in the program. When several tasks can execute in parallel, the master distributes them to a set of *worker* threads including itself. This is the fork step. The master then waits before all worker threads have run to completion before executing the next sequential task. This is the join step. This is known as *fork-join* or *master-worker* parallelism.

With distributed memory programming models, communication is commonly implemented as point-to-point transfers between two or more processing elements. This is known as *message passing*. It is conceptually similar to the exchange of letters that explicitly name the sender and receiver of the information [50]. Since there is no shared address space, all exchange of information and synchronization must happen via exchange of messages.

During execution, multiple instances of the same message passing program are run with different parameters that cause each process to operate on different data. This approach is known as *single program, multiple data*, SPMD. The exchange of messages is typically done via system call or by calling a library function. Thus, a single information exchange has much higher overhead than executing a pair of load and store instructions. The programmer can amortize the communication overhead by sending a few large messages rather than many smaller ones.

The shared memory programming model is a simple extension of the sequential programming model. It allows gradual parallelization of sequential programs and no special primitives are required to communicate among tasks. The message passing programming model requires the programmer to accept more responsibilities. In return, the programmer is given more flexibility to schedule the communication and synchronization among processes.

An important difference between programming models based on message passing and shared memory is that communication among tasks is *explicit* in the former and *implicit* in the latter. With message passing, communication happen via well known function calls that send or receive messages. With shared memory programs, communication happens when accessing shared memory. Since memory which is shared is typically indistinguishable from memory that is private to each thread, the accesses that transfer data between tasks are equally hard to identify.

### 2.3 Program Analysis

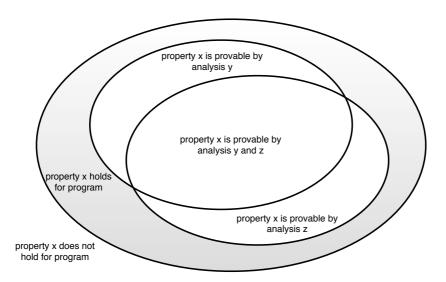

Program analysis refers to techniques that predict safe and computable approximations to the values or behaviors observable during program execution. This enables program optimization. Program analysis is also used to detect functional defects and security vulnerabilities. To remain computable, all variants of program analysis can only provide approximate answers [76, 118]. Correctness of compiled programs is more important than efficiency. When a precise answer cannot be produced, program analysis must therefore err on the safe side. The relation between a program property and the answers computed by program analysis is illustrated in figure 2.3 on the next page.

Figure 2.3 highlights another important point. Different techniques may be used to implement the same program analysis. The implementer must therefore balance the precision delivered by an approach with its computational complexity. Modest increases in precision often comes at the cost of significantly increased computational complexity [75]. The following section introduces data-flow analysis and design choices that affect its precision and speed.

Figure 2.3: Program analysis computes approximate answers regarding program properties. The level of precision and computational complexity varies with the type of analysis. A gray zone exists where all types of program analysis provides imprecise but conservatively correct answers.

#### 2.3.1 Data-Flow Analysis

Basic blocks are sequences of instructions that do not contain branches except for the last instruction in each block. A fundamental type of program analysis computes the data-flow between basic blocks. In a forward flow analysis, the *exit state* – the program state after exiting the basic block – is formulated as a function of the state at entry to the block. This is the transfer function. The *entry state* of a basic block is a function of the exit states of its predecessor blocks. A *join* operator is used to combine multiple exit states. This creates a pair of data-flow equations for each basic block *bb*.

$$entry_{bb} = join(\{exit_p : p \in predecessors(bb)\})$$

$$exit_{bb} = transfer_{bb}(entry_{bb})$$

The transfer function and join operation depend on the type of data-flow analysis. In a backward analysis, the transfer function and join operation translates from the exit to the entry state and the join – or meet – operator computes exit state from entry states of successor basic blocks.

An iterative algorithm is often used to solve the data-flow equations. In a forward analysis, the entry state of each basic block is approximated and the block itself is enqueued in a work list. The exit states are then computed via the transfer functions and the entry states are updated. The process continues iteratively until a *fix-point* is reached. This happens when additional iterations do not generate any new information and therefore drain the work list.

It must be guaranteed that a data-flow algorithm eventually converges on a fix-point solution. The domain of the entry and exit states must therefore be a lattice – i.e. a partially ordered set having an unique least upper bound and greatest lower bound for any two elements. Further, the transfer function and join operation must be monotonic with respect to the lattice [118].

A reaching definitions analysis is the textbook example of a forward analysis. It computes where definitions (assignments) of a variable are used. A *live variables* analysis is an example of a backward data-flow analysis. It detects assignments to variables that are never used. This allows dead assignments to be removed.

#### 2.3.2 Control-Flow Approximation

Data-flow analysis is built on a representation of the program control-flow. The control-flow may be represented by the *control-flow graph*, CFG, or the *loop hierarchy tree* which itself is based on the CFG. Basic blocks form the nodes in a CFG. Each basic block is connected to its successor and predecessor blocks by directed edges that represent the flow of control.

The CFG approximates the actual control-flow. Some edges represent controlflows which will never occur under execution. This happens because controlflow analysis does not analyze the conditional expressions controlling conditional branching. Figure 2.4 on the following page illustrates over-approximated control-flow edges.

#### 2.3.3 Precision of Program Analysis

An advanced compiler performs a hundred or more optimization passes on each file. Each optimization in turn may require one or more types of program

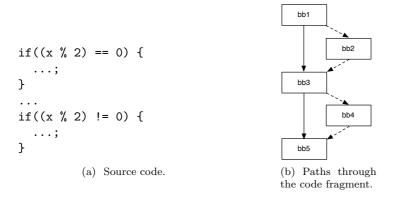

Figure 2.4: 2.4a Simple example to illustrate over-approximation of of controlflow. 2.4b Execution can only follow paths containing both dashed and solid arrows. Program analysis will report that all the shown paths possible.

analysis. To keep compilation times acceptable, a program analysis must balance precision and execution time. This section introduces aspects of this trade-off.

**Analysis scope** The analysis described in the previous section is typically run on basic blocks inside a single procedure. Such types of analysis are called *intra-procedural*. The alternative is to operate on the scope of a translation unit – a set of files being compiled together – or the entire program. In such cases, the scope of the analysis may cross procedure boundaries and is therefore *inter-procedural*.

**Analysis sensitivity** Another dimension is the *sensitivity* of a program analysis. An analysis is said to be *sensitive* or *insensitive* to a program property if it provides distinct or summarized information about the property. An analysis is *flow*-insensitive if it summarizes information across all points in the program. Similarly, an analysis is *context*-insensitive if it summarizes information about a procedure across all calls to that procedure. Finally, an analysis is *field*-insensitive if it does not distinguish between the individual fields of aggregate objects. The time required to perform inter-procedural, context and flow-sensitive analysis is often unacceptable. Summarizing program properties lowers the analysis time at the cost of precision.

**Analysis time** Another important dimension is the time at which the analysis happens. Analysis can take place at compile-time, link-time, run-time or post runtime. The analysis time interacts with the scope of the analysis. For instance, an analysis of the whole program cannot happen at compile time and must be deferred to link-time. If the program analysis happens at run-time it is said to be *dynamic* and otherwise it called *static*. Dynamic program analysis directly adds to the execution time of the program. Static approaches, on the other hand, can afford to spend more time on analysis since it does not add to the execution time. Also note that program analysis at compile or link-time happens before the program is executed in contrast to analysis at run-time and postruntime. The former two approaches are therefore unable to take advantage of information obtained during program execution. The latter two approaches can do so. Both the program source code and profiling provides information to program analysis. Additionally, the source code may contain programmer inserted annotations that assist the analysis.

## 2.4 Program Optimization

The primary goal of program optimization is to improve a programs use of computational resources while preserving its functionality. Some optimizations seek to *minimize* the use of resources such as memory, power, communication and execution time. Others seek to *maximize* the use of caches and the available processing elements. Finally, many optimizations – especially those transforming loops and inlining functions – have an important secondary effect: they create additional opportunities for other types of optimizations. Loop unrolling, for instance, lowers the control overhead in frequently executed loops by duplicating the loop body. This increases the basic block representing the loop body and in turn benefits the instruction scheduling optimization. Loop unrolling also illustrates the time-space tradeoff involved in program optimization. When applied successfully, loop unrolling *decreases* the execution time of the loop but it also *increases* the code size.

**Hotspots and Liveness** Temperature is used as an metaphor for the execution frequency of code. If an instruction or sequence of instructions are executed frequently, it is considered *hot*. Analogously, instructions which are infrequently executed are *cold*. Similarly, liveness is used to describe whether instructions are redundant or not. Instructions computing a result that is never used are said to be *dead*. Instructions that are unreachable in the control-flow of the program are also considered dead.

As a rule of thumb, programs follow the 90/10 rule [125]. For instance, 90% of the execution time may be spent executing just 10% of the code. These frequently executed parts are known as *hot spots*. Obviously, the optimization effort should target these to be effective. Hot spots can be found by profiling the program and re-optimizing the program based on the profiling data. Alternatively, hot spots can be estimated via program analysis. Basic blocks nested inside several loops, for instance, are likely to be hotter than basic blocks outside loops. Optimization can also happen at runtime and this allows optimization of instruction sequences as they become hot.

**Roles of compilers and programmers** Optimization can be done by the compiler, the programmer or both. While programming, the programmer can manually optimize the source code. Unfortunately, manual optimization tends to make the source code less readable. Rather than optimizing the source code directly, the programmer can insert annotations. These direct how the compiler should optimize the source code. Finally, optimization can be performed in a mostly transparent manner during compilation, link or runtime. Generally speaking, the automatic approaches do not obscure the source code and require only modest or no programmer effort. The likelihood that errors are introduced during optimization is therefore much smaller with automatic techniques.

The need for manual optimization is reduced but not removed by automatic optimizations. Automatic optimization relies on program analysis. Opportunities for optimization are necessarily missed since analysis results are approximate. In such situations, the programmer can either optimize by hand or annotate and refactor the source code to make it amenable to program analysis. Annotations are most attractive since they do not obscure the source code. Further – unlike manual optimization – it is not completely left to the programmer to preserve program correctness. Finally, annotated code is transformed automatically so errors are not introduced by the programmer at this step.

## Chapter 3

## **Exploiting Parallelism**

As mentioned in the previous chapter, multi-core processors are now commonplace. Software written for sequential processors need to be modified to to expose parallelism to multi-core processors. This chapter is concerned with the conversion of sequential programs into parallel ones. Programs contain parallelism at different levels of granularity and regularity. Some types of parallelism can be exploited automatically while others must be addressed by the programmer.

Manual and automatic approaches to exploit parallelism are covered by this chapter. It builds on the material introduced in the background chapter. Section 3.1 revisits program analysis and optimizations with a focus on automatic parallelization. Section 3.2 expands the background on programming models by introducing three concrete parallel programming models.

## **3.1** Automatic Parallelization

Automatic parallelization is attractive since the compiler or runtime system must shoulder the burden of finding and exploiting parallelism – rather than the programmer. Writing sequential code is hard in the first place. Programmers must address several concerns such as correctness, maintainability, flexibility, portability, readability and testability [111]. Parallel programming adds a new dimension to many of these concerns. This may explain the substantial research efforts to lower the burden of parallel programming.

With automatic parallelization, the programmer writes sequential code. A compiler or runtime system then analyzes the code to discover parallelism. This is in contrast to manual approaches where the parallel tasks are explicitly marked in the source code.

Programs can contain recognizable, implicit parallelism in one of two ways. First, programs may be constructed out of high-level primitives whose operations are known to be independent. A built-in function that sums a list is an example of such a primitive. Many existing codes, however, are not written this way. Second, many programs contain loops having no inter-iteration dependencies or which can be transformed to remove such dependencies. Many optimizing compilers are able to recognize and generate parallel code for these loops. This section covers program analysis and program optimizations that enable automatic loop parallelization and vectorization.

#### 3.1.1 Program Analysis for Automatic Parallelization

Before a loop can be automatically parallelized by the compiler, it must undergo several types of program analysis. These include alias analysis, induction variable analysis and dependence testing. The sophistication of each analysis step varies from one compiler to another which leads to varying strengths and weaknesses among different compilers.

After introducing dependencies, this section describes three types of program analysis. When combined, they allow automatic loop parallelization. These are dependence testing, alias analysis and induction variable analysis.

**Dependencies** The notion of dependence is central to both automatic and manual parallelization [14, 15]. Parallel execution causes instructions to be reordered. Dependencies among instructions prevent reordering. Programs contain two kinds of dependence: *data dependence* and *control dependence*.

An operation  $o_1$  is *control dependent* on operation  $o_2$  if the latter determines whether  $o_1$  should execute or not. Control dependencies originate from conditional statements and loops. Control dependence can be transformed into data dependence [123, 15]. This can increase the scope of data dependence analysis. Two operations are *data dependent* when they access the same storage location *and* at least one of the accesses is a write. Three types of data dependence exist.

- **Read-after-write** This dependence transfers data which typically prevents reordering. This is called a *true* or *flow* dependence. Special cases exists where reordering is still possible. For instance, true dependencies can be reordered when the sequence of updates forms a recurrence relation.

- **Write-after-read** No data is transferred among the operations. The operations cannot be reordered since the read could then receive the wrong value. The dependence can be removed by renaming the target of one of the accesses. This is also called an *anti* dependence.

- **Write-after-write** Like an anti-dependence, there is no transfer of data. Reordering of the operations is prevented unless the target of one of the accesses is renamed. This is also called an *output* dependence.

Anti and output-dependencies can be classified as *name* dependencies since they are arise from name (resource) conflicts rather than data transfer.

The above classification assumes that the storage locations accessed are internal to the program. When accessing variables that are visible outside the program, reordering is not legal. For instance, accesses to storage locations used for IO must be performed in program order.

**Data dependencies in loops** The execution time of many programs is concentrated in iterative computations such as loops. Parallelization of loops may therefore result in a significant performance increase over sequential execution. Being able to reorder the execution of loop iterations is a requirement for automatic loop parallelization. Dependencies between instructions in loops are therefore important.

Loops are different from straight line code in two respects. Loops execute the statements in their bodies repeatedly. Typically, they also access subscripted variables such as pointers and arrays. The subscripts used to access arrays are often linear functions of the loop counters. Such loops form a regular pattern of computation.

A statement can be nested inside n loops. A statement *instance* refers to the execution of the statement in a given loop iteration. Statement instances can be identified by a n-dimensional *iteration vector* where each loop corresponds to a dimension in the vector. For example, S(1,2) refers to the execution of a

statement S in a doubly nested loop during the first iteration of the outer loop and the second iteration of the inner loop.

Dependencies in loops can be divided into *intra-iteration* or *inter-iteration* dependencies. The former occur between statement instances with identical iteration vectors. The latter describe dependencies between statement instances with different iteration vectors.

Dependencies between two memory accesses in a loop may also be characterized by *distance* vector. Distance vectors must be lexicographically positive. For instance, the dependence vector between a read from an array arr[i,j,k] and a write arr[i+1,j,k-1] is (1,0,-1). The *direction vector* is an abstraction of the dependence vector, which only indicates the direction of the dependence in each dimension. The direction vector corresponding to the distance vector (1,0,-1) is (<,=,>).

Dependencies can be analyzed by a dependence tester during compilation or manually by the programmer [110]. They can also be analyzed via runtime layer [136, 140], hardware support [125], or a combination thereof [71, 138, 128, 161].

**Dependence testing** When array subscripts are affine functions of the loop iteration, dependence testing can be done by the compiler. Such a loop is shown in listing 3.1.

Listing 3.1: Example loop

The loop nest contains a statement with two memory accesses labeled 1 and 2 respectively. Let  $i_1$  and  $j_1$  be the values of variables i and j in array reference 1. Similarly, let  $i_2$  and  $j_2$  be the values of i and j in reference 2. Dependence testing of the loop is then equivalent to finding integer solutions to the following set of linear equalities and inequalities:

$$i_1 = i_2$$

$$j_1 = j_2 - k$$

This is also known as a *dependence problem*. Exact solutions to such problems can be found with integer linear programming [60]. Unfortunately, integer programming is NP-complete [37]. Many approximate or specialized dependence tests have therefore been developed [16, 25, 57, 133, 126, 105].

Compilers may take a divide-and-conquer approach to dependence testing. Specialized and inexpensive tests are applied first. If any data references are unresolved after these tests, a more general and expensive test is applied. Measurements have shown that this strategy is effective since simple cases are most common [67].

The per-iteration increment or decrement of the loop counter is called the *loop* stride. Dependence tests are often based on the assumption that loops have unit strides [67]. Loops with non-unit strides must therefore be *normalized* – at least during dependence testing.

Alias analysis Programming languages lets programmers assign symbol names to memory locations. The naming method allows multiple symbols to name – or *alias* – the same memory location. Given a pair of memory accesses, an alias analysis attempts to determine their aliasing relation. There are three possibilities: *no alias, must alias* and *may alias*. When the alias information cannot be determined, the alias analysis returns may alias, which is conservatively correct. Other types of program analysis rely on alias analysis to disambiguate symbol names [115]. For automatic parallelization, dependence testing must use alias analysis to determine if references to pointers and arrays may alias.

The aliasing problem is undecidable [134, 137] and alias information is necessarily approximate. As a result, many different types of alias analysis algorithms exist. They differ in their level of precision and computational complexity [75]. Compilers must be able to compile millions of lines of source code in reasonable time. Hence, they often use a fast and less accurate alias analysis by default [74]. **Induction variable analysis** Symbolic analysis seeks to express the value of variables as functions of program input and other – *reference* – variables. Induction variable analysis is such an analysis. Induction variable analysis for automatic loop parallelization [163, 130] – as well as many other optimizations such as strength reduction, loop nest transformations and bounds check elimination.

The purpose of induction variable analysis is to approximate the evolution of values inside loops. Given a set of constants  $c_0, c_1, \ldots, c_n$  and reference variables  $r_1, r_2, \ldots, r_n$ , the expression  $c_0 + c_1r_1 + c_2r_2 + \cdots + c_nr_n$  is affine. The array subscript expressions are often affine. Representing these values as affine expressions of reference variables is therefore of special interest. Induction variables are those whose values can be expressed as a function of the iteration count of the closest surrounding loop [7]. Such functions are called *closed form expressions*.

Consider the following loop: for (i = 0; i < N; i++) { j++; ... }. It contains inter-iteration flow and name dependencies on j. The dependencies can be removed by expressing j as a function of i (the reference variable). This can allow automatic parallelization. Replacing induction variables with their closed form expressions is called *induction variable substitution*. Induction variable analysis is a prerequisite to this transformation.

To parallelize a loop, the number of iterations must be *countable*. A loop is countable when the number of iterations can be expressed as i) a constant; ii) a loop invariant expression; or iii) a linear function of surrounding loop counters. For countable loops, the number of iterations can be determined by analyzing the loop exit conditions. To compute the evolution of some scalars, induction variable analysis also needs to compute the number of loop iterations. This eliminates the need for a separate analysis to compute loop iterations.

A reduction is a set of updates to a single location of the form  $var = var op \dots$ where op is a binary associative operation such as arithmetic addition and multiplication and var is a scalar or array. Like induction variables, reductions form a recurrence relations that must be transformed to allow parallelization. A symbolic analysis similar to that which recognizes induction variables is used to recognize reductions [9, 131].

Like alias analysis, induction variable analysis may be unable to properly analyze the code. For instance, when induction variable analysis happens, the code is already transformed by prior optimizations. This may jumble the code seen by induction variable analysis. An additional challenge when transforming induction variables is to preserve the effects of types and the behavior of overflows [130].

### 3.1.2 Code Transformations for Automatic Parallelization

Automatic parallelization relies on code transformation to increase performance and to facilitate further analysis.

Once program analysis has proved that parallelization of a loop nest is legal, the code can be transformed to increase performance. Parallelization can target multiple threads or a vector unit. Auto-parallelization normally refers to multithreaded code generation. The more precise term *threadization* is used by some. *Vectorization* refers to code generation for vector units. Auto-parallelization and vectorization of the same loop or loop nest is sometimes possible.

**Auto-parallelization** Compilers typically transform loops using fork-join style parallelism. The compiler must insert code to start multiple threads before the loop and additional code to join the threads after the loop. The compiler must also arrange for loop iterations to be distributed among threads. OpenMP already includes such functionality. Hence, many compilers reuse parts of the OpenMP runtime for auto-parallelization.

**Vectorization** Two types of vectorization are possible: loop vectorization [24, 56] and vectorization of basic blocks [99, 90]. Only the former type will be discussed here.

Loop vectorization exploits SIMD parallelism by executing multiple loop iterations in parallel. Vectorization has traditionally targeted innermost loops but outer loop vectorization is also possible [120]. The number of iterations executed in parallel is called the *vectorization factor*. It depends on the width of the vector units as well as the size of the data types being operated on. For instance, a 128-bit vector unit and a loop that operates on 32-bit data types yields a vectorization factor of 4. The higher the vectorization factor, the higher is the potential speedup over sequential execution.

Vector units execute specialized vector instructions. Several loop transformations are necessary before vector instructions can be generated. Vector instructions are subject to memory alignment constraints. Accessing data not aligned on a natural vector boundary is either prohibited or carries a performance penalty. Alignment issues can be handled by special instructions to reorder or shuffle data once it has been loaded but degrades performance. Instead, alignment can be analyzed statically or dynamically and loop peeling can remove unaligned loads from the loop to be vectorized [100]. Vector loads and stores must also access consecutive, vector-sized storage locations. However, loops that operate on images or complex numbers often lead to strided access patterns. This must be addressed via platform specific instructions for data manipulation – i.e. packing and unpacking – or additional loop transformations [119].

Two additional loop transformations are applied before vector instructions can be generated for the loop. These are *strip mining* and *loop distribution* [88]. Strip mining transforms a single loop into two nested loops. The inner loop iterates over *strips* whose length equals the vectorization factor. Loop distribution splits the body of the newly created inner loop into several simpler loops so each corresponds to a single vector operation.

**Facilitating transformations** Control-flow in loops can prevent automatic parallelization and vectorization. Dependence tests can only analyze a limited class of loops with control-flow. Furthermore, loop vectorization requires that the flow of control does not diverge between loop iterations executed in parallel.

If-conversion transforms control dependence into data dependence [123]. It removes conditional branches and propagates the conditions to the successor basic blocks. In the successor blocks, assignment statements are changed to conditional assignment statements using the propagated condition. Finally, controlflow is removed by merging the affected basic blocks. Loop unswitching [115] is a related transformation. It hoists loop-invariant branches out of a loop body and replicates each execution path as an independent loop in each branch. This increases the code size but decreases the instructions executed and facilitates parallelization.

Loop normalization was mentioned in the previous section. It changes loop bounds, strides and expressions involving the loop counter so that the loop counter counts from 0 (or 1, depending on the language) in steps of one [88]. This simplifies dependence testing since it does not have to account for variations in loop bounds and strides.

The *inline expansion* or *function inlining* [115] transformation replaces a function call with the body of the callee. It lowers the overhead associated with a function call. It removes function call and return instructions as well as function prologues and epilogues. Inline expansion also enables the caller and callee to be analyzed as a single entity. This is important to allow parallelization of loop bodies containing function calls. When a dependence tester encounters a function call in a loop body, it will assume that inter-iteration dependencies are possible since the function call can have side-effects. Functions that are known to have no side effects - pure functions - do not prevent parallelization. With inline expansion, the function body rather than the function call becomes visible during dependence testing. It can therefore analyze the code as if there had been no function call.

The above mentioned transformation enable dependence testing. If dependencies are identified, additional loop transformations can in sometimes remove these. These transformations include loop reversal, skewing and peeling [122, 115, 88].

**Profitability** Auto-parallelization and vectorization adds additional computation to programs. The overhead sometimes outweighs gains from parallel execution. Hence, these optimizations are not guaranteed to be profitable. Compilers may therefore refrain from optimizing even when doing so is legal. For auto-parallelization, the overhead originates from forking and joining threads and from distributing work among threads which may require synchronization. For vectorization, if-conversion, loop transformations and vector instructions to rearrange unaligned data also create additional computation.

Compilers use a *cost model* to estimate if an optimization is profitable. Some cost models are static and work by analyzing the code at compile time and making informed guesses. Static cost modeling can benefit from program profiling information. Cost models can also be dynamic. With a dynamic cost model, the compiler may generate a sequential and a parallel version of a loop for instance. This is called loop versioning. A runtime check selects a loop version during execution. The runtime checks may analyze iteration counts, aliasing, alignment and features of the processing elements. If the time to evaluate the dynamic cost model outweighs the benefits of parallelization, performance is degraded nevertheless. As with other types of program analysis, programmers can supply information about the profitability of an optimization. The following section shows how programmers can transfer information to program analyzers.

#### 3.1.3 Annotations and Compiler Options