Technical University of Denmark

### Support for Programming Models in Network-on-Chip-based Many-core Systems

Rasmussen, Morten Sleth; Sparsø, Jens; Karlsson, Sven ; Madsen, Jan

Publication date: 2010

Document Version Publisher's PDF, also known as Version of record

#### Link back to DTU Orbit

Citation (APA):

Rasmussen, M. S., Sparsø, J., Karlsson, S., & Madsen, J. (2010). Support for Programming Models in Networkon-Chip-based Many-core Systems. Kgs. Lyngby, Denmark: Technical University of Denmark (DTU). (IMM-PHD-2010-235).

### DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

## Support for Programming Models in Network-on-Chip-based Many-core Systems

Morten Sleth Rasmussen

Kongens Lyngby 2010 IMM-PHD-2010-235 Technical University of Denmark DTU Informatics Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk www.imm.dtu.dk

IMM-PHD: ISSN 0909-3192

## Abstract

This thesis addresses aspects of support for programming models in Networkon-Chip-based many-core architectures. The main focus is to consider architectural support for a plethora of programming models in a single system. The thesis has three main parts. The first part considers parallelization and scalability in an image processing application with the aim of providing insight into parallel programming issues. The second part proposes and presents the tile-based Clupea many-core architecture, which has the objective of providing configurable support for programming models to allow different programming models to be supported by a single architecture. The architecture features a specialized network interface processor which allows extensive configurability of the memory system. Based on this architecture, a detailed implementation of the cache coherent shared memory programming model is presented. The third part considers modeling and evaluation of the Clupea architecture configured for support for cache coherent shared memory. An analytical model and the MC\_sim simulator, which provides detailed cycle-accurate simulation of many-core architectures, have been developed for the evaluation of the Clupea architecture. The evaluation shows that configurability causes a moderate increase of the application execution time. Considering the improved flexibility, this impact is considered acceptable as the architecture can potentially exploit application-specific optimizations and offers a valuable platform for comparing programming models.

i

ii

# Resume

Denne afhandling omhandler aspekter relateret til understøttelse af programmeringsmodeller i mange-kernede arkitekturer baseret op intra-chip netværk. Hovedfokus er overvejelser omkring arkitekturunderstøttelse for et stort antal programmeringsmodeller i et enkelt system. Afhandlingen har tre dele. Den første del omhandler parallelisering af en billedbehandlingsapplikation med formålet at opnå indsigt i udfordringer relateret til parallelprogrammering. Den anden del præsenterer den blok-baserede Clupea arkitektur, som giver mulighed for konfigurerbar understøttelse for programmeringsmodeller med henblik på understøttelse af flere programmeringsmodeller i en enkelt arkitektur. Arkitekturen er baseret på specialiserede netværkinterfaceprocessorer som tillader stor konfigurerbarhed i hukommelsessystemet. Baseret på denne arkitektur bliver en detaljeret implementation af programmeringsmodellen cache coherent delt hukommelse beskrevet. Den tredje del omhandler modellering og evaluering af Clupea arkitekturen konfigureret med understøttelse for cache coherent delt hukommelse. Til evalueringen af Clupea arkitekturen er der blevet udviklet en analytisk model og MC\_sim-simulatoren, som muliggør detaljeret simulation af mange-kernede arkitekturer. Evalueringen viser konfigurerbarhed medfører moderate forøgelser i applikationskøretid. Set i forhold den øgede fleksibilitet anses dette som acceptabelt da arkitekturen potentielt kan udnytte applikationsspecifikke optimeringer og udgør en vigtig referenceplatform til sammenligning af programmeringsmodeller.

iii

iv

# Preface

This thesis was prepared at DTU Informatics, at the Technical University of Denmark in partial fullfillment of the requirements for acquiring the Ph.D.-degree. The Ph.D.-project was supervised by Professor Jens Sparsø, Assistant Professor Sven Karlsson and Professor Jan Madsen.

Kgs. Lyngby, July 3rd, 2010.

Morten Sleth Rasmussen

v

vi

# Acknowledgements

Many people have supported me during this journey. I am grateful to them all.

vii

viii

# List of Figures

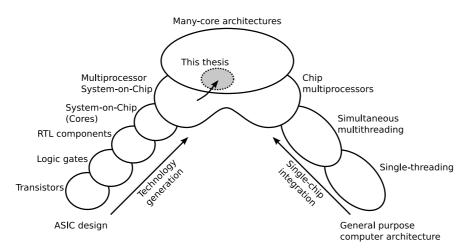

| 1.1         | Evolution of digital design.                                         | 2        |

|-------------|----------------------------------------------------------------------|----------|

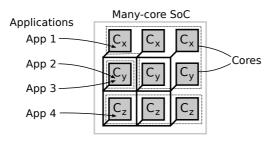

| 1.2         | Heterogeneous SoC platform                                           | 4        |

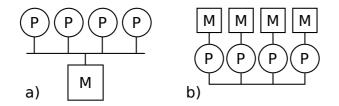

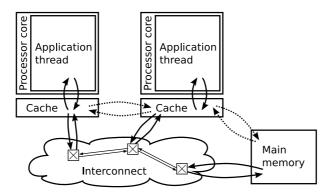

| 2.1         | Logical memory organization in multiprocessors                       | 11       |

| 2.2         | Physical memory organization in multiprocessors                      | 12       |

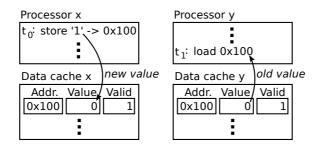

| 2.3         | The cache coherence issue                                            | 14       |

| 2.4         | Cache coherence protocol example                                     | 14       |

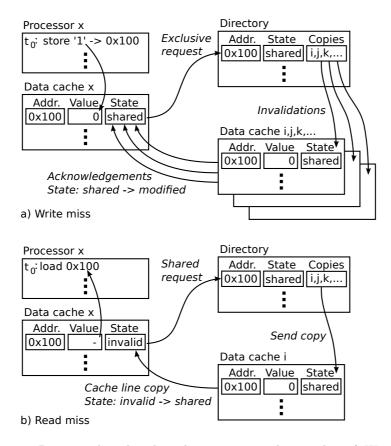

| 2.5         | Example of directory-based cache coherence protocol                  | 16       |

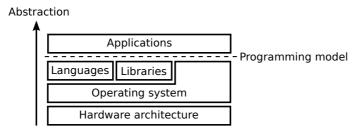

| 2.6         | Programming model abstraction layers                                 | 17       |

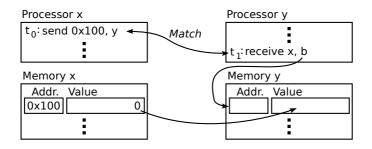

| 2.7         | The message passing programming model                                | 18       |

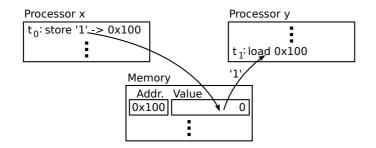

| 2.8         | The shared memory programming model                                  | 19       |

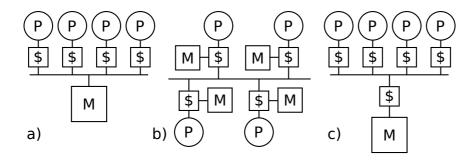

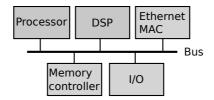

| 2.9         | SoC design example. Cores interconnected by an on-chip bus           | 20       |

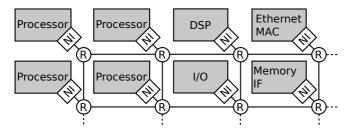

| 2.10        | NoC-based SoC design example.                                        | 22       |

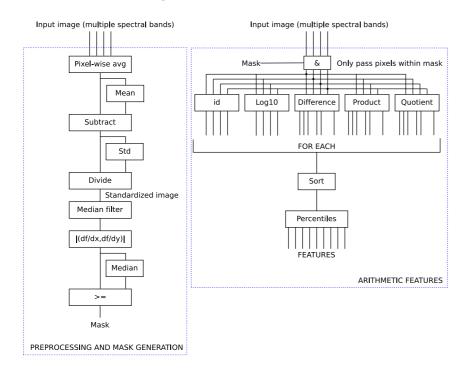

| 4.1         | Overview of the image processing application                         | 37       |

| 4.2         | Spectral image of fungi colonies.                                    | 37       |

| 4.3         | Overview of immediately available parallelism in the application.    | 39       |

| 4.4         | Execution times under non-uniform memory latency                     | 43       |

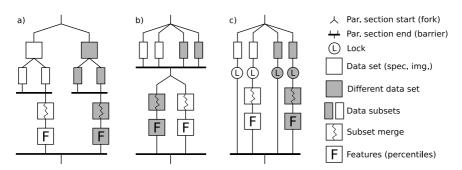

| 4.5         | OpenMP threading strategies                                          | 45       |

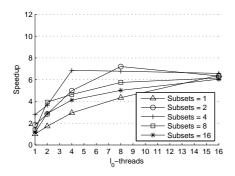

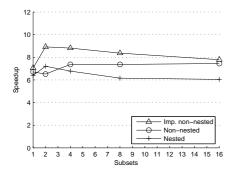

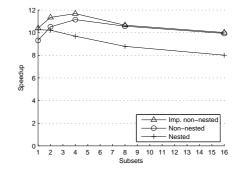

| 4.6         | Speedups for the nested version of feature set 2 with 16 processors. | 48       |

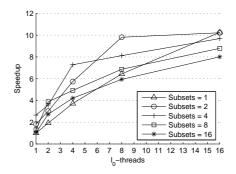

| 4.7         | Speedups for the nested version of feature set 3 with 16 processors. | 48       |

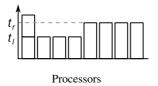

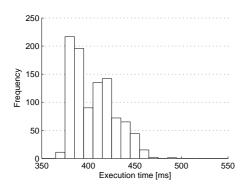

| 4.8         | Thread execution time histogram when running 3 threads               | 49       |

|             | incad execution time instogram when running 5 timeads                | 49       |

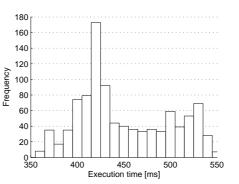

| 4.9         | Thread execution time histogram when running 9 threads               | 49<br>49 |

| 4.9<br>4.10 |                                                                      | 49       |

| -           | Thread execution time histogram when running 9 threads               | 49<br>50 |

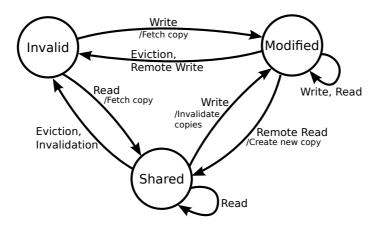

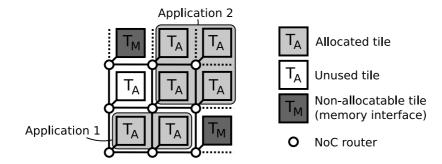

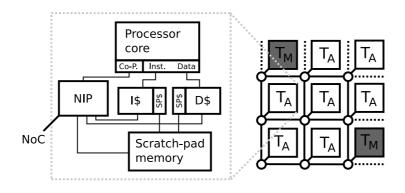

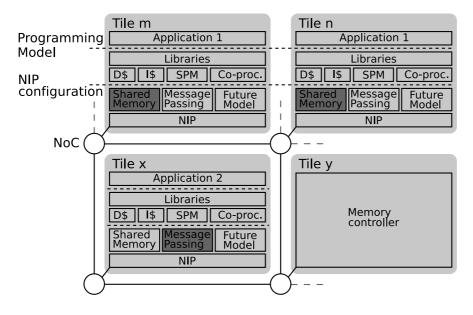

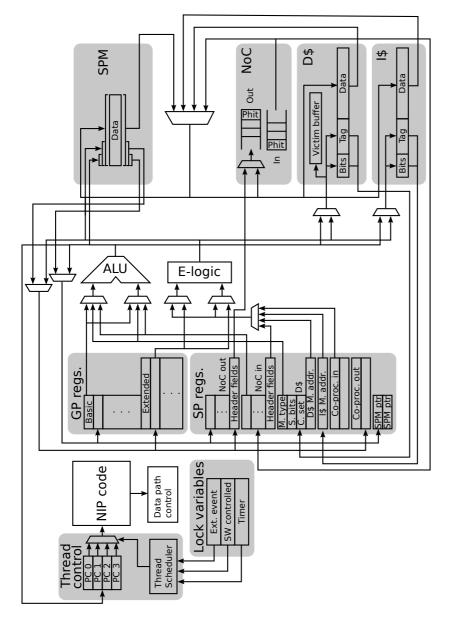

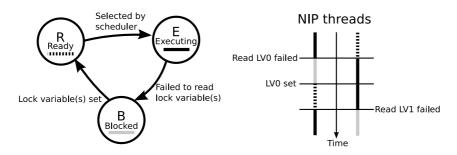

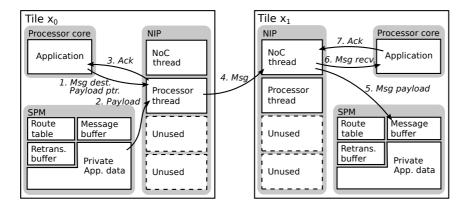

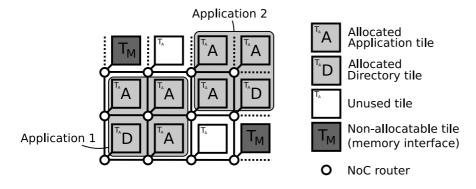

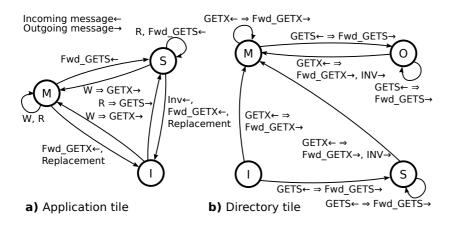

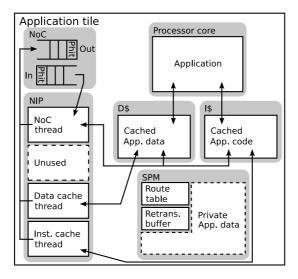

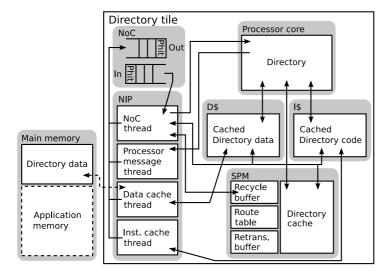

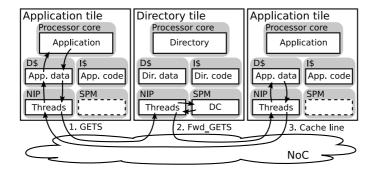

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11$ | Internal processor tile architecture.Configuring programming model support in the NIP.NIP architecture overview.NIP hardware threads.Message passing using the NIP.Tile allocation for cache coherent shared memory.Cache coherence protocol states.Application tile NIP threads and data structures.Directory tile threads and data structures.Cache miss example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58<br>59<br>63<br>66<br>70<br>73<br>75<br>76<br>79<br>82 |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

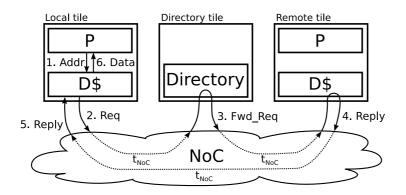

| 6.1                                                                    | Many-core memory system model overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86                                                       |

| 6.2                                                                    | Cache miss example for directory-based cache coherence protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90                                                       |

| 6.3                                                                    | Interconnect model overview.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92                                                       |

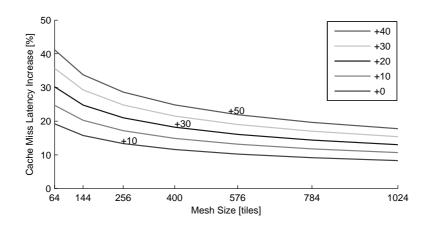

| 6.4                                                                    | Analytical cache miss latency estimates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94                                                       |

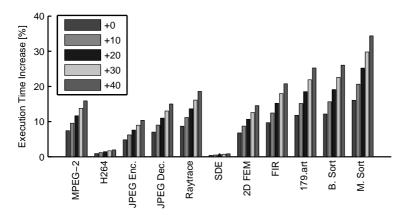

| 6.5                                                                    | Analytical estimates of application execution times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95                                                       |

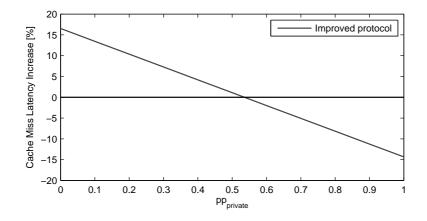

| 6.6                                                                    | Cache miss latencies for optimized cache coherence protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96                                                       |

| 6.7                                                                    | MC_sim component overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 98                                                       |

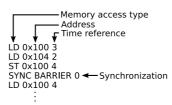

| 6.8                                                                    | Application memory reference trace example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98                                                       |

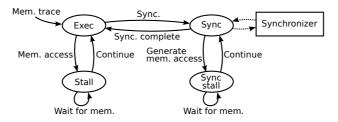

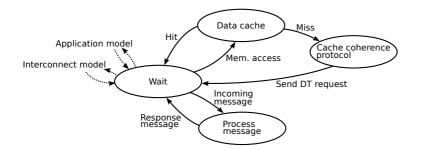

| 6.9                                                                    | $\mathrm{MC\_sim} \ \mathrm{processor} \ \mathrm{core} \ \mathrm{model.} \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99                                                       |

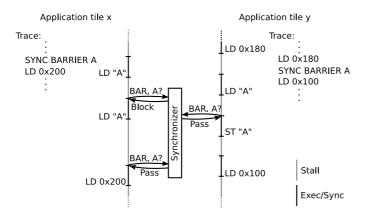

|                                                                        | Barrier synchronization example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 101                                                      |

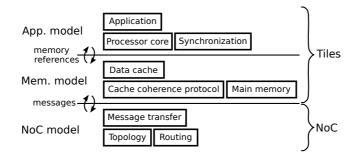

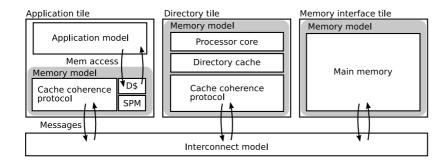

|                                                                        | Memory model overview. $\hdots \ldots \hdots \ldots \hdots \ldots \hdots \ldots \hdots \ldots \hdots \hdots\hdots \hd$ | 103                                                      |

|                                                                        | Local memory system model in each tile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103                                                      |

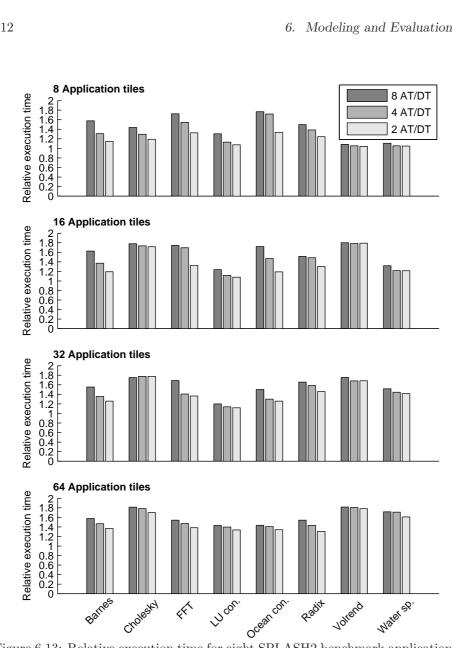

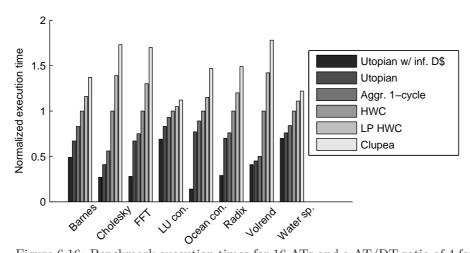

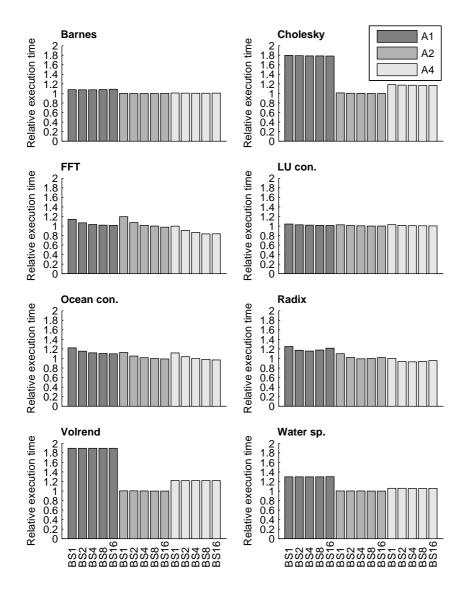

|                                                                        | Simulated Clupea benchmark execution times. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 112                                                      |

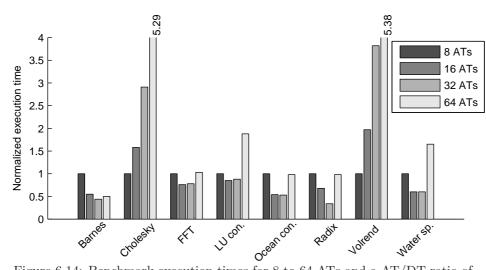

|                                                                        | HWC benchmark scalability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

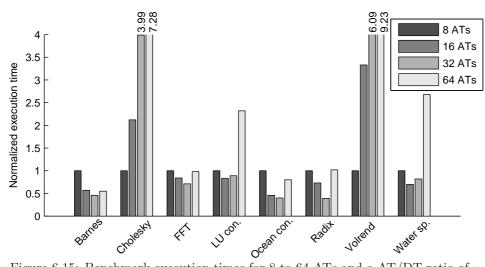

|                                                                        | Clupea benchmark scalability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 115                                                      |

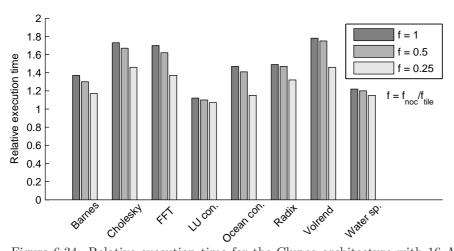

|                                                                        | Relative execution times for all timing models. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 116                                                      |

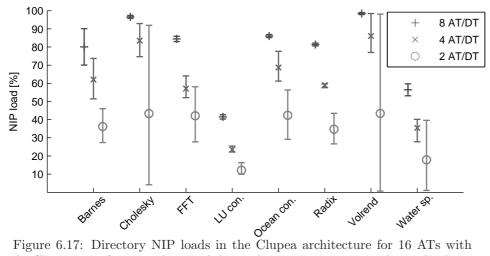

|                                                                        | Clupea directory tile NIP loads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 117                                                      |

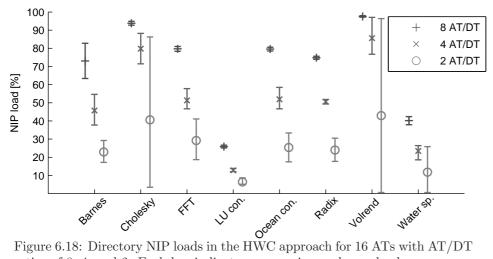

|                                                                        | Hardware directory tile NIP loads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 117                                                      |

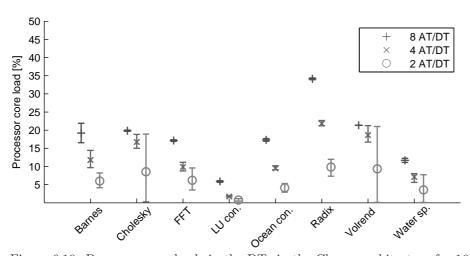

|                                                                        | Clupea directory tile processor core loads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 119                                                      |

|                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

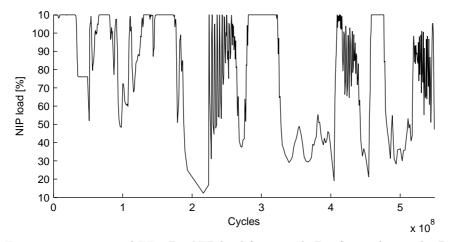

|                                                                        | Temporal FFT directory tile NIP load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

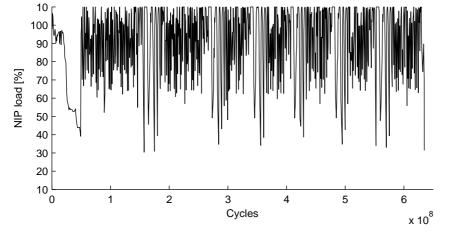

|                                                                        | Temporal Ocean con. directory tile NIP load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

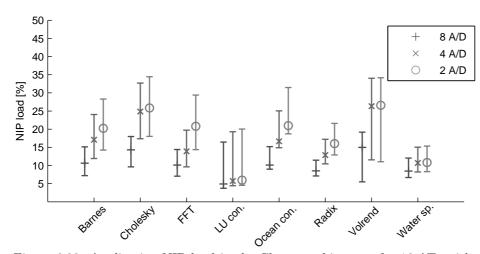

|                                                                        | Clupea application tile NIP load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

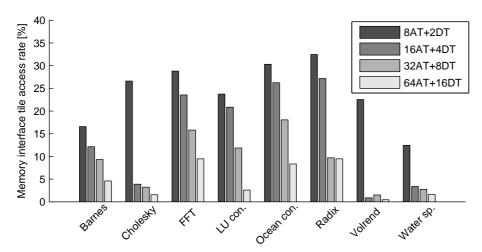

|                                                                        | Memory interface tile load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

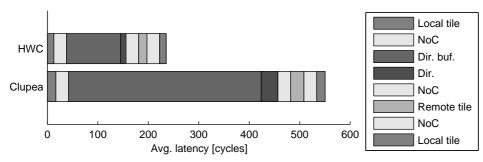

|                                                                        | Cache miss latency overview.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

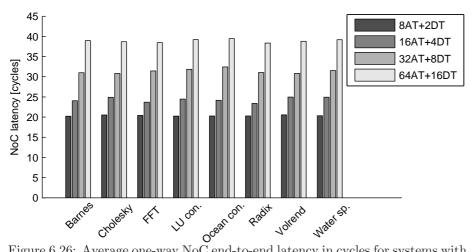

|                                                                        | Simulated NoC latencies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

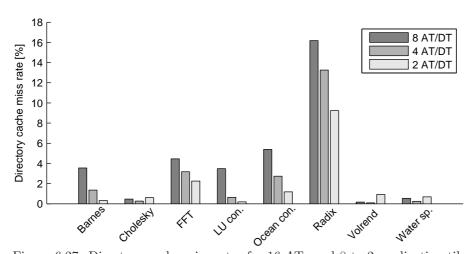

|                                                                        | Directory cache miss rates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |

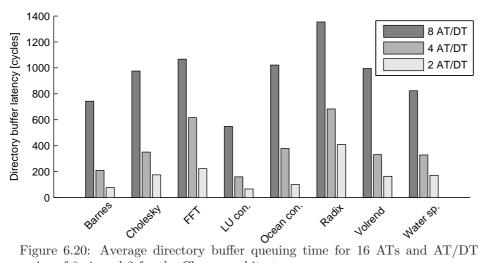

| 0.28                                                                   | Evaluation of different directory cache configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 127                                                      |

#### LIST OF FIGURES

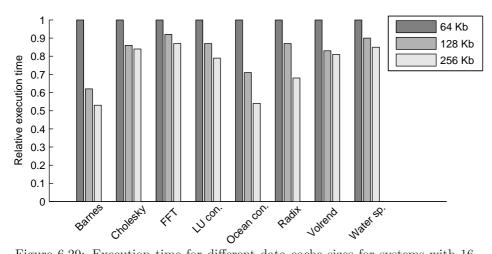

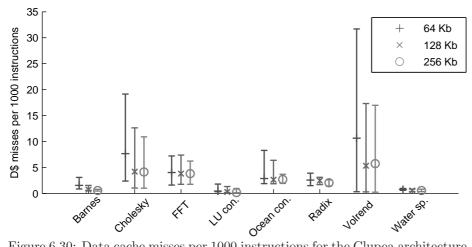

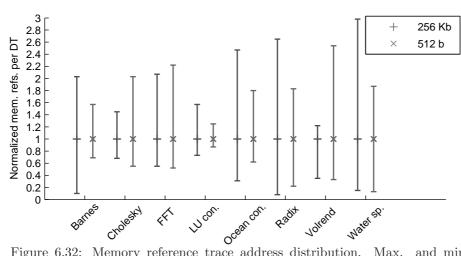

| 6.30 | Evaluation of data cache size.       129         Data cache misses per 1000 instructions.       129         Directore local helpsing       121 | ) |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|---|

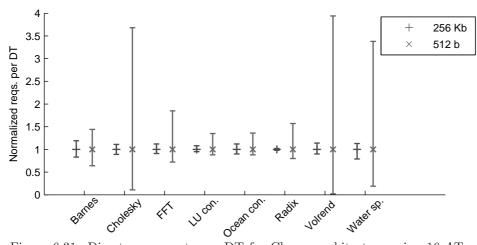

| 6.32 | Directory load balacing                                                                                                                        | 2 |

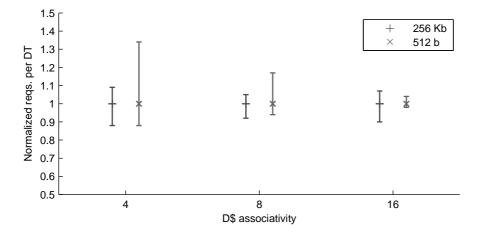

|      | Directory load balancing for increasing data cache associativity. 132<br>Increasing NoC latency                                                |   |

LIST OF FIGURES

# List of Tables

| 5.1 | NoC packet layout                 | 1 |

|-----|-----------------------------------|---|

| 6.1 | Analytical model parameters       | 3 |

| 6.2 | Clupea architecture configuration | 7 |

| 6.3 | MC_sim timing model parameters    | 9 |

| 6.4 | Benchmark applications            | 0 |

xiii

LIST OF TABLES

# Contents

| Intr | oduction                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.1  | Evolution of Digital System Design                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1.2  | Multiprocessor System-on-Chip Design Challenges                                                                                                                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1.3  | Contributions                                                                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |