Provided by Online Research Database In Technology

#### Technical University of Denmark

### Hardware Learning in Analogue VLSI Neural Networks

Lehmann, Torsten; Bruun, Erik

Publication date: 1995

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Lehmann, T., & Bruun, E. (1995). Hardware Learning in Analogue VLSI Neural Networks. Kgs. Lyngby, Denmark: Technical University of Denmark (DTU).

## DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Hardware Learning in Analogue VLSI Neural Networks

A thesis by **Torsten Lehmann**

In partial fulfillment of the requirements for the degree of Doctor of Philosophy

September 1994

Technical University of Denmark DK-2800 Lyngby, Denmark

Typeset using T<sub>E</sub>X (plain format ver. 3.1415N, PhDMac ver. 1.31 by TL)

Edition 1.03

Copyright © 1994 Torsten Lehmann All rights reserved

# Abstract

#### English

In this thesis we are concerned with the hardware implementation of learning algorithms for analogue VLSI artificial neural networks. Artificial neural networks (ANNs) are often successfully applied to problems for which no algorithmic solution exist, but can be described by examples. ANNs are fault tolerant and parallel of nature; analogue VLSI is a technology that can efficiently exploit these properties providing high performance systems. Analogue VLSI implementations of recall mode ANNs are maturing, but the equally important problem of implementing programming (or learning) hardware for these is still in its infancy.

We shall present the analogue VLSI implementation of two supervised, gradient descent learning algorithms for ANNs: the error back-propagation learning algorithm (BPL) for layered feed forward ANNs and the real-time recurrent learning algorithm (RTRL) for general recurrent networks. Both algorithms teach a cascadable analogue VLSI chip set for ANNs which we shall also describe. This chip set use simple capacitive weight storage with a digital RAM back-up memory. The BPL algorithm is implemented on-chip based on a novel bidirectional principle resulting in a very modest hardware increase compared to the recall mode system. The RTRL algorithm is implemented as add-on hardware to the recall mode system, using a compromise between computational speed and hardware consumption. The implementations of several algorithmic variations are also considered (eg. weight decay and momentum). Results from measurements on the fabricated chips are presented as well as measurements on a recall mode system.

We display the novel category of gradient descent like algorithms, non-linear gradient descent, which are better suited for hardware implementations than ordinary gradient descent; both in terms of accuracy and hardware consumption. Further, we argue that ANN ensembles should be used to improve performance of analogue neural systems. Also included are novel considerations on analogue computing accuracy, offset compensation, derivative computation, analogue memories, network topologies, process parameter dependency canceling, and learning in systems with RAM back-up, among other things.

We conclude that though the technology is promising for implementing learning algorithms much research is still needed; both at a algorithmic level and at a implementation level.

Abstract Page iv

#### Dansk

I denne afhandling skal vi beskæftige os med hardware implementeringer af indlæringsalgoritmer til analoge VLSI kunstige neurale netværk. Kunstige neurale netværk (artificial neural networks, ANNs) er ofte med held brugt på problemer for hvilke der ikke eksisterer nogen løsningsalgoritme, men som kan beskrives ved hjælp af eksempler. ANNs er af natur fejltolerante og parallelle; analog VLSI er en teknologi, som effektivt kan udnytte disse egenskaber til implementering af systemer med stor ydeevne. Analog VLSI implementeringer af fast-programerede ANNs er ved at modnes, men det ligeså vigtige problem at implementere programerings (eller indlærings) hardware til disse er stadig i sin spæde begyndelse.

Vi skal her præsentere analoge VLSI implementeringer af to overvågede, gradient nedstignings indlæringsalgoritmer til ANNs: "Error back-propagation" indlæringsalgoritmen (BPL) til lagdelte netværk uden tilbagekobling samt "real-time recurrent learning" algoritmen (RTRL) til generelle, tilbagekoblede netværk. Begge algoritmer oplærer et kaskadekoblet, analogt VLSI chipsæt til ANNs, som vi også skal beskrive. Dette chipsæt benytter et simpelt kapacitivt vægtlager med en digital RAM hukommelse til vægtopfriskning. BPL algoritmen er baseret på et nyt bidirektionelt princip og implementeres internt på ANN chipsættet ved brug af ganske lidt ekstra hardware. RTRL algoritmen implementeres med extern hardware og som et kompromis mellem beregningshastighed og hardware forbrug. Implementeringer af forskellige varianter af algoritmerne bliver også overvejet (fx. vægt henfald og moment). Resultater fra målinger på de fremstillede chips vil blive præsenteret, såvel som målinger på et system baseret på ANN chipsættet.

Vi fremviser den ny kategori af gradient nedstignings lignende algoritmer, ikkelineær gradient nedstigning, som er bedre egnet til hardware implementeringer end sædvanlig gradient nedstigning; både med hensyn til præcision og hardware forbrug. Endvidere påpeger vi at ANN "ensembles" bør benyttes for at forbedre ydeevnen af analoge neurale systemer. I teksten præsenteres også nye overvejelser angående, blandt andet, præcision af analoge beregnende enheder, offset kompensering, differentialkvotient beregning, analoge hukommelser, netværks topologier, udligning af proces-parameter afhængighed, og indlæring i systemer med RAM opfrisknings hukommelse.

Vi konkluderer at, selvom teknologien er lovende for implementering af indlæringsalgoritmer, er megen forskning stadig nødvendig; både på et algoritmemæssigt niveau samt på et implementeringsmæssigt niveau.

# **Preface**

The present thesis is a partial fulfillment of the requirements for the degree of Doctor of Philosophy (licentiatgraden, Philosophiae Doctor, Ph.D.). The work was carried out at the Electronics Institute, the Technical University of Denmark, and was funded on a scholarship from the Technical University of Denmark. Professor Erik Bruun of the Electronics Institute was supervisor.

I have tried to make this thesis a coherent presentation of hardware learning in analogue VLSI neural networks — though by no means exhaustive. This has made it necessary to include work that is not entirely my own and I will state it clearly whenever this is the case. In particular, my fellow Ph.D. student, John Lansner, was responsible for large parts of the work in implementation of neural networks. Thomas Kaulberg was responsible for the op-amps (and current conveyors) used on the chips. A Masters student of mine, Jesper Schultz, did much of the work on the sparse input synapse chip architecture. Finally, John Hertz, Benny Lautrup and Anders Krogh were responsible for the development of non-linear back-propagation. I have tried to refer other authors whenever possible; what is not referred (apart from well known matters) is, for most parts, my own work. Some people will undoubtedly find parts of the text provocative (eg. when I argue that one should refrain from using floating gate memories for synapse strengths) — please do not take offense, it is by no means a mark of disrespect of other peoples work; merely personal views (as well as a deliberate attempt to provoke which I think is sound for development in any field of research).

Regarding the *layout* of the thesis: Disgracefully (some would say) I have the habit of using parenthesis quite often. Note that often they act like subordinate clauses; their contents being important. Figure- and equation numbers, which are globally enumerated, carry chapter labels as superscripts for the ease of location (as figure  $37^4$  and  $(9^4)$ ). In most places references to other peoples work (as Sánchez-Sinencio and Lau [206]) are incomplete in the sense that only a few of the relevant references are displayed; references that cover material related to the text are usually preceded by "cf." or "se also". *Italics* font are used for emphasis and for concepts that are found in the index. I use "we" as as the personal pronoun throughout the thesis as I think this eases reading.

The thesis is organized as follows:

In the *introduction*, the field of analogue VLSI neural networks, including hardware learning, is briefly introduced. Motivations for the research are given

Preface Page vi

and the objective of the thesis is defined.

In the *implementation of the neural network* chapter, the neural network architecture that will make the basis of the rest of this thesis is presented. The results of the chip-in-the-loop training also serves as a standard of reference for on-chip learning implementations.

In the *preliminary conceptions on hardware learning* chapter, the choices of learning algorithms for implementation are considered and I elaborate on general considerations on hardware learning.

In the implementation of on-chip back-propagation chapter, the first hardware learning system is described. It is based on a simple, but elegant, idea and was meant to be just a minor part of the thesis (my initial work was that of implementing RTRL). As it turned out, however, there was a lot of hard work involved in verifying this simple idea (work worth at least  $1\frac{1}{2}$  years). The work has borne fruit, though, in several paper invitations.

The second hardware learning system is described in the *implementation of RTRL hardware* chapter. The system architecture of this work was developed during my studies for the Masters degree. As for the first system, there was a lot of hard work involved in the implementation and testing of the experimental system. A work that is not complete at the time of writing.

In the thoughts on future analogue VLSI neural networks chapter, I have collected some odds and ends of the field which did not fit into the other chapters: During my Ph.D. study, a lot of ideas have come to my mind on network architectures, subcircuits, learning algorithms, etc. Also, I have formed my own personal opinion on several matters. These thoughts are not all mature; however, I find it important to propagate this information to the scientific community in order that other scientists can benefit from the ideas.

Finally, in the last chapter, *conclusions*, the conclusions are drawn. In this section, I have tried to emphasize what is my own contributions to science (denoted by "we" or "our").

The appendices hold material that is of interest mostly to the meticulous reader.

The *enclosures* hold material that is of interest only to the reader who want to carry on my work; and they serves as documentation for my work.

Being organized in a project oriented way, many considerations are placed in the bulk of the text, where it is used, for readability rather than being organized in a logical manner. I hope the index will prove adequate for locating such considerations.

> Lyngby September 1994

Torsten Lehmann

# Acknowledgements

I should like to thank the analogue integrated electronics group at the Electronics Institute for valuable discussions during this work; in particular, Gudmundur Bogason, Erik Bruun, Thomas Kaulberg, John Lansner and Peter Shah. Thanks to the members of CONNECT for discussions on neural networks; especially Lars Kai Hansen and Anders Krogh. Also, thanks to Ole Hansen of the Mikroelektronik Centeret who was always ready with answer and a helping hand. Thanks to Mogens Yndal Petersen of the Electronics Institute for the layout and soldering of numerous PCBs. Thanks to the DTU EUROCHIP staff who endured many questions and pushed deadlines during chip manufacturing.

Thanks to Peter A. Toft, John A. Lansner, Lars Kai Hansen, Thomas Kaulberg and Gudmundur Bogason for valuable criticism of the thesis.

Finally, thanks are due to the Danish Technical Research Council, the Danish Natural Science Council and Analog Devices, Denmark for financial support.

# Contents

| Abstract                                                                                                                                                                                                                                                                        | iii          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Preface                                                                                                                                                                                                                                                                         | $\mathbf{v}$ |

| f Acknowledgements                                                                                                                                                                                                                                                              | vii          |

| Contents                                                                                                                                                                                                                                                                        | viii         |

| Abbreviations                                                                                                                                                                                                                                                                   | xii          |

| Symbols                                                                                                                                                                                                                                                                         | xiv          |

| List of figures                                                                                                                                                                                                                                                                 | xvii         |

| Chapter 1, Introduction 1.1, Implementing ANNs in analogue hardware                                                                                                                                                                                                             |              |

| Chapter 2, Implementation of the neural network  2.1, The artificial neural network model  2.1.1, The neurons  2.1.2, The network  2.2, Mapping the algorithm on VLSI  2.2.1, Architecture  2.2.2, Signalling  2.2.3, Memories  2.2.4, Multipliers  2.2.5, Activation functions |              |

| 2.3, Chip design 2.3.1, The neuron chip 2.3.2, The synapse chip 2.3.3, Sparse input synapse chip 2.4, Chip measurements 2.4.1, The neuron chip 2.4.2, The synapse chips 2.4.3, Chip compound 2.5, System design 2.6, System measurements 2.7, Further work                      |              |

| Contents | Page | ix |

|----------|------|----|

|----------|------|----|

|      | 2.7.1, Process parameter dependency canceling        | 42  |

|------|------------------------------------------------------|-----|

|      | 2.7.2, Temperature compensation                      |     |

|      | 2.7.3, Other improvements                            |     |

| 2    | .8, Summary                                          |     |

| Chap | oter 3, Preliminary conceptions on hardware learning | 46  |

|      | .1, Hardware consumption                             | 47  |

| 3    | .2, Choice of learning algorithms                    | 48  |

|      | 3.2.1, Gradient descent learning                     | 49  |

|      | 3.2.2, Error back-propagation                        |     |

|      | 3.2.3, Real-time recurrent learning                  | 52  |

| 3    | .3, Hardware considerations                          | 55  |

| Chap | oter 4, Implementation of on-chip back-propagation   | 58  |

|      | .1, The back-propagation algorithm                   | 58  |

|      | 4.1.1, Basics                                        | 59  |

|      | 4.1.2, Variations                                    | 59  |

| 4    | .2, Mapping the algorithm on VLSI                    | 62  |

|      | 4.2.1, Hardware efficient approach                   | 64  |

| 4    | .3, Chip design                                      | 66  |

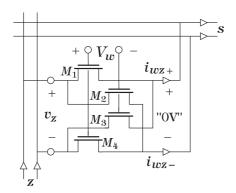

|      | 4.3.1, The synapse chip                              |     |

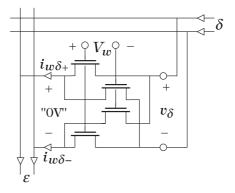

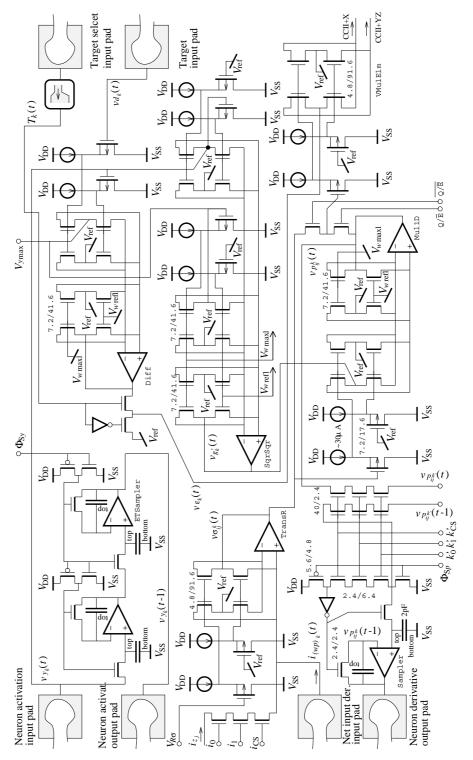

|      | 4.3.2, The neuron chip                               | 68  |

| 4    | .4, Chip measurements                                | 70  |

|      | 4.4.1, The synapse chip                              | 71  |

|      | 4.4.2, The neuron chip                               | 72  |

|      | 4.4.3, Improving the derivative computation          | 75  |

| 4    | .5, System design                                    | 77  |

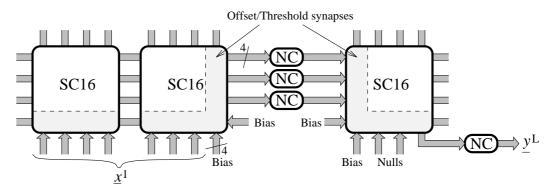

|      | 4.5.1, ASIC interconnection                          | 78  |

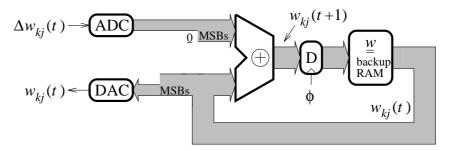

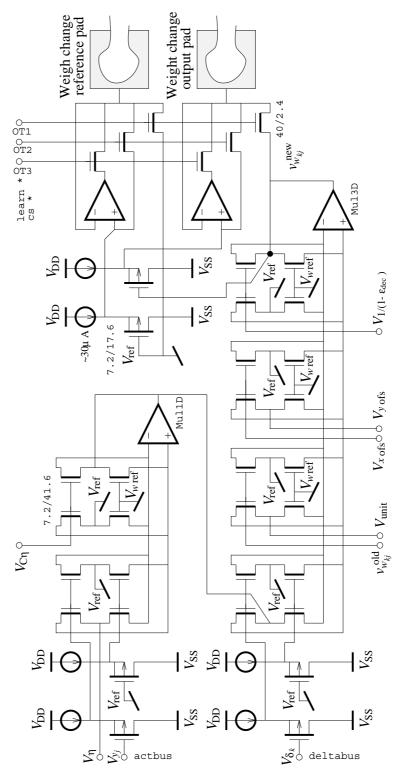

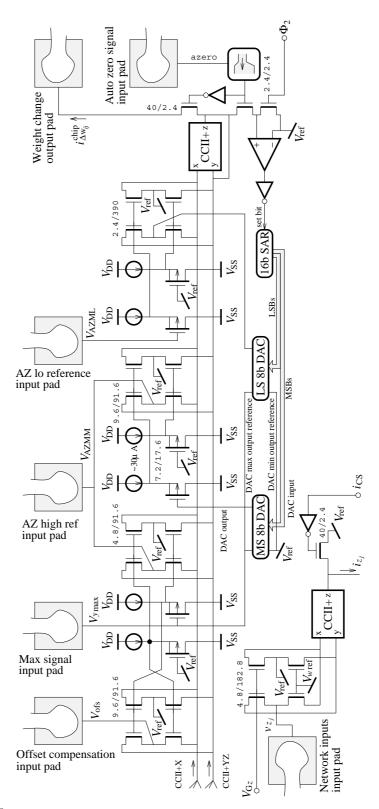

|      | 4.5.2, Weight updating hardware                      | 79  |

| 4    | .6, Non-linear back-propagation                      | 80  |

|      | 4.6.1, Derivation of the algorithm                   | 80  |

|      | 4.6.2, Hardware implementation                       | 82  |

| 4    | .7, Further work                                     | 85  |

|      | 4.7.1, Chopper stabilizing                           | 86  |

|      | 4.7.2, Including algorithmic improvements            | 88  |

|      | 4.7.3, Other improvements                            | 90  |

| 4    | .8, Summary                                          | 90  |

| Chap | oter 5, Implementation of RTRL hardware              | 92  |

| 5    | .1, The RTRL algorithm                               | 92  |

|      | 5.1.1, Basics                                        | 93  |

|      | 5.1.2, Variations                                    |     |

| 5    | .2, Mapping the algorithm on VLSI                    | 95  |

|      | 5.2.1, System simulations                            |     |

| 5    | .3, Chip design                                      | 100 |

|      | 5.3.1, The width N data path module signal slice     | 100 |

|      | 5.3.2, Auto offset compensation                      | 102 |

| Contents | $_{\mathrm{Page}}$ | Х |

|----------|--------------------|---|

| Contents | $_{ m Page}$       | Х |

| 5.4, Chip measurements 5.5, System design 5.5.1, ASIC interconnection 5.5.2, The width 1 data path module 5.5.3, The interface 5.5.4, Algorithm variations 5.6, Non-linear RTRL                               | 107<br>109<br>110<br>111<br>112 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5.6.1, Derivation of the algorithm 5.6.2, Hardware implementation 5.7, Further work 5.7.1, Continuous time RTRL system 5.7.2, Other improvements 5.8, Summary                                                 | 113<br>114<br>115<br>116<br>117 |

| Chapter 6, Thoughts on future analogue VLSI neural networks 6.1, Gradient descent learning? 6.2, Neuron clustering 6.3, Self refreshing system 6.3.1, Neural network ensembles 6.4, Hard/soft hybrid synapses | 121<br>123<br>123               |

| Chapter 7, Conclusions                                                                                                                                                                                        | 128                             |

| Bibliography                                                                                                                                                                                                  | 133                             |

| Index                                                                                                                                                                                                         | 154                             |

| Appendix A, Definitions                                                                                                                                                                                       | 164                             |

| Appendix B, Artificial neural networks  B.1, The ANN model  B.2, Applications and motivations  B.3, Teaching ANNs  B.3.1, Gradient descent algorithms  B.4, Performance evaluation                            | 169<br>170<br>170               |

| Appendix C, Integrated circuit issues  C.1, MOS transistors  C.2, Bipolar transistors  C.3, Analogue computing accuracy  C.4, Integrated circuit layout                                                       | 177<br>178                      |

| C.1, 1110814104 0110411 14,040                                                                                                                                                                                |                                 |

| Contents                                                                                                                             | Page xi |

|--------------------------------------------------------------------------------------------------------------------------------------|---------|

| D.2.4, Back-propagation chip set improvements D.3, The RTRL chip D.3.1, RTRL chip improvements D.4, The RTRL/back-propagation system |         |

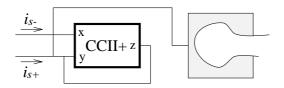

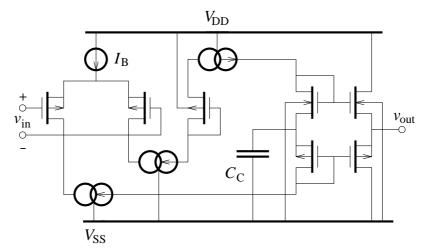

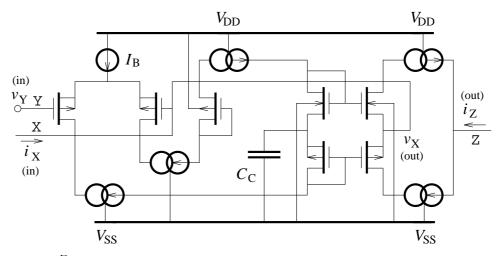

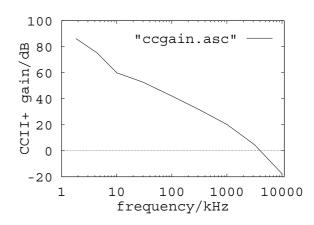

| Appendix E, Building block components  E.1, The op-amp and the CCII+  E.2, The transconductor  E.3, MOS resistive circuit            | 208     |

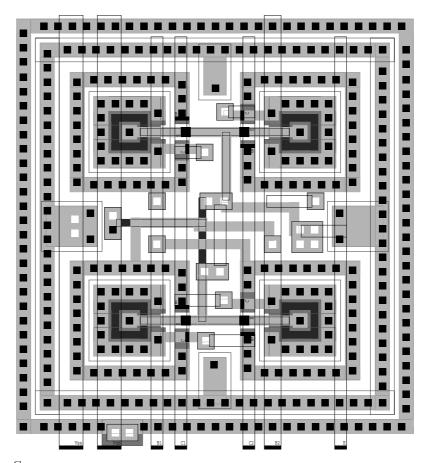

| Enclosure I, Published papers                                                                                                        | E 1     |

| Enclosure II, Chip photomicrographs                                                                                                  | E 68    |

| Enclosure III, Test PCB schematics                                                                                                   | E 74    |

| Enclosure IV, RTRL/back-propagation system interface                                                                                 | E 108   |

# Abbreviations

$\begin{array}{ll} {\rm AC} & {\rm Alternating\ Current} \\ {\rm A/D} & {\rm Analogue/Digital} \end{array}$

ADC Analogue to Digital Converter ANN Artificial Neural Network

ASIC Application Specific Integrated Circuit

BiCMOS Bipolar/Complementary MOS integrated technology

BJT Bipolar Junction Transistor BPL Back-Propagation Learning

CCII Current Conveyor of second generation

CCO Current Controlled Oscillator

CMOS Complementary MOS integrated technology

CPS Connections Per Second

CUPS Connection Updates Per Second

D/A Digital/Analogue

DAC Digital to Analogue Converter

DC Direct Current

DNA DesoxyriboNucleic Acid DSP Digital Signal Processor

EEPROM Electrical Erasable Programmable ROM FLOPS FLoating-point Operations Per Second

FSM Finite State Machine

GCPS Giga CPS GCUPS Giga CUPS

IPM Inner Product Multiplier

IS Input Scale

ISA Industry Standard Architecture

LBM Lateral Bipolar Mode LSB Least Significant Bit

MCPS Mega CPS

MCUPS Mega CUPS

MDAC Multiplying DAC

MFLOPS Mega FLOPS

MLP Multi Layer Perceptron

MOS Metal Oxide Semiconductor

MOSFET MOS Field Effect Transistor

MOST MOS Transistor (MOSFET)

MPC Multi Project Chip

MPW Multi Project Wafer

MRC MOS Resistive Cell

mRNA Messenger RNA

MSB Most Significant Bit

MVM Matrix-Vector Multiplier

NARV Normalized Average Relative Variance

NLBP Non-Linear Back-Propagation

NLRTRL Non-Linear RTRL

NLSM Non-linear Synapse Multiplier

OBD Optimal Brain Damage

OR Output Range PC Personal Computer

PC AT IBM PC AT type compatible computer

PCB Printed Circuit Board

PFM Pulse Frequency Modulation

PLA Programmable Logic Array

PSRR Power Supply Rejection Ratio

PWM Pulse Width Modulation

RANN Recurrent Artificial Neural Network

RAM Random Access Memory RGC Regulated Gain Cascode

RNA RiboNucleic Acid ROM Read-Only Memory

RTRL Real-Time Recurrent Learning

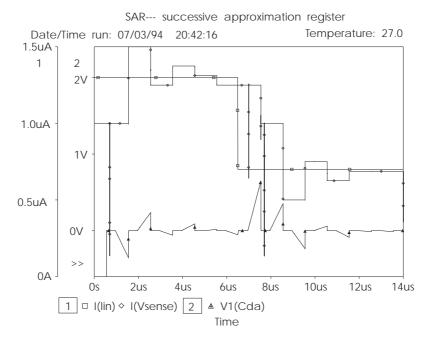

SAR Successive Approximation Register

TTL Transistor-Transistor Logic

UV Ultra Violet

VLSI Very Large Scale Integration

WSI Wafer Scale Integration

# **Symbols**

A list of the less commonly used *symbols* appearing in the thesis is given here. For standard symbols refer to the literature (eg. Geiger et al. [77], Hertz et al. [95] or Sánchez-Sinencio and Lau [206]).

- \* As index: index runs over all possible values.

- $\otimes$  Vector multiplication by coordinates  $(\underline{\xi} \otimes \underline{\zeta} = [\xi_1 \zeta_1, \xi_2 \zeta_2, \ldots]^T)$ .

- \* Convolution operator.

- b $\xi$  As Superscript:  $\zeta^{b\xi}$ : bit number  $\xi$  of  $\zeta$ .

- B Number of bits;  $B_{\xi}$  is a B bit discretization/resolution of  $\xi$ . Also bandwidth.

- $B_{\mathrm{M}\xi}$  Memory necessary to store  $\xi$ .

- $C_{\rm ox}$  MOS gate oxide capacitance per unit area.

- $d_k$  Neuron target value.

- $D_{\xi}$  Non-linearity of  $\xi$ .

- $D_{A\xi}$  Accuracy of  $\xi$ .

- $E_{\rm NARV}$  Normalized average relative variance error measure.

- $g_k(s_k)$  Neuron activation function; also as vector of scalar functions,  $\underline{g}(\underline{s})$ .

- i ANN weight (neuron) index,  $i \in U$ .

- I Set of ANN input indices (m).

- $I_{\rm sm}$  Maximal signal current.

- *j* ANN input/output index,  $j \in I \cup U$ .

- $\mathcal{J}$  Cost function (instantaneous), eg. quadratic ( $\mathcal{J}_{\mathrm{Q}}$ ) or entropic ( $\mathcal{J}_{\mathrm{E}}$ ).

- $\mathcal{J}_{\mathrm{tot}}$  Total cost function.

- k ANN neuron index,  $k \in U$ .

- $k' p_{ij}^k$  (index k) RTRL chip access variable.

- K' MOST process transconductance parameter ( $\mu C_{\rm ox}$ ).

- L Number of layers in ANN. Also MOST channel length.

- $LSB_B$  Sometimes used non unit-less for bit absolute measures.

- l ANN layer number (often indexing as superscript),  $l \in \{1, 2, \dots, L\}$ .

- $\Delta l_{\text{ofs}}$  Geometric device size offset (eg. on L).

- m ANN input index,  $m \in I$ .

- M Number of inputs in ANN.

Symbols Page xv

- $M_k$  Number of inputs to neuron k.

- N Number of neurons in ANN.

- $N_{\mathcal{A}}$  Number of letters in input alphabet  $\mathcal{A}$ .

- $N_{\rm epc}$  Number of epochs ANN is trained.

- O(.) In most places implicitly "order of N": O(f(N)).

- $N_{\rm E}$  Number of networks in ANN ensemble.

- $N_l$  Number of neurons in layer l of ANN.

- ofs As index: offset error.

- $p_{ii}^k$  Neuron derivative variables for RTRL.

- $p_{Nij}^k$  Neuron derivative variables for non-linear RTRL.

- res As index: resolution.

- $R_{\rm D}$  Dynamic range.

- $s_k, s_k^l$  Neuron net input; also as vector,  $\underline{s}$ .

- t Time. Often unit less.

- $t_{\xi \, \mathrm{pd}}$  Propagation delay when calculating  $\xi$ .

- T Set of neuron indices (k) for which a target exist.

- $T_{\rm cyc}$  Learning cycle time.

- $T_{\text{epc}}$  Training epoch;  $t \in T_{\text{epc}}$  when training.

- $T_k$  Indicates if  $k \in T$   $(T_k = 1 \iff k \in T)$ .

- U Set of neuron indices (k).

- $V_{\rm sm}$  Maximal signal voltage.

- $V_{\rm t}$  Thermal voltage:  $V_{\rm t} = kT/q$ .

- $V_{\rm T}$  MOSFET threshold voltage.

- $w_{ij}$ ,  $w_{ij}^l$  Connection strength from input/neuron j (layer l-1) to neuron i (layer l); also as matrix,  $\underline{w}$ .

- $\underline{w}_{\square} \underline{w}$  without the columns corresponding to the inputs.

- $\underline{w}_{\star\star}$  Connection strengths arranged as vector.

- $\Delta w_{ij}$  Connection strength change.

- $\Delta w_{\min}$  Connection strength change threshold.

- W MOST channel width.

- $x_m$  Input to ANN; also as vector,  $\underline{x}$ .

- $y_k, y_k^l$  Neuron activation; also as vector,  $\underline{y}$ .

- $z_j, z_j^l$  Neuron input: ANN input or neuron activation; also as vector,  $\underline{z}$ .

- $\alpha_{\rm FC}$  BJT forward emitter-collector current gain.

- $\alpha_{\rm mtm}$  Learning momentum parameter.

- $\alpha_{\rm N}$  NLBP domain parameter.

- $\beta$  MOSFET transconductance parameter:  $\beta = W/L \cdot \mu C_{\rm ox}.$

- $\beta_{\rm t}$  Activation function steepness  $(\beta_{\rm t} = \partial g(s)/\partial s\big|_{s=0})$ .

- $\gamma_{\rm F}$  Derivative or Fahlman perturbation.

- $\delta_k^l$  Weight strength error for back-propagation; also as vector,  $\underline{\delta}^l.$

Symbols Page xvi

- $\delta_{Nk}^{l}$  NLBP weight strength error.

- $\delta_{\xi}$  Droop rate of sampled signal (eg. weight drift in mV/s).

- $\varepsilon_k, \varepsilon_k^l$  Neuron activation error; also as vector,  $\underline{\varepsilon}$ .

- $\epsilon_{\rm dec}$  Weight decay parameter.

- $\zeta$  General quantity ("random" variable) or free running index.

- $\eta$  ANN learning rate. Also neuron specific,  $\eta_k$ .

- $\Theta_k$  Neuron threshold.

- $\Lambda$  (Weight) restoration efficiency.

- $\mu$  Carrier surface mobility.

- $\xi$  General quantity ("random" variable) or free running index.

- $\sigma_I$  Current mismatch: standard deviation compared to reference device.

- $\sigma_{ij}^k$  Neuron net input derivative variables for RTRL.

- $\phi_{\xi}$  Clock phase  $\xi$ .

Generally, the rules below are obeyed, though deviations do appear. Not all different kinds of signals are distinguished by the rules; the context in which a symbol appear must supply this lack of information. The lack of a consistent, usable standard necessitates this unfortunate "definition".

For electrical signals, the case of the symbol indicates whether it is a DC signal or an AC signal. For the first case (bias voltages, quiescent currents, etc.) we use upper case letters, eg.  $I_{\text{bias}}$ ; for the second (small signal quantities, instantaneous values, etc.) we use lower case letters, eg.  $i_{\text{signal}}$ .

The font of the subscript indicates if the subscript refer to another symbol (italics, eg.  $v_y$ ) or if the subscript is descriptive (roman, eg.  $v_{\text{out}}$ ).

The case of a descriptive index usually indicates whether this is an compound abbreviation (upper case, eg.  $v_{\rm GS}$ ) or not (lower case, eg.  $v_{\rm ofs}$ ).

# List of figures

| Figure $1^2$ , I         | Expandable neural network                        | 11 |

|--------------------------|--------------------------------------------------|----|

| Figure $2^2$ , I         | Expandable recurrent neural network              | 12 |

| Figure $3^2$ , I         | Reconfigurable neural network                    | 13 |

|                          | Typical electronic synapse                       |    |

| Figure $5^2$ ,           | Capacitive storage                               | 15 |

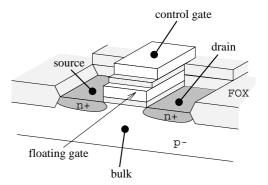

| Figure $6^2$ , 1         | Floating gate MOSFET                             | 17 |

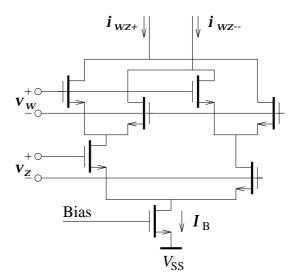

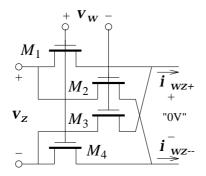

| Figure $7^2$ , I         | MOS Gilbert multiplier                           | 22 |

| Figure $8^2$ , I         | MOS resistive circuit multiplier                 | 23 |

| Figure $9^2$ , 3         | MRC resistive equivalent                         | 23 |

| Figure $10^2$ ,          | Multiplying DAC synapse                          | 24 |

| Figure $11^2$ ,          | Simple non-linear synapse multiplier             | 25 |

| Figure $12^2$ ,          | Weight-output characteristic of NLSM             | 25 |

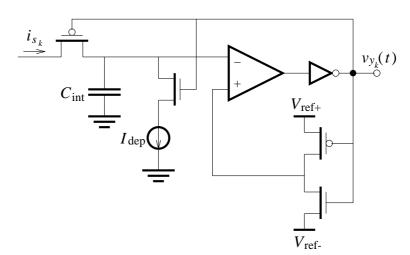

| Figure $13^2$ ,          | Pulse frequency neuron                           | 26 |

| Figure $14^2$ ,          | Distributed neuron                               | 27 |

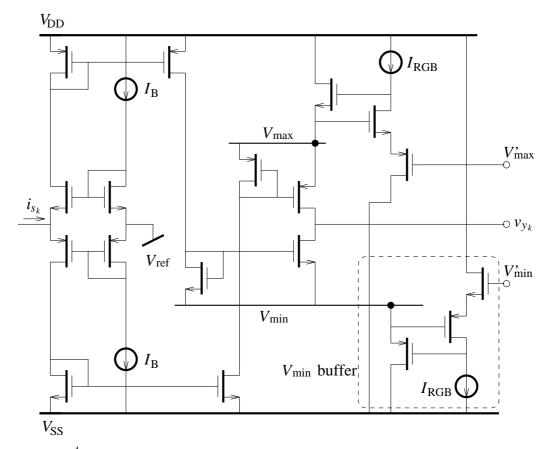

| Figure $15^2$ ,          | Hyperbolic tangent neuron                        | 30 |

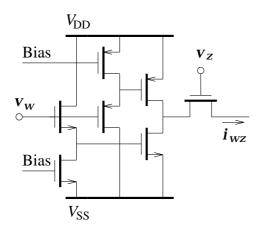

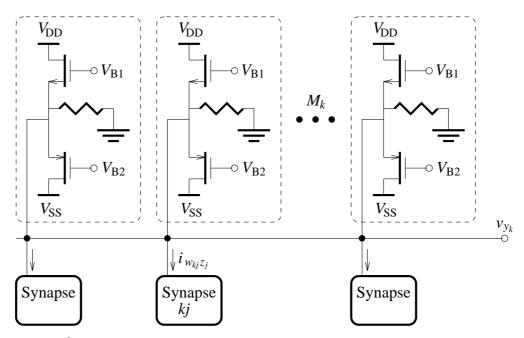

| Figure $16^2$ ,          | Inner product multiplier                         | 32 |

|                          | Synapse schematic                                |    |

| Figure $18^2$ ,          | Current conveyor differencer                     | 33 |

|                          | Nucleotide sequence                              |    |

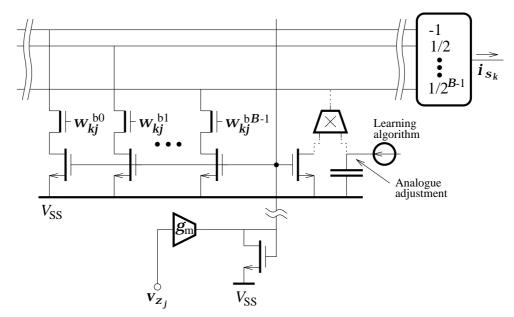

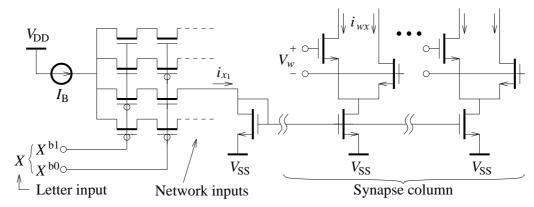

| Figure $20^2$ ,          | Sparse input synapse chip column                 | 35 |

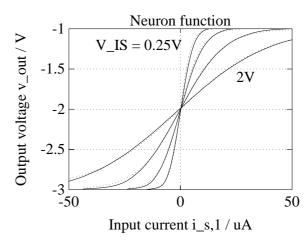

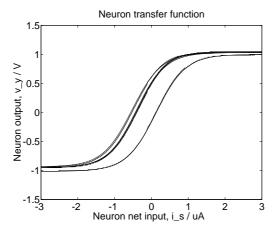

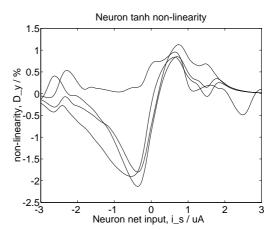

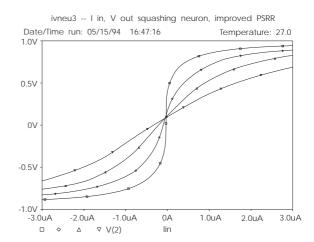

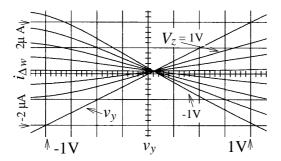

| Figure $21^2$ ,          | Measured neuron transfer function                | 36 |

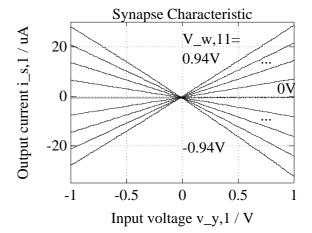

| Figure $22^2$ ,          | Measured synapse characteristics                 | 37 |

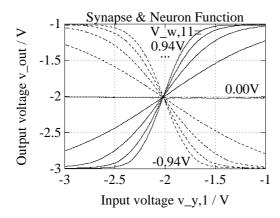

|                          | Measured synapse-neuron transfer characteristics |    |

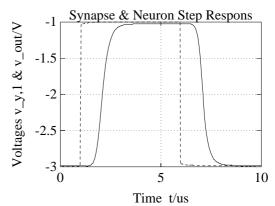

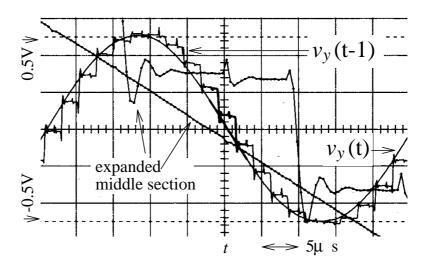

|                          | Measured synapse-neuron step response            |    |

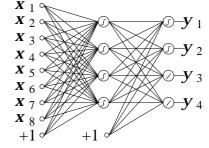

| Figure $25^2$ ,          | Two layer test perceptron                        | 39 |

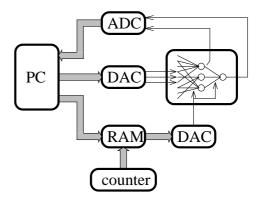

| Figure $26^2$ ,          | Test perceptron system architecture              | 39 |

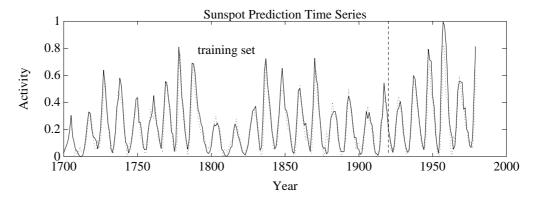

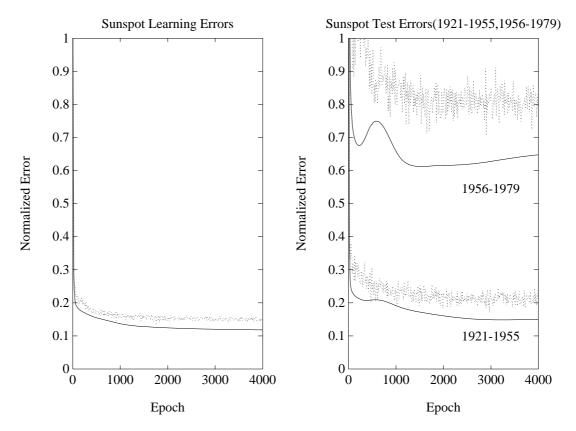

| Figure $27^2$ ,          | Sunspot prediction                               | 40 |

| Figure $28^2$ ,          | Sunspot learning error                           | 41 |

|                          | Sunspot prediction error                         |    |

|                          | Non unity e-c current gain canceling             |    |

| Figure $31^2$ ,          | General process parameter canceling circuit      | 43 |

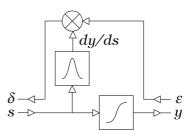

| Figure $32^4$ ,          | Schematic back-propagation synapse               | 62 |

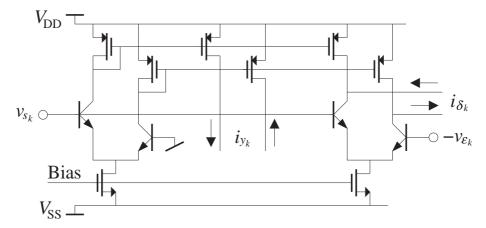

| Figure 33 <sup>4</sup> , | Schematic back-propagation neuron                | 62 |

|                          | MRC operated in forward mode                     |    |

| Figure $35^4$ .          | MRC operated in reverse mode                     | 64 |

|                          | $List\ of\ figures$                                | Page xvii |

|--------------------------|----------------------------------------------------|-----------|

| Figure $36^4$ ,          | Back-propagation system                            | 6         |

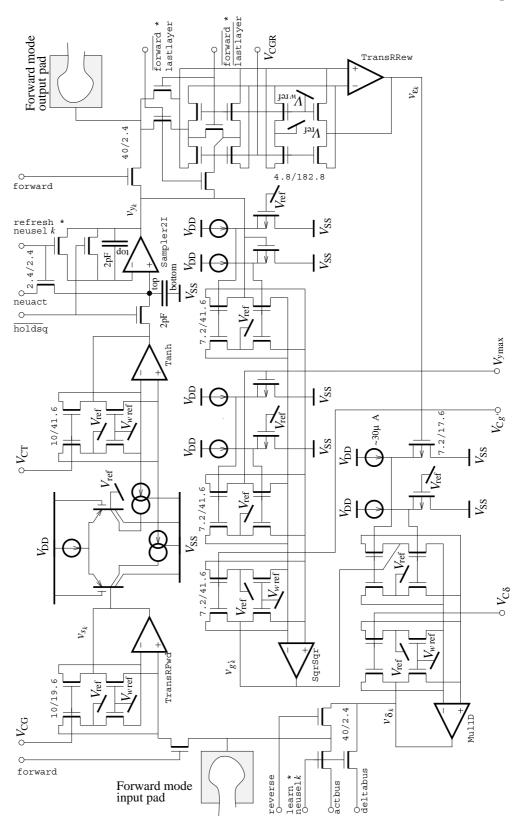

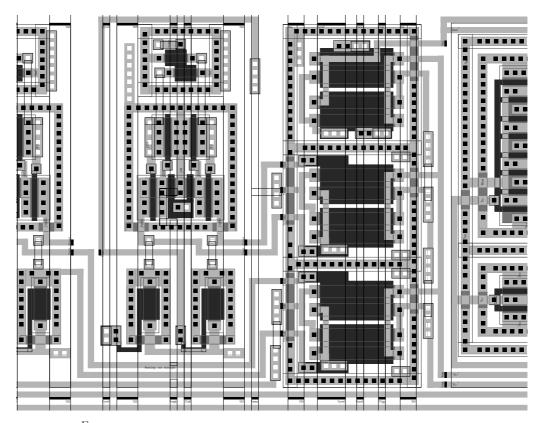

| Figure $37^4$ .          | Second generation synapse chip                     | 6'        |

| Figure $38^4$ .          | Second generation hyperbolic tangent neuron        | 68        |

|                          | Back-propagation neuron                            |           |

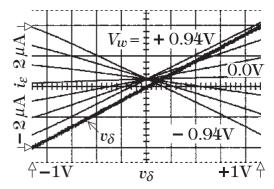

|                          | Forward mode synapse characteristics               |           |

|                          | Reverse mode synapse characteristics               |           |

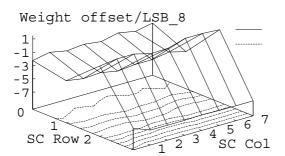

|                          | Forward mode weight offsets                        |           |

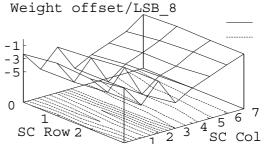

|                          | Reverse mode weight offsets                        |           |

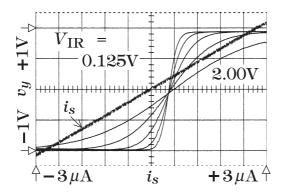

|                          | Forward mode neuron characteristics                |           |

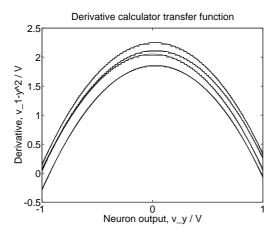

|                          | Computed neuron derivative                         |           |

|                          | Different neuron transfer functions                |           |

|                          | Different neuron non-linearities                   |           |

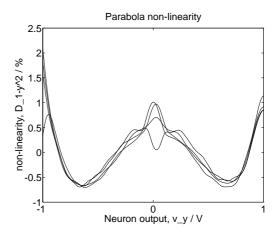

|                          | Different parabola transfer functions              |           |

|                          | Different parabola non-linearities                 |           |

| Figure $50^4$ ,          | Neuron sampler droop rate                          | 74        |

| Figure 51 <sup>4</sup> , | Differential quotient derivative approximation     | 76        |

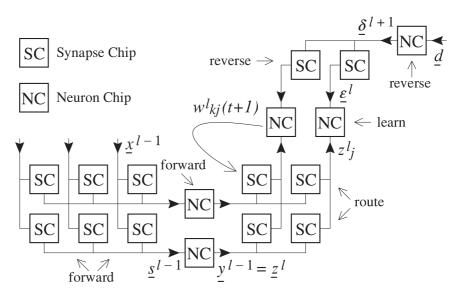

| Figure 52 <sup>4</sup> , | Back-propagation ANN architecture                  | 78        |

| Figure 53 <sup>4</sup> , | Digital weight updating hardware principle         | 79        |

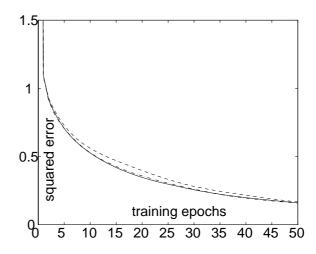

|                          | NLBP training error                                |           |

|                          | Continuous time non-linear back-propagation neuron |           |

|                          | Discrete time non-linear back-propagation neuron   |           |

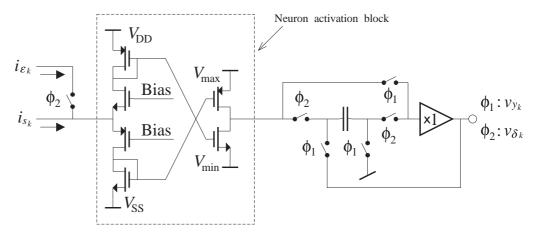

|                          | Neuron activation block schematic                  |           |

|                          | Simulatedi neuron transfer function                |           |

| Figure 59 <sup>4</sup> , | Chopper stabilized weight updating                 | 8'        |

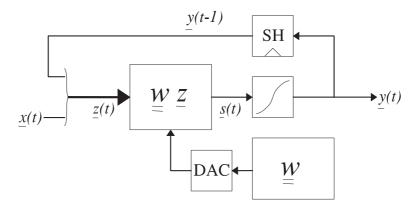

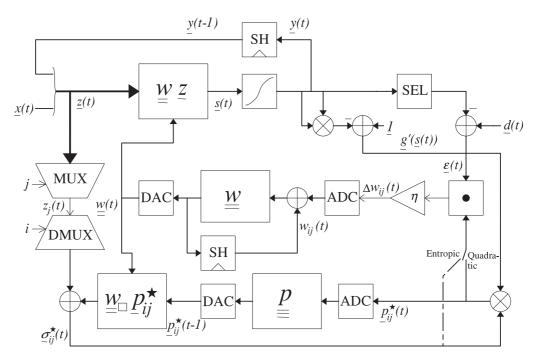

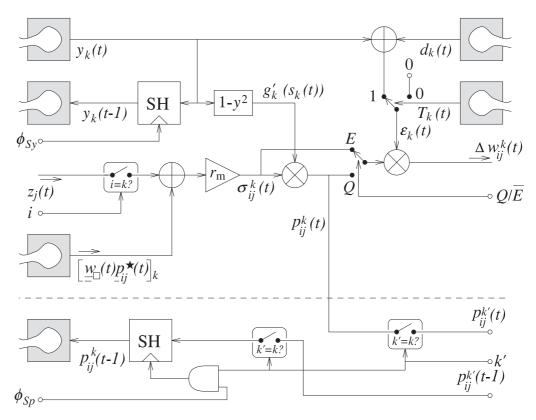

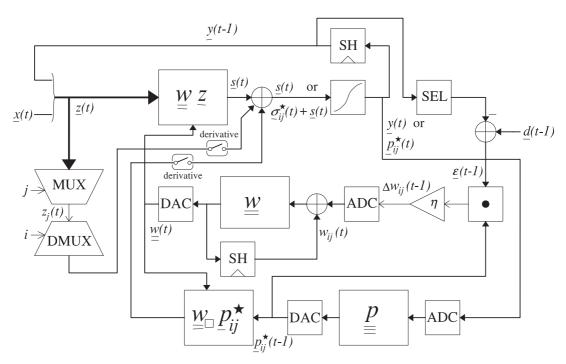

|                          | The discrete time RANN system                      |           |

|                          | The discrete time RTRL system                      |           |

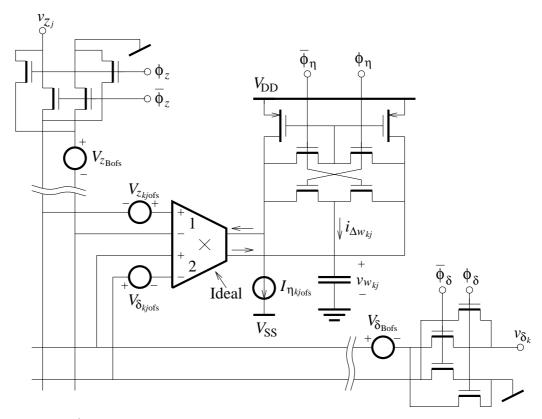

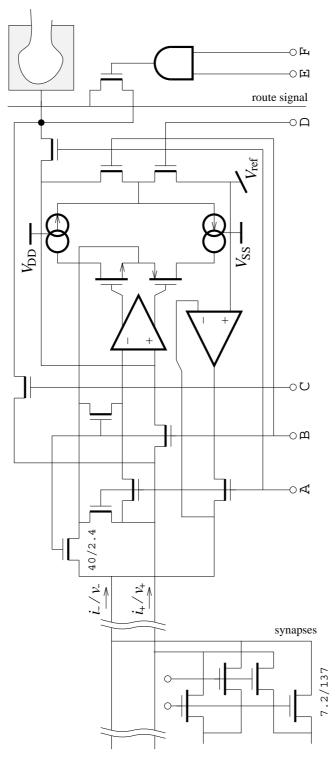

|                          | Order N signal slice                               |           |

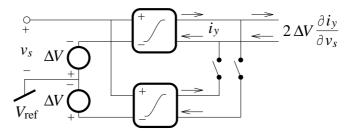

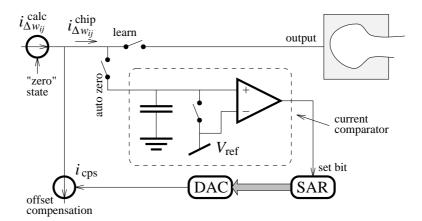

|                          | Current auto zeroing principle                     |           |

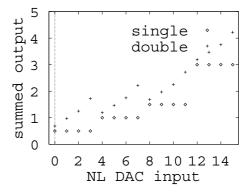

|                          | Double resolution D/A conversion                   |           |

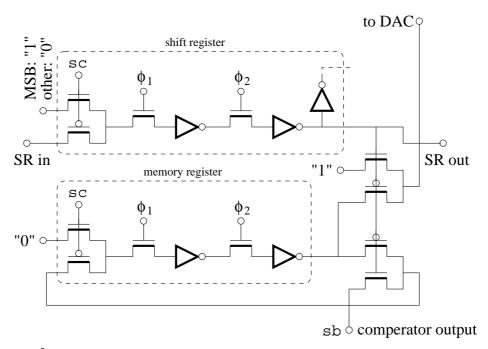

|                          | SAR bit slice                                      |           |

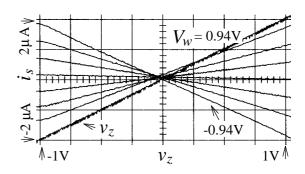

| Figure $66^5$ ,          | Weight change IPM element characteristics          | 10        |

| Figure $67^5$ ,          | Tanh derivative computing block characteristics    | 10        |

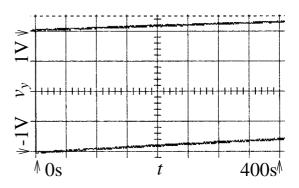

| Figure 68 <sup>5</sup> , | Edge trigged sampler sampling                      | 10'       |

| Figure 69 <sup>5</sup> , | Auto zeroing simulation                            | 108       |

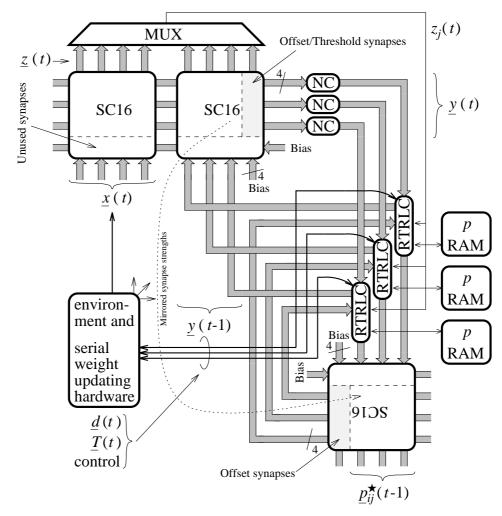

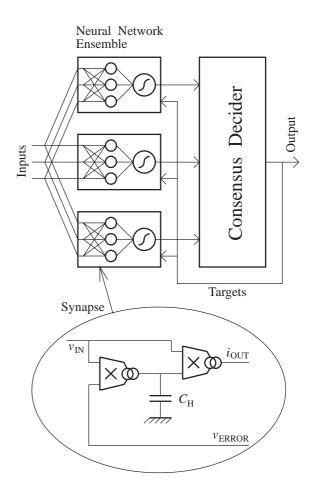

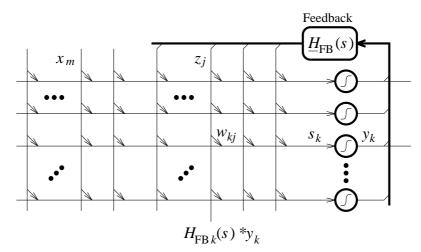

Figure 705, RTRL ANN basic architecture110Figure 715, Non-linear RTRL system114Figure 726, Neuron clustering122Figure 736, Self refreshing ANN system125

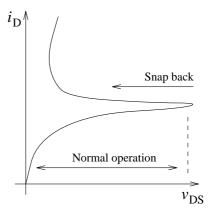

Figure 76 C, N-channel MOS transistor symbols175Figure 77 C, N-channel MOS transistor175Figure 78 C, Short channel snap-back176

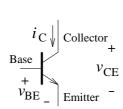

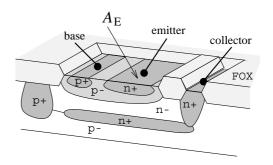

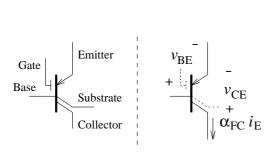

| Figure 81 <sup>C</sup> , Lateral bipolar mode MOSFET symbol                 | 178 |

|-----------------------------------------------------------------------------|-----|

| Figure 82 <sup>C</sup> , Lateral bipolar mode MOSFET                        | 178 |

| Figure 83 <sup>C</sup> , Current subtraction by synapse                     | 178 |

| Figure 84 <sup>C</sup> , Current subtraction by row                         | 179 |

| Figure 85 <sup>C</sup> , Layout of matched transistors                      | 182 |

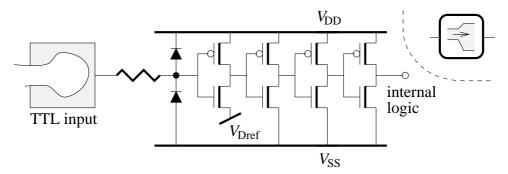

| Figure 86 <sup>D</sup> , Digital level shifter                              | 185 |

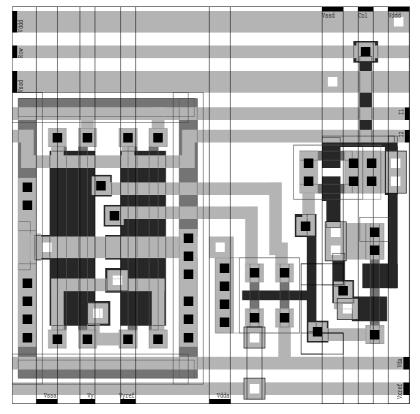

| Figure 87 <sup>D</sup> , Synapse layout                                     | 186 |

| Figure 88 <sup>D</sup> Table of ANN chip set characteristics                | 187 |

| Figure 89 <sup>D</sup> , Table of row/column element control                | 189 |

| Figure 89 <sup>D</sup> , Table of row/column element control                | 190 |

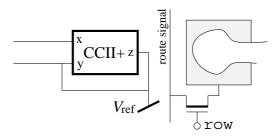

| Figure 91 <sup>D</sup> , Forward mode BPL synapse row element               | 191 |

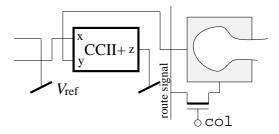

| Figure 92 <sup>D</sup> , Forward mode BPL synapse column element            |     |

| Figure 93 <sup>D</sup> , Route mode BPL synapse row element                 |     |

| Figure 94 <sup>D</sup> , Route mode BPL synapse column element              | 191 |

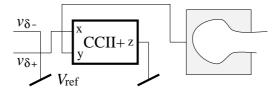

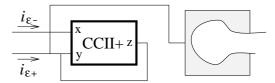

| Figure 95 <sup>D</sup> Reverse mode RPL synapse row element                 | 191 |

| Figure 96 <sup>D</sup> , Reverse mode BPL synapse column element            | 191 |

| Figure 97 <sup>D</sup> , Back-propagation neuron schematic                  | 193 |

| Figure 98 <sup>D</sup> , Back-propagation weight update schematic           | 194 |

| Figure 99 <sup>D</sup> , Table of Back-propagation chip set characteristics | 195 |

| Figure 100 <sup>D</sup> , Table of scaled BPL synapse chip characteristics  | 196 |

| Figure 101 <sup>D</sup> . Scaled synapse chip characteristics               | 197 |

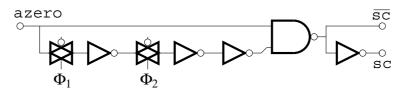

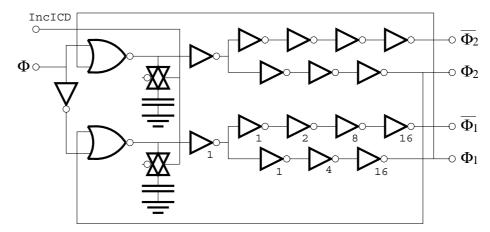

| Figure 104 <sup>D</sup> SAR start signal gating                             | 199 |

| Figure 105 <sup>D</sup> , Transmission gate symbol                          | 199 |

| Figure 105 <sup>D</sup> , Transmission gate symbol                          | 200 |

| Figure 103 <sup>D</sup> , RTRL weight change schematic                      | 201 |

| Figure 106 <sup>D</sup> , Clock generator                                   |     |

| Figure 107 <sup>D</sup> , Table of RTRL chip characteristics                | 203 |

| Figure 108 <sup>E</sup> The operational amplifier                           | 206 |

| Figure 109 <sup>E</sup> , Regulated gain cascode                            | 206 |

| Figure 110 <sup>E</sup> , RGC current mirror                                | 206 |

| Figure 111 <sup>E</sup> , The current conveyor                              | 207 |

| Figure 112 <sup>E</sup> , Op-amp frequency response                         | 207 |

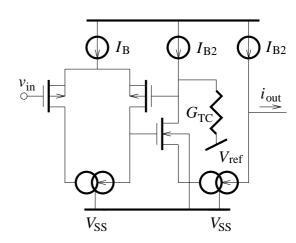

| Figure 113 <sup>E</sup> , The transconductor                                |     |

| Figure 114 <sup>E</sup> , Typical MRC layout                                |     |

|                                                                             |     |

$List\ of\ figures$

Page xix

# Chapter 1

# Introduction

This thesis describes the analogue VLSI implementation of two supervised learning algorithms for artificial neural networks. One is the error back-propagation learning algorithm for a layered feed-forward network and the other is the real-time recurrent learning algorithm for a general recurrent network. Both operate in discrete time on a cascadable analogue VLSI neural network that has a digital random access backup memory for the weights. Also included in this thesis is the implementation of a cascadable analogue VLSI neural network as well as some general conceptions on hardware learning and thoughts on future analogue VLSI neural networks.

During the last decade or so, the field of artificial neural networks (ANNs, see appendix B) has matured. Artificial neural networks are no longer "magic devices" but powerful tools — when used in the right manner — for classification problems and similar tasks for which no algorithmic solution is known. The ANN foundation — both theoretically and on an application level — growing increasingly solid, hardware implementations (primarily analogue and digital VLSI, see appendix C) for high performance systems have begun to emerge. VLSI implementations of recall-mode ANNs are maturing and the field is ready for the step towards fully adaptive VLSI ANNs (ie. including learning). This is the objective of the present thesis: to study analogue VLSI implementations of computational neural networks, with the emphasis on learning hardware implementations. In this introduction motivations for using analogue VLSI to implement ANNs and learning algorithms are described and the objective of the present work is defined.

## 1.1 Implementing ANNs in analogue hardware

Why use analogue hardware? Artificial neural networks can easily be simulated on standard, digital von Neumann computers. These general purpose computers are rapidly moving into every imaginable part of our society. They are the subject of very intense research world-wide, and the competition among manufactures is very hard. The computational performance is growing exponentially over time. How can we possibly hope to compete with them? We can not. There are niches, though, where analogue integrated neural networks have the advantage. In this section we will examine these.

• Parallelism: In the ever present pursuit for faster data processing, two approaches are possible: One is to use faster systems (eg. higher clock frequencies). During the recent years, this procedure has been exploited to the utmost limit: interfacing to and communication with these very fast systems is ever more difficult (Seitz [213]). The other way to speed up data processing is to use parallel data processing elements. This is no trivial task, though, as many problems can not be parallelized (Almasi and Gottlieb [8], Leighton [148]). Neural networks are inherently parallel and are therefore easily mapped on parallel hardware. Further, though analogue data processing elements are inherently slower than their digital equivalents, the analogue versions of the neural network computing primitives, multiplication and addition, can be much smaller than their digital equivalents. Thus massively parallel neural systems are efficiently implemented using analogue VLSI, giving a potential for very fast data processing (eg. Murray et al. [175], Ismail and Fiez [106], Graf and Jackel [82]).

This claim requires a couple of remarks: As the exact mapping on parallel hardware depends heavily on the network topology (which is application dependent), the massively parallel neural systems should be application specific rather than general purpose (Lehmann [142], Jackel [110], Mead [162]). Further, an analogue neural network should not be thought of as an accelerator for a von Neumann computer as using a serial computer to supply the data for a massively parallel neural network would, in most cases, severely limit the performance. Also note that, for very high precision computations digital circuits are required; however, it is generally believed that the precision offered by analogue components is sufficient in many neural systems (though, cf. the following chapters, Edwards and Murray [67], Hollis et al. [97], Tarassenko et al. [238]).

Massively parallel analogue neural networks have been reported by Arima et al. [16], Castro et al. [42] and Masa et al. [157] among others.

• Asynchronousness: Many neural networks are asynchronous in nature. This asynchronousness can be efficiently exploited. Asynchronous (or self timed) systems have a number of distinct advantages over systems governed by a clock (Seitz [213], Sutherland [233], Ramacher and Schildberg [194], Murray et al. [175]):

- Synchronous systems must be designed to run at a conservative clock frequency to ensure functionality in worst case situations; asynchronous systems run at the maximum speed of the present hardware. Furthermore, if a certain component is the bottleneck of the system, this can be replaced by a faster component with immediate improvement of the overall performance.

- When increasing a system clock frequency, communication between components becomes a problem as it is very difficult to distribute the system clock (without skew) over a large area. Asynchronous communication is usually the solution.

- o In synchronous systems all components change states (and thus draw current from the power supply) simultaneously at the clock edges. This puts very heavy demands on the tolerable power supply peak currents, capacitive decoupling, etc. The heavy peak currents also introduce a lot of noise. Asynchronous systems are power averaging.

- Real world interfacing is basically an asynchronous task; using asynchronous systems for this is the natural approach and eliminates, for instance, problems associated with metastability (Seitz [213], Gabara et al. [73]).

In spite of the very attractive features of asynchronous systems, few "conventional" digital data processing systems have been successfully implemented because of the hardware overhead needed for handshaking (Sparsø et al. [227]). Pure analogue systems have no need for handshaking and are thus well suited to implement asynchronous systems. (Though in systems with feed-back the stability must be considered.)

Asynchronously operated analogue neural networks have been reported by Alspector et al. [9], Hollis and Paulos [98] and Mead [162] among others.

- Fault tolerance: A well trained ANN is insensitive to small weight changes as  $\partial \mathcal{J}/\partial w_{kj} \approx 0$  at the equilibrium (where  $\mathcal{J}$  is the error cost and  $w_{kj}$  is a weight, cf. (36<sup>B</sup>)). However it is not insensitive to the complete loss of a connection (due to a short circuit, a RAM fault, radiation, etc.) as the network must have as simple an architecture as possible to ensure good generalization ability. To ensure fault tolerance, even down to the hardware level, it is necessary to introduce redundant hardware. This is in favour of hardware implementations of neural networks; in particular analogue hardware as the cost of an extra synapse is relative low. In this context, a new emerging technology, wafer scale integration (WSI), deserves mentioning, as fault tolerant systems are crucial to the applicability of WSI. This technology is well tailored to the implementation of massively parallel neural networks (Yasunaga et al. [273]).

- Low power applications: The use of sub-threshold operated MOSFETs offer the possibility of extremely low power systems. Though digital systems can function in sub-threshold, analogue systems carry more information per wire and fewer transistors per operation and thus inherently use less power (cf. eg. Ismail and Fiez [106]).

Low power analogue neural networks have been reported by Leong and

Jabri [149] and Mead [162] among others.

• Real-world interfacing: As well as being asynchronous, real-world interfaces are often required to be analogue. Analogue neural networks obviously eliminate the need for A/D and D/A converters, which is an attractive feature. However, this becomes of paramount importance when the data is applied in massive parallelism. The use of hundreds or thousands of high speed A/D converters would seldom be justified. For low power systems with real-world interfaces it is also of great importance that no power is wasted in the processes of A/D and D/A converting.

Analogue neural networks with real-world interfaces have been reported by Leong and Jabri [149], Masa et al. [157] and Mead [162] among others.

• Regularity: The regularity of artificial neural networks makes them well suited for massively parallel implementations: The design effort can be put in designing a few efficient components which are used repeatedly and interconnected in a regular way.

To conclude: At least two niches for analogue integrated neural systems exist, both possibly asynchronous or with redundant hardware:

- Massively parallel, application specific systems having a parallel real-world interface.

- Small, low power, application specific systems with a real-world interface.

In this work we will be predominantly interested in the massively parallel analogue neural networks rather than the low power ones.

Today, several applications using analogue integrated neural networks have been reported. For instance high energy particle-detector track-reconstruction devices (Masa et al. [157]), implantable heart cardioverters/defibrillators (Leong and Jabri [149]) and silicon cochleas, retinas and motion sensors (Mead [162], Park et al. [185], Cao et al. [38]).

Though most systems reported embrace the principles above, general purpose analogue neural systems have been reported (Mueller et al. [173], Van der Spiegel et al. [228], Satyanarayana et al. [207]). Systems that do embrace the above principles can be found in Bibyk and Ismail [23, 24], Bruun et al. [32], Corso et al. [53], Eberhardt et al. [65], Hollis and Paulos [98], Kub et al. [126], Lansner and Lehmann [130, 131], Linares-Barranco et al. [151], Mead [162], Moon et al. [169], Murray et al. [175, 176], Neugebauer and Yariv [180] and Ramacher and Rückert [193].

# 1.2 Implementing learning algorithms in analogue hardware

Because of the non-ideal characteristics, analogue integrated neural networks are most often taught using chip-in-the-loop training (Castro et al. [42], Eberhardt et al. [66]) — that is, rather than down loading predetermined weights for a given application, each individual chip (or system) is trained by (i) applying an input pattern to the chip, (ii) compute the network error on the basis of the target values and the actual chip outputs, and (iii) adjust the weights on the chip according to the learning algorithm such that the network error decreases. This can accommodate for offset errors, non-linearities, etc.

There is a wealth of different training approaches which quite easily can be programmed on a host computer for chip-in-the-loop training. The question now arising is: Why should we sacrifice the flexibility of chip-in-the-loop training using a host computer in favour of implementing learning algorithms in analogue hardware? The reasons are similar to the reasons for implementing ANNs in analogue hardware in the first place:

Performing similar operations on all synapses/neurons of a regular system composed of synapses and neurons, many learning algorithms have the same properties as neural networks when implemented in analogue hardware:

• Parallelism: Learning is computationally a very heavy task. Typically of the order  $O(N^4)$  or  $O(N^6)$  in a system with N neurons. (Compare to the recall-mode task which is of the order  $O(N^2)$ , assuming the system has  $O(N^2)$  synapses.) In terms of speed, it is therefore of even greater importance to utilize inherent parallelism for the learning algorithm than for the neural network itself. Fortunately many learning algorithms can be parallelized to a great extent. The arguments for using analogue hardware to utilize the parallelism are the same as above.

Massively parallel implementations of learning algorithms have been reported by *Arima et al.* [16] among others.

- Adaptability: Adaptive neural systems are continuously taught while being used. At least two situations exist where the learning algorithm must be embedded in the system hardware: (i) In large adaptive systems, where it is crucial to utilize the inherent parallelism of the learning algorithm. (ii) In small, adaptive, low-power systems, where a host computer is not available. In these two application areas it is likely that the neural network is analogue—and the arguments that advocated the use of analogue hardware for the neural network holds for the implementation of the learning algorithm too.

- Asynchronousness: Many learning algorithms can be formulated in continuous time, which enables asynchronous, analogue hardware implementations of learning algorithms. An asynchronous, analogue neural network with asynchronous, analogue interfaces is most naturally taught by such a learning algorithm.

- Fault tolerance: Some learning algorithms can be formulated to operate on local data in such a way that the learning algorithm can be embedded in the

(extended) synapse and neuron hardware. In a fault tolerant analogue neural network, the inclusion of such a learning algorithms does not sacrifice the fault tolerance for the system as a whole.

- Low power applications: As is the case for the analogue neural networks, analogue implementations of learning algorithms can use MOSFETs operated in sub-threshold for extremely low-power applications.

- Data conversion: The learning algorithm needs access to inputs, outputs and intermediate variable of the neural network. If the neural network is analogue, the use of analogue hardware for the learning algorithm eliminates the need of A/D and D/A converters (cf. above).

- Regularity: As is the case for the neural networks, many learning algorithms are regular in structure; thus the design of the equivalent hardware is inexpensive.

Combining these properties with the conclusion in section 1.1, we conclude that at least two niches for analogue hardware implementations of learning algorithms exist, both possibly asynchronous or with redundant hardware:

- Massively parallel, possibly adaptive, application specific systems having a parallel real-world interface.

- Small, adaptive, low power, application specific systems with a real-world interface

As for the neural networks, it is believed in certain circles that the limited precision of analogue hardware is sufficient for the implementation of (certain) learning algorithms, because of the present feed-back. Some even argue that limiting effects as noise (Murray and Edwards [177]) can improve learning ability. Certain offset errors, however, can be completely destructive for the learning scheme (Montalvo et al. [168], Lehmann [139, 140]), and it is not yet generally accepted whether or not this prohibits analogue implementations of learning algorithms (though a few systems have been reported, eg. Alspector et al. [9], Shima et al. [220] and Valle et al. [251]). Thus research on implementing analogue learning hardware still has a wealth of unexplored areas. This is to what we will commit the following chapters.

Architectures for analogue hardware learning can be found in Alspector et al. [9], Arima et al. [16], Card [39], Caviglia et al. [44], Hollis et al. [99], Jabri and Flower [107], Lehmann [139, 141, 142], Linares-Barranco et al. [151], Macq et al. [154], Matsumoto and Koga [160], Montalvo et al. [168], Murray [174], Reyneri and Filippi [196], Schneider and Card [210], Shima et al. [220], Tarassenko and Tombs [237], Valle et al. [251], Wang [256] and Woodburn et al. [270].

# Chapter 2

# Implementation of the neural network

Rather than implementing a learning system all at once, we have chosen a sequential approach, first implementing an acting neural system, and second implementing learning hardware for this system. In this chapter the implementation of the artificial neural network that is the core of the systems in this thesis will be presented. The chapter includes reflections on the choice of network models and topologies suitable for an analogue VLSI implementation. Also, the choices of hardware topologies and essential subcircuits (memories, multipliers and thresholding hardware) are discussed — with the future implementation of hardware learning in mind. Several examples from the literature are given. After the presentation of the design of and measurements on our cascadable ANN solution, and after the presentation of system level measurements, reflections on future work are given: the inclusion of process parameter dependency canceling and temperature compensation. A summary concludes the chapter.

### 2.1 The artificial neural network model

As the very first thing, we must decide on a model for our artificial neural network. There are three properties that this model must possess; it must be:

- General purpose

- Simple

- Suitable for the technology

It was argued in chapter 1 that analogue ANNs have to be application specific. With no particular application in mind at this point, we shall deviate slightly from this principle without actually violating it: the object is to design a set of general purpose building block components or modules (Eberhardt et al. [65], see also Mueller et al. [173]). Application specific systems can then be composed of a number of these.

Analogue computational hardware is typically limited to a relative precision of about 1% (eg. O'Leary [182], see appendix C). For this reason, and for the reason of limiting the hardware cost, it is preferable to use a *simple ANN model*. Some researchers try to model the biological mechanisms of neural networks very closely (Grillner et al. [86], see also MacGregor [153]) or use other complicated network models. This should not be necessary for computational neural networks as many of the properties of these are owing to the structure and non-linearity of the system.

It is of paramount importance that our ANN model is compatible with the restrictions imposed by the analogue VLSI technology (eg. Mead [162]). Otherwise the advantages of using the technology in the first place would be lost. It must be absolutely clear that we thus can not justify the implementation of an arbitrary model (just as we can not justify the use of analogue integrated ANNs for an arbitrary application as argued in the previous chapter); the model must be easy to map on the hardware in terms of both topology and computation primitives.

Our first objective will be to implement an acting system — which can be refined later if necessary.

#### 2.1.1 The neurons

Using stochastic neurons gives the possibility of implementing very powerful networks such as Boltzmann machines (Hertz et al. [95]). The activation,  $y_k$ , of the stochastic neuron k, typically of value 1 or -1, is probabilistically determined:

$$\Pr(y_k = 1) = 1 - \Pr(y_k = -1) = g_k(s_k),$$

where  $s_k$  is the neuron k net input and  $g_k(.)$  is the activation function (cf. appendix B). Stochastic systems can very efficiently explore the state space of the system's free parameters during a learning process. They are somewhat slow, however, as the outputs must be averaged over time to find the probability distributions of the outputs, and the stochastic processes are not very well suited for analogue signal processing (though see Alspector et al. [9] for a VLSI implementation that come around these problem using different kinds of annealing processes).

A very general, deterministic, network model uses higher order neurons (Wulff [271], Giles et al. [79]):

$$y_{k} = g_{k}(s_{k})$$

$$= g_{k}\left(\sum_{j} w_{kj}z_{j} + \sum_{j_{1} \leq j_{2}} w'_{kj_{1}j_{2}}z_{j_{1}}z_{j_{2}} + \sum_{j_{1} \leq j_{2} \leq j_{3}} w''_{kj_{1}j_{2}j_{3}}z_{j_{1}}z_{j_{2}}z_{j_{3}} + \cdots\right),$$

$$(1^{2})$$

where the  $w_{kj}$ s,  $w'_{kj_1j_2}$ s,  $w''_{kj_1j_2j_3}$ s, ... are the connection strengths and the  $z_{j\xi}$ s are the neuron k inputs  $\dagger$  (cf. appendix B). The highest number of  $z_{j\xi}$ -factors gives the order of the neuron. Though higher order networks can be very efficient compared to "conventional" (ie. first order) networks, they map poorly on VLSI because of their high structural dimensionality (a Dth order network has a D+1-dimensional structure). Thus, using first order deterministic neurons is preferable from a VLSI implementation point of view. This is also theoretically the most well-studied one which is also significant.

Finally there is the choice of the neuron transfer function. The simplest possible choice would be setting  $g_k(.) \equiv \text{sign}(.)$  (a hard limiter) which is used in Hopfield networks and which is well suited for an analogue VLSI implementation (Hollis and Paulos [98], Sánchez-Sinencio and Lau [206]). This, however, would sacrifice the generality of the system (obviously continuous valued outputs would be impossible; also, many learning algorithms rely on a smooth transition from "low" to "high" neuron output). The choice, therefore, is to set  $g_k(.) \equiv g(.)$ , where g(.) is a sigmoid-like function, which is a sufficiently general solution (networks using this kind of neurons can approximate any limited function (Lapedes and Farber [134])).

#### 2.1.2 The network

Ideally we should put no constraints on the *network topology*. However, as we shall see in the following, sparse interconnections between neurons will be difficult to implement in general. Thus the choice is to use fully interconnected (groups of) neurons which is the most general topology.

Using an unconstrained topology imposes another problem if feedback is present: instability. An unknown number of neurons in a feedback loop would cause an unknown phase shift at high frequencies and might lead to oscillations. The problem is further complicated by the fact that signs and magnitude of the gains (weights) in the system change during learning. A solution is to place the feedback as shown in figure 74<sup>B</sup> and ensuring a single dominating pole in the loop (refer to Hollis and Paulos [98], Linares-Barranco et al. [151], Graf and Jackel [82], and

<sup>†</sup>  $z_{j_{\xi}}$  can be either a *network input*,  $x_{j_{\xi}}$ , or the output *activation* from another *neuron*,  $y_{j_{\xi}}$  (see sections 4.1.1 and 5.1.1).

Mueller et al. [173], eg., for such systems). In non-relaxation systems† the network time constants should — in some way — match the time constants of the input data and of possible learning hardware. In this case it is easier to use a discrete time feedback (ie. a sampler) in a general system, though the asynchronousness is sacrificed. Even using discrete time systems, there is still a wealth of problems to which we can apply analogue ANNs, and most of the systems in this thesis will be designed to work in discrete time.

# 2.2 Mapping the algorithm on VLSI

Before presenting our analogue integrated ANN solution, we shall have a look at different aspects of such implementations. More specifically we shall discuss different architectures, signalling methods, memories, multiplication and thresholding circuits — with the future implementation of learning algorithms in mind.

#### 2.2.1 Architecture

The architecture of a small, low power, application specific system (cf. chapter 1) must be tailored to the application. The building block components for such systems are thus the atomic parts of neural networks — synapses and neurons — and would have the form of, say, a cell library to a CMOS process. Though the discussions in the present thesis are meant for massively parallel systems, many of the considerations apply equally well for small, low power systems. Only, the circuits should be replaced by low power ones. We shall use strong inversion circuits rather than subthreshold ones as the former are inherently faster than the latter.

For massively parallel, application specific systems, the level of integration of the building block components is preferably very high (this reduces design time). Unfortunately, this puts constraints on the architecture and minimizing these constraints is one of the objects of VLSI neural networks design.

Reformulating  $(1^2)$  for a vector of first order neurons (cf.  $(30^B)$ ) — corresponding to, say, a layer — we have:

$$\underline{y} = \underline{g}(\underline{s}), \quad \text{where} \quad \underline{s} = \underline{\underline{w}}\,\underline{z}\,,$$

(2<sup>2</sup>)

where  $\underline{g}(.)$  is a vector of sigmoid-like functions. Assuming we have a parallel operated matrix-vector multiplier (MVM) that gives as output the multiplication of its input vector and a stored matrix, the number of rows in the multiplier is increased

<sup>†</sup> Systems where the network is *not* allowed to settle to a steady state before the next input pattern is applied (*Williams and Zipser* [267] and others); these are used in time sequence data processing.

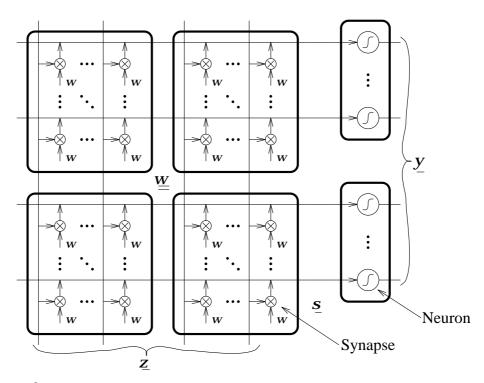

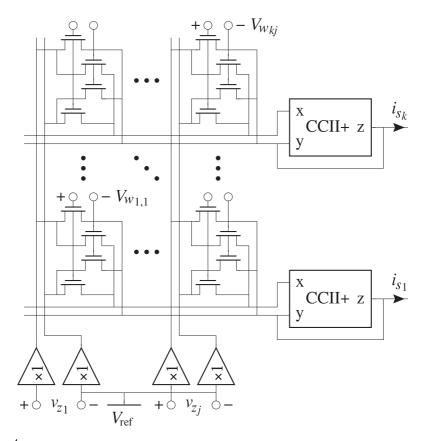

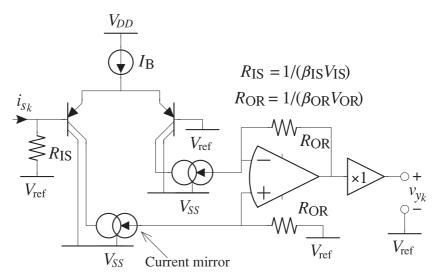

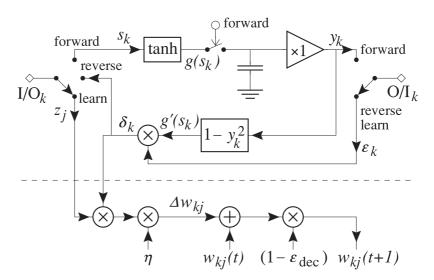

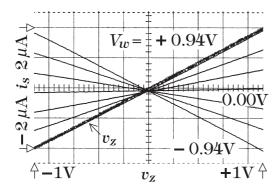

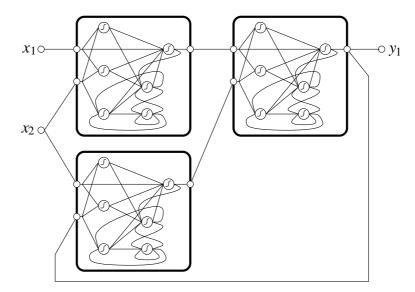

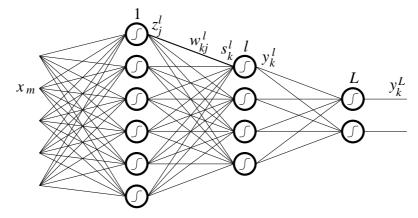

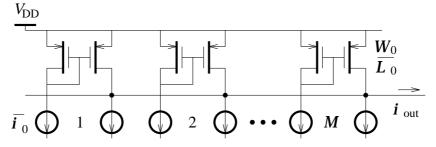

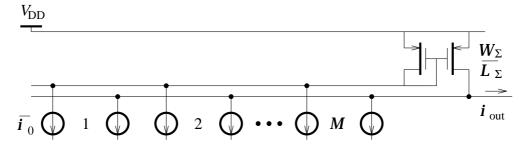

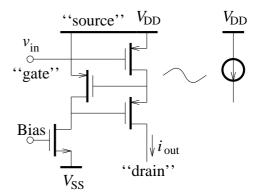

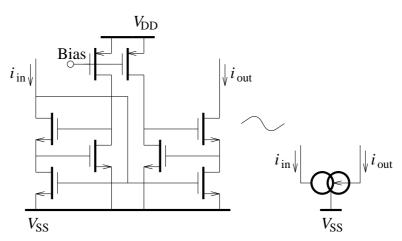

simply by adding another multiplier with the same input vector. The number of columns is increased by adding the output vector to that of another multiplier. As dimensions are easily added to a vector of functions, the implementation of an ANN that is fully interconnected (between layers, if layered) and which can be scaled to an arbitrary size, is feasible using two building block components (Eberhardt et al. [65], Lansner and Lehmann [131], Shima et al. [220]). This is shown in figure  $1^2$ ; it is assumed that adding the outputs from several multipliers is done simply by connecting their outputs together (cf. next section). This cascadability is most important. We shall use the terms synapse chip (the multiplier) and neuron chip (the squashing functions) for the two modules. Further, we shall refer to the rows/columns of  $\underline{w}$  as rows of synapses and columns of synapses.

For a recurrent network, an elegant approach is to place synapses on the neuron chip as illustrated in figure  $2^2$  (here:  $\underline{y} = \underline{g}(\underline{w}\underline{y})$ ) (Duong et al. [63]). This makes module interconnection easier.

Figure 1<sup>2</sup>: Expandable neural network. This topology can implement systems of arbitrary size, fully connected between the layers.

One could expect routing problems in systems with rigorously interconnected units. The distributed and regular placement of the synapses in the above systems, however, practically eliminates this problem (massive inter-chip communication is still inconvenient, though). For sparse, random connectivity routing would consume considerably more area per synapse.

Obviously, any first order ANN topology can be mapped on one of the above systems by setting some of the connection strengths equal to zero (feedback and extra layers can be added in figure 1<sup>2</sup>). If the system is known to have sparse

Figure  $2^2$ : Expandable recurrent neural network. This topology can also implement systems of arbitrary size. The neurons must not be larger than the synapses in order not to waste area.

connectivity, though, it would be preferable not to waste hardware for all the null-connections. This could be accomplished by "folding" the synapse matrix, in a way similar to the folding of sparse PLAs, if the structure of the network is known in advance (*Bruun et al.* [32]). Often it is not, however; and certainly not when implementing general neural architectures.

Solving a problem with unknown properties, one would typically arrive at the sparse architecture by pruning (ie. removing unnecessary connections) a fully connected network, eg. using optimal brain damage (OBD) (Le Cun et al. [55], see also Larsen [135]). Thus preferably, a reconfigurable neural network should be able to emulate a fully connected one during the pre-pruning phase. As, depending on how it is used, OBD can remove as few as 50%–75% of the connections, and as simple synapses can be very small, care should be taken that interconnections and routing switches does not take up more area than left free by the reduced number of synapses. Another way to avoid "wasting" hardware in a pruned network would be to use the "null-connections" of a fully connected architecture to introduce redundancy in the system.

We believe that the fully connected "building block" topology of figure 1<sup>2</sup> is, though simple, a very capable one. We shall use this in the present work.

A number of systems with reconfigurable network topologies have been proposed in the literature (Mueller et al. [173], Satyanarayana et al. [207], Graf and Henderson [84], and others). Though it can be questioned if a "random" connected neural network can be mapped efficiently on these systems, they do provide a gen-

eral problem-solving environment. Also, the reconfigurability can be used to alter the ANN topology during training and to map out defective blocks.

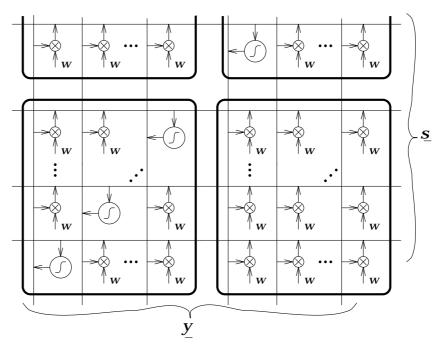

Figure 3<sup>2</sup>: Reconfigurable neural network. The philosophy of this kind of topology is to implement a general neural computer.

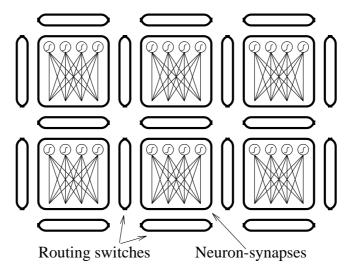

A particularly interesting reconfigurable ANN is found in Satyanarayana et al. [207], see figure 3<sup>2</sup> and 14<sup>2</sup>, p. 27. In this implementation the "lumped" synapses and neurons above are replaced with "distributed neuron-synapses": The neuron squashing circuit is distributed among the connected synapses and can be connected in parallel with other neuron-synapses, ensuring that the routing switch area is kept reasonably low, as indicated in figure 3<sup>2</sup>.

## 2.2.2 Signalling

The *domains* in which the various signals are carried are closely related to the needs of the matrix-multiplier above — or the needs of a synapse:

- The output from a neuron (or a network input) must easily be distributed to a column of synapses.

- The outputs from a row of synapses must easily be accumulated.

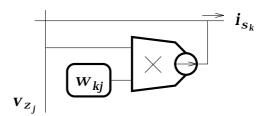

Distributing a signal is most easily done using a voltage as this can be detected using high impedance sensors in parallel (ie. MOS gates). In the current domain the addition of analogue signals is simply done by connecting the input wires to the output wire. Thus, using synapses with voltage inputs and current outputs satisfies the above requirements — which is fortunate as multipliers typically have voltage inputs and current outputs. This is illustrated in figure  $4^2$ . A variation of the current output scheme is to use charge packages which can be accumulated on an integrator.

Figure 4<sup>2</sup>: Typical electronic synapse. The multiplier has voltage inputs and current output to ensure the cascadability of synapses.

Analogue signals carried in the voltage/current domains are sensitive to noise; for instance coupled via the power supply or capacitive/inductive parasitics. In a pulse stream neural network, the noise sensitivity of the neuron outputs is efficiently reduced by moving the information from the voltage domain to the time domain — for instance using pulse frequency modulation (PFM) or pulse width modulation (PWM) (Murray et al. [175, 176]): A digital voltage signal can be easily distributed and regenerated, and the temporal information is insensitive to most noise sources. The noise sensitivity of the synapse outputs is not so easily reduced because of the requirement for easy accumulation. The synapse outputs would thus typically be charge packages (the connections strengths multiplied by the stream of input pulses). To get the full advantage of the noise insensitive neuron outputs it is therefore important that the synapse-to-neuron connections are kept at a minimum, local area. That is, only neuron outputs should be used for inter-chip communication.

The disadvantages of pulsed neural networks is a reduction in speed: Given a bandwidth B of our system, we can process 2B data points (Tugal and Tugal [250]) in a pure analogue system† whereas only 2B/100 in a PFM neural network with a dynamic range of  $40 \, \mathrm{dB}$ .

The above are the most commonly used signalling methods in integrated neural network contexts, though other methods exist (Neugebauer and Yariv [180], Murray et al. [175], Mead [162], Webb [259], Mortara and Vittoz [171]). We shall use continuous valued signalling in the voltage and current domains in this work as this is inherently the fastest signalling method compatible with a simple synapse architecture.

As seen in figure 4<sup>2</sup>, the typical electronic synapse consists of two components: a

<sup>†</sup> That is the fundamental Nyquist upper limit, assuming we use sinc (sinc(x)  $\stackrel{\text{def}}{=}$  sin(x)/x) pulses in a linear system. A more realistic measure would be, for instance, B data points (per second): assuming the system has a single dominating pole at the frequency  $f_{3dB}$ , the output corresponding to a step input would settle to 8 bit accuracy within the time  $1/f_{3dB} = 1/B$  (Lehmann [140]); ie. we could process B data points.

multiplier and a connection strength memory cell. As the number of synapses in an ANN (mostly) scale as  $O(N^2)$ , where N is the number of neurons, reducing the synapse area has been one of the major objects of integrated neural network research. Thus a discussion of memory cells and multipliers are the subject of the following two sections.

#### 2.2.3 Memories

Storing analogue signals are by no means simple; no true, efficient analogue electronic memory exists today. Thus, the storage of the synaptic strengths is a major concern in analogue ANNs research; the solutions found in the literature are compromises of one kind or another, most of which can be put in one of the following categories:

- Capacitive storage

- Storage using special process facilities

- Digital storage

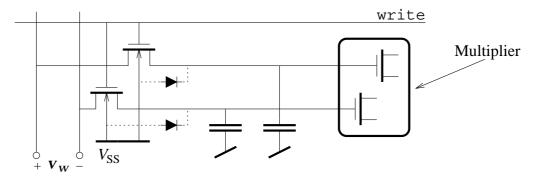

Capacitive storage The simplest method for storing an analogue signal is to put a charge on a capacitor and reading this using the very high impedance gate terminal of a MOSFET (Tsividis and Satyanarayana [246]). The drawback of this method is that the leakage current (primarily) through the sampling switch (or some other weight changing device) eventually exhausts the weight. Several approaches to reduce the leakage current are possible. For instance using a differential scheme as shown in figure 5<sup>2</sup>, which cancels the predominant source-bulk reverse biased junction current. (This scheme also cancels the offset error due to charge injection.) Alternatively, using a low offset voltage buffer, one can ensure a 0 V voltage drop across the source-bulk diode, efficiently eliminating this leakage (see Shah [217], Vittoz et al. [254], Horio and Nakamura [101]). Whatever method employed, though, weight decay can not totally be eliminated and some kind of refresh is necessary.

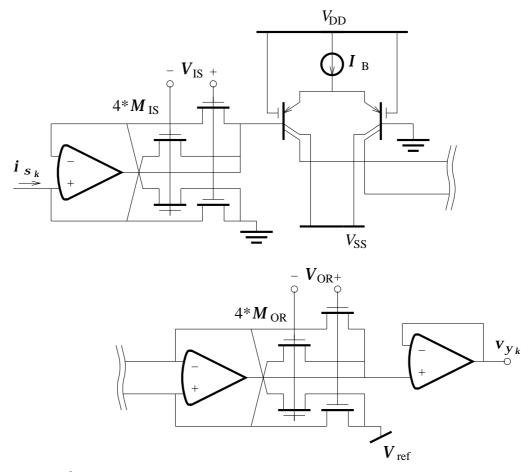

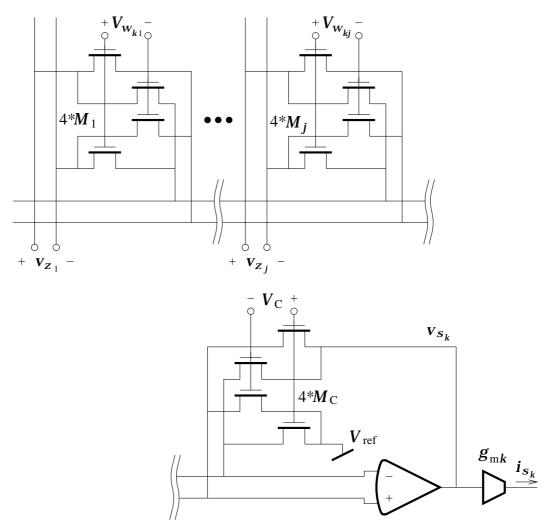

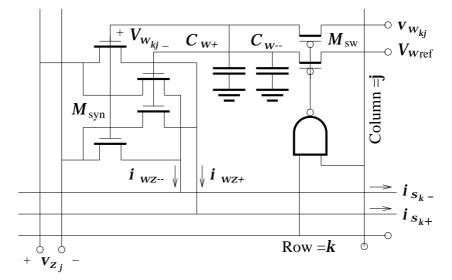

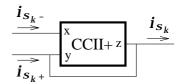

Figure 5<sup>2</sup>: Capacitive storage. Several approaches to refreshing the charge and reducing leakage (as the differential scheme shown) are possible.