#### Technical University of Denmark

#### Nano-cantilevers flully integrated with CMOS for Ultrasensitive mass detection

Forsén, Esko Sebastian; Boisen, Anja

Publication date: 2006

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Forsén, E. S., & Boisen, A. (2006). Nano-cantilevers flully integrated with CMOS for Ultrasensitive mass detection.

#### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# NANO-CANTILEVERS FULLY INTEGRATED WITH CMOS FOR ULTRASENSITIVE MASS DETECTION

Esko Forsén<sup>1</sup>

September 26th, 2005

<sup>1</sup>Department of Micro and Nanotechnology, Technical University of Denmark, Building 344, 2800 Kgs. Lyngby, Denmark

#### Supervisor:

Professor Anja Boisen Department of Micro and Nanotechnology Technical University of Denmark

#### Thesis Defence:

Wednesday December 14th 2005, 1 p.m. building 341, auditorium 22 Technical University of Denmark.

#### **Evaluation Committee:**

Professor Pietro Andreani Ørsted, Center for Physical Electronics Technical University of Denmark.

Dr. Javier Tamayo Institute of Microelectronics of Madrid, Spain.

Professor Michael Roukes Kavli Nanoscience Institute California Institute of Technology, USA.

# Preface

This thesis has been written as a part of the requirements for obtaining the Ph.D. degree at the Technical University of Denmark (DTU). The Ph.D. project has been carried out at the Department of Micro and Nanotechnology at DTU in the period from July 2002 to September 2005.

This Ph.D. project has been financed by a DTU Ph.D. grant. The work has been conducted within the Nanomass project within the BioProbe group under the supervision of:

#### Professor, Dr. Anja Boisen

I would like to thank all the persons involved in the *Nanomass*-project at CNM and UAB in Spain for their inspirative enthusiasm. I would especially like to thank Assoc. Prof. F. Pérez-Murano for all his kinds help during my visits at UAB and CNM and his patience in learning me SFM nanolithography. Assis. Prof. G. Abadal for sharing his vast experience and for his help with characterization of devices. Prof. N. Barniol, J. Verd, J. Teva, X. Borrisé, and M. Villaroya for their effort in answering every possible question regarding CMOS and other.

I would like to thank the nano-team at Lund University for which I hold the highest of respect. S. G. Nilsson for her beautiful EBL work and our many heartily discussions. P. Carlberg for his immense processing expertise and all the nightly brainstorming events at conference pubs, and Prof. L. Montelius who aided me in applying for this Ph.D.

I wish to thank Z. J. Davis, first for helping me as a new Ph.D. candidate, introducing me to all aspects of the Nanomass project, and secondly for his feedback proof reading parts of the thesis. I would like to thank R. Kougholt-Sandberg for his feedback on proof reading the thesis. S. Dohn for his help with the latex deposition experiment. A. Grigorov for the noisy-discussions. Ex. MIC D. Nilsson for our daily discussions on the øresund train which made commuting bearable. I would like to thank all the other past and present members of the BioProbe group; P. Rasmussen, R. Marie, M. Nordström, M. Holmberg, R. Matieu, W. Svendsen, M. Calleja, D. Häfliger, J. Hales, and A. Johansson for achieving a dynamic work environment with plenty of laughs. I feel that the spirit in the group is one of its kind, which is also reflected in the productivity. This spirit has been nourished by the leadership of Prof. A. Boisen, to whom I owe special thanks. First, for supervising me during my Ph.D., making me grow as a scientist by always supporting me to make my own decisions. Second, for her help during the last stage of the Ph.D., proof reading the thesis and giving valuable feedback.

I would like to take the opportunity to thank: My mother for all her support, and who managed to convince me to learn the multiplication table by heart when I started school. My father who always nourished my curiosity, showing me books on atom physics as a child.

The greatest of thanks goes to my family, Annika and Emmy. To Emmy, who was born as I was in the middle of writing this thesis, and made my perception of the world turn upside down. To Annika, who helped me during the hard times and celebrated the good. Without your love, support and encouragement this would never have been possible.

Esko Forsén

Kgs. Lyngby, September 26. 2005

# Abstract

This Ph.D. thesis deals with the development of mass sensitive silicon cantilever systems integrated with complementary metal oxide semiconductor (CMOS). The principle is based on the change in resonance frequency as mass adsorb onto the cantilever, which is measured using the signal amplification circuitry of the CMOS.

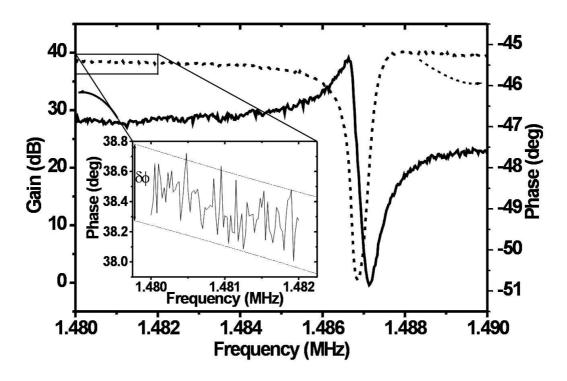

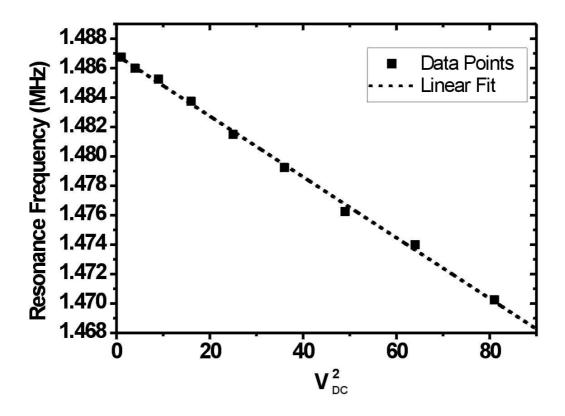

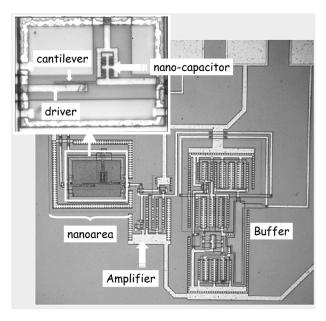

The cantilever is made to oscillate by using electrostatic actuation, and the resonance frequency is measured by capacitive readout as the cantilever oscillates in close proximity to a parallel electrode. The capacitive detection method necessitates CMOS integration due to the need to minimize the parasitic capacitance contribution, which otherwise would screen the resonance signal. The CMOS integration is achieved by adopting a post-process scheme on standard CMOS.

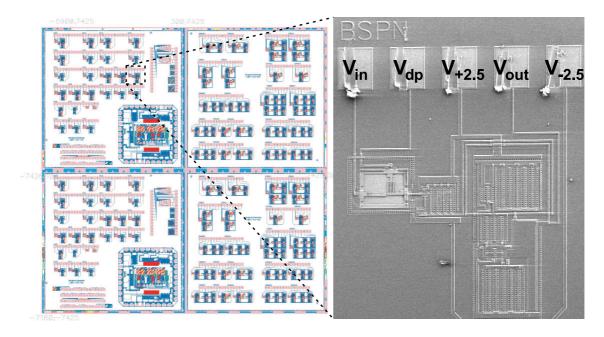

By reducing the dimensions of the cantilever to the nanometer regime, and consequently increasing the resonance frequency, an increased mass sensitivity is achieved. Hence, in order to define nanoresonators the use of lithography techniques such as electron beam lithography, scanning force microscopy based nanolithography, and direct write laser lithography have been evaluated. Resonator structures comprising of cantilevers having widths of 400 nm, a thickness of 600 nm, and a length of 20  $\mu$ m, having a resonance frequency of the order of 1.5 MHz have successfully been fabricated onto pre-processed standard CMOS. The developed post-process is directly transferable onto state-of-the-art CMOS.

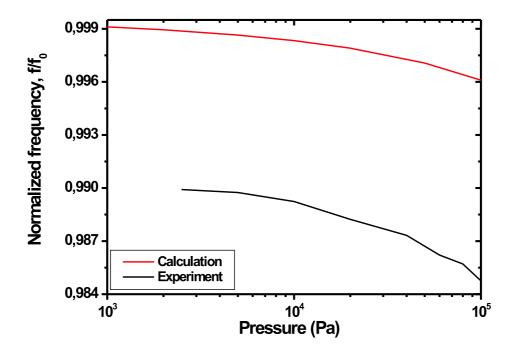

The devices have been characterized in ambient air and vacuum conditions and the mass sensitivity has been determined by adding point masses onto the cantilever. The resulting mass sensitivity is of the order of attogram  $(10^{-21} \text{ kg})$ , which is the same order of magnitude as a single medium size biomolecule such as heme.

Possible applications are found within the field of biosensors, in detection of hazardous or non-hazardous agents such as explosives, nerve gas, gas system diagnostics. Another possible application is characterization and calibration of advanced lithography systems such as atom- or molecular beam lithography systems.

# Dansk Resumé

Denne afhandling behandler udviklingern af massesensorer baseret på silicium bjælker (eng: cantilever), som er integreret med komplementerende metal-oxid-halvledere (eng: CMOS). Ændringen i silicium bjælkens resonansfrekvens forårsaget af masse adsorption detekteres af CMOS-forstærkeren.

Ved at påtrykkeen vekselspænding mellem cantileveren og en parallel elektrode, initieres cantileverens vibration. Da cantileveren vibrerer, når den er i nærheden af en elektrode-overflade, bliver der skabt en vekslende kapacitet mellem dem, som bliver detekteret af de integrerede kredse. CMOS integration er nødvendig, da dette signal er meget svagt og ville drukne i støjen skabt af ydre kapacitets-kilder. CMOS integrationen af cantilever strukturen er sket gennem mikro- og nanofabrikation efter fremstilling af de integrerede kredse.

Ved at reducere størrelsen på cantileverne til nanometer-dimensioner, og derigennem øge resonansfrekvensen, opnås en øget massefl<br/>somhed. Dermed er litografi-teknikker som elektronstrålelitografi, atom<br/>kraftsmikroskopi-baseret nanolitografi samt direkte laserlitografi undersøgt for struktureringen af nano<br/>cantilevere på standart CMOS. Cantilevere med en bredde på 400 nm, en tykkelse på 600 nm og en længde på 20 µm, som har en resonans-frekvens i størrelse<br/>sordenen 1.5 MHz er fremstillet på standart CMOS. Den udviklede fabrikationsteknik kan endog anvendes på mere avanceret CMOS teknologier.

Fremstillede strukturer er karakteriseret i luft samt vacuum og massefølsomheden er undersøgt ved at placere punktmasser på cantileveren. Derved er en massefølsomhed i størrelsesorden af et attogram ( $10^{-21}$  kg) blevet bestemt. Dette er i samme størrelsesorden som en enkelt middelstort biomolekyle.

Mulige anvendelsesområder findes indenfor biosensorindustrien, indenfor gas detektion af farlige emner som eksempelvis sprænstofer og nerve-gasser, samt diagnosticering af gassystemer. Et yderligere anvendelsesområde er karakteriseringen og kalibreringen af avancerede atom- og molekylestråle-litografisystemer.

# Svensk Resumé

Denna avhandling behandlar utvecklingen av mass-sensorer baserade på kiselresonatorer vilka är integrerade med komplementerande metalloxid-halvledare (eng: CMOS). Förändringen i kiselresonatorns resonansfrekvens orsakad av massadsorption detekteras av CMOS-förstärkaren.

Genom att applicera en växelspänning mellan resonatorn och en parallell elektrod initieras vibrationen av resonatorn. Eftersom resonatorn vibrerar nära en electrod skapas en alternerande kapacitans mellan dem, vilken detekteras av de integrerade CMOS-kretsarna. CMOS-integration är en nödvändighet eftersom den kapacitiva signalen är mycket svag och annars skulle döljas i bruset skapat av externa kapacitanskällor. CMOS-integrationen av resonatorstrukturen har skett genom mikro- och nanofabrikation efter framställningen av de integrerade CMOS-kretsarna.

Genom att reducera storleken av resonatorn till dimensioner i nanometerstorlek, och därigenom höja resonansfrekvensen, erhålls en ökad masskänslighet. Därmed har lithografi-tekniker som elektronstråle-lithografi, atomkraftsmikroskopi baserad nanolithografi samt direkt laser-lithografi undersökts för stuktureringen av nanoresonatorer på CMOS. Resonatorer med en bredd av 400 nm, en tjocklek av 600 nm och en längd av 20  $\mu$ m, som har en resonansfrekvens i storleksordningen 1.5 MHz har tillverkats på standard CMOS. Den utvecklade fabrikationstekniken kan även tillämpas på mer avancerade CMOS-teknologier.

Tillverkade strukturer har karakteriserats i luft och i vakuum och masskänsligheten har undersökt genom att placera punktmassor på resonatorn. Härigenom har en masskänslighet bestämts i storleksordningen av attogram ( $10^{-21}$  kg). Detta är i samma storleksordning som en enda medelstor biomolekyl, t.ex. hemin.

Möjliga användningsområden finns inom biosensorindustrin, inom gasdetektion av farliga ämnen som t.ex. sprängmedel och nervgaser, inom diagnostisering av gassystem. Ytterligare ett tillämpningsområde finns inom karakteriseringen och kalibreringen av avancerade atom- och molekylärstråle-lithografisystem.

# Contents

| 1        | Intr          | roduction                                 | 1               |

|----------|---------------|-------------------------------------------|-----------------|

|          | 1.1           | Cantilever Based Sensing                  | 2               |

|          |               | 1.1.1 Static System                       | 3               |

|          |               | 1.1.2 Dynamic System                      | 4               |

|          | 1.2           | CMOS integrated cantilever sensor systems | 7               |

|          |               | 1.2.1 CMOS Pre-processing                 | 7               |

|          |               | 1.2.2 CMOS Intermittent processing        | 8               |

|          |               | 1.2.3 CMOS Post-processing                | 8               |

|          |               | 1.2.4 Hybrid integration                  | 10              |

|          | 1.3           | Thesis Outline                            | 10              |

|          |               | 1.3.1 Chapters Outline                    | 11              |

| <b>2</b> | The           | e Nanomass Project                        | 13              |

|          | 2.1           | Work-Packages                             | 13              |

| 3        | The           | PORV                                      | 17              |

| U        | 3.1           | Cantilever Theory                         | 17              |

|          | 3.2           | The Quality Factor                        | 21              |

|          | 0.2           | 3.2.1 Intrinsic                           | $\frac{21}{22}$ |

|          |               | 3.2.2 Extrinsic                           | $\frac{22}{23}$ |

|          | 3.3           | Noise                                     | $\frac{20}{23}$ |

|          | 0.0           | 3.3.1 Thermomechanical Fluctuations       | 23              |

|          |               | 3.3.2 Adsorption-Desorption Processes     | $\frac{20}{25}$ |

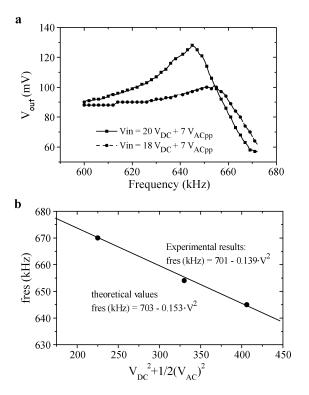

|          | 3.4           | Spring Softening                          | $\frac{20}{27}$ |

|          | 3.5           | Summary                                   | $\frac{-1}{28}$ |

|          |               | ·                                         |                 |

| 4        | $\mathbf{CM}$ | IOS Design                                | 31              |

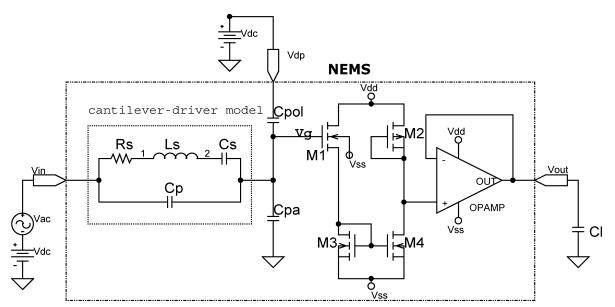

|          | 4.1           | Sensor Principle                          | 31              |

|          | 4.2           | Snap-In Voltage                           | 32              |

|          | 4.3           | Small Signal Model                        | 33              |

|          | 4.4           | Readout Circuitry                         | 37              |

|          | 4.5           | Electrical Noise                          | 38              |

|          | 4.6           | Fabrication of Standard CMOS              | 39              |

|          | 4.7           | SOI-CMOS                                  | 41              |

| <b>5</b> | $\mathbf{Litl}$        | nography 43                                                                                                                                        |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 5.1                    | Photo Lithography                                                                                                                                  |

|          | 5.2                    | Laser Lithography                                                                                                                                  |

|          |                        | 5.2.1 Instrumentation $\ldots \ldots 46$                                     |

|          |                        | 5.2.2 Laser Induced Thermal Oxidation of Al                                                                                                        |

|          |                        | 5.2.3 Laser Lithography by Ablation of Polymers                                                                                                    |

|          | 5.3                    | Scanning Probe Lithography                                                                                                                         |

|          |                        | 5.3.1 Process $\ldots \ldots 56$                        |

|          |                        | 5.3.2 SFM Nanolithography Combined with Laser Lithography 61                                                                                       |

|          | 5.4                    | Electron Beam Lithography                                                                                                                          |

|          |                        | 5.4.1 EBL Process $\ldots \ldots $ |

|          |                        | 5.4.2 EBL Combined With DWL-TA                                                                                                                     |

|          | 5.5                    | Summary                                                                                                                                            |

| 6        | $\mathbf{C}\mathbf{M}$ | OS Post-Processing 73                                                                                                                              |

|          | 6.1                    | The Post-Process                                                                                                                                   |

|          | 6.2                    | Reactive Ion Etching                                                                                                                               |

|          | 6.3                    | Stiction                                                                                                                                           |

|          |                        | 6.3.1 Freeze Drying                                                                                                                                |

|          |                        | 6.3.2 Dry Plasma Release                                                                                                                           |

|          |                        | 6.3.3 Anti-sticktion Layer                                                                                                                         |

|          | 6.4                    | CMOS Compatibility                                                                                                                                 |

|          |                        | 6.4.1 CMOS Compatibility: DWL                                                                                                                      |

|          |                        | 6.4.2 CMOS Compatibility: EBL                                                                                                                      |

|          | 6.5                    | Summary                                                                                                                                            |

| 7        | Dev                    | vice Characterization 83                                                                                                                           |

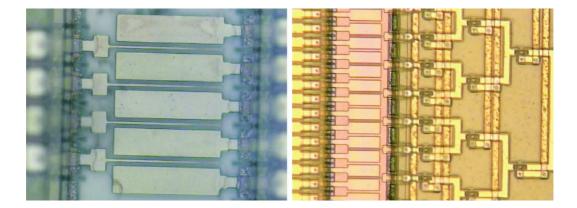

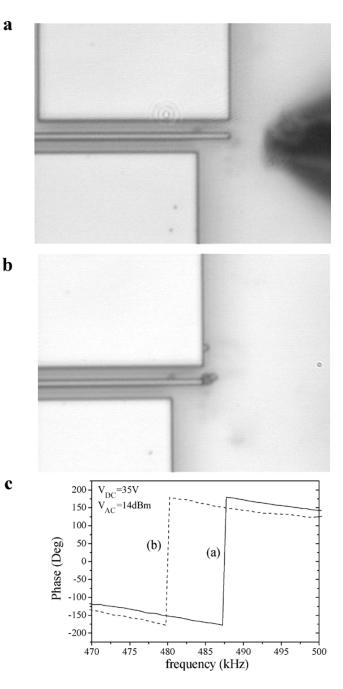

| •        | 7.1                    | Optical Verification   83                                                                                                                          |

|          | 7.2                    | Controlled Environment Chamber                                                                                                                     |

|          | 7.3                    | Measurement Instrumentation                                                                                                                        |

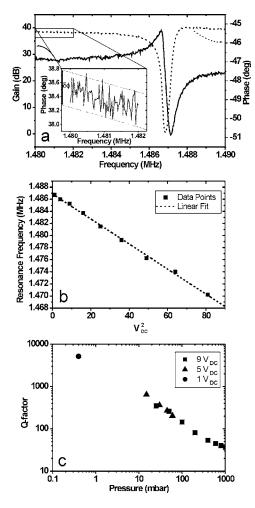

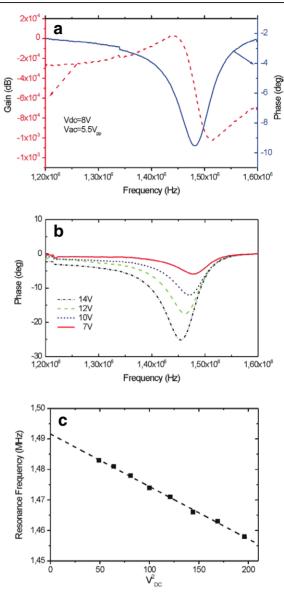

|          | 7.4                    | Single Cantilever CMOS Characterization                                                                                                            |

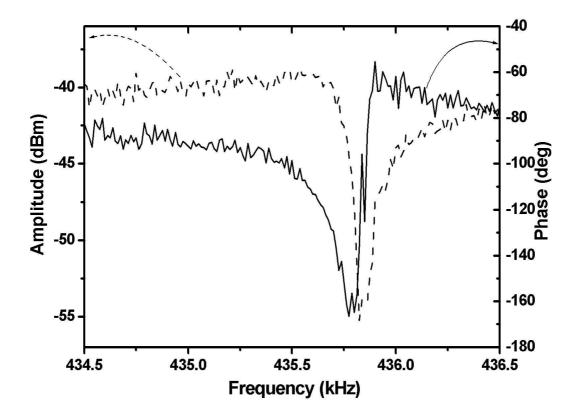

|          |                        | 7.4.1 Resonance Frequency                                                                                                                          |

|          |                        | 7.4.2 Spring Softening                                                                                                                             |

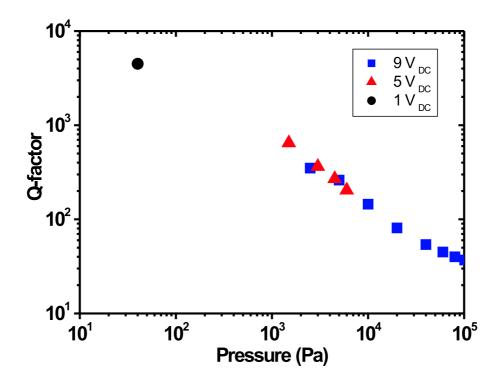

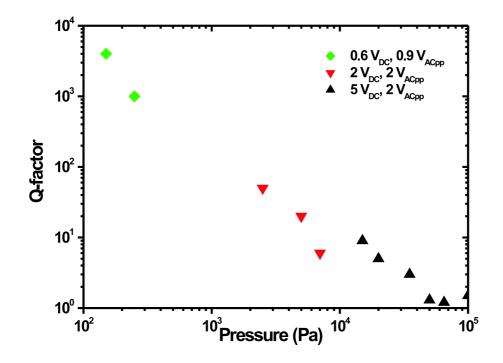

|          |                        | 7.4.3 Pressure                                                                                                                                     |

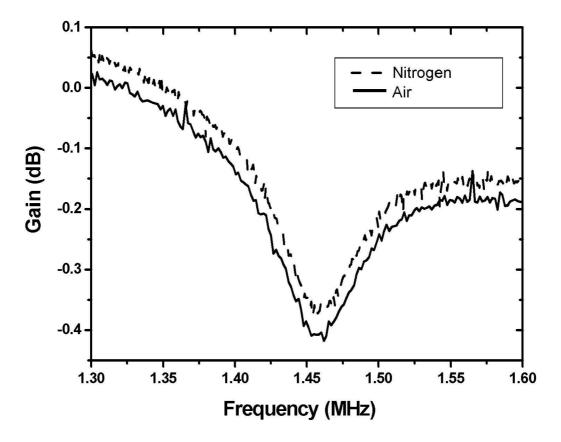

|          |                        | 7.4.4 Gas Composition                                                                                                                              |

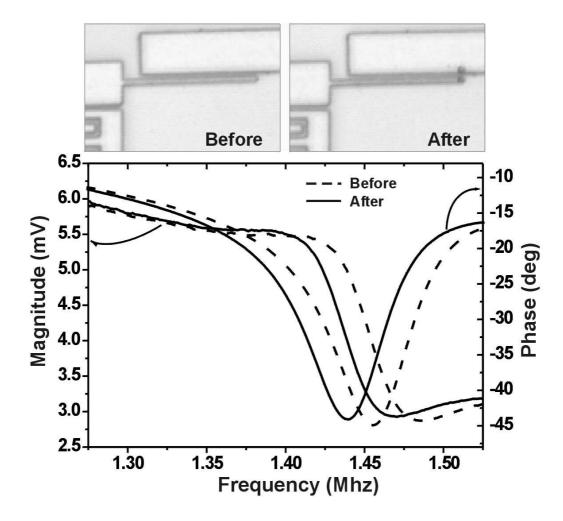

|          | 7.5                    | Cantilever Array CMOS Characterization                                                                                                             |

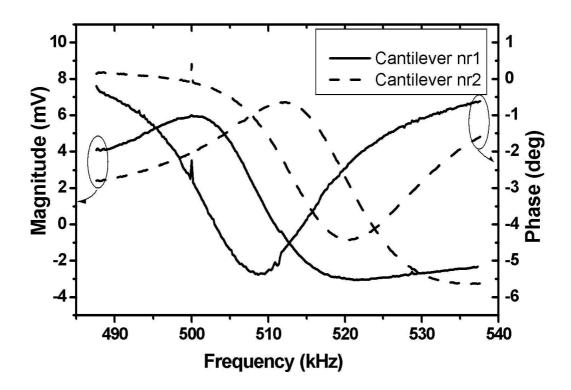

|          |                        | 7.5.1 Resonance                                                                                                                                    |

|          |                        | 7.5.2 Pressure                                                                                                                                     |

|          | 7.6                    | Mass sensitivity                                                                                                                                   |

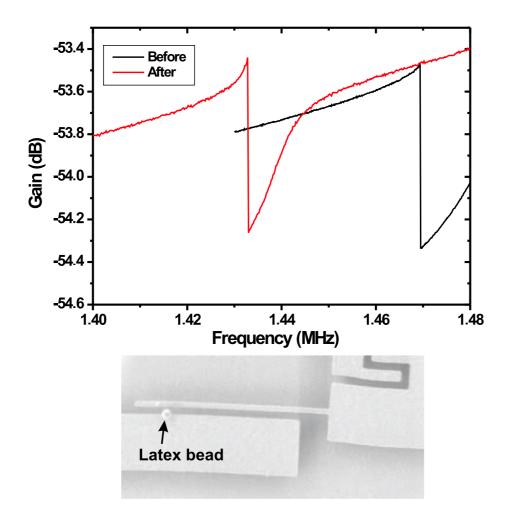

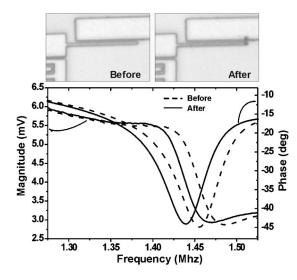

|          |                        | 7.6.1 Latex $\tilde{\text{Bead}}$                                                                                                                  |

|          |                        | 7.6.2 Glycerine Drop                                                                                                                               |

|          | 7.7                    | Noise - Ultimate Sensitivity                                                                                                                       |

|          | 7.8                    | Summary                                                                                                                                            |

|          |                        |                                                                                                                                                    |

| 9  | Publication List                                                                                                                                     | 113             |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 10 | "Ultrasensitive mass sensor fully integrated with complementary<br>metal-oxide-semiconductor circuitry"                                              | y<br>117        |

| 11 | "Design, fabrication, and characterization of a submicrometerelectromechanical resonator with monolithically integrated CMOS read-<br>out circuitry" |                 |

| 12 | "Resonators with integrated CMOS circuitry for mass sensing ap<br>plications, fabricated by electron beam lithography"                               | -<br>135        |

| 13 | "Fabrication of cantilever based mass sensors integrated with CMOS<br>using direct write laser lithography on resist"                                | $\frac{5}{141}$ |

| 14 | "Dry release of suspended nanostructures"                                                                                                            | 149             |

| 15 | "Laser lithography on resist bi-layer for nanoelectromechanical systems prototyping"                                                                 | -<br>155        |

| 16 | CMOS Post-Process Sequence                                                                                                                           | 161             |

| 17 | Freeze Drying                                                                                                                                        | 163             |

| 18 | Plasma Release                                                                                                                                       | 165             |

# List of Figures

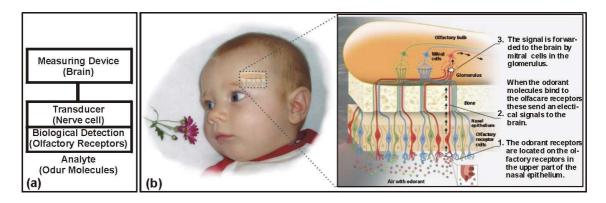

| Schematic representation of a sensor                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

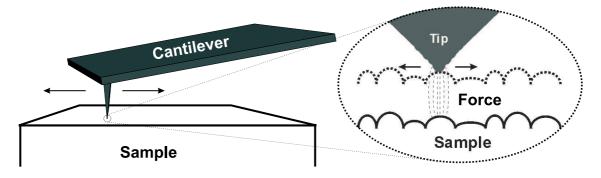

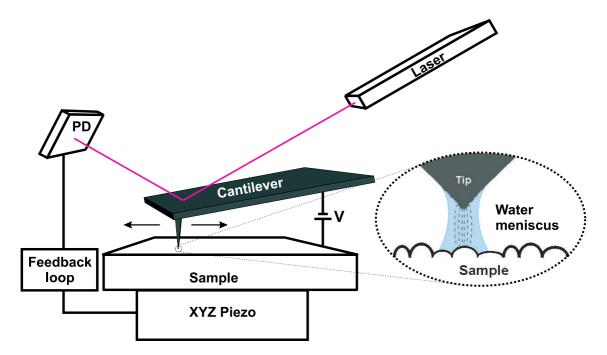

| Illustration of SFM                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

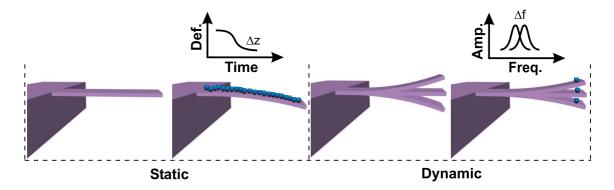

| Schematic representation of static and dynamic cantilever sensor           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

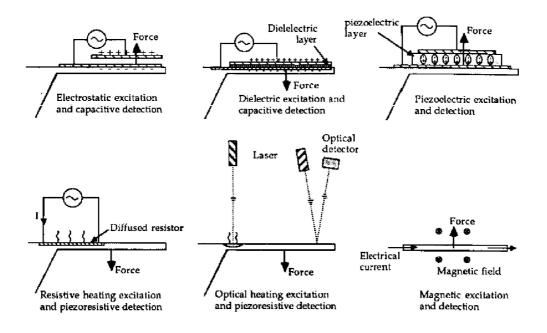

| Schematic representation of dynamic cantilever actuation and read-out      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| principles                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

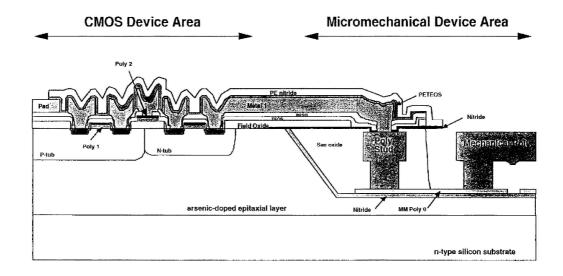

| Cross sectional illustration of the $MM/CMOS$ process                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

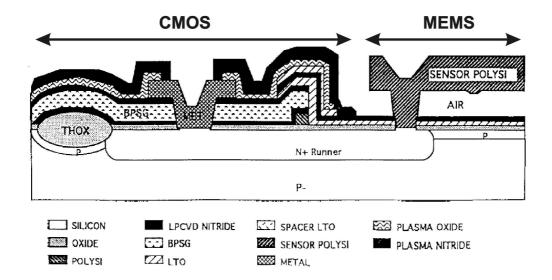

| Cross sectional illustration of a BiMEMS system by Analog devices          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

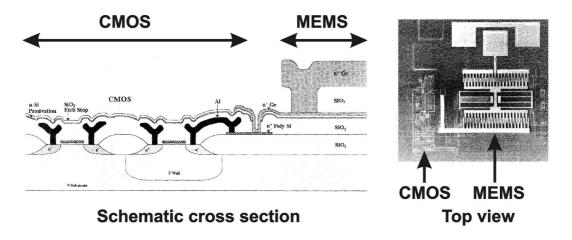

| Cross sectional illustration of modular CMOS integration                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

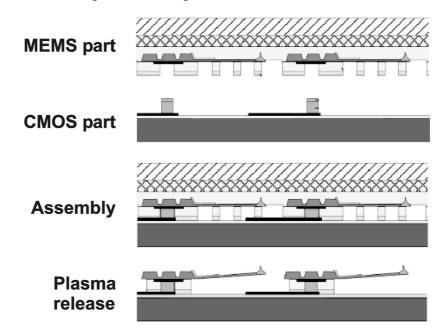

| IBM Millipede flip-chip process flowchart of the basic cantilever-transfer |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| processing steps.                                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Schematic illustration of the SoC principle of the Nanomass II project.    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

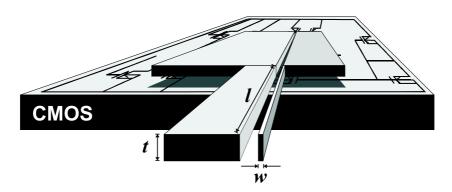

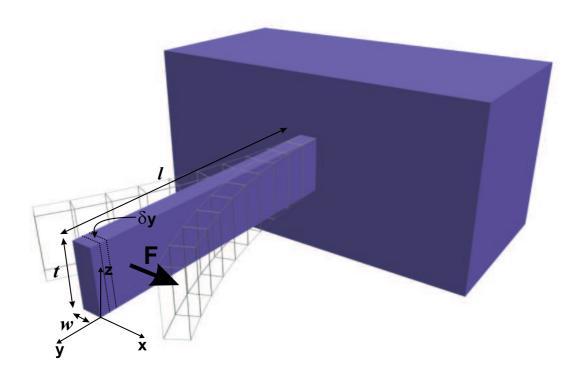

| Schematic illustration of cantilever system                                | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

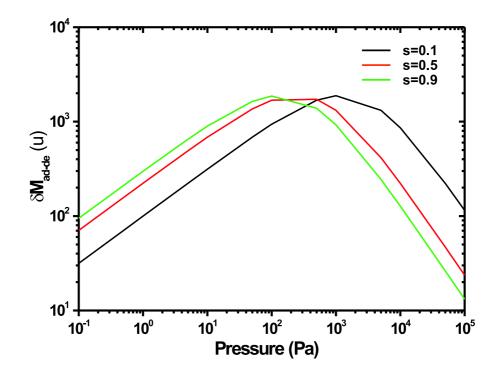

|                                                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

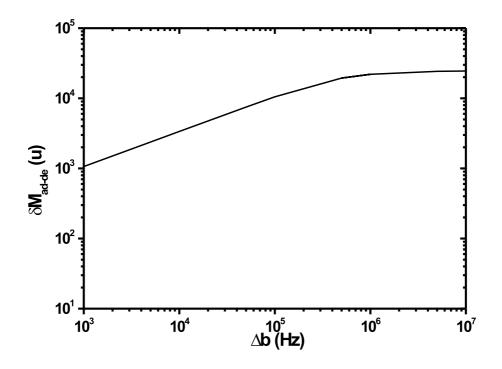

|                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| desorption noise processes as function of the measurement bandwidth.       | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

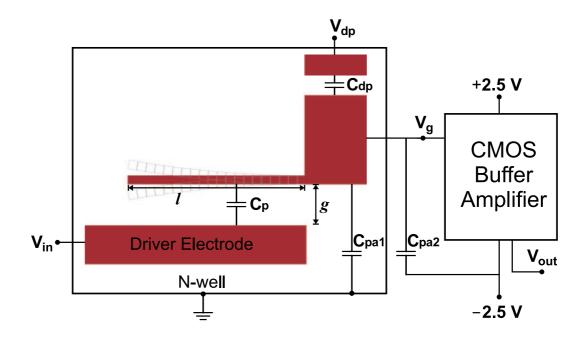

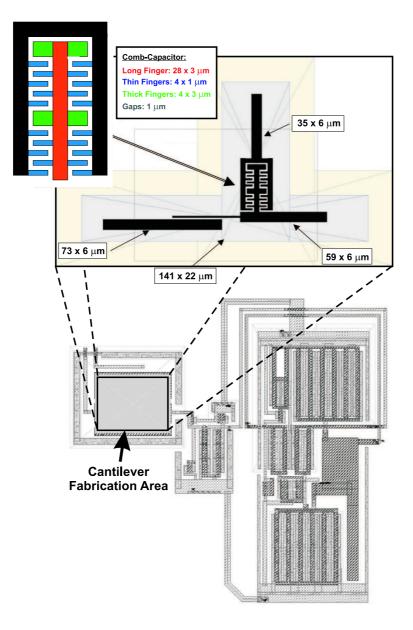

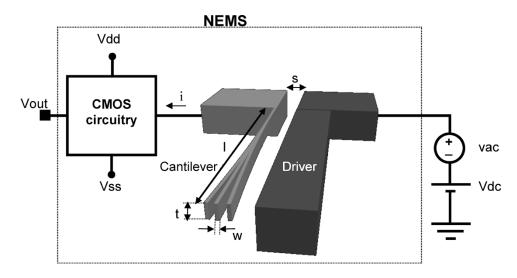

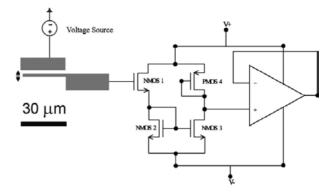

| Schematic illustration of the resonator actuation and read-out system      | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                            | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

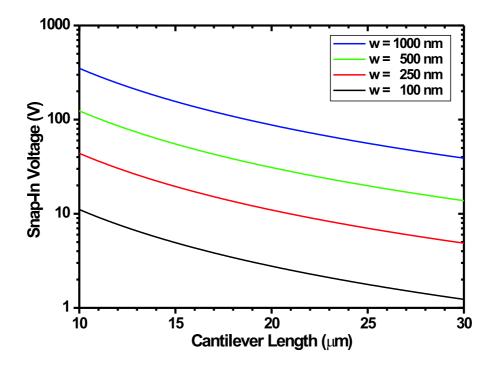

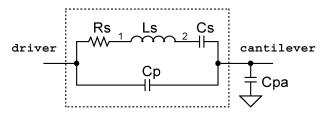

|                                                                            | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                            | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

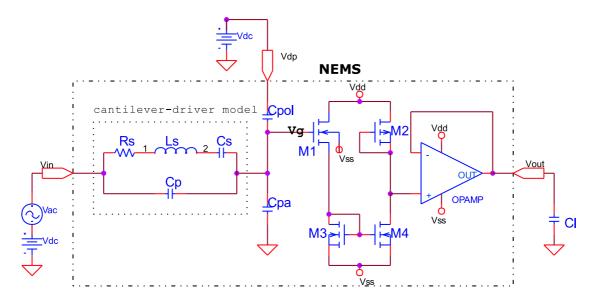

|                                                                            | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

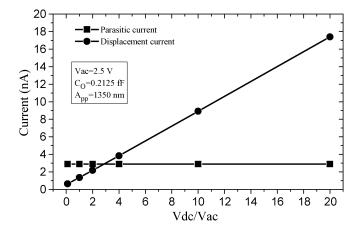

|                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

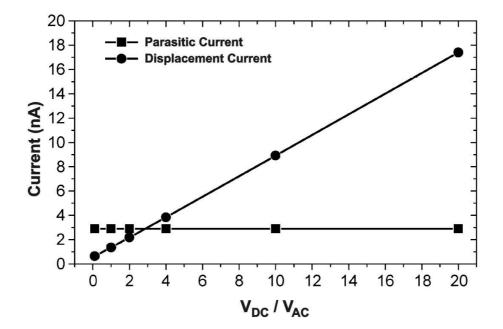

| $I_{pa}$ as a function of the ratio $\frac{V_{DC}}{V}$                     | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

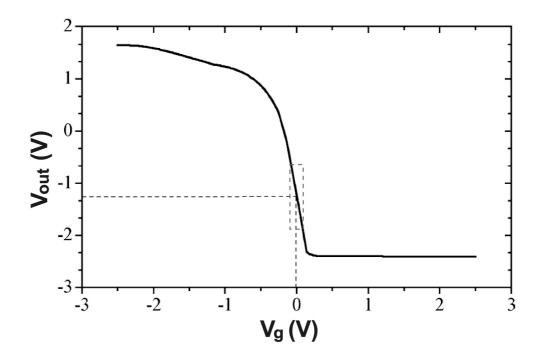

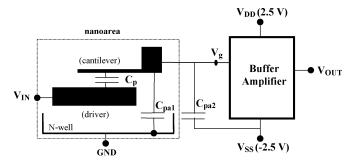

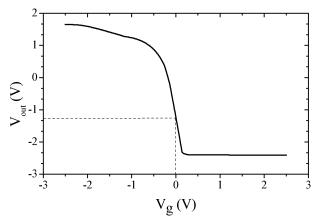

| Graphs showing the optimal operation regime for $V_a$                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                            | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

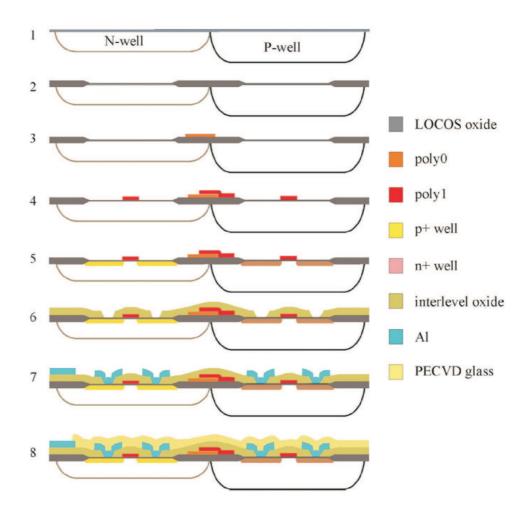

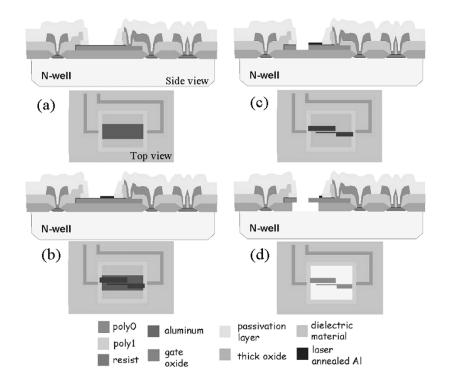

| Schematic description of the CNM CMOS25 process                            | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

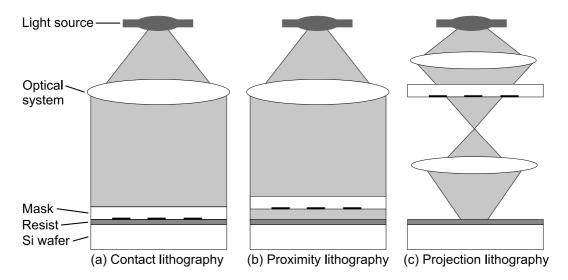

| Schematic illustration of contact provimity and projection lithography     | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

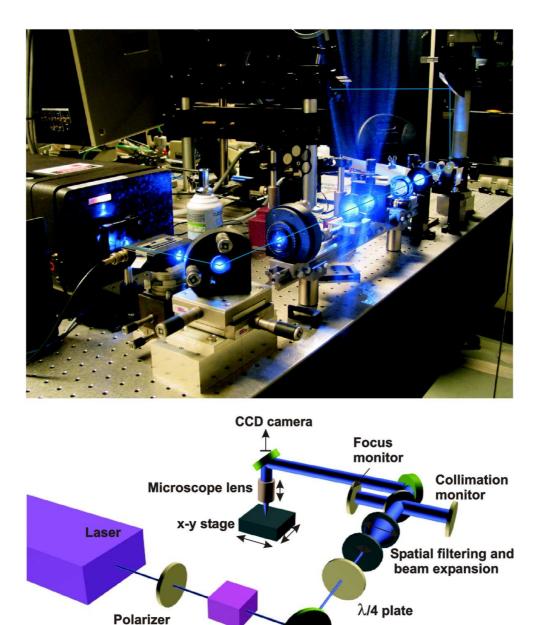

|                                                                            | 44<br>47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                            | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

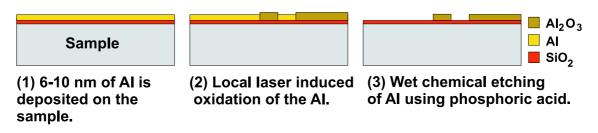

| -                                                                          | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| - •                                                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| on CMOS.                                                                   | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                            | Illustration of SFMSchematic representation of static and dynamic cantilever sensorSchematic representation of dynamic cantilever actuation and read-outprinciplesCross sectional illustration of the MM/CMOS process.Cross sectional illustration of a BiMEMS system by Analog devices.Cross sectional illustration of modular CMOS integration.IBM Millipede flip-chip process flowchart of the basic cantilever-transferprocessing steps.Schematic illustration of the SoC principle of the Nanomass II project.Schematic illustration of cantilever systemGraph showing the calculated minimum detectable mass due to adsorption-<br>desorption noise processes as function of pressure.Graph showing the calculated minimum detectable mass due to adsorption-<br>desorption noise processes as function of the measurement bandwidth.Schematic illustration of the resonator actuation and read-out system.Graph of the calculated snap-in voltage $V_{si}$ for various cantilever di-<br>mensions.Graph showing the displacement current $I_d$ and the parasitic current $I_{pa}$ as a function of the ratio $\frac{V_{PC}}{V_{AC}}$ .Graph showing the optimal operation regime for $V_g$ .Schematic illustration of the CNM CMOS25 process.Schematic illustration of contact-, proximity-, and projection lithographyIllustration of the used Laser Lithography set-up.Schematic illustration of the process flow of Direct Write Laser lithog-<br> |

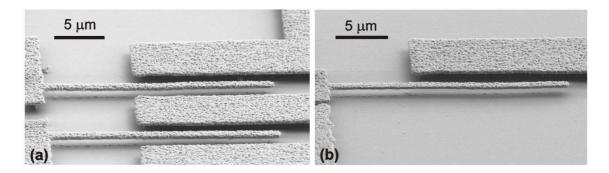

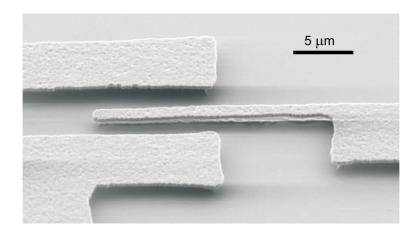

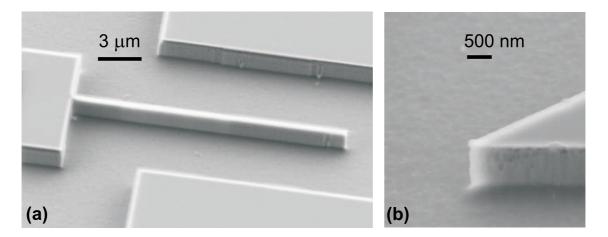

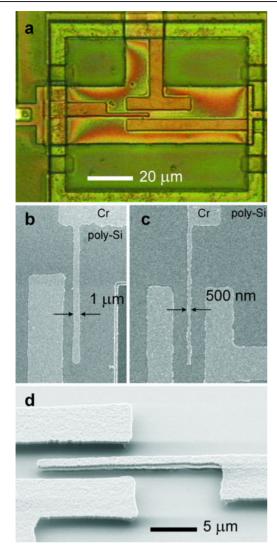

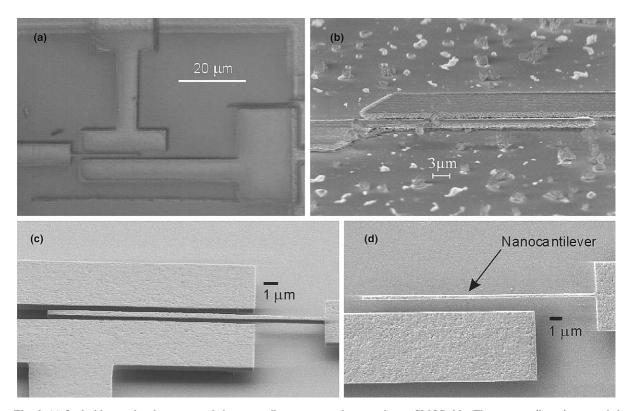

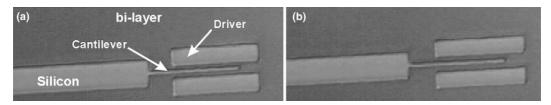

| 5.5        | $\operatorname{SEM}$ images of fully processed cantilevers defined by DWL-TO on CMOS. | 50       |

|------------|---------------------------------------------------------------------------------------|----------|

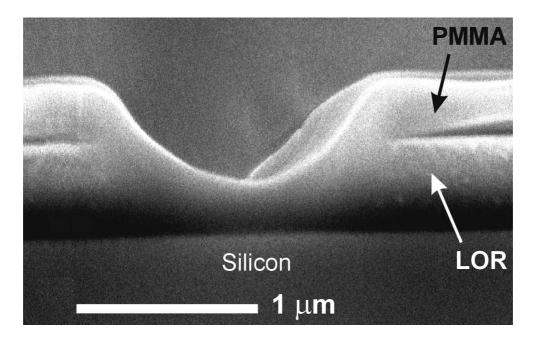

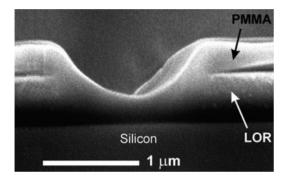

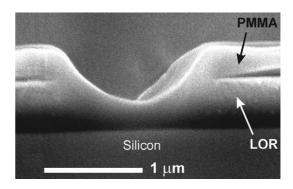

| 5.6        | SEM image of a cross-section of PMMA/LOR bilayer on Si after laser                    |          |

|            | ablation.                                                                             | 51       |

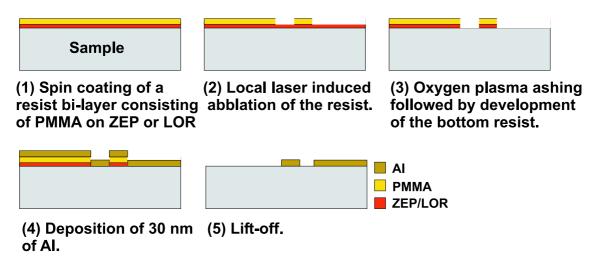

| 5.7        | Schematic illustration of the process flow of Direct Write Laser lithog-              | ~ 4      |

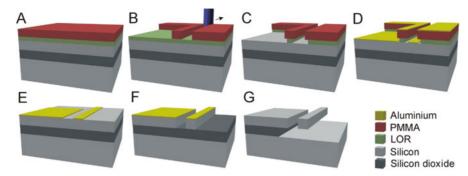

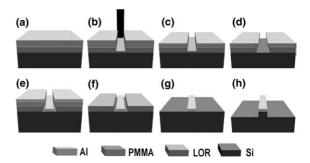

| <b>F</b> 0 | raphy based on ablation of thin polymer films.                                        | 51       |

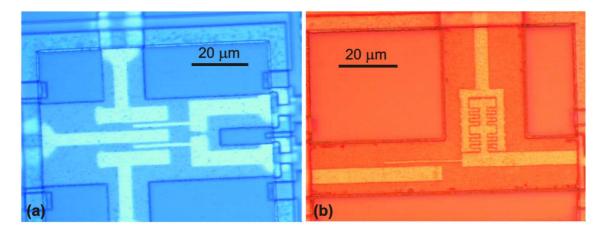

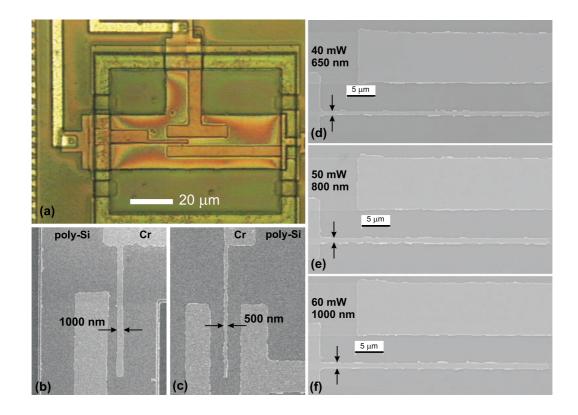

| 5.8        | Images of Al cantilever mask patters defined by DWL-TA on CMOS.                       | 54       |

| 5.9        | SEM image of a fully processed poly-Si cantilever defined by DWL-TO                   | F 4      |

| F 10       | on CMOS.                                                                              | 54       |

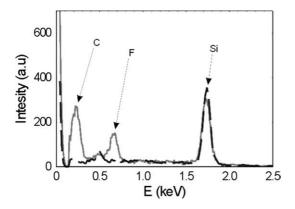

| 5.10       |                                                                                       | 55<br>57 |

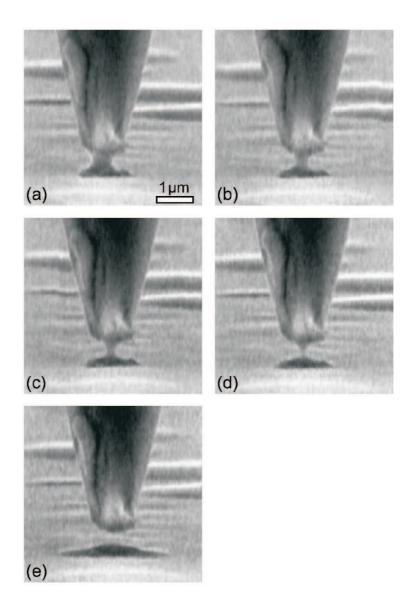

|            | Time-resolved ESEM images of water meniscus formation                                 | 97       |

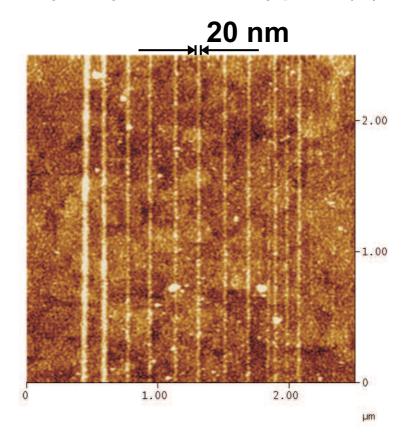

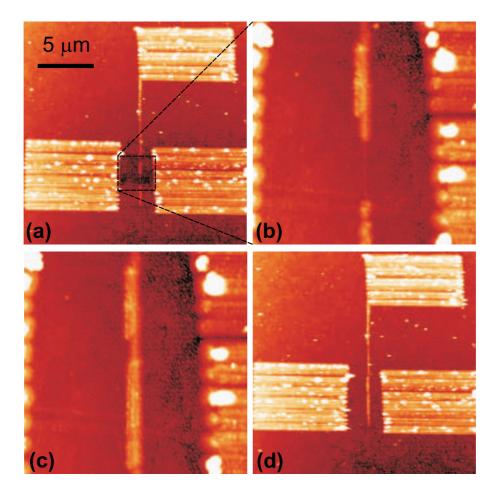

| 0.12       | SFM image of 20 nm oxide lines defined in Al on SOI using SFM nanolithography.        | 58       |

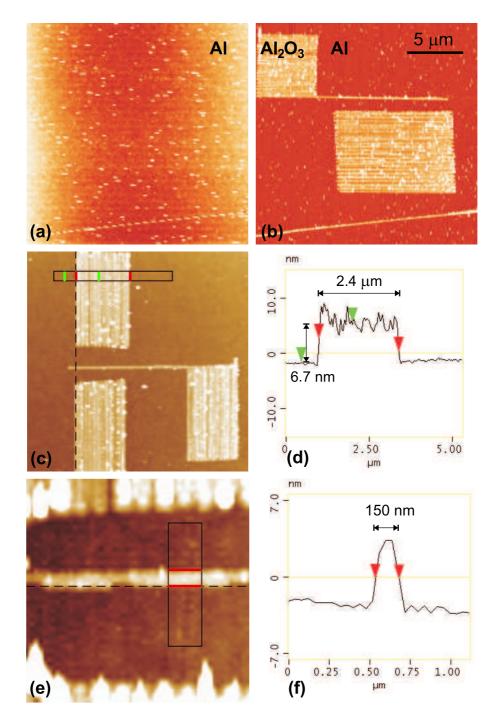

| 5 1 3      | SFM images of resonator patterns defined in 6 nm Al on SOI using                      | 90       |

| 0.10       | SFM nanolithography                                                                   | 59       |

| 5.14       | SFM images visualizing the image and repair flexility of SFM nano-                    | 00       |

| 0.11       | lithography.                                                                          | 60       |

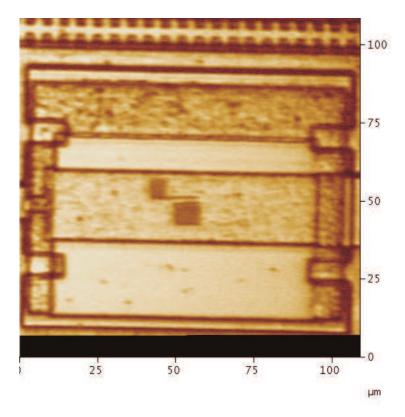

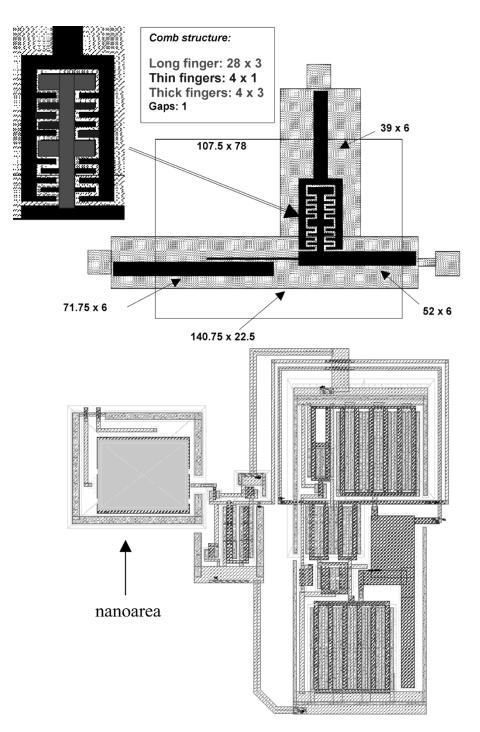

| 5.15       | Optical image of a cantilever structure defined on standard CMOS as                   |          |

|            | obtained with the CCD of the SFM system.                                              | 61       |

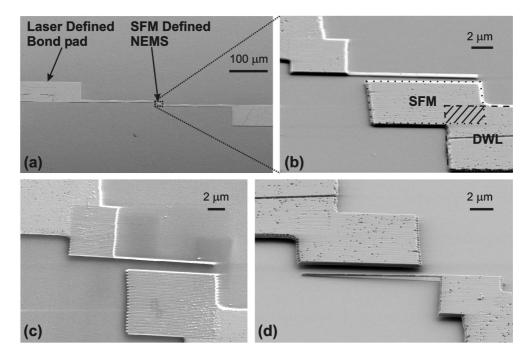

| 5.16       | SEM images of a NEMS resonator device defined by a combination of                     |          |

|            | SFM nanolithography and direct write laser lithography on SOI                         | 62       |

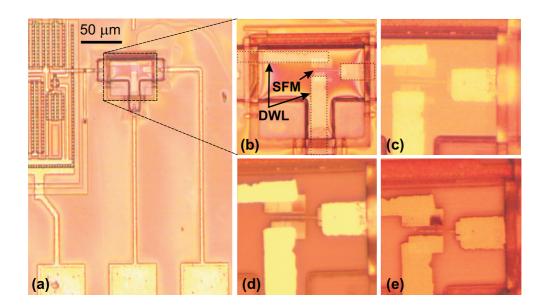

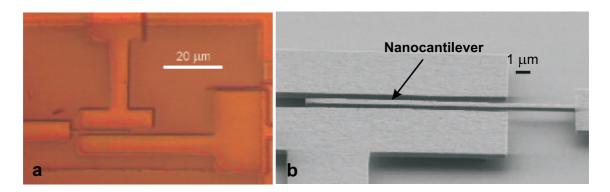

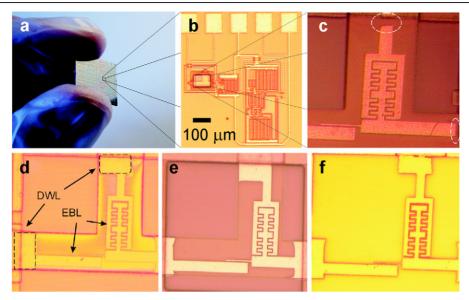

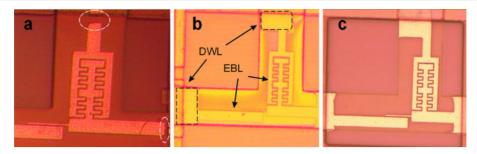

| 5.17       | Optical images of a NEMS resonator device defined by a combination of                 |          |

|            | SFM nanolithography and direct write laser lithography on SOI-CMOS.                   | 63       |

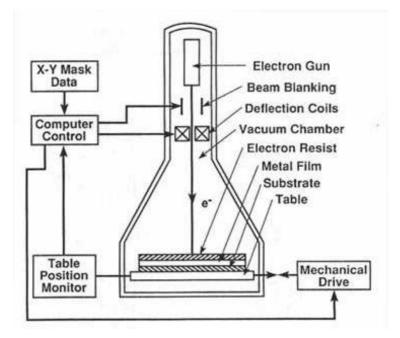

| 5.18       | Schematic illustration of the main constituents of an EBL and system.                 | 64       |

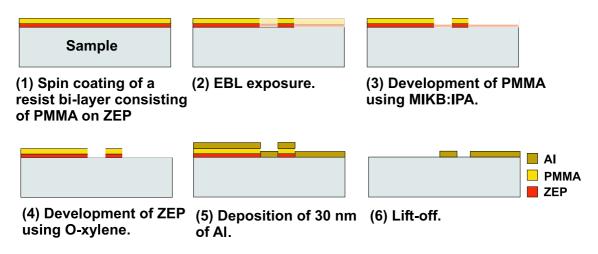

| 5.19       | Schematic illustration of the Electron Beam Lithography process used.                 | 65       |

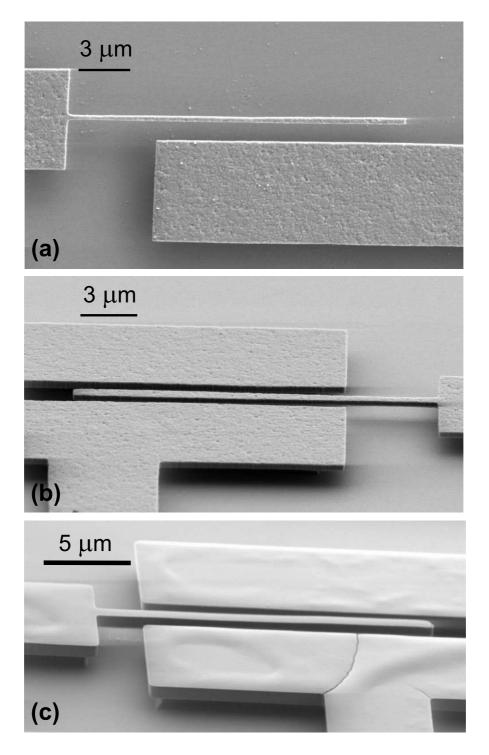

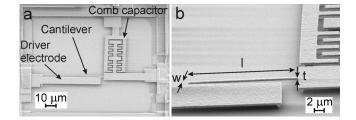

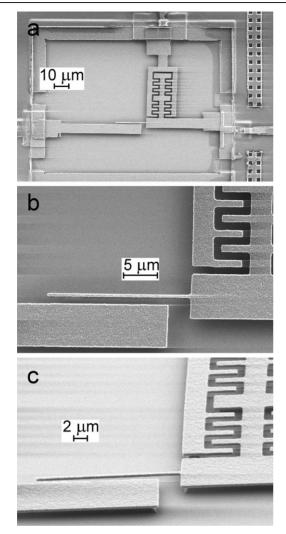

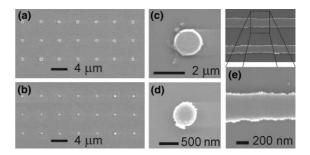

| 5.20       | SEM images of NEMS resonators defined by EBL $(35 \text{ kV})$ on CMOS.               | 67       |

| 5.21       | SEM images of NEMS resonators defined by 3 kV EBL on standard                         |          |

|            | CMOS                                                                                  | 68       |

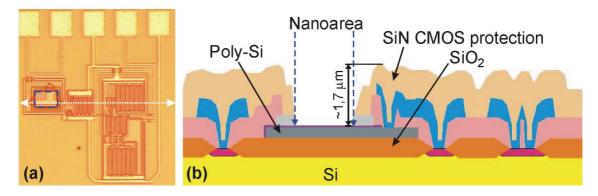

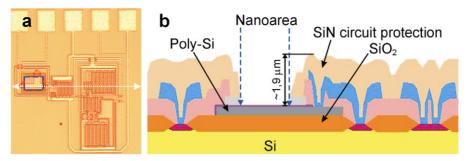

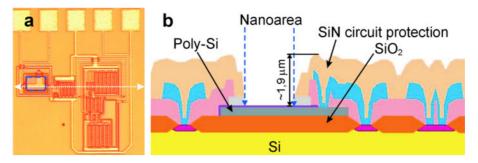

|            | Schematic illustration of the cross section of the nanoarea                           | 69       |

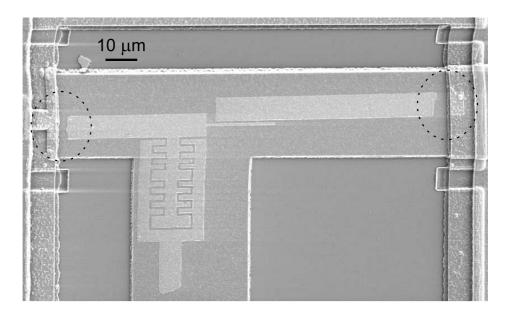

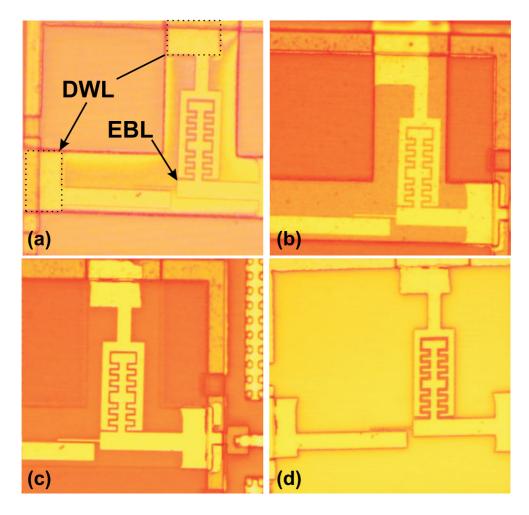

| 5.23       | Optical images of cantilevers defined by EBL combined with DWL-TA.                    | 71       |

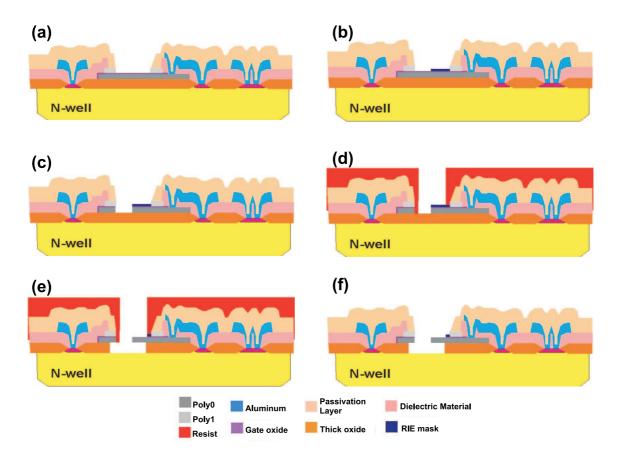

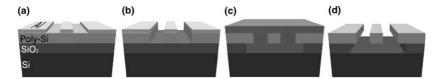

| 6.1        | Schematic illustration of post-process steps.                                         | 74       |

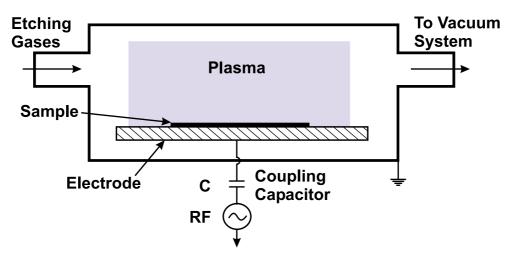

| 6.2        | Illustration of a basic RIE system                                                    | 75       |

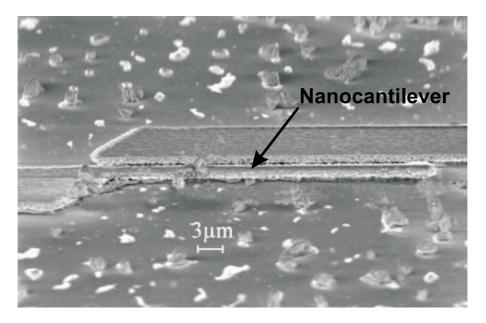

| 6.3        | SEM images of resonator structures after anisotropic RIE                              | 76       |

| 6.4        | SEM image of contaminations caused by Tert-Butanol release                            | 77       |

| 6.5        | Results of dry plasma release.                                                        | 78       |

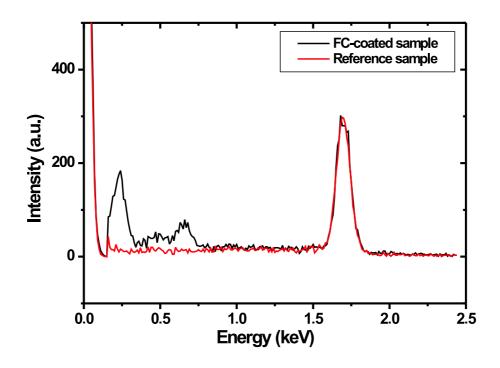

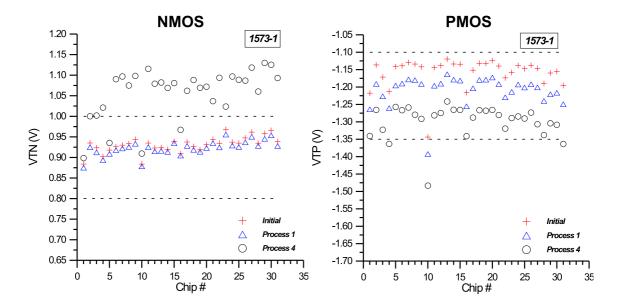

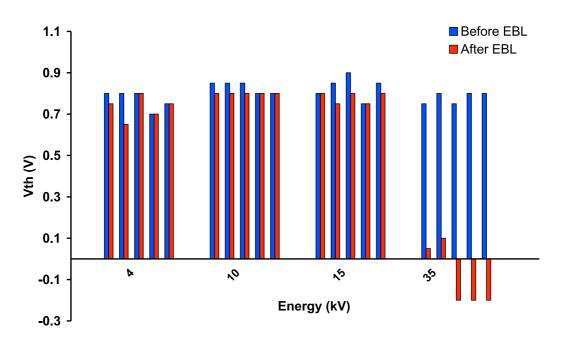

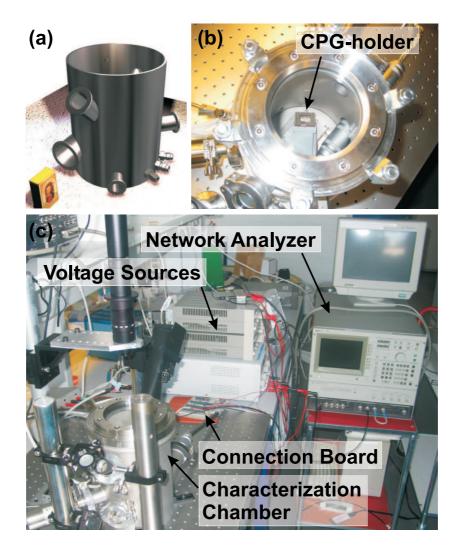

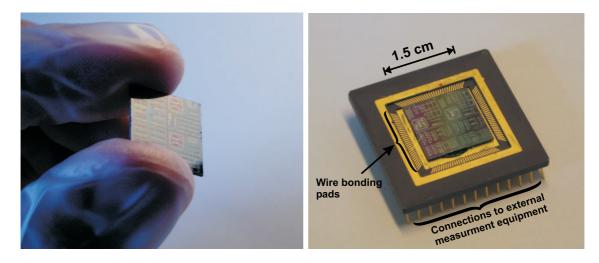

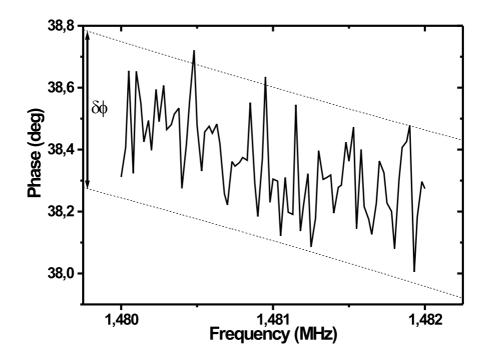

| 6.6        | noise                                                                                 | 79       |