#### Technical University of Denmark

## Single Conversion stage AMplifier - SICAM

Ljusev, Petar; Andersen, Michael A. E.

Publication date: 2006

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Ljusev, P., & Andersen, M. A. E. (2006). Single Conversion stage Amplifier - SICAM.

## DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Petar Ljušev

# SIngle Conversion stage AMplifier - SICAM

PhD thesis, December 2005

To Elena and Emma, for their endless love and devotion

## **Preface**

The work presented in this thesis is part of the project "SICAM - SIngle Conversion stage AMplifier", funded by the Danish Energy Authority under the EFP2002 program, J.nr. 1273/02-0001. The project was carried out at the Ørsted·DTU Automation department within its Power Electronics Group (PEG) during the period November  $15^{th}$  2002 to December  $31^{st}$  2005. On the industry side, the cooperation with Bang & Olufsen ICE-power a/s in Kgs. Lyngby has given additional quality to the project, by emphasizing its relevance and importance within the extremely "crowded" consumer audio market.

Part of the work concerning the direct audio power amplifiers for portable applications and their digital modulators was conducted during my 1,5 months long external research stay in the Laboratory for Low Power Management and Integrated SMPS at the University of Toronto in Canada, under the supervision of Professor Aleksandar Prodić.

First I would like to express deepest gratitude to my supervisor Professor Michael A.E. Andersen for taking me as his Ph.D. student to work on this highly interesting topic, providing unbounded support for my wide research interests, managing the practical issues about the demanding project, as well as spending lots of hours on fruitful discussions and sharing his vast knowledge. Together with the colleagues from the Power Electronics Group and the Ørsted·DTU Department, they are most responsible for making me feel so comfortable and secure.

The practical relevance and technical appeal of the project would be much less pronounced, if it was not for the tremendous effort shown by my second supervisor Lars Petersen, from the cooperating company Bang & Olufsen ICEpower. His curious remarks and on-place questions have always provoked me to rejudge the conclusions and find a way out of the large maze I was put into when undertaking this project. The enthusiastic B&O ICEpower employees showing me around the labs and attending my presentations helped me build a serious approach so needed when tackling such a relevant subject.

Another thanks goes to my external research supervisor Professor Aleksandar Prodić from the University of Toronto, for allowing me to spend a challenging few weeks in his "fully digital world" and sharing his ideas and opinions, making the time spent in Toronto an unforgettable experience.

During these three stressful years of hard work, tight schedules and numerous obligations, I have always found a peaceful shelter and source of endless joy and fulfilment in my closest family - my wife Elena and our little daughter Emma. I would like to thank you for being always by my side and showing me that the most important things in life cannot be represented by equations, expressed in numbers nor measured in physical units...

Kongens Lyngby Petar Ljušev

### Abstract

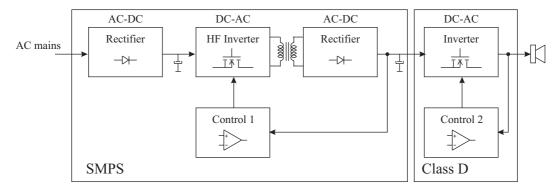

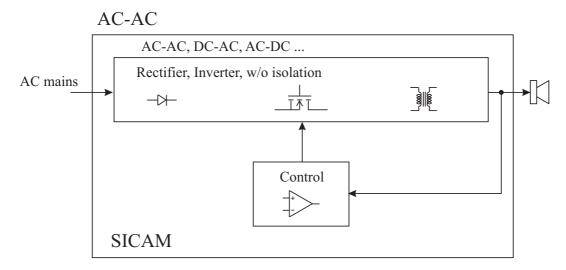

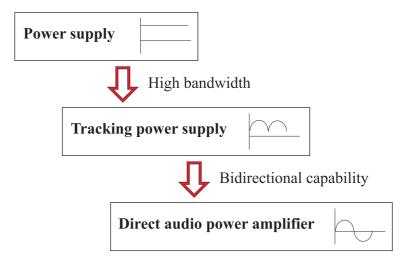

This Ph.D. thesis presents a thorough analysis of the so called SICAM - SIngle Converter stage AMplifier approach to building direct energy conversion audio power amplifiers. The mainstream approach for building isolated audio power amplifiers today consists of isolated DC power supply and Class D amplifier, which essentially represents a two stage solution, where each of the components can be viewed as separate and independent part. The proposed SICAM solution strives for direct energy conversion from the mains to the audio output, by dedicating the operation of the components one to another and integrating their functions, so that the final audio power amplifier represents a single-stage topology with higher efficiency, lower volume, less board space, lower component count and subsequently lower cost.

The SICAM approach is both applicable to non-isolated and isolated audio power amplifiers, but the problems encountered in these two cases are different. Non-isolated SICAM solutions are intended for both AC mains-connected and battery-powered devices. In non-isolated mains-connected SICAMs the main idea is to simplify the power supply or even provide integrated power factor correction (PFC) functions, while still maintaining low component stress and good audio performance by generally decreasing the input voltage level to the Class D audio power amplifier. On the other hand, non-isolated battery-powered SICAMs have to cope with the ever changing battery voltage and provide output voltage levels which are both lower and higher than the battery voltage, while still being simple and single-stage energy conversion solutions. In isolated SICAMs the isolation transformer adjusts the voltage level on the secondary side to the desired level, so the main challenges here are decreasing the size of the magnetic core and reducing the number and size of bulky reactive components as much as possible.

The main focus of this thesis is directed towards the isolated SICAMs and especially the so called isolated SICAM with non-modulated transformer voltages. The latter is found to be the most interesting isolated SICAM solution for the modern multichannel audio power amplification systems, since all of the output stages corresponding to the different audio channels can reuse the same input stage and transformer core. While the proposed approach tends to be very simple from topological perspective and allows for reduction of reactive component count, the commutation of the load current in the output bridge and the bridge itself are much more complicated than their Class D predecessors.

The main contribution of the thesis can be found in the thorough analysis of the present topologies for isolated SICAMs, as well as the numerous structural improvements and several newly proposed control methods for alleviating the problem of load current commutation and high-performance control of the whole SICAM. Another significant contribution is the presentation of several interesting topologies and associated control principles in the field of non-isolated SICAMs for mains-connected and portable audio amplifiers.

# Resumè (Abstract in Danish)

Denne Ph.D. afhandling giver en grundig analyse af den så kaldte SICAM - SIngle Converter stage AMplifier fremgangsmåde til opbygning af audio effektforstærkere til direkt energiomforming. Den aktuelle fremgangsmåde til opbygning af isolerede audio effektforstærkere i dag består af en isoleret DC elforsyning efterfulgt af en Klasse D audio effektforstærker, som faktisk repræsenterer to-trins løsning, hvor hver halvdel kan ses som seperat og uafhengig del. Den foreslåede SICAM-løsning stræber efter så direkte energiomforming fra lysnetindgangen til audioudgangen som overhovedet muligt, ved at dedikere virkningsmåden af delene til hinanden og integrere deres funktioner således, at den endelige audio effektforstærker repræsentere en en-trins topologi med højere effektivitet, mindre volumen, mindre printareal, færre komponenter og dermed lavere omkostninger.

SICAM fremgangsmåden kan bruges til både uisolerede og isolerede audio effektforstærkere, men problemstillingerne som i de to tilfælde er i grunden meget forskellige. Uisolerede SICAMs anvendes til både lysnettilsluttede og batteridrevne apparater. Hovedideen i de uisolerede lysnettilsluttede SICAMs er at forenkle spændingsforsyningen og lave PFC-funktion, mens det lav komponentstress og den god audioperformance bevares ved at reducere indgangsspændingen til Klasse D forstærkeren. Uisolerede batteridrevne SICAMs skal klare den varierende batterispænding og skabe en udgangsspænding, som er både lavere og højere end batterispænding, men de skal stadigvæk være simple og en entrins energiomformer. I transformatoren i isolerede SICAMs designes spændingsniveauet på sekundæren til det ønskede niveau og derfor er de vigtigste udfordringer her at reducere volumen af den magnetiske kerne og reducere antallet af reaktive komponenter så meget som muligt.

Hovedfokus i denne afhandling ligger på isolerede SICAMs og især de såkaldte isolerede SICAM med umodulerede transformatorspændinger. Den ovennævnte omformer er den mest interessante SICAM-løsning til multikanalens audio effektforstærkersystemer, fordi alle udgangstrinnene kan bruge det samme indgangstrin og den samme transformatorkerne. Den foreslåede løsning er meget enkelt fra en topologiside og tillader reduktion af antalet of reaktive komponenter på sekundærsiden, men kommuteringen af belastningsstrømmen i udgangstrinnet og udgangstrinnets ombygning selv er mere indviklet end i Klasse D forstærkeren.

Afhandlingens hovedbidrag findes i den grundige analyse af nuværende topologier for isolerede SICAMs, såvel som flere strukturele forbedringer og nogle foreslåede kontrol metoder til at forbedre kommuteringen af belastningsstrømmen i udgangstrinnet og realisere højperformance styring af hele SICAM-trinnet. Det anden væsentlige bidrag er fremvisningen af adskillige interessanter topologier og deres styrestrategier til uisolerede SICAMs til lysnettilslutning og brbare audio effektforstærkere.

# Contents

| 1        | 1.1<br>1.2<br>1.3<br>1.4 | Linear audio power amplifiers  Switching-mode audio power amplifiers  SICAM project and problem definition  Need for energy storage on a single-phase AC-mains  Thesis outline | 15<br>15<br>17<br>20<br>22<br>24 |

|----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Pa       | rt I                     | Non-isolated SICAMs                                                                                                                                                            |                                  |

| <b>2</b> | Ma                       | trix SICAM                                                                                                                                                                     | 27                               |

|          | 2.1                      | Matrix converters                                                                                                                                                              | 27                               |

|          | 2.2                      | Single-phase AC to single-phase AC matrix converter                                                                                                                            | 29                               |

|          |                          | Two-phase AC to single-phase AC matrix converter                                                                                                                               | 31                               |

|          |                          | 2.3.1 2ph-AC to 1ph-AC matrix converter without a central tap                                                                                                                  | 33                               |

|          |                          | 2.3.2 2ph-AC to 1ph-AC matrix converter with fixed central tap                                                                                                                 | 34                               |

|          |                          | 2.3.3 2ph-AC to 1ph-AC matrix converter with switched central tap                                                                                                              | 35                               |

|          |                          | 2.3.4 Switching strategies for 2ph-AC to 1ph-AC matrix converter with                                                                                                          |                                  |

|          |                          | switched central tap                                                                                                                                                           | 37                               |

|          |                          | 2.3.5 Obtaining another phase- lagging/leading voltage from AC-mains                                                                                                           | 42                               |

|          | 2.4                      | Matrix SICAM with <i>LC</i> -network                                                                                                                                           | 46                               |

|          |                          | 2.4.1 Analysis of matrix SICAM switching between $L  R $ and $C  R $                                                                                                           | 47                               |

|          |                          | 2.4.2 Time domain analysis of the two load combinations                                                                                                                        | 51                               |

|          |                          | 2.4.3 HF switching of matrix SICAM for constructing the audio waveform.                                                                                                        | 52                               |

|          |                          | 2.4.4 Design of matrix SICAM with resonant <i>LC</i> -network                                                                                                                  | 53                               |

|          |                          | 2.4.5 Design example of matrix SICAM with resonant <i>LC</i> -network                                                                                                          | 56<br>57                         |

|          |                          | 2.4.6 Influence of the output low-pass filter $L_f, C_f$                                                                                                                       | 57<br>58                         |

|          |                          | 2.4.8 Simulations of matrix SICAM with <i>LC</i> -network                                                                                                                      | 63                               |

|          | 2.5                      | Conclusion about matrix SICAMs                                                                                                                                                 | 64                               |

| 3        | AC                       | -mains connected Class D audio power amplifiers as SICAMs                                                                                                                      | 71                               |

|          | 3.1                      | Non-isolated DC power supply                                                                                                                                                   | 71                               |

|          | 3.2                      | Class D audio power amplifier with non-isolated DC power supply                                                                                                                | 73                               |

|          | 3.3                      | 1 1                                                                                                                                                                            | 75                               |

|          | 3.4                      | 1                                                                                                                                                                              | 76                               |

|          |                          | 3.4.1 Combined Class D audio power amplifier and boost PFC                                                                                                                     | 78                               |

|          |                          | 3.4.2 Combined Class D audio power amplifier and buck-boost PFC                                                                                                                | 83                               |

|          | 3.5                      | Conclusion                                                                                                                                                                     | 87                               |

| 4  | SIC   | CAM for portable devices                                                         |

|----|-------|----------------------------------------------------------------------------------|

|    | 4.1   | Single-stage step-up audio power amplifier topology for portable applications 89 |

|    | 4.2   | Digital audio modulator for the double-boost SICAM 91                            |

|    |       | 4.2.1 Implementation of the digital modulator                                    |

|    |       | 4.2.2 Precompensator noise                                                       |

|    |       | 4.2.3 Simplified control block diagram                                           |

|    | 43    | Simulation of the double-boost SICAM with digital modulator 100                  |

|    |       | Conclusion                                                                       |

|    | 7.7   | Conclusion                                                                       |

| Pa | rt Il | I Isolated SICAMs                                                                |

| 5  | Int   | roduction to isolated SICAMs                                                     |

|    |       | Conventional solution with isolated SMPS and Class D audio power amplifier 109   |

|    |       | Isolated audio power amplification through HF-link conversion                    |

|    |       | Frequency domain analysis of different PWM SICAM solutions                       |

|    | 0.0   | 5.3.1 Time domain and frequency domain operations of power electronics . 111     |

|    |       | 5.3.2 Audio amplification with only a primary side switching stage 113           |

|    |       |                                                                                  |

|    |       | 5.3.3 Coding and decoding of the audio signals for isolated amplifiers 113       |

|    |       | 5.3.4 SICAM with modulated transformer voltages                                  |

|    | _ ,   | 5.3.5 SICAM with non-modulated transformer voltages                              |

|    |       | Developing SICAMs from SMPSs                                                     |

|    | 5.5   | Bidirectional switches and gate drives for isolated SICAMs                       |

|    |       | 5.5.1 Bidirectional switch arrangements                                          |

|    |       | 5.5.2 Gate drives for bidirectional switches                                     |

|    | 5.6   | Other possible approaches for isolated SICAMs                                    |

|    | 5.7   | Patent investigation                                                             |

|    | 5.8   | Conclusion                                                                       |

| 6  | Top   | pologies for isolated SICAMs                                                     |

|    |       | Input stage                                                                      |

|    |       | 6.1.1 Introduction                                                               |

|    |       | 6.1.2 Topologies for the input stage                                             |

|    |       | 6.1.3 Resonant converter as input stage                                          |

|    |       | 6.1.4 Soft-switched ZVS PWM inverter as input stage                              |

|    |       | 6.1.5 Hard-switched DC-AC inverter as input stage                                |

|    |       | 6.1.6 Integration of the inverter input stage within the SICAM                   |

|    |       | 6.1.7 Overdimensioning of the input stage in SICAMs                              |

|    | 6.0   |                                                                                  |

|    | 0.2   | Output stage                                                                     |

|    |       | 6.2.1 Commutation of the load current in the output stage through                |

|    |       | safe-commutation switching sequences                                             |

|    |       | 6.2.2 Commutation of the load current in the output stage with load clamps 160   |

|    |       | 6.2.3 SICAM with active capacitive voltage clamp                                 |

|    |       | Output impedance of isolated SICAMs                                              |

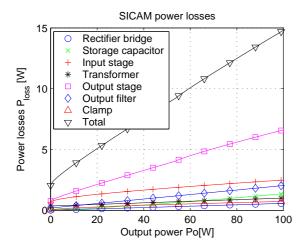

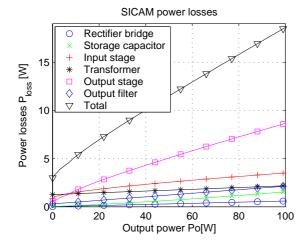

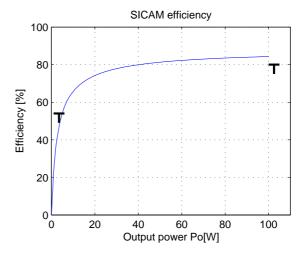

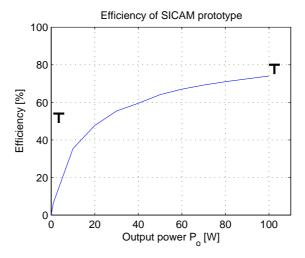

|    | 6.4   | Power losses and efficiency calculation in SICAMs                                |

|    |       | 6.4.1 Current and voltage levels in SICAMs                                       |

|    |       | 6.4.2 Power losses in SICAM components and stages                                |

|    | 6.5   | Conclusion                                                                       |

|      | Contents                                                                      | ΧV   |

|------|-------------------------------------------------------------------------------|------|

| 7    | Control methods for isolated SICAMs                                           | 195  |

|      | 7.1 Unsynchronized control of both stages in isolated SICAMs                  | 195  |

|      | 7.1.1 Simple PWM modulator for unsynchronized operation                       | 195  |

|      | 7.1.2 Master/Slave operation of the input/output stage to accomplish          |      |

|      | output stage safe commutation                                                 |      |

|      | 7.2 Synchronized control of both stages in isolated SICAMs                    | 199  |

|      | 7.2.1 Simple synchronized PWM method                                          | 200  |

|      | 7.2.2 Optimized PWM method with synchronization and lower output              |      |

|      | stage switching frequency                                                     | 200  |

|      | 7.2.3 Frequency spectrum of the new optimized PWM method in general           | 205  |

|      | case                                                                          |      |

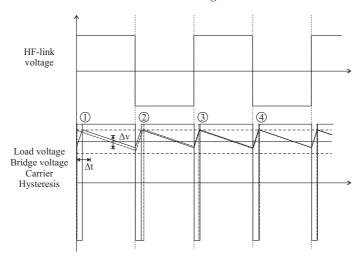

|      | 7.3 Self-oscillating modulators for isolated SICAMs - SOHF                    |      |

|      | 7.3.1 Application and limitations                                             |      |

|      | 7.3.2 Operation fundamentals                                                  |      |

|      | 7.3.3 Normal operation with $M < M_{lim}^*$                                   |      |

|      | 7.3.4 Locked operation with $M \ge M_{lim}^*$                                 |      |

|      | 7.3.6 Audio distortion of self-oscillating SICAM                              |      |

|      | 7.4 Closed-loop control schemes                                               |      |

|      | 7.5 Conclusion                                                                |      |

|      | 7.6 Conclusion                                                                | 211  |

| 8    | Prototypes of isolated SICAMs with non-modulated transformer                  |      |

|      | voltages                                                                      | 217  |

|      | 8.1 Isolated SICAM with master/slave operation for achieving safe commutation | 1217 |

|      | 8.2 Isolated SICAM with simple PWM modulator and active capacitive load       |      |

|      | voltage clamp                                                                 | 218  |

|      | 8.3 Isolated SICAM with optimized PWM modulator and safe-commutation          |      |

|      | switching sequence                                                            |      |

|      | 8.4 Isolated self-oscillating SICAM with GLIM modulator                       |      |

|      | 8.5 Conclusion                                                                | 223  |

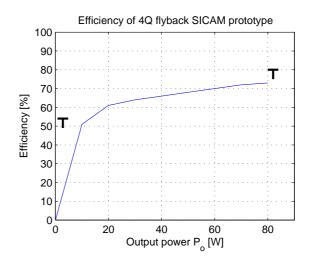

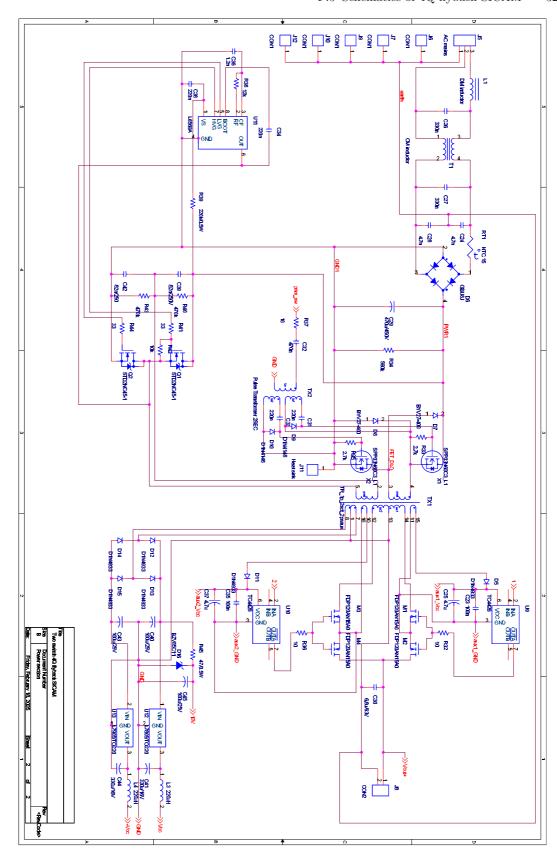

| 9    | 4Q flyback SICAM with modulated transformer voltages                          | 220  |

| J    | 9.1 Operation and design of 4Q flyback SICAM                                  |      |

|      | 9.2 Control of 4Q flyback SICAM                                               |      |

|      | 9.2.1 Peak current-mode control                                               |      |

|      | 9.2.2 Average current-mode control                                            |      |

|      | 9.3 Measurements on a 4Q flyback SICAM prototype with average                 |      |

|      | current-mode control                                                          | 235  |

|      | 9.4 Conclusion                                                                |      |

| -1.0 |                                                                               | 226  |

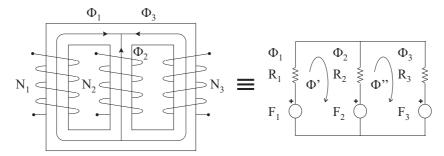

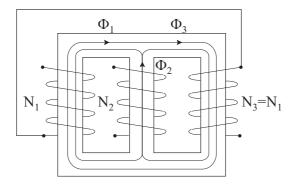

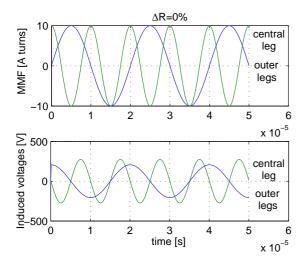

| 1(   | Integrated magnetics for isolated SICAMs                                      |      |

|      | 10.1 Analysis of the integrated magnetics                                     |      |

|      | 10.2 Application to HF-link converters                                        |      |

|      | 10.2.1Practical investigation of the proposed integrated magnetics            |      |

|      | 10.3 Conclusion                                                               | Z4đ  |

| 11   | 1 General conclusion about SICAMs                                             | 245  |

| A            |                                                                               | <ul><li>247</li><li>247</li><li>250</li></ul> |

|--------------|-------------------------------------------------------------------------------|-----------------------------------------------|

| В            | Analysis of combined mains-connected Class D audio power amplifier            |                                               |

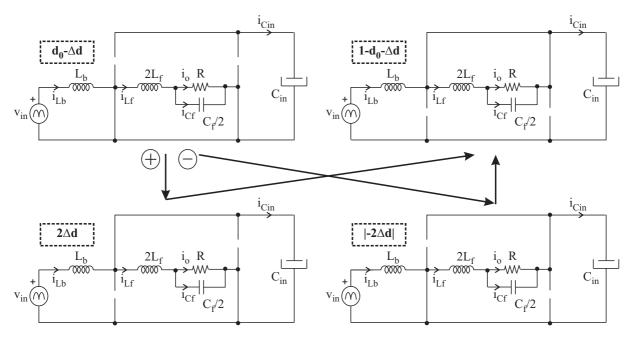

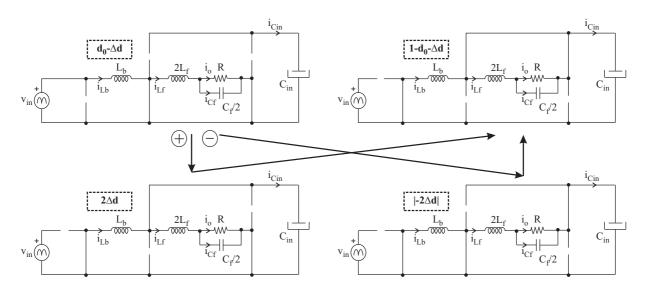

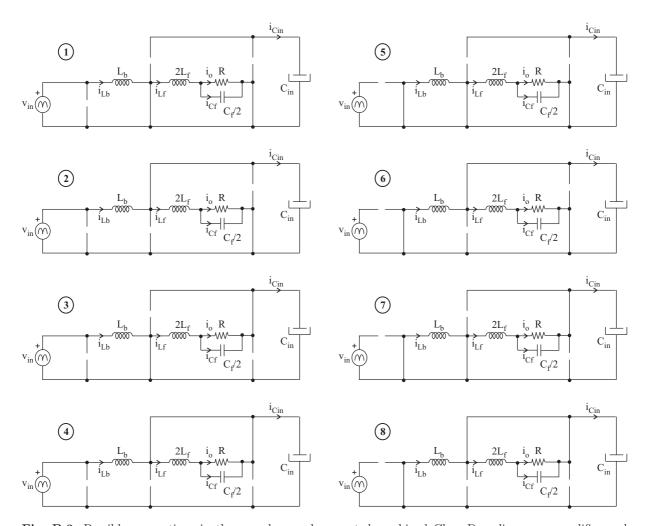

|              | and PFC  B.1 Analysis of combined Class D audio power amplifier and boost PFC | <ul><li>257</li><li>257</li></ul>             |

|              | B.2 Analysis of the synchronous operation of the combined Class D audio       |                                               |

|              | power amplifier and buck-boost PFC                                            | 264                                           |

|              | power amplifier and buck-boost PFC                                            | 273                                           |

| $\mathbf{C}$ | Analysis of double-boost SICAM for portable applications                      | 295                                           |

| D            | Analysis of flyback auxiliary converter for SICAM with active                 |                                               |

|              | capacitive voltage clamp                                                      |                                               |

|              | D.1 Analysis of CCM flyback auxiliary converter                               |                                               |

|              | D.2 Analysis of DCM flyback auxiliary converter                               | 305                                           |

| $\mathbf{E}$ | Analysis of control methods for SICAMs                                        | 309                                           |

|              | E.1 Frequency spectrum of different PWM waveforms in isolated SICAMs          | 309                                           |

|              | E.1.1 Double Fourier Series of $F_{NADS,1h}$                                  |                                               |

|              | E.1.2 Double Fourier Series of $F_{NADS,2h}$                                  |                                               |

|              | E.1.3 Double Fourier Series of $F_{NADD,1h}$                                  |                                               |

|              | E.1.4 Double Fourier Series of $F_{NADD,2h}$                                  |                                               |

|              | E.2 Switching frequency of GLIM self-oscillating modulator                    | 313                                           |

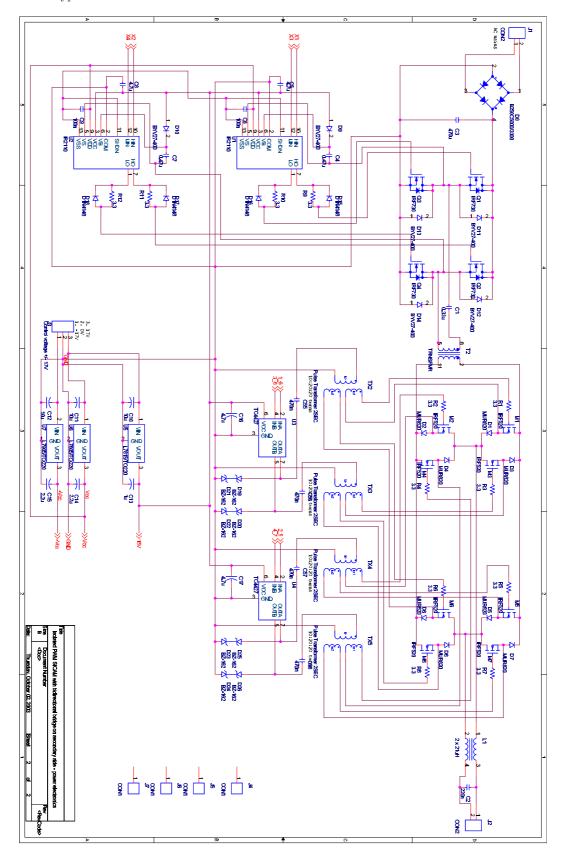

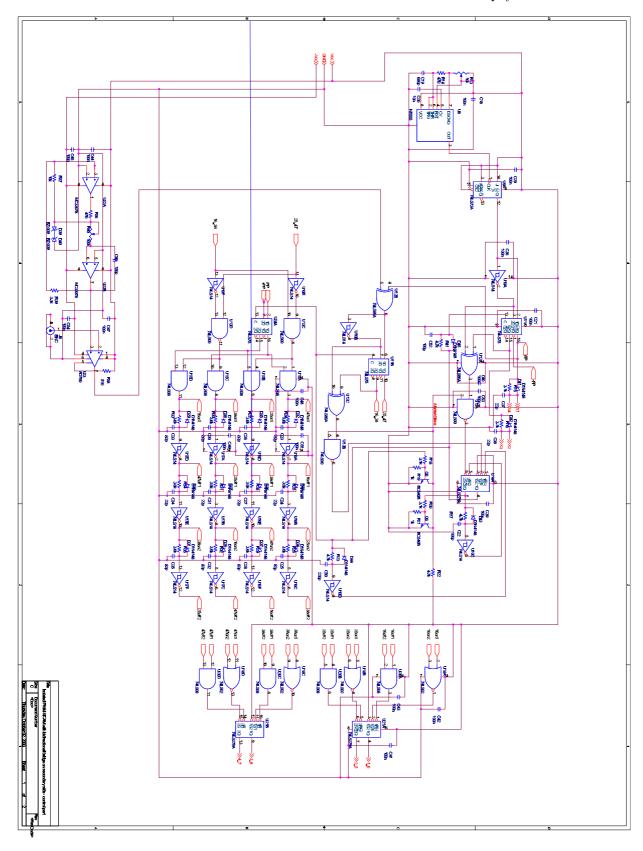

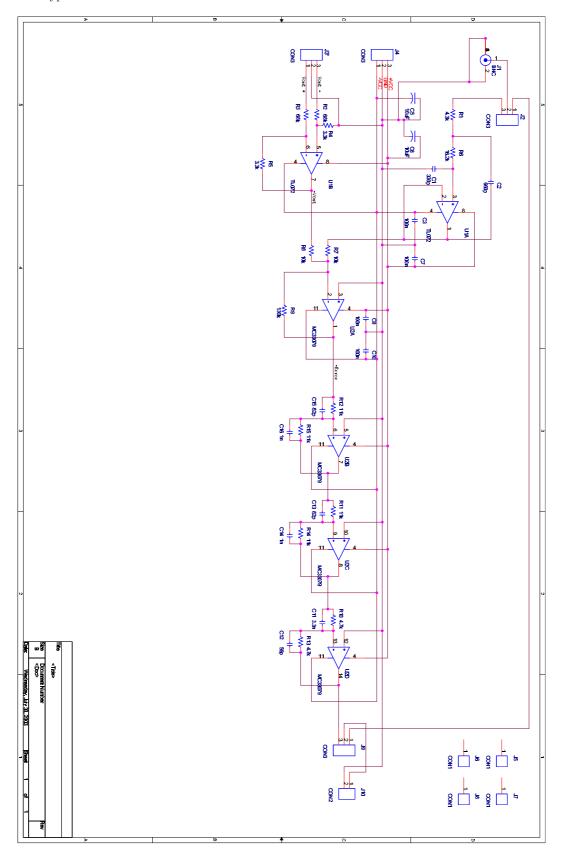

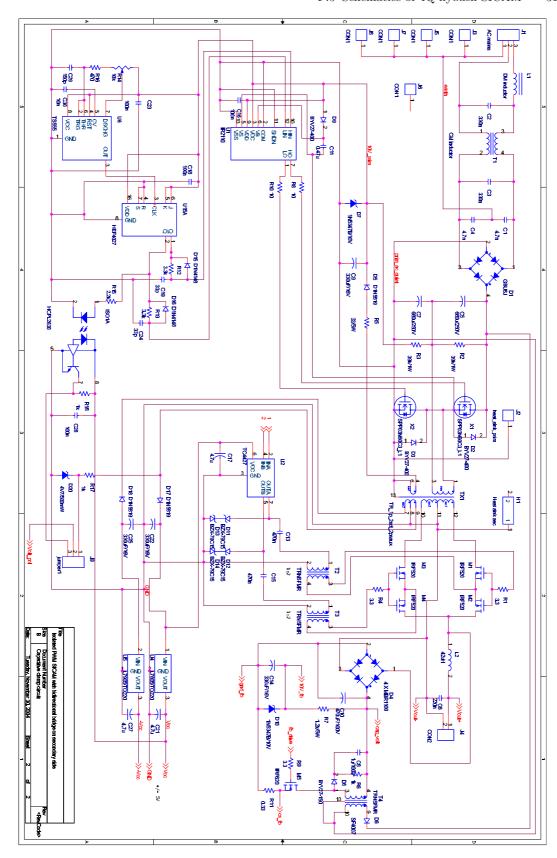

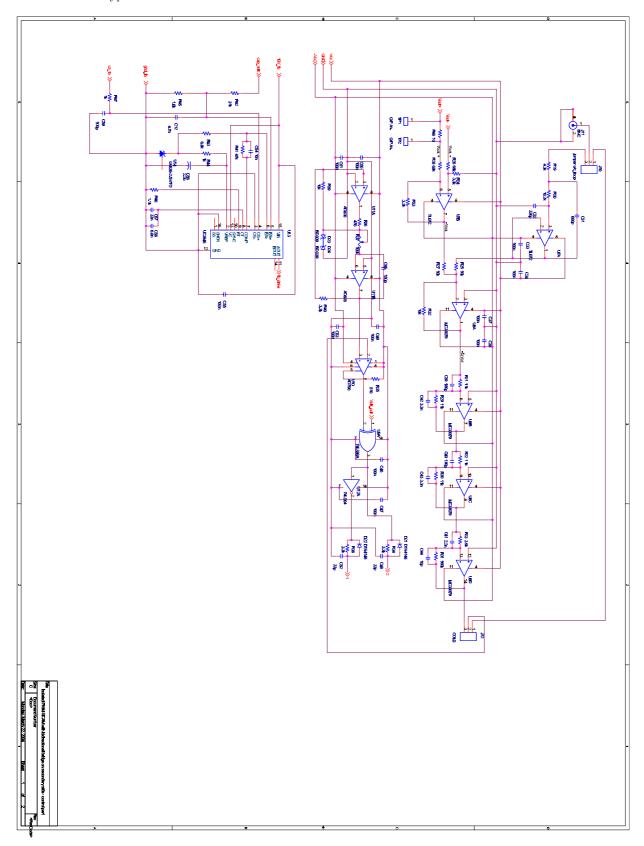

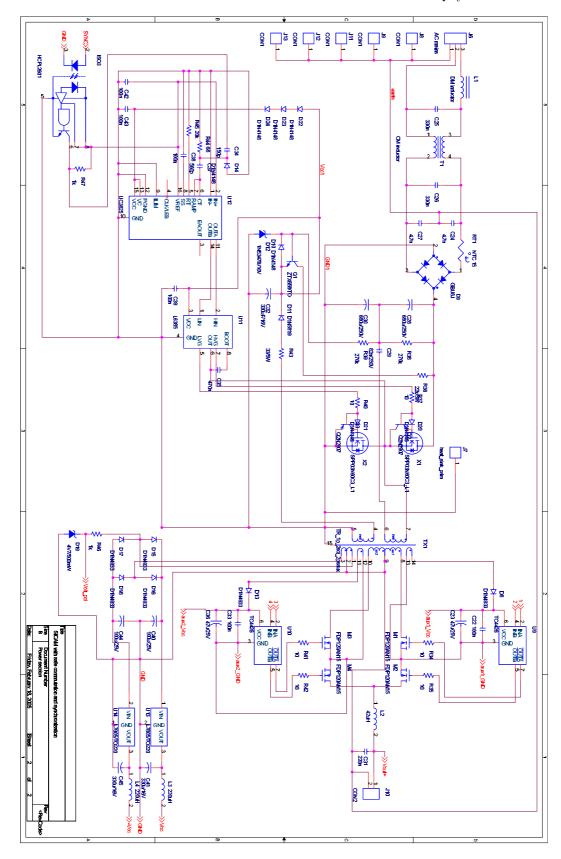

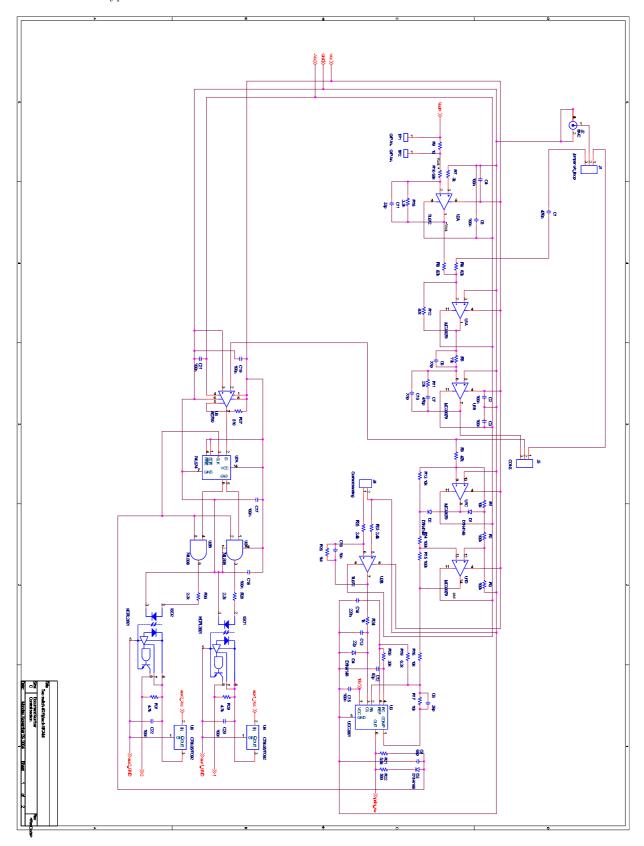

| $\mathbf{F}$ | Prototype schematics                                                          | 315                                           |

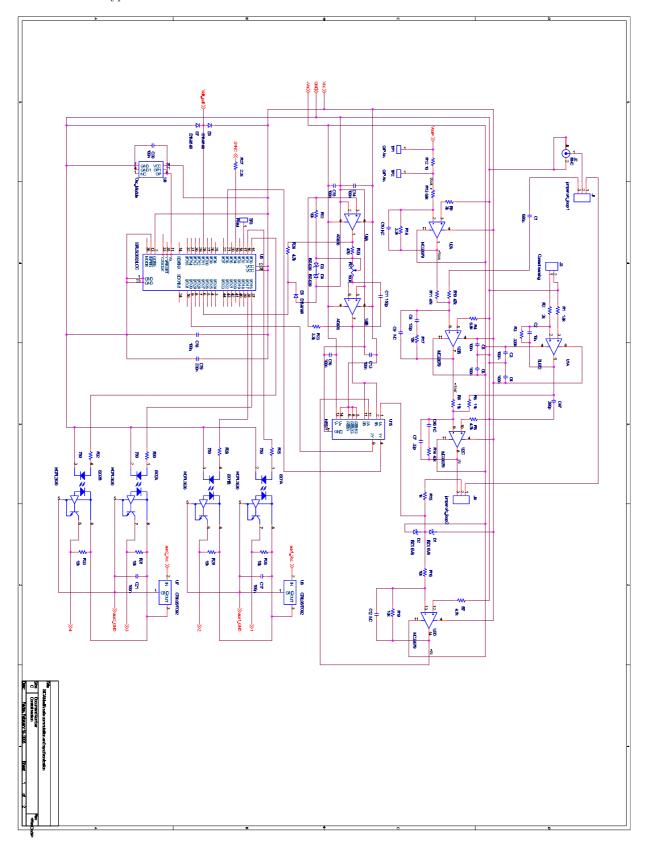

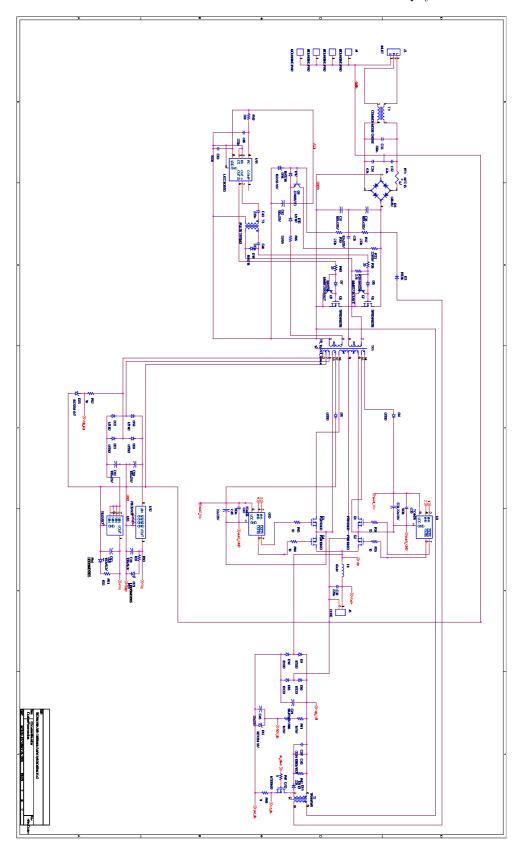

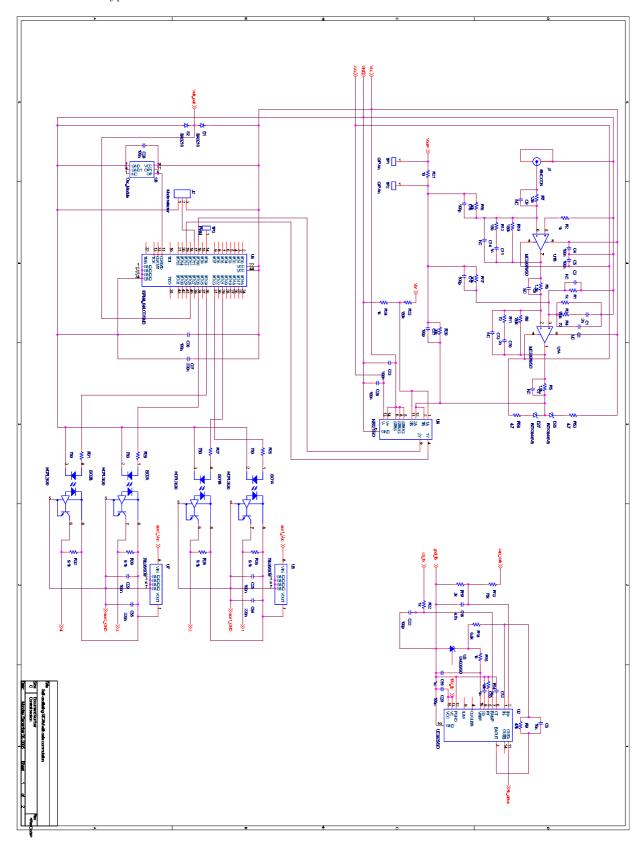

|              | F.1 Schematics of isolated SICAM with master/slave operation                  | 315                                           |

|              | F.2 Schematics of isolated SICAM with active capacitive load voltage clamp    | 315                                           |

|              | F.3 Schematics of isolated SICAM with optimized PWM modulator and             |                                               |

|              | safe-commutation switching sequence                                           |                                               |

|              | F.4 Schematics of isolated self-oscillating SICAM with GLIM modulator         |                                               |

|              | F.5 Schematics of 4Q flyback SICAM                                            | 315                                           |

# Contents of inclosed CDROM

- PhD thesis

- single file

- multiple files

- Orcad

- PSpice simulation files

- PCB files

- MATLAB

- My functions

- SICAM design

- VHDL Verilog

- Safe-commutation algorithm

- Double-boost SICAM control

- References

- My articles

# List of Figures

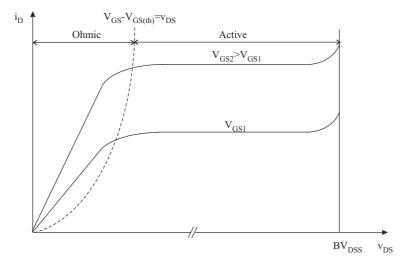

| 1.1  | I-V characteristics of MOSFET                                              | 16 |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Linear audio power amplifier with MOSFETs                                  | 16 |

| 1.3  | Power supply voltage and load voltage with linear audio power amplifier    | 16 |

| 1.4  | Switching-mode audio power amplifier with MOSFETs                          | 18 |

| 1.5  | PWM bridge voltage and load voltage with switching-mode audio power        |    |

|      | amplifier                                                                  | 18 |

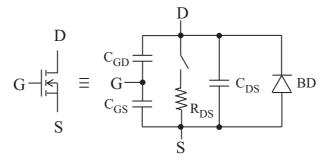

| 1.6  | Equivalent scheme of MOSFET                                                | 19 |

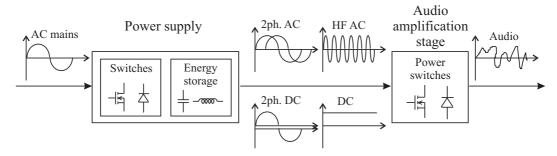

| 1.7  | Block diagram of completely switching-mode audio power amplifier           | 19 |

| 1.8  | Simple block diagram of SICAM                                              | 20 |

| 1.9  | Dedication of the SMPS to the audio power amplifier in SICAM               | 21 |

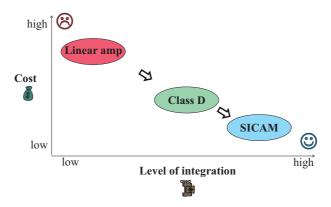

| 1.10 | Comparison of linear amplifiers, switching-mode amplifiers and SICAMs      | 22 |

|      |                                                                            |    |

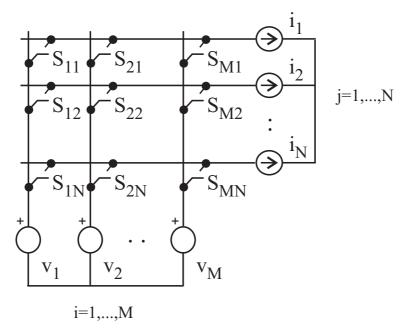

| 2.1  | M-phase to N-phase matrix converter                                        | 28 |

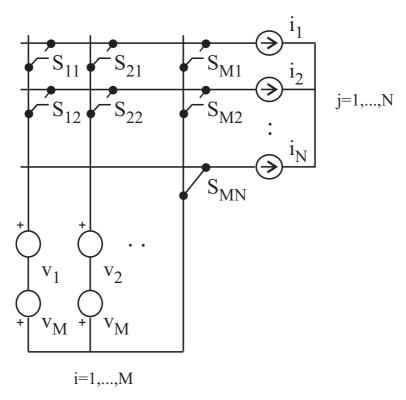

| 2.2  | M-phase to N-phase matrix converter with central tap in the M-th line      | 28 |

| 2.3  | Single-phase to single-phase matrix converter                              | 29 |

| 2.4  | Bounding region for the output voltage of a single-phase to single-phase   |    |

|      | matrix converter                                                           | 31 |

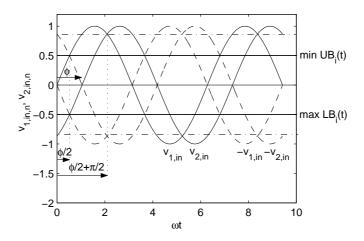

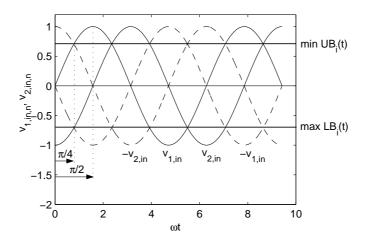

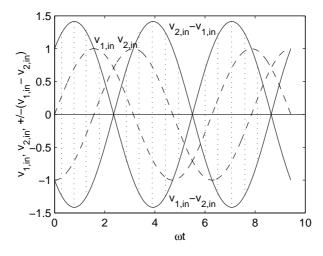

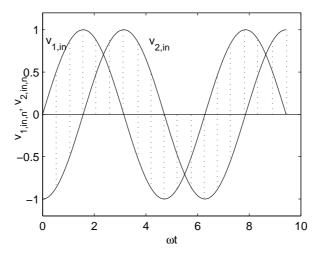

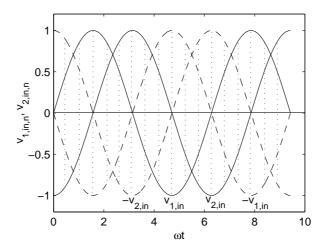

| 2.5  | Upper and lower bounds of the input voltages of a two-phase to             |    |

|      | single-phase matrix converter                                              | 32 |

| 2.6  | Upper and lower bounds of the input voltages of a two-phase to             |    |

|      | single-phase matrix converter in the optimal case $\phi = \pi/2 \dots$     | 33 |

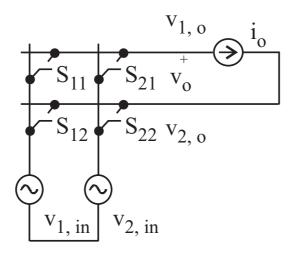

| 2.7  | 2ph-AC to 1ph-AC matrix converter without a central tap                    | 33 |

| 2.8  | Bounding region for the output voltage of a 2ph-AC to 1ph-AC matrix        |    |

|      | converter without a central tap                                            | 34 |

| 2.9  | 2ph-AC to 1ph-AC matrix converter with fixed central tap                   | 35 |

| 2.10 | Bounding region for the output voltage of a 2ph-AC to 1ph-AC matrix        |    |

|      | converter with fixed central tap                                           | 35 |

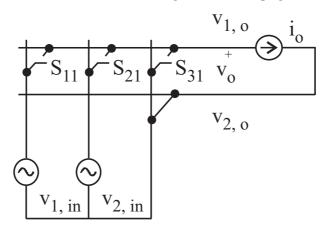

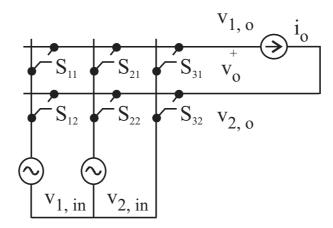

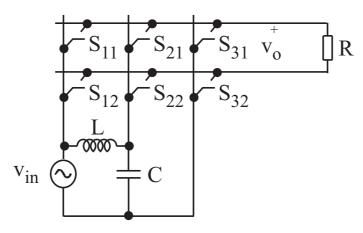

| 2.11 | 2ph-AC to 1ph-AC matrix converter with switched central tap                | 36 |

| 2.12 | Bounding region for the output voltage of a 2ph-AC to 1ph-AC matrix        |    |

|      | converter with switched central tap                                        | 37 |

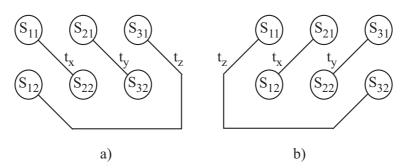

| 2.13 | Diagonal switching: a) type A and b) type B                                | 38 |

| 2.14 | Bounding region for the output voltage of a 2ph-AC to 1ph-AC matrix        |    |

|      | converter with switched central tap in case of diagonal switching strategy |    |

|      | - type A                                                                   | 39 |

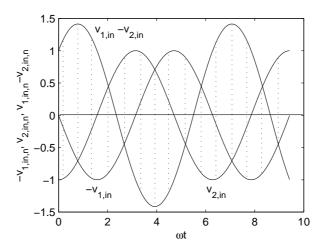

| 2.15 | Time diagram for the diagonal switching strategy - type A                  | 40 |

|      | Phasor diagram for input voltages                                          | 40 |

| 2.17 | Phasor diagram for input voltages and output voltage                       | 41 |

| 2.18 | Distribution of switching patterns' time intervals through one switching              |            |

|------|---------------------------------------------------------------------------------------|------------|

|      | interval $T_s$                                                                        | 42         |

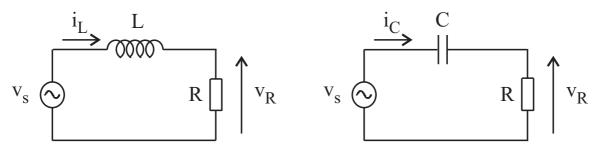

| 2.19 | L-R series circuit                                                                    | 43         |

| 2.20 | C-R series circuit                                                                    | 43         |

| 2.21 | L-C-R series circuit                                                                  | 44         |

|      | L-C-R parallel circuit                                                                | 44         |

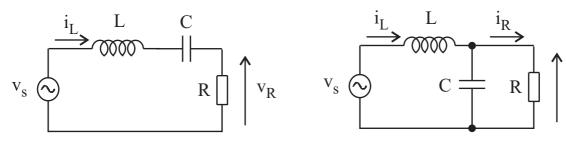

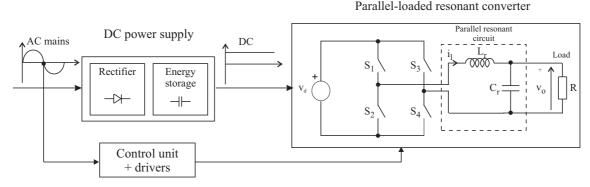

|      | Parallel-loaded resonant converter used for obtaining another voltage phase           | 45         |

|      | MC-based SICAM with an <i>LC</i> -network                                             | 46         |

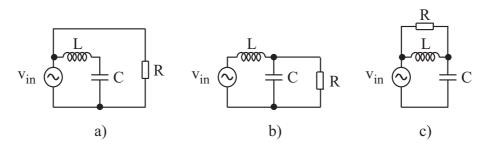

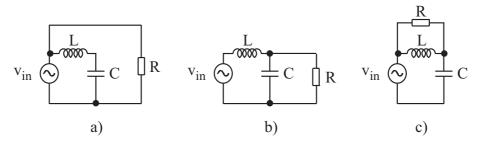

|      | General topologies: a) $v_{in}  R$ , b) $L  R$ and c) $C  R$                          | 46         |

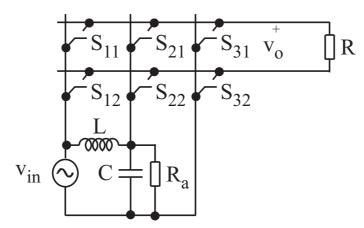

|      | Loading the $LC$ -network with an additional resistor $R_a$                           | 48         |

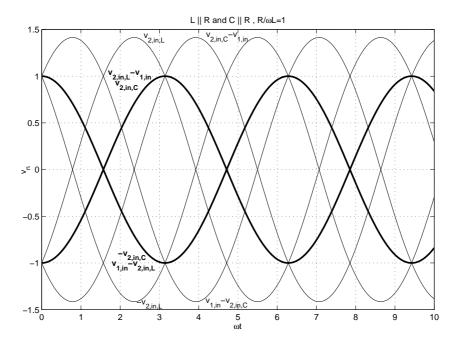

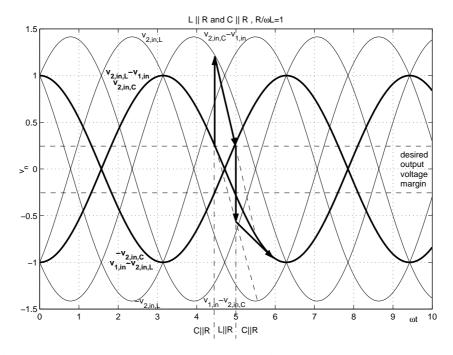

|      | Steady-state voltages in MC-based SICAM with resonant $LC$ -network                   | 10         |

| 2.21 | and $R/\omega L=1$                                                                    | 49         |

| 2 28 | Approximate transient voltages in MC-based SICAM with resonant                        | 10         |

| 2.20 | $LC$ -network and $R/\omega L=1$                                                      | 50         |

| 2 20 | Possible topologies for the MC-based SICAM with loaded $LC$ -network                  | 53         |

|      | Matrix SICAM with $LC$ -network and output low-pass filter                            | 55<br>57   |

|      | <u> </u>                                                                              | 58         |

|      | Frequency characteristic of the input impedance $Z_{in}(f)$ of the output filter      | 98         |

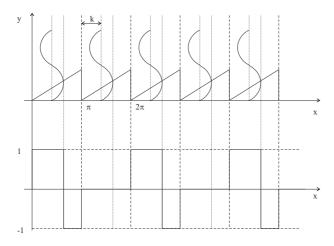

| 2.32 | Open-loop control principles: a) AM of the triangular carrier and b) $\Delta$         | <b>F</b> 0 |

| 0.00 | modulation technique                                                                  | 59         |

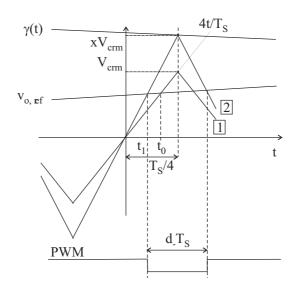

|      | AM of triangular carrier                                                              | 60         |

|      | Δ modulation control principle                                                        | 63         |

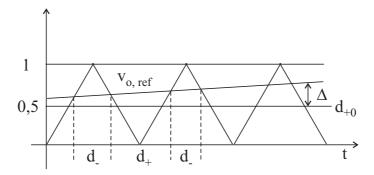

| 2.35 | Matrix SICAM with $LC$ -network and purely resistive load (m=0,8,                     |            |

|      | f=10 kHz) - Top: Output voltage $v_{out}$ , Middle: FFT up to 1 MHz, Bottom:          | 0.0        |

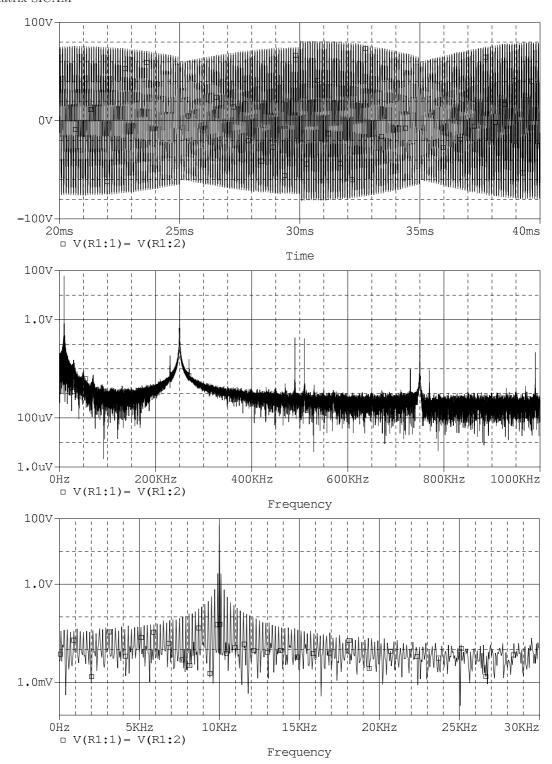

| 2.24 | FFT up to 30 kHz                                                                      | 66         |

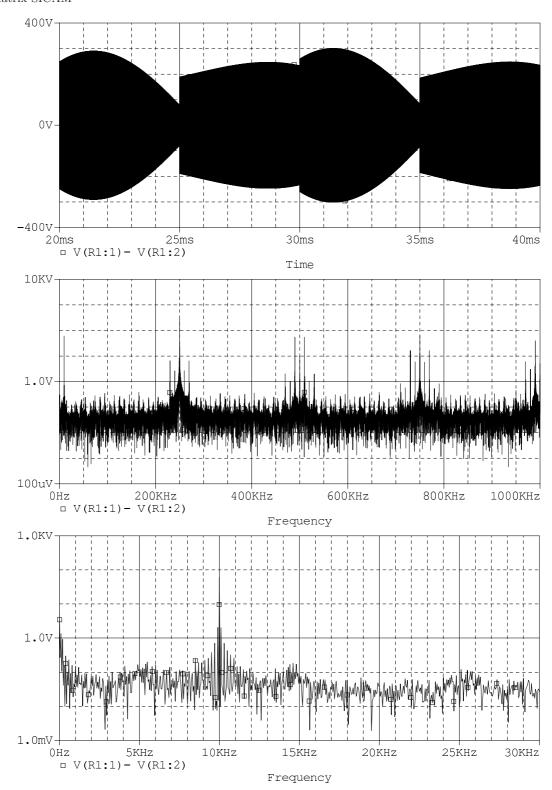

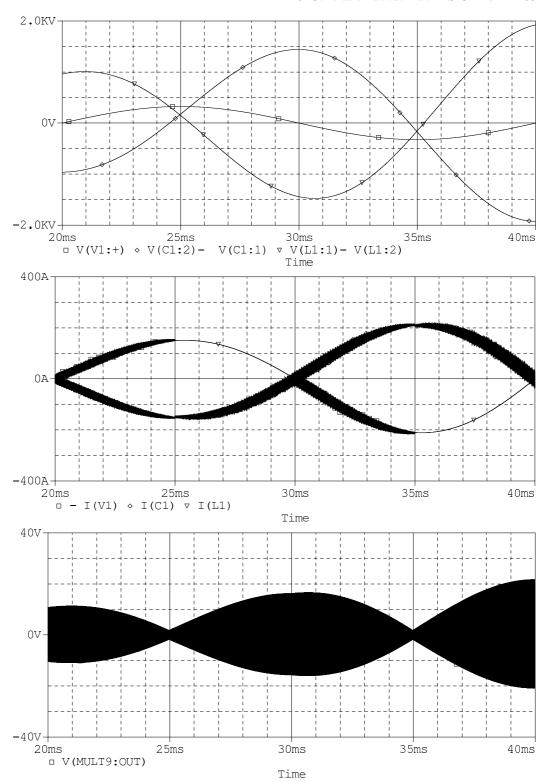

| 2.36 | Matrix SICAM with $LC$ -network and purely resistive load (m=0,8,                     |            |

|      | f=10 kHz) - Top: Input voltage $v_{in}$ , capacitor voltage $v_C$ and inductor        |            |

|      | voltage $v_L$ , Middle: Input current $i_{in}$ , capacitor current $i_C$ and inductor |            |

|      | current $i_L$ , Bottom: AM of triangular carrier                                      | 67         |

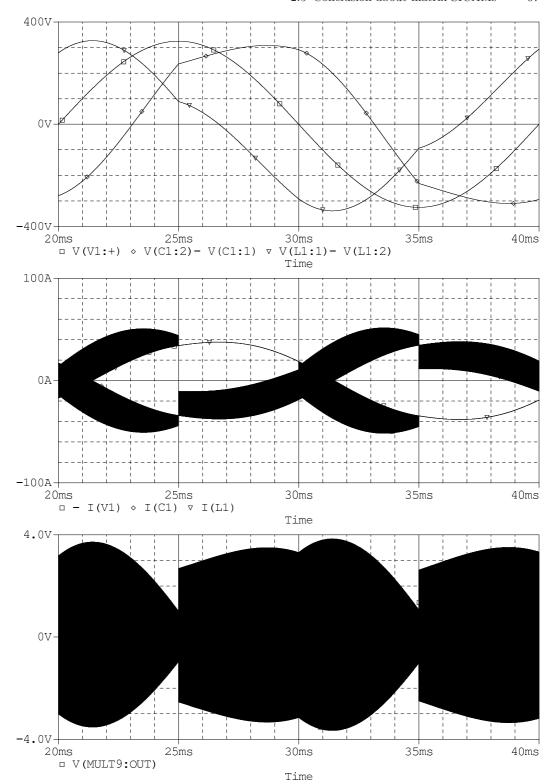

| 2.37 | MC-based SICAM using an LC-network (m=0,8, f=10 kHz) - Top: Output                    |            |

|      | voltage $v_{out}$ , Middle: FFT up to 1 MHz, Bottom: FFT up to 30 kHz                 | 68         |

| 2.38 | MC-based SICAM using an $LC$ -network (m=0,8, f=10 kHz) - Top: Input                  |            |

|      | voltage $v_{in}$ , capacitor voltage $v_C$ and inductor voltage $v_L$ , Middle: Input |            |

|      | current $i_{in}$ , capacitor current $i_C$ and inductor current $i_L$ , Bottom: AM of |            |

|      | triangular carrier                                                                    | 69         |

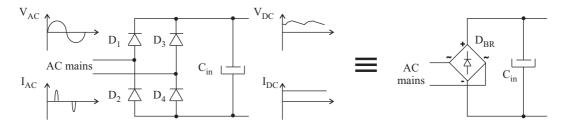

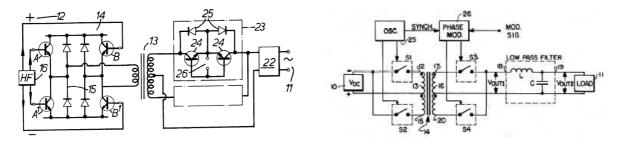

| 3.1  | Non-isolated DC power supply                                                          | 71         |

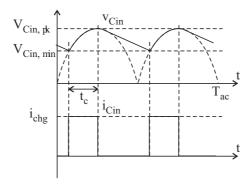

| 3.2  | Voltage and current of the input storage capacitor                                    | 72         |

| 3.3  |                                                                                       | 73         |

|      | Class D audio power amplifier with non-isolated DC power supply                       |            |

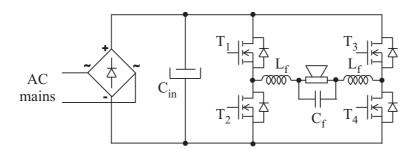

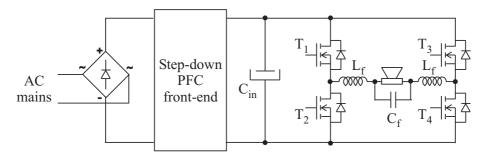

| 3.4  | Class D audio power amplifier with step-down PFC front-end                            | 75<br>76   |

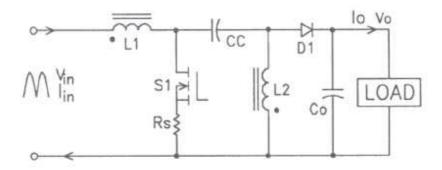

| 3.5  | SEPIC PFC preregulator [1]                                                            | 76         |

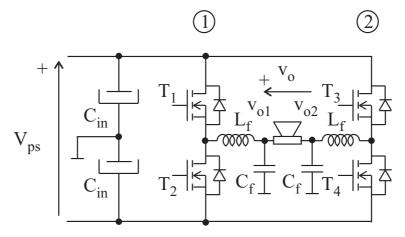

| 3.6  | Full-bridge Class D audio power amplifier                                             | 77         |

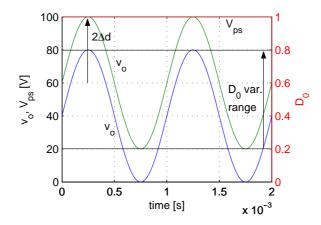

| 3.7  | Variations in the output voltage and duty cycles                                      | 78         |

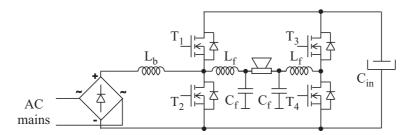

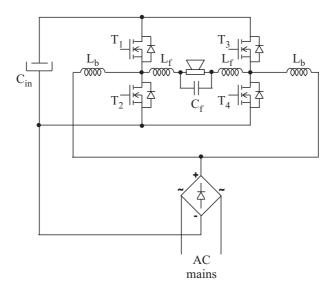

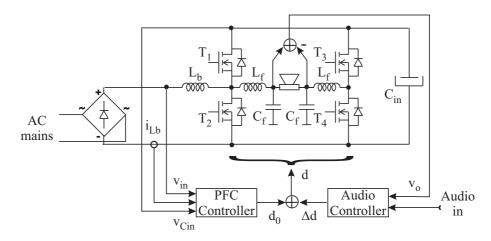

| 3.8  | Combined Class D audio power amplifier and boost PFC                                  | 78         |

| 3.9  | Possible connections in the combined Class D audio power amplifier and                | =0         |

| 0.10 | boost PFC                                                                             | 79         |

| 3.10 | Combined Class D audio power amplifier and boost PFC with two boost                   |            |

| 0.11 | inductors                                                                             | 79         |

| 3.11 | Control diagram of a combined Class D audio power amplifier and boost                 |            |

|      | PFC                                                                                   | 81         |

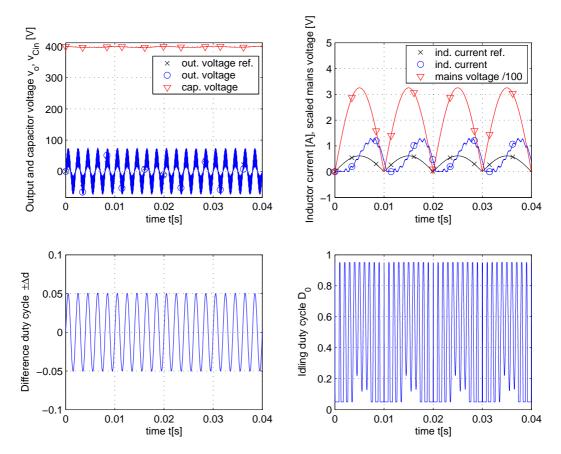

| 3.12                                                        | Simulated waveforms of combined Class D audio power amplifier and boost PFC                                                                                                                                            | 82                                   |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

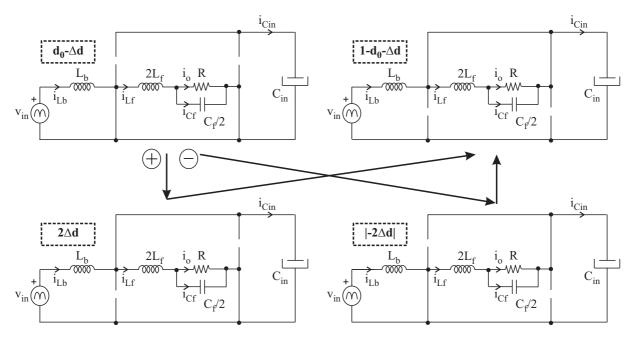

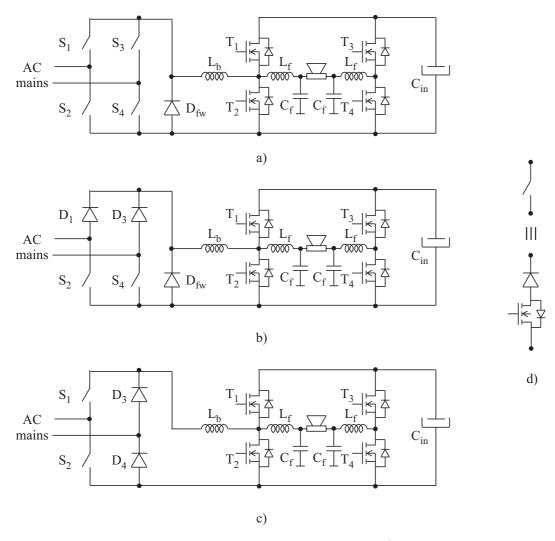

| 3.13                                                        | Combined Class D audio power amplifier and buck-boost PFC: a) with 4 switches and a freewheeling diode, b) with 2 switches and a freewheeling diode, c) with 2 switches, and d) one possible realization of the switch | 83                                   |

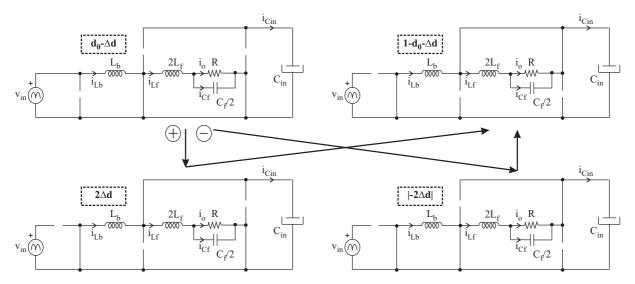

| 3.14                                                        | Possible connections in the synchronously-operated combined Class D audio power amplifier and buck-boost PFC                                                                                                           | 84                                   |

| 3.15                                                        | Possible connections in the asynchronously-operated combined Class D audio power amplifier and buck-boost PFC                                                                                                          | 86                                   |

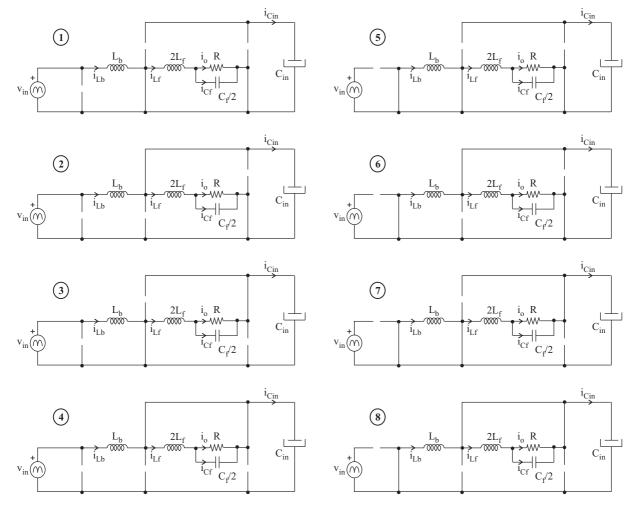

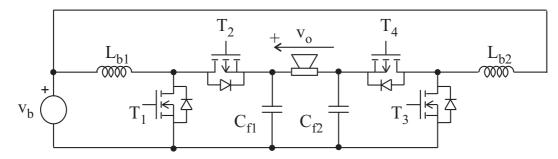

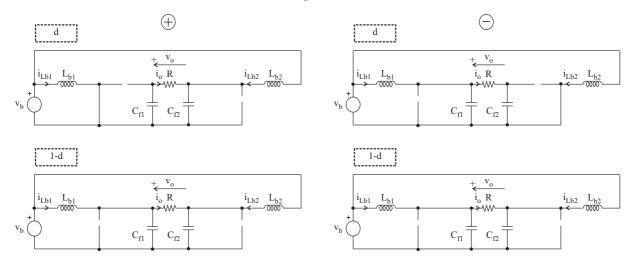

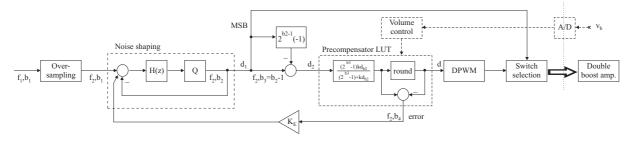

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                      | Double boost SICAM                                                                                                                                                                                                     | 90<br>91<br>92<br>94<br>95           |

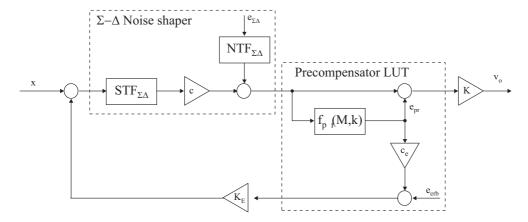

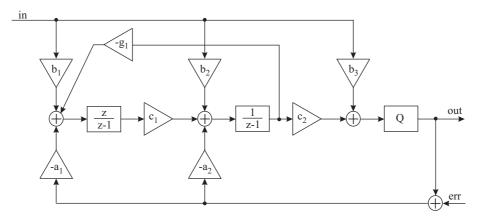

| 4.7<br>4.8                                                  |                                                                                                                                                                                                                        | 96<br>99<br>99                       |

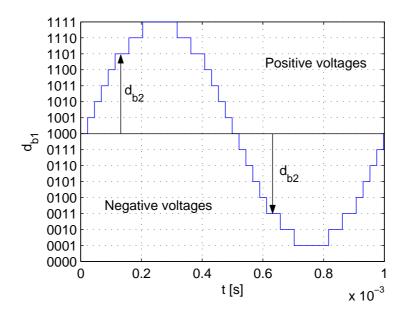

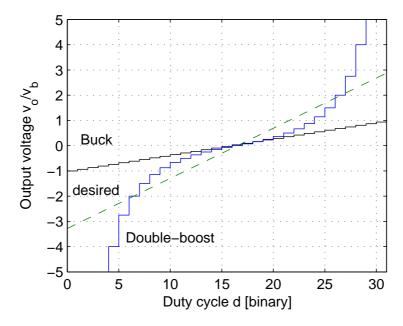

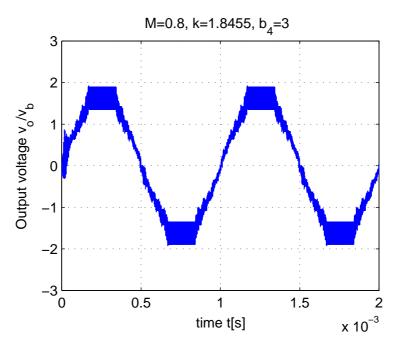

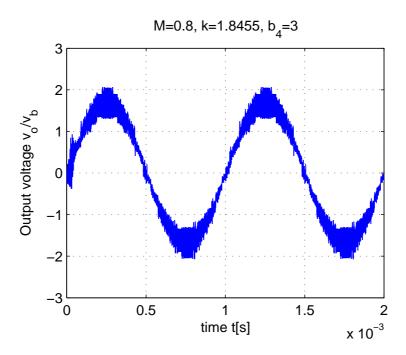

| 4.9<br>4.10                                                 | Normalized output voltage $v_o/v_b$ of the fully-digital double-boost SICAM                                                                                                                                            | 101<br>101                           |

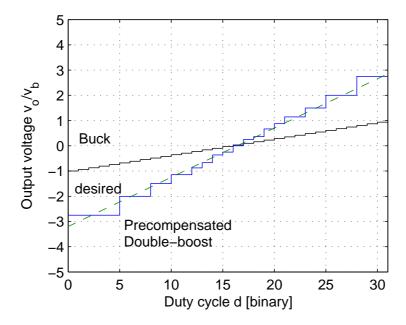

|                                                             | Normalized output voltage $v_o/v_b$ of the fully-digital double-boost SICAM with feedback from the precompensator                                                                                                      | 102                                  |

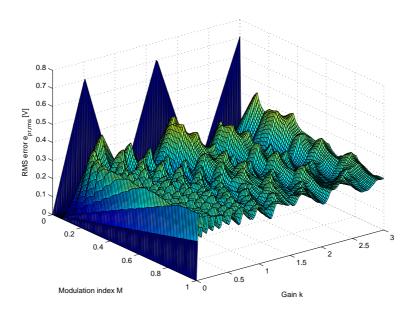

|                                                             | without feedback from the precompensator as a function of the modulation                                                                                                                                               | 102                                  |

| 4.14                                                        | Normalized output voltage $v_o/v_b$ of the fully-digital double-boost SICAM with feedback from the precompensator as a function of the modulation                                                                      | 103                                  |

| 4.15                                                        | Normalized output voltage $v_o/v_b$ of the fully-digital double-boost SICAM with feedback from the precompensator as a function of the selected                                                                        | 104<br>105                           |

| 4.16                                                        | Normalized output voltage $v_o/v_b$ of the fully-digital double-boost SICAM with feedback from the precompensator as a function of the number of                                                                       | 106                                  |

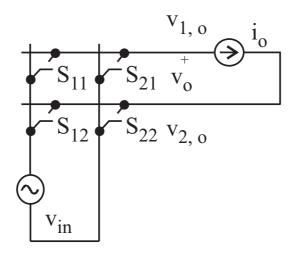

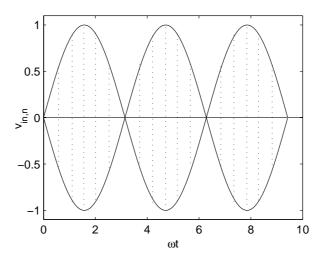

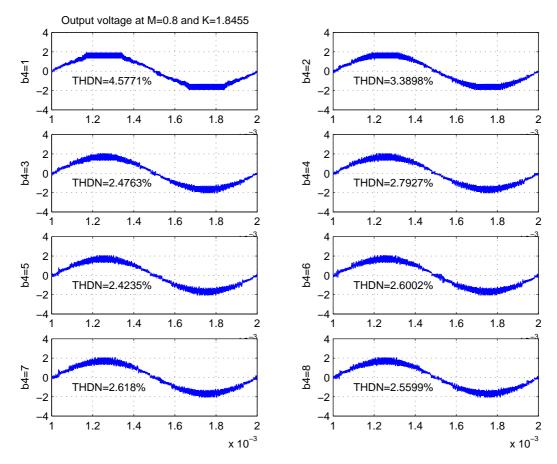

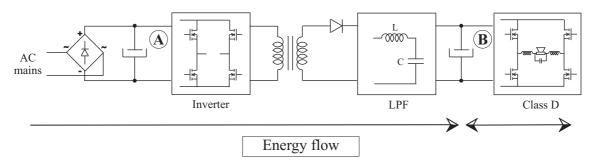

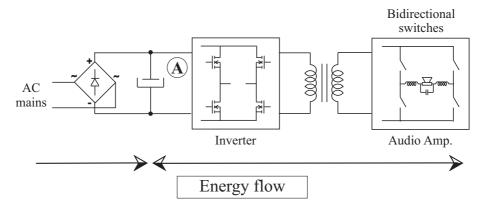

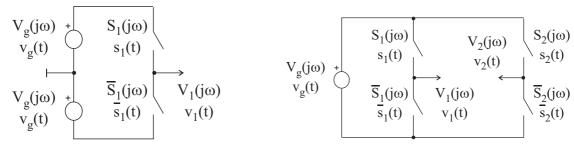

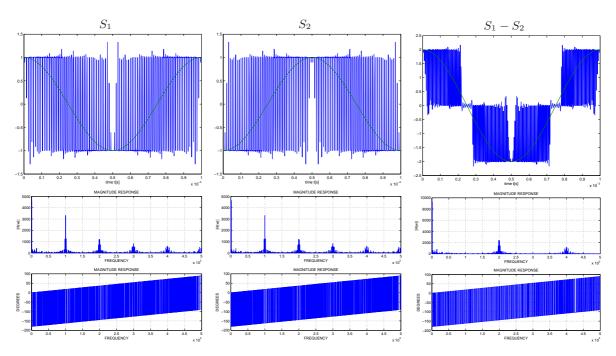

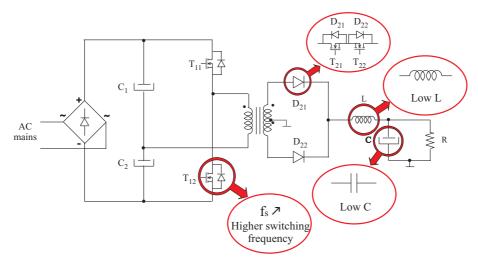

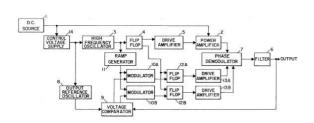

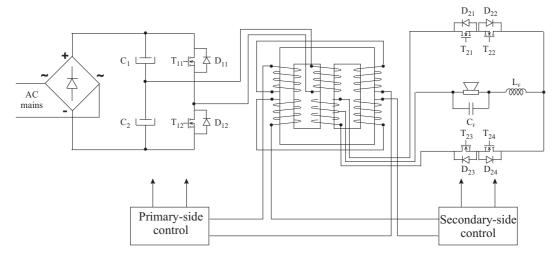

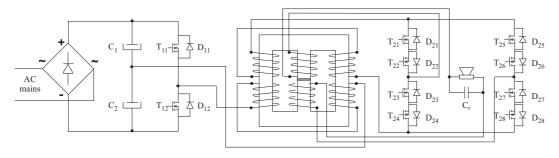

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | Half-bridge schematic with the associated voltages and switching functions  Full-bridge schematic with the associated voltages and switching functions  1                                                              | l 11<br>l 12<br>l 12<br>l 13<br>l 16 |

| 5.10                                                        | Frequency spectrum of $F_r$                                                                                                                                                                                            | 116                                  |

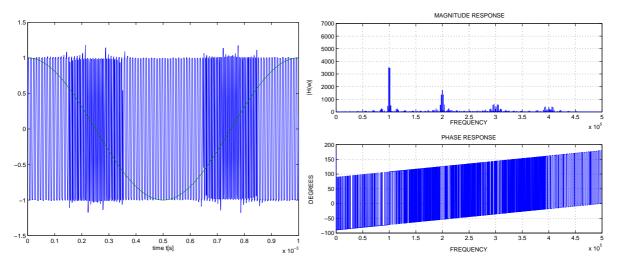

| 5.11 | Resultant PWM signal $F_{NADD} \cdot F_r$                                                       | 116  |

|------|-------------------------------------------------------------------------------------------------|------|

| 5.12 | Frequency spectrum of $F_{NADD} \cdot F_r \dots \dots \dots \dots \dots$                        | 116  |

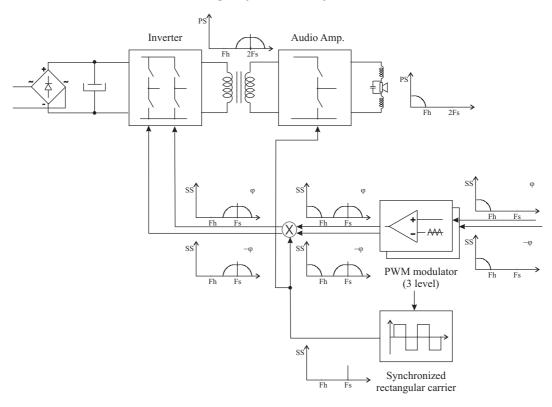

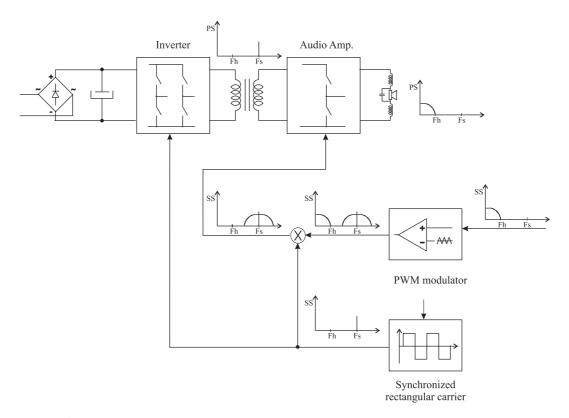

| 5.13 | SICAM with modulated transformer voltages                                                       | 117  |

| 5.14 | SICAM with non-modulated transformer voltages                                                   | 117  |

| 5.15 | SICAM development steps                                                                         | 118  |

| 5.16 | Reworking a half-bridge SMPS for SICAM operation                                                | 119  |

|      | a) Voltage 2QSW, b) Current 2QSW, c) Antiparallel connection of two                             |      |

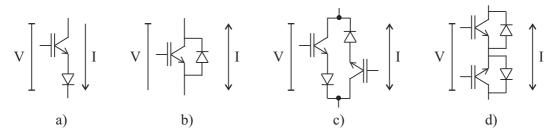

|      | voltage 2QSW, d) Antiseries connection of two current 2QSW                                      | 119  |

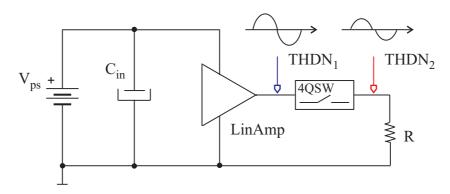

| 5.18 | Different arrangements of bidirectional switches (4QSW)                                         | 121  |

|      |                                                                                                 | 121  |

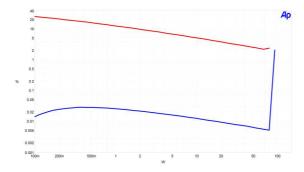

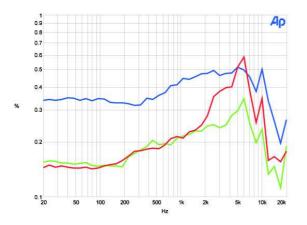

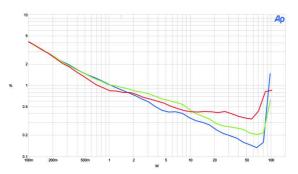

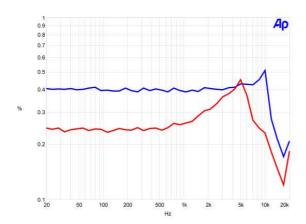

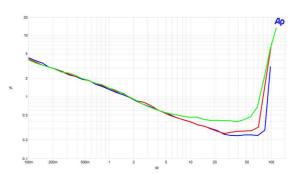

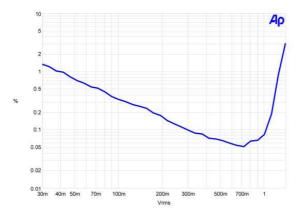

|      | THD+N as function of power at 1 kHz for 4QSW with one MOSFET and                                |      |

|      | four diodes in Fig. 5.18a measured before (bottom) and after (top) the                          |      |

|      | 4QSW                                                                                            | 122  |

| 5.21 | THD+N as function of power at 1 kHz for 4QSW with two MOSFETs                                   |      |

|      | and two diodes in Fig. 5.18b measured before (bottom) and after (top)                           |      |

|      | the 4QSW                                                                                        | 122  |

| 5.22 | THD+N as function of power at 1 kHz for 4QSW with two common-source                             |      |

|      | connected MOSFETs in Fig. 5.18c measured before (bottom) and after                              |      |

|      | (top) the 4QSW                                                                                  | 122  |

| 5.23 | THD+N as function of power at 1 kHz for 4QSW with just a single                                 |      |

|      | Junction FET shown in Fig. 5.18d measured before (bottom) and after                             |      |

|      | (top) the 4QSW                                                                                  | 122  |

| 5.24 | a) Conventional grounding scheme for HF-link converters and b) Newly                            |      |

|      | proposed grounding scheme for easy level shifting                                               | 124  |

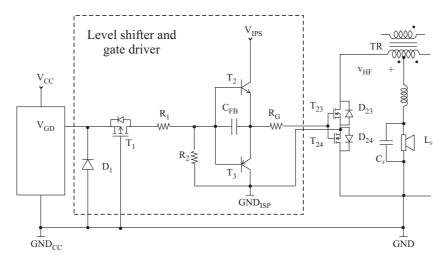

| 5.25 | Negative voltage-tolerant level shifter and gate driver                                         | 125  |

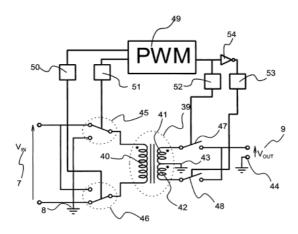

|      | Circuit diagram from [2]                                                                        | 126  |

| 5.27 | Circuit diagram from [3]                                                                        | 126  |

| 5.28 | Circuit diagram from [4]                                                                        | 127  |

| 5.29 | Circuit diagram from [5]                                                                        | 127  |

|      | Circuit diagram from [6]                                                                        | 128  |

| 5.31 | Circuit diagram from [7]                                                                        | 128  |

|      | Circuit diagram from [8]                                                                        |      |

| 5.33 | Circuit diagram from [9]                                                                        | 128  |

| 5.34 | Circuit diagram from [10]                                                                       | 129  |

| 5.35 | Circuit diagram from [11]                                                                       | 129  |

| 5.36 | Circuit diagram from [12]                                                                       | 129  |

| C 1  |                                                                                                 |      |

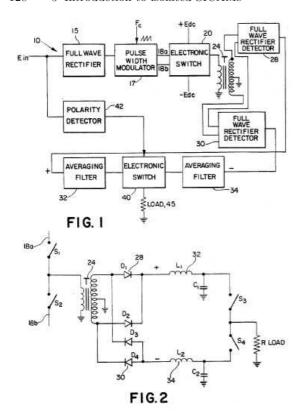

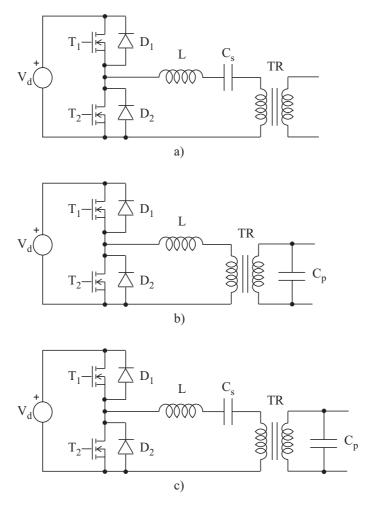

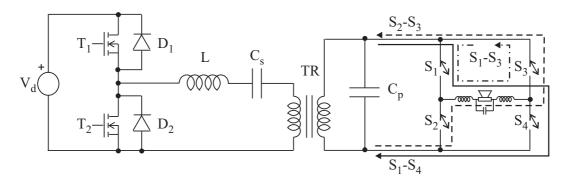

| 6.1  | Class D resonant converter types: a) series LC, b) parallel LC and                              | 135  |

| 6.0  | c) series-parallel LCC                                                                          | 199  |

| 6.2  | -                                                                                               | 196  |

| 6.2  | amplifier                                                                                       | 136  |

| 6.3  |                                                                                                 | 191  |

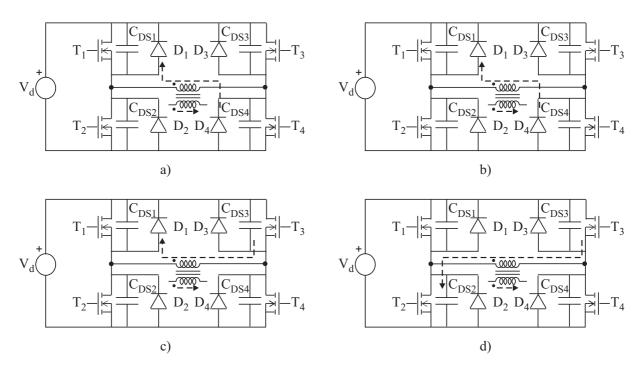

| 6.4  | ZVS PWM inverter: a) power delivered to the load, b) capacitance of                             |      |

|      | T <sub>3</sub> gets discharged, c) freewheeling cycle and d) capacitance of T <sub>2</sub> gets | 190  |

| 6 5  |                                                                                                 | 138  |

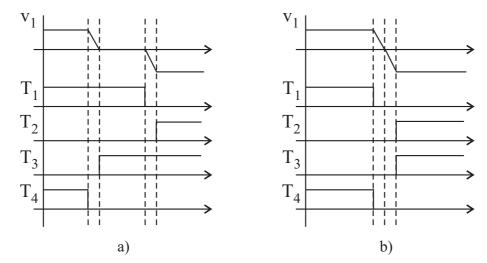

| 6.5  | ZVS PWM inverter output voltage $v_1$ and switching waveforms:                                  | 1 40 |

|      | a) phase-shift ZVS PWM inverter and b) simultaneous ZVS PWM inverter                            | 140  |

| 6.6  | ZVS PWM inverter with reflected load current in opposite direction from                                  |          |

|------|----------------------------------------------------------------------------------------------------------|----------|

|      | the magnetizing current: a) power regenerated from the load through $D_1$                                |          |

|      | and $D_3$ , b) $T_4$ is turned off with ZVS, c) capacitance of $T_4$ gets charged                        |          |

|      | and $T_3$ gets discharged and d) capacitance of $T_1$ gets charged and $T_2$ gets                        |          |

|      | discharged                                                                                               | 141      |

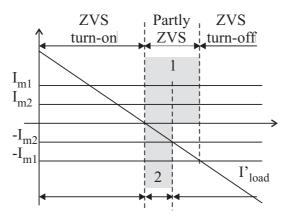

| 6.7  | Soft-switched PWM inverter switching losses dependance on reflected load                                 |          |

| .,   | current $I'_{load}$ for two different magnetizing currents $I_{m1} = 2I_{m2} \dots \dots$                | 142      |

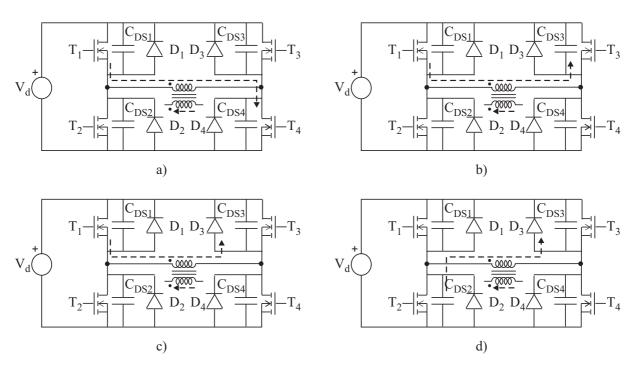

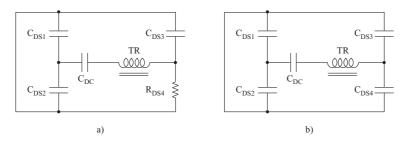

| 6.8  | Determining the resonant capacitance $C_r$ when switching: a) single leg                                 |          |

| 0.0  | and b) both legs at the same time                                                                        | 144      |

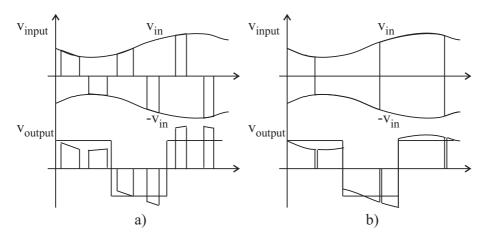

| 6.9  | Input and output stage output voltage waveforms: a) PDM and b) PWM,                                      | 111      |

| 0.5  | with the dashed line showing the desired output stage output voltage                                     | 148      |

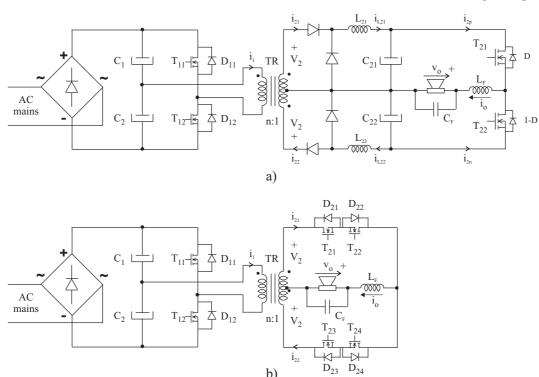

| 6.10 |                                                                                                          | 140      |

| 0.10 | and b) SICAM                                                                                             | 149      |

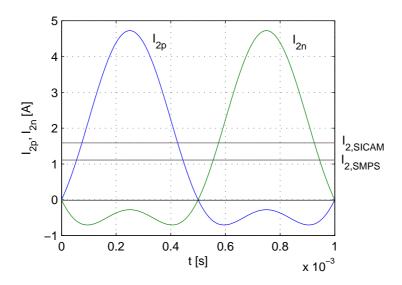

| £ 11 | Class D audio power amplifier average MOSFET currents and average                                        | 149      |

| 0.11 |                                                                                                          | 150      |

| C 10 | secondary-side SMPS and SICAM currents                                                                   | 150      |

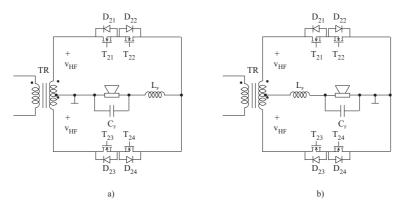

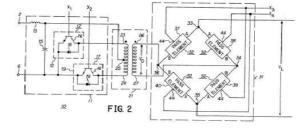

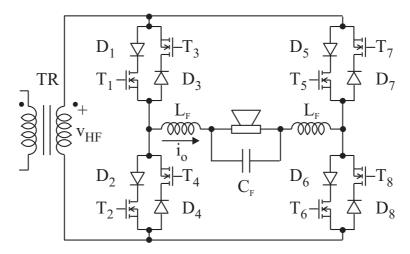

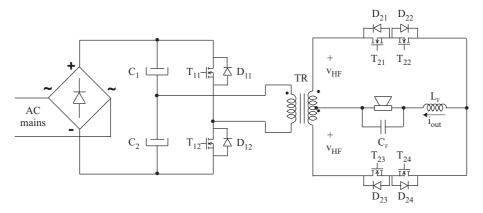

|      | Full-bridge bidirectional SICAM output stage                                                             | 152      |

|      | Scheme of SICAM with single-ended output stage                                                           | 154      |

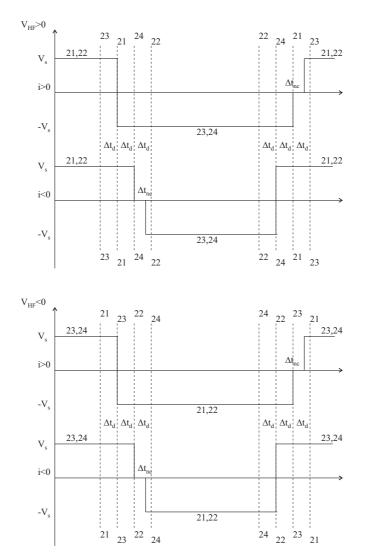

| 6.14 | Commutation diagrams with positive and negative HF-link voltages and                                     |          |

|      | load currents                                                                                            | 155      |

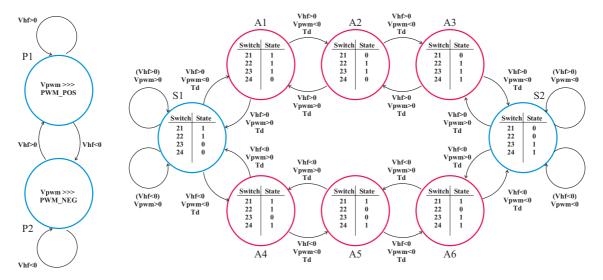

|      | State diagram of the safe-commutation switching sequence                                                 | 156      |

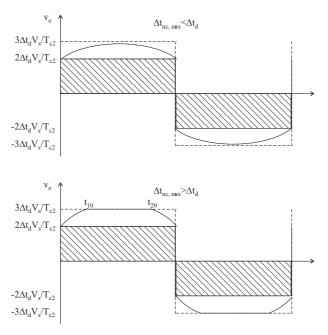

| 6.16 | Average voltage error with $\Delta t_{nc,max} < \Delta t_d$ (above) and $\Delta t_{nc,max} > \Delta t_d$ |          |

|      | (below)                                                                                                  | 158      |

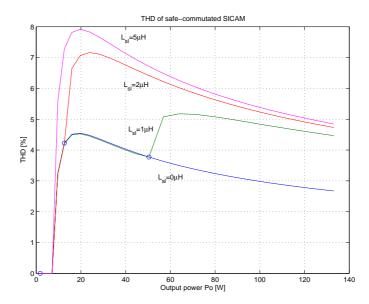

| 6.17 | THD of a safe-commutated SICAM with different secondary-side leakage                                     |          |

|      | inductances                                                                                              | 160      |

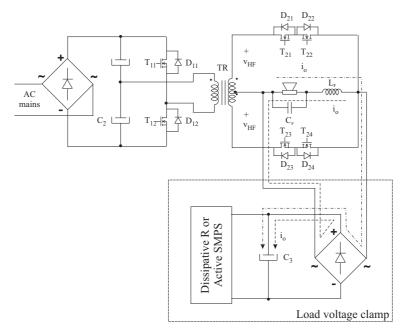

|      | Isolated SICAM with output filter and load clamp                                                         | 161      |

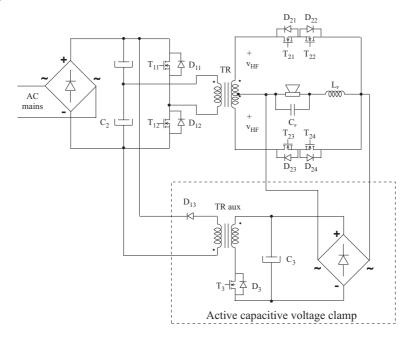

|      | Isolated SICAM with an active capacitive voltage clamp                                                   | 162      |

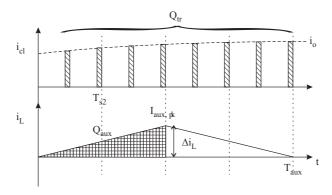

| 6.20 | Time waveforms of the active clamp                                                                       | 163      |

|      | Buck-boost auxiliary converter                                                                           | 165      |

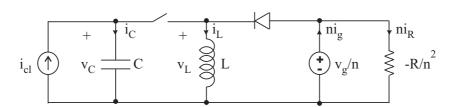

| 6.22 | Averaged switch model of the DCM flyback auxiliary converter                                             | 166      |

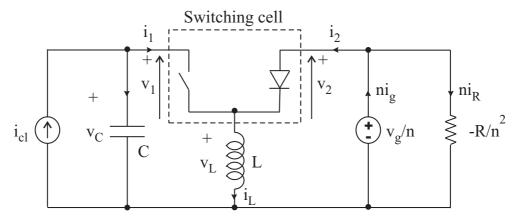

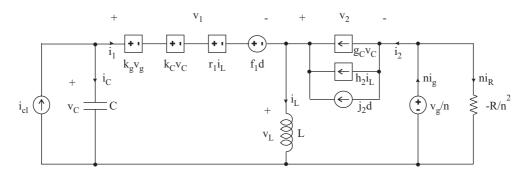

| 6.23 | Small-signal AC model of DCM flyback auxiliary converter                                                 | 167      |

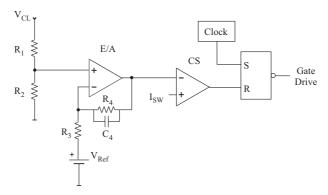

| 6.24 | Current-mode control of the auxiliary converter                                                          | 168      |

| 6.25 | Average voltage error $v_e$ of the SICAM with active capacitive voltage clamp                            | 168      |

| 6.26 | THD of SICAM with active capacitive voltage clamp                                                        | 169      |

| 6.27 | Simplified schematic of SICAM for determining output impedance                                           | 170      |

| 6.28 | Relationship between the duty cycle and the normalized peak filter ripple                                |          |

|      | current                                                                                                  | 172      |

| 6.29 | Relationship between the modulation index and the normalized average                                     |          |

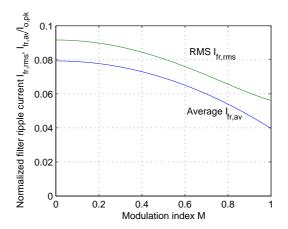

|      | and RMS filter ripple current                                                                            | 172      |

| 6.30 | Switching transitions of the upper MOSFET in a switching leg driven                                      |          |

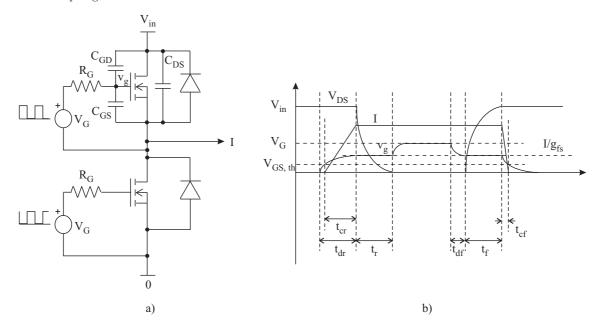

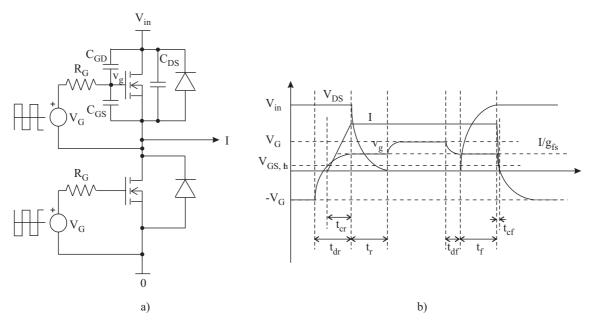

|      | with $0, V_G$ : a) schematic and b) waveforms                                                            | 176      |

| 6.31 | Switching transitions of the upper MOSFET in a switching leg driven                                      | _,,      |

| 0.01 | with $\pm V_G$ : a) schematic and b) waveforms                                                           | 177      |

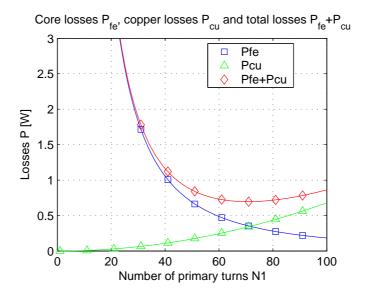

| 6.32 | Core losses $P_{fe}$ , copper losses $P_{cu}$ and total losses $P_{TR}$ as a function of the             | 111      |

| 0.02 | primary number of turns $N_1$                                                                            | 182      |

| 6 33 | a) Bidirectional switch and b) Voltage drop across the reverse conducting                                | 102      |

| 0.00 | MOSFET                                                                                                   | 182      |

| 6 24 | Energy stored in the parasitic output capacitance $E_{Cds}$ and energy stored                            | 102      |

| 0.04 |                                                                                                          | 188      |

| 6 25 | in the transformer secondary leakage inductance $E_{Lsl}$                                                |          |

| 0.00 | Output mote at man chount and Di tun chount                                                              | $\pm 03$ |

| 7.1                                                  | Modified PWM modulator for SICAM                                                                                                                                                                                                                                                                          | 196                                                                               |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

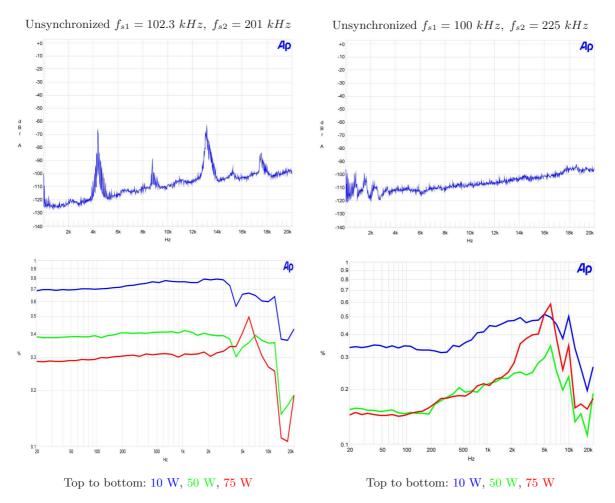

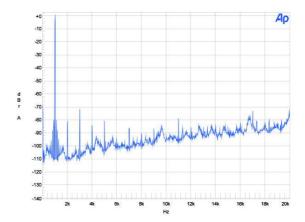

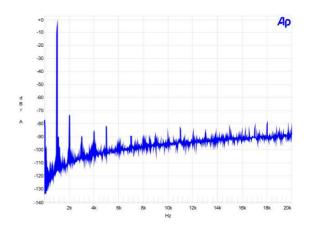

| 7.2                                                  | FFT (top) and THD+N (bottom) of two unsynchronized SICAMs with                                                                                                                                                                                                                                            |                                                                                   |

|                                                      | and without tight control of switching frequencies                                                                                                                                                                                                                                                        | 197                                                                               |

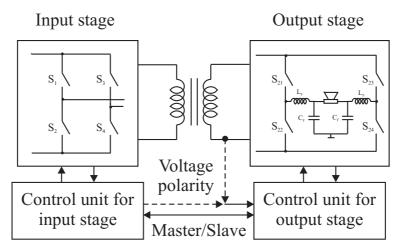

| 7.3                                                  | Master/slave control of isolated SICAM with safe commutation switching                                                                                                                                                                                                                                    |                                                                                   |

|                                                      | strategy                                                                                                                                                                                                                                                                                                  | 198                                                                               |

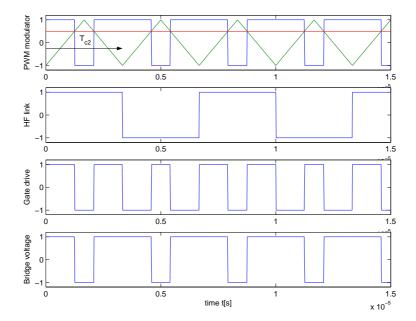

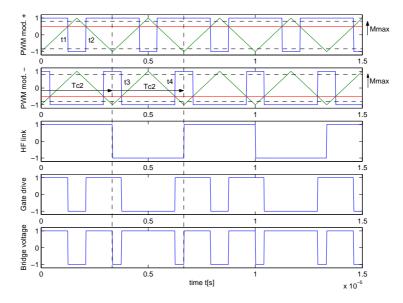

| 7.4                                                  | PWM method with 3 switchings during one carrier period $T_{c2}$                                                                                                                                                                                                                                           | 200                                                                               |

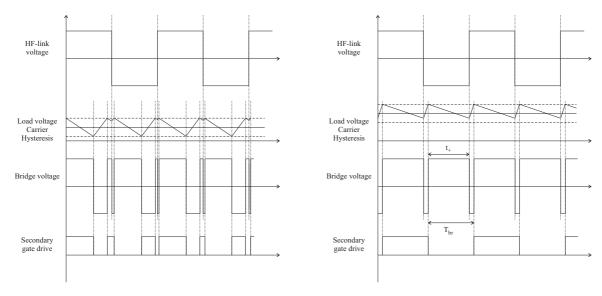

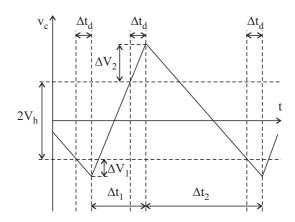

| 7.5                                                  | Proposed PWM method with 2 switchings during one carrier period $T_{c2}$                                                                                                                                                                                                                                  | 201                                                                               |

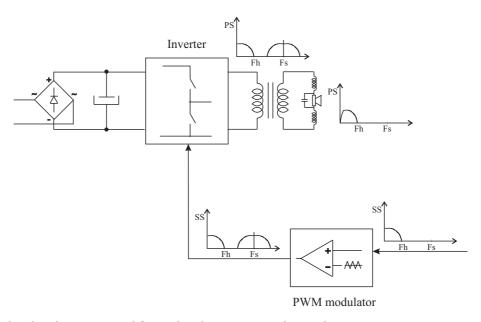

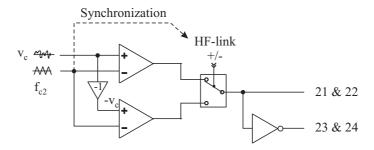

| 7.6                                                  | Optimized PWM modulator for SICAM                                                                                                                                                                                                                                                                         | 202                                                                               |

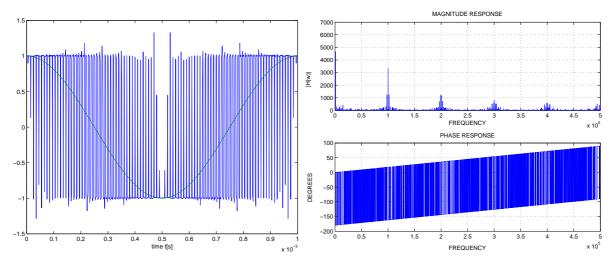

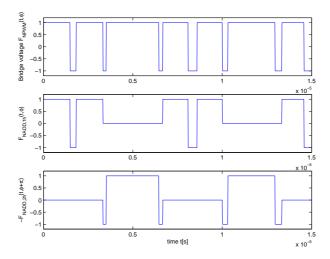

| 7.7                                                  | The new PWM pulse train (top) and its two constitutive parts (below)                                                                                                                                                                                                                                      | 203                                                                               |

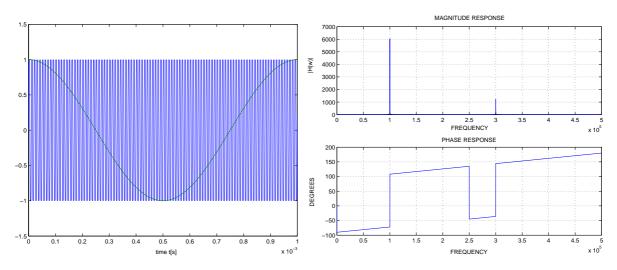

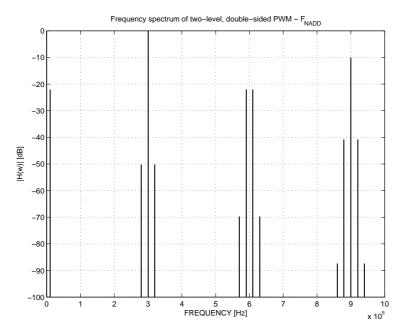

| 7.8                                                  | Frequency spectrum of the conventional PWM method $F_{NADD}$ with                                                                                                                                                                                                                                         |                                                                                   |

|                                                      | $M = 0.1, f_m = 10 \text{ kHz},$ $f_{s1} = 150 \text{ kHz}, f_{c2} = 300 \text{ kHz} \dots$                                                                                                                                                                                                               | 204                                                                               |

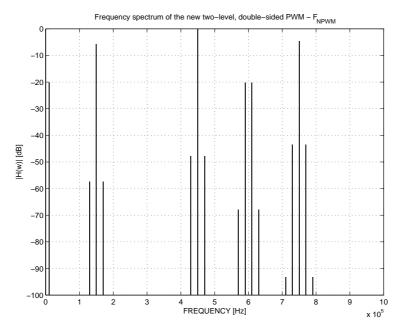

| 7.9                                                  | Frequency spectrum of the new PWM method $F_{NPWM}$ with $M=0.1$ ,                                                                                                                                                                                                                                        |                                                                                   |

|                                                      | $f_m = 10 \text{ kHz}, f_{s1} = 150 \text{ kHz},$ $f_{c2} = 300 \text{ kHz} \dots \dots \dots \dots$                                                                                                                                                                                                      | 205                                                                               |

| 7.10                                                 |                                                                                                                                                                                                                                                                                                           |                                                                                   |

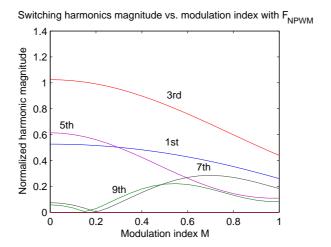

|                                                      | modulation index                                                                                                                                                                                                                                                                                          | 206                                                                               |

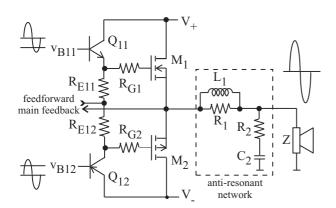

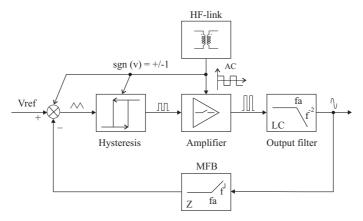

| 7.11                                                 | GLIM SOHF.                                                                                                                                                                                                                                                                                                | $\frac{1}{207}$                                                                   |

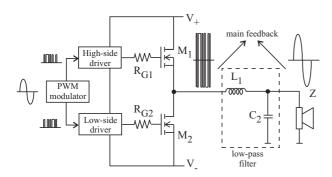

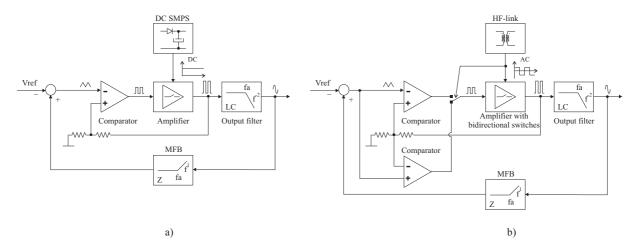

|                                                      | Practical implementation of GLIM modulator for: a) Class D audio power                                                                                                                                                                                                                                    | _ 。                                                                               |

|                                                      | amplifier and b) SOHF                                                                                                                                                                                                                                                                                     | 208                                                                               |

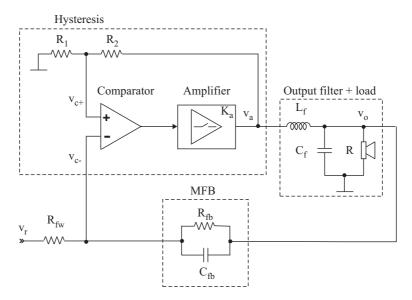

| 7.13                                                 | Schematic of GLIM for Class D audio power amplifier                                                                                                                                                                                                                                                       | 208                                                                               |

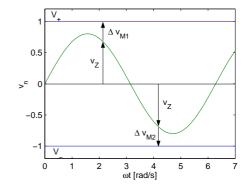

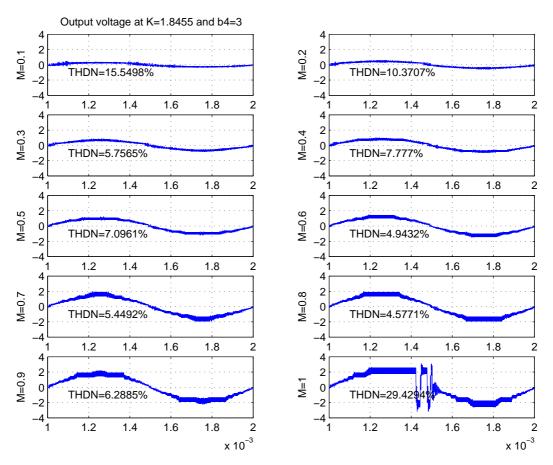

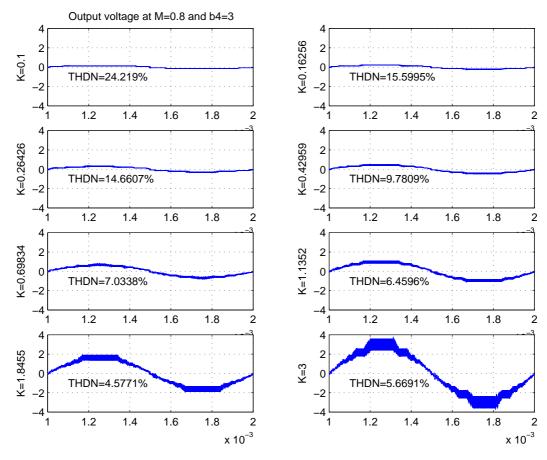

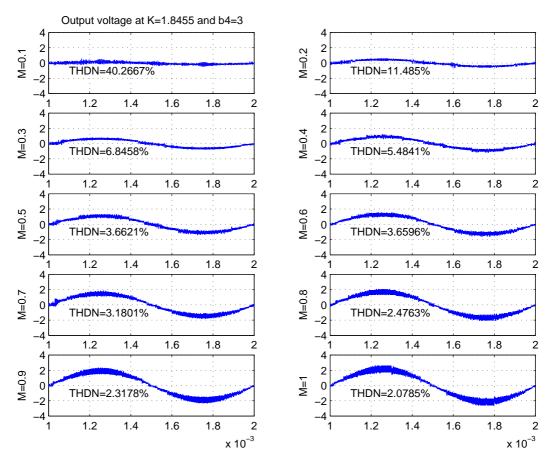

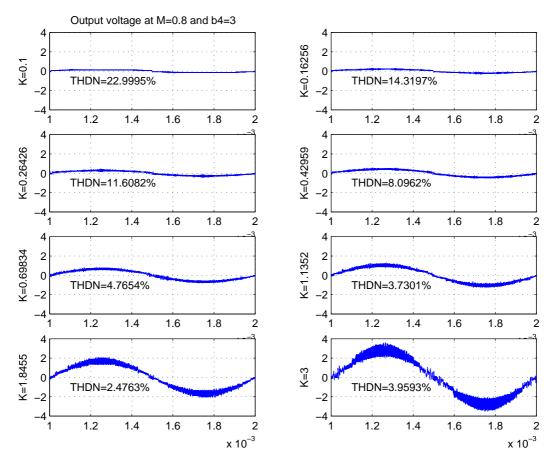

|                                                      |                                                                                                                                                                                                                                                                                                           | 210                                                                               |

|                                                      | Locked operation with $M \geq M_{lim}^*$                                                                                                                                                                                                                                                                  |                                                                                   |

|                                                      |                                                                                                                                                                                                                                                                                                           | 211                                                                               |

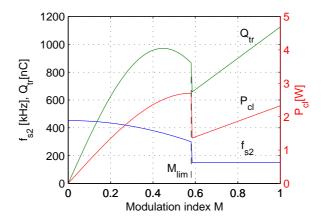

|                                                      | Output stage switching frequency, transferred charge and clamp power (in                                                                                                                                                                                                                                  |                                                                                   |

|                                                      |                                                                                                                                                                                                                                                                                                           | 212                                                                               |

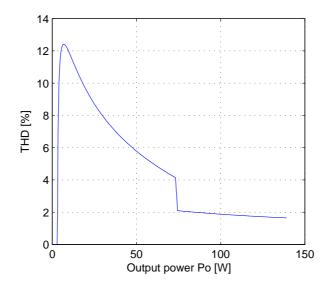

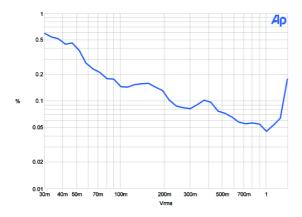

| 7.18                                                 | THD of SICAM with active capacitive voltage clamp                                                                                                                                                                                                                                                         |                                                                                   |

|                                                      | Block diagram of simple output voltage control                                                                                                                                                                                                                                                            | 214                                                                               |

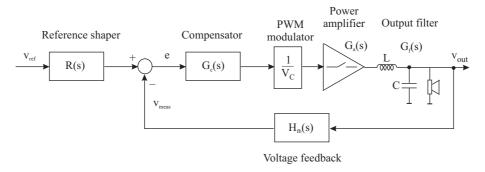

|                                                      |                                                                                                                                                                                                                                                                                                           | 214                                                                               |

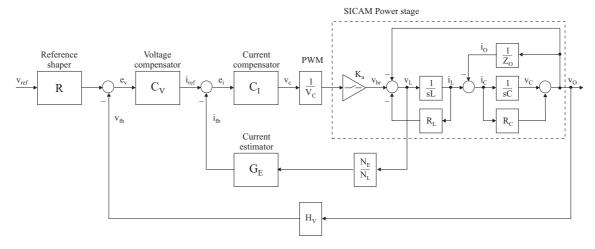

| 1.20                                                 |                                                                                                                                                                                                                                                                                                           |                                                                                   |

|                                                      |                                                                                                                                                                                                                                                                                                           |                                                                                   |

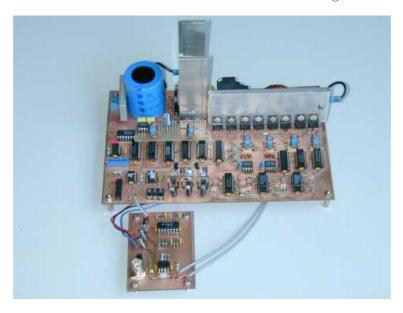

| 8.1                                                  | Photograph of the prototype master/slave-operated SICAM                                                                                                                                                                                                                                                   |                                                                                   |

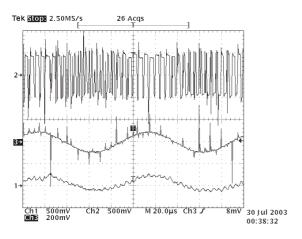

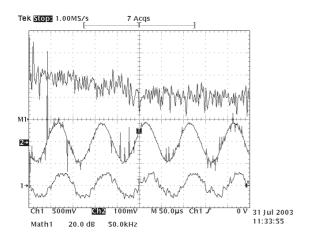

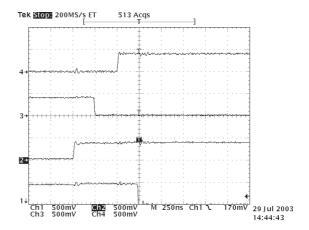

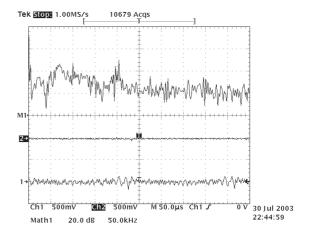

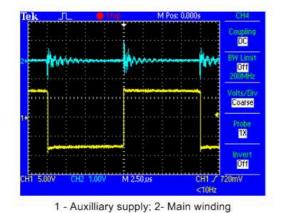

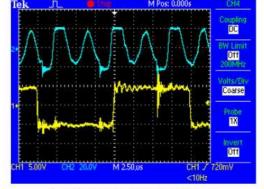

|                                                      | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver                                                                                                                                                                             |                                                                                   |

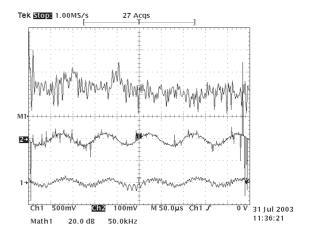

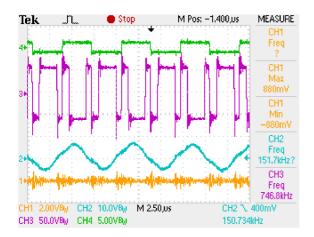

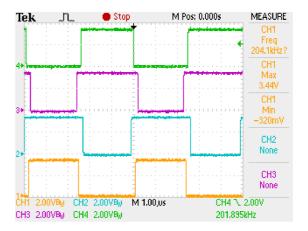

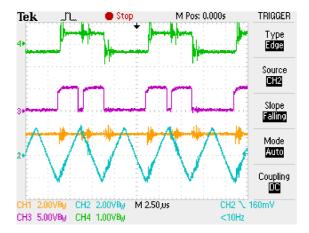

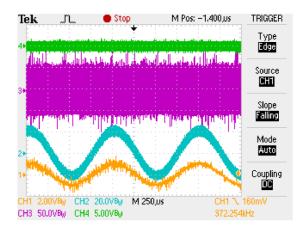

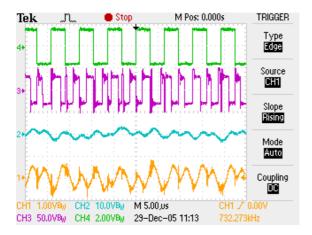

| 8.1                                                  | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line                                                                                                     |                                                                                   |

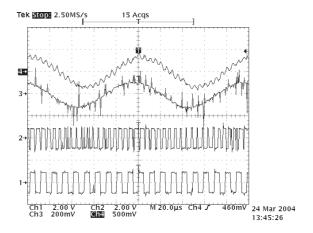

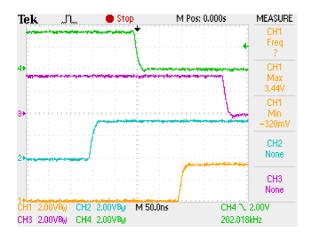

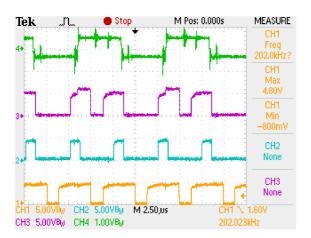

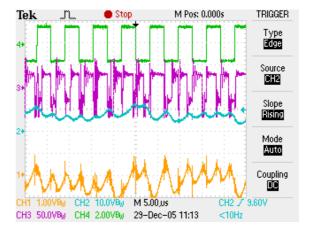

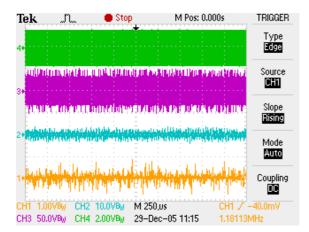

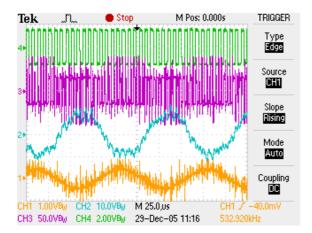

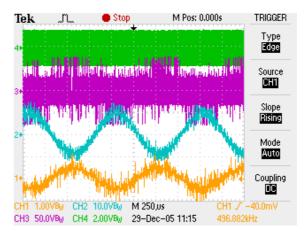

| 8.1                                                  | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity $(T_1/T_4 \text{ driving signal})$ (all                | 218                                                                               |

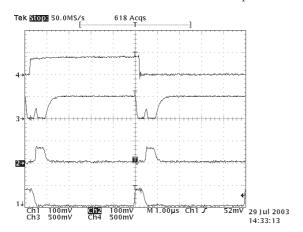

| 8.1<br>8.2                                           | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity $(T_1/T_4 \text{ driving signal})$ (all probes $10x$ ) |                                                                                   |

| 8.1                                                  | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity $(T_1/T_4 \text{ driving signal})$ (all probes $10x$ ) | 218                                                                               |

| 8.1<br>8.2                                           | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity $(T_1/T_4 \text{ driving signal})$ (all probes $10x$ ) | <ul><li>218</li><li>219</li></ul>                                                 |

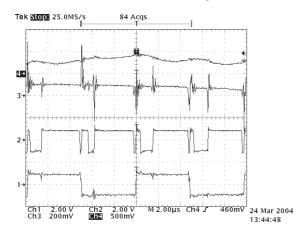

| 8.1<br>8.2<br>8.3                                    | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity $(T_1/T_4$ driving signal) (all probes $10x$ )         | <ul><li>218</li><li>219</li></ul>                                                 |

| 8.1<br>8.2                                           | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li></ul>                                     |

| 8.1<br>8.2<br>8.3                                    | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li></ul>                                     |

| 8.1<br>8.2<br>8.3                                    | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li><li>219</li></ul>                         |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5                      | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li></ul>                                     |

| 8.1<br>8.2<br>8.3                                    | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li><li>219</li><li>219</li></ul>             |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6               | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li><li>219</li><li>219</li></ul>             |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5                      | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li><li>219</li><li>219</li><li>219</li></ul> |

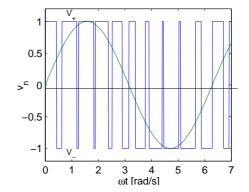

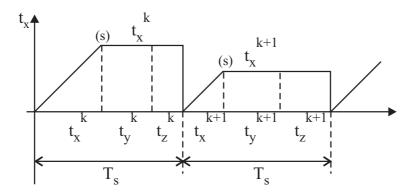

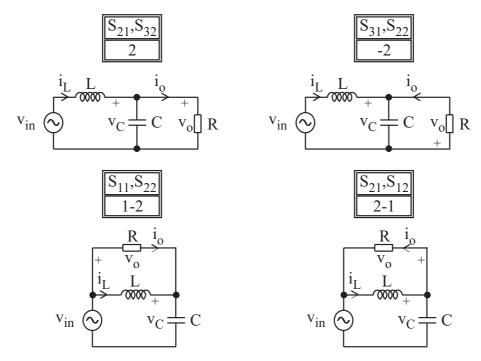

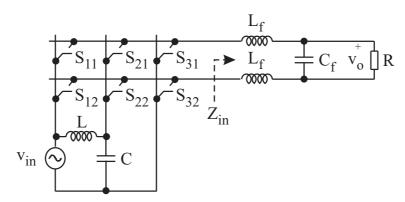

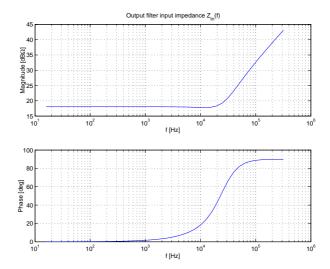

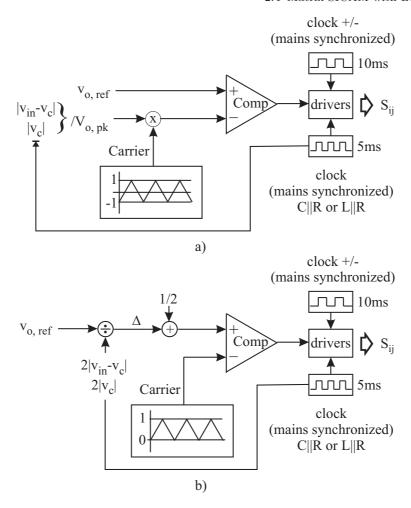

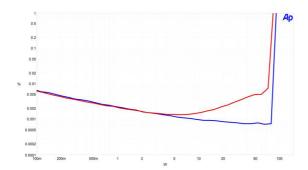

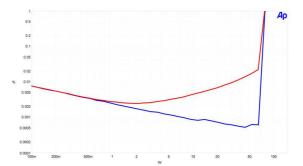

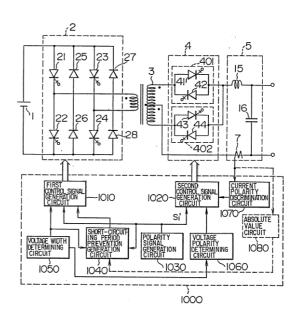

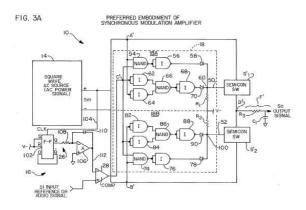

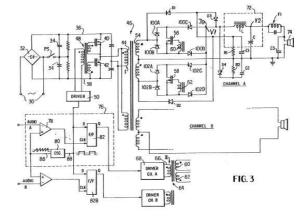

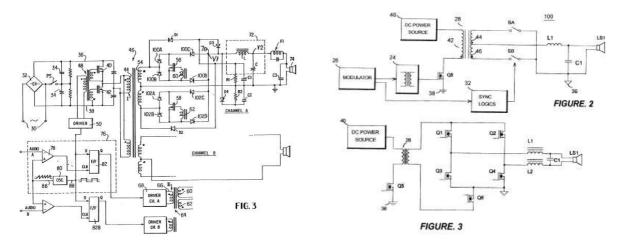

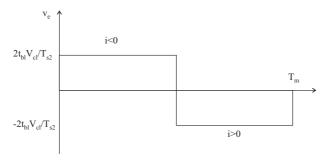

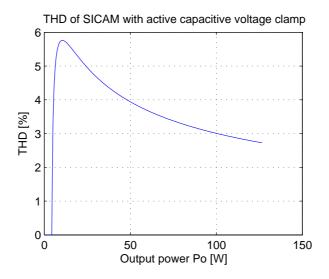

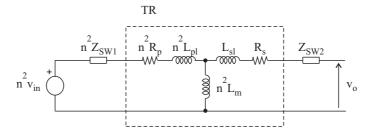

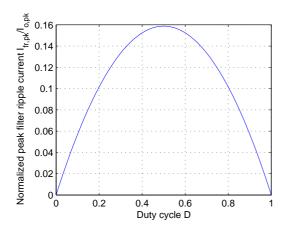

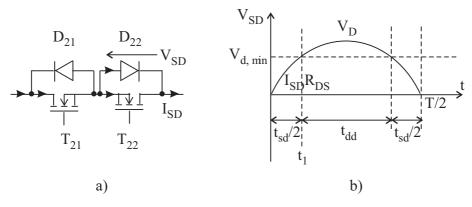

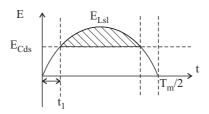

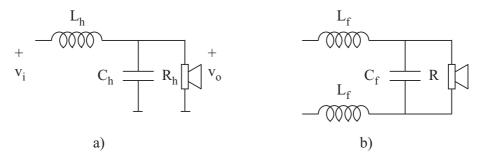

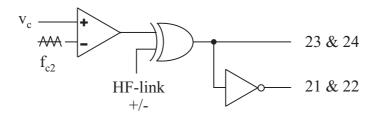

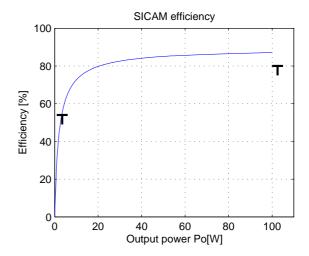

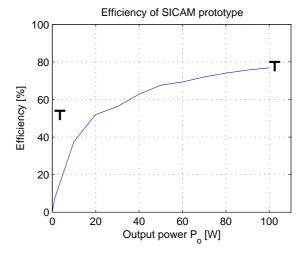

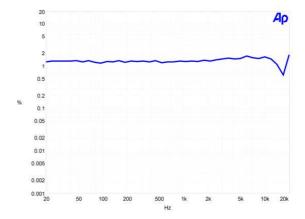

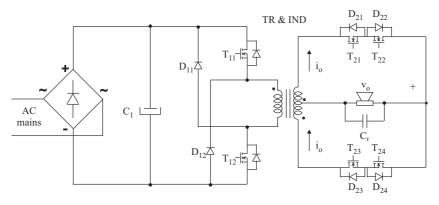

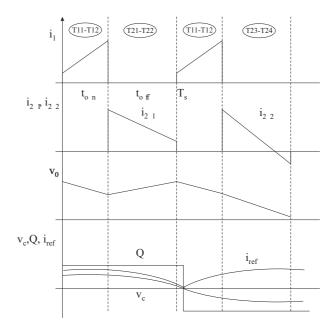

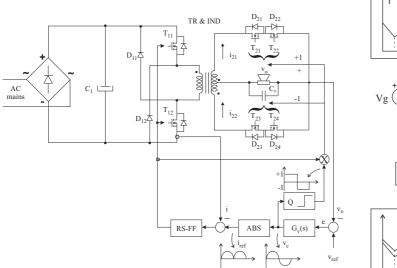

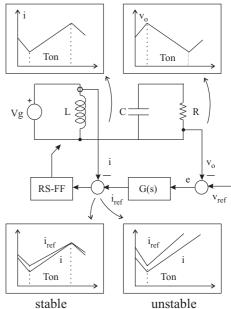

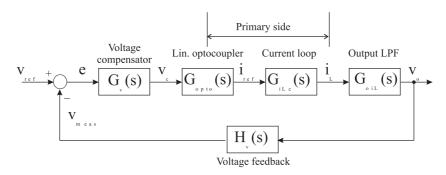

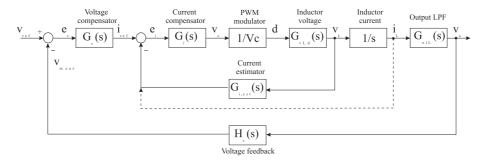

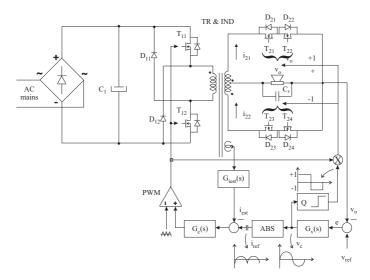

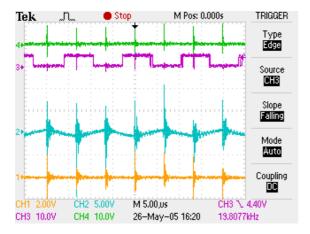

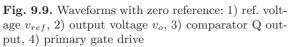

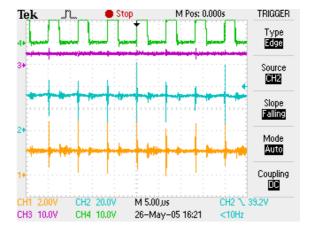

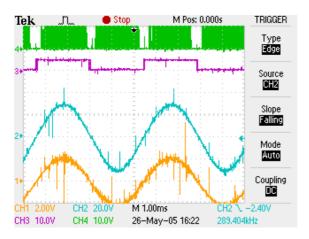

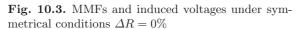

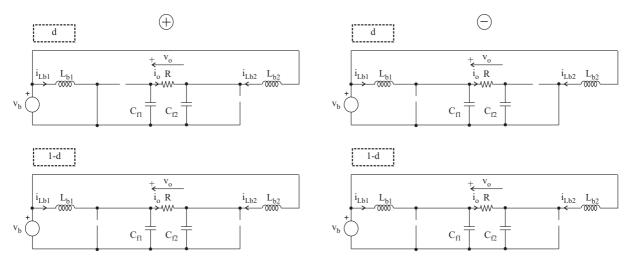

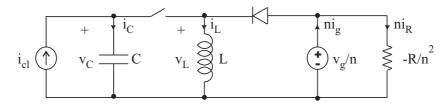

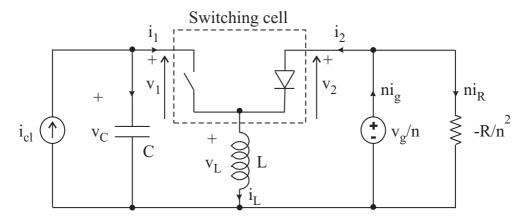

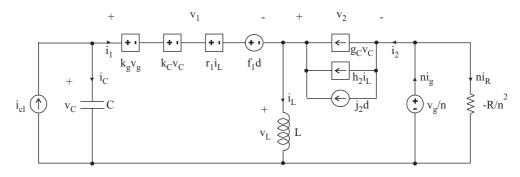

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7        | Photograph of the prototype master/slave-operated SICAM Detailed master/slave SICAM operation: 1) Input stage M/S line driver base voltage, 2) output stage M/S line driver base voltage, 3) M/S line voltage, and 4) input stage voltage polarity ( $T_1/T_4$ driving signal) (all probes $10x$ )        | <ul><li>218</li><li>219</li><li>219</li><li>219</li><li>219</li><li>219</li></ul> |