### Technical University of Denmark

### **High-speed Integrated Circuits for electrical/Optical Interfaces**

Jespersen, Christoffer Felix; Dittmann, Lars

Publication date: 2008

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Jespersen, C. F., & Dittmann, L. (2008). High-speed Integrated Circuits for electrical/Optical Interfaces.

### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# High-Speed Integrated Circuits for Electrical/Optical Interfaces at 100 Gb/s

Christoffer F. Jespersen

Communication Technology

Department of Photonics Engineering, DTU Fotonik

TECHNICAL UNIVERSITY OF DENMARK

Kgs. Lyngby, Denmark 2006

High-Speed Integrated Circuits for Electrical/Optical Interfaces at 100 Gb/s

Christoffer Felix Jespersen

Kgs. Lyngby, Denmark, 2006

Technical University of Denmark Department of Photonics Engineering, DTU Fotonik Communication Technology DK-2800 Kgs. Lyngby, Denmark Phone: +45 4525 6352

©2006 Christoffer F. Jespersen

### Abstract

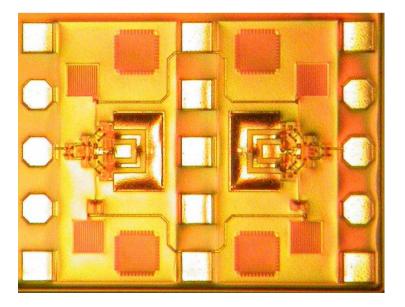

This thesis is part of the general effort to increase the bandwidth of communication networks. The thesis presents the results of the design of several high-speed electrical circuits for an electrical/optical interface. These circuits have been a contribution to the ESTA project in collaboration with the OptCom project. The aim of the ESTA project was to investigate issues at 100 Gb/s and beyond, such as architecture and components. The OptCom project had a more tangible purpose; to create a 100 Gb/s optical/electrical transceiver demonstrator. The thesis focuses on the design of VCO, LA and CDR circuits at the receiver interface, though VCOs are also found in the transmitter, where a multitude of independent sources have to be synchronized before they are multiplexed. The circuits are based on an InP DHBT process (VIP-2) supplied by Vitesse and made publicly available as MPW. The VIP-2 process represents the avant-garde of InP technology, with  $f_t$  and  $f_{max}$  well above 300 GHz.

Principles of high speed design are presented and described as a useful background before proceeding to circuits. A static divider is used as an example to illustrate many of the design principles.

Theory and fundamentals of LC-oscillators, such as oscillator criteria, phase noise and different topologies, are given as background.

The theory of PLL circuits is also presented.

Guidelines and suggestions for static divider, VCO, LA and CDR design are presented using static divider,  $50\text{-}100~\mathrm{GHz}$  VCO and  $100\mathrm{Gb/s}$  LA+CDR circuits as examples.

Finally, it is concluded that the VIP-2 process is suitable technology for creating circuits for  $100~{\rm Gb/s}$  communication networks.

**Keywords:** Indium Phosphide (InP), DHBT, VCO, Colpitt, Static Divider, CDR, PLL, Transceiver

# Sammenfatning på dansk

Transmission af data (bl.a. telefoni) sker i dag ved brug af optiske fiber, som har stor båndbredde og lang rækkevidde. Optiske kommunikationssystemer består af optiske fiber og knudepunkter, som benævnes routere og switche. I knudepunkterne foretages modtagelse og behandling af den indkomne data samt sendning af udadgående data. Behandlingen af data kan ske både optisk og elektrisk. Enkle valg kan foretages optisk, men mere kompleks behandling må ske elektrisk. Det senere kræver en omdannelse af signalet fra det optiske til det elektriske domæne. Ligeledes kan der ske en omdannelse af et signal fra det elektriske til optiske domæne.

Projektet omhandler udvikling af elektroniske kredse til grænsefladen mellem det optiske og det elektriske domæne, samt at forhøje båndbredden fra  $10\text{-}40~\mathrm{Gb/s}$  (i eksisterende systemer) til  $100~\mathrm{Gb/s}$ . Forruden selve den fysiske omdannelse af signalet, mellem lys og strøm, må der tages hensyn til både det optiske signals tab af synkronisering og forholdsvis store båndbredde. Det første skyldes at data transmitteres optisk uden brug af et tilhørende klokkesignal som angiver hvornår forskellige bits i datastrømmen begynder og slutter. Uden denne synkronisering er det vanskeligt at fortolke og genskabe den oprindelige information. Det andet skyldes at optiske signaler kan transmitteres ved større båndbredde end hvad som er fysik muligt eller økonomisk rimeligt at behandle elektronisk.

En komplet elektrisk/optisk grænseflade består af mange forskellige kredse. Dette projekt har fokuseret på variable oscillatorer (VCO), som benyttes i flere af kredsene, omformning af frekvens og fase (static divider) samt genskabelse af data og synkronisering (LA og CDR). Genskabelsen er en kompleks proces hvor der foretages en genskabelse af det oprindelige signal i form, amplitude og synkronisering (3R). Den store båndbrede har stillet høje krav til de elektroniske kredse, som er blevet produceret i en avanceret InP proces fra Vitesse (VIP-2).

# List of Appended Papers

### Paper A W-Band VCOs in InP DHBT for Electrical/Optical Transceivers.

C. Jespersen

7th Topical Workshop on Heterostructure Microelectronics (TWHM 2007), IEEE, 21-24 August 2007.

### Paper B 100 Gb/s CDR in InP DHBT.

C. Jespersen Manuscript.

# Related papers

I Design and test of InP DHBT ICs for a 100  $\mathrm{Gb/s}$  demonstrator system.

T. Swahn, J. Hallin and T. Kjellberg.

International indium phosphide and related materials conference proceedings, IEEE, 79–84, 7-11 May 2006.

- II A 165-Gb/s 4:1 multiplexer in InP DHBT technology.

- J. Hallin, T. Kjellberg and T. Swahn.

Journal of Solid State Circuits, IEEE, 41:2209-2214, October 2006.

- III A 100-Gb/s 1:4 Demultiplexer in InP DHBT technology.

- J. Hallin, T. Kjellberg and T. Swahn.

Journal of Solid State Circuits, IEEE, 41:2209-2214, October 2006.

- IV Flip-Chip mounted 1:4 demultiplexer IC in InP DHBT technology operating up to 100 Gb/s.

- C. Kärnfelt, J. Hallin, T. Kjellberg, B. Hansson and T. Swahn. Manuscript.

- V 104 Gb/s 2e11-1 and 110 Gb/s 2e9-1 PRBS generator in InP HBT technology.

- T. Kjellberg, J. Hallin and T. Swahn.

International conference digest of technical papers solid-state circuits, IEEE, 2160-2169, February 6-9 2006.

# Contents

| A  | bstra | act                                            | iii          |

|----|-------|------------------------------------------------|--------------|

| Sa | mm    | enfatning på dansk                             | $\mathbf{v}$ |

| Li | st of | Appended Papers                                | vii          |

| 1  | Intr  | roduction                                      | 1            |

|    | 1.1   | The future of high speed communication systems | 1            |

|    |       | 1.1.1 The need for 40 & 100 GbE                | 2            |

|    |       | 1.1.2 Technical feasibility                    | 2            |

|    | 1.2   | Transceiver components                         | 3            |

|    |       | 1.2.1 Scope of the thesis                      | 3            |

|    |       | 1.2.2 State of the art circuits                | 5            |

|    |       | 1.2.2.1 LA                                     | 5            |

|    |       | 1.2.2.2 CDR                                    | 6            |

|    |       | 1.2.2.3 Multiplexer and demultiplexer          | 6            |

|    |       | 1.2.2.4 Static divider                         | 7            |

|    |       | 1.2.2.5 VCO                                    | 7            |

| 2  | Hig   | h-speed design                                 | 11           |

|    | 2.1   | Current Mode Logic                             | 11           |

|    |       | 2.1.1 ECL operation                            | 12           |

|    |       | 2.1.2 CML or ECL                               | 14           |

|    | 2.2   | Signaling and transmission lines               | 16           |

|    |       | 2.2.1 Signal wavelength                        | 16           |

|    |       | 2.2.2 Differential signalling                  | 17           |

|    |       | 2.2.3 Termination and reflection               | 19           |

|    |       | 2.2.4 Conductor modelling and realisation      | 22           |

|    | 2.3   | $f_t$ and $f_{max}$                            | 23           |

|    | 2.4   | Current sources                                | 26           |

|    |       | 2.4.1 Resistive current source                 | 26           |

|    |       | 2.4.2 Current mirror                           | 27           |

|    | 2.5   | Layout                                         | 29           |

|    |       | 2.5.1 Power supply & distribution              | 30           |

xii CONTENTS

| 3 | Sta           | tic divider                                                                      | 35  |

|---|---------------|----------------------------------------------------------------------------------|-----|

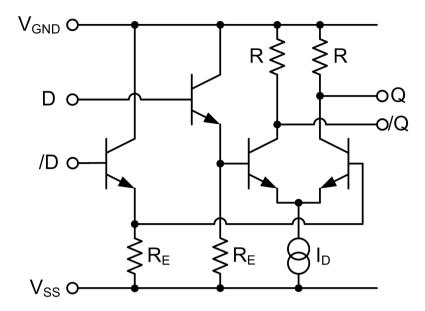

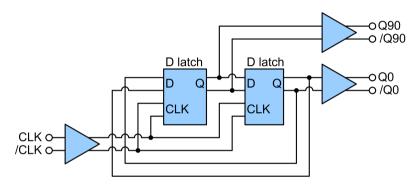

|   | 3.1           | T flip-flop                                                                      | 36  |

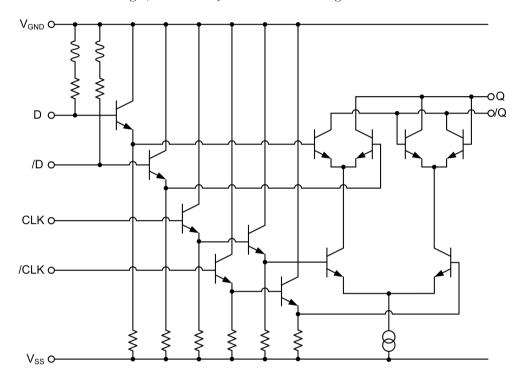

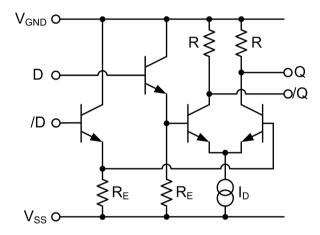

|   | 3.2           | D latch                                                                          | 37  |

|   | 3.3           | Buffers                                                                          | 39  |

|   | 3.4           | Simulation                                                                       |     |

|   | 3.5           | Measurement                                                                      | 41  |

| 4 | $\mathbf{vc}$ | 0                                                                                | 45  |

|   | 4.1           | Phase noise & jitter                                                             | 45  |

|   | 4.2           | Design flow                                                                      | 47  |

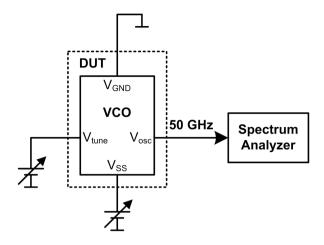

|   | 4.3           | Testing                                                                          | 50  |

|   | 4.4           | Colpitt VCO circuit #1 (microstrip)                                              | 52  |

|   | 4.5           | Negative resistance VCO circuit                                                  | 56  |

|   | 4.6           | Colpitt VCO circuit #2 (coplanar waveguide)                                      | 58  |

|   | 4.7           | VCO conclusion                                                                   | 61  |

| 5 | Pha           | se Locked Loops                                                                  | 65  |

|   | 5.1           | Phase detector                                                                   | 66  |

|   | 5.2           | Low-pass filter                                                                  |     |

|   | 5.3           | Linear amplifier                                                                 |     |

|   | 5.4           | VCO                                                                              |     |

|   | 5.5           | Divider                                                                          | 70  |

|   | 5.6           | PLL                                                                              | 70  |

|   |               | 5.6.1 Locked state                                                               | 70  |

|   |               | 5.6.1.1 PLL transfer function                                                    | 71  |

|   |               | 5.6.1.2 PLL error transfer function                                              | 73  |

|   |               | 5.6.1.3 PLL error response                                                       |     |

|   |               | 5.6.2 Tracking and acquisition                                                   | 78  |

| 6 | Clo           | ck and data recovery                                                             | 81  |

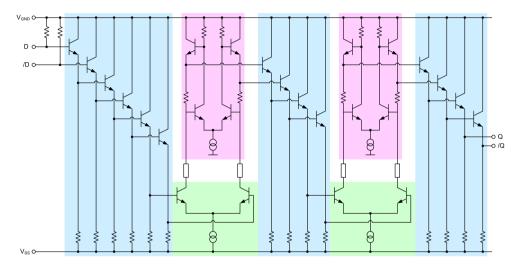

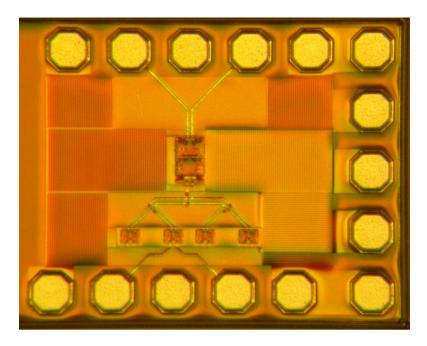

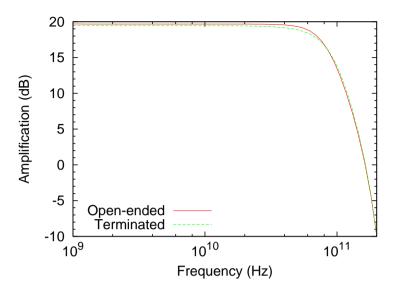

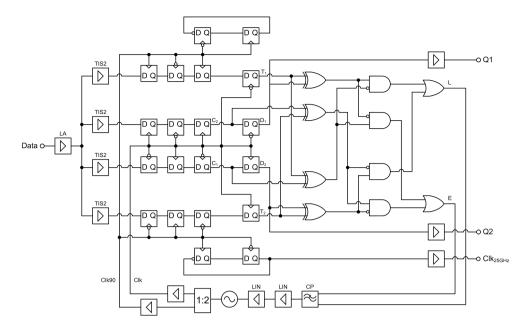

|   | 6.1           | Architecture                                                                     | 84  |

|   | 6.2           | Receiver interface                                                               | 86  |

|   | 6.3           | Limiting amplifier                                                               |     |

|   | 6.4           | Phase detector                                                                   |     |

|   |               | 6.4.1 Hogge-type phase detector (linear)                                         | 91  |

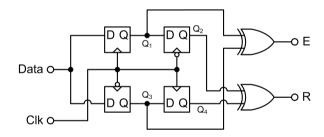

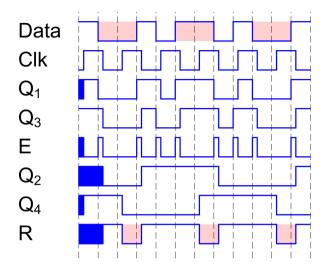

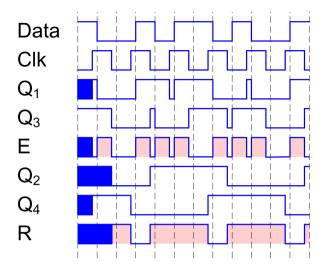

|   |               | 6.4.2 Alexander-type phase detector (non-linear)                                 | 93  |

|   |               | 6.4.3 Double Alexander-type phase detector (non-linear)                          | 95  |

|   |               | 6.4.4 D flip-flops                                                               | 98  |

|   |               | 6.4.5 Logical gates                                                              | 102 |

|   |               | 6.4.5.1 XOR gates                                                                | 102 |

|   |               | $6.4.5.2  \text{AND/NAND gates} \dots \dots \dots \dots \dots \dots \dots \dots$ | 104 |

|   | 6.5           | Charge-pump filter                                                               |     |

|   |               | 6.5.1 Hogge-type phase detector input                                            |     |

|   |               | 6.5.2 Double Alexander-type phase detector input                                 |     |

|   |               | 6.5.3 Charge-pump filter implementation                                          |     |

|   | 6.6           | Buffers                                                                          |     |

|   | 6.7           | Linear amplifier                                                                 | 112 |

CONTENTS xiii

|              | <ul><li>6.8</li><li>6.9</li><li>6.10</li></ul> | 6.8.1<br>6.8.2<br>CDR c<br>6.9.1<br>6.9.2<br>Sugges<br>6.10.1 | nentation of CDR circuits  Double Alexander-type CDR circuit  Hogge-type CDR circuit  ircuit measurements  VCO measurement results  CDR measurement results  tions and improvements  Design rule restrictions | . 116<br>. 121<br>. 122<br>. 123<br>. 126<br>. 127<br>. 128 |

|--------------|------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|              |                                                |                                                               | Circuit improvements                                                                                                                                                                                          |                                                             |

| Cc           | nclu                                           | sions                                                         |                                                                                                                                                                                                               | 131                                                         |

| Ac           | knov                                           | vledger                                                       | nent                                                                                                                                                                                                          | 133                                                         |

| Bi           | bliog                                          | raphy                                                         |                                                                                                                                                                                                               | 145                                                         |

| A            | A.1<br>A.2                                     | Different<br>Inducti<br>A.2.1<br>A.2.2<br>Relativ             | Alculations Intial stage                                                                                                                                                                                      | . 150<br>. 151<br>. 153                                     |

| В            | B.1                                            | HBT in                                                        | mulations  nput capacitance  al range of characteristic impedance for transmission lines (mi-                                                                                                                 |                                                             |

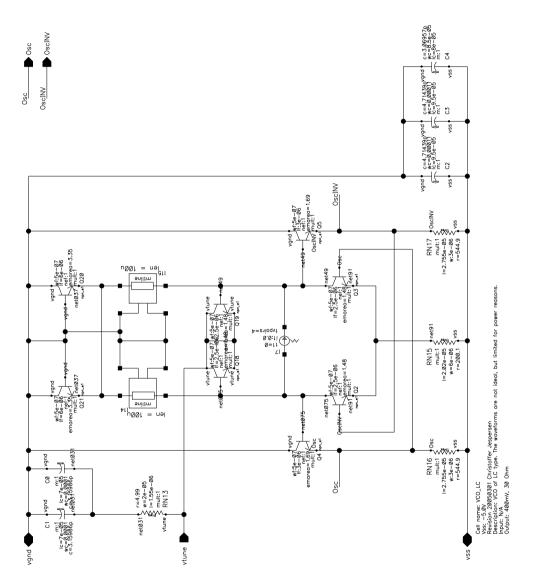

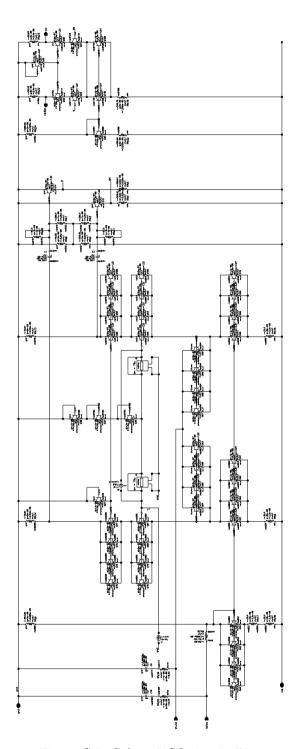

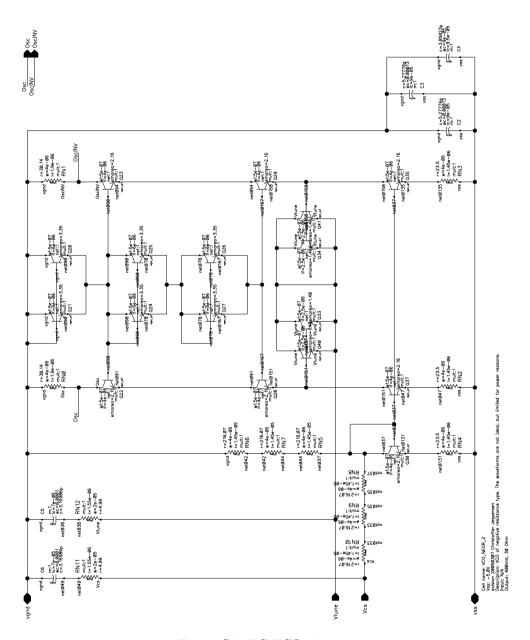

| $\mathbf{C}$ | Sche                                           | -                                                             | s of select circuits                                                                                                                                                                                          | 159                                                         |

|              |                                                |                                                               | n table for W-band measurements                                                                                                                                                                               | 163                                                         |

|              |                                                |                                                               | n table 101 W band measurements                                                                                                                                                                               |                                                             |

| Ľ            | VIP                                            | - 4                                                           |                                                                                                                                                                                                               | 165                                                         |

xiv CONTENTS

# Abbreviations and notations

3R Reshape, Reamplify & Retime

AC Alternating Current AGC Automatic-Gain-Control

AHDL Analog Hardware Description Language

BER Bit Error Rate

BJT Bipolar Junction Transistor CDR Clock and Data Recovery CID Consecutive Identical Digits

CML Current Mode Logic

CMOS Complementary Metal-Oxide-Semiconductor

CPW CoPlanar Waveguide

DC Direct Current

DEMUX DEMUltipleXer

DFF D Flip-Flop

DFT Discrete Fourier Transformation

DHBT Double Heterostructure Bipolar Transistor

DUT Device Under Test

ECL Emitter-Coupled Logic

EF Emitter Follower

FEC Forward Error Correction FFT Fast Fourier Transformation

GaAs Gallium Arsenide

GbE Gigabit Ethernet

GSG Ground-Signal-Ground

HB Harmonic Balance

HBT Heterostructure Bipolar Transistor HEMT High Electron Mobility Transistor

HSE Higher Speed Ethernet HSSG Higher Speed Study Group

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers, inc.

$\begin{array}{ll} \text{InP} & \text{Indium Phosphide} \\ \text{I/O} & \text{Input/Output} \end{array}$

ISI Inter Symbol Interference

LA Limiting Amplifier

xvi CONTENTS

LSI Large Scale Integration

LO Local Oscillator

M# Metal layer #

MAC Media Access Control

MC2 ???

MIM Metal-Insulator-Metal

MMF MultiMode Fiber

MPW Multi-Project Wafer

MSI Medium-Scale Integration

MUX MUltipleXer

NRZ Non-Return-to-Zero encoding OM3 Optimized Multimode fiber type 3

OTN Optical Transport Network

PD Phase Detector

PLL Phase Locked Loop

PLS Physical Layer Signaling

PRBS Pseudo-Random Binary Sequence

RMS Root Mean Square

RLGC Resistance, inductance, conductance, Capacitance

RZ Return-to-Zero encoding

SiGe Silicon-Germanium

SMF Single Mode Fiber

SNR Signal to Noise Ratio

SSI Small-Scale Integration

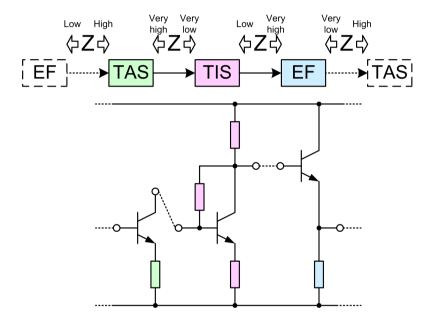

TAS TransAdmittance Stage

TFF T Flip-Flop

TIA TransImpedance Amplifier

TIS TransImpedance Stage

TTL Transistor-Transistor Logic

TWA Travelling Wave Amplifier

VCO Voltage Controlled Oscillator

VDO Video On Demand

# Chapter 1

# Introduction

# 1.1 The future of high speed communication systems<sup>1</sup>

IEEE established the 802.3 Higher Speed Study Group (HSSG) to develop a road map ahead of 10 GbE. The HSSG was later transformed into the P802.3ba 40 Gb/s and 100 Gb/s Ethernet Task Force, once the preliminary study was complete. The objective of the Task Force is to amend the IEEE 802.3 standard to encompass increased data rates while preserving as much of the current IEEE 802.3 standard as possible. The target completion date for the amendment is June 2010.

The amendment will support MAC data rates of 40 & 100 Gb/s and provide Physical Layer specifications which support 40 & 100 Gb/s operation over various media, as summarised in table 1.1. It must also provide the appropriate support for OTN. Amending the existing standard will maintain compatibility with the installed base of IEEE 802.3 interfaces, previous investments in research and development as well as principles of network operation and management. The amendment will provide for the interconnection of equipment satisfying the distance requirements of the intended applications.

$<sup>^1</sup>Information$  relating to the progress of the 40 & 100 GbE amendment to IEEE 802.3 can be found on the IEEE P802.3ba 40 Gb/s and 100 Gb/s Ethernet Task Force homepage: http://www.ieee802.org/3/ba/

| Medium                              | 40 GbE | 100 GbE |

|-------------------------------------|--------|---------|

| Backplane ≥1 m                      |        |         |

| Cu cable $\geq 10 \text{ m}$        |        |         |

| $OM3 \text{ MMF} \ge 100 \text{ m}$ |        |         |

| $SMF \ge 10 \text{ Km}$             |        |         |

| $SMF \ge 40 \text{ Km}$             |        |         |

Table 1.1: Physical layer specifications to be defined by the HSE Task Force.

#### 1.1.1 The need for 40 & 100 GbE

The demand is driven by applications that have been demonstrated to require bandwidth beyond the existing capabilities, as defined by the 10 GbE standard. These include data centers, Internet exchanges, high performance computing and VOD. Bandwidth requirements for computing and core networking applications are growing at different rates, which necessitates the definition of two distinct data rates for the next generation of Ethernet networks in order to address these applications in a cost effective manner:

- Servers, high performance computing clusters, blade servers, storage area networks and network attached storage all currently make use of GbE and 10 GbE.

I/O bandwidth projections for server and computing applications indicate that there will be a significant market potential for a 40 Gb/s Ethernet interface.

- Core networking applications have demonstrated the need for bandwidth beyond existing capabilities and the projected bandwidth requirements for computing applications. Switching, routing, and aggregation in data centers, Internet exchanges and service provider peering points, and high bandwidth applications, such as video on demand and high performance computing environments, have demonstrated the need for a 100 Gb/s Ethernet interface.

#### 1.1.2 Technical feasibility

The principle of scaling the IEEE 802.3 MAC to higher speeds has been well established by previous work within IEEE 802.3, such as GbE & 10 GbE. The principle of building bridging equipment which performs rate adaptation between IEEE 802.3 networks operating at different speeds has been amply demonstrated by the broad set of product offerings that bridge between 10, 100, 1000, and 10000 Mb/s. Systems with an aggregate bandwidth of greater than or equal to 100 Gb/s have been demonstrated and deployed in operational networks. The IEEE 802.3 amendment will build on the array of Ethernet component and system design experience, and the broad knowledge base of Ethernet network operation:

- The experience gained in the development and deployment of 10 Gb/s technology is applicable to the development of specifications for components at higher speeds. For example, parallel transmission techniques allow reuse of 10 Gb/s technology and testing.

- Component vendors have presented data on the feasibility of the necessary components for higher speed solutions. Proposals, which either leverage existing technologies or employ new technologies, have been provided.

The reliability of Ethernet components and systems can be projected in the target environments with a high degree of confidence. Presentations demonstrating this have been provided by participants in the 802.3 HSSG.

### 1.2 Transceiver components

A glance at the block diagrams of various communication systems reveal that all systems, regardless of transmission medium, are made from a combination of just a few basic building blocks. The VCO, static divider, limiting amplifier and the CDR circuits are among this handful of standard components. The VCO is an oscillator used for synchronization of data streams or band selection. Synchronization is required for both CDR and MUX<sup>2</sup> circuits. The static divider creates a signal with a clock frequency equal to a fraction of the frequency of a reference clock and may also generate a quadrature half-rate<sup>3</sup> clock, which is often required by the decision circuits found in MUX, DEMUX and CDR circuits. MUX and DEMUX circuits require a fractional clock signal for each level of multiplexing/demultiplexing, whereas the clocking requirements for the CDR circuit depends on the choice of architecture. A limiting amplifier is a non-linear amplifier that amplifies an input signal to a fixed voltage level, assuming that the input signal is not too weak. The limiting amplifier restores the digital property of a signal that has suffered shape and amplitude distortion. The CDR circuit performs retiming or even complete 3R<sup>4</sup> if it is combined with a limiting amplifier.

#### 1.2.1 Scope of the thesis

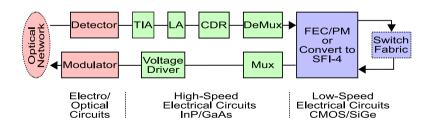

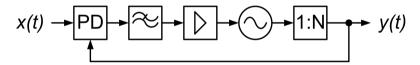

The circuits presented in this thesis are intended as building blocks for a 100 Gb/s serial optical/electrical transceiver. The transceiver performs a conversion between the optical domain and the electrical domain. The transceiver is placed between the optical network and the electrical switch fabric or is used to insert data into an optical switch fabric. The CDR function is part of the receiver path. A limiting amplifier is placed at the ingress of the CDR circuit because the input data signal has a very low (voltage) amplitude at this point. The VCO and static divider circuits are components of the CDR circuits. The static divider is also of interest in the receiver DEMUX and in the transmitter MUX, where it generates the clock frequencies required for multi-stage multiplexing and demultiplexing. A block diagram of a transceiver architecture is shown in fig. 1.1.

Figure 1.1: Block diagram of an electrical/optical transceiver.

<sup>&</sup>lt;sup>2</sup>If the incoming data channels are independently timed.

<sup>&</sup>lt;sup>3</sup>Typically half-rate, but could be  $1:2^n, n \in \mathbb{N}^*$  by iterating the process.

<sup>&</sup>lt;sup>4</sup>Reshape, Reamplify and Retime, i.e. complete regeneration of the signal.

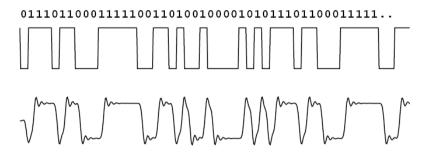

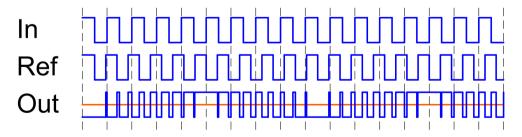

The CDR function is required to recover the synchronization and data of the incoming stream. The data signal is distorted during optical transmission, and the optical network carries no separate synchronization signal (clock) to aid the interpretation of the data, see fig. 1.2. The signal shape and amplitude can be regenerated

Figure 1.2: PRBS prior to and after transmission.

by the LA, but the timing of the data is lost at the point of transmission. The timing must be recovered for the data to be correctly interpreted. The CDR circuit utilizes the incoming data signal to generate a clock signal that is phase-locked to the incoming data carrier, though the frequencies are not necessarily the same<sup>5</sup>. The regenerated clock signal is subsequently used to capture the data using a decision circuit (i.e. D flip-flops). The regenerated clock signal is propagated alongside the regenerated data to provide the essential downstream synchronization. Typically, the subsequent step is a demultiplexing process to (further) lower the signaling bandwidth to a more manageable, and less costly, level.

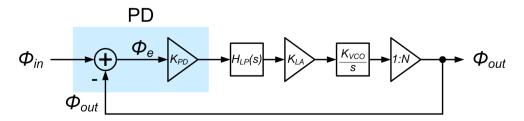

The VCO is a voltage controlled oscillator and acts as the heart of the PLL based CDR circuit. The VCO generates a clock signal and the phase of the clock signal is adjusted to match the phase of the incoming data carrier. A VCO circuit may also be used in the MUX where several data channels from independent sources may have to be buffered and synchronized before being merged. The choice of VCO center frequency depends on the system architecture and data bandwidth.

The static divider generates a (possibly quadrature) clock signal at 1:2 the frequency of the incoming clock signal. A CDR circuit has an internal VCO whereas the MUX and DEMUX circuits rely on external clocks. The quadrature signal is useful for demultiplexing and for some types of phase detectors<sup>6</sup>. Several dividers may also be daisy-chained to provide the clock signals for consecutive steps of multiplexing or demultiplexing.

Design principles, simulation and measurement of the various circuits will be discussed within individual chapters, while the process description will be confined to an appendix.

<sup>&</sup>lt;sup>5</sup>The VCO has a center frequency closely corresponding to a fraction of the bitrate,  $1:2^n, n \in \mathbb{N}_0$ . The required center frequency depends on the choice of architecture.

<sup>&</sup>lt;sup>6</sup>A CDR circuit component.

#### 1.2.2 State of the art circuits

Equipment is commercially available for 10 and 40 Gb/s communication systems and circuits operating in this range<sup>7</sup> have been published in recent years in various III-V technologies, such as InP, GaAs and SiGe. It is even possible to make the 10 Gb/s serial interface circuits in CMOS, and higher bandwidths are being explored using the same technology. The road ahead is as yet resolved, with several possibilities currently being standardised and approved by the IEEE P802.3ba HSE Task Force. It is likely that these original standards will be provisional, i.e. they will be based on practical realisations and gradually fade away as technology develops and more mature standards begin to emerge. The telecommunication industry would prefer a standard of 2, 3 or 4×40 Gb/s to facilitate multiplexing and demultiplexing of existing 2.5/10/40 Gb/s channels, while the Ethernet standard has progressed in orders of magnitude and thus could be expected to aim at 100 Gb/s. The developing 802.3ba standards focus on 100 Gb/s Ethernet in various forms. None of these currently aim at employing 100 Gb/s serial interfaces but instead utilise multiplexing schemes such as  $2 \times 50$ ,  $4 \times 25$  or  $10 \times 10$  Gb/s. However, a 100 Gb/s serial interface is within reach of current III-V IC technology. Several groups have been working to provide the components and system verification of such interfaces. The experimental field has traditionally been dominated by NTT and various small groups working at different companies and universities.

Connecting circuits within a transceiver is no mean feat at  $40~\mathrm{Gb/s}$  and beyond. The obvious solution is to achieve a high degree of integration, so that several circuits can be merged into one or placed adjacently within customised flip-chip packages. The road map for  $40~\mathrm{Gb/s}$  has been to begin with simple circuits and progressively add complexity. The same path will be taken for  $100~\mathrm{Gb/s}$ . Several of the circuits mentioned in the following will thus have varying degrees of complexity.

#### 1.2.2.1 LA

The photo detector of the receiver generates a very weak current signal that has to be converted into a voltage signal and amplified. This is performed by a TIA/TWA circuit. The resulting signal is still weak and requires regeneration of shape and amplitude to regain its digital characteristics. This is the function of the LA circuit that provides the appropriate input data signal to a CDR circuit. Both the photo detector and the CDR circuit can be manufactured in InP technology but the processes for the two types of circuits are not compatible. This makes it (as yet) impossible to place both circuits on the same die. The solution has been to integrate the photo detector and the TIA/TWA as one package. Integrating the LA with the TIA/TWA would not be a good idea because the imperfect interface between the LA and the CDR circuit would then require another LA at the ingress of the CDR circuit. Thus the solution has been to integrate the photo detector and the TIA/TWA as a package and the LA and the CDR circuit on a single die. Eventually, the TIA/TWA, LA, CDR circuit etc. will be integrated on a single die and share a package with the TIA/TWA.

$<sup>^7\</sup>mathrm{The~40~Gb/s}$  data stream is encoded to provide error correction and line coding. The typical bit-rates are 43 or 47 Gb/s.

| Technology | InP         | SiGe           | CMOS                                     |

|------------|-------------|----------------|------------------------------------------|

| 1999       |             | [1, 20]        |                                          |

| 2000       |             | [21, 22, 23]   |                                          |

| 2001       | [5]         | [3, 24, 25]    | [12]                                     |

| 2002       | [2, 6, 26]  | [27]           | [28]                                     |

| 2003       | [8, 29, 30] | [31, 9, 4, 32] | [33, 34, 35, 36, 37, 38, 39, 40, 41, 42] |

| 2004       | [7]         | [43]           | [44, 45, 46, 47, 48, 49]                 |

| 2005       | [10, 50]    | [51, 52, 53]   | [54, 55, 56, 57]                         |

| 2006       | [11]        | [58]           | [59, 60, 61, 13, 62, 63]                 |

| 2007       |             |                | [14, 15, 16, 17, 18, 64, 65, 19]         |

Table 1.2: Publications on CDR circuits at 10 Gb/s and beyond in the period 1999-2007.

The performance of the LA must then be viewed in the context of the CDR circuit. It's most revealing characteristic is the input sensitivity it gives the CDR circuit. The input sensitivity is not a fail or pass parameter but a trade-off between signal input power and BER in a particular environment. The HSSG objectives for 40 & 100 GbE aim at supporting a BER that is better than or equal to  $10^{-10}$  or  $10^{-12}$  at the MAC/PLS service interface.

#### 1.2.2.2 CDR

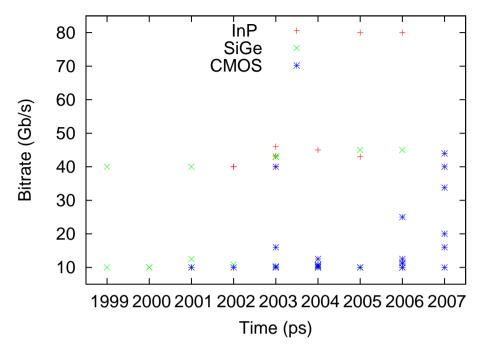

The CDR circuit is the most complex of the transceiver circuits. Siemens was first out with a 40 Gb/s CDR circuit [1]. Lucent<sup>8</sup> was next with a 40 Gb/s CDR circuit that also included a limiting amplifier and a 1:2 demultiplexer [2, 3, 4]. A 40 Gb/s MUX was later developed to make an integration test [4]. NTT has a long history in this field, including complex, low-power 10 Gb/s CDR circuits with integrated 1:4 DEMUX [5, 6]. A 40 Gb/s CDR circuit was then presented two years later [7], when Inphi Corporation and Sierra Monolithics, Inc. published similar results [8, 9]. The most recent development comes from the Fraunhofer Institute (Freiburg), where an 80 Gb/s CDR circuit with integrated 1:2 DEMUX [10, 11] has been developed. A 10 Gb/s CDR circuit emerged early on the CMOS front [12] and recent results have pushed the bandwidth beyond that limit [13, 14, 15, 16, 17, 18, 19]. The achievement demonstrated [14] is particularly impressive. All the published results on (electrical) CDR circuits at 10 Gb/s and beyond have been assembled in table 1.2 to provide an overview. The results have also been condensed into graphical form to illustrate the recent trends. The results have been distributed according to bandwidth and type of IC technology and presented in fig. 1.3.

#### 1.2.2.3 Multiplexer and demultiplexer

Multiplexers and demultiplexers are not a particular topic of this thesis, but they are based on the same D latches that are found in the phase detectors of CDR circuits. NTT has steadily improved their InP process, resulting in matching performance in

<sup>&</sup>lt;sup>8</sup>Several of the authors switched to CoreOptics during this period.

Figure 1.3: Published results for CDR circuits with a bitrate  $\geq 10~\mathrm{Gb/s}$  in the period 1999-2007 distributed according to bitrate and technology.

their MUX and DEMUX circuits. 10 Gb/s DEMUX circuits were the first to emerge [5, 6] and were later followed by 50, 80 and 100 Gb/s MUX and DEMUX circuits [66, 67, 68] based on similar high performance decision circuits [69, 70]. Several other groups have also been involved [9, 32, 4, 11, 71, 18]. CTH has recently published a 100 Gb/s packaged demultiplexer [72, 73] as well as a 165 Gb/s multiplexer [74] for a 100 Gb/s demonstrator system [75, 76]. Some CDR circuits have also been fitted with on-chip multi-channel demultiplexers, e.g. [8, 32, 11, 71]

#### 1.2.2.4 Static divider

The performance of static dividers are often used as a benchmark for IC technology. Static dividers are digital circuits and are usually based on D flip-flops, thus providing a realistic view of the performance a particular process may offer. There are two known results using VIP-1 and VIP-2 [77, 78], and a few in other InP processes, e.g. [79]. [77, 78] operate in the 40-80 Gb/s range.

#### 1.2.2.5 VCO

VCO circuits are a bit tricky to compare for a VCO has many different parameters. One or more of these parameters may be optimized, but often at the expense of other parameters. An obvious reference is [78], because it has been manufactured in VIP-2. Fraunhofer has the current bandwidth record for CDR circuits, and have published

two (almost identical) VCO circuits that are explicitly intended for CDR circuits [80, 81]. There are also a few InP-based VCO circuits in the W-band (75-110 GHz) and beyond. These results have been placed in a table with a few key parameters for easy comparison, see table 1.3. The phase noise and output power are the best values achieved within the tuning range. Higher frequencies have been achieved using other III-V technologies. These results have also been added to the table. The output power,  $P_{out}$ , is for differential output signals.

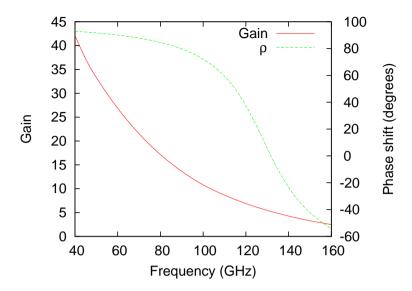

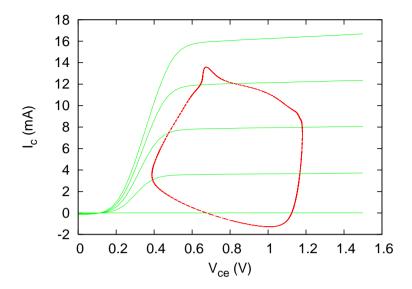

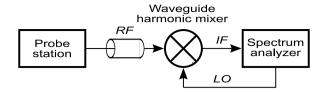

L @ 1 MHz offset (dBc/Hz) Maximum  $f_{osc}$  (GHz) Reference Year Technology  $P_{out}$  (dBm) [82] 1999 InP HBT 108 -88 0.92 [83] 1999 InGaP/InGaAs -95 -3.4 104 [83] 1999 InGaP/InGaAs 134 -72 -10.4 -85 [84] 2000 InP HBT 100 -2 SiGe HBT -85 [85]2003 150 3 [86] 2003 GaInP/GaAs HBT 77 -92 -2.3 [87] 2003 SiGe 77 -95 14.3 [88] 2003 SiGe 79.6 -94 11  $N/A^9$ SiGe 99 [89] 2004 14.3 2004 InP HBT 75 -97 [80] 11  $N/A^{10}$ 2004 InP DHBT 84 -71 [78] [90] 2004 InP HBT 80 -118 [81] 2005 InP HBT 89 -102 8

Table 1.3: 1999-2007 period. Publications on III-V VCO circuits in the W-band and beyond in

## Chapter 2

# High-speed design

The O/E-interface consists of high-speed building blocks. The designer has to make several choices, such as choosing an appropriate process technology and architecture for the task, as well as employing various design techniques to achieve the specifications. Some of the design techniques will be described in this chapter.

### 2.1 Current Mode Logic

The CDR circuit consists of a mix of digital and analog components. The digital components are based on the current mode logic (CML) family, also known as emitter-coupled logic (ECL) [91]. The chief characteristic of CML is that the transistors are always in the active region and can thus change state very rapidly, allowing CML circuits to operate at a very high speed. The main disadvantage is that the circuits are drawing a constant current, independent of the state, resulting in high current densities and power consumption. Most of the power is turned into heat, which has an adverse effect on circuit performance. Heat must be both restricted and effectively dissipated, for excess heat may impede, damage or even destroy a circuit if left unchecked. Current densities must also be limited to avoid electro-migration<sup>1</sup>.

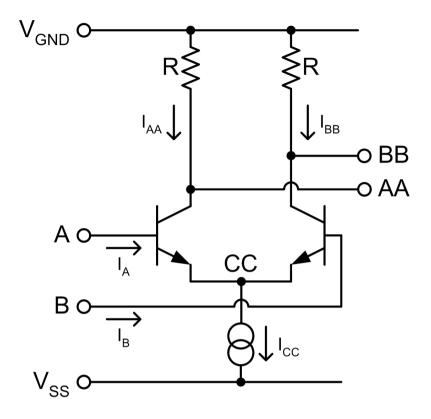

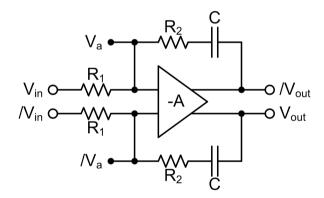

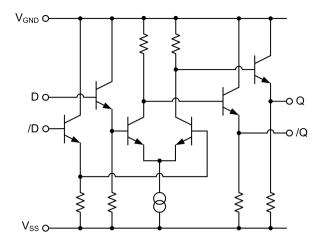

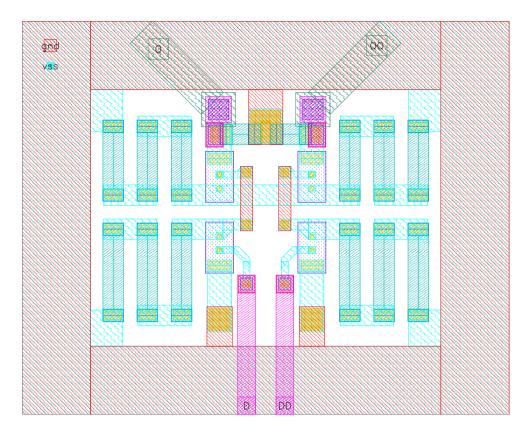

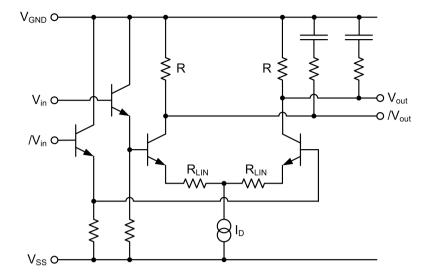

CML gates are based on differential stages, as shown in fig. 2.1. The differential stage can be fitted with a pair of emitter followers (also known as a common collector configuration). This combination is denoted ECL. The emitter followers provide a bias configuration supplying a suitable, constant voltage level to the differential stage. The constant voltage level is at the midrange of the low and high logic levels to the differential stage. A differential input signal will overlay the constant bias voltage and pass almost unchanged (with respect to voltage amplitude) across the emitter followers.

The emitter followers perform level shifting as well as decoupling (impedance transformation) of the signal. The emitter followers act as buffers and can reduce

<sup>&</sup>lt;sup>1</sup>Electro-migration is the transport of material caused by the gradual movement of ions in a conductor due to the momentum transfer between conducting electrons and diffusing metal atoms. The gradual process will cause erosion to conductors, eventually resulting in circuit failure. Fabs specify design rules to avoid electro-migration, generally by applying limits for current densities (given as  $I/\mu m$  for a particular layer).

Figure 2.1: CML principle using a differential stage and emitter followers (ECL).

the input load. The transistors of the emitter followers can be smaller than the transistors of the differential stage. This reduces the parasitic capacitance,  $C_{BC}$ , of the input and results in improved bandwidth.

The effective current gain of transistors decreases with frequency, reducing the decoupling. Thus two (or even three) cascaded emitter followers are often required, sometimes denoted  $E^2CL$ . However, the improved decoupling comes at some cost to signal amplitude, primarily because of parasitic voltage losses over  $r_E$  in the transistor. The emitter followers also provide gain peaking near the the upper frequency limit, extending the bandwidth.

ECL offers a number of advantages, but it also requires more area, current & power relative to CML. ECL is used in critical circuits where speed is paramount, whereas CML is used elsewhere.

### 2.1.1 ECL operation

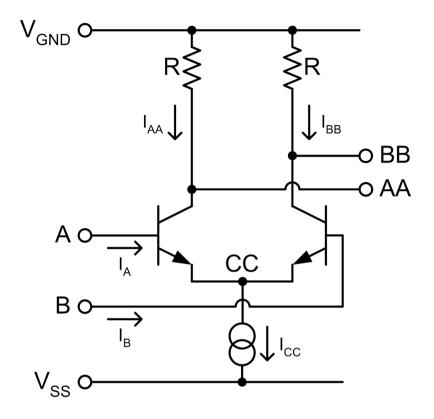

The principle of the differential stage operation can easily be demonstrated using the Ebers-Moll model [92]. A differential stage, with currents and voltages indicated, is shown in fig. 2.2. The three current equations can be stated as:

$$I_A = \frac{I_S}{\beta + 1} \left[ \exp\left(\frac{V_A - V_{CC}}{V_T}\right) - 1 \right] \tag{2.1}$$

$$I_B = \frac{I_S}{\beta + 1} \left[ \exp\left(\frac{V_B - V_{CC}}{V_T}\right) - 1 \right]$$

(2.2)

$$I_{CC} = (\beta + 1)(I_A + I_B)$$

(2.3)

Figure 2.2: Differential stage marked with currents and voltages.

The differential output voltage is:

$$V_{out} = V_{AA} - V_{BB} = R(I_{BB} - I_{AA}) = R\beta(I_B - I_A)$$

(2.4)

Fiddling about<sup>2</sup> for a few minutes eventually yields:

$$V_{out} = \frac{R\beta \left(I_{CC} + 2I_S\right)}{(\beta + 1)} \times \tanh\left(\frac{-V_{in}}{V_T}\right) \approx RI_{CC} \times \tanh\left(\frac{-V_{in}}{V_T}\right)$$

(2.5)

where:

$$V_{in} = V_A - V_B \tag{2.6}$$

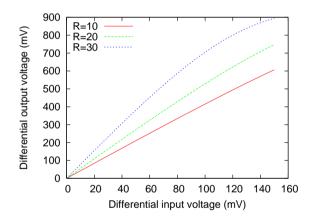

The details are shown in section A.1. The resulting equation has the form  $V_{out} = f(V_{in})$ . The function is shown in fig. 2.3 for a set of typical values.  $V_{out}$  rises steeply with  $V_{in}$  around origin for realistic values of R. A maximum differential voltage swing of  $\sim RI_{CC}$  can be achieved. For a cascade of identical differential stages, the voltage swing can be found as  $V_{out} = -V_{in}$  in the curve, and is typically

$<sup>^2</sup>$ See e.g. Using English.com.

Figure 2.3: Differential stage output voltage as a function of input voltage.

about 95% of the full voltage swing. The differential stage operates as a non-linear amplifier, reshaping and reamplifying a differential signal that has become distorted or weakened, providing the basis for digital logic.

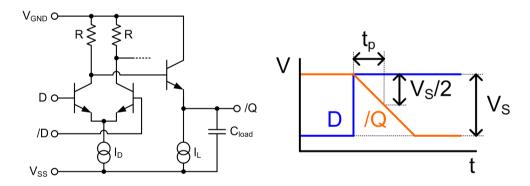

#### 2.1.2 CML or ECL

The choice between CML and ECL depends on a number of factors. The emitter followers require additional power without contributing to the logical function. The emitter followers also serve the purpose of buffering the collector load resistor of the CML thereby isolating the load from the switching time constant. It is this property that is usually given for arguing that ECL is faster than CML. This is probably true for an SSI circuit operating in the transistor limited speed range. The argument becomes less convincing for MSI/LSI circuits where the current levels involved produce RC time constant limited gate speeds. The increase in gate propagation delay caused by the emitter followers is approximately equal to the transit time of the transistor. This can be justified if the extra propagation delay is more than compensated by a reduction in the RC time constant that the external load places on the differential pair.

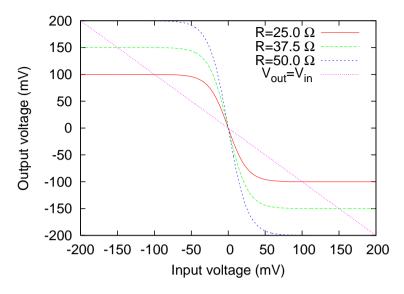

A capacitively loaded CML gate and switching waveforms are shown in figs. 2.4 & 2.5. The differential pair itself is given a zero delay to simplify the comparison. The CML output voltage exhibits a typical RC time constant. The voltage swing,  $V_S$ , is defined as  $V_H - V_L$ . The propagation delay,  $t_p$ , is defined as the time when the output voltage crosses the threshold at the midpoint between the logical levels,  $(V_H - V_L)/2$ :

$$t_{p,CML} = RC_L \ln(2) = \frac{V_S C_L \ln(2)}{I_D} \approx \frac{V_S C_L}{1.4 \times I_D}$$

(2.7)

Figure 2.4: Loaded CML gate.

Figure 2.5: Waveform for CML gate switching.

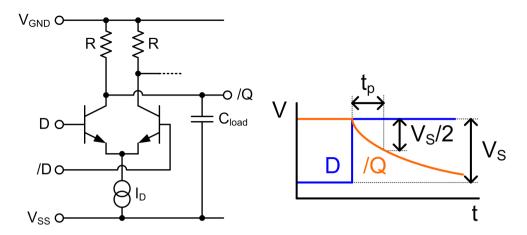

The worst case for the ECL gate is the falling edge. It is limited by the amount of current available to drive the load from the pull-down current source,  $I_L$ . The loaded circuit and corresponding waveform are shown in figs. 2.6 & 2.7. The propagation

Figure 2.6: Loaded ECL gate.

Figure 2.7: Waveform for ECL gate switching.

delay is:

$$t_{p,ECL} = \frac{V_S C_L}{2 \times I_L} \tag{2.8}$$

The next step is to determine when the propagation delay for both CML and ECL are equal:

$$t_{p,ECL} - t_{p,CML} = 0 \Rightarrow \tag{2.9}$$

| $\frac{P_{ECL} - P_{CML}}{P_{ECL}}$ | $I_D = I_L$ | $I_D = 2I_L$ |

|-------------------------------------|-------------|--------------|

| Single-ended                        | 30%         | 7%           |

| Differential                        | 50%         | 30%          |

Table 2.1: Power savings of CML relative to ECL, for stages with equal performance.

$$\frac{V_S C_L}{2 \times I_L} - \frac{V_S C_L \ln(2)}{I_D} = 0 \Rightarrow \tag{2.10}$$

$$I_D = 2\ln(2) \times I_L \approx 1.4 \times I_L \tag{2.11}$$

The current sources of the differential stage and the emitter followers are typically of similar size. The CML gate would then use about 30% less power than a ECL gate with similar performance. The previous examples are all single-ended. One of the features of ECL/CML is the complementary logic output function. Using a second emitter follower on the complementary output would further improve the power consumption advantage of the CML gate to about 50%. Operating the differential stage at optimum current density would require twice the current through the core relative to the emitter followers, given similar size transistors. The power advantage of CML would then be reduced to 7% and 30% for single ended and differential output respectively. The results are shown in table 2.1. The conclusion, so far, is that CML has an inherent power advantage over ECL.

The differential voltage swing,  $V_s$ , is  $\approx RI_{CC}$ . This is a straightforward formula, but not any set of values for R and  $I_{CC}$  is desirable. A large voltage swing will make the signal more immune to noise, but requires a large R and/or substantial  $I_{CC}$ . A large R increases switching time. The output load,  $C_{load}$ , is discharged through a resistance, R, creating a time constant of  $\tau_{fall} = RC_{load}$ . The switching time is thus proportional to R (and  $C_{load}$ ).  $I_{CC}$  is equally problematic. The circuit power consumption, and thus heat generation, is  $P = -V_{SS}I_{CC}$ . An improved voltage swing is therefore bought at the cost of switching time and/or power consumption.

CML has the additional feature of having a nearly constant current consumption. This reduces the noise in the supply voltages considerably. Some current spikes occur during switching due to the limitations of the less than ideal current source. The problem can be mitigated by having adding on-chip decoupling capacitance to the supply grid and by the design of the current source, see section 2.4.

### 2.2 Signaling and transmission lines

### 2.2.1 Signal wavelength

A chip consists of interconnected circuits. The interconnections are electrical signals propagating through metal conductors. Some circuits are placed together to form functional blocks, such as a VCO or an amplifier. Interconnects can be categorised based roughly on length; short interconnects within functional blocks and long interconnects between functional blocks. The reference to length is a bit loose, for it is related to both the signal bandwidth and the physical length of the interconnect.

An interconnect is considered short if  $l \ll \lambda/4$ , i.e. the signal can safely be assumed to be uniform over the length of the conductor. The wave nature of a signal can be ignored for short interconnects but must otherwise be taken into consideration. The signal wavelength is related to both the signal bandwidth<sup>3</sup> and the signal propagation velocity of a particular conductor:

$$l \ll \lambda/4 = \frac{v}{4f} \tag{2.12}$$

The velocity is related to physical properties of the conductor and its surrounding materials, as well as geometry:

$$v = \frac{1}{\sqrt{\epsilon \mu}} = \frac{c}{\sqrt{\epsilon_r \mu_r}} \tag{2.13}$$

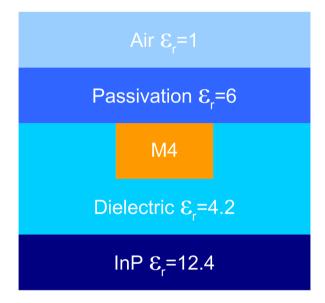

The relative permeability,  $\mu_r$ , is close to unity (for most materials), whereas the permittivity,  $\epsilon_r$ , is effectively close to 4.0 for the VIP-2 process<sup>4</sup>. This yields  $v = c/\sqrt{4} = 1.5 \times 10^8 m/s$ . The critical length,  $l_c$ , in VIP-2 can thus be easily found for an interconnect, given the frequency.  $l_c = 375 \ \mu m$  for a 100 GHz clock signal. The designer must be mindful of the length of interconnections and take the appropriate action where necessary.

### 2.2.2 Differential signalling

Differential signalling on balanced lines has several advantages over single-ended signalling [93]:

- A differential signal requires no common reference voltage, unlike a single-ended signal. This facilitates signalling across different logic families (ECL, TTL etc.), technologies (e.g. SiGe), circuits and chips.

- The voltage swing can be made lower, while maintaining the integrity of the signal.

- Symmetrical pulse edges compensates for transients.

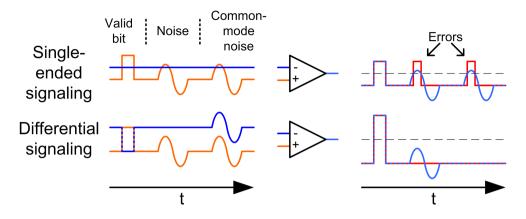

The lack of a common reference voltage eliminates the problem of jitter in the reference voltage affecting the interpretation of the signal. Noise is also improved by the relative increase in amplitude and the rejection of common mode noise. An example is shown in fig. 2.8. The single ended signal is interpreted relative to a reference voltage. A differentiator is used to discern the binary value. Both noise and (more specifically) common mode noise may result in erroneous interpretation if the noise amplitude crosses the threshold, as shown by the two errors slipping through.

<sup>&</sup>lt;sup>3</sup>It is actually the spectral component with the highest frequency that dictates the minimum wavelength. The spectral component with the highest frequency and the signal bandwidth are the same for a baseband data signal. Not all signals employ the baseband, e.g. clock signals occupy extremely narrow bandwidths while their respective spectrums are located around much higher center frequencies.

<sup>&</sup>lt;sup>4</sup>The effective  $\epsilon_r$  depends on the configuration. The conductor is placed differently, relative to the surrounding layers, for each of the four metal layers in the VIP-2 process. Metal 4 is the most useful signal conductor due to its greater distance to substrate.

Figure 2.8: The effects of noise in single-ended and differential signaling.

The differential signal is complementary, and the subtractor thus yields twice the amplitude. The improved noise margin reduces the likelihood of errors. The differential line is subjected to the same level of noise as the single-ended line, but the noise is now significantly below the threshold and does not generate any errors.

The two lines are closely spaced to minimize the effects of interference. The intention is to ensure that any noise source has equal influence on both of the balanced lines. The noise would then become common mode. Common mode noise is effectively eliminated at the differentiator, as shown by the example, whether it originates in the source or along the lines.

The example shows how the effective signal amplitude doubles with differential signaling. This is also true for the slope of the pulse edges, becoming twice as steep. This allows for higher data rates with improved eye diagrams. Slope ( $\propto 1/RC_{load}$ ), Differential voltage swing ( $\sim RI_{CC}$ ) and power consumption ( $-V_{SS}I_{CC}$ )<sup>5</sup> are somewhat interchangeable.

Differential signalling also has several disadvantages. Twice as many conductors are used, requiring additional area, longer conductors (because of the larger area occupied by the conductors) and possibly creating routing problems. The length of the conductors also have to be matched to ensure synchronous arrival of the signal at the receiver. Furthermore, the conductors must be closely spaced to reap the reward of common mode suppression, particularly if significant noise sources are found on-chip.

All of the circuits presented in this thesis employ differential signalling for all signals, both analog and digital, with the exception of DC biasing signals.

$<sup>^5</sup>$ Reducing the voltage swing across the output resistors would reduce the  $-V_{SS}$  required for driving the circuit. The circuit power consumption is  $P=-V_{SS}I_{SS}$ . A typical  $V_{SS}$  is -4 V and a 50% reduction of a 400mV voltage swing (200 mV) would save 5% of the power. Changes in  $I_{CC}$  for a particular circuit has a much greater impact. A 50% reduction in  $I_{CC}$  would yield a 50% reduction in both the voltage swing and in P.

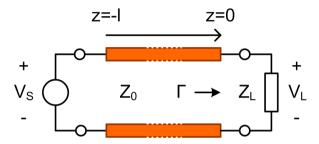

#### 2.2.3 Termination and reflection

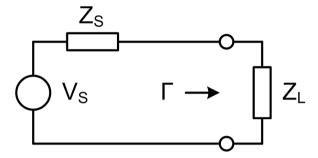

Signals are transmitted between circuits. For long transmission lines, the wave nature of the signals can not be ignored. A simple circuit containing a source and a load is shown in fig. 2.9. The difference between the impedance of the source,  $Z_S$ , and the

Figure 2.9: Simple circuit configuration showing measurement location of reflection coefficient.

impedance of the load,  $Z_L$ , will cause a discontinuity. This will result in part of the wave being reflected at the discontinuity. The reflection coefficient,  $\Gamma$ , is the ratio of the amplitude of the reflected wave to the amplitude of the incident wave. The reflection coefficient is given by:

$$\Gamma = \frac{Z_L - Z_S}{Z_L + Z_S} \tag{2.14}$$

The same process takes place whenever a wave encounters a discontinuity. The formula shows that no reflection ( $\Gamma = 0$ ) occurs if the line and the load are impedance matched:  $Z_S = Z_L$ .

A simple case is shown in fig. 2.10. The source and the receiver are separated by

Figure 2.10: Transmission line without termination.

a transmission line with the characteristic impedance of  $Z_0$ . The receiver consists of emitter followers with high impedance  $(|Z_L| \gg |Z_0|)$  and the result is that much of

the signal is reflected ( $|\Gamma| \approx 1$ ). The reflected wave will eventually arrive back at the source, where  $Z_S \approx R_L$ . Another reflection will occur at the source if the source and line are not perfectly matched ( $Z_S \neq Z_0$ ). The signal will quickly stabilize for short lines, but the effect on longer lines will be ringing and signal distortion.

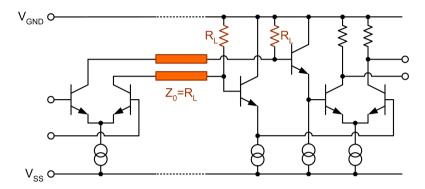

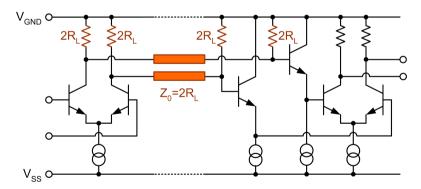

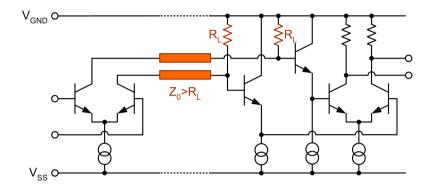

The reflections can be dealt with by moving the load to the receiver, as shown in fig. 2.11. It is possible to achieve a very good impedance match between the

Figure 2.11: Transmission line with single termination.

transmission line impedance and the load resistors, but the load will still present a mismatch because of the input capacitance of the emitter followers. The resulting reflections will eventually arrive back at the source, which is not impedance matched at all.

Reflections on the transmission line can be efficiently reduced by employing impedance matching at both the source and receiver. This is shown in fig. 2.12. The

Figure 2.12: Transmission line with double termination.

load and source resistances have now been doubled, as well as the line impedance. This could be difficult to implement. Resistors are manufactured from specialized layers. Resistance depends on the geometry used and can cover a wide range of values, typically three orders of magnitude<sup>6</sup>. The same dynamic range is not possible

$<sup>^6 \, {\</sup>rm The}$  practical range is about 2 to 2000  $\Omega$  for VIP-2.

for transmission lines, as will be shown in section 2.2.4. Having double matched termination is therefore only possible when load resistance, and thus the matching line impedance, is sufficiently low for the transmission line impedance to be realized.

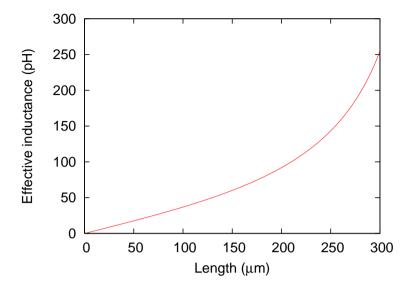

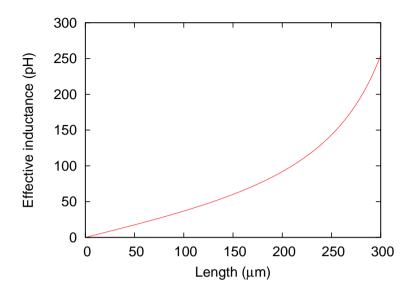

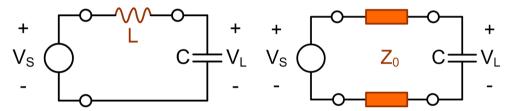

The voltage at the emitter followers can be amplified by utilizing the transmission line as an inductive element, see fig. 2.13. The inductive line and the (parasitic)

Figure 2.13: Transmission line with inductive line.

load capacitance of the emitter follower will resonate and create gain peaking. The effective inductance,  $L_{eff}$ , is given by:

$$L_{eff} = \frac{Z_0}{2\pi f} \tan\left(\frac{2\pi l}{\lambda}\right) \tag{2.15}$$

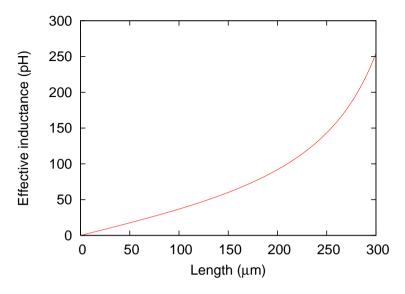

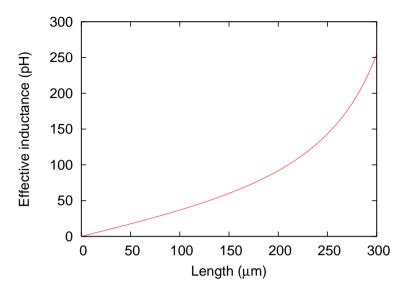

The gritty details have been relegated to section A.2. It should be noted that  $L_{eff}$  is proportional to  $Z_0$ . The difficulties in achieving a high  $Z_0$  effectively limit  $L_{eff}$ . The highest  $Z_0$  that can be obtained using VIP-2 is about 52  $\Omega$ . The length of the transmission line has to be restricted to less than  $\lambda/4$ , because the line appears to be capacitive beyond this point. The line should be made well short of this boundary to ensure that the signal spectrum is encompassed.  $L_{eff}$  also becomes less predictable around this point. The effective inductance for a realistic VIP-2 transmission line is calculated for various lengths and the results are presented in fig. 2.14. The effective inductance is less than 100 pH for realistic lengths.

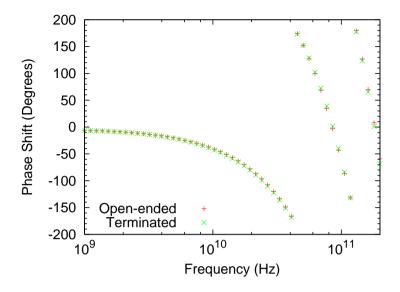

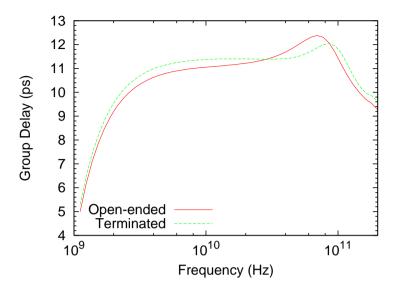

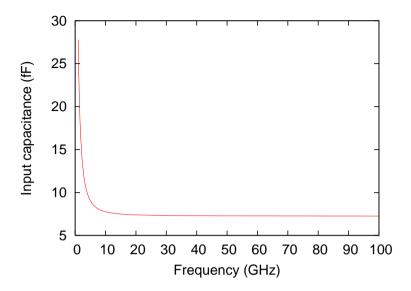

The effect of the inductive line will depend on the signal, and thus on the application. An example will demonstrate the resonance between the inductive line and the capacitive load. A frequency domain analysis is selected because it simplifies the conditions. The setup is identical to fig. 2.13, but the differential stage source is replaced with an ideal source. The rest of the components use their respective models.  $R_L$  and  $Z_0$  are both set to 52  $\Omega$ . l is 150  $\mu$ m; equivalent to about 50 pH. The emitter followers use minimum size<sup>7</sup> transistors. The input capacitance is about 7.3 pF, but somewhat frequency dependent; see section B.1 for details. The result is shown in fig. 2.15 for various frequencies. The extra amplitude is useful, but the price is ringing/overshot and group delay.

$<sup>^7</sup>$ With respect to VIP-2. Minimum emitter width and length are 0.5  $\mu$ m×1.0  $\mu$ m, corresponding to an effective area of 0.85  $\mu$ m $^2$ .

Figure 2.14: Effective inductance of a transmission line. f=100 GHz,  $Z_0=52$   $\Omega$  &  $\lambda=375$   $\mu m$ .

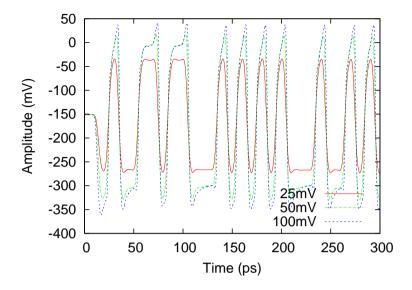

A time domain analysis will complete the picture. The setup is similar to the previous example with a sinusoid source. Two different lengths of transmission line are used, one 20  $\mu$ m and the other 200  $\mu$ m. The voltage at the emitter followers are shown in fig. 2.16. The source signal is shown as reference.

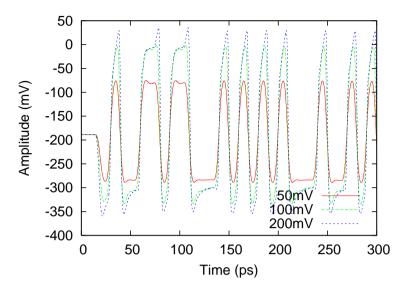

The The rise and fall time of the signal can be improved by adding inductive elements to the receiver load, as shown in fig. 2.17. The inductors are implemented as microstrips shorted to ground. The method is known as inductive peaking [94, 95] and increases the AC load resistance:

$$\frac{V_{out}}{I_{in}} = j\omega L + R_L \tag{2.16}$$

Again, the inductor will resonate with load capacitance and the result will be ringing and signal distortion (jitter). The effects of inductive peaking are demonstrated in fig. 2.18.

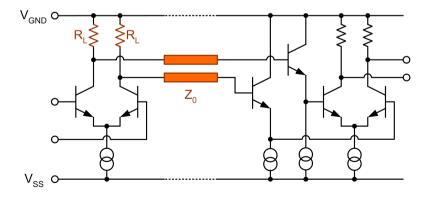

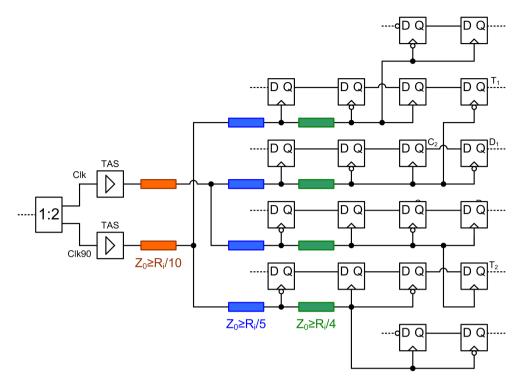

### 2.2.4 Conductor modelling and realisation

The CDR circuit is fairly large, both in physical size and number of components. This makes it necessary to use long interconnections between sub-circuits. Long signal lines<sup>8</sup> are modeled and realized as frequency dependent transmission lines to more accurately predict their behavior.

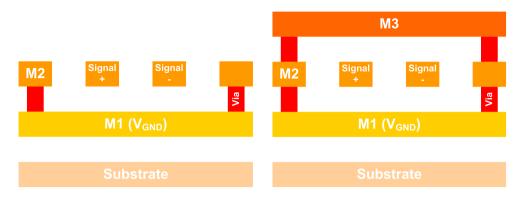

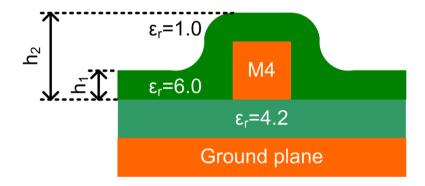

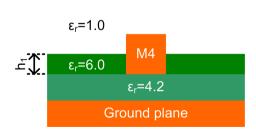

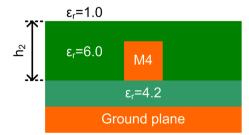

Transmission lines use the top metal layer (metal 4) over an unbroken ground  $(V_{GND})$  layer (metal 2), and the lines are adequately spaced to minimize coupling

$<sup>^8</sup> Length > \lambda/10$ , or about 140  $\mu m$  for a 100 GHz signal in the VIP-2 process. Top and intermediary  $\varepsilon_T$  is 6.0 and 4.2 respectively.

Figure 2.15: Simulation of inductive line with and without capacitive load.

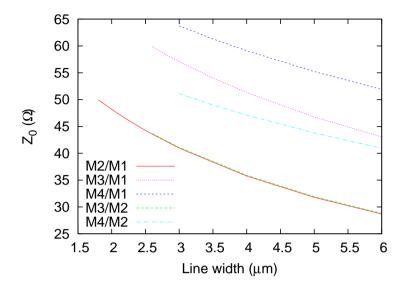

(6-8  $\mu$ m). 50  $\Omega$  is used for most terminations, but 36  $\Omega$  at the latches. The highest achievable impedance is 51.6  $\Omega$  (3  $\mu$ m metal 4 over metal 2), and a slightly wider line (3.5  $\mu$ m) yields almost exactly 50  $\Omega$ . 33.9  $\Omega$  can be achieved by 4.5  $\mu$ m metal 3 over metal2. The practical range is between 30-51.6  $\Omega$ .

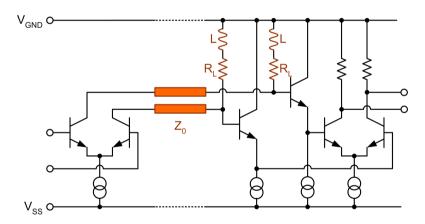

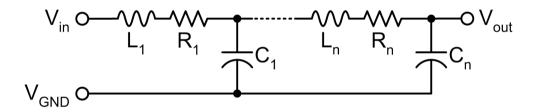

2-D models for transmission lines exists in both ADS and Cadence, but the complexity of the models make them very time-consuming for large circuits. The inherent Cadence model is particularly slow, and tends to cause convergence difficulties more often than not, when the initial state is computed. A simpler, frequency specific model, is shown in fig. 2.19. It consists of a cascade of ten identical stages, creating a simple, distributed model. Such a model was used extensively, but not exclusively, for system simulations. Clock distribution in particular is confined to a narrow bandwidth, suitable for a distributed model, whereas a PRBS sequence occupies a much wider frequency band.

## 2.3 $f_t$ and $f_{max}$

$f_t$  and  $f_{max}$  are important figures of merit for transistors, though neither directly predicts digital circuit speed.  $f_t$  is the cutoff frequency and is important for analysing the bandwidth of small-signal amplifiers and the power gain of power amplifiers. The cutoff frequency is given by the well-known approximation [96, 97] as follows:

$$f_t = \frac{1}{2\pi\tau_{EC}} \approx \frac{1}{2\pi \left[r_E \left(C_{JE} + C_{JC}\right) + \tau_B + \tau_C + R_C C_{JC}\right]}$$

(2.17)

where:

$$r_E = kT/qI_C (2.18)$$

Figure 2.16: Time domain analysis of inductive line.

Figure 2.17: Transmission line with inductive peaking at the load.

The maximum frequency of oscillation is approximated by:

$$f_{max} \approx \sqrt{\frac{f_t}{8\pi R_B C_{JC}}} \tag{2.19}$$

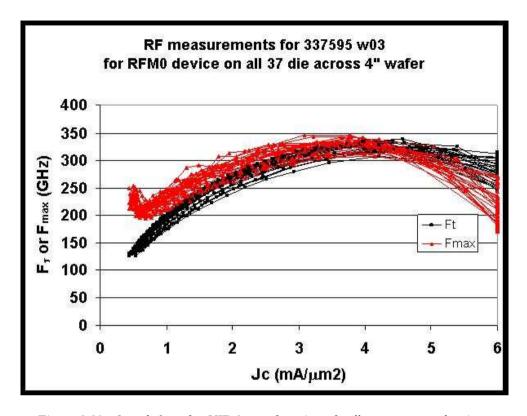

It is clear that  $f_t$  and  $f_{max}$  of VIP-2 are very dependent on the collector current density (and temperature for  $\tau_B$  &  $\tau_C$ ).  $f_t$  and  $f_{max}$  reach their global maxima at around 3.8 mA/ $\mu$ m<sup>2</sup>, as seen in fig. 2.20. Critical transistors (where switching speed is paramount) are generally biased to operate around this point, but it does result in a significant current (and power) consumption. The heat generated by large circuits such as a CDR circuit can easily destroy the circuit if preventive and

Figure 2.18: The effect of inductive peaking on transients.

Figure 2.19: Simple, distributed transmission line model. The model is shown single-ended for the sake of simplicity.

remedying measures are not taken. Less critical parts of a circuit could be more economical with respect to current density without any significant impact. In some cases, such as current sources,  $f_t$  and  $f_{max}$  should actually be minimised. Stability is the hallmark of good sources and slower transistors become less susceptible to noise, as will be shown in the following section.

Emitter followers have a fairly constant collector current, but the same is not true for the differential stage. Current will almost exclusively pass through only one of the two collectors when the stage is not switching, as shown (indirectly) in eq. 2.5. The solution is to set the current source to drive twice the optimum current for either transistor. The idea is that both transistors will have optimum current density, and thus optimum switching speed, at the critical switching moment.

Figure 2.20:  $f_t$  and  $f_{max}$  for VIP-2 as a function of collector current density.

#### 2.4 Current sources

Ideal current sources are used in CML based circuits, as well as in other designs presented in this thesis. The physical realization of ideal sources offers a compromise between complexity and performance.

#### 2.4.1 Resistive current source

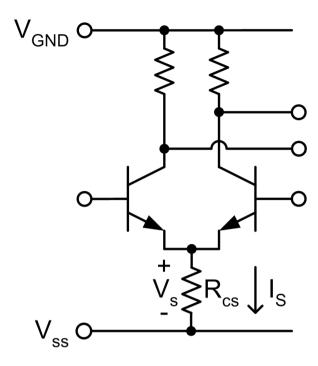

The simplest current source takes the form of a resistor, as shown in fig. 2.21. This is a very simple solution with a compact layout. The resistor adds very little parasitic capacitance to the common emitter node, which is helpful in maintaining the impedance at high frequencies.

The simplicity has its price. The current through the resistor is not constant, but proportional to the voltage over the resistor,  $I_S = V_S/R_{CS}$ . As a result, the current is sensitive to variations in the common emitter node voltage, supply voltage  $(V_{SS})$ , process and ambient temperature. Obviously,  $V_{SS}$  can be adjusted to optimize the output voltage swing to a particular process outcome, but this will impact the chip globally. Furthermore, the voltage dependency means that the switching noise in the differential stage is not decoupled from  $V_{SS}$ . Each source may only be a small contributor, but having numerous sources on a chip exhibiting synchronous switching

Figure 2.21: Resistive current source.

will make its presence felt. The noise will have a direct impact on analog circuits, but could be acceptable for CML (though it would cause jitter in the eye-diagram).

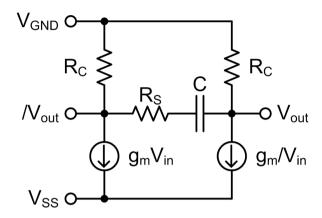

#### 2.4.2 Current mirror

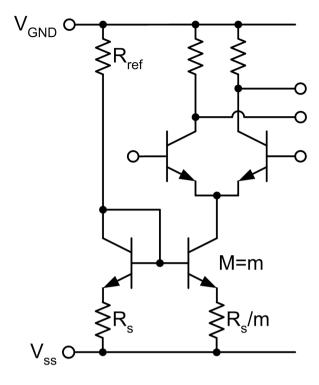

A more complex current source is able to mitigate the short-comings of the resistive current source. A current mirror is based on a transistor with a controlled reference current. The reference current is being mirrored in one or more load transistors. A current mirror is shown in fig. 2.22. The current mirror contains resistors,  $R_s$ , to make the (current) source less dependent on the collector voltage and to dampen any resonance with  $V_{ss}$ . The resistors are usually set to have a voltage drop of 200 mV at nominal supply voltage,  $V_{ss} = -4.2$  V, and have minimum width with respect to current density (to save space). The reference resistor,  $R_{ref}$ , fixes the mirror current at the desired DC level and takes some heating off the transistor.

The current mirror is less sensitive to variations in  $V_{ss}$  relative to the resistive current source. The change in supply voltage,  $\Delta V_{ss}$ , is felt directly over  $R_{cs}$  for the resistive current source:

$$\Delta I_s \approx \Delta V_{ss} / R_{cs} \tag{2.20}$$

The voltage over the reference transistor in the current mirror can roughly assumed to be constant, and  $\Delta V_{ss}$  would thus be distributed over  $R_{ref} \& R_s$ :

Figure 2.22: Current mirror with internal bias.

$$\Delta I_s \approx \Delta V_{ss} / (R_{ref} + R_s) \tag{2.21}$$

The implication is that the current source will show less variation, given  $R_{ref} + R_s > R_{cs}$ . This is a reasonable assumption, all else being equal.

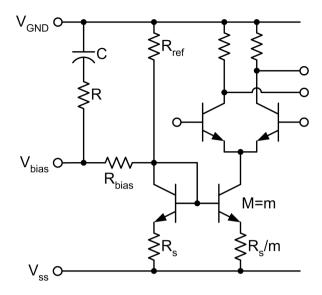

An external control of the bias voltage may be desirable in some cases. This is shown in fig. 2.23. An external bias signal,  $V_{bias}$ , is connected to the current mirror through a resistor,  $R_{bias}$ , of the same size as  $R_{ref}^{\,\,9}$ . Setting  $V_{bias}$  to the same level as  $V_{GND}$  would thus result in roughly doubling the current. The bias voltage originates off-chip, and some stabilization is required to prevent undesirable interference from noise sources such as switching noise. This is achieved by inserting a relatively large capacitor (C=2.89 pF). The capacitor is connected through a resistor ( $R=8.5~\Omega$ ) with the intention of dampening possible oscillations. The dampening resistor is much smaller than the bias resistor to ensure that noise will be absorbed before reaching the reference voltage node.

As previously mentioned, key transistors in the design have a current density of  $3.5\text{-}4.5~\text{mA}/\mu\text{m}^2$  to maximize  $f_t$  and  $f_{max}$ . An optimized transistor is obviously not desirable for a current source, which should react as slowly as possible (or ideally, not at all) to any variation (primarily) in collector voltage. The current density must therefore be set to a much different value. A higher current density would

<sup>&</sup>lt;sup>9</sup>This is simply a reasonable size; no quantitative argument is implied.

2.5. Layout 29

Figure 2.23: Current mirror with external bias.

be both wasteful and outside the safe envelope of operating conditions, and the remaining option is to decrease current density by increasing the size (or number) of the transistor(s). In general, the current mirror transistors have been limited to a current density around or slightly less than 1 mA (commonly 0.95 mA). Lower current densities are easily achieved but would take too much space (too large or too numerous transistors) to be practical.

The current mirror load, m, has limitations. The bias current feeds the base currents of both the reference and controlled transistors. This makes the mirror dependent on m, and  $R_{ref}$  has to be adjusted accordingly. Parasitic capacitance,  $C_{cb}$  in particular, is another issue. It couples the switching noise to the biasing voltage. Experience indicate a reasonable limit for m around four. The simplified current mirrors have been shown as driving m load transistors belonging to a single differential stage, but the load transistors usually belong to parallel differential stages and are not necessarily of the same size as the reference transistor.

An external bias signal requires a DC pad. Having several separate circuits on the same chip with independent biasing would require an equal number of additional pads. Obviously, using a common bias signal (and a single pad) for all current mirrors is the most realistic choice, particularly for small circuits.

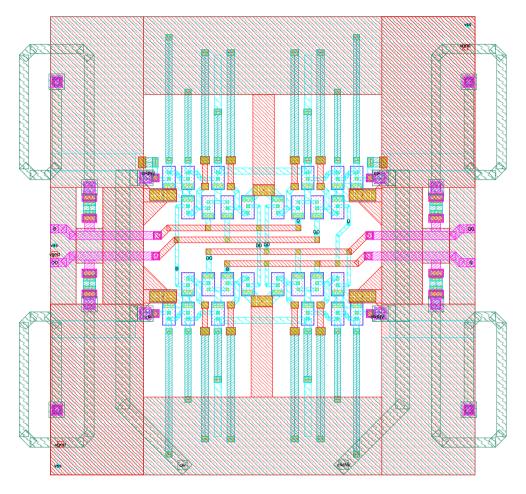

## 2.5 Layout

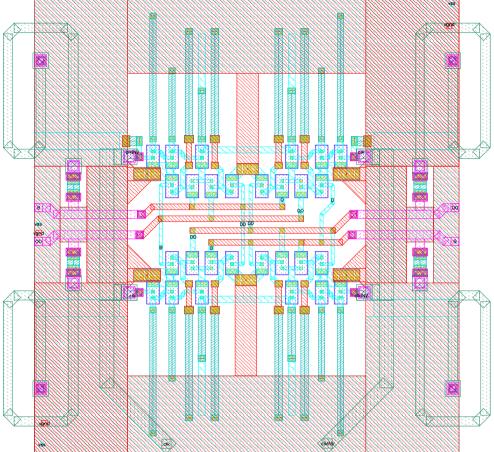

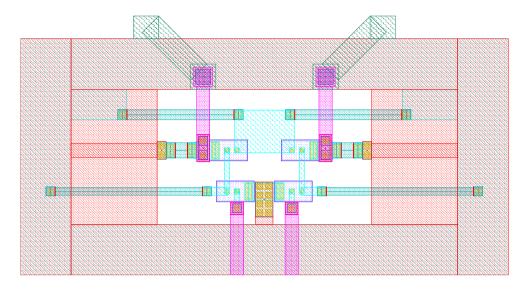

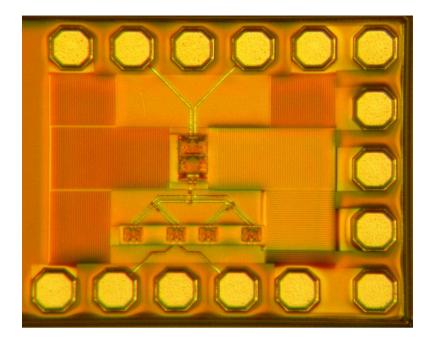

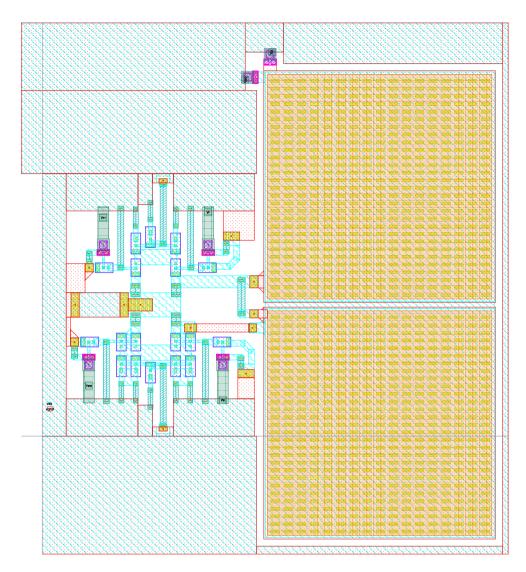

A schematic is a two-dimensional functional description of a circuit. Signals are either drawn or represented by labels. Neither the functional blocks nor signals in a schematic is limited by physical constraints. Some of these limitations first show up during the layout step of the design process. A medium-size circuit, a static divider, is used to demonstrate some of the issues at stake. The core of the static divider is

shown in fig. 2.24, with some of the layout features visible.

Figure 2.24: Layout of a CML static divider.

#### 2.5.1Power supply & distribution

Circuits are powered by voltage sources. The external sources should be stable and immune to noise. The conditions on and off-chip will be different. Wires, leads, pins, packages, bonding wires and pads will inevitably add distributed resistance, capacitance and inductance to an otherwise ideal, external power supply. The internal power distribution also suffers from limitations. Inductance may be negligible and decoupling capacitance benevolent, but the resistance has a significant impact.

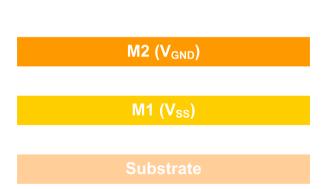

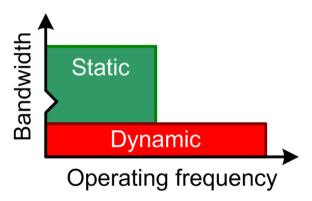

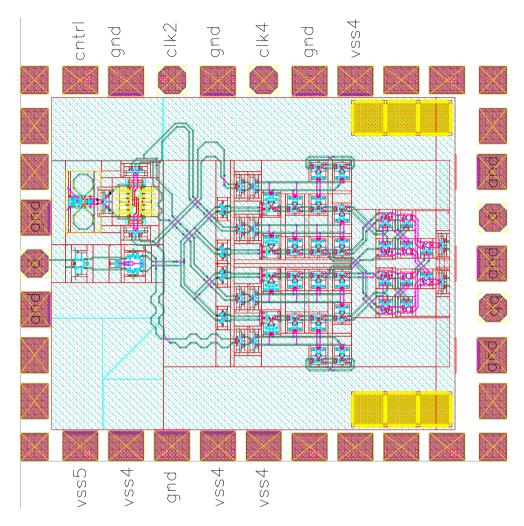

The digital CML supposedly exhibits a constant current consumption. However, the current sources are not perfect. As a result, switching noise is inserted in the power supply every time a digital gate or buffer changes state. The digital circuits are 2.5. Layout 31

designed with an adequate noise-margin, but mixed-mode<sup>10</sup> circuits are vulnerable. The digital noise will affect the sensitive analog circuits. An obvious solution is to have a completely separate analog and digital power supply [98]. The separation should preferably encompass separate external power supplies as well. This requires additional power supply pads or sharing the existing pads between the supplies. The concept of separate supplies also offers the possibility for local voltage level optimisation for performance or power consumption. An intermediary solution is achieved by isolating only one of the supply levels, preferably the layer shielding the signal lines. This method has been used in the CDR circuit presented in chapter 6. The VCO in the CDR circuit has a separate  $V_{SS}$  to provide isolation, but also to save power<sup>11</sup> and optimize the collector current density in the VCO. A completely separate supply, including  $V_{GND}$ , would have required more pads than was available; most, if not all, of the circuits designed during the OptCom project have been pad limited.

Another precaution is to lay out the digital and analog circuitry in different sections of the chip. The two (or more) sections should be separated by guard rings. This is particularly important for CMOS where a grid style power supply net will be insufficient to protect against substrate noise. The guard rings protects against noise by being low ohmic.

Multiple power supply pads (and bonding wires etc.) are advantageous with respect to resistance and inductance ( $L_{total} = L \parallel ... \parallel L = L/n$ ). Any available pad not used for signalling should be assigned to power supply. AC signals use a GSG configuration for shielding, inherently benefiting  $V_{GND}$  access. The problem is usually restricted to finding enough suitable pads for  $V_{SS}$ . Multiple pads also reduce current density, which prevents electro-migration and decreases internal voltage drop.

Noise is being capacitively coupled into transmission lines, when the lines are adjacent to substrate, other transmission lines and circuits. The noise can be effectively reduced by employing grounded shields between the transmission line and noise sources. A simple shield is illustrated in fig 2.25. A grounded metal layer (M1) is used to provide a shield between signal and substrate. The shield is extended by two connected, parallel sidebars (M2) to reduce noise coupling through fringe capacitance. Nearly complete shielding is achieved by enclosing the transmission line, as shown in fig. 2.26. Ideally, no capacitive coupling should exist between the transmission line and the exterior. It requires a wide space and an additional metal layer, which may not be attractive with regards to routing.

The shield should preferably employ a separate net  $(V_{GND,Shield})$  that is solely used for shields. If this type of connection is not possible due to layout and space constraints, then the noisy digital ground  $(V_{GND,Digital})$  can be used for shields, although this does not provide ideal shielding. The digital ground is used even though the digital circuits are themselves both more noise generating and noise immune relative to analog circuits. Most of the effect on differential signalling will be common mode and have little impact. Using the sensitive analog ground  $(V_{GND,Analog})$  for shielding both analog and digital routing would couple digital noise directly to analog

<sup>&</sup>lt;sup>10</sup>Containing both analog and digital circuitry.

$<sup>^{11}{\</sup>rm The~VCO}$  requires a  $V_{SS}$  of -5.0 V while -4.2 V is sufficient for the remaining circuits. The VCO is fairly small in terms of power consumption relative to the remainder. Using a global  $V_{SS}$  of -5.0 V would increase power consumption about 19 % in the remainder.

Figure 2.25: Transmission line using partial shield.

Figure 2.26: Transmission line fully enclosed by shield.

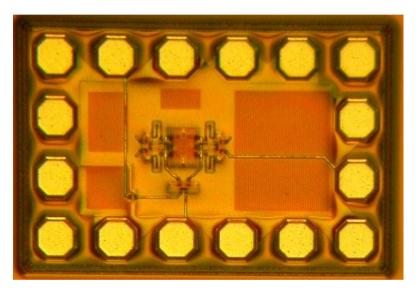

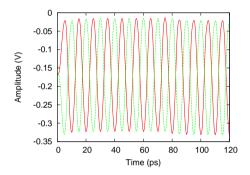

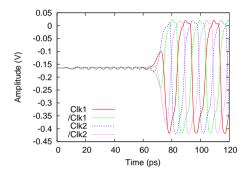

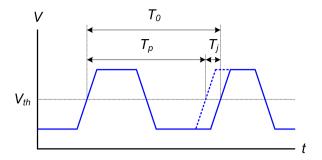

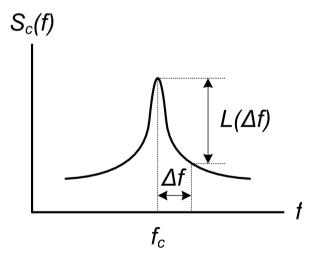

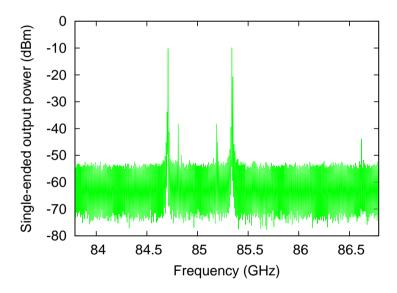

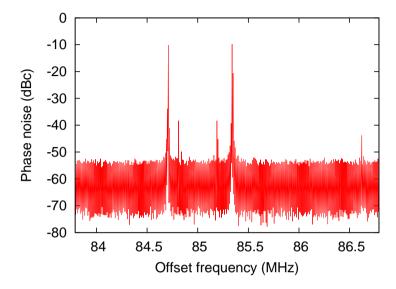

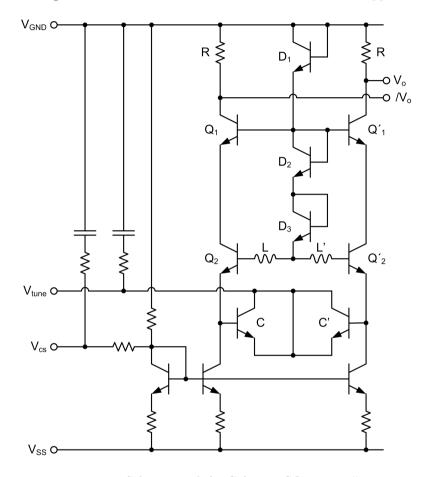

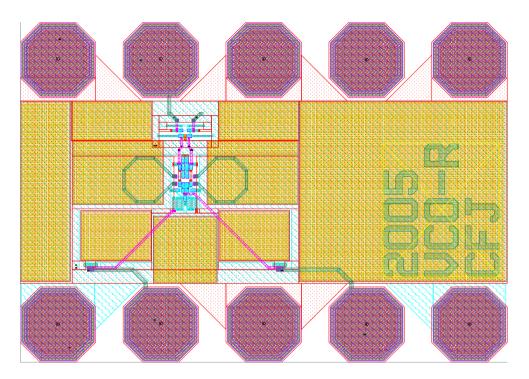

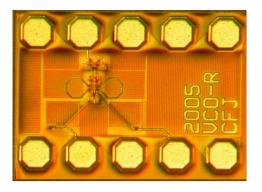

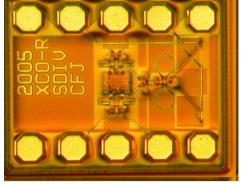

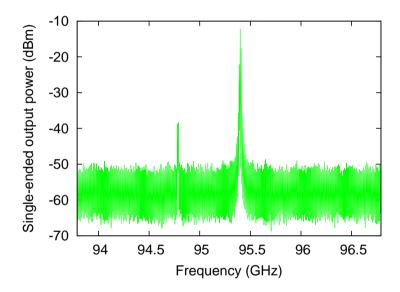

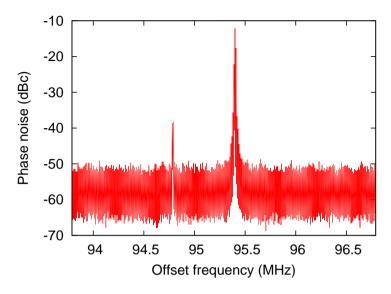

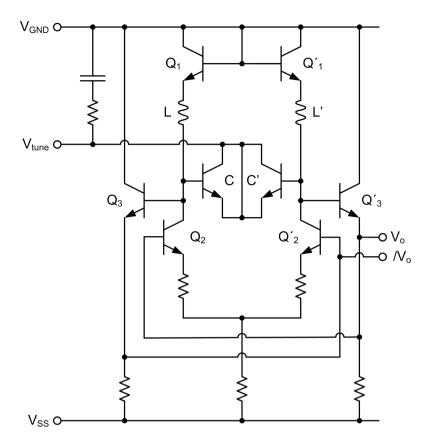

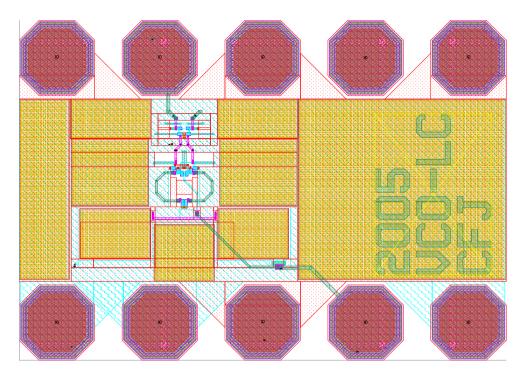

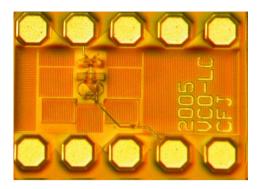

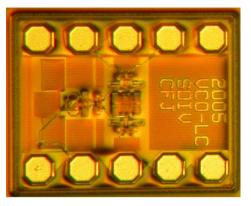

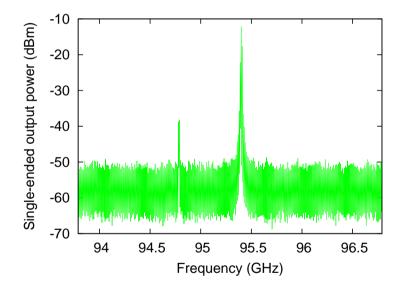

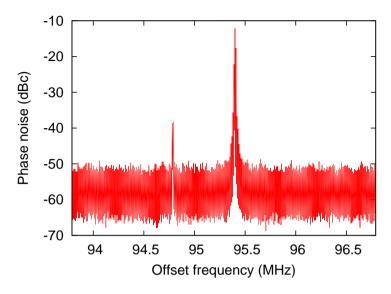

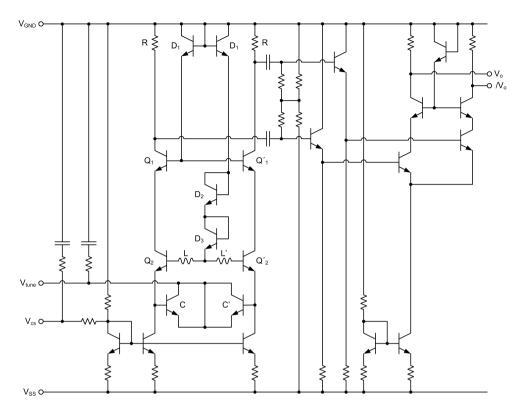

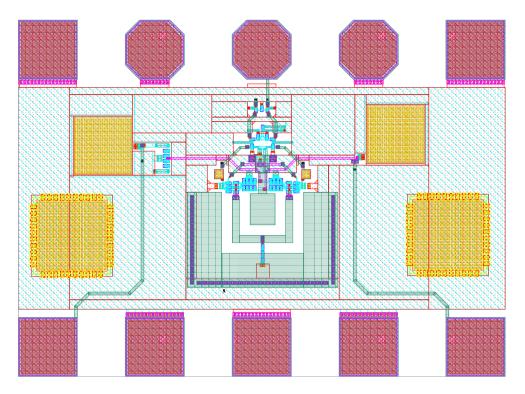

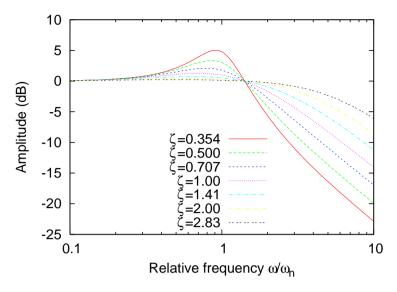

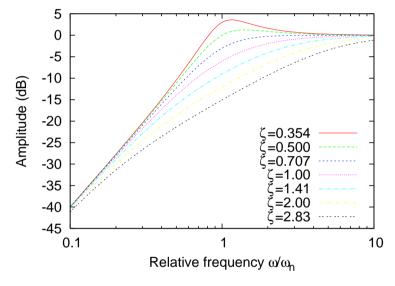

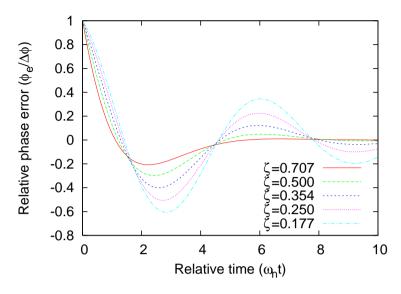

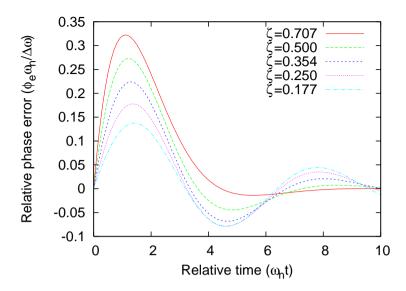

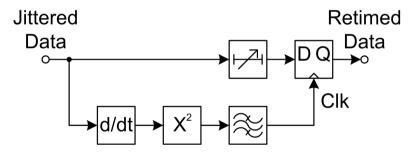

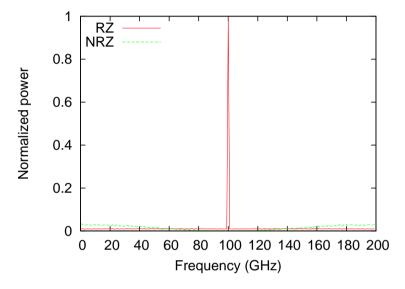

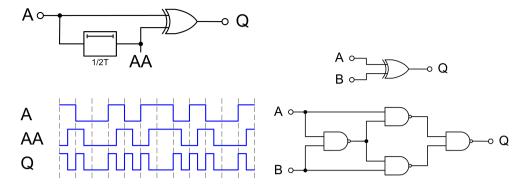

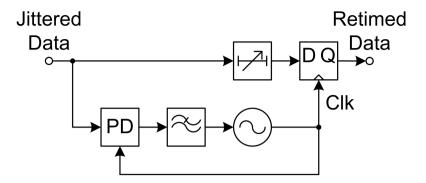

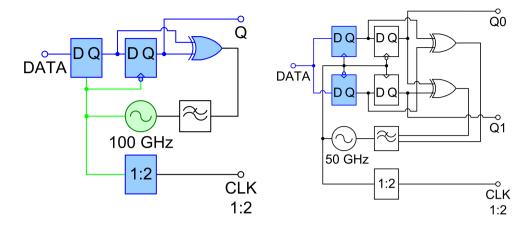

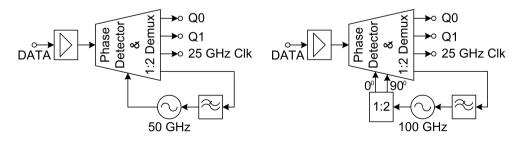

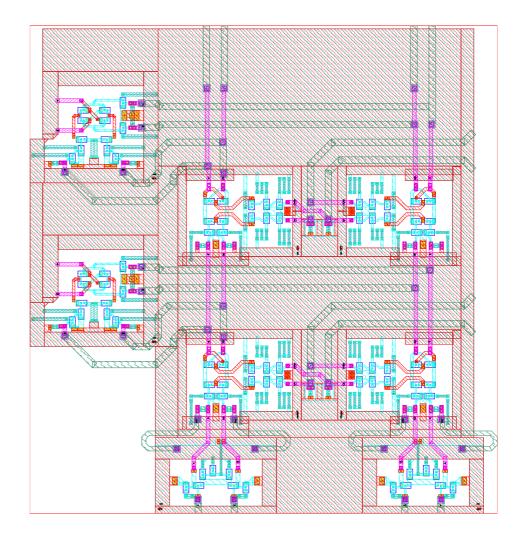

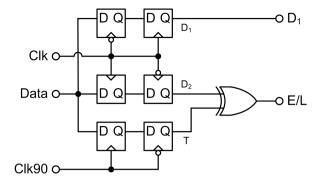

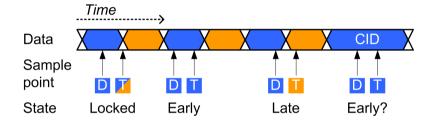

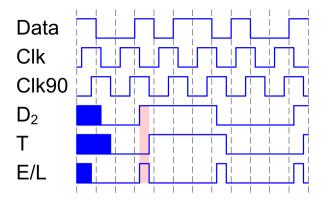

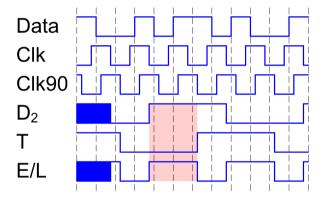

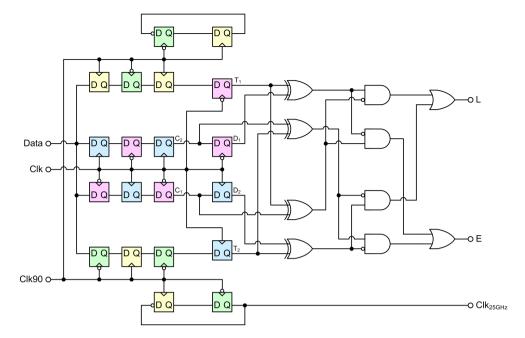

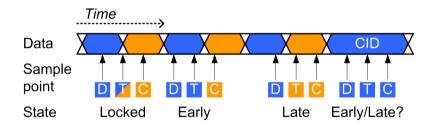

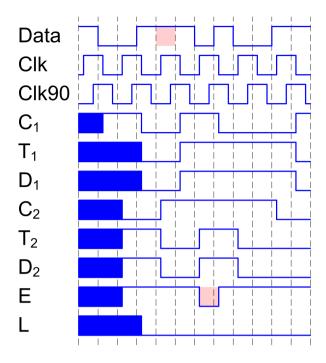

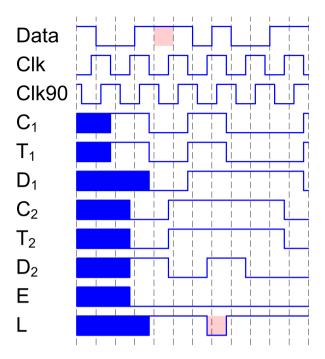

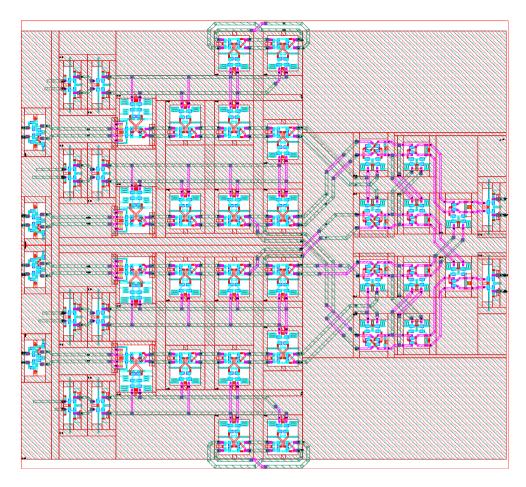

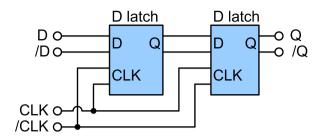

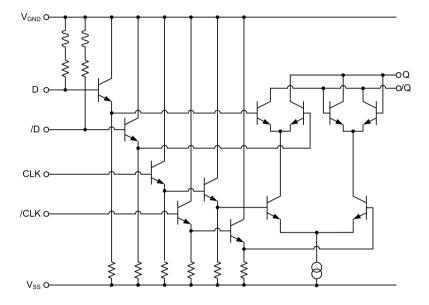

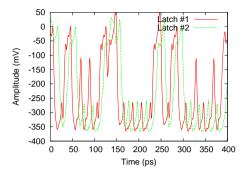

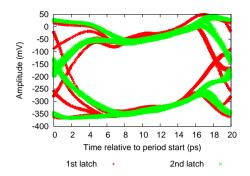

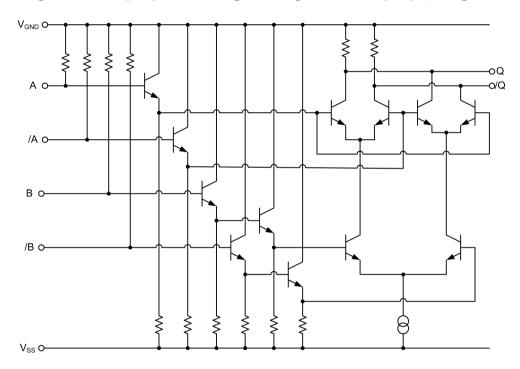

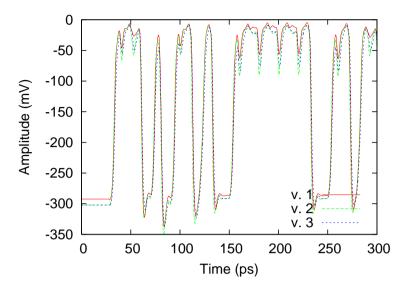

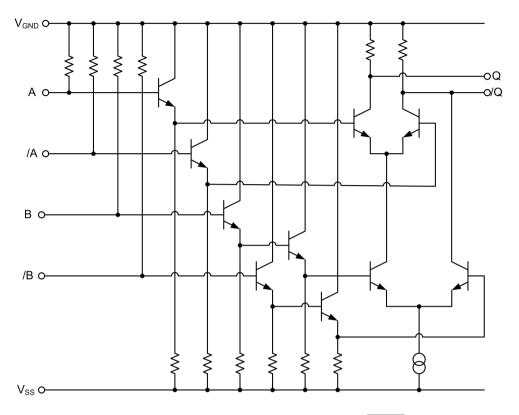

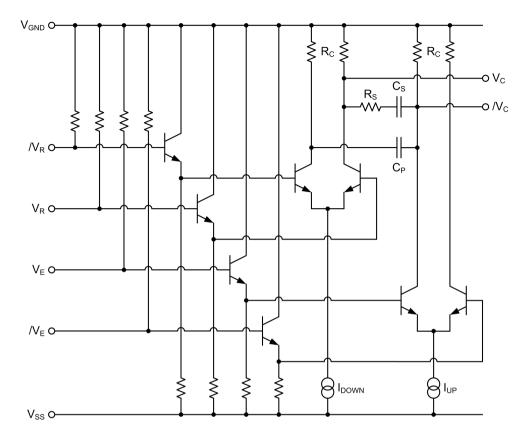

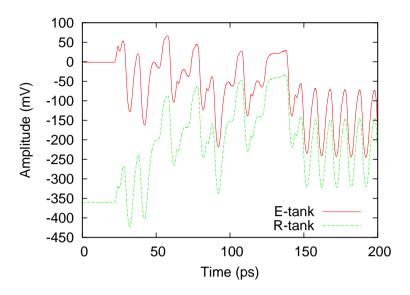

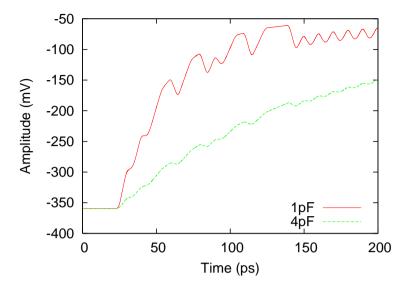

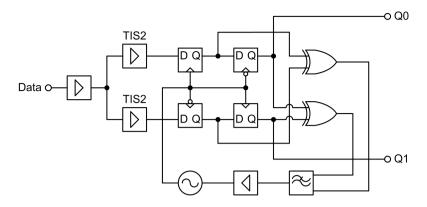

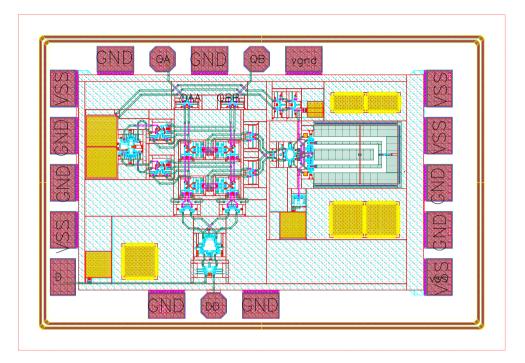

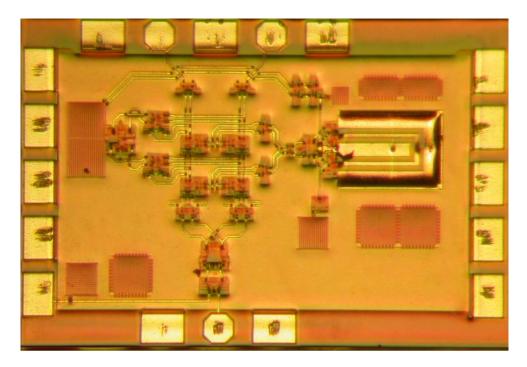

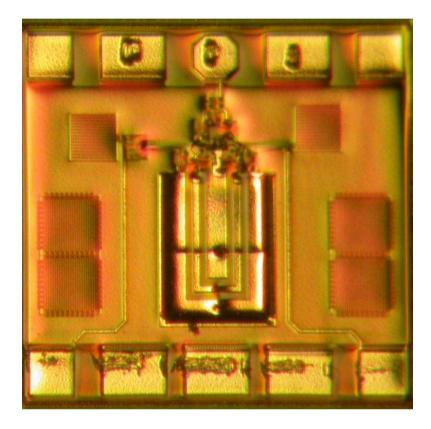

circuits.